# Design, Fabrication, and Characterization of Nano-scale Cross-Point Hafnium Oxide-Based Resistive Random Access Memory

A Thesis

Presented to The Academic Faculty

By

Noah Ellis

In Partial Fulfillment Of the Requirements for the Degree Master of Science in Materials Science and Engineering

Georgia Institute of Technology

May 2016

**Copyright © Noah Ellis 2016**

# Design, Fabrication, and Characterization of Nano-scale Cross-Point Hafnium Oxide-Based Resistive Random Access Memory

Approved by:

Dr. Eric Vogel, Advisor School of Materials Science and Engineering *Georgia Institute of Technology*

Dr. Mark D. Losego School of Materials Science and Engineering Georgia Institute of Technology

Dr. Faisal Alamgir School of Materials Science and Engineering *Georgia Institute of Technology*

Date Approved: April 21, 2016

## ACKNOWLEDGEMENTS

I would like to thank Dr. Eric Vogel for his generosity in allowing me to participate in this project, as well as for his patience and support throughout my time in his research group. Thanks also to Dr. Mark Losego and Dr. Faisal Alamgir for agreeing to serve on my committee. Additionally I would like to thank Chris Yang and Devin Brown as well as the rest of the IEN clean room staff for all the support and guidance they provided me during the fabrication process. Thanks also to all the members of the Vogel lab past and present for their support and feedback during all phases of the project. Finally, I would like to thank my family, without whose support and encouragement my participation in this project would never have been possible.

# TABLE OF CONTENTS

| Page                                                                         |

|------------------------------------------------------------------------------|

| ACKNOWLEDGEMENTSiii                                                          |

| LIST OF TABLESvi                                                             |

| LIST OF FIGURESvii                                                           |

| SUMMARYix                                                                    |

| CHAPTER                                                                      |

| 1 INTRODUCTION1                                                              |

| 1.1 Motivation1                                                              |

| 1.2 Non-Volatile Memory2                                                     |

| 1.3 Flash Memory3                                                            |

| 1.4 Future of Flash Memory7                                                  |

| 1.5 Memristance and Memristive Systems                                       |

| 1.6 Memristive Systems as NVM12                                              |

| 1.6.1 Electrochemical Mechanism13                                            |

| 1.6.2 Valence Change Mechanism14                                             |

| 1.6.3 Thermomechanical Mechanism15                                           |

| 1.6.4 Resistive Random Access Memory as NVM15                                |

| 1.7 Metal Oxide RRAM17                                                       |

| 1.8 Metal Oxide RRAM Functionality17                                         |

| 1.9 Conduction in Metal Oxide RRAM Cells21                                   |

| 1.10 HfO <sub>2</sub> -based Metal Oxide RRAM23                              |

| 1.11 Fundamental Performance Metrics for HfO <sub>2</sub> Metal Oxide RRAM28 |

| 1.11.1 LRS                                                                   |

| 1.11.2 HRS                                                                   |

| 1.11.3 Forming Voltage                                                       |

| 1.11.4 Reset Current                                                         |

| 1.12 Thesis Overview                                                         |

| 2 DESIGN AND FABRICATION OF HfO2 RRAM                           |

|-----------------------------------------------------------------|

| 2.1 RRAM Device Design Considerations                           |

| 2.2 Design 1                                                    |

| 2.3 Process Development                                         |

| 2.3.1 Determination of Electron Beam Dosage for Patterning HSQ4 |

| 2.3.2 Design 1 Process Flow                                     |

| 2.4 Characterization of Design 1 Outcomes                       |

| 2.5 Effect of Electron Beam Dosage on PMMA Cross-linking4       |

| 2.6 Design 25                                                   |

| 2.6.1 Design 2 Process Flow                                     |

| 2.7 Characterization of Design 2 Outcomes                       |

| 2.8 Chapter Summary                                             |

| 3 CHARACTERIZATION OF HfO2 RRAM                                 |

| 3.1 Switching Parameter Analysis5                               |

| 3.1.1 Forming, Set, and Reset voltages5                         |

| 3.1.2 LRS and HRS6                                              |

| 3.1.3 Reset Current                                             |

| 3.2 Chapter Summary                                             |

| 4 CONCLUSIONS AND FUTURE WORK                                   |

| 4.1 Conclusions                                                 |

| 4.2 Future Work                                                 |

| APPENDIX A: DESIGN 1 PROCES FLOW                                |

| APPENDIX B: DESIGN 2 PROCES FLOW                                |

| REFERENCES                                                      |

# LIST OF TABLES

| Table 1:Resistivity of TiN After PMMA/HSQ Removal.    52 | able 1:Resistivity of TiN Afte | r PMMA/HSQ Removal |  |

|----------------------------------------------------------|--------------------------------|--------------------|--|

|----------------------------------------------------------|--------------------------------|--------------------|--|

# LIST OF FIGURES

| Figure 1.1: Cross-section of a floating gate transistor                        | 4  |

|--------------------------------------------------------------------------------|----|

| Figure 1.2: Energy band diagram of a floating gate transistor                  | 5  |

| Figure 1.3: Tunneling mechanisms in a floating gate transistor                 | 6  |

| Figure 1.4: Cross-point configuration of TiO <sub>2</sub> -based memristors    | 10 |

| Figure 1.5: Operation of TiO <sub>2</sub> -based memristors                    | 11 |

| Figure 1.6: Periodic table of common metal oxide RRAM materials                | 18 |

| Figure 1.7: Typical metal oxide RRAM cell                                      | 19 |

| Figure 1.8: RRAM conductive filaments                                          | 20 |

| Figure 1.9 : Conduction mechanisms through a metal oxide RRAM cell in the HRS. | 23 |

| Figure 1.10: Multi-phonon TAT model for TiN/HfO <sub>x</sub> /TiN RRAM         | 27 |

| Figure 1.11: Compliance current and CF cross-sectional area                    | 29 |

| Figure 1.12: Relationship between compliance current and LRS                   | 31 |

| Figure 1.13: Cell area and resistance                                          | 32 |

| Figure 1.14: Relationship between oxide thickness and forming voltage          | 33 |

| Figure 1.15: Cell area and forming voltage                                     | 35 |

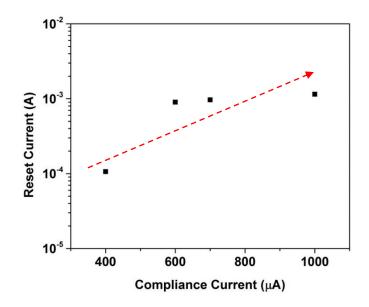

| Figure 1.16: Reset current and compliance current                              | 36 |

| Figure 2.1: Design 1 RRAM                                                      | 40 |

| Figure 2.2: Base dose determination                                            | 42 |

| Figure 2.3: SEM image of a design 1 RRAM electrode                             | 43 |

| Figure 2.4: EBL patterning of bottom electrodes for design 1 RRAM              | 46 |

| Figure 2.5: Typical current-voltage performance of design 1 RRAM               | 47 |

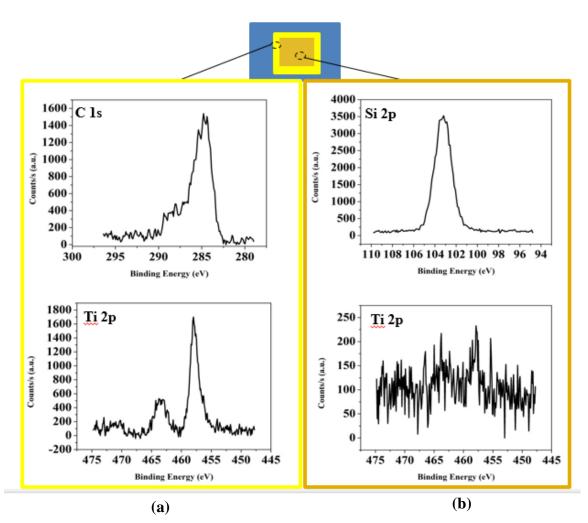

| Figure 2.6: XPS data for the surface of a TiN test structure                   | 51 |

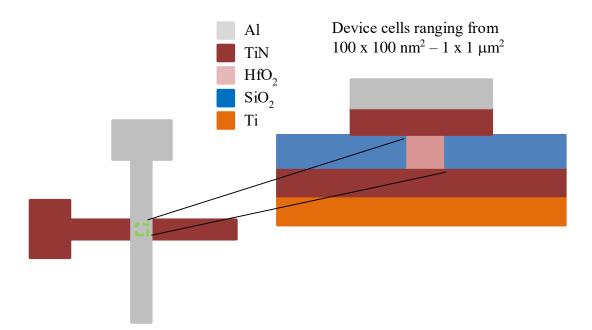

| Figure 2.7: Design 2 RRAM                                                      | 53 |

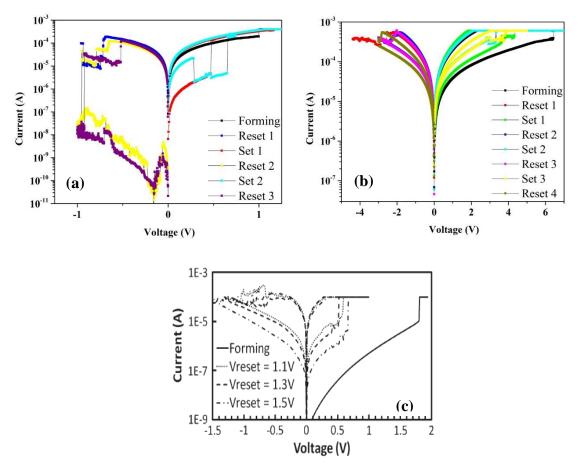

| Figure 3.1: Current-voltage curves for HfO <sub>2</sub> RRAM                   | 58 |

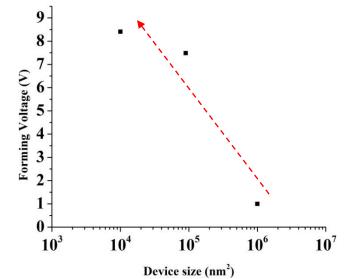

| Figure 3.2: Average forming voltage vs. device area                            | 59 |

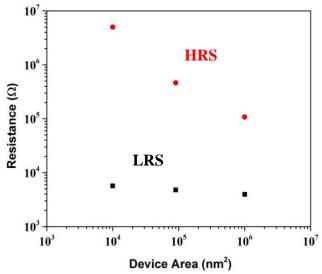

| Figure 3.3: Change in resistance state magnitudes with device area             | 60 |

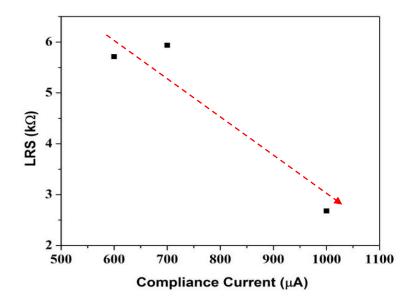

| Figure 3.4: Change in LRS with compliance current         | .60 |

|-----------------------------------------------------------|-----|

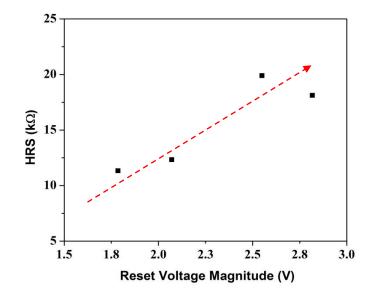

| Figure 3.5: Change in HRS magnitude with reset voltage    | .61 |

| Figure 3.6: Reset current vs. compliance current          | .63 |

| Figure A.1: EBL wafer-level and die-level alignment marks | 67  |

| Figure A.2: Sample bottom electrode pattern               | 69  |

| Figure A.3: Sample top electrode pattern                  | .71 |

| Figure A.4: Sample bottom electrode opening pattern       | 72  |

| Figure A.5: Single completed device array                 | 74  |

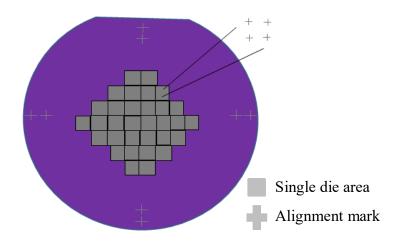

| Figure B.1: EBL and OL alignment marks                    | 76  |

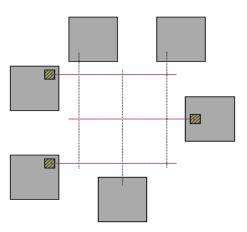

| Figure B.2: Sample bottom electrode pattern               | .81 |

| Figure B.3: Sample device cell opening pattern            | 83  |

| Figure B.4: Sample top electrode pattern                  | .85 |

| Figure B.5: Sample bottom electrode opening pattern       | .86 |

| Figure B.6: Single completed device array                 | 87  |

## SUMMARY

Non-volatile memory (NVM) is a form of computer memory in which the logical value (1 or 0) of a bit is retained when the computer is in its' powered off state. Flash memory is a major form of NVM found in many computer-based technologies today, from portable solid state drives to numerous types of electronic devices. The popularity of flash memory is due in part to the successful development and commercialization of the floating gate transistor. However, as the floating gate transistor reaches its' limits of performance and scalability, viable alternatives are being aggressively researched and developed. One such alternative is a memristor-based memory application often referred to as ReRAM or RRAM (Resistive Random Access Memory). A memristor (memory resistor) is a passive circuit element that exhibits programmable resistance when subjected to appropriate current levels. A high resistance state in the memristor corresponds to a logical '0', while the low resistance state corresponds to a logical '1'. One memristive system currently being actively investigated is the metal/metal oxide/metal material stack in which the metal layers serve as contact electrodes for the memristor with the metal oxide providing the variable resistance functionality. Application of an appropriate potential difference across the electrodes creates oxygen vacancies throughout the thickness of the metal oxide layer, resulting in the formation of filaments of metal ions which span the metal oxide, allowing for electronic conduction through the stack. Creation and disruption of the filaments correspond to low and high resistance states in the memristor, respectively. For some time now,  $HfO_2$  has been researched and developed to serve as a high-k material for use in high performance

ix

CMOS MOSFETs. As it happens, HfO<sub>2</sub>-based RRAM devices have proven themselves as viable candidates for NVM as well, demonstrating high switching speed (< 10 ns), large OFF/ON ratio (> 100), good endurance (>  $10^6$  cycles), long lifetime, and multi-bit storage capabilities. HfO<sub>2</sub>-based RRAM is also highly scalable, having been fabricated in cells as small as 10 x 10 nm<sup>2</sup> while still maintaining good performance. Previous work examining switching properties of micron scale HfO<sub>2</sub>-based RRAM has been performed by the Vogel group. However, a viable process for fabrication of nano-scale RRAM is required in order to continue these studies. In this work, a fabrication process for nano-scale cross-point TiN/ HfO<sub>2</sub>/TiN RRAM devices will be developed and described. Materials processing challenges will be addressed. The switching performance of devices fabricated by this process will be compared to the performance of similar devices from the literature in order to confirm process viability.

# **Chapter 1**

# Introduction

## **1.1 Motivation**

Semiconductor digital logic devices, key components in major computing and information technologies, have transformed many aspects of human society over the past four to five decades. Semiconductor memory devices in particular are partially responsible for both the speed of operation as well as the massive data storage capabilities exhibited by modern computers, portable electronics, and many other important commercial applications. The semiconductor technology industry has long been engaged in an aggressive trend of downscaling components in pursuit of higher performance speed, higher density of both devices and data, lower power consumption, and increased functionality of electronic products and systems. Consequently, nonvolatile memory (NVM) products have been developed and manufactured down to a  $\sim 16$ nm critical dimension. However, a number of serious challenges face scaling to the < 10nm dimension in order to achieve ever higher data and code storage capabilities [1]. As one possible solution for these challenges, alternative memory technologies based on material systems which demonstrate programmable resistance, or 'memristive', characteristics are being researched and in some cases developed. One such NVM alternative is resistive random access memory, or RRAM. HfO<sub>2</sub>-based RRAM has demonstrated excellent switching characteristics as well as potential scalability. In this work, the design, fabrication, and characterization of nano-scale cross-point HfO<sub>2</sub>-based RRAM will be discussed towards the aim of enabling continued studies intended to

develop a fundamental understanding of the impact of nano-scale dimensions on filament formation. In the following chapter, a brief background on NVM will be provided, along with discussions about memristance, resistive switching mechanisms, and basic metaloxide RRAM functionality. In chapter 2, a successful process for fabrication of nanoscale cross-point HfO<sub>2</sub>-based RRAM will be described, as well as processing challenges identified and addressed along the way. In chapter 3, the performance of the RRAM devices will be characterized and compared with the performance of similar devices from previous works, with a focus on the impact of scaling on fundamental device performance metrics. In the last chapter, conclusions as well as suggestions for further work will be offered.

#### **1.2 Non-volatile memory**

Computer memory can be separated into two broad classifications: volatile and non-volatile. Volatile memory requires a powered state in order to maintain data storage capabilities. Two baseline forms of volatile memory are dynamic random access memory (DRAM), which achieves a high memory density by storing bits of information on individual capacitors within an integrated circuit, and static random access memory (SRAM), which has very fast reading and writing capabilities and stores a single bit of information on multiple transistors simultaneously [2,3]. Non-volatile memory on the other hand, while generally exhibiting reduced performance capabilities as compared to volatile memory [4], allows for data retention in the powered-off state, which makes it a very desirable form of data storage for a wide range of electronics applications including consumer, automotive, computing, and communication. The explosion in these markets over the past decades, particularly in the portable electronics market, has driven the

success of a form of NVM called flash memory, which stores one or more bits of information on a single floating-gate transistor. Flash memory has allowed for an excellent compromise between cost, reliability, and performance capabilities such as data density, programming speed, and retention [4,5].

#### **1.3 Flash memory**

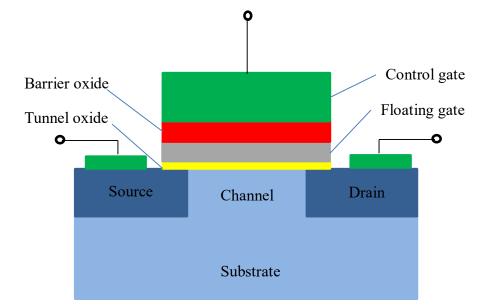

Flash memory in its modern forms evolved in the 1980's from a type of memory called EPROM (erasable programmable read-only memory) that required exposure to UV light in order to execute the erase procedure (the term 'flash' arose from the fact that the data in an entire memory array could be erased very quickly, i.e. in a 'flash'). Improvements on EPROM technology eventually led to the development of the two main forms of flash memory in the memory market today: NOR flash and NAND flash. Both types owe their success in part to the flexibility of the program and erase operations [4,5]. NOR flash memory can be both programmed and erased on the individual cell (single device) level, while offering comparatively low storage densities compared to NAND. NAND flash also consists of individually programmable cells, however the erase procedure must be performed on blocks of cells simultaneously. NAND on the other hand offers much greater storage densities as compared to NOR, and has therefore become the dominant form of flash memory [6]. Both forms exhibit good endurance (i.e., the capability of retaining information after many program/erase/read cycles) as well as retention (capability of maintaining stored information for long periods of time), and have the floating gate transistor as their primary functional basis. Figure 1.1 below shows the general structure of a floating gate transistor.

Figure 1.1. Cross-section of a floating gate transistor.

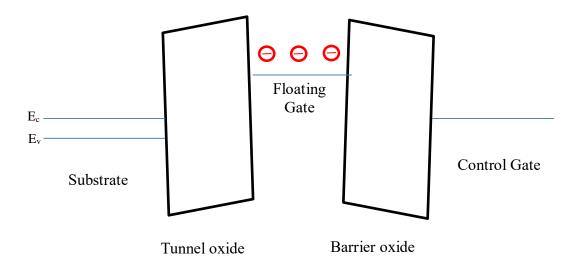

The basic operating principle of any floating gate transistor involves the ability to have its' threshold voltage (i.e., the minimum voltage differential between the gate and the source terminals required to achieve conduction between the source and drain terminals) controllably altered between different magnitudes which in turn correspond to different logic states of the cell. The "program" and "erase" operations for an individual NAND flash cell (i.e., a floating gate transistor) correspond to inducing the desired change in the value of the threshold voltage for the cell. For single-bit cells, these threshold voltage values and their corresponding conductive states correspond to logical 1's or 0's stored as part of a binary digital byte or word. The "read" operation for an individual cell consists of applying a gate voltage to the transistor between the known low and high values of the threshold voltage, then measuring the resulting current that flows through the cell[6]. Program and erase operations on a floating gate transistor consist of generation or removal of charge on the floating gate, facilitated by injection onto or removal of electrons from the gate, respectively. Both the program and erase operations consist of application of the appropriate voltage across the control gate, source, and drain terminals of a floating gate transistor such as that in Figure 1.1. This causes electrons to tunnel back and forth from the floating gate through the tunnel oxide in a direction consistent with the operation being performed. The key functionality lies in the fact that the floating gate acrts as potential well. Once a charge has been applied to it, electrons cannot escape without the application of an external electric field (see Figure 1.2 below) [5]. The two primary electron tunneling mechanisms used for the program and erase operations in a NAND flash cell are direct tunneling and Fowler-Nordheim (FN) tunneling .

Figure 1.2 Energy band diagram of a floating gate transistor showing electrons trapped on the floating gate.

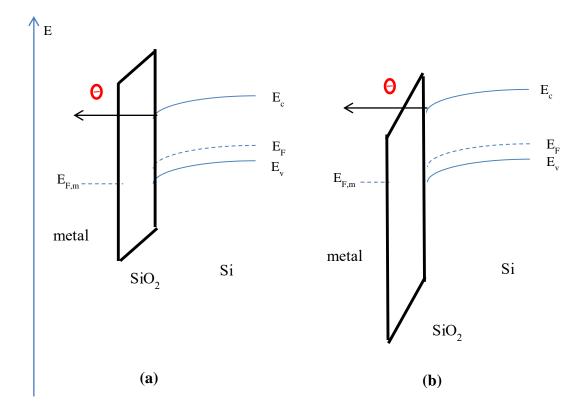

The FN tunneling mechanism occurs when large magnitude electric fields are directed through a thin oxide. The energy band diagram for the oxide becomes very steep at high energies, resulting in a higher probability of an electron being able to pass through the barrier. Figure 1.3 shows an energy band diagram of the primary tunneling mechanisms in a floating gate transistor.

Figure 1.3 Tunneling mechanisms in a floating gate transistor (a) direct tunneling (b) FN tunneling

Although the operating mechanisms for popular and successful forms of flash memory such as NAND –type memory cells are well understood, flash memory faces emergent challenges as the trend toward further device scaling in relentless pursuit of higher device density and increased performance in the microelectronics industry continues. These challenges will be discussed in the following section.

#### **1.4 Future of flash memory**

The semiconductor technology industry has long been engaged in an aggressive trend of downscaling components in pursuit of higher performance speed, higher density of both devices and data, lower power consumption, and increased functionality of electronic products and systems. Currently, flash memory products have been developed and manufactured down to a ~16 nm critical dimension. However, a number of serious challenges face scaling to the < 10 nm dimension in order to achieve ever higher data and code storage capabilities [1]. Key challenge areas include:

1. *Performance, reliability, and endurance requirements*: Reducing the thickness of the tunneling oxide and control dielectric have been key processing parameters driving lower power consumption, shorter program/erase times, and increased device density. However, a bottleneck has occurred at the  $\sim 10$  nm thickness range, below which serious problems emerge. Some of these problems include unwanted injection of electrons into the tunnel oxide during erase operations and loss of adequate control over the conduction channel due to undesirably low capacitive coupling between the channel and the tunneling oxide layer. Thinner oxides also become more prone to charge leakage and defect formation due to voltage stress, both of which reduce performance quality over time [4,8].

2. *Increased data storage density*: Limits on device dimensions and therefore device density are naturally imposed due to increasing cell-to-cell electrical interference and breakdown between word lines as size decreases. Additionally few-electron storage issues arise due to thinner oxide layers, which limits data density as well as increasing potential for unwanted electrical noise [1].

Potential solutions to this range of issues include the development of multi-bit storage capabilities, as well as development of novel 3-D architectures in order to increase overall memory efficiency as well as data and device densities. Alternative material systems and memory technologies such as RRAM which exploit memristive characteristics are being explored as well. This novel memory application as well the property of memristance will be examined more closely in the sections that follow.

#### **1.5 Memristance and memristive systems**

As just stated, novel forms of NVM with memristors as the functional basis are being researched and developed as one of the possible solutions for driving the continued increase in data density and device performance in the NVM market.

In 1971, Leon Chua predicted the existence of a fourth passive circuit element called a memristor ("memory resistor"), which exhibited behavior he called memristance ("memory resistance"). Through a quasi-static expansion performed on Maxwell's equations of electromagnetism analogous to that performed in order to derive the relationships between voltage and current for resistors, magnetic flux and current for inductors, and voltage and charge for capacitors, Chua established a relationship between flux-linkage and charge which he predicted would be demonstrated by memristors [7,10]:

$$M(q) \equiv \frac{d\varphi(q)}{dq} \tag{1.1}$$

,where *M* is memristance,  $\varphi$  is the flux linkage and *q* is the charge. The voltage across a charge-controlled memristor is then given by

$$v(t) = M(q(t))i(t)$$

(1.2)

where v is the voltage, t is time, and i is the current. The reference to "memory" in the term "memristor" comes from the fact that the value of the memristance at any time  $t_0$  depends on the time integral of the current (i.e., the charge q) through the memristor from time  $t = -\infty$  to  $t = t_0$ . Thus, while a memristor behaves as an ordinary resistor at any time  $t_0$ , its' resistance value is determined by the complete past history of the current through the memristor. As equation 1.2 shows, for linear passive circuit elements the memristance is constant and therefore indistinguishable from standard electrical resistance. When M is a function of q however, the resistance becomes non-linear, and Chua found that no combination of non-linear passive resistive, capacitive, or inductive components could reproduce the i-v characteristics of a memristor [7,10]. Five years later in 1976, Chua and Kang generalized the memristor concept by introducing a broad class of non-linear dynamical systems they termed memristive systems, which are described by the following equations [8,9]:

$$v = R(w, i)i \tag{1.3}$$

$$\frac{dw}{dt} = f(w, i) \tag{1.4}$$

, where R is the resistance, f is a function, w is a set of state variables, and R and f can be explicit functions of time. At the time of these publications, Chua and Kang suggested that many systems could be described as memristive, including certain electrochemical cells, nerve axon membranes, thermistors, discharge tubes, and others, though no system had ever been formally identified as such.

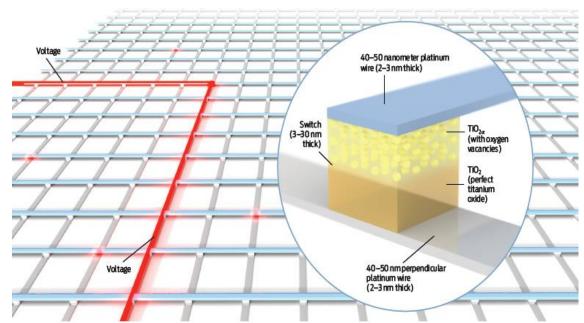

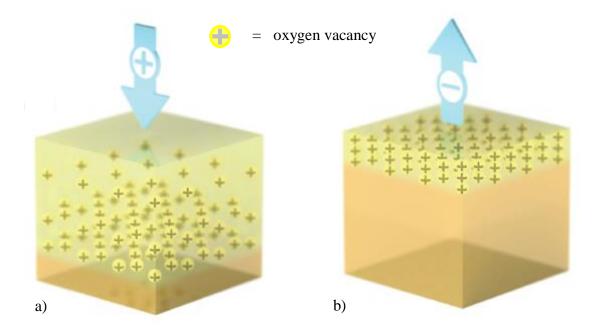

The first passive physical system demonstrably exhibiting memristance as such was announced in a Nature journal article in 2008 by Waser, et.al., and was created by R.S. Williams and his research team in the Hewlett-Packard labs [8,10]. Their memristor structure was a metal-metal oxide-metal material system, consisting of a cross-point array of 40 nm wide platinum wires, with 40 nm cubes of titanium dioxide (TiO<sub>2</sub>) at each cross-point, which themselves consisted of two layers : a perfectly stoichiometric lower layer (2:1 Ti to O), and an oxygen deficient upper layer of TiO<sub>2-x</sub> (x  $\approx$  0.05) (see Figure 1.4 below). The mechanism for the memristive behavior is as follows: application of a positive voltage to electrode in contact with the TiO<sub>2-x</sub> region of the

Figure 1.4. Cross-point configuration of TiO<sub>2</sub>-based memristors showing structure and composition of a single memristor cell. © 2008 IEEE

cell causes oxygen vacancies from this O-deficient region to migrate towards the stoichiometric region (Figure 1.5.a). This migration in turn causes the boundary between the two layers to migrate away from the more positive voltage source towards the less positive source, functionally increasing the length of the metal-oxide region consisting of conductive  $TiO_{2-x}$  as opposed to insulating  $TiO_2$ . The increased effective concentration of

$TiO_{2-x}$  then functionally reduces the resistance in the memristor by increasing the length of the conductive region, thereby enhancing electronic current through the cell. Application of a negative voltage has the reverse effect, i.e. the oxygen vacancies migrate towards the oxygen deficient region once again, thus effectively increasing the percentage of insulating  $TiO_2$  in the memristor, thereby increasing the resistance through the cell (Figure 1.5.b). What makes this system memristive is the fact that no migration of

Figure 1.5 Operation of TiO<sub>2</sub>-based memristors a) Application of a positive voltage to the TiO<sub>2-x</sub> region of the cell causes the oxygen vacancies to migrate towards the opposite electrode, thereby increasing the effective length of the conductive region of the cell. b) Reversing the voltage polarity has the opposite effect, restoring the insulating effect of the TiO<sub>2</sub> by increasing its' effective concentration in the cell. © 2008 IEEE

oxygen ions occurs if no voltage is being applied. Hence, the switch "remembers" its' most recent resistance state. The relationship between voltage and current for these memristors is modeled by the equations

$$\nu(t) = \left(R_{ON}\frac{w(t)}{D} + R_{OFF}\left(1 - \frac{w(t)}{D}\right)\right)i(t)$$

(1.5)

$$\frac{dw}{dt} = \mu_V \frac{R_{ON}}{D} i(t) \tag{1.6}$$

where  $R_{ON}$  is the resistance in the sub-stoichiometric region, *w* is the distance which the boundary between the layers has traveled(defined on the interval [0,D]),  $R_{OFF}$  is the resistance in the stoichiometric region, and  $\mu_V$  is the mobility of the oxygen vacancies.  $R_{ON}$  and  $R_{OFF}$  are treated as resistances connected in series, and D is the complete width of the metal-oxide region of the cell[8]. As equation 1.5 implies, the overall resistance of the cell decreases as the boundary between the different regions moves from w=0 to w=D. Additionally, the i-v characteristics of these cells showed hysteretic (non-linear) behavior under various voltage application regimes, which eventually provided the clue that led Williams and his team to connect this behavior to the memristance that Chua had theorized 40 years earlier [10].

As it happened, the switching behavior was fast, occurred over very small distance ranges (3-30 nm), and had significant off/on resistance ratios (approx. 1000) which remained stable for very long periods of time[10]. This made it apparent to Williams and others that this new memristive system (or others that functioned in a similar fashion), could represent a viable candidate as a form of NVM or any other computing systems whose functionality requires various resistance states, principally by exploiting the hysteretic i-v behavior as a form of resistive switch [10,11].

#### 1.6 Memristive Systems as NVM

In addition to the memristive system described above, many other similar material systems classifiable as memristive have been researched, i.e., metal-insulator-metal (MIM) stacks which exhibit variable resistance[11,12]. While the physical driving force

is usually electrically induced, functionality of the resistive switching mechanisms exhibited by these MIM stacks can vary quite distinctively [11]. For example, mechanical forces can be utilized to induce memory effects, or changes in ferromagnetic domain polarization, or changes in phase, e.g., change between amorphous and crystalline phases [11]. Redox-reaction-based mechanisms in these systems are a common means of resistance change, and these mechanisms can be broadly classified as falling into three categories: change in resistance due to a redox reaction induced by electrochemical metallization, valence change, or thermochemical mechanisms[11]. These classifications and their mechanisms are briefly described in the following sections.

### **1.6.1 Electrochemical mechanism**

In these systems, the resistive switching mechanism involves the electrochemical dissolution of one electrode metal and its' subsequent deposition at the other electrode. An individual MIM cell consists of an electrochemically active electrode such as Ag, Cu, or Ni, and an inert electrode such as Pt, Ir, W, or Au. Sandwiched between the two metals is a solid electrolyte capable of conducting metal ions. Prior to switching, a cell is in its' high resistance state. The switch to a low resistance state results from the formation of a metallic conductive filament through the insulating region, which can be characterized in three steps[11,13]:

1. Dissolution at the active electrode by the reaction

$$M \to M^{n+} + ne^- \tag{1.7}$$

2. Migration of the  $M^{n+}$  cations through the electrolyte under the influence of an applied electric field.

3. Reduction and electrocrystallization of the metal ions at the inert electrode surface according to the reaction

$$M^{n+} + ne^- \to M \tag{1.8}$$

Interestingly, this resistance change mechanism was predicted by Chua in his original 1971 paper [7].

### 1.6.2 Valence change mechanism

In valence change systems, the resistance change in the MIM cell is induced through a valence change of metal cations present in the insulator layer. Typical examples of this mechanism are found in MIM structures that contain transition metal oxides as the insulator[11]. Application of a voltage of the appropriate magnitude and polarity at one of the electrodes can induce diffusion of oxygen anions through the insulator layer. The ionization process for oxygen can be described by

$$O_0 = V_0'' + 0'' \tag{1.9}$$

where standard Kroger-Vink notation is used to describe lattice occupancy and charge conditions. As a result of the presence of positively charged oxygen vacancies, a conductive "trail" of metal cations remains which allows for electronic conduction through the stack, by the reactions

$$V_0' = V_0'' + e' \tag{1.10}$$

$$V_0 = V_0' + e'$$

(1.11)

The creation of a conductive pathway thereby changes the resistance state of the MIM cell from a high resistance to a low resistance state after application of the voltage. The

reverse reaction, i.e. the change back to a high resistance state, is governed by recombination of oxygen anions with unoccupied oxygen vacancies by the reverse of reaction 1.12 [14].

### **1.6.3** Thermochemical mechanism

The thermochemical resistance change mechanism results from local Joule heating effects which occur in the insulator due to high current resulting from a voltage applied across the electrodes. If a large enough electric field is applied across the insulator, electrical breakdown, i.e., a shift to a conductive state, can occur [15]. After breakdown, the insulator is in a low resistance state until such time as the film can be recovered in some way, e.g., by subsequent application of another voltage.

It is important to note that more than one of these mechanisms can contribute to the resistance change in a particular system, and isolation of one of the mechanisms as being the dominant one, where possible, will depend on the nature of the particular switching system. Also, analytical models for key values associated with switching tend to be particular to specific material systems, making generalization of the overall mechanisms even more challenging [14,16].

#### 1.6.4 Resistive random access memory as NVM

NVM applications that exploit resistance change mechanisms have come to be generally referred to as resistive random access memory (RRAM or ReRAM). The exploitation of the resistance changes described above in pursuit of a viable form of nextgeneration NVM technology requires that any RRAM application meets certain general performance specifications [11]. These include:

1. *Write operation*: the write operation for an RRAM cell should be in the range of a few hundred millivolts to a few volts in order to not only be CMOS compatible, but to provide an advantage over typical flash programming voltages.

2. *Read operation*: Read voltages in general must be capable of being small enough such that application of the voltage does not induce resistance change in the cell. This necessity introduces a challenge to the low magnitude requirement for the write voltage due to fact that the read voltage cannot be less than approximately one-tenth of the write voltage for practical reasons of circuit design.

3. *Resistance ratio*: the ratio of  $R_{off}/R_{on}$  must be > 10 in order to allow for technologies that incorporate small and efficient sense amplifiers, making them effective cost competitors with flash memory.

4.*Endurance*: flash memory can endure up to  $10^7$  write cycles, depending on the particular type. RRAM cells would need to be at least approximately this robust in terms of endurance in to order to be viable commercially.

5. *Data retention* :universal NVM standards require data retention times to be >10 years up to a thermal stress of 85° C, and electrical stress due to a constant stream of read voltage applications. Again RRAM cells would have to at least approximately match these specifications in order to be competitive in the NVM market.

Various forms of RRAM utilizing a MIM structure with transition metal oxides serving as the insulating layer have proven to be up to the challenge of matching these

performance requirements in many cases. The properties and functionality of metal oxide RRAM will be examined in more detail in the following section.

## 1.7 Metal Oxide RRAM

As mentioned in the previous section, MIM RRAM in which metal oxides serve as the insulator have demonstrated the potential to serve as viable NVM applications. Across a range of material systems, RRAM cells of this type have demonstrated CMOScompatibility, very fast read/write speeds, excellent endurance, and very low power/energy consumption consistent with the general standards for viability discussed in the previous section [11,16]. Additionally, it is envisioned that RRAM cells could be readily stacked into a 3-D cross-point architecture, providing the potential to contribute to a revolution not only in memory technology, but to play a key role in next-generation computing system architectures as well[10,16].

A variety of metals and metal oxides have been characterized for RRAM electrodes and switching layers, respectively. Common insulator materials are binary metal oxides such as TiO<sub>2</sub> or HfO<sub>2</sub>. Different materials in varying combinations exhibit different switching characteristics. Common metal (electrode) and binary metal oxide (insulator) materials are shown in figure 1.6 below [16].

In the following section, the basic principles behind the general functionality of a metal oxide RRAM cell as a resistance-switching memory device will be described.

#### **1.8 Metal Oxide RRAM Functionality**

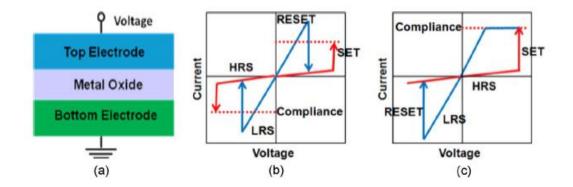

The principle behind the basic functionality of any RRAM cell is controllable switching between a high resistance state (HRS) and a low resistance state (LRS). Through application of a voltage of the appropriate magnitude and polarity at an electrode, the resistance state in the insulator can be changed, leaving the device in a

Figure 1.6 Periodic table showing common RRAM electrode (blue) and binary metal oxide (yellow) materials © 2012 IEEE.

stable altered state with respect to its' resistance, where the HRS corresponds to the OFF state, (low current) and the LRS to the ON state (high current). The change from the HRS to the LRS is often referred to as the "set" process, while the shift from LRS to HRS is called "reset". Metal oxide RRAM devices fall broadly into several categories with respect to switching mode as well. If the set and reset operations depend on the polarity of the applied voltage, this is referred to as bipolar switching, due to the necessity of applying two opposite voltage polarities in order to a complete a single ON/OFF cycle. Switching that depends only on the magnitude of the applied voltage and not the polarity is referred to as unipolar switching. When switching behavior is neither polarity- nor magnitude- dependent, the switching is called non-polar. General i-v characteristics for both the unipolar and bipolar switching modes are shown in figure 1.7 below.

Figure 1.7 a) Diagram of a typical metal oxide RRAM cell. b) Schematic of typical current-voltage characteristics of unipolar switching c) Schematic of a typical current-voltage characteristics of bipolar switching. © 2012 IEEE

For all switching modes, a maximum value of the current allowed to flow through the device, (a "compliance" current ), is imposed during the forming and set operations in order to control characteristics of the conductive filament formed during the operation. The forming operation as well the conductive filament will be discussed next.

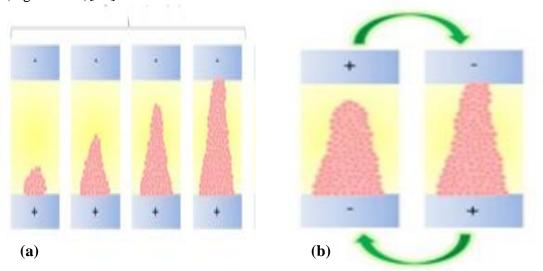

The application of a voltage across the RRAM cell induces a resistance switching event which is generally agreed upon to correspond to the formation or disruption of a conductive filament (CF) resulting from breakdown of the dielectric layer [16,17,18]. A switch to a LRS corresponds to initial formation or re-formation of a CF, while a switch to HRS corresponds to a disruption of the filament. For some material systems, fresh (i.e., never switched) cells require an initial higher voltage "forming" step in order to form the CF and thereby enable subsequent switching. Set/reset operations in these systems typically occur at lower voltages than that required for the forming step[17]. Application of the forming voltage results in the initial creation of the CF through electrically and thermally induced diffusion of oxygen anions. A conductive pathway for electrons consisting of oxygen vacancies then remains across the metal oxide layer after the voltage is removed (Figure 1.8a). Reset and set operations, respectively, correspond to the disruption and subsequent re-formation of the CF in the CF/electrode interface region (Figure 1.8b)[19].

Figure 1.8 RRAM conductive filaments a) Initial formation of a CF during the forming step. b) Schematic showing set/reset operations, which correspond to repeatable formation and disruption of the CF near the insulator/electrode interface, respectively. (Lanza, 2014)

Elimination of the higher voltage initial forming step is sometimes possible through use of appropriate design and processing parameters and insulator/electrode materials and compositions as well [16,20,21]. This is a desirable characteristic for any RRAM application as it allows for reduced energy consumption due to the removal of the necessity to include a higher voltage forming step prior to regular operation.

In the next section, conduction mechanisms through the formed CF will be examined more closely.

#### **1.9 Conduction in Metal Oxide RRAM Cells**

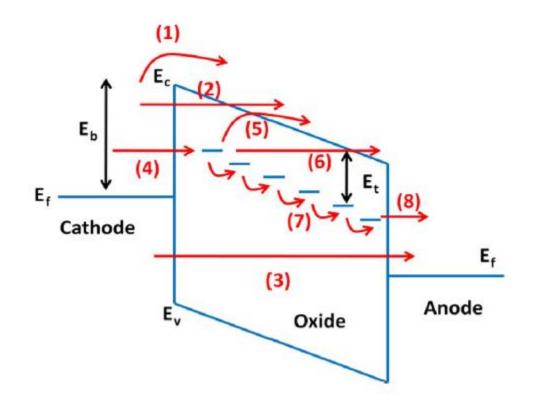

The nature of the conduction through the CF in a metal oxide RRAM cell depends on what resistance state the cell is currently in. In the LRS, cells exhibit a linear i-v relationship, typical of ohmic conduction [16,18,22]. In the HRS however, a variety of conduction models may apply, depending on the particular material system in question. Parameters such as dielectric properties of the insulator, fabrication conditions used to create the cell, and properties of the oxide/electrode interface all effect the nature of the formation of the CF. These then determine both the transition between the HRS and LRS as well as the nature of the attendant electron conduction that occurs during set/reset operations [16].The possible conduction paths for electrons traveling through metal oxide RRAM cells in the high resistance state are listed below (see Figure 1.9). Regardless of which form of conduction is dominant for a certain type of cell, electrons will always choose the least resistive path from cathode to anode.

1. *Schottky emmission*: electrons acquire enough thermal energy to overcome the oxide energy barrier and travel directly into the conduction band.(Fig. 1.9.1)

2. *Fowler-Nordheim tunneling (FN)*: when the magnitude of the applied electric field is high enough, band bending in the oxide energy barrier can allow for electrons to tunnel through the narrow portion of the energy barrier into the conduction band. (Fig. 1.9.2)

3. *Direct tunneling*: if the oxide layer is thin enough, application of a voltage across the cell allows for electron tunneling directly from one electrode to another. (Fig. 1.9.3)

If enough defects are present in the oxide layer (e.g. oxygen vacancies), then a variety of trap-assisted conduction mechanisms become possible. In these cases, the path of an individual electron through the oxide layer will always begin with conduction from an electrode to a trap (Fig. 1.9.4), and end with conduction from a trap to an electrode (Fig. 1.9.8). Trap-assisted conduction mechanisms include:

4. *Poole-Frenkel emission*: this occurs when an electron already in a trap acquires enough energy to enter the conduction band (Fig. 1.9.5).

5. *FN-like tunneling*: this effect can occur when an electron is able to enter the conduction band directly from a trap under the influence of a large electric field (Fig. 1.9.6).

6. *Trap-assisted tunneling*: depending on the wave functions of the electrons in question, electrons can "hop" from trap to trap occupying either localized energy states, or in the case of overlapping states, in conduction that resembles metallic conduction (Fig. 1.9.7).

In the next section, the conduction mechanism in metal oxide RRAM cells with  $HfO_2$  as the insulator will be examined in more detail, as this form of RRAM is not only heavily investigated in the research community, but is also the form developed and characterized in the present work.

Figure 1.9 Conduction mechanisms through a metal oxide RRAM cell in the HRS (1).Schottky emmission (2).Fowler-Nordheim tunneling (FN) (3).Direct tunneling (4) Conduction from an electrode to a trap (5).Poole-Frenkel emission (6).FN-like tunneling (7).Trap-assisted tunneling(8) Conduction from a trap to an electrode. © 2012 IEEE

#### 1.10 HfO<sub>2</sub>-based RRAM

For some time now, HfO<sub>2</sub>-based dielectric films have been researched and developed to serve as high-k materials for use in high performance CMOS MOSFETs[16]. For this reason, HfO<sub>2</sub> was a natural candidate for further examination with respect to serving as the insulator material in a metal oxide RRAM cell as well. As it happens, a variety HfO<sub>2</sub>-based RRAM devices have proven themselves as viable candidates for NVM[16]. In particular, TiN/Ti/HfO<sub>x</sub>/TiN stacks have been shown to demonstrate high switching speed (< 10 ns), large OFF/ON ratio (> 100), good endurance (>  $10^6$  cycles), long lifetime, and multi-bit storage capabilities[16,23]. HfO<sub>2</sub>-based metal

oxide RRAM stacks have also proven themselves to be highly scalable, having been fabricated in cells as small as 10 x 10 nm<sup>2</sup> while still maintaining good performance [16,24].As the focus of this paper is on TiN/HfO<sub>2</sub>/TiN RRAM, both the mechanisms for CF formation and electronic conduction in this system will be described in more detail in this section.

When a forming voltage is initially applied across a TiN/HfO<sub>2</sub>/TiN cell in a fresh state, in the low bias regime electronic current is dominated by trap-assisted tunneling through oxygen vacancies already present in the insulator layer around HfO<sub>2</sub> grain boundaries (GB's)[18]. Continuing to increase the magnitude of the applied voltage results in the generation of new vacancies at a rate governed by

$$G = G_0 e^{\left(-\frac{(E_A - bF)}{kT}\right)} \tag{1.12}$$

where G is the defect generation rate,  $G_0$  is a rate constant,  $E_A$  is the activation energy required to produce an oxygen vacancy, b is a bond polarization factor, F is the magnitude of the applied electric field, k is the Boltzmann constant, and T is the local temperature. We see that generation of new vacancies is strongly influenced by increasing the applied voltage, which increases the magnitude of the electric field across the insulator, lowering the energy barrier for generation of new vacancies.

New vacancy generation also occurs preferentially around already-existing vacancies in the growing CF. This is due to the fact that electron transfer through an individual trap causes distortion of the surrounding lattice, with consequent emission and absorption of phonons that then tend to increase the local temperature. Additionally, the generation of new oxygen vacancies further distorts the lattice, which tends to lower the activation energy for creation of additional new vacancies. This positive feedback cycle of more vacancies allowing more tunneling, which then leads to higher temperatures and lower activation energies for new vacancy generation, eventually results in formation of the CF consisting of sub-stoichiometric hafnia (HfO<sub>x</sub>), which then serves as a permanent conduction sub-band for the electrons[18,25].

Both during CF formation and set/reset operations, the rate of formation/disruption of a filament is also governed by the diffusion rate D, and recombination rate R, of oxygen anions around the CF region, where

$$D = D_0 e^{\left(\frac{-\left\{E_D - Q\frac{\lambda}{2}[F + F_L]\right\}}{kT}\right)}$$

(1.13)

and

$$R = R_0 e^{\left(\frac{-E_R}{kT}\right)} \tag{1.14}$$

with  $D_0$  and  $R_0$  the rate constants associated with diffusion and recombination respectively,  $E_D$  and  $E_R$  the activation energy required for oxygen diffusion and recombination respectively, Q the charge on an oxygen ion,  $\lambda$  the hopping distance to the nearest neighbor lattice site, F the applied electric field, and  $F_L$  the local electric field determined by oxygen anions and vacancy charge states[25].

During forming and set/reset operations, oxygen anions both diffuse away from and recombine in the bulk oxide around the CF region [24]. After the formation of the CF, the subsequent set/reset operations occur at lower voltages due to smaller values of activation energies required for diffusion and recombination as compared to the energy required for vacancy generation [25]. Consequently, reversible disruption and reformation of the CF corresponds to the diffusion of oxygen anions both by Joule heating and electric-field-induced drift over a relatively short distance ( $\sim 1 \text{ nm}([18,22])$ ) towards or away from the insulator/electrode interface (see Fig.1.8b) [18].

Due to the fact that larger temperatures increase both the rate of creation of new vacancies as well as the rate of diffusion of oxygen ions through the insulator, the values of the compliance current chosen for the forming operation have a significant effect on the size of a newly formed CF, with larger compliance currents leading to larger temperatures, which result in CF's with larger average cross-sectional areas[24].

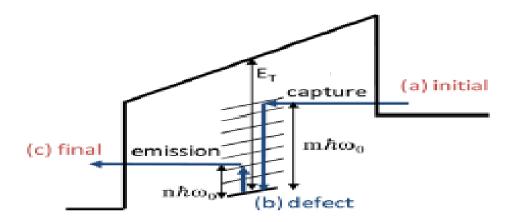

Bersuker, et. al. formulated an empirical model for the basic conduction mechanisms for a TiN/HfOx/TiN RRAM cell in various resistance states which agreed well with experimental data[18].During the forming step, electronic conduction was found to occur predominantly by multi-phonon trap assisted tunneling (TAT) through oxygen vacancies present in the dielectric layer. In the model, capture of an electron at a trap is associated with the release of energy by phonon emission of

$$\Delta E = m\hbar\omega_0 \tag{1.15}$$

where m is the total number of released phonons, and  $\omega_0$  is the frequency of a single phonon. Additionally, release of an electron from an individual vacancy is associated with a gain of energy due to phonon absorption of

$$\Delta E = n\hbar\omega_0 \tag{1.16}$$

where n is the total number of absorbed phonons. Figure 1.10 below shows an energy band diagram for the multi-phonon TAT of an electron through the dielectric layer.

Figure 1.10 Capture and emission of an electron in the multi-phonon TAT model for HfO<sub>x</sub> in TiN/HfO<sub>x</sub>/TiN RRAM. Copyright 2011, AIP Publishing LLC

Conduction through a path consisting of oxygen vacancies then is described by

$$I_p = \frac{q}{\tau_{C,max} + \tau_{E,max}} \tag{1.17}$$

where  $I_p$  is the electronic current through a percolation path, q is the charge on an electron, and  $\tau_{C,max}$  and  $\tau_{E,max}$  are the time constants associated with capture and emission of an electron to and from the slowest trap on the path, respectively. Time constants are calculated by accounting for each phonon and absorption and emission event, which are themselves determined by a number of factors such as energy levels and density of states at both traps and electrodes, as well as tunneling and occupation probabilities for an electron. As mentioned previously, conduction through a formed filament was found to be essentially metallic (ohmic) in nature [18].

In the next section, the fundamental performance metrics of metal oxide RRAM will be discussed, along with the effects of scaling on these metrics.

#### **1.11 Fundamental performance metrics for HfO<sub>2</sub> RRAM**

For any metal oxide RRAM cell, the fundamental device performance metrics are the magnitudes of the LRS, the HRS, the forming voltage, and the reset current (i.e., the current required to initiate the reset operation). How these metrics are related to key processing and material characteristics of a RRAM cell as well as the effects of dimensional scaling on overall cell performance will be discussed in the following.

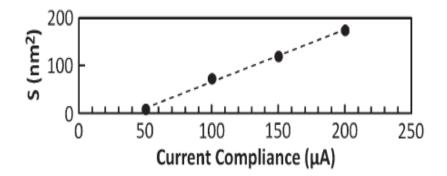

As conduction through the RRAM cell is related to formation of conductive filaments as discussed previously, control of the size of the CF during the forming step becomes of key importance with respect to subsequent cell performance metrics, particularly with respect to the magnitudes of the LRS, HRS, and reset currents. Because the current travels through a filament which occupies a small region of the electrode, current density through an individual cell will be strongly affected by the size of the CF.As mentioned previously, increasing the magnitude of the compliance current used during the forming step increases the number of oxygen vacancies produced in the insulator layer, and therefore the cross-sectional size of the CF. This relationship between compliance current and filament area for a TiN/HfOx/TiN cell is shown in fig. 1.11 below [22]. Naturally, as the filament area changes, the current density flowing through the cell during the set and reset operations will change accordingly, and hence the power consumption per set/reset operation for a single cell will change as well. Because power consumption is directly related to cost and reliability of electronic devices, control of filament size therefore becomes a key factor in the consideration of the design of an economically viable RRAM cell.

Figure 1.11 Relationship between compliance current and CF cross-sectional area (S) for TiN/HfOx/TiN RRAM. Circles are experimental data values, while the dashed line is a linear fitting. © 2013 IEEE

The larger a filament becomes, the lower the current density through the filament for a given applied voltage becomes. However, for larger filaments, it is also the case that larger current magnitudes are required during the reset operation in order to achieve sufficient oxidation of the filament tip [16,19]. As will be discussed further below, a larger filament will also result in both a larger-magnitude HRS as well as a smaller-magnitude LRS, which will then improve the value of the OFF/ON ratio for the cell. This will come at a cost of greater power consumption however, due to the necessity of a larger compliance current during forming, as well as for a larger reset current during every reset operation. Hence, a trade-off exists between filament size, performance capabilities, and power consumption for a RRAM cell.

As the functionality of a RRAM cell lies in the control of the resistance to electronic conduction through a cell, a viable analytical model of the resistance becomes an important aspect of successful development of a robust RRAM technology as well. Puglisi, et.al. have proposed an empirical expression for the resistance (R) consistent with experimental data for the TiN/HfOx/TiN system as below[22],

$$R = R_{SET} \left( e^{\left(\frac{x}{\kappa}\right)} - \frac{x}{t_{Ox}} \right)$$

(1.18)

$$R_{SET} = \rho_{Hf,CF} \frac{t_{OX}}{s} \tag{1.19}$$

,where x is the length of the oxidized (recovered) portion of an existing filament,  $\kappa$  is an empirical factor based on a TAT simulation model of current through the insulator from [18],  $\rho_{Hf,CF}$  is the resistivity of the filament,  $t_{Ox}$  is the thickness of the HfO<sub>2</sub> film, and S is the cross-sectional area of the filament.

The relationship of the filament with the fundamental performance metrics mentioned above will be further examined in the following sections.

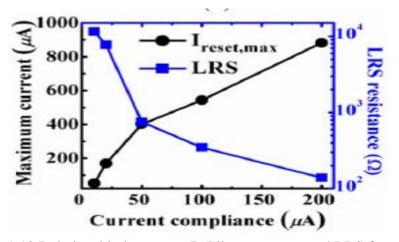

#### 1.11.1 LRS

LRS is the value of the resistance through the cell when the CF is in the ON, i.e., non-oxidized state. As equation 1.18 for  $HfO_x$  RRAM shows above, LRS corresponds to the condition where x = 0, and therefore is equivalent to  $R_{SET}$ , which is essentially ohmic conduction. As  $R_{SET}$  is inversely proportional to filament area S, LRS values should decrease with increasing filament area, i.e., with increasing magnitude of the compliance current. Figure 1.12 for Ag/HfO<sub>x</sub>/Pt RRAM demonstrates this relationship[26].

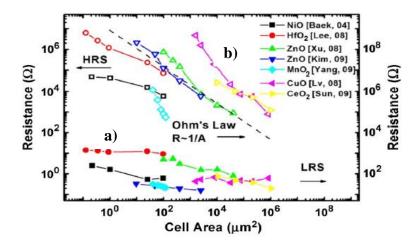

Additionally, as LRS is controlled mainly by filament properties, the magnitude of the LRS should be independent of electrode area for a given  $HfO_x$  thickness and filament size (i.e., compliance current). The trend in LRS with electrode size is shown for various metal oxide RRAM systems in Fig.1.13(a)[16].

Generally speaking, the more times a cell is switched, the larger the number of oxygen vacancies in the disrupted region becomes, eventually leading to a permanent LRS or ON state for an individual cell, a characteristic sign of device failure[16].

# 1.11.2 HRS

The magnitude of the HRS in a HfOx RRAM cell that has previously undergone a forming operation is primarily controlled by the distance x (equation 1.18) near the

Figure 1.12 Relationship between compliance current and LRS for Ag/HfOx/Pt RRAM. The blue curve shows decreasing LRS with increasing compliance current. ©2014 IEEE

Figure 1.13 a) Relationship between cell area and LRS for a variety of metal oxide RRAM systems (HfO<sub>2</sub> shown in red). b) Relationship between cell area and HRS for a variety of metal oxide RRAM systems. © 2012 IEEE

insulator/electrode interface region over which a filament has been re-oxidized, and thus effectively 'ruptured' in terms of electrical performance [16,18,19,22].Variation in these distances is related to the magnitude of the reset voltage[22], and also by the stochastic nature of the diffusion/recombination of atoms[16]. Equation 1.18 suggests that the total magnitude of the HRS in this system can be thought of as the sum of two series resistances, one resistance due to the length of the ruptured filament, and one resistance due to the remaining unaffected length[22]. The resistance associated with the re-oxidized filament tip (ruptured region) is represented by the exponential term, i.e., an increase in the length x of the re-oxidized region of the filament corresponds to an exponential increase in resistance, while the resistance through the remainder of the filament is ohmic [22].

The HfO<sub>x</sub> RRAM HRS shows variability not only with length of the disrupted region but with device area as well, generally increasing with decreasing cell area (see fig. 1.13 (b) above). Set and reset voltages show a slight increase in magnitude with decreasing cell area [24], which can therefore lead to larger diffusion and recombination rates by equations 1.13 and 1.14 respectively. These larger rates therefore result in a larger value of x in equation 1.18, and correspondingly to a larger value of the HRS after reset. While filamentary current describes the resistance characteristics of RRAM cells reasonably well, it is also probable that direct tunneling through the dielectric layer occurs simultaneously with filamentary current. Therefore, another reason for increased HRS with decreasing device area could be that area-dependent direct tunneling dominates the total current through the cell as the total cell area approaches the total area of the switching layer over which conductive filaments have been formed.

# **1.11.3 Forming Voltage**

Forming voltage is a fundamental performance metric for a metal oxide RRAM cell due to the fact that material systems requiring a forming step cannot undergo regular set/reset operations until a CF has been formed. The magnitude of the forming voltage then naturally becomes an important consideration. As larger forming voltages mean more power consumption per cell, reducing this value as much as possible becomes advantageous in order to reduce overall power consumption.

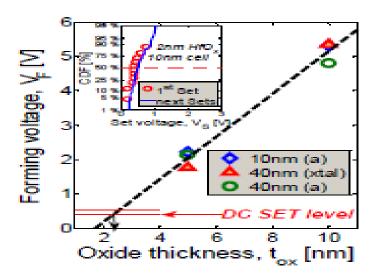

For a HfO<sub>2</sub> RRAM cell, the magnitude of the forming voltage is significantly affected by oxide thickness [24].Figure 1.14 below shows change in forming voltage with thickness of HfO<sub>2</sub> films, with the inset indicating the disappearance of a forming step altogether when the oxide thickness is reduced to 2 nm.

Figure 1.14 a) Relationship between oxide thickness and forming voltage for HfOx RRAM. ©2011 IEEE

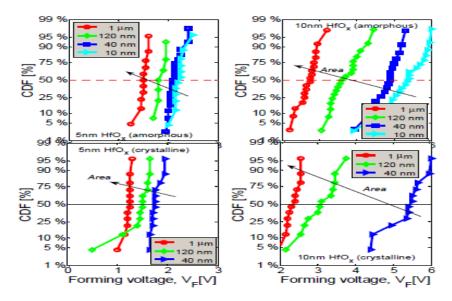

The presence of defects in the un-switched HfO<sub>2</sub> –based metal oxide RRAM cell also plays an important role in determining the magnitude of the forming voltage required to form a CF[16,24]. As mentioned previously, the CF is initially formed due to voltage stress build-up that occurs preferentially at hafnia GB's. Reduced electrode area naturally corresponds to a reduced number of GB's present in the un-switched insulator near the electrode/insulator interface. Because new defect generation occurs preferentially at preexisting defect sites, the reduced number of pre-existing defects present in the reduced cell area thereby increases the amount of voltage stress required to initiate new defects, which then increases the magnitude of the forming voltage required to produce CF's in smaller cells. This effect is demonstrated in [24], in which it was found that for larger cell sizes, crystalline hafnia required lower forming voltages as opposed to amorphous hafnia, while for smaller cells, this condition is reversed, with amorphous hafnia cells exhibiting the smaller forming voltages [24]. Figure 1.15 below shows the trend in forming voltage magnitude with electrode area for both crystalline and amorphous hafnia [24].

Figure 1.15 Data for both amorphous and crystalline HfO<sub>x</sub> RRAM showing increasing magnitude of the forming voltage with increased hafnia thickness and decreased cell area ©2011 IEEE.

# **1.11.4 Reset Current**

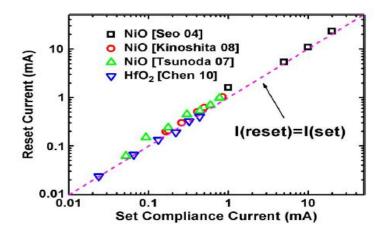

The magnitude of the reset current is a key parameter for economically viable RRAM functionality because maximum power consumption during set/reset operations will naturally occur during the reset operation, i.e. during the transition from the LRS to the HRS. Due to a temperature gradient across the insulator generated during the forming step, the CF tends to be smaller at the forming cathode (see fig.1.8).Concurrently, a larger resistance to electronic current is therefore experienced in this region, leading to higher temperatures generated during the reset voltage sweep which then contribute both to the re-oxidization of the filament tip as well as significant current noise due to structural instability associated with the diffusion/recombination process [18]. For HfO<sub>2</sub> RRAM systems, magnitude of the reset current has been found to trend linearly with the magnitude of the compliance current, and therefore with CF size (see fig 1.16 below).

Figure 1.16 Data for NiO and HfO<sub>2</sub> RRAM systems showing linear relationship of reset current with compliance current. (HfO<sub>2</sub> RRAM shown in blue). © 2012 IEEE

Consequently, the best strategy for minimizing power consumption of a metal oxide RRAM cell is to reduce the magnitude of the compliance current.

Reset current plays an important role in scaling considerations as well. As current through a RRAM cell in the LRS is primarily filamentary, the amount of current required in the reset operation to induce filament tip rupture is roughly the same regardless of cell area. However, as cell area is reduced, current density naturally goes up, which can cause problems of unwanted high temperature during device operation due to power handling considerations in memory cell selection or current limiting devices associated with the memory cell, which then can have various negative effects on the performance of the cell or of a circuit of which it is a part [16].The primary strategy for addressing this challenge for scaled devices is again to reduce the magnitude of the reset current by reducing the magnitude of the compliance current.

#### 1.12 Thesis overview

In this chapter, a background was provided on non-volatile memory, and in particular the form of NVM typically referred to as flash memory. Different tunneling mechanisms employed in the operation of flash cells were described as well as challenges facing the continued scaling and performance improvements for flash. Memristors were then discussed from a theoretical and historical perspective, and the suggestion made that memristive systems could offer one way forward for the NVM market. A memristive system generally referred to as metal oxide RRAM, in particular metal oxide RRAM with HfO<sub>2</sub> as the oxide material, was described with respect to functionality, conduction mechanisms, and fundamental performance metrics, as RRAM of this type has proven to be a viable candidate for addressing the scaling issues associated with NVM and flash. In

this work, a fabrication process for nano-scale cross-point TiN/ HfO<sub>2</sub>/TiN RRAM devices will be developed and described. Materials processing challenges will be addressed. The switching performance of devices fabricated by this process will be compared to the performance of similar devices from the literature in order to confirm process viability. In chapter 2, the design and fabrication process as well as processing and design challenges that were identified and addressed during development will be presented and described. In chapter 3, the electrical performance of these RRAM cells will be characterized and compared with the performance of similar devices from the literature, with a focus on the connection between device area and switching behavior. Chapter 4 provides conclusions as well as suggestions for future work.

# Chapter 2

# **DESIGN AND FABRICATION OF HfO2 RRAM**

In this chapter, the design and fabrication process of the RRAM will be explained. Descriptions and the associated processing overviews for two designs (design 1 and design 2) will be provided, as well as descriptions of the relevant design and processing challenges that emerged and how these challenges were addressed in order to successfully fabricate nano-scale cross-point HfO<sub>2</sub> -based RRAM.

#### **2.1 RRAM Device Design Considerations**

A significant design challenge associated with RRAM as a viable NVM application is related to uniformity of the switching behavior [16]. This necessitates strict control over formation of the CF, due to the strong connection between size of the CF and the magnitudes of all of the fundamental performance metrics of the RRAM cell. As mentioned in the previous chapter, there is a strong connection between compliance current and the CF. Additionally, strict control of the forming current is necessary in order to achieve stable multi-level switching, which could greatly increase data density through controlling the size or number of the CF's[16].

A variety of design solutions have been researched to address the issue of strict control of CF size, many of which involve the inclusion of current limiters such as transistors or diodes in the design of a memory device cell in order to limit current overshoot during the forming operation[11,16]. While integration of these devices into the memory cell design can effectively offer more precise control over the current through the MIM stack, new problems with scaling limits and parasitic electrical effects due to the presence of the current limiting elements then arise, greatly magnifying the already significant challenge of achieving all of the benchmarks for viable NVM applications mentioned in chapter 1.

A possible alternative to the inclusion of a current limiting device in a memory cell is the arrangement of the RRAM cells in a cross-point array in a manner similar to that shown in figure 1.4. If the memristive system being employed has a significantly high degree of non-linearity in the switching behavior, the resulting OFF/ON ratio for an individual cell can be high enough to exhibit desirable resistance read-out characteristics while simultaneously preventing unwanted leakage currents from the cell during read-out or programming of itself or of neighboring cells. This effect then also eliminates the space and power requirements associated with the inclusion of a current limiting device on a per-cell basis. The simple cross-point structure also shows great potential for stacking of memory cell arrays in three dimensions, thereby making significantly increased data density possible by increasing overall device density [10,11,12,16].

For these reasons, a cross-point design was chosen as the primary design of the HfO<sub>2</sub> RRAM described in this work.

#### **2.2 Design 1**

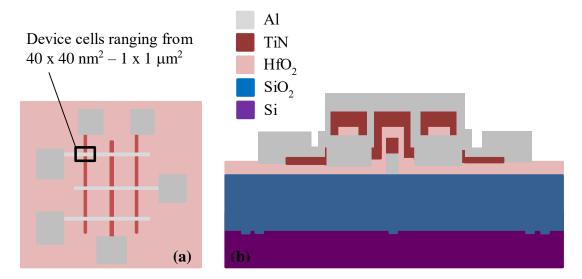

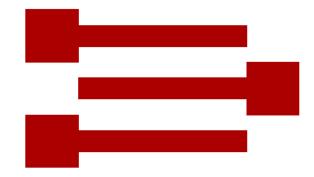

Design 1 was a 5-lithography-level cross-point device structure employing both optical and direct-write lithography for feature patterning. The cells were arranged in arrays consisting of nine device cells each (see fig.2.1(a)). Nominal electrode widths ranged from 40 nm – 1  $\mu$ m (1 electrode size per array). In order to facilitate the patterning of nano-scale electrodes, a hydrogen silsesquioxane (HSQ) -based negative

electron beam lithography (EBL) resist was chosen (product name XR-1541). Due to the difficulty associated with complete removal of HSQ, however, an additional positive EBL resist, poly-methyl-methacrylate (PMMA), was used as a sacrificial under-layer, in a process similar to that used for patterning Si nano-wires in previous work [27].Fig 2.1(b) shows a cross-section of a single device array.

Figure 2.1.Design 1 RRAM (a) Top view of a single 9-cell cross-point device array (b) Cross-section of a 9-cell cross-point device array.(Figures not to scale)

#### **2.3 Process development**

In order to determine appropriate processing parameters that would result in device features as close as possible to the nominal design values, process development experiments were performed in order to develop process steps that would produce the desired feature sizes, as well as stable, functional post-etch device patterns in both resist and metal stacks. These experiments are described in the following.

#### 2.3.1 Determination of electron beam dosage for patterning HSQ

For design 1, the electrodes were initially patterned in the HSQ over-layer through EBL, then the pattern was subsequently transferred to the PMMA under-layer with a low pressure O<sub>2</sub> etch, and finally to the metal stack with a Cl/Cl<sub>3</sub> etch. Hence, control of electrode size is primarily determined by the electron beam dosage chosen for the initial patterning in HSQ. HSQ has been under investigation as a negative EBL resist since 1997due to its' demonstrated ability to produce stable sub-20-nm features with good etch resistance, low line edge roughness, and small molecular size [28, 29].HSQ is an oligomer with a cage-like structure with the general formula [HSiO<sub>3/2</sub>]<sub>n</sub>, which in a resist solution forms a random network of partially connected structures. Upon exposure to an electron beam, the Si-H bonds are broken, subsequently forming unstable Si-OH groups which then condense, breaking down the cage-like network and forming a linear network of strong SiO bonds[30].

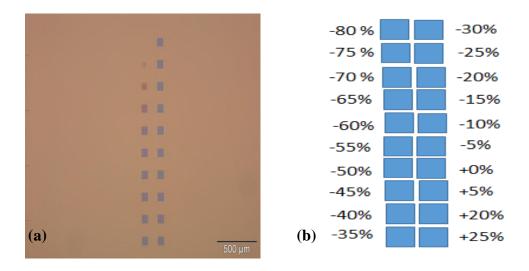

A key step in establishing the correct dosage that will result in the desired electrode size in HSQ after e-beam exposure is establishing what is called a base dose. The base dose for an exposure is essentially a dosage standard that represents complete exposure of the HSQ, i.e., a more or less complete reaction of all the oligomers in the resist, thus leading to a maximum post-exposure thickness. The base dose can then be used as a reference in the tool control code with respect to any desired changes in beam dosage in single exposure, or between different exposures used to monitor resist performance. To establish the base dose, an appropriate dosage range is chosen based on material data sheets, and a set of structures whose feature size is easily measured are exposed to the entire dosage range. Subsequent measurement of the exposed features can

then help identify the dosage at which complete exposure was achieved. This dose can then be identified as a base dose value. By using a base dose as a basis for identifying an optimal dosage range for an exposure, the desired feature sizes for patterns can be more readily achieved. Data for base dose determination for HSQ exposure as determined from the exposure and subsequent height measurement of 75 x 75  $\mu$ m<sup>2</sup> is shown in Fig. 2.2 below. Note that a base dose of 2000  $\mu$ C/cm<sup>2</sup> was chosen for electrode patterning for design 1.

Figure 2.2 Base dose determination (a) Post-exposure characterization squares of patterned HSQ. The blueish squares are more fully exposed, while the reddish and/or incomplete squares are under-exposed. (b) Typical dosage assignments for an exposure. +0% corresponds to choice of reference dose in the tool code. The dosage that led to greatest feature height then becomes the base dose for subsequent exposures.

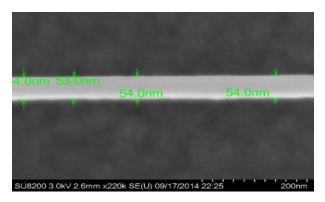

Once a base dose has been established, an appropriate dosage range for exposure of the desired structures can then be chosen. A range of doses is often chosen to account for the stochastic nature of the beam/resist reaction, or to optimize exposure conditions for a particular sample or feature. Confirmation of desired feature sizes can be confirmed by SEM (Figure.2.3)

The processing steps for design 1 are described in the following section (for recipe details, see Appendix A).

Figure 2.3 SEM image of a design 1 RRAM electrode structure patterned in HSQ on PMMA.

# 2.3.2 Design 1 Process Flow

- Substrate cleaning: Test-grade p-type Si wafers are cleaned by standard AMI cleaning (acetone rinse to remove organic contaminants, methanol rinse to remove any ionic species present on surface, isopropyl alcohol (IPA) rinse to remove any remaining residues).

- Patterning of EBL alignment marks: wafer-level and die-level alignment marks must be etched into the Si wafer in order to facilitate pattern alignment between the EBL levels. Etched marks are preferable to metal marks in order to simplify mark detection during subsequent processing on the JEOL 9300FS electron beam lithography system. In order to produce the etch pattern, positive EBL resist (PMMA (6%)) is used as the resist mask. After exposure, the wafer is developed in a 1:1 methyl-isobutyl-ketone (MIBK)/IPA bath , then rinsed in IPA and dried with N<sub>2</sub>.

- Etching of EBL alignment marks into Si wafer: with the wafer- and die- level alignment marks patterned in the PMMA(6%) ,deep reactive ion etching (DRIE) is performed on the wafer + resist pattern through alternating passivation/etch steps in SF<sub>6</sub>/C<sub>4</sub>F<sub>8</sub> plasmas, respectively. Approximate desired final mark depth in Si of 2-3 µm can be confirmed by profilometry performed on test patterns.

- **Resist strip**: after the Si etch, the resist mask is stripped by 30 min. soak in 1165 resist remover at a temperature of 120° C.

- **Deposition of buffer oxide**: after an AMI clean, PECVD SiO<sub>2</sub> is deposited on the wafer at a nominal thickness of 300 nm in order to electrically isolate MOR cell arrays devices from the Si substrate.

- **Bottom electrode metallization**: a metal bi-layer of 70 nm of PVD –deposited TiN on 100 nm of evaporation-deposited Al serves as the bottom electrode. The higher –conductivity Al layer is included to enhance electronic conduction through the MIM cells.

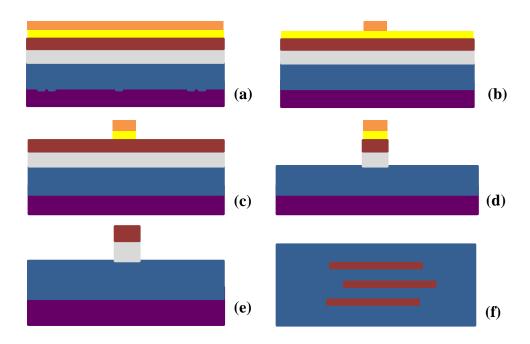

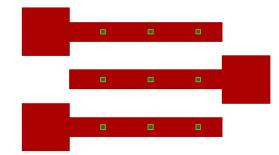

- Patterning of bottom electrodes: in order produce the electrode structures, first the above-mentioned EBL resist bi-layer is spun in two steps, the first step being the spinning of a PMMA(2%) under-layer and the second being the spinning of the HSQ. After the resist layers are applied, the electrodes are patterned by the JEOL in the negative resist only (top layer), then developed in a 25% tetra-methyl ammonium hydroxide (TMAH) solution. The PMMA under-layer between the electrode structures is then etched away by reactive ion etching (RIE) in a lowpressure O<sub>2</sub> plasma, and finally the metal electrodes are patterned by RIE in a

Cl/Cl<sub>3</sub> plasma. The bi-layer resist mask is then removed in a sonicated acetone bath. Figure 2.4 below illustrates the steps involved in electrode patterning.

- **Descum**: in order to ensure the removal of any remaining resist residue from the surface of the newly patterned bottom electrode, a brief etch is performed in an O<sub>2</sub> plasma.

- **Deposition of active dielectric**: deposition of the 5 nm-thick HfO<sub>2</sub> film which will serve as the switching layer is performed by atomic layer deposition (ALD)

- Top electrode metallization: a metal bi-layer of 100 nm of evaporationdeposited Al on 70 nm of PVD –deposited TiN serves as the top electrode of the MIM structure.

- **Patterning of top electrodes**: patterning of the top electrodes follows a similar series of steps as indicated in Fig.2.4 below

- Patterning of openings in the dielectric layer: in order to facilitate metal –tometal contact between the surface of a bottom electrode and the metal pad which will serve as its' electrical contact, 20 x 20 µm<sup>2</sup> openings are patterned in the dielectric film using optical lithography. A negative photoresist (NR-9) is spun onto the wafer, then given a pre-exposure bake at 150°C for 1 minute. The wafer is then exposed using a 365 nm wavelength, post-baked at 100°C for 1 minute, and the resulting pattern is then developed in RD-6.

- Etching of openings in the dielectric layer: electrode openings are etched in a 6:1 buffered oxide etch (BOE) solution for 2 minutes.

- **Descum**: in order to ensure the removal of any remaining residue from the surface of the bottom electrode, a brief etch is performed in an O<sub>2</sub> plasma.

Figure 2.4 EBL patterning of bottom electrodes for design 1 (a)Spinning of PMMA/HSQ bi-layer (b)Patterning of HSQ by EBL (c) Patterning of PMMA by oxygen plasma etch (d) Patterning of Al/TiN bi-layer by chlorine plasma etch (e)PMMA/HSQ bi-layer stripped in acetone (f) Overview of completely patterned electrodes

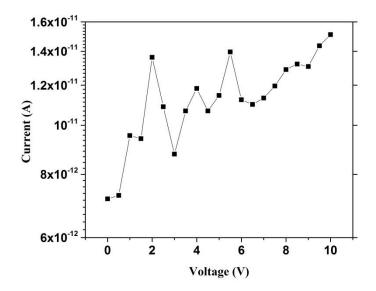

- Electrical contact/text/border patterning: the electrical contact pads, device cell labels and borders, are patterned in NR-9 by optical lithography, using the same steps as those used for patterning the openings in the dielectric layer.