## SCALING SYNCHRONIZATION PRIMITIVES

A Dissertation

Presented to

The Academic Faculty

Ву

Sanidhya Kashyap

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Computer Science

Georgia Institute of Technology

August 2020

## **SCALING SYNCHRONIZATION PRIMITIVES**

## Approved by:

Dr. Taesoo Kim, Advisor School of Computer Science Georgia Institute of Technology

Dr. Changwoo Min, Co-advisor The Bradley Department of Electrical and Computer Engineering Virginia Tech

Dr. Ada Gavrilovska School of Computer Science Georgia Institute of Technology Dr. Irina Calciu VMWare Research

Dr. Joy Arulraj School of Computer Science Georgia Institute of Technology

Date Approved: June 11, 2020

To maa: for her strength, wisdom, and love.

To papa: for his unconditional belief in me.

To my brother: for being my critic.

To my background thread.

#### ACKNOWLEDGEMENTS

I am fortunate to have had the opportunity to collaborate with and learn from amazing people. First, I owe my deepest gratitude to my advisor, Taesoo Kim. Throughout my Ph.D., Taesoo gave me an ample amount of freedom to explore ideas and collaborate with anyone. I am never going to forget these words: "Do whatever you want to do." His in-depth technical insight, concrete feedback, advice, encouragement, and guidance has led me to where I am today. I hope one day, I can be a good advisor to my future students, as Taesoo has been to me.

Another person who had an immeasurable impact on my life is my co-advisor: Changwoo Min. His vast knowledge of designing parallel systems was essential to realize any of this work. I am never going to forget our discussions, which I still miss. I used to bug him almost every day during his postdoc days, and I still do when I am excited to share some new ideas. I am immensely grateful to him, as he was my mentor, friend, and guide, all at the same time, and continues to do so.

In my later part of Ph.D., I was fortunate to work with Irina Calciu. Working with Irina always kept me on edge, as she asked too many (difficult) questions to make me rethink about the work. I hope this continues for the foreseeable future. I also want to thank the other members of my committee: Ada Gavrilovska, and Joy Arulraj. Both of them were always available to discuss ideas and even my career options.

I want to thank all the amazing folks that I got to know, learn from, and work with through these years, notably: Sudarsun Kannan, Virendra Maratha, Seulbae Kim, Meng Xu, Insu Yun, Mingwei Shih, Steffen Maass, Mohan Kumar, Tushar Krishna, Fan Sang, Ren Ding, Kyuhong Park, Pradeep Fernando, Mansour Alharthi, Hong Hu, Woonhak Kang, Byoungyoung Lee, Chengyu Song, Woonhak Kang, Wen Xu, Kangnyeon Kim, Hyungon Moon, Seulbae Kim, Meng, Xu, Jean Pierre Lozi, Margo Seltzer, Alex Kogan, Dave Dice, Hong Hu, Hanqing Zhao, Se Kwon Lee, Soujanya Ponnapalli, Madhavan Krishnan

Ramanathan, Sujin Park, Chulwon Kang, and Xiaohe Cheng. I am really grateful to Seulbae for being a good friend. I want to thank our previous Ph.D. coordinator, Venkat, for his help in navigating various PhD-related administrative issues and even suggesting I work with Taesoo. I am also grateful to our administrative problem-solvers, who made my life easier, especially Elizabeth Ndongi, Trinh Doan, and Sue Jean Chae.

Finally, I want to thank my parents for their support and patience along this journey. I want to thank my friend, Jaspal, who has been there through thick and thin, remotely. I am especially grateful to my brother, from whom I have a lot to learn in the arena of life, philosophy, and about myself.

# TABLE OF CONTENTS

| Ackno   | wledgments                                 |

|---------|--------------------------------------------|

| List of | Tables                                     |

| List of | Figures xii                                |

| List of | Pseudo-Code                                |

| Summ    | ary                                        |

| Chapte  | er 1: Introduction                         |

| 1.1     | Ordering in Concurrency Control Algorithms |

| 1.2     | Double Scheduling in Virtualization        |

| 1.3     | Scalable and Practical Locking Primitives  |

| 1.4     | Outline and Contributions                  |

| Chapte  | er 2: Background and Motivation            |

| 2.1     | A Primer on Multicore Machines             |

| 2.2     | Ordering in Concurrency                    |

|         | 2.2.1 Multicore Hardware Clocks            |

| 2.3     | Locking Primitives                         |

|         | 2.3.1 Evolution of Lock design             |

|       | 2.3.2    | Locks in the kernel space (Linux)                               | 12 |

|-------|----------|-----------------------------------------------------------------|----|

|       | 2.3.3    | Locking Bottlenecks in Deployed File Systems                    | 13 |

| 2.4   | Double   | e Scheduling in VMs                                             | 15 |

| 2.5   | Conclu   | asion                                                           | 17 |

| Chapt | ter 3: ( | Ordering Primitive                                              | 18 |

| 3.1   | Ordo:    | A Scalable Ordering Primitive                                   | 19 |

|       | 3.1.1    | Embracing Uncertainty in Clock: Ordo API                        | 20 |

|       | 3.1.2    | Measuring Uncertainty between Clocks: Calculating ORDO_BOUNDARY | 20 |

| 3.2   | Algori   | thms with Ordo without Uncertainty                              | 26 |

|       | 3.2.1    | Read-Log-Update (RLU)                                           | 26 |

|       | 3.2.2    | Concurrency Control for Databases                               | 29 |

|       | 3.2.3    | Software Transactional Memory (TL2)                             | 31 |

|       | 3.2.4    | Oplog: An Update-heavy Data Structures Library                  | 33 |

| 3.3   | Implei   | mentation                                                       | 33 |

| 3.4   | Evalua   | ation                                                           | 34 |

|       | 3.4.1    | Scalability of Invariant Hardware Clocks                        | 36 |

|       | 3.4.2    | Evaluating Ordo Primitive                                       | 36 |

|       | 3.4.3    | Physical Timestamping: Oplog                                    | 38 |

|       | 3.4.4    | Read Log Update                                                 | 39 |

|       | 3.4.5    | Concurrency Control Mechanism                                   | 43 |

|       | 3.4.6    | Software Transactional Memory                                   | 46 |

|       | 3 4 7    | Sensitivity Analysis of ORDO ROUNDARY                           | 48 |

| 3.5    | Chapter Summary                                   | 49 |

|--------|---------------------------------------------------|----|

| Chapte | er 4: Impact of Scheduling on Virtual Machines    | 50 |

| 4.1    | Design                                            | 51 |

|        | 4.1.1 Lightweight Para-virtualized methods        | 53 |

|        | 4.1.2 Eventual Fairness with Selective Scheduling | 55 |

| 4.2    | Use Case                                          | 56 |

| 4.3    | Implementation                                    | 57 |

| 4.4    | Evaluation                                        | 59 |

|        | 4.4.1 Overhead of <i>e</i> CS                     | 60 |

|        | 4.4.2 Performance in an Over-committed Scenario   | 61 |

|        | 4.4.3 Performance in an Under-committed Case      | 67 |

|        | 4.4.4 Addressing BWW Problem via eCS              | 69 |

|        | 4.4.5 System Eventual Fairness                    | 70 |

| 4.5    | Chapter Summary                                   | 72 |

| Chapte | er 5: Scalable Locking Primitives                 | 73 |

| 5.1    | Dominating Factors in Lock Design                 | 74 |

| 5.2    | SHFLLOCKS                                         | 77 |

|        | 5.2.1 The Shuffling Mechanism                     | 78 |

|        | 5.2.2 SHFLLOCKS Design                            | 78 |

| 5.3    | Implementation                                    | 90 |

| 5.4    | Evaluation                                        | 90 |

|        | 5.4.1 SHELLOCK Performance Comparison             | 01 |

|        | 5.4.2 Improving Application Performance    |

|--------|--------------------------------------------|

|        | 5.4.3 Performance Breakdown                |

|        | 5.4.4 Performance With Userspace Shfllock  |

| 5.5    | Chapter Summary                            |

| Chapte | er 6: Related Work                         |

| 6.1    | Ordering in Concurrency Control Algorithms |

| 6.2    | Double Scheduling in VMs                   |

| 6.3    | Locking Primitives                         |

| Chapte | er 7: Reflections                          |

| 7.1    | Limitations                                |

|        | 7.1.1 Ordering in Concurrency with Ordo    |

|        | 7.1.2 Enlightened Critical Sections        |

|        | 7.1.3 Shuffling-based Lock Algorithms      |

| 7.2    | Future Work                                |

| Chapte | er 8: Conclusion                           |

| Refere | nces                                       |

# LIST OF TABLES

| 2.1 | Evolution of synchronization primitives in the last 15 years in Linux along with their introduction with the corresponding Linux version                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Identified lock-based scalability bottlenecks in tested file systems with FxMark [77]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14 |

| 3.1 | Various machine configurations that we use in our evaluation as well as the calculated offset between cores. While $min$ is the minimum offset between cores, $max$ is the global offset, called ORDO_BOUNDARY (refer to Figure 3.1), which we used, including up to the maximum hardware threads (Cores*SMT) in a machine.                                                                                                                                                                                                                                                                   | 36 |

| 4.1 | Set of para-virtualized methods exposed by the hypervisor to a VM for providing hints to the hypervisor to mitigate double scheduling. These methods provide hints to the hypervisor and VM via shared memory. A vCPU relies on the first four methods to ask for an extra schedule to overcome LHP, LWP, RP, RRP, and ICP. Meanwhile, a vCPU gets hints from the hypervisor by using the last two methods to mitigate LWP and BWW problems. The cpu_id is the core id that is used by tasks running inside a guest OS. †Currently, is_vcpu_preempted() is already exposed to the VM in Linux | 52 |

| 4.2 | Applicability of our six lightweight para-virtualized methods that strive to address the symptoms of double scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56 |

| 4.3 | eCS requires small modifications to the existing Linux kernel, and the annotation effort is also minimal: 60 LoC changes to support the 10 million LoC Linux kernel that has around 12,000 of lock instances with 85,000 lock invocations.                                                                                                                                                                                                                                                                                                                                                    | 58 |

| 4.4 | Cost of using our lightweight para-virtualized methods with various synchronization primitives and mechanism. <i>I core</i> and <i>80 core</i> denote the time (in ns) to execute an empty critical section with one and 80 threads, respectively. Although, our approach slightly adds an overhead on a single core count, there is no performance degradation for our evaluated workloads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

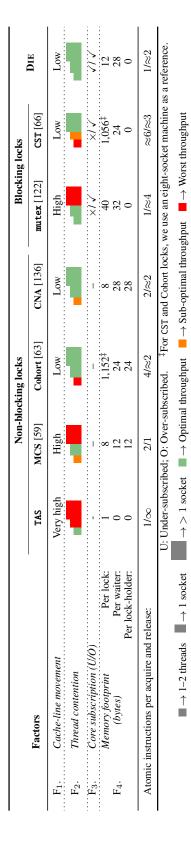

| 5.1 | Dominant factors affecting locks that are in use in the Linux kernel or are the state-of-the-art for NUMA architecture. Cache-line movement refers to shfllock/data movement inside a critical section. Boxes represent the scalability of locks with increasing thread count from one thread to threads within a socket to all threads among multiple sockets. Core subscription is only applicable to blocking locks and denotes the best throughput for a varying number of threads. Both mutex and CST are sub-optimal when undersubscribed but maintain good throughput once they are over-subscribed. Memory footprint is the memory allocation for locks: the size of each lock instance (per lock), a queue node required by each waiting thread before entering the critical section (per waiter), and a queue node retained by a lock holder within the critical section (per lock-holder). If the lock holder uses the queue node, which happens for MCS, CNA, and Cohort locks, the thread must keep track of the node, as it can acquire multiple locks: a common scenario in Linux. Note that queue nodes can be allocated on the stack for each algorithm. However, in practice, a lock user needs to explicitly allocate it on the stack for MCS, CNA, and Cohort locks, while mutex, CST, and SHFLLOCKS avoid this complexity. We also summarize the number of atomic instructions in the non-contended/contended scenarios | 75 |

| 5.2 | Locks evaluated in both the kernel space and the userspace. In the kernel space, we replace all locks with SHFLLOCKS. We use LD_PRELOAD to replace all the mutex-based locks in the userspace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 91 |

| 5.3 | Lock usage in various micro-benchmarks [77, 146]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92 |

# LIST OF FIGURES

| 2.1 | Multicore machine design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Indirect metric of the growing complexity of lock usage: the number of lock() API calls in the Linux kernel source code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10 |

| 3.1 | Algorithm to calculate the ORDO_BOUNDARY: a system-wide global offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21 |

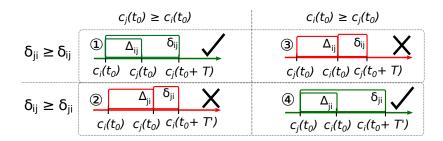

| 3.2 | Calculating offset $(\delta_{i\leftrightarrow j})$ using pairwise one-way-delay latency between clocks $(c_i \text{ and } c_j)$ . $\Delta_{ij}$ and $\Delta_{ji}$ are the physical offsets between $c_i$ and $c_j$ , and $c_j$ and $c_i$ , respectively. $\delta_{ij}$ and $\delta_{ji}$ are measured offsets with our approach. Depending on physical and measured offsets, there are four possible cases. Unlike existing clock-synchronization protocols [56, 57, 54, 95] <sup>3</sup> that average the calculated latency based on RTT, we consider each direction separately to measure the offset and consider only the direction that is always greater the positive physical offset, such as cases 1 and 4 | 23 |

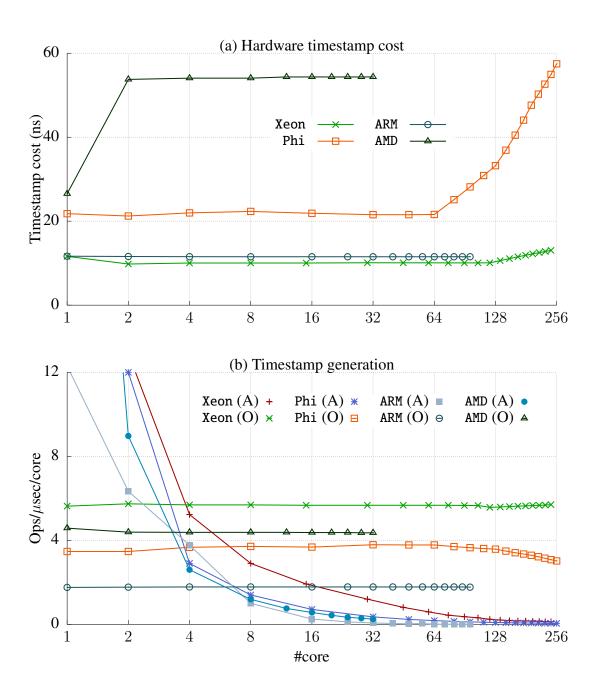

| 3.3 | Micro evaluation of the invariant hardware clocks used by the Ordo primitive.  (a) shows the cost of a single timestamping instruction when it is executed by varying the number of threads in parallel; (b) shows the number of per-core generated timestamps in a micro second with atomic increments (A) and with new_time() (O), which generates timestamps at each ORDO_BOUNDARY.                                                                                                                                                                                                                                                                                                                             | 35 |

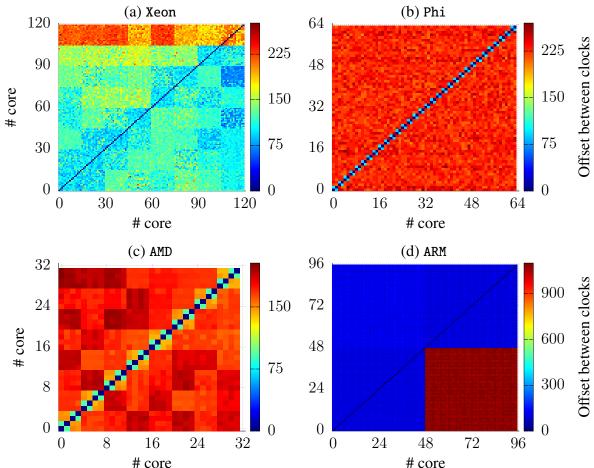

| 3.4 | Clock offsets for all pairs of cores. The measured offset varies from a minimum of 70 ns to 1,100 ns for all architectures. Both Xeon (a) and ARM (d) machines show that the one of the sockets has a $4-8\times$ higher offset than the others. To confirm this, we measured the bandwidth between the sockets, which is symmetric in both machines                                                                                                                                                                                                                                                                                                                                                               | 37 |

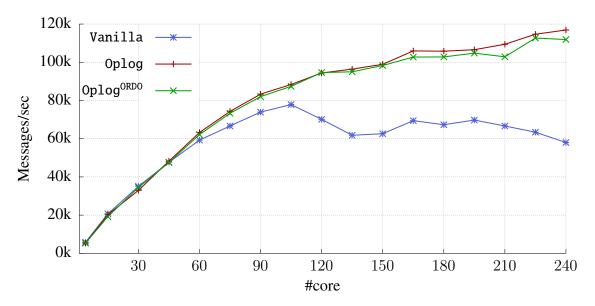

| 3.5 | Throughput of Exim mail-server on a 240-core machine. Vanilla represents the unmodified Linux kernel, while Oplog is the rmap ordo/data structure modified by the Oplog API in the Linux kernel. Oplog <sup>ORDO</sup> is the extension of Oplog with the Ordo primitive                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39 |

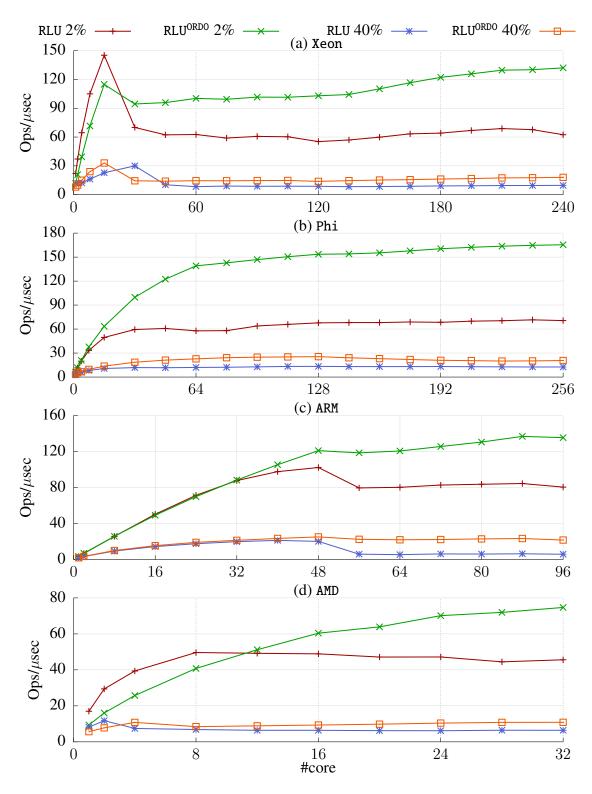

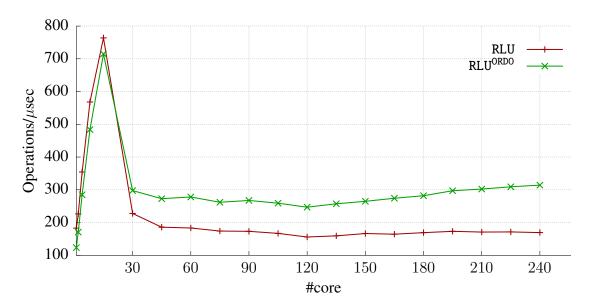

| 3.6  | Throughput of the hash table with RLU and RLU <sup>ORDO</sup> for various update ratios of 2% and 40% updates. The user space hash table has 1,000 buckets with 100 nodes. We experiment it on four machines from Table 3.1                                                                                                                                                                                                                                                                                                       | 40 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

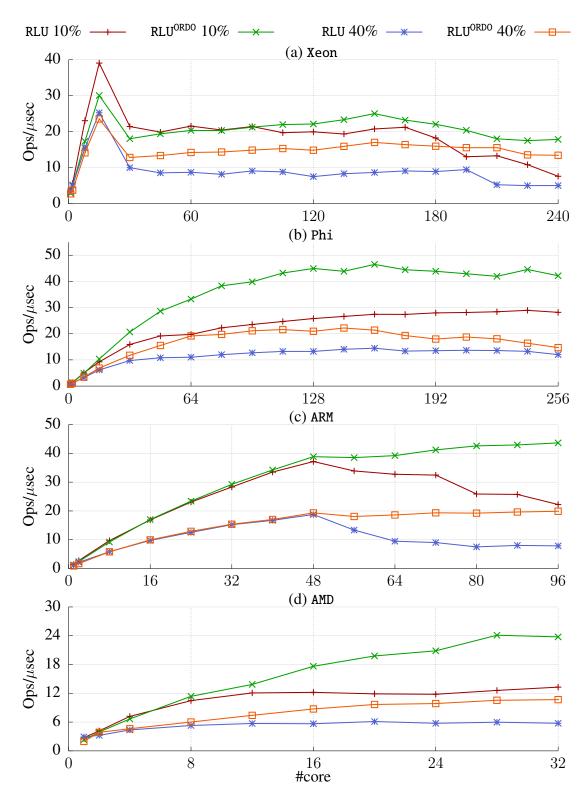

| 3.7  | Throughput of the citrus tree with RLU and RLU $^{\rm ORDO}$ that consists of 100,000 nodes with varying updates ratio of 10% and 40% on various machines                                                                                                                                                                                                                                                                                                                                                                         | 41 |

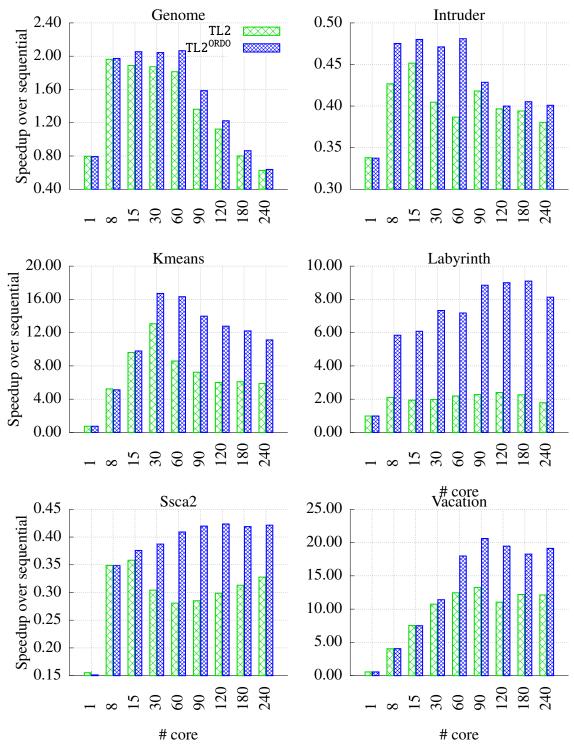

| 3.8  | Throughput of the hash table benchmark (40% updates) with the deferred-based RLU and RLU <sup>ORDO</sup> approach on the Xeon machine. Even with the deferred-based approach, the cost of the global clock is still visible after crossing the NUMA boundary                                                                                                                                                                                                                                                                      | 43 |

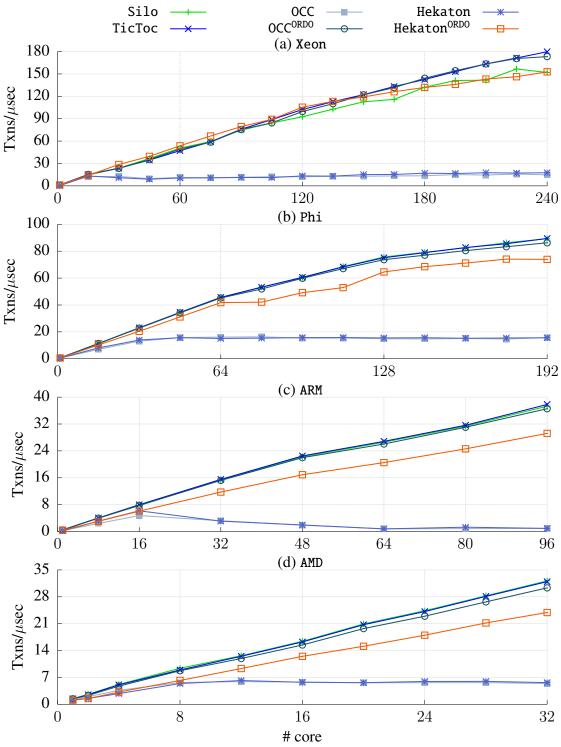

| 3.9  | Throughput of various concurrency control algorithms of ordo/databases for read-only transactions (100% reads) using the YCSB benchmark on various architectures. We modify the existing OCC and Hekaton algorithms to use our Ordo primitive (OCC <sup>ORDO</sup> and Hekaton <sup>ORDO</sup> , respectively) and compare them against the state-of-the-art OCC algorithms: Silo and TicToc. Our modifications removes the logical clock bottleneck across various architectures.                                                | 44 |

| 3.10 | Throughput and abort rates of concurrency control algorithms for TPC-C benchmark with 60 warehouses on 240 Intel Xeon machine                                                                                                                                                                                                                                                                                                                                                                                                     | 45 |

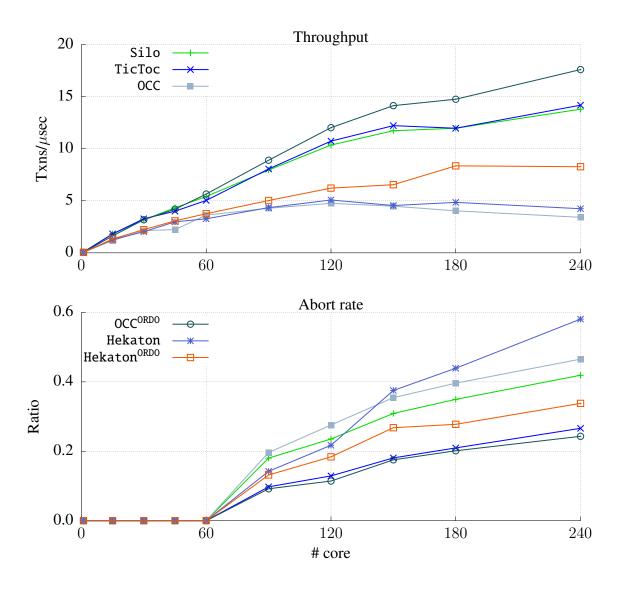

| 3.11 | Speedup of the STAMP benchmark with respect to the sequential execution on Xeon machine for TL2 and TL2 <sup>ORDO</sup> algorithms. TL2 <sup>ORDO</sup> improves the throughput up to 3.8× by alleviating the cache-line contention that occurs of the global logical clock. TL2 <sup>ORDO</sup> shows significant improvement in the case of workloads running with very short transactions (Kmeans and Ssca2) and the ones with very long transactions by decreasing their aborts due to the cache-line mitigation (Labyrinth). | 47 |

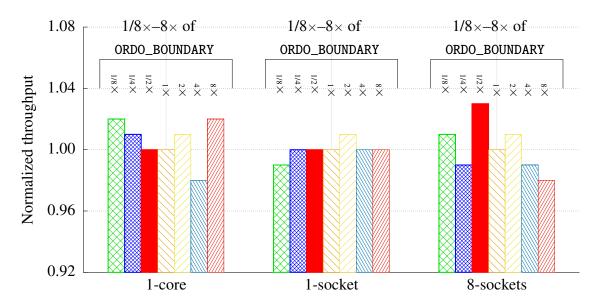

| 3.12 | Normalized throughput of the RLU <sup>ORDO</sup> algorithm for varying ORDO_BOUNDARY on the Xeon machine on 1-core, 1-socket (30 cores), and 8-sockets (240 cores) with 98% reads and 2% writes. We vary the ORDO_BOUNDARY from $1/8 \times -8 \times$ for all three configurations, which shows that the throughput varies by only $\pm 3\%$ , thereby proving two points: 1) timestamping is one of the bottlenecks, and 2) ORDO_BOUNDARY does not act as a backoff mechanism for such logical timestamping-based algorithms    | 48 |

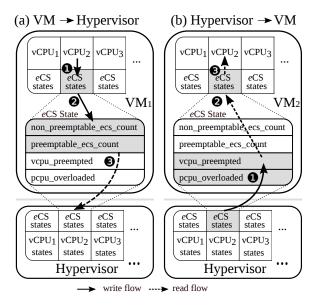

| 4.1 | Overview of the information flow between a VM and a hypervisor. Each vCPU has a per-CPU state that is shared with the hypervisor, denoted as eCS state. Figure (a) shows how the vCPU <sub>2</sub> relays information about an eCS to the hypervisor. On entering a critical section or an interrupt context (1), vCPU <sub>2</sub> updates the non_preemptable_ecs_count (2). After a while, before scheduling out vCPU <sub>2</sub> , the hypervisor reads its eCS state (3), and allows it run for one more schedule to mitigate any of the double scheduling problems. Figure (b) shows how the hypervisor shares the information whether a vCPU is preempted or a physical CPU is overloaded, at the schedule boundary. For instance, the hypervisor marks vcpu_preempted, while scheduling out a vCPU; or updates pcpu_overloaded flag to one if the number of active tasks on that physical CPU is more than one. Both try to further mitigate LWP and BWW problems | 54 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

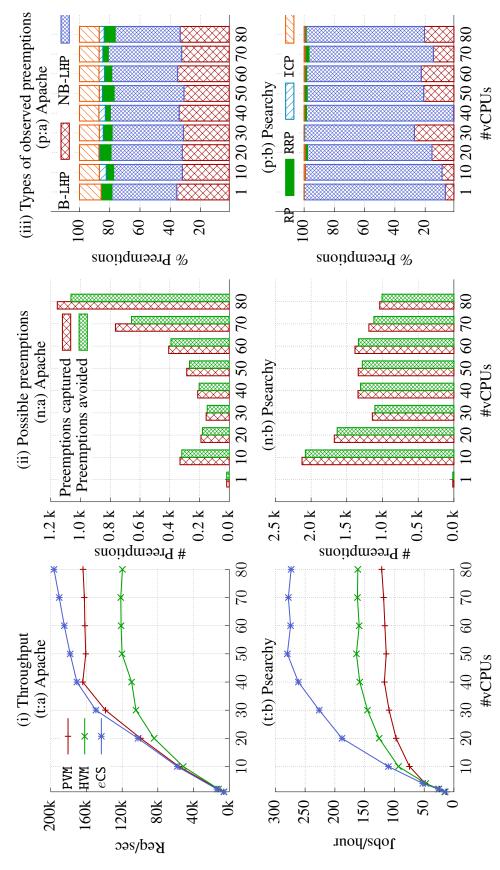

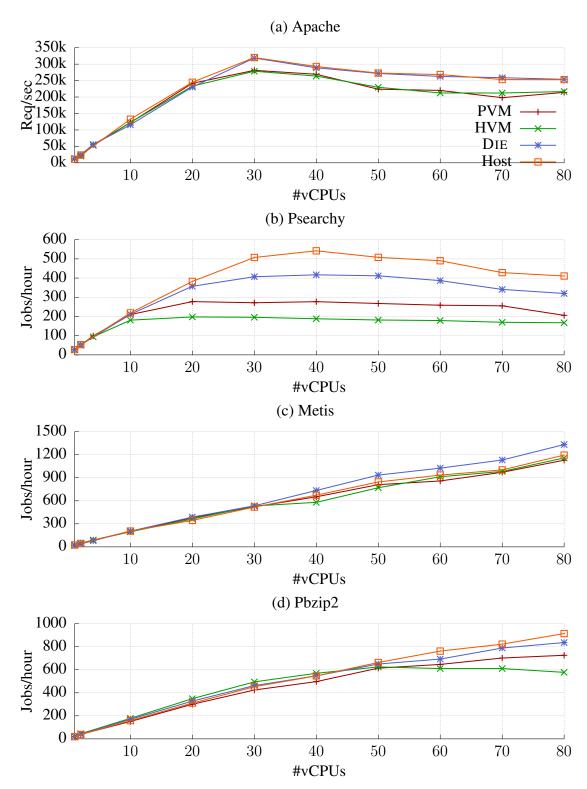

| 4.2 | Analysis of real-world workloads (Apache and Psearchy) in an overcommitted scenario, <i>i.e.</i> , two instances of VM are executing the same workload. Column (i) represents the scalability of selected workloads in three settings: PVM, HVM, and with <i>e</i> CS annotations. Column (ii) represents the number of preemptions caught and prevented by the hypervisor with our methods. Column (iii) represents the type of preemptions caught by the hypervisor (refer Table 4.4). By allowing an extra schedule, our approach reduces preemptions by 85–100% and improve scalability of applications by up to 2.5×, while observing almost all types of preemptions for each workload                                                                                                                                                                                                                                                                               | 62 |

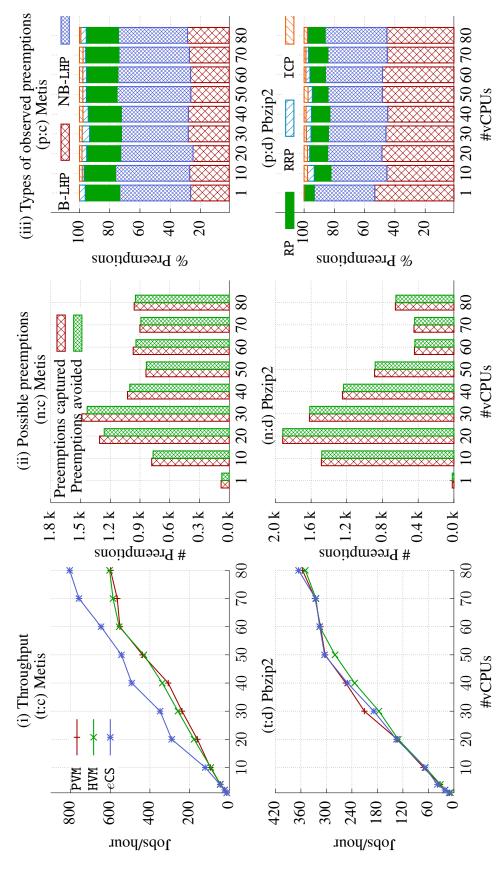

| 4.3 | Analysis of real-world workloads (Metis and Pbzip2) in an over-committed scenario, <i>i.e.</i> , two instances of VM are executing the same workload. Column (i) represents the scalability of selected workloads in three settings: PVM, HVM, and with $e$ CS annotations. Column (ii) represents the number of preemptions caught and prevented by the hypervisor with our methods. Column (iii) represents the type of preemptions caught by the hypervisor (refer Table 4.4). By allowing an extra schedule, our approach reduces preemptions by 85–100% and improve scalability of applications by up to $2.5 \times$ , while observing almost all types of preemptions for each workload                                                                                                                                                                                                                                                                             | 63 |

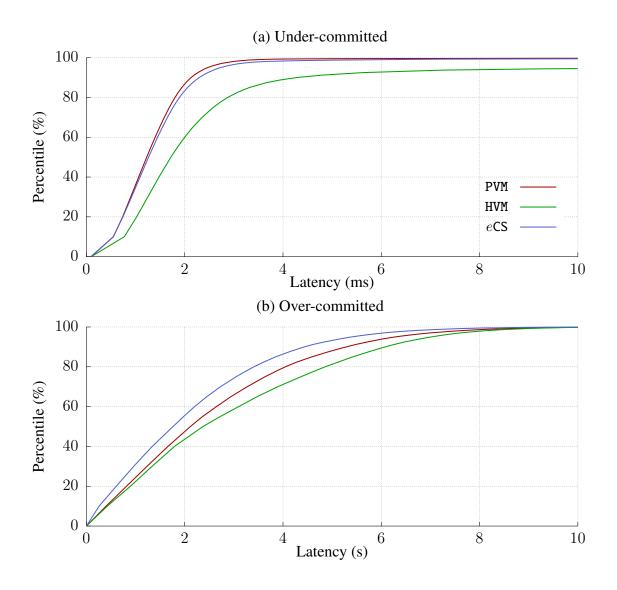

| 4.4 | CDF of the latency of requests for the Apache web server workload in both under- and over-committed scenarios at 80 cores. It clearly shows the impact of <i>e</i> CS in the over-committed scenario, while having minimal impact in the under-committed case                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65 |

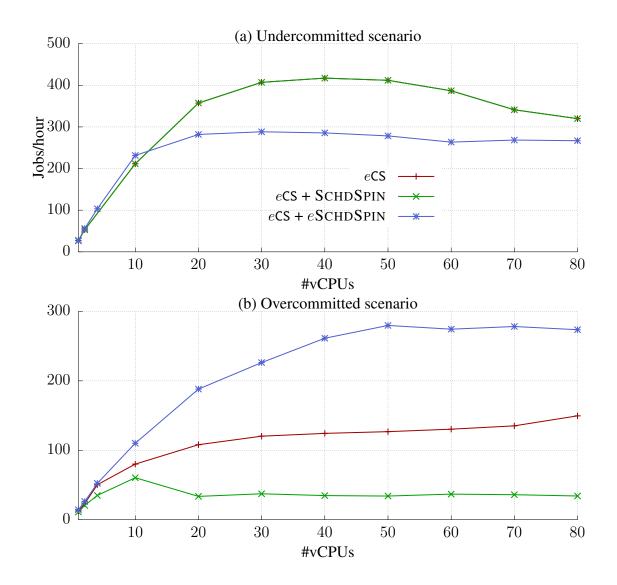

| 4.5 | Performance of real-world workloads when running on the bare metal (Host), and inside a VM with three configurations: PVM, HVM, and with eCS annotations. In this scenario, only one VM is running. We use Host as the baseline for the comparison because we consider Host to have almost optimal performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 68 |

| 4.6 | Impact of both BWW problem and $e$ CS method (refer Hypersivor $\rightarrow$ VM in Table 4.1) on Psearchy in both under- and over-committed scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

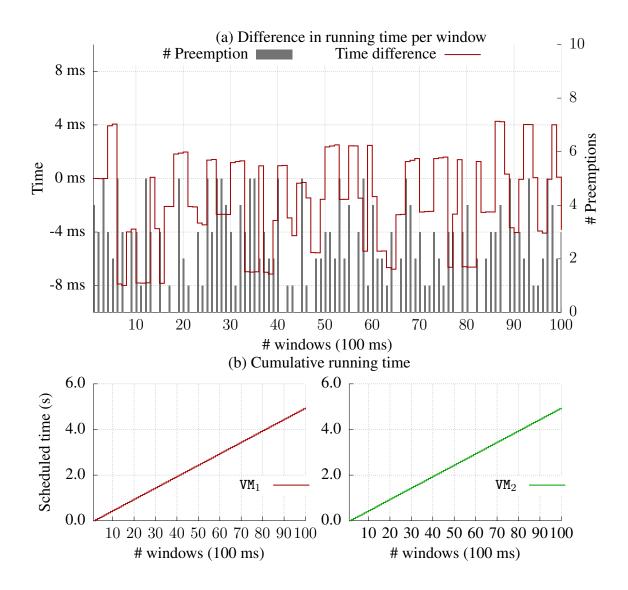

| 4.7 | Fairness in $e$ CS. Running time of a vCPU of two co-scheduled VMs (VM <sub>1</sub> and VM <sub>2</sub> ) with $e$ CS annotations for a period of 10 seconds with 100 ms window granularity while executing a kernel intensive task (reading the contents of a file) that involves read side of rwsem. (a) shows the difference in running time of vCPU per window granularity as well as the number of preemptions occurring per window, while (b) illustrates the cumulative running time, and shows that the hypervisor maintains eventual fairness in the system, even if VM <sub>2</sub> is allowed extra schedules. Both VMs get 4.95 seconds to run                                                                                                                                                                                                                                                                                                                                                   | 71 |

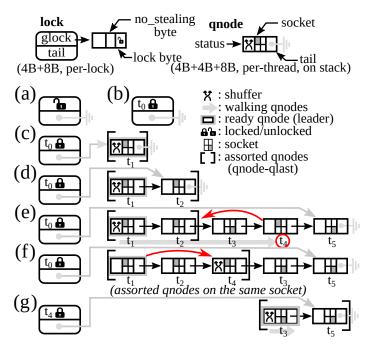

| 5.1 | SHFLLOCK <sup>NB</sup> example. The lock structure consists of a state (glock) and the queue tail. The first byte of glock is the lock/unlock state, while the second byte denotes whether stealing is allowed. We encode multiple information in the qnode structure. (a) Initially, there is no lock holder. (b) $t_0$ successfully acquires the lock via CAS and enters the critical section. (c) $t_1$ , of socket 1, executes SWAP on the lock's tail after the CAS failure on TAS. (d) Similarly, $t_2$ from socket 1, also joins the queue. (e) Now, there are five waiters ( $t_1$ – $t_5$ ) waiting for the lock. $t_1$ is the very first waiter, so it becomes the shuffler and traverses the queue to find waiters from the same socket. $t_1$ then moves $t_4$ (same socket) after $t_2$ . (f) After the traversal, $t_1$ selects $t_4$ as the next shuffler. (g) $t_4$ acquires the lock after $t_1$ and $t_2$ have executed their critical sections. At this point, $t_3$ becomes the shuffler | 81 |

| 5.2 | A running example of how a shuffler shuffles waiters with the same socket ID and wakes them up. (a) $t_0$ is the lock holder; $t_1$ is the shuffler and is traversing the queue. $t_2$ is sleeping, but $t_1$ wakes it up. (b) $t_2$ becomes active, while $t_1$ continues shuffling and reaches $t_4$ , $t_1$ first moves $t_4$ after $t_2$ , and wakes up $t_4$ to mitigate the wakeup latency. (c) When $t_0$ releases the lock, $t_1$ acquires it; $t_2$ and $t_4$ are actively spinning for their turn; $t_4$ is the shuffler                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 86 |

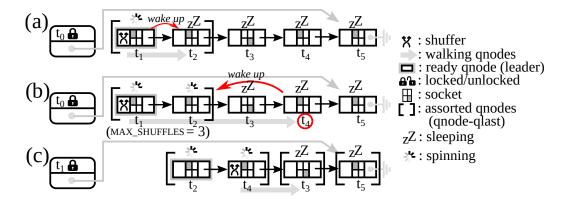

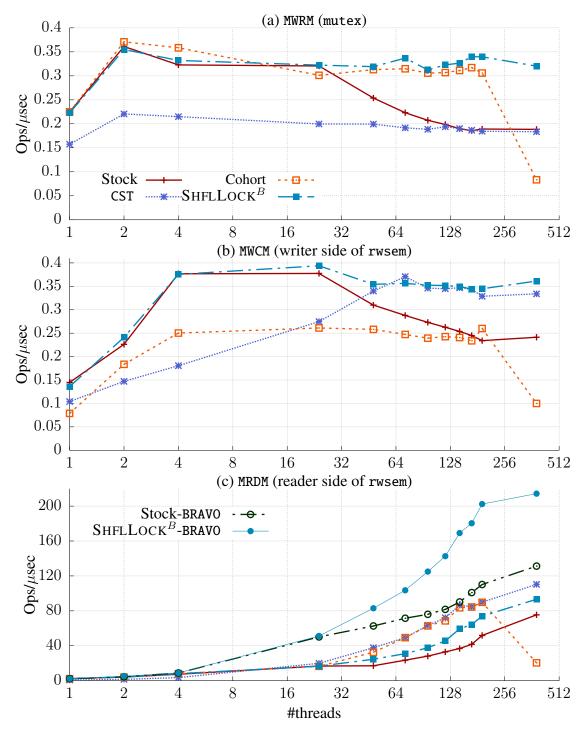

| 5.3 | Impact of non-blocking locks on the scalability of micro-benchmarks [77, 146]. Refer to Table 5.3 for lock usage. Here, Stock refers to the default spinlock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 92 |

| 5.4 | Impact of blocking locks on the scalability of micro-benchmarks with up to $2\times$ over-subscription (384 threads: we pin two threads on each core). Cohort and CST are the non-blocking and blocking hierarchical locks, respectively. Refer to Table 5.3 for lock usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 93 |

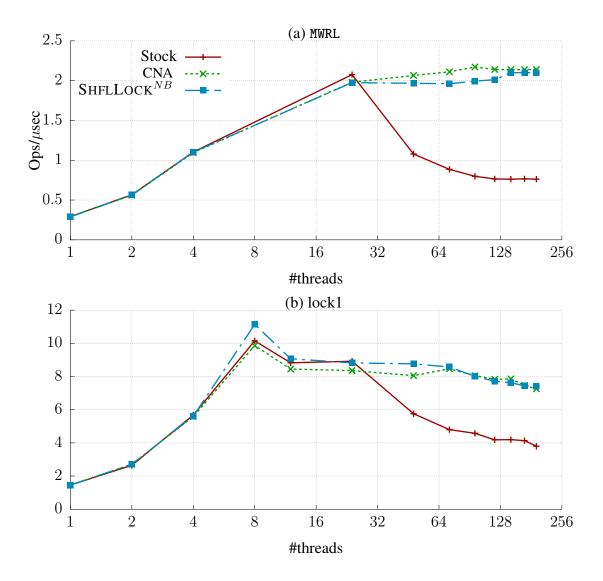

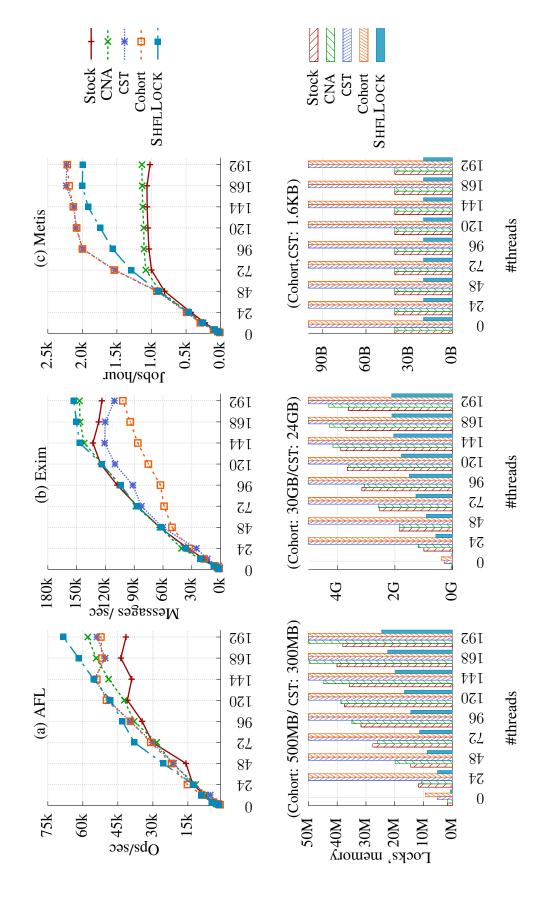

| 5.5 | Impact of locks on application scalability and on memory footprint, while running three applications with Shfllocks, Linux stock version (Stock), CNA, CST, and Cohort. Refer to Table 5.2 for specific changes. Shfllock reduces the memory footprint because of the blocking locks that are embedded in inodes, task structure, and memory management structures                                                                                                                                                          | 96  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

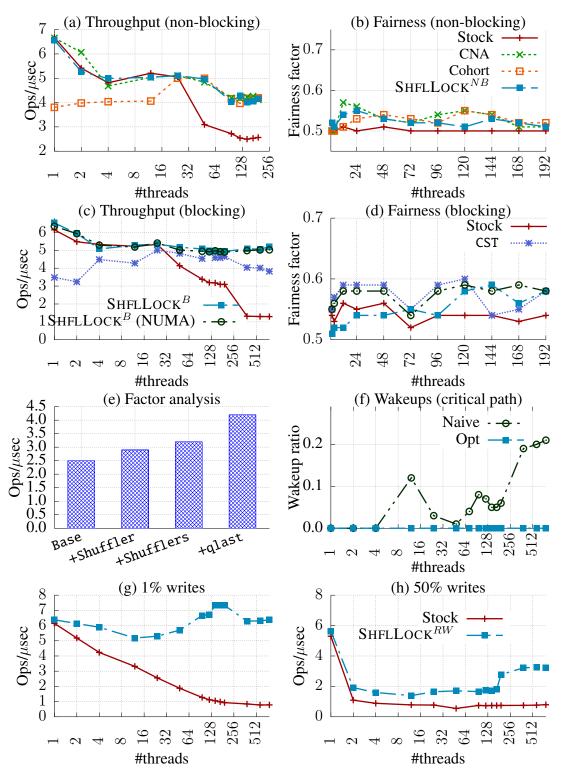

| 5.6 | Impact on throughput and long-term fairness of non-blocking and blocking locks on the hash-table benchmark. For blocking locks, we over-subscribe the system by $4\times$ . We also include the factor analysis of several phases introduced by Shfllock <sup>NB</sup> , and the number of wakeups in the critical path for Shfllock <sup>B</sup> . Later, we show the impact on throughput with centralized readers-writer locks: Stock and Shfllock <sup>RW</sup> for 1% and 50% writes up to $4\times$ over-subscription | 100 |

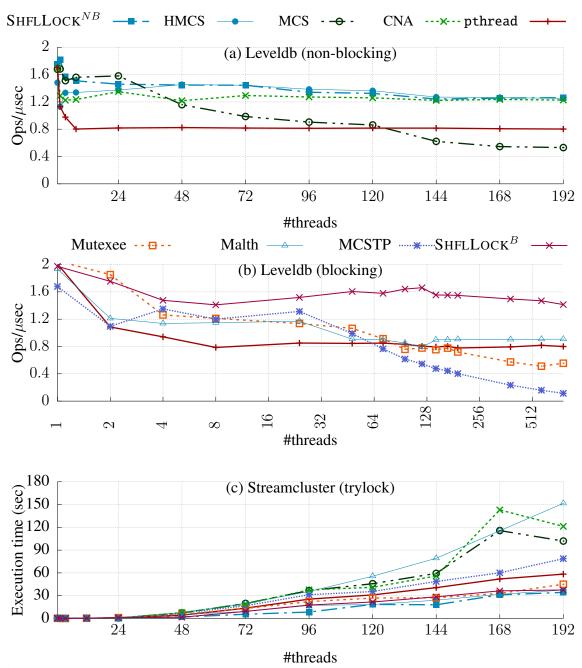

| 5.7 | Total throughput of LevelDB benchmark and the streamcluster benchmark with various blocking and non-blocking locks. We further over-subscribe the cores for levelDB (b) to test the impact of blocking locks with $4\times$ the number of cores                                                                                                                                                                                                                                                                             | 102 |

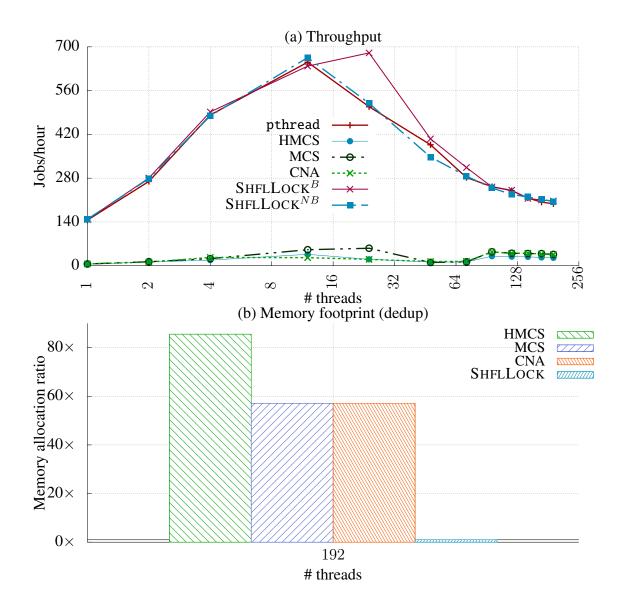

| 5.8 | Impact of locks and their memory allocation overhead on the scalability of Dedup. We report the overall memory allocation overhead that is used during the entire run, with respect to pthread.                                                                                                                                                                                                                                                                                                                             | 104 |

# LIST OF PSEUDO-CODE

| 3.1 | Ordo clock API. The get_time() method returns the current timestamp       |    |

|-----|---------------------------------------------------------------------------|----|

|     | without reordering instructions                                           | 19 |

| 3.2 | Pseudo-code of logical timestamping algorithms used in STM [1, 2] and     |    |

|     | databases [3, 4, 5], and that of physical timestamping used in Oplog [6]. | 25 |

| 3.3 | RLU pseudo-code including our changes                                     | 27 |

| 5.1 | Pseudo-code of the non-blocking version of Shfllocks and the shuf-        |    |

|     | fling mechanism.                                                          | 84 |

| 5.2 | The extra modification required to convert our non-blocking version of    |    |

|     | ShflLock to a blocking one                                                | 87 |

| 5.3 | An optimization for avoiding a waiter wakeup issue in the critical path   |    |

|     | with an extra state update before the TAS lock                            | 88 |

#### **SUMMARY**

Over the past decade, multicore machines have become the norm. A single machine is capable of having thousands of hardware threads or cores. Even cloud providers offer such large multicore machines for data processing engines and databases. Thus, a fundamental question arises is how efficient are existing *synchronization primitives*—timestamping and locking—that developers use for designing concurrent, scalable, and performant applications. This dissertation focuses on understanding the scalability aspect of these primitives, and presents new algorithms and approaches, that either leverage the hardware or the application domain knowledge, to scale up to hundreds of cores.

First, the thesis presents Ordo, a scalable ordering or timestamping primitive, that forms the basis of designing scalable timestamp-based concurrency control mechanisms. Ordo relies on *invariant hardware clocks* and provides a notion of a globally synchronized clock within a machine. We use the Ordo primitive to redesign a synchronization mechanism and concurrency control mechanisms in databases and software transactional memory.

Later, this thesis focuses on the scalability aspect of locks in both virtualized and non-virtualized scenarios. In a virtualized environment, we identify that these locks suffer from various preemption issues due to a semantic gap between the hypervisor sheeduler and a virtual machine scheduler—the double scheduling problem. We address this problem by bridging this gap, in which both the hypervisor and virtual machines share minimal scheduling information to avoid the preemption problems.

Finally, we focus on the design of lock algorithms in general. We find that locks in practice have discrepancies from locks in design. For example, popular spinlocks suffer from excessive cache-line bouncing in multicore (NUMA) systems, while state-of-the-art locks exhibit sub-par single-thread performance. We classify several dominating factors that impact the performance of lock algorithms. We then propose a new technique, *shuffling*, that can dynamically accommodate all these factors, without slowing down the critical

path of the lock. The key idea of shuffling is to re-order the queue of threads waiting to acquire the lock with some pre-established policy. Using shuffling, we propose a family of locking algorithms, called SHFLLOCKS that respect all factors, efficiently utilize waiters, and achieve the best performance.

### **CHAPTER 1**

### INTRODUCTION

The last decade has seen dramatic changes in the hardware landscape. Until the last decade, processor vendors improved application performance by increasing CPU frequency. However, physical limitations in the form of CPU to heat up has resulted in pursuing the direction of multicore machines. As a result, microprocessor vendors have been building bigger multi-core and multi-socket (NUMA) machines [7, 8]. These machines provide a massive amount of memory, accessible by tens-to-hundreds of CPUs in a single machine. Besides, these machines are also capable of supporting non-volatile memory [9, 10, 11], storage devices [12, 13, 14], and even specialized support for hardware virtualization [15, 16, 17]. Because of fast-evolving hardware, concurrent programming is now the de-facto standard to design today's application to leverage today's hardware.

On the software front, almost every application, such as databases [18], processing engines [19, 20], and operating systems are now concurrent. Application developers are parallelizing their applications to use multiples of available cores efficiently. Also, to further improve hardware utilization, organizations are predominantly using virtualization to run multiples of applications together. This scheduling leads to over-subscribing hardware resources, even for large multicore and multi-socket machines.

Thus, application developers rely on various types of synchronization primitives to design concurrent data structures, algorithms, concurrency frameworks, and applications. These primitives handle the concurrency of operations by not only ensuring the correct use of the shared resources but also scheduling the concurrent events. For example, several applications use timestamping as an ordering mechanisms to design 1) concurrency control algorithms in databases and software transactional memory (STM); 2) logging in databases and file systems; and 3) memory reclamation in both memory allocators and garbage

collectors. Furthermore, application developers rely on the lock-based programming model to design concurrent and parallel applications. Lock-based programming model provides mutual exclusion (*i.e.*, exclusive access to shared resources) and also schedule the concurrent requests to access or modify the shared resource. The reason this model is so successful because it is the easiest to reason about correctness and enables easy composability of multiple data structures.

The basic premise of these primitives is to not only ensure application correctness but also have almost negligible overhead while scheduling concurrent events in an application. Unfortunately, with today's evolving hardware and ever-changing application requirements, most of these synchronization primitives have been designed specifically for either hardware or software requirements. For instance, first, most of the timestamp-based concurrency algorithms rely on atomic instructions that become scalability bottleneck with increasing thread count. Second, in the case of lock-based programming, there is no lock algorithm that satisfies various factors, such as data movement, thread contention, over-subscription, and memory footprint, which impact the scalability of locks and their adoption. Finally, the introduction of multiple layers of abstractions, such as virtualization, introduces scheduling overhead for VMs. This overhead stems from the missing semantic information across layers that inhibits the forward progress of applications running inside VMs.

#### **Thesis Statement**

Synchronization primitives are the basic building blocks for today's software stacks that not only ensure application correctness but also schedule concurrent events. Hence, this thesis further improves the performance of applications by providing right abstractions for these primitives that leverage both software and hardware interfaces to efficiently schedule such concurrent events.

This thesis focuses on efficiently scheduling concurrent events at various levels with respect to synchronization primitives: 1) leveraging hardware to minimize ordering overhead (*timestamping*); 2) exposing semantic information across layers to solve the *double-scheduling* issues; and 3) decoupling the policy from the design/implementation of *lock* algorithms. Hence, this thesis makes the following contributions:

## 1.1 Ordering in Concurrency Control Algorithms

Chapter 3 describes 0rdo, a scalable timestamping primitive for multicore machines that employs invariant hardware clocks to address problem of timestamping. This invariant hardware clock is already supported by current major processor architectures [21, 22, 23, 24]. An invariant clock has a unique property: It is monotonically increasing and has a constant skew, regardless of dynamic frequency and voltage scaling, and resets itself to zero whenever a machine resets (on receiving the RESET signal), which is ensured by the processor vendors [25, 26, 22, 24]. However, assuming that all invariant clocks in a machine are synchronized is incorrect because processors do not receive the RESET signal at the same time, which makes these clocks unusable. Thus, we cannot compare two clocks with confidence when correctly designing any time-based concurrent algorithms. The comparison of clocks with no confidence makes them unusable to correctly design a concurrent algorithm. To provide a guarantee of correct use of these clocks, we propose a new primitive, called 0rdo, that embraces uncertainty while comparing two clocks and provides an illusion of a globally synchronized hardware clock in a single machine. We find that various timestamp-based algorithms can benefit from the Ordo primitive. We expose three simple clock-specific methods to replace existing clock with 0rdo in applications. The only trick lies in handling the uncertainty window. We modify both physical and logical timestamp-based algorithms with the 0rdo primitive. Some examples include concurrent data structure libraries and concurrency control algorithms for STM and databases.

### 1.2 Double Scheduling in Virtualization

Cloud providers provide the notion of horizontal as well as vertical application scaling. By running oversubscribing resources. Unfortunately, the multiplexing of VMs introduces the double scheduling problem: 1) the guest OS schedules processes on virtual CPUs (vCPUs) and 2) the hypervisor schedules vCPUs on physical CPUs. The root cause of this problem is a semantic gap between a hypervisor and guest OSes. Chapter 4 identifies several symptoms of the problem that have been individually studied and are very limited. We present an overall one-shot solution with a particular insight: if a certain component of a guest OS is allowed to proceed further, that guest OS will make forward progress. These critical components are the shared critical sections that synchronization mechanisms guard to ensure OS correctness. We bridge the semantic gap between a guest OS and the hypervisor with the following four ideas for making an effective scheduling decision to allow its forward progress. First, we consider shared resources running inside VMs as a critical component. Such resources are guarded by locks or are executing inside interrupt contexts Hence, these components act as forward progress indicators for an applications running inside VMs. Second, we devise a set of para-virtualized methods that annotate these critical components as enlightened critical sections (eCS). These methods are lightweight and rely on shared memory operations to notify a hypervisor from the VM and vice-versa, Third, the hypervisor can now figure out whether a vCPU is executing an eCS and can reschedule it. Finally, we leverage our methods to design a virtualized schedule-aware spinning strategy that allows VMs to be more cooperative to other VMs running on a machine.

### 1.3 Scalable and Practical Locking Primitives

Chapter 5 answers a fundamental question regarding the design of locking primitives. We first present four dominating factors that affect the locks' scalability and their adoption for evolving hardware and software requirements. Moreover, none of the existing lock

algorithms meet all the required criteria. We address all these factors by designing a new breed of locking protocols, called SHFLLOCKS, that are highly performant and practical locks. SHFLLOCKS rely on the *shuffling* technique, that allows the decoupling of the lock design from policy enforcement, such as NUMA-awareness and parking/wake-up strategies. Moreover, shuffling enables enforcing these policies mostly off the critical path by the waiters. Our evaluation in both kernel space and userspace shows that SHFLLOCKS maintain the best throughput regardless of the number of threads contending for the lock.

#### 1.4 Outline and Contributions

The main contributions of this thesis are designing 1) a new ordering primitive that handles the scalability bottleneck in timestamp concurrency control algorithms, 2) understanding the scalability bottlenecks that arise due to synchronization primitives, 3) addressing the limitations of existing synchronization primitives by designing five new algorithms 4) even in the case of virtualized environments.

The rest of this dissertation is organized in the following chapters. Chapter 2 provides the necessary background used throughout this dissertation, such as the importance of ordering, synchronization in the age of many-core machines across the software stack. Chapter 3 presents the Ordo, a scalable ordering primitive for multicore machines. The later part of this dissertation focuses on rethinking the design of synchronization primitives and the associated problems occurring in a virtualized environment. Chapter 4 describes an approach to address the double scheduling problem in a virtualized environment. Chapter 5 presents a family of locking algorithms that use a new technique, called *shuffling*, that allows the decoupling of lock design from policy enforcement. Then Chapter 6 peruses over a set of related works that led us to this dissertation. In Chapter 7, we discuss some of the limitations of proposed approaches and some open-ended questions. Finally, Chapter 8 concludes this dissertation.

### **CHAPTER 2**

### **BACKGROUND AND MOTIVATION**

Synchronization primitives are the backbones for designing concurrent applications. At the hardware level, users rely on hardware constructs, such as atomic instructions that provide a linearizability guarantee [27]. At the software level, we rely on these atomic instructions to provide basic software abstractions, such as synchronization frameworks, and locking primitives for designing concurrent applications. This chapter offers some general ideas, concepts, and background material for such constructs on multicore machines.

### 2.1 A Primer on Multicore Machines

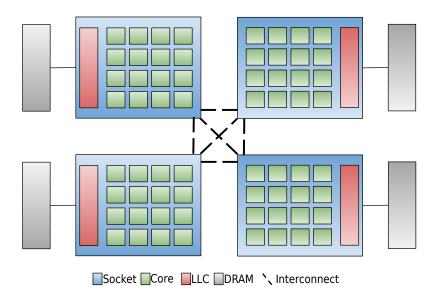

Figure 2.1: Multicore machine design.

Figure 2.1 shows a modern multicore machine, which comprises several sockets. Each socket has several homogeneous cores and a set of private and shared caches. Generally, a core has its private cache (*L1* and *L2*). It accesses a bigger shared cache (*LLC*) with

other cores in a socket. Moreover, each core stores data in DRAM, which is accessible via the memory controller. These multicore machines have non-uniform memory access (NUMA) architecture, *i.e.*, a high-speed interconnect (*e.g.*, Intel QPI/UPI [28, 29] or AMD HyperTransport [30]) links all sockets together. On such machines, accessing the local socket memory is faster than accessing the remote socket memory (hence, the term NUMA). Moreover, each machine provides a coherent view of memory to all cores through a cache-coherence protocol [31]. The coherence protocol works at the granularity of a cache line (64 bytes), as each core tracks the status of a memory location and communicates to other cores when the location is modified or accessed. Unfortunately, maintaining cache-coherence is costly in NUMA machines because of the expensive communication through the interconnect. This latency cost is up to 2-3× higher than within a socket [32].

## 2.2 Ordering in Concurrency

With the advent of multicore machines, concurrent programming is the de facto approach to design today's algorithms, which applications rely upon. Hence, ordering becomes fundamental to the design of any concurrent algorithm. With ordering, algorithms can achieve varying levels of consistency to squeeze out the performance from hardware. For systems software, consistency depends on algorithms that require linearizability [27] for the composability of data structures [33, 6], concurrency control mechanisms for software transactional memory (STM) [1], or different isolation levels for database transactions [5, 34, 3]. The notion of ordering not only is limited to consistency, but also is applicable to either maintaining the history of operations for logging [35, 36, 37, 38] or determining the quiescence period for memory reclamation [39, 40, 33]. Depending on the consistency requirement, ordering such as a logical timestamping [33, 1], physical timestamping [39, 41, 6, 42, 43], and data-driven versioning [34, 44] can be achieved in several ways. The most common approach is to use a logical clock that is easier to maintain by software and is amenable to various ordering requirements.

A logical clock is a favorable ordering approach. An algorithm can globally update or access the clock in a single machine. However, the logical clock is one of the prime scalability bottlenecks on large multicore machines [7, 8] because it is maintained via an atomic instruction that incurs cache-coherence traffic. Unfortunately, these atomic instructions create cache-line contention that becomes the scalability bottleneck and it is more severe in multi-socket machines and in hyper-threaded scenarios [32, 45, 46]. Thus, maintaining a software clock is a deterrent to the scalability of an application, which holds true for several concurrency control mechanisms for concurrent programming [1, 47] and database transactions [3, 5]. To address this problem, various approaches—ranging from batched-update [5] to local versioning [34] to completely share-nothing designs [48, 49] have been put into practice. However, these approaches have some side effects. They either increase the abort rates for STM [50] and databases [5] or complicate the design of the system software [49, 34, 51]. In addition, in the past decade, physical timestamping has been gaining traction for designing data structures [52, 43] synchronization mechanisms [6] for large multicore machines. However, such approaches assume that timestamp counters provided by hardware are synchronized, which is not entirely correct for existing hardware.

### 2.2.1 Multicore Hardware Clocks

Today's multicore machines provide per-core or per-processor hardware clocks [21, 22, 23, 24]. For example, all modern processor vendors such as Intel and AMD provide an RDTSC counter, while Sparc and ARM have stick and cntvct counter, respectively. These hardware clocks are **invariant** in nature, *i.e.*, processor vendors guarantee that these clocks are monotonically increasing at a constant rate, regardless of the processor speed and its fluctuation. Moreover, they reset to zero whenever a processor receives a RESET signal (i.e., reboots). To provide such an invariant property, the current hardware always synchronizes these clocks from an external clock on the motherboard [53, 26, 25]. This is required

<sup>&</sup>lt;sup>1</sup>These clocks may increase at a different frequency than that of a processor.

because vendors guarantee that the clocks do not fluctuate even if a processor goes to deep sleep states, which is always ensured by the motherboard clock. However, vendors do not guarantee the synchronization of clocks across a processor (socket) boundary in a multicore machine [21], not even within a processor because there is no guarantee that each processor can receive the broadcasted RESET signal at the same instant either inside a socket or across them. In addition, these hardware clocks do not provide the notion of real time.

These current invariant clocks are not reliable enough to design concurrent algorithms. To use them with confidence, we need to have a clock synchronization mechanism that provides constant physical skew between clocks, or we measure our offset to synchronize these clocks in software. Unfortunately, none of clock synchronization approaches work because hardware vendors cannot provide physical skew for every processor, and we cannot measure using existing clock synchronization protocols [54, 55, 56, 57], as software measurement induces overhead, in which the measured offset may be greater than the physical offset.

## 2.3 Locking Primitives

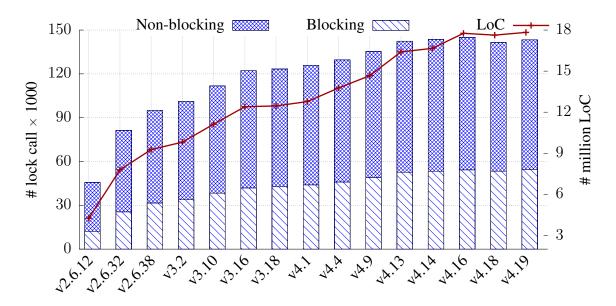

Locks are one of the easiest approach to designing concurrent application. Figure 2.2 illustrates the increasing use of locks in the Linux OS. Similar to the evolution of multicore [7, 8], not only the use of locks has dramatically increased for fine-grained locking [58], but also they have evolved into several types to minimize the cost of handling critical sections. For instance, the current OSes rely on several types of locks, ranging from non-blocking (*e.g.*, spinlocks, read-write locks) to blocking (*e.g.*, mutex, read-write semaphores). This trend is also applicable in other concurrent applications, such as databases, and other OSes. Another interesting trend is that these locks have been continuously evolving, as shown in Table 2.1, to improve the scalability of OS. For instance, a simple spinlock has evolved from a simple test-and-set (TAS) lock to a para-virtualized qspinlock (a variant of MCS lock and also supports virtualized environment). Hence, we try to understand the implication of these primitives and their interplay with the task scheduler on application performance. We first

**Figure 2.2:** Indirect metric of the growing complexity of lock usage: the number of lock() API calls in the Linux kernel source code.

describe the general evolution of locks and later contrast it with lock evolution inside the Linux kernel.

## 2.3.1 Evolution of Lock design

Since the dawn of concurrent programming, hardware has been the dominant factor [32] in the evolution of lock algorithms. For instance, queue-based locks [59] reduce cache traffic relative to test-and-set (TAS) and ticket locks. On NUMA architectures, hierarchical locks improve throughput [60, 61, 62, 63, 64, 65] as they amortize remote access cost by physically partitioning a lock into a global lock and per-node locks. Cohort locks [63] generalize this design for any lock combination up to two levels, while Chabbi *et al.* [64, 65] further extended this approach to multiple hierarchies, using the MCS lock as a building block. Unfortunately, hierarchical locks have two issues: degraded performance for small numbers of cores, and, most importantly, memory overhead. AHMCS [65] addresses the problem of single thread performance but suffers from the memory overhead of hierarchical locks. Meanwhile, our CST locks work [66] partially addresses the problem of memory overhead by allocating the lock's memory on a first touch basis. However, it still suffers from

**Table 2.1:** Evolution of synchronization primitives in the last 15 years in Linux along with their introduction with the corresponding Linux version.

| Locks                | Features/Optimization                                             | Reason:                                                                                        | Linux ve |

|----------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------|

|                      | TAS                                                               | Simple test-and-set based lock that continously spins                                          | v2.6.12  |

|                      | Ticket                                                            | FIFO locks for fairness up to 255 cores                                                        | v2.6.25  |

|                      | Ticket with para-virtualized TAS                                  | Ticket lock in normal case, but TAS lock in para-virtualized scenario                          | v2.6.27  |

| ${\tt spinlock}(NB)$ | Paravirtualized Ticket                                            | Use Ticket locks in both para-virtualized and non-paravirtualized scenario                     |          |

|                      | Paravirtualized Ticket with slow-<br>path                         | Schedule out vCPUs in paravirtualized case to mitigate LHP/LWP                                 | v3.11    |

|                      | qspinlock with paravirtualized TAS                                | 4 byte MCS lock to remove cache-line contention, but TAS to remove LHP/LWP                     | v4.4     |

|                      | Unfair paravirtualized qspinlock                                  | Limited lock stealing and adaptive lock spinning to mitigate LHP/LWP                           | v4.5     |

|                      | 4 byte TAS                                                        | Simple test-and-set lock with first byte for storing reader count                              | v2.6.12  |

|                      | 4 byte TAS with 4 byte read count                                 | Increase the readers count to compensate for larger machines                                   | v3.11    |

| rwlock (NB)          | Ticket with 4 byte read/write                                     | Improves the throughput and latency of the rwlock                                              | v3.16    |

|                      | (qrwlock) qspinlock with four byte read- /write counter (qrwlock) | Further removes cache-line contention of the Ticket lock                                       |          |

|                      | spinlock with sequence number                                     | Non-starving writers with retrying readers to read consistent data                             | v2.6.12  |

| eqlock (NB)          | New locking reader type method                                    | Allow readers to acquire the lock without updating the sequence count                          | v3.12    |

|                      | New latch API                                                     | Allows queries during non-atomic modifications with two versions                               | v4.2     |

|                      | A counter with a spinlock and a wait list                         | A semaphore with a wait queue that maintains waiters                                           | v2.6.12  |

| mutex (B)            | atomic counter with a waiting queue                               | An atomic counter with a simple wait queue to handle waiters                                   |          |

|                      | Optimistic spinning                                               | Allowed waiters to spin for a time period before scheduling out                                |          |

|                      | Queue-based optimistic spinning                                   | Allow waiters to form a queue while spinning to reduce cache-line contention                   |          |

|                      | Lockless next waiter wakeup                                       | Shortens the fast path to wake-up the very next waiter, thereby decreasing spinlock contention |          |

|                      | Break if vCPU is preempted                                        | Schedule out in the mid-path phase if the owner vCPU is preempted                              | v4.9     |

| rwsem (B)            | A counter with a spinlock and a wait list                         | A counter maintains both writers and readers with wait list for waiters                        | v2.6.12  |

|                      | Optimistic spinning                                               | Allow waiters to wait while spinning to mitigate blocked-waiter wakeup problem                 |          |

|                      | Writer optimistic spinning                                        | Disallow waiting writers to waste CPU cycles                                                   | v4.7     |

| percpu-rwsem (B)     | percpu counter with mutex                                         | Lightweight RCU-based readers, with rcu_synchronize()-based mutex writers                      | v3.6     |

|                      | rwsem with percpu and global counter                              | Optimize readers' counter latency after a writer unlocks                                       |          |

|                      | Optimized readers                                                 | Removed the global counter by ordering reader-state vs reader-count with RCU                   |          |

the memory overhead in the worst case and introduces a large memory allocate overhead on the critical path. Unfortunately, both of these works partially address one of these issues, but not both concurrently.

We observe a similar evolution in designing readers-writer locks. Mellor-Crummey and Scott [67] proposed variants of readers-writer locks on top of the queue-based locks. However, these locks create coherence traffic in NUMA machines. Calciu *et al.* [68] proposed a per-socket read indicator on top of Cohort locks to localize the reader contention within a socket, but both per-socket or per-CPU [69] approaches require extra memory and are beneficial only in particular cases [70, 71, 72].

## 2.3.2 Locks in the kernel space (Linux)

Over the past decade, the Linux kernel has been striving for more concurrency by switching to finer granularity locks, as shown in Table 2.1. One of the most significant goals is to maintain optimal single-thread performance. In addition, lock design must consider: 1) the interaction with the scheduler, 2) the size of the lock structure, and 3) avoiding any explicit memory allocation. These factors have led to sophisticated optimizations. The spinlock is the primary locking construct in Linux; it has evolved from TAS to ticket locks to an MCS variant [73]. The current design is an amalgamation of two locks: a TAS lock in the fast path and an MCS lock in the slow path.

The second most widely used synchronization primitives are blocking locks. Moreover, various OSes, in particular Linux, do not allow nested critical sections for any blocking locks. Currently, these locks can be considered as the big-kernel locks in Linux, as they are the most common guards that an OS uses for guarding inodes in file system, and address space manipulation. There are two variants: mutex and rwsem.

mutex incorporates a fast path comprising of test-and-test-and-set lock (TTAS), an abortable queue-based spinning in mid-path [74], and a parking list per-lock instance in the slow path. The algorithm works by first trying to atomically update the lock variable, called fast path; on failure, the mid-path phase (optimistic spinning) begins in which only a single waiter is queued up if there is no spinning waiter and optimistically spins until its schedule quota expires. If the waiter still does not acquire the lock, it goes to the slow-path phase in which it acquires a lock on the parking list (parking lock), adds itself, and schedules out after releasing the parking lock. During the unlock phase, the lock holder first resets the TTAS variable and wakes up a waiter from the parking list while holding the parking lock. Meanwhile, it is possible that either a new waiter can acquire the lock in the fast path or a spinning waiter in the mid path. Now, once a waiter is scheduled in, it again acquires the parking lock and tries to acquire the TTAS lock. If successful, it removes itself from the parking list and enters the critical section; otherwise, it schedules itself out again and

sleeps until a lock holder wakes it up. The current algorithm is unfair because of the TTAS lock; even starves its waiters in the slow-path phase. Moreover, the algorithm also suffers two overheads. Firs is from cache-line contention because of the TTAS lock and waiters maintenance. Second is the scheduling overhead in the slow-path phase and the unlock phase for parking a running waiter and waking up a sleeping waiter [66].

The readers-writer semaphore (rwsem) is an extension of mutex, with a writer-preferred version [75, 76]. Both the write lock and the readers count are encoded in a word to decide readers, writer, and waiting writers or readers. Moreover, rwsem maintains a single parking list in which both readers and writers are added in the slow path. Similar to mutex, it also suffers from severe cache-line movement both when the cores are over- and under-subscribed because of the contention on the reader-writer indicator.