## SIGNATURE DRIVEN LOW COST TEST, DIAGNOSIS AND

### **TUNING OF WIRELESS SYSTEMS**

A Dissertation Presented to The Academic Faculty

by

Shyam Kumar Devarakond

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology May, 2013

## **COPYRIGHT 2013 BY SHYAM KUMAR DEVARAKOND**

## SIGNATURE DRIVEN LOW COST TEST, DIAGNOSIS AND

## **TUNING OF WIRELESS SYSTEMS**

Approved by:

Dr. Abhijit Chatterjee, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Linda Milor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. David Keezer School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Xiaoli Ma School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Suresh K. Sitaraman School of Mechanical Engineering *Georgia Institute of Technology*

Date Approved: March 12, 2013

To my loving family...

### ACKNOWLEDGEMENTS

First and foremost, I would like to express my sincere gratitude to my advisor Professor Abhijit Chatterjee for his constant support and advice throughout the course of my PhD. I would like to thank him for providing me an opportunity to conduct research under his guidance. His energy and motivation has always inspired me to do my best. Over the years, our numerous discussions have had a significant influence in my professional and personal outlook. He is a remarkable person who has made this entire journey highly interesting.

I would like to take this opportunity to thank my committee members, Prof. David Keezer, Prof. Linda Milor, Prof. Xiaoli Ma, Prof. Suresh Sitaraman for taking time to serve on my committee and offering valuable suggestions in regards to my research. I would like to thank Semiconductor Research Corporation (SRC), Gigascale Systems Research Corporation (GSRC), National Science Foundation (NSF) and National Semiconductor for their support during various stages of my research at Georgia Tech.

I would like to thank Nash Khouzam, Dr. Zhenhai Fu, Dr. Soumendu Bhattacharya and John M. Carulli Jr. for their guidance and help during my internships at National Semiconductor and Texas Instruments. The opportunities they provided helped me understand the many practical challenges relating to IC industry. Their timely guidance has provided direction to my research.

I would like to thank all my colleagues in my research group whose support and suggestions have been invaluable during the course of my stay here at Georgia Institute of Technology. I would like to thank Rajarajan Senguttuvan, Vishwanath Natarajan, Shreyas Sen, Hyun Choi, Mudassar Nisar, Sehun Kook, Jayaram Natarajan, Joshua Wells, Aritra Banerjee, Debashis Banerjee, Debesh Bhatta, Sabyasachi Deyati, Nicholas Tzou, Sen-Wen Hsiao, Thomas Moon, Barry Muldrey, Xian Wang, and Suvadeep Banerjee. I am lucky that my path crossed with all these unique individuals.

I would like to thank my friends Jayaram Natarajan, Vijay Sukumaran, Sourabh Khire, Kaushik Ramachandran, Debashis Banerjee, Rishiraj Bheda, Gokul Kumar, Rohan Verma, Srikaanth Niranjan, Divyanshu Agarwal, Hemant Sane, Bravishma Narayan, Krishna Bharath, Ashok Kumar, Kiran Iyer. Thanks to these people, I had a wonderful time during my time here in Atlanta.

I would like to thank Dr. Sriram Rallabhandi, Dr. Tushar Kumar for their guidance and help during my initial stages of PhD and my stay here in Atlanta. I would like to thank my family members Anuradha Ikkurti and Vijay Yellai for their help during my initial phase of life in US.

Finally yet importantly, I am ever grateful to my parents Sarath Kumar and Vijayasri Sarath for their unconditional love, constant support, and wishes. Their numerous personal sacrifices for my ambitions have made this possible. I am lucky to have such parents who have helped me through all the high and low points of my life. I would also like to thank my brother Shravan Kumar for all his love and moral support. I would like to thank my grandfather Venkateswarlu Ikkurty for his support.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTSiv                                                          |

|-----------------------------------------------------------------------------|

| LIST OF TABLESxi                                                            |

| LIST OF FIGURESxiii                                                         |

| LIST OF ABBREVIATIONSxix                                                    |

| SUMMARY xxi                                                                 |

| CHAPTER 1. INTRODUCTION1                                                    |

| 1.1. Process Variation and Yield loss                                       |

| 1.2. Conventional Specification Testing of Analog/RF Circuits and Systems 4 |

| 1.3. Alternative Methodologies for Testing of Analog/RF Circuits            |

| 1.4. Diagnosis for Analog/RF Circuits and Systems7                          |

| 1.5. System-Level Specification Testing 10                                  |

| 1.6. Prior Work in Tuning of Analog/RF Circuits                             |

| 1.6.1. Digital Baseband or DSP-Based Monitoring and Tuning                  |

| 1.6.2. On-Chip Monitoring and Analog Tuning                                 |

| 1.6.3. Digital Baseband Monitoring, with Analog and Digital Co-tuning 17    |

| CHAPTER 2. PRINCIPLES OF SUPERVISED LEARNING AND MODEL-                     |

| SOLVING-BASED TEST TECHNIQUES20                                             |

| 2.1. Supervised Learning or Alternate Testing Technique                     |

| vi                                                                          |

| 2.2. Model-Solving-Based Testing/Monitoring                           | . 22 |

|-----------------------------------------------------------------------|------|

| 2.3. Test Optimization                                                | . 24 |

| CHAPTER 3. TEST AND DIAGNOSIS OF RF CIRCUITS AND SYSTEMS              | . 25 |

| 3.1. Concurrent Test and Diagnosis of Analog/RF Circuits              | . 26 |

| 3.1.1. Proposed Methodology                                           | . 27 |

| 3.1.2. Test Generation                                                | . 29 |

| 3.1.3. Determination of Significant Device/Circuit Parameters         | . 32 |

| 3.1.4. Simulation Results - Diagnosis and Testing                     | . 32 |

| 3.1.4.1. Case Study I - Operational Amplifier                         | . 32 |

| 3.1.4.2. Case Study II - Low Noise Amplifier                          | . 35 |

| 3.1.5. Simulation Results - Cause-Effect Monitoring                   | . 39 |

| 3.1.6. Hardware Validation of Proposed Methodology                    | . 41 |

| 3.1.6.1. E-test Parameters and Process control                        | . 42 |

| 3.1.6.2. Spatial Interpolation                                        | . 44 |

| 3.1.6.3. Device Results                                               | . 45 |

| 3.1.6.4. Significant E-test Parameters (Dimensionality Reduction)     | . 57 |

| 3.1.7. Key Contributions and Applications                             | . 61 |

| 3.2. Online Testing or Performance Monitoring of Analog/RF Front Ends | . 63 |

| 3.2.1. Proposed Approach                                              | . 65 |

| 3.2.2. Architecture of Proposed Solution                              | . 65 |

| 3.2.3. Mathematical Framework                                         | . 66 |

| 3.2.4. Application to Transmitter Framework                           | . 69 |

| 3.2.5.    | OFDM Transmitter Baseband Modeling                         | 71   |

|-----------|------------------------------------------------------------|------|

| 3.2.6.    | Modeling RF Front Ends                                     | 72   |

| 3.2.7.    | Simulation Setup and Results                               | 73   |

| 3.2.8.    | Key Contributions                                          | 74   |

| CHAPTER 4 | 4. DIGITALLY ASSISTED TUNING TECHNIQUES FOR                |      |

|           | ND RF SYSTEMS                                              | . 77 |

|           |                                                            |      |

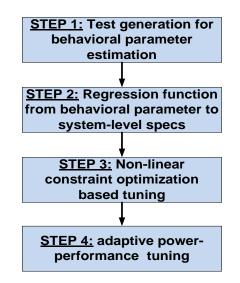

| 4.1 Ove   | erview of Self-Tuning/Self-Healing Methodology             | 78   |

| 4.2. Prin | ciples of the Proposed Tuning Approach                     | 79   |

| 4.2.1.    | Optimal Stimulus Generation                                | 79   |

| 4.2.2.    | Tuning Methodologies Overview                              | 81   |

| 4.3. Dig  | ital Baseband (DSP) Based Monitoring and Tuning            | 82   |

| 4.3.1.    | Low-Cost Digital Correction Scheme for PA Imperfections    | 82   |

| 4.3.1.    | 1. Proposed Methodology                                    | 84   |

| 4.3.1.    | 2. Behavioral Modeling of Power Amplifier                  | 85   |

| 4.3.1.    | 3. Simulation Results                                      | 88   |

| 4.3.2.    | BIST-Assisted Digital Compensation for MB-UWB Transmitters | 90   |

| 4.3.2.    | 1. Motivation                                              | 93   |

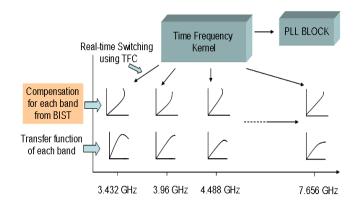

| 4.3.2.    | 2. Compensation Technique                                  | 94   |

| 4.3.2.    | 3. System Description                                      | 96   |

| 4.3.2.    | 4. BIST for Non-Linearity Parameter Estimation             | 98   |

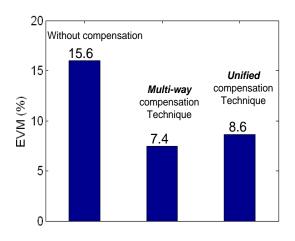

| 4.3.2.    | 5. Simulation Results - Multi-Way Compensation Technique   | 100  |

| 4.3.2.    | 6. Simulation Results - Unified Compensation Technique     | 102  |

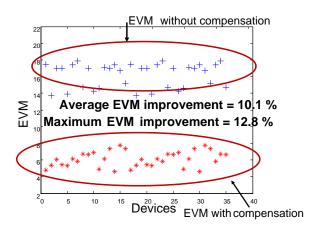

| 4.3.2.7   | 7. Effectiveness of Digital Compensation Under Process Variation 10 | 03 |

|-----------|---------------------------------------------------------------------|----|

| 4.3.3.    | Key Discussions                                                     | 05 |

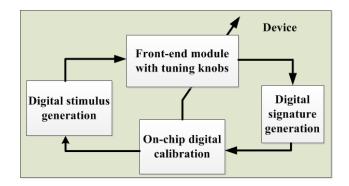

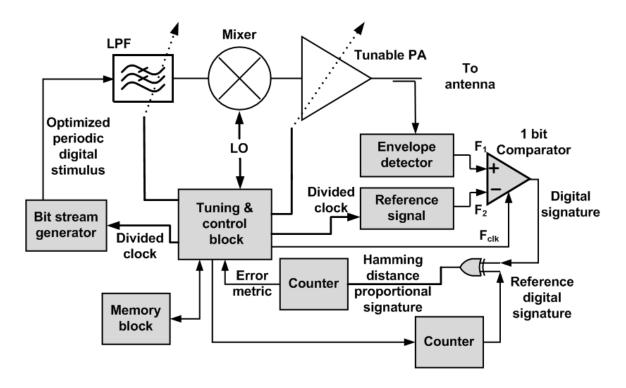

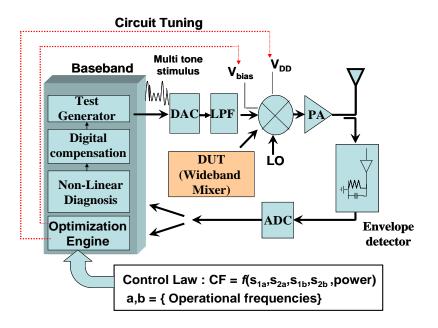

| 4.4. On-0 | Chip Digital-Assisted RF System Tuning Methodology 10               | 06 |

| 4.4.1.    | DUT Performance Evaluation                                          | 08 |

| 4.4.2.    | Tuning Architecture                                                 | 14 |

| 4.4.3.    | Tuning Methodology1                                                 | 16 |

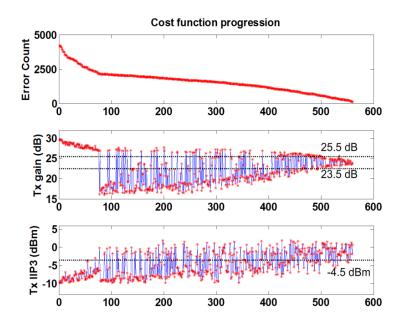

| 4.4.4.    | Cost Function Formulation1                                          | 18 |

| 4.4.5.    | Optimized Stimulus Generation                                       | 20 |

| 4.4.6.    | Simulation Results                                                  | 21 |

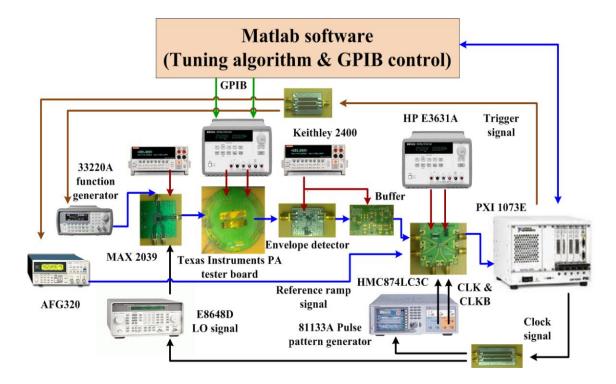

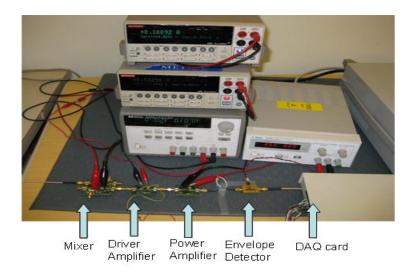

| 4.4.7.    | Hardware Validation                                                 | 27 |

| 4.4.8.    | Key Discussions                                                     | 31 |

| 4.5. DSP  | -Assisted System Architecture with Analog and Digital Co-tuning 13  | 33 |

| 4.5.1.    | DSP-Based BIST for Multiple Performance Metrics Estimation 13       | 33 |

| 4.5.1.1   | . Control Law for Tuning a Circuit Knob                             | 34 |

| 4.5.1.2   | 2. Cost Function Formulation                                        | 36 |

| 4.5.1.3   | B. Simulation Framework                                             | 37 |

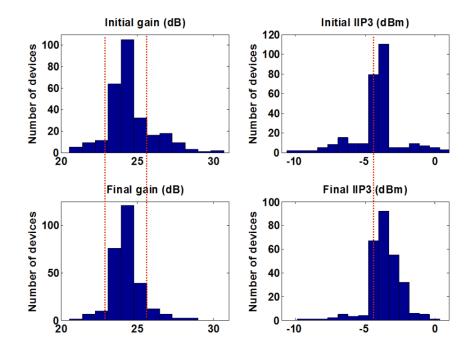

| 4.5.1.4   | . Yield Analysis 14                                                 | 43 |

| 4.5.1.5   | 5. Hardware Validation                                              | 44 |

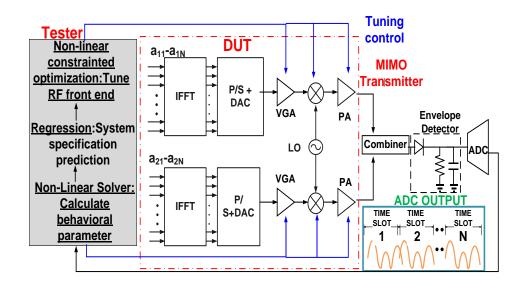

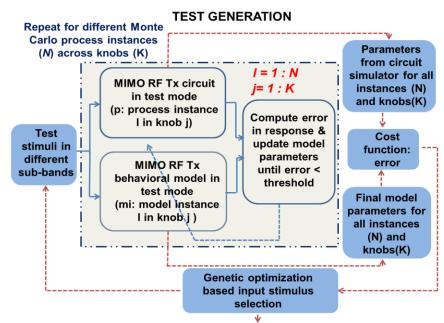

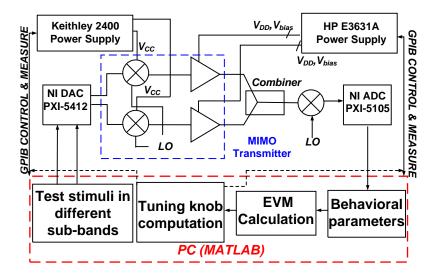

| 4.5.2.    | System-Level Test and Adaptive Tuning of MIMO RF Systems 14         | 46 |

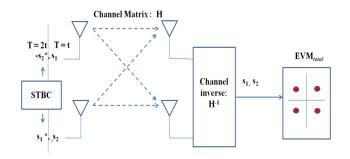

| 4.5.2.1   | . Overview of MIMO-OFDM Systems                                     | 47 |

| 4.5.2.2   | 2. Test and Tune Architecture and Methodology                       | 50 |

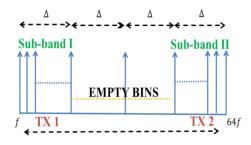

| 4.5.2.3   | B. Optimized Stimulus Generation for MIMO RF Transmitter            | 51 |

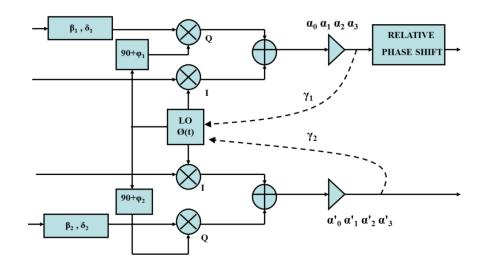

| 4.5.2.4   | MIMO RF Transmitter System Impairment Modeling 1                    | 55 |

| REFERENCES   | 5                                  |     |

|--------------|------------------------------------|-----|

| CHAPTER 5. ( | CONCLUSION AND FUTURE WORK         | 180 |

| 4.5.2.9.     | Hardware Validation                | 177 |

| 4.5.2.8.     | System Results                     |     |

| 4.5.2.7.     | Adaptive Tuning Framework          |     |

| 4.5.2.6.     | Tuning Methodology                 |     |

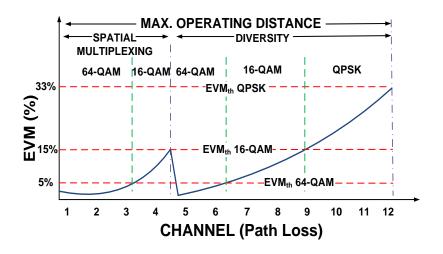

| 4.5.2.5.     | System-Level Specification Testing |     |

# LIST OF TABLES

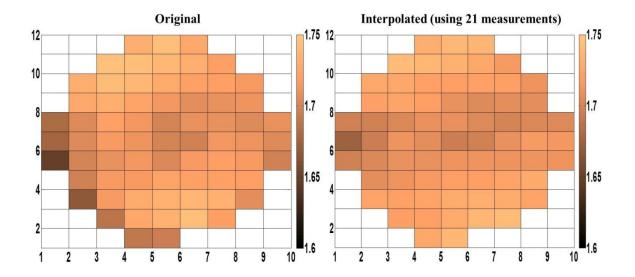

| Table 1: Error metrics obtained by interpolating 21 measurements.    48           |

|-----------------------------------------------------------------------------------|

| Table 2: Error metrics obtained by interpolating nine measurements.    49         |

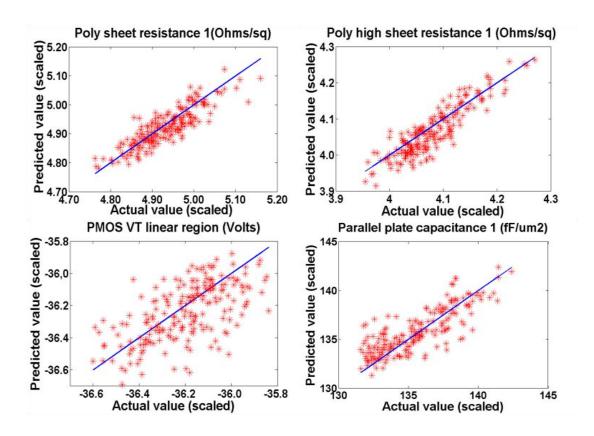

| Table 3: Prediction of e-test parameters                                          |

| Table 4: Rank correlation between test measurements and poly sheet resistance 55  |

| Table 5: Dimensionality reduction results for e-test parameters.    60            |

| Table 6: Relative error in specification monitoring of the system                 |

| Table 7: Specification monitoring in presence of feedback performance deviation75 |

| Table 8: Relative error in AM/AM and AM/PM characteristics.    89                 |

| Table 9: Nominal specifications of the device.    122                             |

| Table 10: Error and reconstruction error for different instances                  |

| Table 11: Nominal hardware specifications                                         |

| Table 12: Hardware validation of the technique.    132                            |

| Table 13: Nominal test specifications limits.    141                              |

| Table 14: Performance metrics of the boundary process.    142                     |

| Table 15: Tuning trade-offs for a boundary process                                |

| Table 16: Hardware validation of proposed methodology                             |

| Table 17: Error variation with ADC word size                                      |

| Table 18: Error in the prediction of various MIMO transmitter specifications.      | 172 |

|------------------------------------------------------------------------------------|-----|

| Table 19: MIMO transmitter nominal specifications and pass bounds                  | 173 |

| Table 20: Average performance metric of devices tuned in 3 <sup>rd</sup> iteration | 176 |

| Table 21: Tuning of performance metrics for MIMO-RF transmitter instances          | 179 |

# LIST OF FIGURES

| Figure 1: Dissertation outline and scope                                | xxiii |

|-------------------------------------------------------------------------|-------|

| Figure 2: Future trends in wireless systems (Source: ITRS [2])          | 2     |

| Figure 3: Overview of the tuning concept                                | 13    |

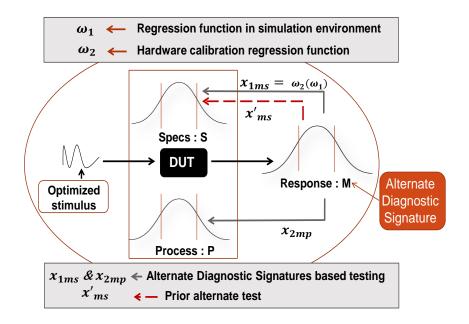

| Figure 4: Alternate test or supervised learning technique               | 22    |

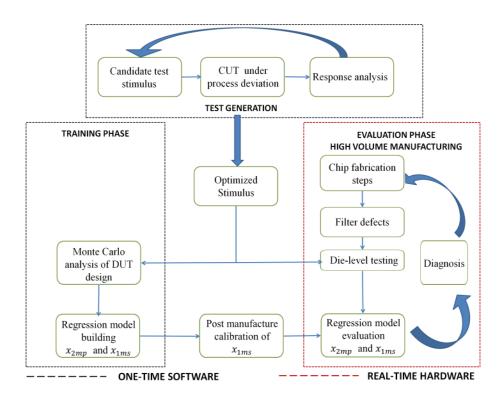

| Figure 5: Implementation of supervised learning in production floor.    | 22    |

| Figure 6: Model-solving-based testing                                   | 23    |

| Figure 7: Proposed concept                                              | 27    |

| Figure 8: Overview of the methodology.                                  | 29    |

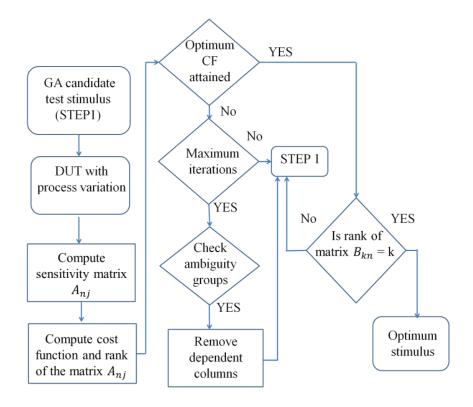

| Figure 9: Flowchart of the test generation algorithm                    | 34    |

| Figure 10: Complete methodology of proposed technique                   | 34    |

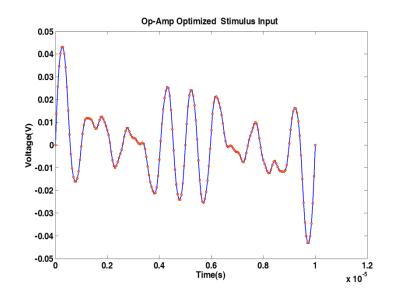

| Figure 11: Optimized input stimulus.                                    | 35    |

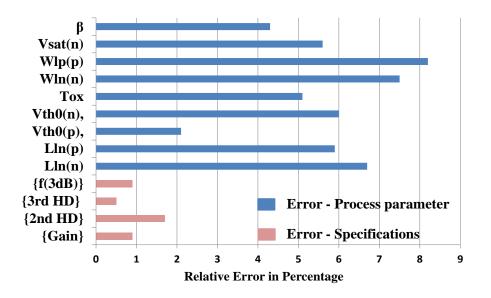

| Figure 12: Prediction error in specifications and process parameters    | 35    |

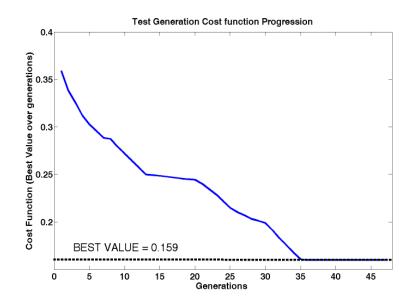

| Figure 13: Test generation cost function progression                    | 36    |

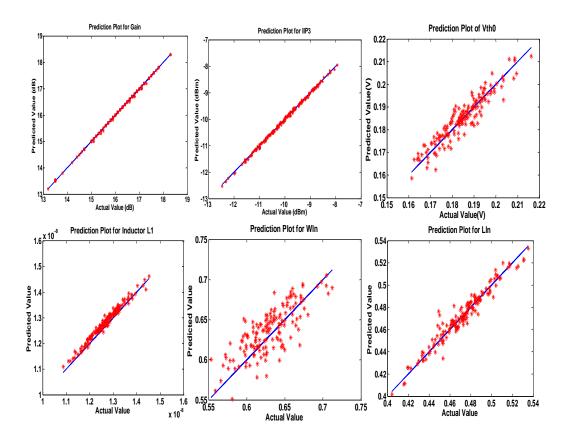

| Figure 14: Prediction plots for specifications and process parameters   | 37    |

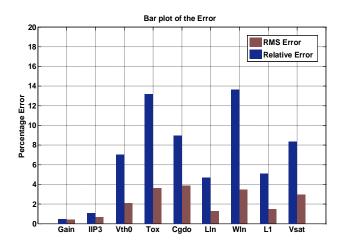

| Figure 15: Error in prediction of the parameters                        | 38    |

| Figure 16: Specification and Spice-level parameter histograms           | 38    |

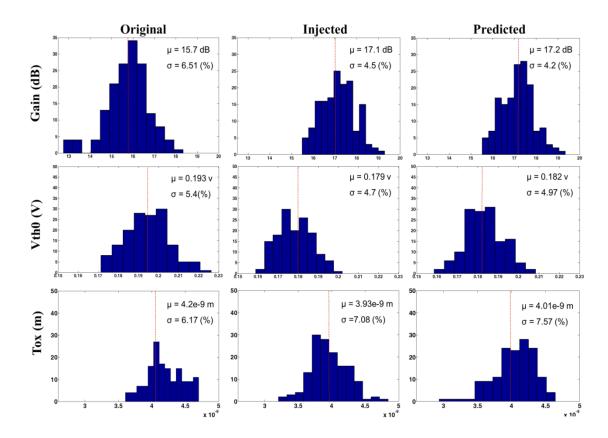

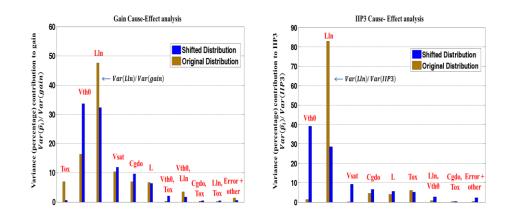

| Figure 17: Cause-Effect analysis of gain and IIP3 specifications of LNA | 40    |

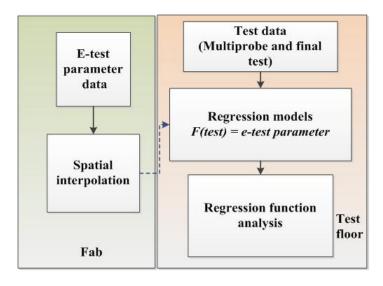

| Figure 18: Hardware validation approach                                               |

|---------------------------------------------------------------------------------------|

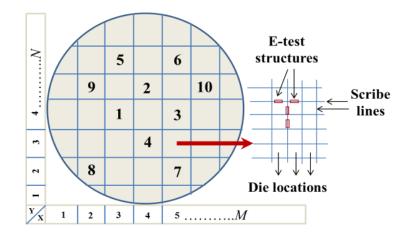

| Figure 19: Hypothetical shot-map of the wafer                                         |

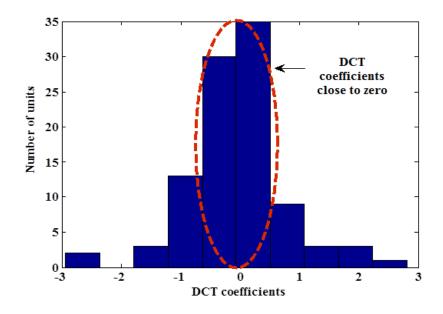

| Figure 20: Histogram plot of the DCT coefficients                                     |

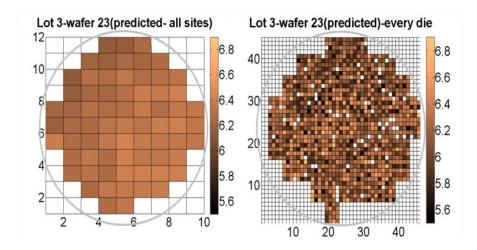

| Figure 21: Original and interpolated e-test wafer maps for N-well sheet resistance 49 |

| Figure 22: Scaled prediction plots for process e-test parameters                      |

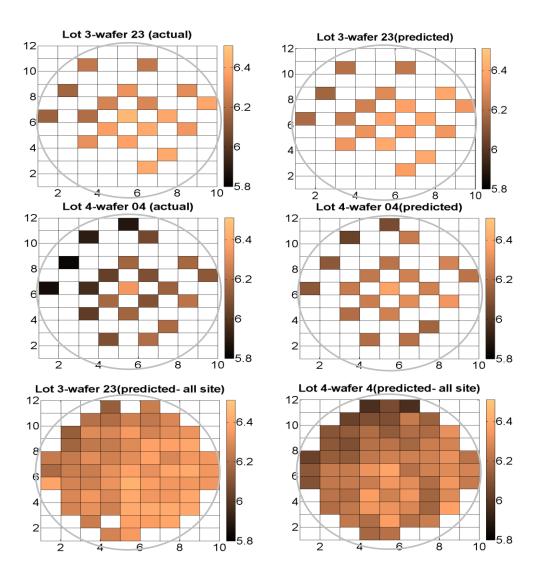

| Figure 23: Scaled prediction plots of PMOS drive current for different wafers 54      |

| Figure 24: Prediction plots of PMOS drive current at site-level and die-level         |

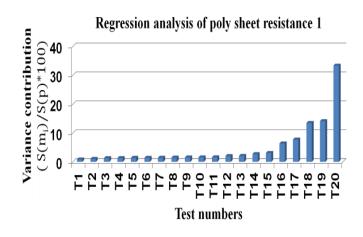

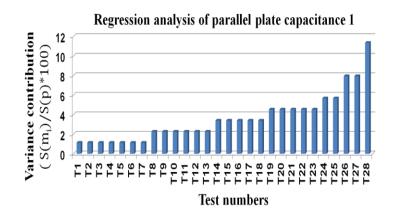

| Figure 25: Analysis of regression model for poly sheet resistance 1                   |

| Figure 26: Analysis of regression model for poly sheet resistance 1                   |

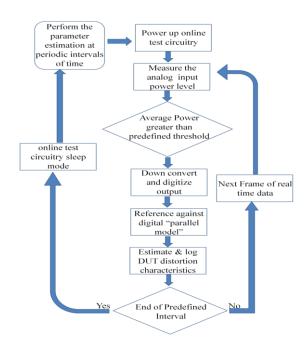

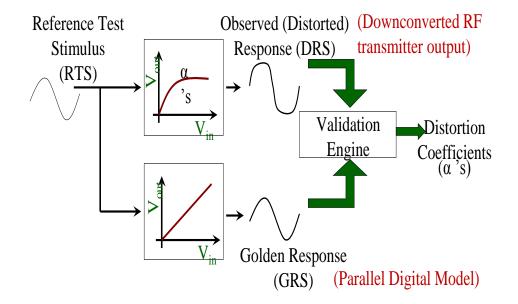

| Figure 27: Block diagram of the proposed technique67                                  |

| Figure 28: Flowchart of the proposed methodology                                      |

| Figure 29: Conceptual diagram for proposed theory                                     |

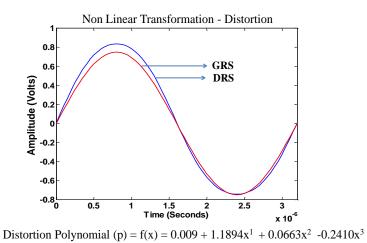

| Figure 30: Sine wave example of the mathematical theory                               |

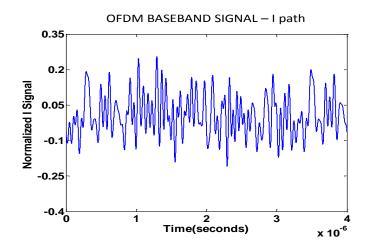

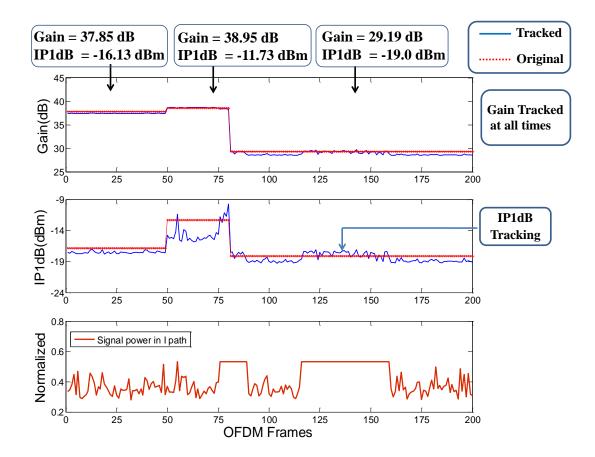

| Figure 31: Baseband OFDM signal72                                                     |

| Figure 32: Performance monitoring of in-field RF transmitter74                        |

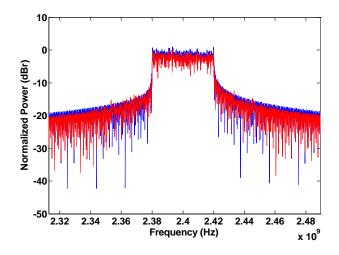

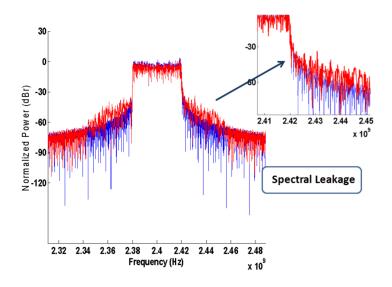

| Figure 33: Spectral plot of frame 65-minimal distortion76                             |

| Figure 34: Spectral plot of frame 120-spectral leakage causing distortion76           |

| Figure 35: System-level self-healing conceptual diagram79                             |

| Figure 36: Optimum test stimulus generation concept                            |

|--------------------------------------------------------------------------------|

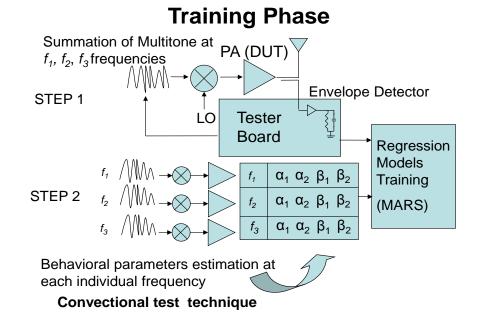

| Figure 37: Training phase of the proposed methodology in production            |

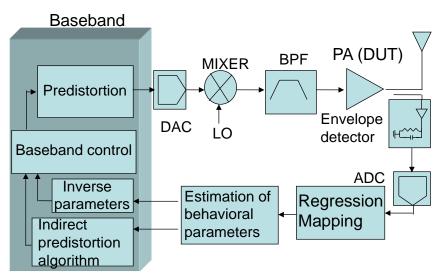

| Figure 38: DSP-assisted linearization of PA                                    |

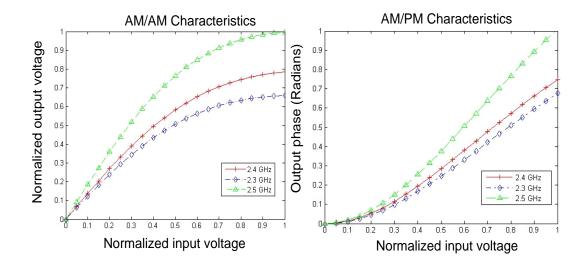

| Figure 39: AM/AM and AM/PM characteristics at different carrier frequencies 89 |

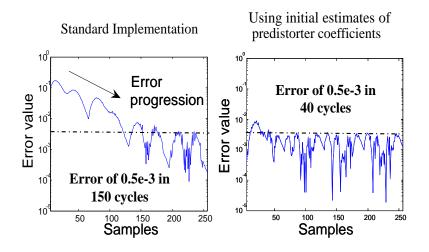

| Figure 40: Error progression comparison                                        |

| Figure 41: Constellation points of the transmitter                             |

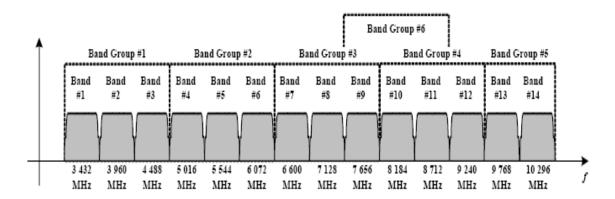

| Figure 42: Band groups in MB-OFDM UWB scheme                                   |

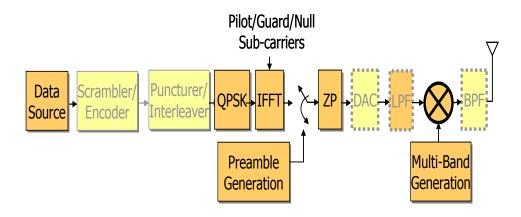

| Figure 43: Traditional MB-OFDM transmitter                                     |

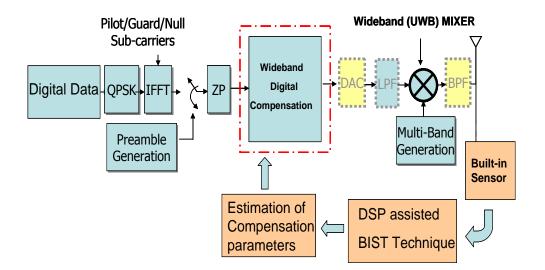

| Figure 44: MB-OFDM system with digital compensation                            |

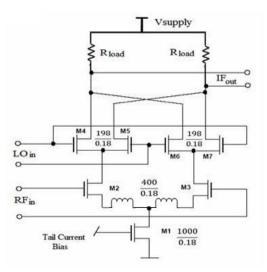

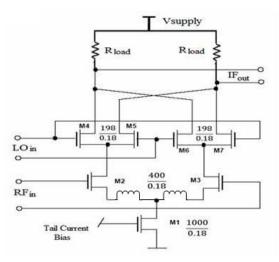

| Figure 45: Schematic of wide-band mixer97                                      |

| Figure 46: Variation of mixer gain over a single band of frequency (528 MHz)97 |

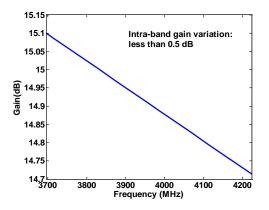

| Figure 47: Mixer specifications variations over an operating frequency range   |

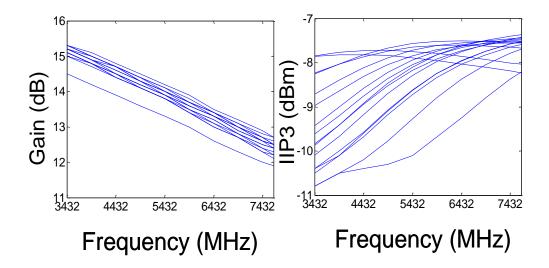

| Figure 48: Block diagram of BIST for non-linearity parameter estimation        |

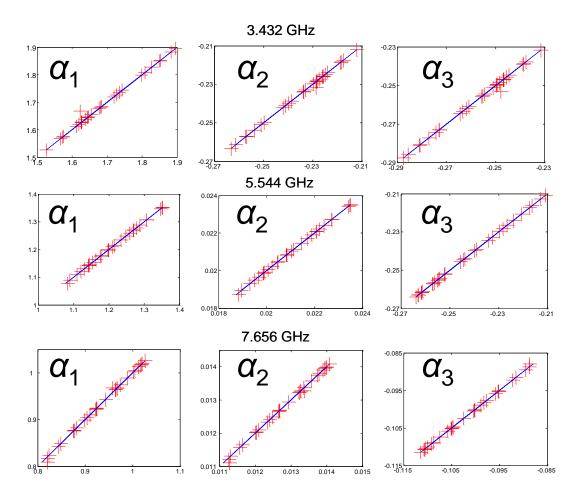

| Figure 49: Behavioral parameter prediction for the three bands 101             |

| Figure 50: Multi-way compensation technique 102                                |

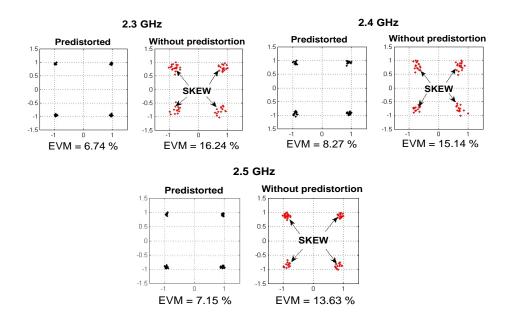

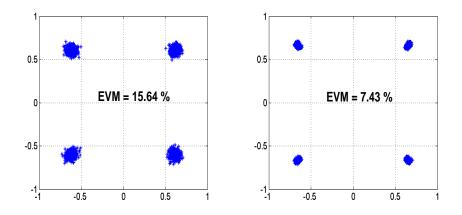

| Figure 51: EVM without and with compensation (multi-way) 102                   |

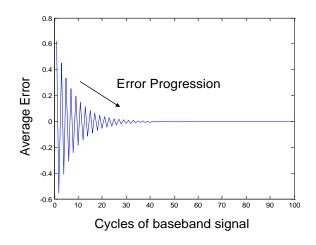

| Figure 52: Error progression for optimum compensation coefficients 104         |

| Figure 53: EVM variation due to proposed technique                             |

| Figure 54: EVM of the devices with and without compensation 105                  |

|----------------------------------------------------------------------------------|

| Figure 55: Conceptual diagram of the proposed methodology 106                    |

| Figure 56: On-chip digitally assisted DUT architecture                           |

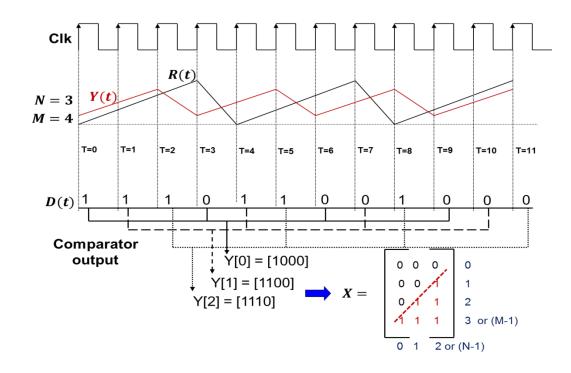

| Figure 57: HDP signature example                                                 |

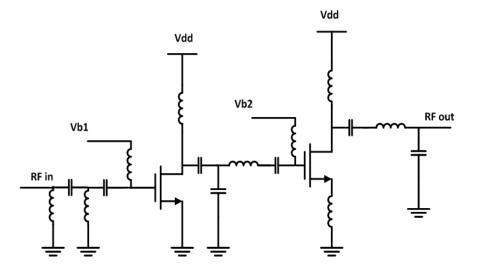

| Figure 58: Two-stage PA design with tunable elements                             |

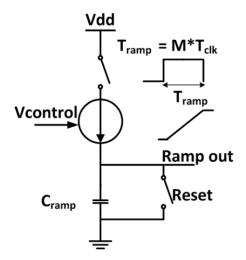

| Figure 59: On-chip ramp-signal generator [123] 116                               |

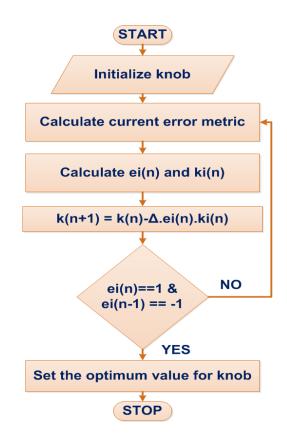

| Figure 60: Sign-Sign LMS-based algorithm for tuning process-skewed instances 118 |

| Figure 61: Test generation progression                                           |

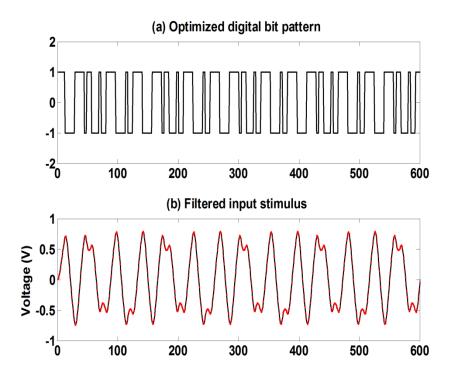

| Figure 62: Optimized digital bit pattern and input stimulus                      |

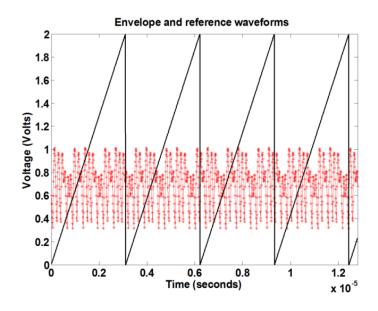

| Figure 63: Comparator input signals                                              |

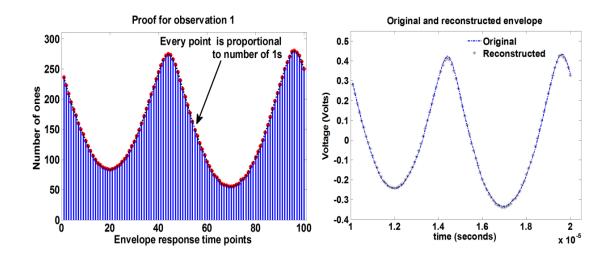

| Figure 64: Validation of Observation 1 124                                       |

| Figure 65: Cost function variation across tuning knobs and process instances 126 |

| Figure 66: Yield histograms 126                                                  |

| Figure 67: Hardware validation of the proposed concept                           |

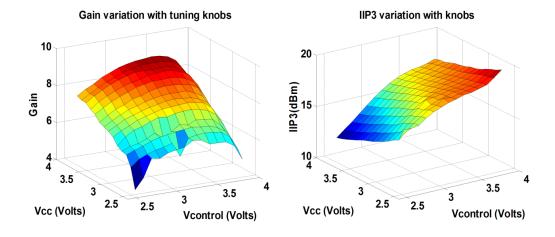

| Figure 68: Specification value variation with tuning knobs                       |

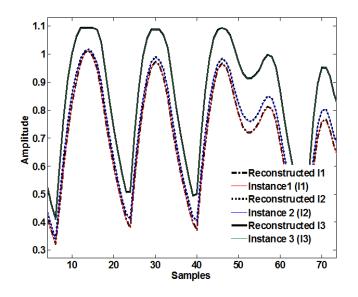

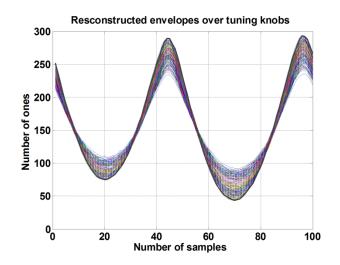

| Figure 69: Reconstructed and original envelope signals                           |

| Figure 70: Reconstructed envelopes across tuning knobs                           |

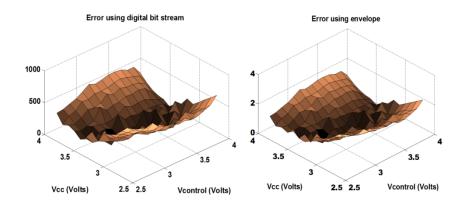

| Figure 71: Error from envelope and XOR output (proof of Observation 2)           |

| Figure 72: DSP-based tuning approach                            | 135 |

|-----------------------------------------------------------------|-----|

| Figure 73: Gradient search with adaptive step size              | 136 |

| Figure 74: Schematic of the wideband mixer used as a case study | 138 |

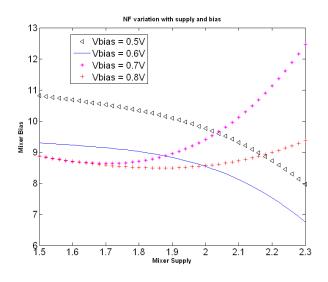

| Figure 75: NF vs. circuit knobs                                 | 138 |

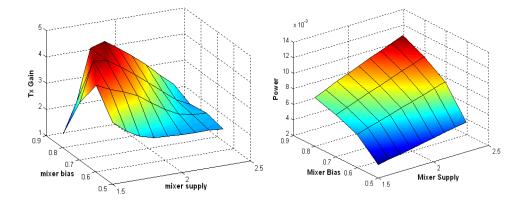

| Figure 76: Gain and power surfaces for a process instance       | 139 |

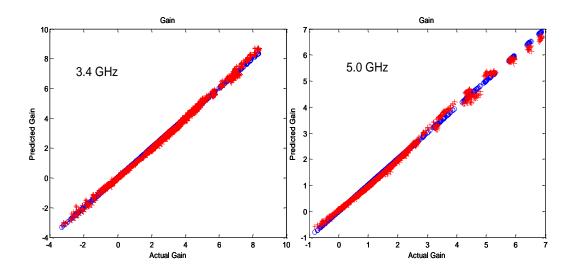

| Figure 77: Gain performance metric estimation.                  | 140 |

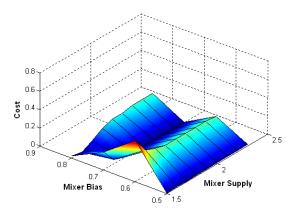

| Figure 78: Cost function surface for gain at 3.4 GHz with power | 143 |

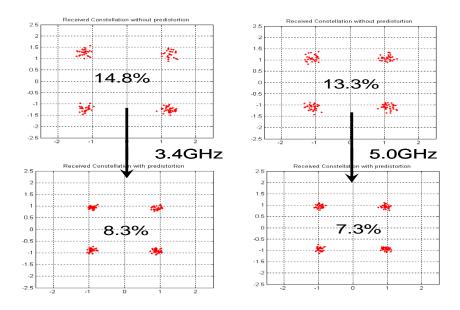

| Figure 79: EVM improvements at 3.4 GHz and 5.0 GHz              | 143 |

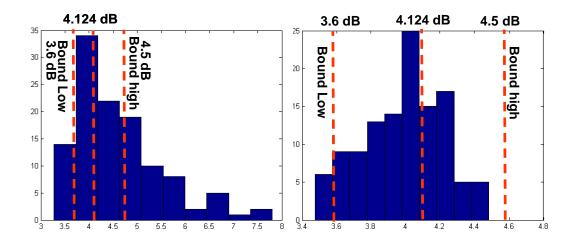

| Figure 80: Yield enhancement.                                   | 144 |

| Figure 81: Hardware setup of the proposed approach.             | 145 |

| Figure 82: 2 x 2 MIMO-OFDM system in spatial diversity mode     | 149 |

| Figure 83: EVM variation in nominal transmitter device.         | 149 |

| Figure 84: Test architecture and methodology                    | 151 |

| Figure 85: Proposed steps in the technique                      | 153 |

| Figure 86: Selection of test tones scheme                       | 154 |

| Figure 87: Flowchart describing test generation algorithm.      | 154 |

| Figure 88: Model of the MIMO-RF front end impairments.          | 156 |

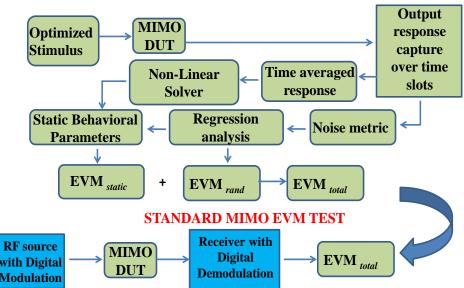

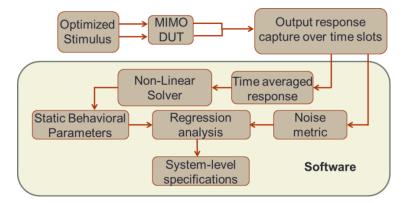

| Figure 89: Overview of the proposed EVM testing methodology     | 160 |

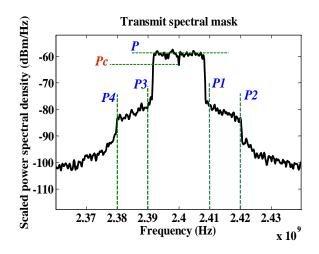

| Figure 90: Typical transmit spectral mask1                                    | 61 |

|-------------------------------------------------------------------------------|----|

| Figure 91: Overview of specification testing                                  | 61 |

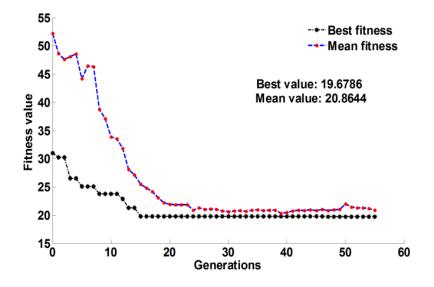

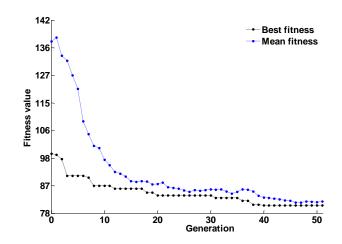

| Figure 92: Cost function progression over generations                         | 66 |

| Figure 93: Optimized input stimulus                                           | 67 |

| Figure 94: Envelope response of the combined signal                           | 67 |

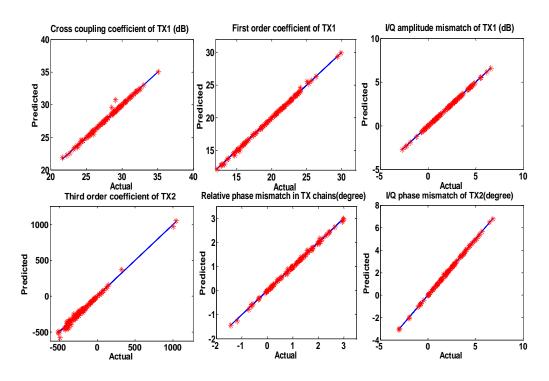

| Figure 95: Prediction plots of static parameters                              | 68 |

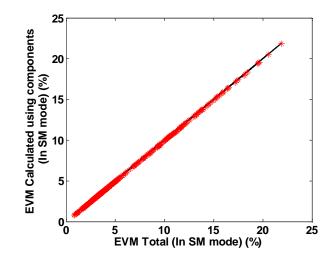

| Figure 96: EVM calculated using decomposition versus actual EVM 1             | 69 |

| Figure 97: EVM <sub>rand</sub> prediction plot                                | 69 |

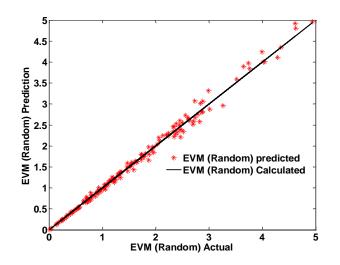

| Figure 98: Prediction plots of the EVM under different channel conditions 17  | 73 |

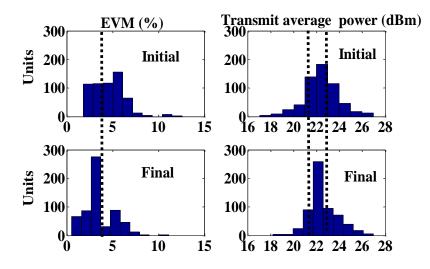

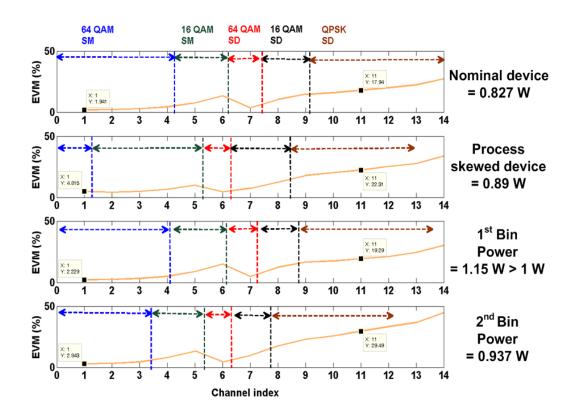

| Figure 99: Devices tuned for nominal specs (1 <sup>st</sup> iteration or bin) | 73 |

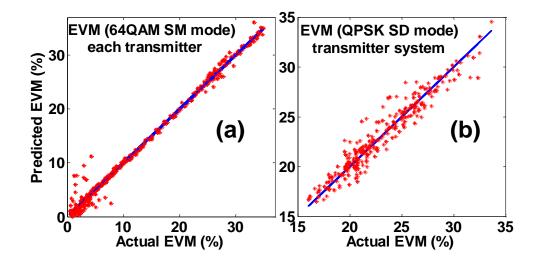

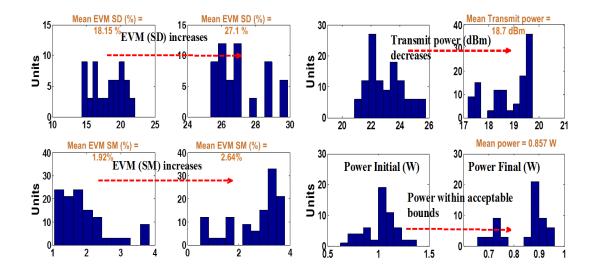

| Figure 100: Histogram plots of devices tuned for 2 <sup>nd</sup> tuning       | 74 |

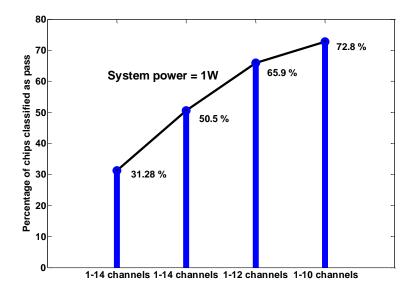

| Figure 101: System performance variation for devices in different bins        | 75 |

| Figure 102: Adaptive tuning results                                           | 76 |

| Figure 103: Hardware setup for MIMO RF transmitter                            | 77 |

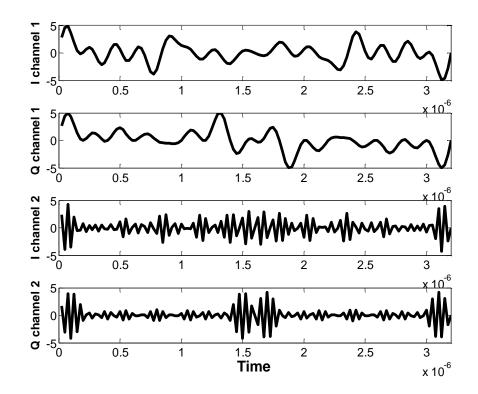

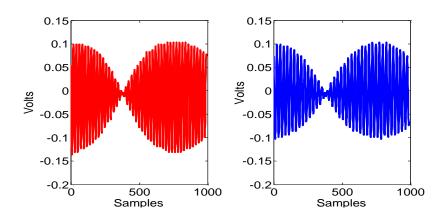

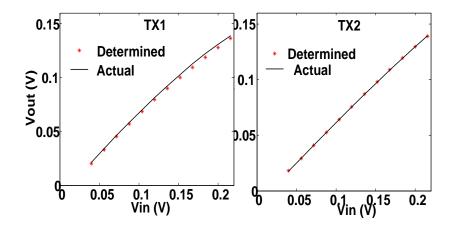

| Figure 104: Time domain output waveforms from each chain                      | 78 |

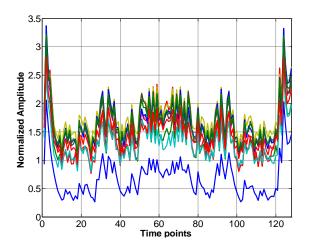

| Figure 105: Non-linearity characteristics of the transmitter chains           | 78 |

# LIST OF ABBREVIATIONS

| RF      | Radio Frequency                                       |

|---------|-------------------------------------------------------|

| SISO    | Single Input Single Output                            |

| MIMO    | Multiple Input Multiple Output                        |

| DUT     | Device Under Test                                     |

| CUT     | Circuit Under Test                                    |

| E-test  | Electrical-test                                       |

| MB-OFDM | Multi Band Orthogonal Frequency Division Multiplexing |

| DAC     | Digital to Analog Converter                           |

| ADC     | Analog to Digital Converter                           |

| UWB     | Ultra Wide Band                                       |

| EVM     | Error Vector Magnitude                                |

| BER     | Bit Error Rate                                        |

| CCDF    | Complementary Cumulative Distribution Function        |

| SM      | Spatial Multiplexing                                  |

| SD      | Spatial Diversity                                     |

| IFFT    | Inverse Fast Fourier Transform                        |

| PA      | Power Amplifier                                       |

| ITRS | International Technology Roadmap for Semiconductors |

|------|-----------------------------------------------------|

| DCT  | Discrete Cosine Transform                           |

| PDF  | Probability Distribution Function                   |

| RMS  | Root Mean Square                                    |

| VCO  | Voltage Controlled Oscillator                       |

| PLL  | Phase Locked Loop                                   |

| SOC  | System On Chip                                      |

| Tx   | Transmitter                                         |

| LUT  | Look Up Table                                       |

### **SUMMARY**

As the demands for cost efficient, low power wireless communication solutions increases, analog and radio frequency (RF) systems have been implemented in scaled nanometer nodes. At these nodes, multi-dimensional process variations affect the fidelity of these systems resulting in highly unstable yields, in-field wear-out, and signal-integrity problems. Besides random defects, high parametric variations in the fabrication phase have a significant impact on quality and yield of these systems. As technology nodes scale into the extreme nanometer regime, the "guarantee by design" approaches lead to highly pessimistic designs that require significant area and/or power. As a result, the process variations in these systems have mandated the need for increased efforts in post-manufacturing test and diagnosis phases of the devices.

As the trend for integration of complex SoCs continues, the lack of access to internal nodes and cost considerations has increased the testing focus towards system-level test techniques. Traditionally, the measurement of the system specifications requires the use of high cost instrumentation and long test times. These system-level test specifications need to be obtained in an intelligent manner to reduce the overall manufacturing costs of these devices. At the diagnosis-level, traditional process variation management involving the use of test/kerf structures to measure individual process parameter is insufficient in terms of diagnosis resolution and turnaround time.

Finally, it is necessary to develop fast and efficient techniques for performing postmanufacture tuning in the devices for improving the yield and reliability of these systems. Current state of the art techniques for yield improvement through post-manufacture tuning involves performing trimming or switching of various resistors and current sources to compensate for an individual specification. Further, these trimming techniques are, in general, performed sequentially leading to high tune or trim times in the production environment. To offset the parametric performance deviations in these analog/RF circuits and systems, intelligent post-manufacture compensation framework that can be used to tune concurrently multiple specifications of a system in a timeefficient manner is required. In addition, such techniques need to be able to compensate for process variation with optimal power performance to ensure reliable operation.

In this thesis, the above-mentioned bottlenecks in test, diagnosis, and self-tuning/selfhealing are addressed. A concurrent test and diagnosis methodology is developed to obtain the specifications of the DUT as well as the critical circuit process parameters measurements on a per-die basis using specialized diagnostic signatures. The die-level simultaneous test and diagnosis approach aids in identifying process variations and providing feedback for correcting it in a quick and efficient manner. An on-line performance monitoring methodology that uses real-time signal to obtain the performance degradation characteristics of the single input single output (SISO) RF system is investigated. A rapid low cost system-level test technique has been presented for advanced wireless systems such as the multiple input multiple output orthogonal frequency division modulation (MIMO-OFDM) RF systems.

A framework for performing low cost, signature driven post-manufacture tuning of RF systems is developed. Depending on the system computational resources and tuning knobs, different approaches have been detailed for SISO/MIMO-OFDM systems. Considering reliability and power budget limitations of the system, an adaptive power performance tuning approach has been developed that attempts to maximize the device performance considering the system power constraint.

The strategies developed in this work facilitate rapid diagnosis of process variations as well as tune for these variations leading to yield improvement. The solutions presented in this thesis have a significant impact in reducing the manufacturing cost and the time to market of these systems. The outline of the thesis is presented in Figure 1.

Figure 1: Dissertation outline and scope.

### CHAPTER 1. INTRODUCTION

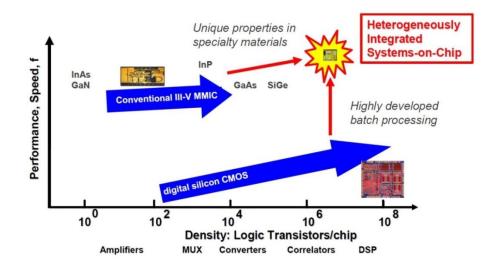

The increasing demands for higher data rates and low power wireless solutions have required the implementation of complex RF systems in nanometer nodes. Increased push towards system on chip (SoC) solutions has made the implementation of integrated wideband multi-standard wireless systems feasible. Commercially available state-of-theart radio products integrate conventional communication standards along with application specific wireless solutions such as FM radio (100 MHz), RFID (13 MHz), digital TV (800-1600 MHz), GPS (1.5 GHz), Bluetooth (2.4 MHz), 802.11 (2.4 and 5 GHz), WiMax (2.5-3.5 GHz) etc. [1]. The recently adopted IEEE 802.16e and IEEE802.11n standards implement multiple input multiple output (MIMO) front-end chains with multiple antennas in a quest for increased data rates. To reduce the cost of these systems, the integration of multiple chains on a single chip is essential. The ITRS roadmap for RF and mixed-signal technologies developed for wireless applications emphasizes on the integration of various systems and process technology nodes in a single platform as shown in Figure 2. A critical aspect for co-existence of these multi-standard systems is the high fidelity of each of these front-end modules. The high fidelity ensures that there exists minimal interference between the different chains.

However, the resulting circuits implemented in these scaled nodes have been increasingly susceptible to manufacturing process variations. Further, low-power design techniques have made the goal of obtaining high yields at these nanometer nodes a greater challenge. At nodes such as 60 nm and below, process variations in the manufacturing of silicon systems by integrating analog/RF with digital pose a significant challenge to designers [3]. These challenges include problems in signal integrity, verification, and process variations among other problems. As increased efforts are been made to implement more analog and digital IP on the same chip, the optimization of a

technology node for digital performance has led to significant yield challenges for analog components.

Figure 2: Future trends in wireless systems (Source: ITRS [2]).

Performance deviations (both inter-die and intra-die variations) due to parametric variations are of significant importance in wideband and multi-standard wireless devices over its narrowband counterparts. This challenge is due to the need to maintain the performance over a wider range of frequencies (broadband signals) as well as produce minimal interference. Further, as the number of components or chains in multi-standard wireless devices increase, the possibility of potential yield loss increase rapidly as well. Due to input-output pin constraints, it is highly unlikely that most of these systems have access to internal nodes. Hence, testing these complex SoCs consisting of complex circuitry that have limited access to internal nodes in production environment in an intelligent and low cost manner is critical for commercial success. The low yield returns in these systems further mandate the use of post-manufacturing calibration/tuning methodologies to improve performance metrics.

#### 1.1. Process Variation and Yield loss

As analog and RF systems are implemented in nanometer nodes, the yield of these systems is affected by multi-dimensional process variation. Increased variance in process parameters as the technology nodes scale has been reported extensively in prior literature. In [4], the authors show that due to process variations, the worst-case specification variations in a VCO module is close to 43 %. The authors provide a technique to account for these process variations in the design flow using optimization techniques. In [5], it has been reported that the intra-die variation in threshold voltage has doubled as technology scaled from 130 nm to 45 nm. The substantial effect of drain induced barrier lowering (DIBL) on threshold voltage of CMOS transistors at 65 nm node is shown in [6]. The increased process variations cause the corresponding specifications of the devices to vary beyond the acceptable limits thereby leading to lower yields. To compensate for increased process variations, new design approaches have been formulated. Design centering approaches [7] that try to compensate for the effect of process variations on a given design by using genetic algorithm-based yield optimization on neutral network process models has been investigated in the past. Another approach is designing circuits based on process corners. In this approach, the circuit is designed such that the circuit's specifications are within limits for extreme process parameter variations [8]. However, such a technique leads to over design of the circuit, usually at the cost of higher power consumption.

Current industrial practices for performing process variation simulation at circuit-level involve the use of Pelgrom models [9]. Pelgrom models have been used traditionally, to analyze the effect of mismatches and process variations in a group of transistors. While these are commonly used in the design product development kits (PDK), they are not accurate enough for chips of larger dimensions. Due to the increased process variations, leading to parametric as well as catastrophic variations in the DUT, there exists a need for development of low cost, time efficient techniques for test and diagnosis of analog/RF circuits. These manufacturing variations, along with other signal integrity impairments such as coupling (arising due to higher levels of integration and packaging), lead to degradation of the overall Quality of Service (QoS) metric in wireless systems. To improve yield in the presence of these high multi-dimensional process variations, it is essential to devise methods of performing post manufacturing tuning at different levels depending on the availability of test and tuning resources.

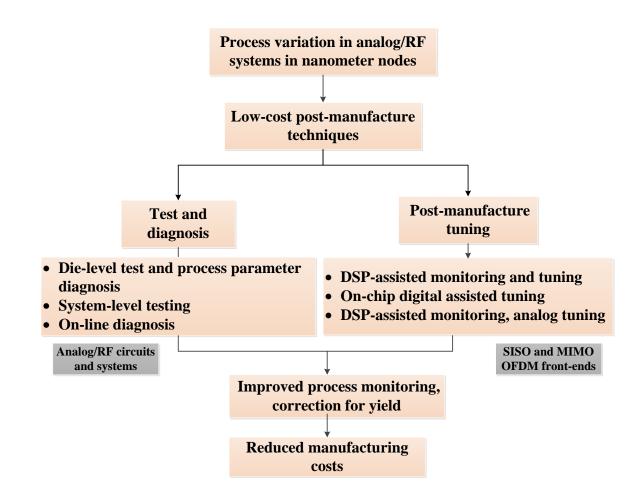

To summarize, as complex analog and RF systems are implemented in scaled nanometer nodes, for achieving low manufacturing costs and improved yields, the following aspects need to be addressed:

- Fast and low-cost techniques for testing and diagnosis of complex SoCs are required. These include techniques that are suitable for production and in field environment.

- Rapid post-manufacturing techniques need to be developed to increase the yield of the process-skewed instances in the production environment considering power and reliability.

#### 1.2. Conventional Specification Testing of Analog/RF Circuits and Systems

Conventional approach for production testing follows a sequential approach to test for each individual specification of the device. As modern analog/RF system DUTs consists of a slew of specifications in different modes, during the characterization phase of the product, bench test is performed to determine each specification along with its guard bands. During the production-testing phase, a set of critical specifications is identified based on various criteria as well as initial yield characteristics [10]. The DUT is then tested in a sequential manner for these critical specifications using certain test-ordering techniques to minimize the test cost of the DUT. Each test configuration involves a particular hardware setup, application of the test stimulus, settling time of the DUT response, response capture, and finally analysis. Further, tests of different nature such as DC and AC tests are applied to the DUT using different signal sources and relays are used to switch between the different paths on the load board. With increasing levels of integration, the production test cost of complex wireless systems can amount to as much as 45% of total manufacturing test cost [11]. For example, a wireless MIMO transceiver is characterized by hundreds of specifications in different set of modes as shown in [12]. Some of the critical specifications for these chips include gain, non-linearity or distortion parameters such as input referred third order intercept point (IIP3), I/Q amplitude and phase imbalances, noise figure, DC offsets, transmitter input impedances, transmitter non-linearities, and VCO phase noise.

#### 1.3. Alternative Methodologies for Testing of Analog/RF Circuits

To reduce the test cost and test time of standard specification-based testing approach, a number of techniques that involve concepts such as test ordering, compaction, test generation, designs for test have been developed. The authors in [13][14] provide a good overview of techniques for testing analog, mixed-signal and RF circuits. Defect-oriented testing is a technique that focuses on identifying faults in the system [15]. In this technique, fault models or dictionaries are developed through correlation of data. These fault models are used to avoid tests with high cost or test time. In quiescent current testing (Iddq), the current from various DUTs is monitored to provide information of fault coverage [16]. Structural testing of circuits is another low cost methodology for performing testing of analog/RF circuits [17]. In structural test, as opposed to functional test, the test emphasis is on the circuit implementation rather than the circuit specification. Oscillation-based test technique is discussed in [18]. In this technique, the oscillation frequency of the DUT under certain condition is measured to determine its functional specification. In VDD ramp test, the current signature over time is monitored

as the VDD of the DUT is stepped up, based on which the pass/fail decision is obtained [19]. Alternate test techniques or supervised learning techniques have been used in the past to replace specification tests [20][21][22][23]. In this technique, regression models are developed to predict multiple specifications of the device using the test measurements obtained from the DUT. The DUT is excited by an optimized stimulus such that its output response shows good correlation to specifications in the presence of process variations. Besides building regression models, another low cost test methodology for multiple specifications determination is the use of iterative model-solving techniques for mixed-signal/RF systems. In this methodology, the system is represented using a behavioral model whose parameters can be iteratively changed such that its characteristics match that of the DUT. In [24], random OFDM frames are used as test inputs, to compute a number of specifications by analysis of demodulated data. The use of optimized test stimulus for diagnosis of RF specifications using nonlinear model solving was demonstrated in [25]. In [26], the authors implemented different learning techniques to determine go/no-go tests for RF devices.

Another approach for low cost testing of wireless and wireline systems is the loopback testing. In this technique, the output of the wireless transmitter is fed back to the receiver, with or without frequency translation using an external mixer. The received signal is then processed in the tester or digital baseband (in built in test (BIT) methodology) to determine if the device is good or defective [27][28]. To perform loopback testing without external components, an internal programmable switch can be used between the transmitter output and receiver output. However, the isolation provided by the switch and the non-linearity effects of the switch are critical parameters that need to be taken into account.

BIT methodology is a low cost technique that is particularly useful for complex SOC where access to all the internal nodes might not be feasible. To perform BIT testing of

high frequency devices, various sensors such as the peak detectors, RMS detectors and envelope detectors have been used to obtain the low frequency or DC signal corresponding to high frequency outputs [29][30][31]. To implement BIT methodology, area overhead and signal integrity effects due to the sensor loading are some of the important aspects that need to be considered.

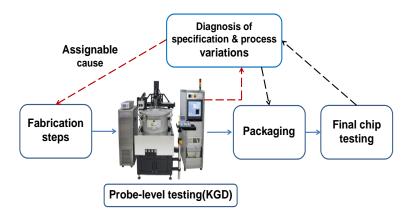

### 1.4. Diagnosis for Analog/RF Circuits and Systems

In the context of integrated circuit manufacturing, diagnosis is the process of determining the causes of variation/failure in the DUT caused by manufacturing variations. As technology nodes continue to scale, die-to-die and wafer-to-wafer has variations have become significant resulting in inconsistent device yield. Ideally, the circuit should be designed to ensure that the specifications of the device, under process variations, lie within the acceptable region of the device. The acceptable region of a device is a complex multi-dimensional hyper surface that defines a region where all the specifications are within its lower and upper bounds. However, as process technology scales, ensuring compliance with acceptable region limits consistently is a challenge. This challenge is due to the high variability and time-varying effects of process parameters and their interaction effects occurring in production environment. As a result, continuous monitoring of process deviations and correction of these deviations are required for shorter time to market and yield sustainability of the device. This process of monitoring, determine the cause of a parametric shift or failure and providing feedback is referred to as diagnosis in this thesis. As process shifts are tracked, the variation in these shifts is fed back to the fab, to prevent any yield loss.

The causes of failure/variation can be attributed at various levels of manufacturing. These include manufacturing variations such as etch variation, photo resist variations, chemical composition variations, photolithographic variations. These variations are reflected in variations in the Spice-level process parameters such as Tox, Vth0, Lln, mismatches in capacitances, transconductance of transistors, and other layout parameters etc.

Depending on the nature of the variations, there exist two different types of yields namely functional and parametric yield. Functional yield of a device characterizes the defects occurring due to the random nature of process variations. Parametric yield characterizes the failure of devices due to systematic shifts in process parameter values that cause the system specifications to spread beyond acceptable limits. In deep nanometer nodes, parametric variations and the associated yield problems are more prevalent and challenging as opposed to functional yield problems, which can be pruned out with minimal testing efforts at early stages of manufacturing testing. Diagnosis efforts in this work focus solely on developing an efficient methodology for identifying parametric variations with high resolution without adding significant overhead to existing manufacturing cycle, and providing feedback at the earliest to correct for these process deviations.

Current state-of-art diagnosis efforts rely on electrical test (e-test) measurements and their correlation to parametric variations in specifications. Using the above information, parametric yield loss is characterized and yield management is performed. On each wafer, the e-test parameters are measured at a limited number of test sites. To account for any deterministic e-test parameter variation that would result in yield loss, a significant amount of data needs to be collected for a long timeframe. Faster feedback can be achieved by increasing the number of test structures per wafer. However, the drawback of such a technique would be longer test time and increased silicon area.

In the past, parametric test measurements [32] for zero-yield wafers were used to predict process parameters. Data-mining [33] techniques have been used for diagnosis of process integration errors. In [34], process variation testing using sensing circuitry and frequency domain analysis, to obtain information pertaining to specific regions of a wafer, is proposed. In [35], the authors use Bayesian theory aided by the construction of fault dictionaries to detect large parametric variations. To increase diagnostic resolution they perform online computations as well. Defect filtering and regression modeling were used to diagnose faults in a LNA circuit in [36]. Certain parameters of the circuits such as R, L, and C are obtained by analyzing the polynomial coefficients of the behavioral models of the analog circuit in [37]. A methodology for diagnosing critical process and circuit parameter values from diagnostic performance measurements (generated from specific measurements at critical nodes of the circuits) using reverse solution of forward regression models (mapping process/circuit parameters to the test measurements) was developed in [38]. In [39], the nearest neighbor residual (NNR) technique is implemented on Iddq tests to help identify outliers.

In digital chips such as microprocessors, a common trend in the recent years is to implement ring oscillators, delay lines for speed measurements, and memory matrices to identify certain MOSFET process parameters such as transistor threshold voltages, channel length, gate capacitance, drain to source resistance etc. [40][41]. These on-die measurements can be used to compensate for local process variations using adaptive bias of substrate etc. However, such techniques are not common for analog chips because of the high area overhead involved in implementing the on-die parametric measurements.

A technique for performing concurrent testing and diagnosis of analog/RF circuits in production environment on a per chip basis is developed in this work. This allows both, the specifications and critical spice-level device parameters, of the analog/RF circuits to be predicted accurately from the DUT response with lower test-time and test-hardware cost compared to standard testing techniques and allows for rapid yield debug and process correction.

#### 1.5. System-Level Specification Testing

Recent years have witnessed a surge for high data rate portable wireless communication devices while low power wireless front-ends have become ubiquitous in day-to-day life. Currently, complete system-on-chip (SoC) implementations of WLAN modules are available in the wireless market. To meet the demand for higher data rates, MIMO systems have rapidly emerged as leading technology. Within a relatively short time, MIMO has been adopted into modern communication standards such as WLAN, WiMax and LTE. To maintain healthy profit margin, with higher levels of integration, it is necessary to develop efficient system-level testing solutions, thereby eliminating the test time and test cost associated with performing individual specification tests for each RF sub-module. While circuit-level specifications characterize the analog/RF modules of the individual circuit, system-level specifications such as error vector magnitude (EVM), bit error rate (BER), transmit spectral mask, receiver sensitivity, complementary cumulative distribution (CCDF), and transmit center frequency leakage can be used to quantify the end-to-end imperfections that exist in the wireless systems. These quantify the effect of all the imperfections that are present in analog/RF front end and the mixed signal circuits (such as ADC and DAC clock jitter, offsets, distortion, quantization noise etc.) as well as the interaction efforts that exist between these impairments.

Testing advanced RF modules, especially for system-level metrics such as EVM, BER, and CCDF etc. is challenging due to the capital and computational costs involved, thereby limiting parallel multi-site testing architectures. In the past, specialized patterns of test stimuli have been used to develop regression-based prediction of system specifications of single input single output (SISO) transceiver in [42]. This technique requires an explicit training phase on hardware measurements and hence uses standard testing procedures for calibration.

A number of techniques have been developed for determining the system-level EVM of SISO systems. An order of EVM computation test time is saved using technique discussed in [43] by sharing data while testing different modulators. A built-in test approach that uses the baseband processor for EVM computation is discussed in [44]. In [45], the authors develop methods for enhancing EVM test using refined EVM computation in conjunction with measurement of path input-output impedances. In [46], the authors discuss a technique for performing EVM testing by rotation of constellation points in a WLAN OFDM SISO system. In [47], the authors propose the decomposition of transceiver performance into static and dynamic non-idealities for calculating the EVM metric of RF SISO systems using regression functions. In [48], the authors propose design of simple digital design for test (DFT) circuits in the baseband of the RF transmitter to determine the overall transceiver EVM. It was shown that EVM could be determined from knowledge of RF system non-linearities and the noise spectrum by expressing EVM as an analytical function of these parameters [49]. All the above techniques have been proposed to determine system-level EVM specification for SISO systems. In [50], the authors provide a low cost methodology for performing BER testing of pulsed transceivers. In [52], a technique is developed for reducing the test time to determine the EVM and CCDF specifications for MB-OFDM UWB systems. The technique uses specialized digital streams obtained through test generation for exciting the DUT rather than the conventional pseudo-random digital inputs used to test the above specifications. These digital streams excite the imperfections of the system in an optimal manner as compared to the standard digital streams thereby reducing the time taken to determine these specifications.

In the case of advanced wireless transmitter modules such as MIMO RF SOCs, the authors in [53] present a low cost technique of measuring MIMO specifications using a combination of signal sources and switches that define a set of RF measurements. The

Gain, IIP3 and the phase offset of various RF chains are measured. Multiple RF chains are tested concurrently by applying tones at specific frequencies to different RF chains in such a way that the fidelity of each chain can be determined by observing spectral content across non-overlapping frequency bands of the observed response. However, the authors determine specifications such as cross coupling by testing the RF chains sequentially. The scalability of the methodology with RF chains is not possible without switching matrices and multiple sources. Further, the authors do not tie the lower-level specifications to higher system-level test parameters like EVM, transmit spectral mask. While commercial systems are available for performing system-level testing of different MIMO system specifications [54], these incur high cost in terms of the test equipment and test time.

In this work, a methodology for performing parallel system-level testing of MIMO-OFDM RF transmitter modules using optimized bandwidth-partitioned stimulus applied from the embedded DSP module of the RF system and a simple combination of sensors on the load board. A comprehensive set of behavioral specifications of multiple RF modules chains are computed simultaneously from the observed DUT response using a single data acquisition and are used to compute the system-level specifications. As multiple chains of the MIMO front-end system are tested concurrently, the presented technique enables lower test cost and test time.

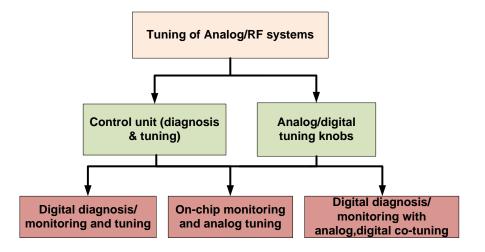

#### 1.6. Prior Work in Tuning of Analog/RF Circuits

As analog/RF circuits approach the nanometer regime, process variations assume great significance in the overall yield. The emphasis on design for manufacturability (DFM) and design for yield (DFY) in the case of analog/RF circuits as technology is scaled is highlighted in [55]. The two essential components of yield improvement through post-manufacturing tuning or calibration are as follows:

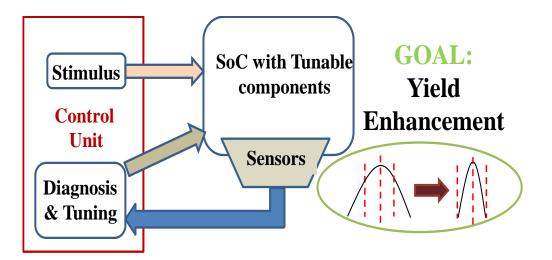

- Existence of a control unit that runs algorithms to estimate or monitor the imperfections in the DUT due to process variations. This can be the system DSP or the tester in production environment.

- Analog or digital tuning "knobs" for correcting the imperfections at various points of the system. Compensation of the non-idealities of a RF system can be performed both in the DSP domain using digital linearization techniques such as pre-distortion (digital knob) and in the analog domain using techniques such as feedback, tuning of varactors, inductors, bias current.

The tuning and control strategy that is adopted depends on numerous factors such as area, power, and complexity of the chip. Based on the above two factors, various tuning techniques that have been proposed in prior literature can be broadly classified as one of the following categories:

- Digital baseband (also known as the digital signal processor (DSP)) monitoring and tuning

- On-chip monitoring and analog tuning

- Digital baseband monitoring and analog and digital co-tuning

The overview of the tuning techniques is shown in Figure 3.

## 1.6.1. Digital Baseband or DSP-Based Monitoring and Tuning

This methodology involves estimating the imperfections in the front ends using measurements obtained from sensors/auxiliary components present in the front ends and correcting the imperfections in the baseband. The baseband is either before the transmitter front end or after the receiver front end. The imperfections that are corrected include DC-offsets, I/Q mismatches, and non-linearities. The advantage of using digital baseband for monitoring and correction is the high level of controllability in terms of resolution and precision that can be obtained. Unlike analog tuning knobs, no special hooks need to be incorporated into the front-end circuits for post-manufacture tuning.

Further, these techniques can be characterized as direct learning or non-adaptive and indirect learning or adaptive methods based on the implementation technique. In adaptive compensation, continuous online monitoring and calibration of the system is performed by using techniques like least squares (LS), least mean squares (LMS) or recursive least squares (RLS). In [56], a digital compensation technique is described for correction of I/Q impairments up to 10% amplitude mismatch and  $10^{\circ}$  of phase mismatch. Adaptive techniques for I/Q mismatch compensation, DC-offset cancellation is described in [57] [58]. Non-iterative techniques based on one-time characterization for quadrature compensation is presented in [59]. For non-linearity correction, digital predistortion is a widely used linearization technique. The popularity of the above technique can be attributed to its flexible adaptive nature as well as the extent of implementation accuracy at lower cost. Baseband predistortion creates inverse characteristics of the transfer function of the RF power amplifier, thereby increasing the effective 1dB compression point of the power amplifier. Adaptive predistortion uses methods such as the recursive least squares (RLS) [60] [61] algorithm to tune the predistorter coefficients during field operation. Standard techniques used for adaptive predistortion perform tuning of the predistortion coefficients using the receiver down conversion chain [60]. The power

amplifier output is downconverted, demodulated and fed back through the internal receiver chain. The signal is then processed digitally to improve the overall end-to-end linearity. The digital correction and tuning technique, however, is affected by receiver LNA and down conversion mixer non-linearities, I/Q demodulator mismatches, and ADC non-linearities arising in the down conversion procedure. Further, the drawback of such an adaptive compensation technique is the time the system takes to converge to its optimum performance. In non-adaptive compensation, a one-time calibration of the system is done during production test and the results are stored in a look up table (LUT) and used in real time operation [59]. The drawback of this methodology is that it does not take care of ageing related performance drifts. Digital compensation techniques cannot correct large impairments due to the limitations in the dynamic range of the data-converters in the system, amplification of DC-offset or saturation of front-end analog modules. However, these techniques are sufficient for correction of amplitude and phase impairments arising due to I/Q mismatches and DC-offset errors.

# 1.6.2. On-Chip Monitoring and Analog Tuning

In this methodology, the impairments are estimated by circuitry on the chip and are from the estimated performance criteria the device circuit parameters are tuned. These techniques can be analog or digital in nature. In analog tuning or compensation, the calibration/tuning is performed in the analog domain by changing the circuit parameters such as bias, supply voltage, passive components such as capacitors, inductors, and resistors. Generally, this methodology involves some form of circuit-level feedback. A completely analog scheme for tuning I/Q mismatches and the resulting image rejection ratio (IRR) performance in a two-stage down conversion receiver is presented in [62]. In this technique, an auxiliary chain performs a two-stage down conversion by either using In-phase or Quadrature phase LO at any point of time. The final output of the main transceiver is mixed with the output from the auxiliary chain to obtain the mismatch

values in the DC component after low pass filtering. More than 15 dB of IRR performance improvement is achieved using this technique. Analog pre-distortion for non-linearity improvement is performed using matching network design with independent amplitude and phase control [63]. A self-calibration scheme for tuning the impedance mismatches of a LNA by using a variable inductor with taps is presented in [64]. The technique involves real-time current sensing whose magnitude varies with the input match of the LNA, which is then amplified and peak detected to obtain a dc signal corresponding to the input match. To determine the frequency offset in matching, two tones of different frequencies are applied one after the other and the difference in the corresponding DC voltage is used to calibrate the shift in  $S_{11}$  of the circuit. In this technique, the inductor has taps with switches connecting to these taps. The parasitics of the switches as well as those of the interconnects need to be characterized. The advantage of using on-chip monitoring and tuning is the fact that short calibration time (in the order of microseconds) is achieved as opposed to digital baseband calibration schemes (generally in the order of milliseconds). The bandwidth of the analog feedback system generally decides the convergence in this methodology. In the digital monitoring design paradigm, on-chip digital logic is used to monitor and aid the compensation of mixedsignal/RF performance due to process variations. By implementing such a technique, the design focus is shifted from the analog circuitry to the digital circuitry. There has been significant work in the area of digitally assisted tuning of analog circuits including PLLs, frequency synthesizers, and ADCs. In the past, there has been numerous digital techniques for calibration of PLL, which is predominantly a digital block [65][66][67]. A LMS based technique for calibration of pipelined ADC is presented in [68].

In this methodology, there is no requirement for interaction with the system baseband leading to possibly lesser number of pin counts. This technique reduces the load on the system baseband processor. However, as opposed to analog circuit, voltage or current sampling for feedback is difficult to achieve in RF circuits without actually affecting the output response. Depending on the type of feedback circuitry, the PVT variations in the feedback circuitry itself can affect the calibration performance.

However, the above research examples focus primarily on testing and tuning of specific analog/RF/ADC specifications. There is no generic scalable methodology that can concurrently tune multiple design specifications using on-chip circuitry. In this work, a self-contained on-chip digital-logic-based tuning methodology is developed.

## 1.6.3. Digital Baseband Monitoring, with Analog and Digital Co-tuning

In this methodology, the monitoring and control unit is the DSP of the transceiver system and numerous knobs in the baseband as well as analog front end have been incorporated in the system to tune for front-end imperfections. Such a methodology has gained significant attention in the past decade. The bias voltages of various front-end circuits are controlled using DACs that can be configured in post manufacturing phase for tuning. In [69], the authors use current DACs to compensate for the LO feed through (LOFT). The output of the transmitter is envelope detected and the frequency spectrum of the output calculated in the DSP is used for impairment correction. In [70], the authors develop an adaptive technique to compensate for I/Q mismatches observed in typical RF front ends, by making use of a variable delay gain cell to feedback correction vectors to the system LO. In [71], a dual mode 802.11b/Bluetooth radio along with tunable bias for LNA, Mixer and LOFT cancellation. In [72], the authors propose a scheme for compensating static and time varying dc offset as well as TX LO leakage using the baseband processor. There exist a number of internal calibration paths, which are controlled through switches, for calibrating the front-end components during test mode. In [73], a technique for tuning of RF front-end modules by running a gradient algorithm that attempts vary the output response of the transmitter to the reference output is presented.

To develop a monitoring scheme that is generic for performing multi-dimensional tuning, it is necessary to observe the variation in specifications simultaneously. Alternate test methodology or supervised learning methodology is well suited for this purpose [20][21][22][23]. The authors in [74] develop a one-time tuning technique in which the values of the analog tuning knobs of a LNA are directly predicted using supervised learning techniques. The methodology leads to lesser calibration time. However, it is limited by the accuracy of the regression models and does not guarantee power optimality. In [75], the circuit is reconfigured to oscillate in test mode and the oscillation signature in conjunction with regression models are used to tune the amplifier for yield improvement. A critical aspect of the analog tuning is the availability of hooks in the front-end circuits. Various papers have been published in the past that discuss the various tunable circuits. In [72], current steering DACs are used for dc-offset cancellation. Conversion gain of each I and Q path and IIP2 correction technique in mixers have been proposed in [76]. The conversion gain can be used for tuning of I/Q amplitude mismatch. In [77], an orthogonal tunable LNA in which the gain and the non-linearity characteristics of the device can be controlled independently without affecting each other is presented. A technique for controlling the input match, gain, and resonant operating frequency of LNA is presented in [78]. Baseband analog filter tuning can be achieved using RC reconfigurable filters [79]. This scheme is relatively easily to implement as the signal is in the low-frequency domain where the parasitics have less impact. A self-healing 60 GHz PA amplifier implemented in 65 nm technology nodes that can self-tune its gain and 1dB compression point is presented in [80]. Three control knobs operating at different power-levels are used for tuning.

With respect to the above tuning techniques, multiple specifications are tuned sequentially one after the other leading to considerable tune times. Further, in each step of the tuning, standard specification testing is performed. In this work, a framework for performing rapid low cost iterative tuning of multiple RF systems in a power conscious manner using the system DSP is presented. Finally, none of the prior techniques investigates the effect of the power increase due to self-tuning. In this work, an adaptive tuning methodology is developed that attempts to optimally trade-off performance metrics against power, i.e. a methodology that maximizes performance of the device for a given power constraint is developed.

# CHAPTER 2. PRINCIPLES OF SUPERVISED LEARNING AND MODEL-SOLVING-BASED TEST TECHNIQUES

# 2.1. Supervised Learning or Alternate Testing Technique

As explained in chapter 1, conventional test strategies for mixed-signal, analog and RF circuits are based upon specification-based testing techniques where the DUT specifications are measured using one or more input signals with possibly different test setups for each specification. These specifications are compared against pre-defined specification bounds to make device pass/fail decisions. This requirement of multiple test stimulus and different test set-up for each specification results in increased costs in terms of test time and test infrastructure. Alternate testing or supervised learning methodology involves the use of a single test configuration and predicts multiple specifications of interest with a single highly optimized input stimulus, thereby, reducing the overall test time and test cost. The fundamentals of alternate test or supervised learning framework are briefly described in this chapter.

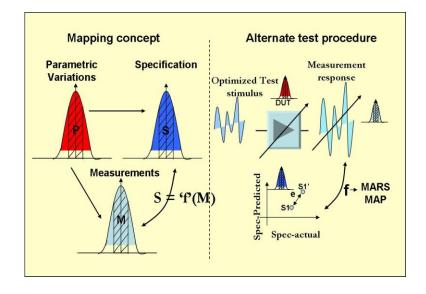

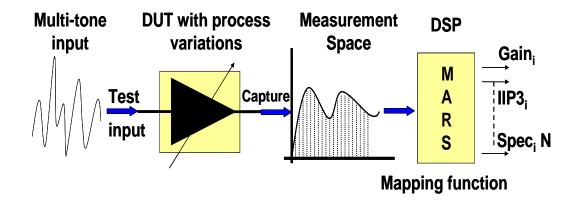

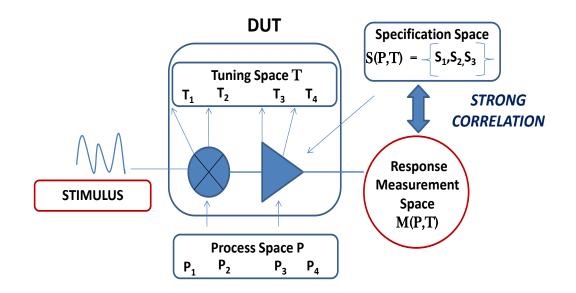

Consider variations in the process parameter space P as shown in Figure 4 that affect the specifications of the DUT. For low cost diagnosis, an alternate set of measurements is determined such that the test measurements under process variations are strongly correlated with variations in the test specification values of the DUT. This set of measurements defines the measurement space M. Any deviation in the observed measurements from the expected implies a corresponding deviation of the measured RF specifications of the DUT from the expected in the specification space S, due to perturbations in the process space P. Hence, if an optimized stimulus is used such that the corresponding output response of the DUT varies due to process variations resulting in specification variations, then a model can be developed relating the specification (S) and measurement (M) domains. This model can be stated as follows:

There exist a number of different techniques for developing the regression mapping function f relating the test measurements and the specifications. In alternate test technique, a nonlinear regression model is developed using the technique called Multivariate Adaptive Regression Splines (MARS) [81]. The devices are excited by an optimized stimulus and the regression model is developed using measurements obtained on a "training set" of devices and the corresponding specifications. In the production environment, this model is then used to predict the RF test specifications S of the DUT from the observed alternate test measurements M as shown in Figure 4. The MARS algorithm selects a set of basis functions (linear or higher order) using the input variables. It also selects the coefficients for the basis functions to develop the regression function. Based on the input data variations, the MARS algorithm uses the concept of recursive partitioning to develop the model. The MARS algorithm consists of two steps that are referred to as the forward step and the backward step. In the forward step, basis functions are added to the model. In the backward step, the basis functions that contribute minimally to the least square fit of the model are removed. The backward step is evaluated using the generalized cross-validation error (GCVE) criterion. The criterion balances between over-fitting of the data and the residual error. The failure coverage of the alternate testing technique depends on the choice of the input test stimulus.

Learning or training: The optimized test stimulus is applied to each of these DUTs and their resulting responses are sampled and stored. Simultaneously, the output specifications of these devices are measured using the conventional specification-based test set-ups. The sampled transient measurements are mapped onto the specifications of the device using non-linear regression functions. During production test, this non-linear regression function is used to predict the specifications of a DUT from its response to the same optimized test stimulus. The production test implementation of alternate test or supervised learning technique is shown in Figure 5. The requirement of standard test setup during the training phase is a disadvantage of the supervised learning technique.

Figure 4: Alternate test or supervised learning technique.

Figure 5: Implementation of supervised learning in production floor.

## 2.2. Model-Solving-Based Testing/Monitoring

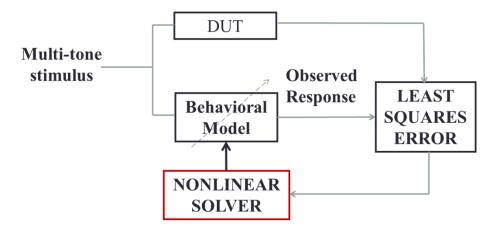

Model-solving-based testing/monitoring, as the name suggests uses a parametric behavioral model of the system for testing purposes. In this technique, an optimized stimulus, obtained through pre-computed test generation scheme is used to excite the DUT as well as a behavioral model of the DUT simultaneously [24][25]. The output from both is compared by computing the least square error between their responses, which is

used to guide a non-linear solver in updating the behavioral model of the DUT. When the error in response is minimized, from the computed behavioral parameters, the system specifications can be computed using correlation techniques or through simulating the behavioral parameters in the software domain to compute the DUT specifications. Many different non-linear optimization techniques can be used for obtaining the behavioral parameters of the system. In this work, we use the trust-region-reflective algorithm for determining the behavioral parameters [82]. The bounds on the values of the behavioral model parameters of the DUT need to be determined during the characterization phase devices. Alternatively, the model can be solved directly without using any iterative techniques. The choice of the technique depends on the availability of computational resources, model complexity, and accuracy required in determining the model parameters.

In this technique, it is assumed that the behavioral model closely matches the behavior of the device. The concern with this technique is that behavioral parameters must accommodate uncertainties in measurement, which can be alleviated using a carefully calibrated and accurate measurement setup. The overview of the technique is shown in Figure 6. The advantage of this technique is that it avoids the need for a training phase and cost associated with it.

Figure 6: Model-solving-based testing.

## 2.3. Test Optimization

The test optimization procedure is a one-time offline optimization that needs to be performed to ensure that the input test stimulus is carefully optimized to result in an output response that is highly correlated with the specification values of interest. This forms the basis of supervised learning technique as well as model-solving-based test technique. This step can be either performed in simulation environment on the DUT circuit or on the initial set of characterization devices (provided there is a considerable process variation distribution among these devices). The optimization of the test stimulus depends on the type of DUT being tested and the performance parameters being evaluated. For a given DUT, there are several test generation algorithms available for optimizing the input test stimulus. An initial population of the DUT is selected such that it covers the entire process space with reasonable accuracy and the optimization is performed on this set. In the simulation environment, more than the expected process variations (which is in general  $\pm 3\sigma$  where  $\sigma$  is the standard deviation of process parameter) are used to ensure that the process space of the DUT is well represented. The effectiveness of each test stimulus at each stage of test generation is evaluated by using the captured test response from all the devices and using the test technique (either supervised learning technique or model solving based technique) to compute their specifications. The prediction error in the specifications is used to drive the optimization. In this thesis, various versions of genetic optimization algorithm are used to determine the optimized stimulus to excite the DUT.

# CHAPTER 3. TEST AND DIAGNOSIS OF RF CIRCUITS AND SYSTEMS

With increasingly shorter product cycles, yield entitlement is a critical parameter for commercial success of semiconductor devices. In the case of analog and RF circuits implemented in advanced nanometer nodes, attaining high yields is a challenge. Higher levels of circuit integration and implementation of circuits in scaled nanometer nodes has made the DUT test and diagnosis steps a crucial step in the manufacturing cycle.

In scaled technology nodes, to maintain good yield, it is necessary to monitor process variations continuously. Process variation management involves continuous process monitoring and feedback to offset process deviations due to environmental and thermal effects thereby improving chip yield. Current industry practice has two lines of defense that prevent misclassification of devices and thereby affect the yield of a device. These lines of defense are the fab parameter limits and test specification limits. The overall yield of a given device is determined by these limits.

At the fabrication level, a number of statistical control methods are used to monitor individual e-test parameters. The values of the e-test parameters are used to decide whether a wafer is good or defective. In general, a fab monitors a large gamut of e-test parameters based on the process technology used. These parameters are monitored through control charts where each e-test parameter is expected to be within an upper control limit (UCL) and a lower control limit (LCL). Current industry practice to determine yield/specification compliance of analog/RF devices at the test floor involves testing the DUT through standard specification testing techniques. To determine if the device has passed or defective, various specifications of a device are checked against their respective specification limits. In general, analog/RF circuits are characterized through a multitude of specifications. For each individual specification, the standard testing technique involves a distinct test setup and utilizes expensive instrumentation that increases test time and test cost. Further, these testing techniques do not provide any insight into process parameter variations. While the above-mentioned test and fab checkpoints exist, each of these checkpoints operates independently.

## 3.1. Concurrent Test and Diagnosis of Analog/RF Circuits