## A COMPUTER ARCHITECTURE FOR

## DISCRETE MANUFACTURING

## A THESIS

## Presented to

The Faculty of the Division of Graduate

Studies and Research

Βу

Robert Baugh Sledge, Jr.

In Partial Fulfillment

of the Requirements for the Degree Master of Science in Electrical Engineering

Georgia Institute of Technology

August, 1974

# A COMPUTER ARCHITECTURE FOR

# DISCRETE MANUFACTURING

## ACKNOWLEDGMENTS

I wish to take this opportunity to thank my advisor, Dr. Cecil O. Alford, for his help in identifying the problem and for his aid and advice during the research. Thanks are due also to Dr. E. B. Wagstaff for his numerous critical suggestions which resulted in improving the final copy.

I would also like to recognize the help of my lord Jesus Christ, without whose help this thesis would not have been completed within the allocated time constraints.

# TABLE OF CONTENTS

•

|          | Page                                                                   | 2 |

|----------|------------------------------------------------------------------------|---|

| ACKNOWLI | EDGMENTS                                                               | 1 |

| LIST OF  | TABLES                                                                 | v |

| LIST OF  | ILLUSTRATIONS                                                          | i |

| SUMMARY  | vii                                                                    | i |

| Chapter  |                                                                        |   |

| I.       | INTRODUCTION AND PAST APPROACHES                                       | 1 |

|          | Introduction                                                           |   |

| II.      | IDENTIFICATION OF SYSTEM REQUIREMENTS                                  | 7 |

|          | Microprocessor System Requirements                                     |   |

| III.     | PROFOSED SYSTEM ARCHITECTURE                                           | L |

|          | Level (1) System Architecture<br>Level (1) Microprocessor Architecture |   |

| rv.      | COMPARISON AND EVALUATION OF PERFORMANCE                               | 2 |

|          | Performance Evaluation<br>Conclusions                                  |   |

| APPENDIC | TES                                                                    |   |

| A.       | INPUT MODULE CIRCUITRY                                                 | 1 |

| В.       | INTERRUPT MODULE                                                       | 4 |

| c.       | OUTPUT MODULE CIRCUITRY                                                | 7 |

| D.       | MEMORY MODULE                                                          | 9 |

| E.       | BASIC INSTRUCTION SET FOR THE GT 1248 10                               | 5 |

| F.       | INTEL 8080 PROCESS CONTROL ROUTINES                                    | 4 |

| G.       | ROBOT CONTROL PROGRAMS                                                 | 0 |

iii

|              | Page |  |

|--------------|------|--|

| BIBLIOGRAPHY | 146  |  |

.

.

# LIST OF TABLES

.

| Tabl | e                                                           | Page       |

|------|-------------------------------------------------------------|------------|

| 1.   | Computer Usage in Manufacturing Operations                  | 8          |

| 2.   | Computer Functional Requirements                            | 12         |

| 3.   | Characteristics of the Level (1) System                     | 30         |

| 4.   | Comparison of Microprocessor Capabilities                   | 47         |

| 5.   | Flag Flip Flop Functions                                    | 51         |

| 6.   | ALU Operation Set                                           | 53         |

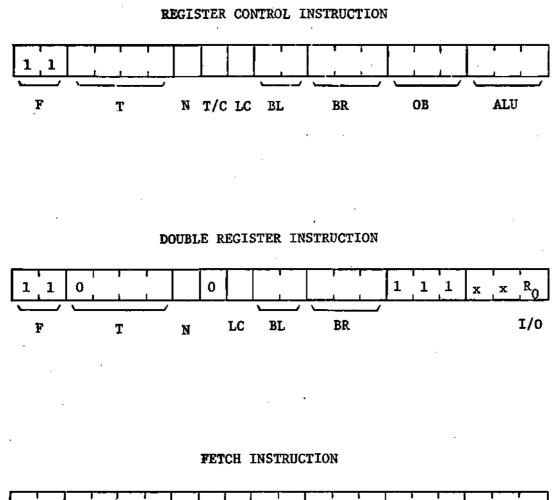

| 7.   | Field Specifications for the Register Control Instruction . | 60         |

| 8.   | Double Register Field Specifications                        | 61         |

| 9.   | Fetch Instruction Functions                                 | 62         |

| 10.  | Jump Instruction Functions                                  | <u>6</u> 6 |

| 11.  | Pulse Instruction Functions                                 | 69         |

| 12.  | Characteristics of the GT 1248 Instruction Set              | 73         |

| 13.  | Relative Performance for Bit Oriented Instructions          | 79         |

| 14.  | Evaluation of Test Program Results                          | 86         |

| 15.  | Programming Symbols                                         | 106        |

v

# LIST OF ILLUSTRATIONS

.

| Figu | re                                                    | Page       |

|------|-------------------------------------------------------|------------|

| 1.   | IBM Comats Computer System                            | 4          |

| 2.   | Diagram of Computer/Process Interfacing               | 6          |

| 3.   | Characteristics of Manufacturing Operations           | 7          |

| 4.   | Four-Level Hierarchical Control System                | 10         |

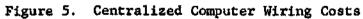

| 5۰   | Centralized Computer Wiring Costs                     | 14         |

| 6.   | Interlevel Communication                              | 27         |

| 7.   | Level (1) Computer System Architecture                | 32         |

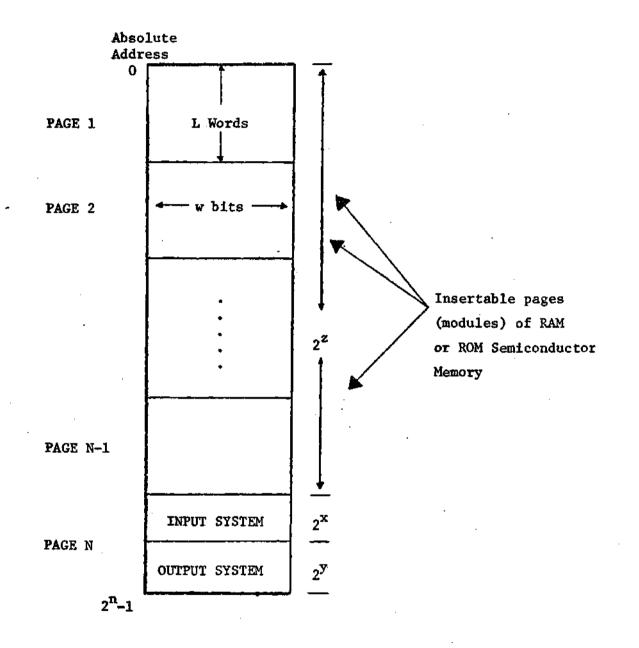

| 8.   | Partitioning of CPU Address Space                     | 34         |

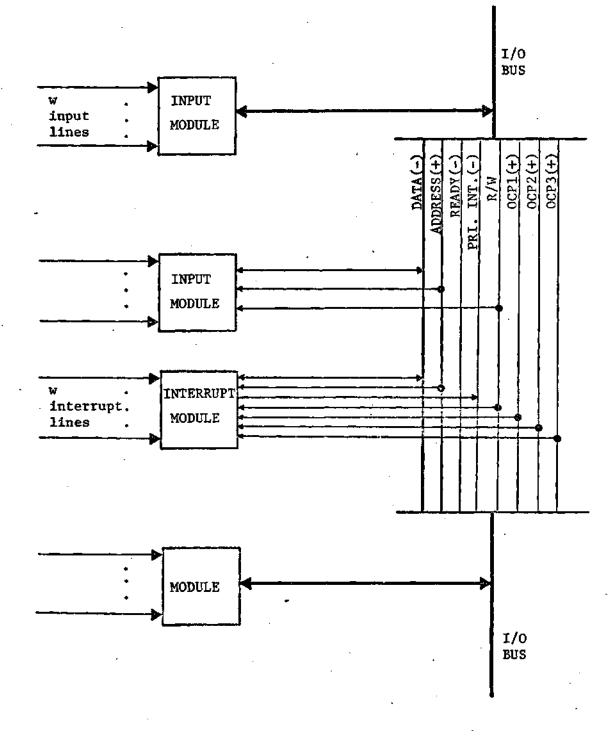

| 9.   | Block Diagram of Input System                         | 37         |

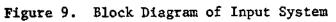

| 10.  | Output System Block Diagram                           | 40         |

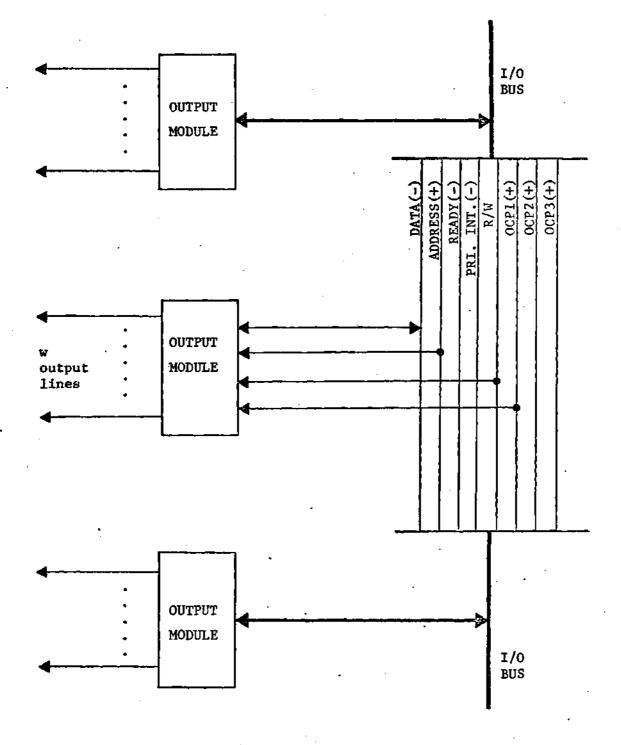

| 11.  | Memory System Block Diagram                           | 43         |

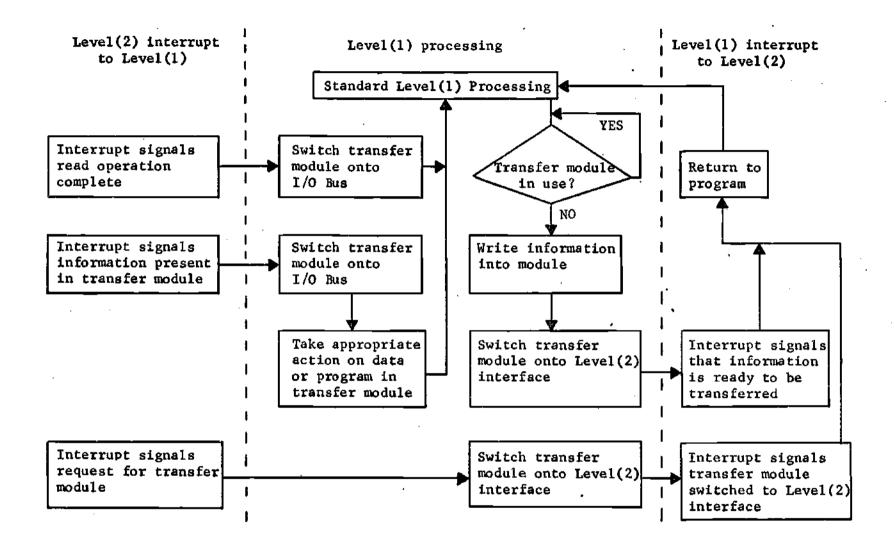

| 12.  | Flowchart for Vertical Information Transfer           | 45         |

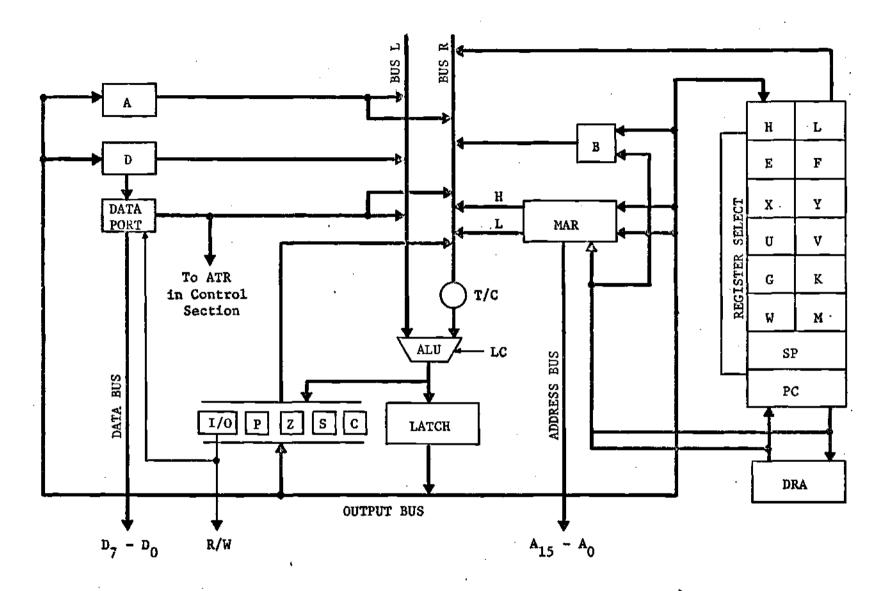

| 13.  | Microprocessor CPU Architecture                       | 48         |

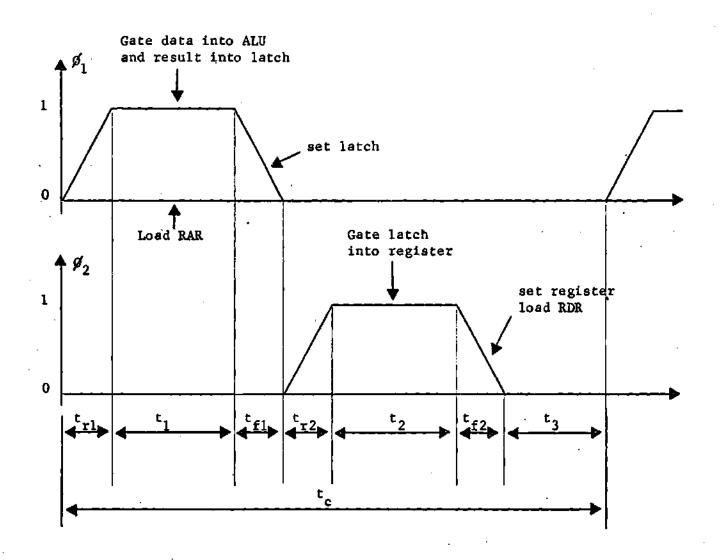

| 14.  | Two Phase Clock Used for System Timing                | 54         |

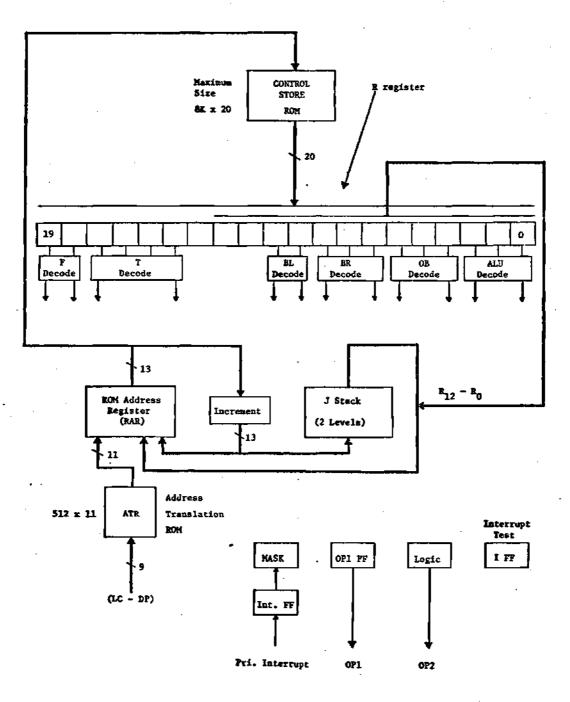

| 15.  | Control Section Architecture                          | 56         |

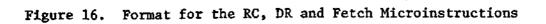

| 16.  | Format for the RC, DR and Fetch Microinstructions     | 59         |

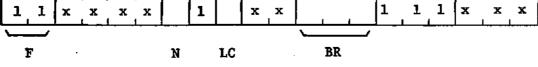

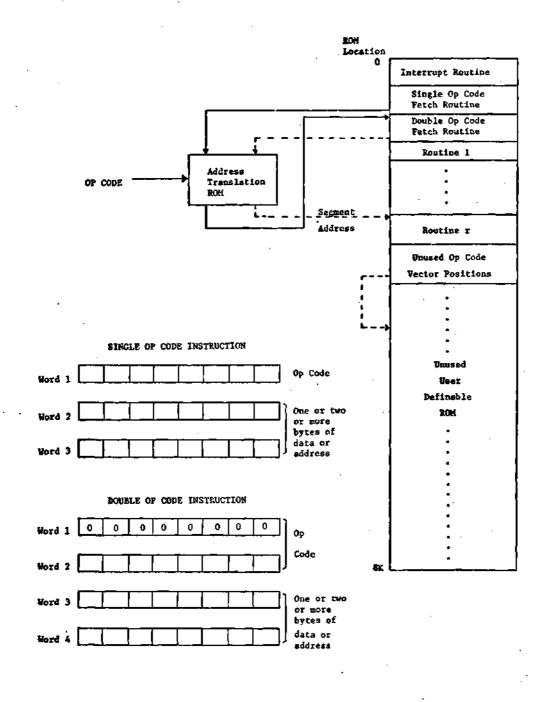

| 17.  | Control Store Address Mapping                         | 64         |

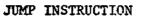

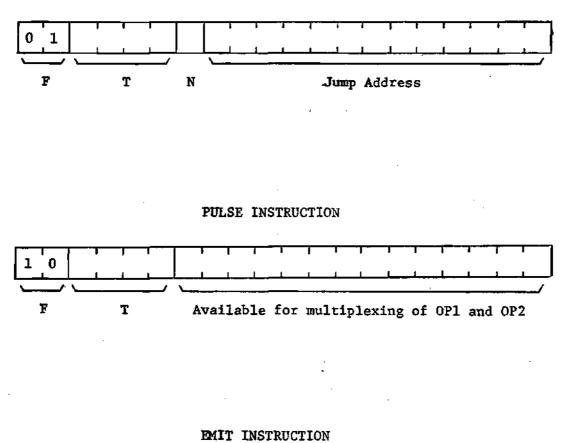

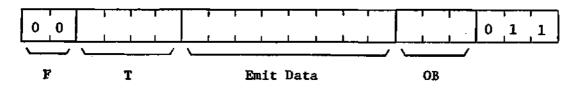

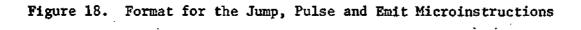

| 18.  | Format for the Jump, Pulse and Emit Microinstructions | 6 <b>5</b> |

| 19.  | Robot Control Configuration                           | 81         |

| 20.  | Memory and I/O Map for the Robot Control Problem      | 83         |

| 21.  | Robot Control Flowchart                               | 84         |

| 22.  | Input Module Circuit Diagram                          | 92         |

| Figu | re                            | Page |

|------|-------------------------------|------|

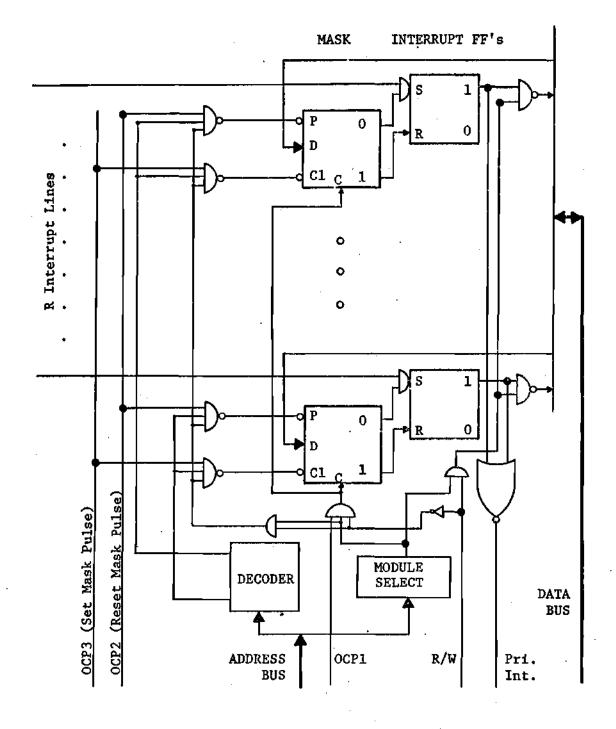

| 23.  | Interrupt Module Circuitry    | 96   |

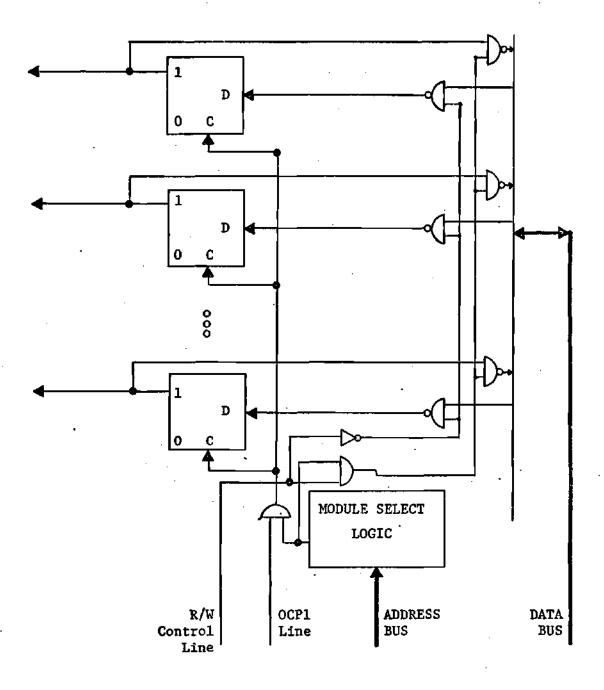

| 24.  | Output Module Logic Circuitry | 98   |

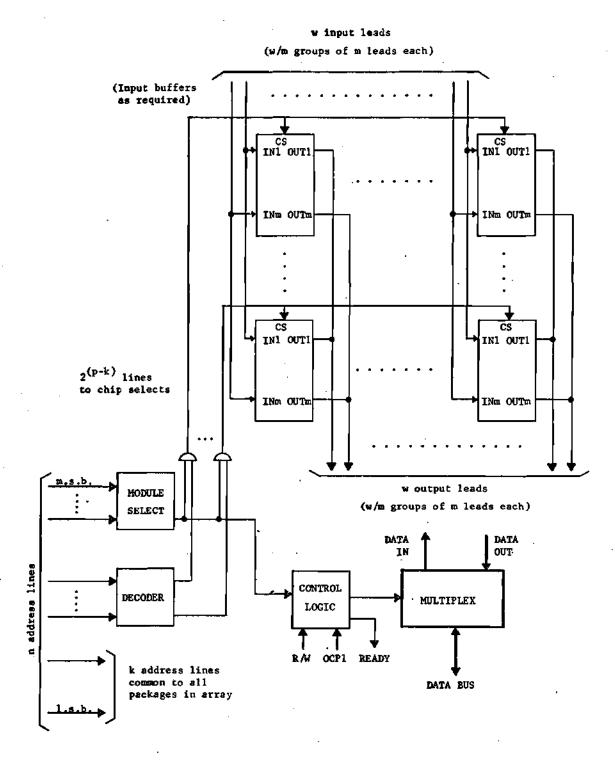

| 25.  | Memory Module Circuitry       | 100  |

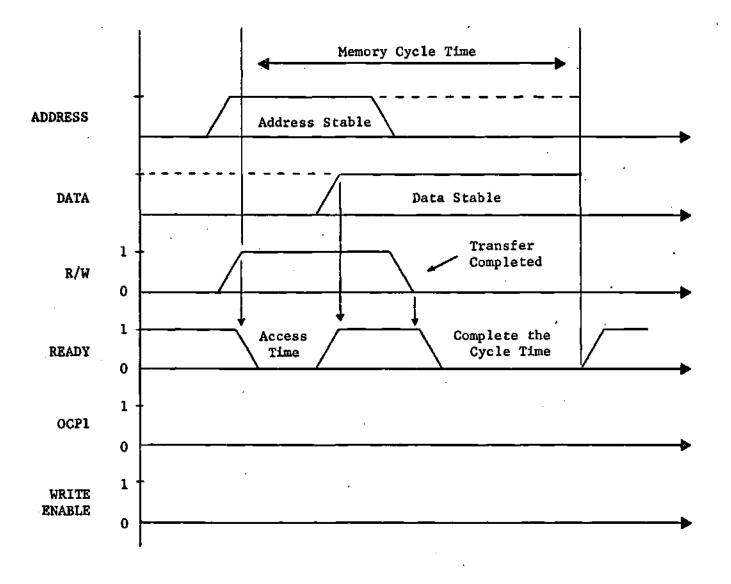

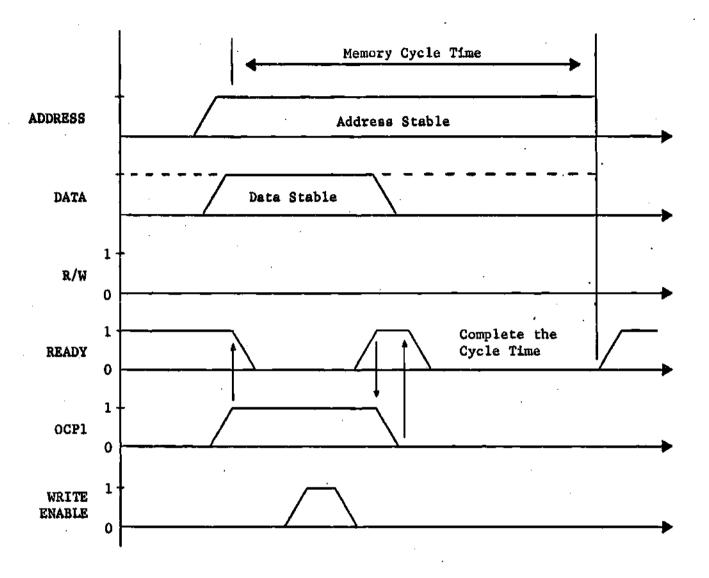

| 26.  | Memory Read Timing Sequence   | 102  |

| 27.  | Memory Write Timing Sequence  | 103  |

.

#### SUMMARY

Over the last decade, industrial control systems utilizing digital computers have typically implemented large centralized computer facilities. Two major drawbacks to this approach have been noted. First, the reliability of the central computer facility must be maintained near 100 percent since a system failure at this level can cause a cessation of all manufacturing operations. The second objection stems from the fact that excessively long control loops are necessary when using the centralized facility. Economic and noise shielding problems accompany the use of these control lines.

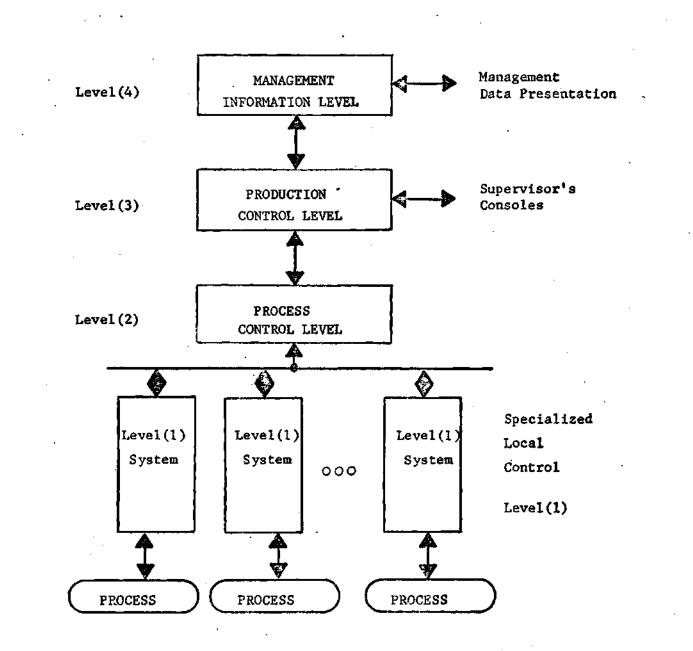

A four-level distributed computer hierarchy has been proposed for industrial control applications. Different segments of the overall control problem are assigned to dedicated computers at each of the four levels. The levels are: 1) Material Flow Level, 2) Process Control Level, 3) Production Control Level and 4) Management Control Level. At the Material and Process Control levels, the emphasis is on real time direct control of machines and processes while the Production and Management Control levels are concerned with matters such as scheduling and forecasting.

It has been proposed that real time control of machines and processes at the Level (1) Material Flow Level may be efficiently implemented using microprocessor CPU chips. In this scheme, each machine or process on the plant floor would have a dedicated real time computer system effecting control over that particular process. Such a system

viii

promises to offer benefits over the centralized concept with regards to both reliability and economic factors.

The object of this research was to identify the specific requirements placed on a microprocessor based computer control system capable of operating as a Level (1) processor. Using these requirements to specify the system, an architecture for the overall Level (1) system was developed. This architecture covered both a theoretical microprocessor architecture as well as the computer system hardware architecture.

It was concluded that the microprocessor CPU should have an instruction set that directly supports the control of machines and processes. This means that the microprocessor should be able to manipulate both single and double word data as well as single bit data. The microprocessor system must have an expandable multilevel interrupt structure to receive interrupts from the Level (2) supervisory computer as well as from the plant floor. A writeable control store control section was shown to offer an increase in system throughput and flexibility.

In comparing the performance of the Intel 8080 microprocessor CPU with that of the theoretical microprocessor developed in the paper, it was found that performance was comparable in operations working with eight bit (single word) data. The 8080 proved to be moderately deficient in its ability to manipulate double word data due to its reduced double word instruction set. In manipulating single bit data, the 8080 suffered its worst performance degradation in comparison to the theoretical microprocessor with execution times on the order of six times as large.

It was concluded that the Intel 8080 is capable of operating as

ix

a Level (1) microprocessor within applications compatible with its execution speed. A modification of the instruction set to better manipulate double word data and the addition of a bit processing feature would significantly increase the process control capabilities of the Intel 8080.

х

#### CHAPTER I

### INTRODUCTION AND PAST APPROACHES

## Introduction

### Definition of the Problem

Manufacturing control systems over the past ten years have tended toward digital control systems utilizing one or two large central computer systems exercising control over all processes within an entire plant. Typically the entire spectrum of applications programs ranging from management to process control are run in a multiporgramming environment within the computer system, necessitating a large central facility.

Major drawbacks resulting from this approach to manufacturing control have been noted. The centralized facility concept places an extreme emphasis on central system reliability in that a major system failure results in the termination of all control functions, resulting in a manufacturing halt. It has been reported that system availability (uptime divided by uptime plus downtime) in some cases has been less than 99.5 percent [1]. In order to increase system availability, some systems have utilized the principle of dynamic backup in which a second backup central processor is incorporated into the computer system. In the event of a failure in the main central processing unit (CPU), the secondary unit is automatically switched into the system, yielding availabilities as high as 99.95 percent. In addition to the reliability problem, the centralized concept has problems associated with program interaction in the multiprogramming environment and high cabling costs involved in bringing large amounts of data from the plant floor to the computer facility.

The problems associated with large centralized control facilities have led to a breaking apart of the control function into smaller subsets that may be more efficiently handled by dedicated computers in a hierarchical computer system.

#### Background Information

The evolution of computerized process control stemmed from two directions, the automobile industry and the aerospace industry. With the advent of numerically controlled machine tools in the early 1950's, the trend was set for direct digital control of machines in on-line operation [2]. Computer control systems typically cover a broad range of control functions in the total plant automation role, incorporating management, production and equipment control functions. Management information systems and production support systems are typically not real time critical activities, although they may account for a substantial portion of the computer workload in the total system. Equipment control functions are in most applications real time critical, demanding relatively frequent interaction between the control system and the controlled process. Machines and processes under the equipment control function usually fall into one of three main task categories referred to as Make, Move or Test [3].

Early attempts at decentralizing the computer control facility often resulted in a nonintegrated system structure. Such a system is characterized by computers, totally unrelated to each other, spread out

over the plant. Each computer provides equipment control over Make, Move and Test operations occurring simultaneously in from one to a number of separate processes or operations on the plant floor [4].

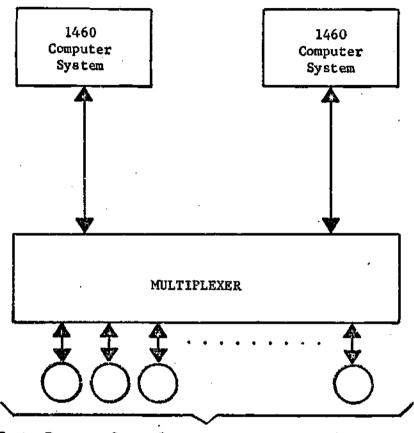

In an effort to overcome the shortcomings of the nonintegrated system, the trend has been toward a hierarchy of computers. Each computer in the hierarchy is associated with a particular level of the control function. The IBM COMATS computer system [5] shown in Figure 1 is an example of one of the first large scale hierarchical manufacturing control systems. The hierarchical nature of this system stems from the fact that the 1460 computers act as supervisor over the terminals which in turn provide the direct interfacing and control at the plant floor. Three types of terminals are used with this system. A universal tester, a process control terminal built around the IEM 1441 CPU, or a data acquisition terminal which acts as an Input/Output (I/O) buffer can be used to interface the computer to the plant. Up to 99 such terminals can be multiplexed to either of the two IBM 1460 computers. One 1460 is normally used to handle the real time interrupts generated by the terminals while the other is used for time shared processing and dynamic backup capability.

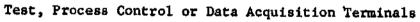

COMATS was the predecessor to the IBM Manufacturing Process Control System [6]. This architecture is similar to the COMATS architecture but was designed to be more versatile. Two system /360 computers provide data analysis and large data banks for the satellite computers. The satellite computers interface to the process and test equipment through sensor based Input/Output typically employing standard sensors such as input and output contact interfaces, analog-to-digital (A/D) interfaces

Figure 1. IBM COMATS Computer System

.

and digital-to-analog (D/A) interfaces [7] as shown in Figure 2. This IBM system placed most of the data processing requirements at the higher level /360 computers in an effort to minimize satellite computer requirements. Satellite computers were typically IBM 1130, 1800 or System /360 series computers and each satellite computer typically controlled more than one process. A special purpose operating system called PCOS (Process Control Operating System) was developed for the main /360 computers to permit them to act in a supervisory and data processing mode for the satellite computers [8]. A high data rate intelligent multiplexing system known as the TCU (Transmission Control Unit) was developed to handle data requests and multiplexing between the supervisory computers and satellite computers [9]. This IEM process control system represented a significant advance in integrated hierarchical control, but the total plant automation function encompasses more than just equipment control. The management information system function must be incorporated into the computer hierarchy. Additional integrated computer control systems similar to the two mentioned here are described in the literature [10], [11], [12].

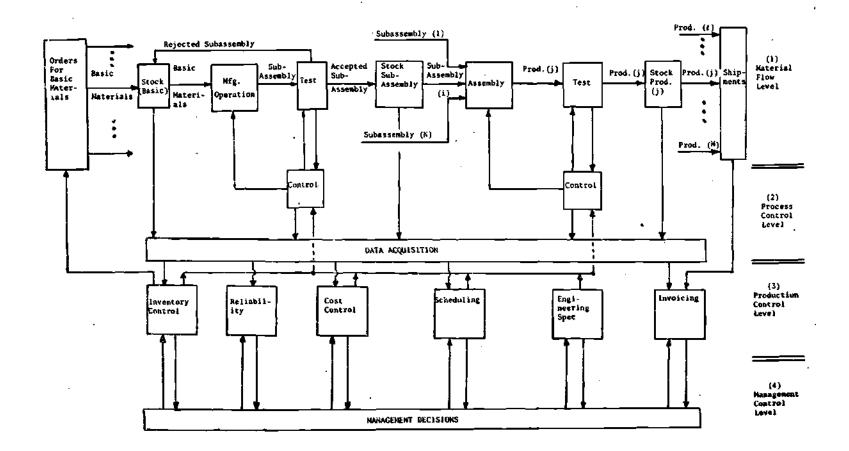

Hammond and Oh have characterized manufacturing operations as being divided into four levels as shown in Figure 3. These levels are: 1) the Material Flow Level, 2) the Process Control Level, 3) the Production Control Level and 4) the Management Control Level [2]. Computer usage at the different levels is cited in Table 1.

The most critical response times occur at the Process Control Level where real time interaction between computer and process are crucial. At the Production and Management Control Levels the shift is

Figure 2. Diagram of Computer/Process Interfacing

Figure 3. Characterization of Manufacturing Operations

$\overline{}$

|                            |                                        | ON-LINE                                             |            | OFF-LINE                                                                                    |

|----------------------------|----------------------------------------|-----------------------------------------------------|------------|---------------------------------------------------------------------------------------------|

| Process<br>Control         | A.1                                    | l Data Acquisition                                  | A.5        | Manufacturing Support Operation<br>(e.g., N/C tape production, IC<br>mask generation, etc.) |

|                            | A.2 Test Control                       | Test Control                                        |            |                                                                                             |

|                            | A.3                                    | Manufacturing Operation<br>Control                  |            | man generation, coc.,                                                                       |

|                            | A.4                                    | Assembly Operation                                  |            |                                                                                             |

| _                          | B.1                                    | Accounting                                          | B.5        | Cost Control                                                                                |

|                            | B.2                                    | • • • • •                                           | в.6        | Inventory Control                                                                           |

| Produc-<br>tion            |                                        | Scheduling                                          | B.7        | Quality and Reliability                                                                     |

| Control                    | B.3 Inventory of Products<br>and Parts |                                                     | Parameters |                                                                                             |

|                            | в.4                                    |                                                     | в.8        |                                                                                             |

|                            | D,4                                    | Quality Control                                     |            | Parameters from Engineering<br>Data                                                         |

| - <del></del>              | C.1                                    | Generation of Management                            | C.2        | Simulation Studies for                                                                      |

| Manage-<br>ment<br>Control |                                        | Information (e.g., Profit,                          |            | Forecasting Economic                                                                        |

|                            |                                        | Resource Utilization, Pay-<br>roll, Personnel Data) |            | Environment, Product Demand,<br>Rates of Return, etc.                                       |

|                            |                                        |                                                     | C.3        | Maintenance of Management<br>and Engineering Information<br>Files                           |

# Table 1. Computer Usage In Manufacturing Operations

.

away from real time response and toward more conventional batch type processing. At these two upper levels information is the basic flow quantity.

What is needed is a hierarchical computer system capable of exercising the proper control at all four levels of manufacturing operations. A computer control system architecture structured as in Figure 4 has been proposed to meet this need [1], [13]. At the lowest level of the hierarchy, Level (1), the emphasis is on real time control of a single machine or process. The computer at this level contains the program and data necessary for such control. Since it is desirable to minimize the storage requirements of the Level (1) system, the Process Control Computer System, Level (2), will contain in its mass memory files a copy of all applications programs used at Level (1). Level (2) memory may also contain those parameters that influence initial machine setup, assembly operations and required product output. Since there is no direct horizontal communication between Level (1) computers, the Level (2) Process Control Computer acts as a transmission link as well as a supervisor. The real time requirements at Level (2) are much less critical than those at Level (1) since no direct control of a given machine takes place at this level. Interlevel communication may be initiated by either Level (1) or Level (2) via interrupts to the called processor. In this hierarchical architecture, Level (2) will be used as a coordinating and supervisory control for all the machines, processes and operations at Level (1) [13].

The task of setting up primary production schedules is handled by the Production Control Computer System at Level (3). This function

requires input from a variety of sources associated with scheduling as detailed in Figure 3. The computer system at this level is a general purpose data processor with large memory, mass storage, high speed input/output and the capability to support multiple terminals for message requests. The system should support a number of high level languages, offer a high speed interrupt capability and feature a multiprogramming operating system [14]. Included at this level should be the necessary software to support program development in a suitable process control language for Level (1) process control programs.

The Management Control Computer System at Level (4) has the large task of generating the decisions for future plant directions and plans. Computer architecture at this level must be data base oriented and capable of the time shared support of a large number of terminals for managers. Functional requirements [13] of the various computer systems may be found in Table 2.

A four level hierarchy of control represents a shift away from the centralized control concepts of the last decade toward the distributed computer systems [14] mentioned in the literature today. This distributed system shifts the bulk of the real time process control away from a relatively large computer controlling many processes to many dedicated computers at Level (1), each controlling a single process or machine. Three advantages of using a distributed hierarchical architecture as opposed to a centralized architecture immediately suggest themselves.

<u>Modularity</u>. The modular system structure at Level (1) will tend to increase system availability. In a centralized system, a processor

# Table 2. Computer Functional Requirements

|         | INFORMATION SYSTEMS FUNCTIONS                                                                                                                                                                          | EQUIPMENT CONTROL SYSTEM FUNCTIONS               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Level 4 | Management Information System<br>Planning Tools for Management Decisions                                                                                                                               |                                                  |

|         | General Support Functions<br>Payments<br>Cost Reporting<br>Cost Estimating<br>Pricing<br>Tax Reporting<br>Personnel                                                                                    |                                                  |

|         | Simulation Models                                                                                                                                                                                      |                                                  |

| Level 3 | Production Support Functions                                                                                                                                                                           | Production Control                               |

|         | Product Data for each item<br>Specifications<br>Test & Reliability<br>Scheduling Information<br>Resources Required<br>Inventory<br>Product Changes<br>Unit Cost<br>Sales History<br>Critical Resources | Inventory Control<br>Optimal Resource Allocation |

| Level 2 |                                                                                                                                                                                                        | Data Acquisition and Control                     |

| డ       |                                                                                                                                                                                                        |                                                  |

| Level 1 |                                                                                                                                                                                                        |                                                  |

4

.

failure can lead to many machines and processes coming to a halt for lack of control. A system failure in a Level (1) processor would only have the immediate effect of stopping one machine or process, although other processes could presumably be affected. In this case the Level (2) Supervisory Computer would rearrange the workload among the remaining machines by altering the programs in their controlling processors.

Partial System Installation. The total control system could be built up in parts. A starting system could consist of only the first two levels of the control hierarchy. As plant equipment requirements expanded, additional Level (1) systems could easily be added without having to expand Level (2) hardware requirements. The ability of one Process Control Computer to supervise many subordinate processors is due to the fact that on a time scale, communication between any Level (1) processor and the Level (2) Supervisor is envisioned as being relatively infrequent and short. Each Level (1) processor is a complete computer system capable of independent operation to the extent that the controlled process will allow. This suggests a fallback capability to Level (1) operation exclusively in the event of a major Level (2) system failure.

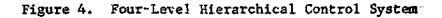

<u>Wiring Economics</u>. A centralized control facility requires that large amounts of information must be brought from the plant floor to the control computer. Figure 5 shows an analysis of the cost of the cabling necessary to run control loops from the plant floor to a centralized facility [1]. From this graph it is apparent that the cost of installing this wiring network is not insignificant, especially under the consideration that a single process on the plant floor may require

tens of control loops. The distributed hierarchical control architecture would eliminate the majority of this cable network. All control loops for a process would terminate at the Level (1) processor controlling that particular process. One data link from each Level (1) processor to Level (2) Supervisor is all that is required, thus eliminating the need for many long control loops. Other problems associated with noise shielding and data multiplexing are also eliminated using on-site computers.

## Purpose of the Research

In proposing a four level control hierarchy, both Alford and Keyes have suggested that the Level (1) computer system may be efficiently implemented using microprocessors as the central processing unit. This research will seek to determine the requirements placed on a Level (1) microprocessor system under the constraints of the distributed hierarchical control system. Various methods of satisfying these requirements will be examined. A theoretical microprocessor system architecture will be investigated that will efficiently satisfy Level (1) control requirements. Structure for the memory system and the input/output system will be examined as well as the internal architecture of a Read Only Control Store (microprogrammable) microprocessor.

In addition, the performance of the Level (1) microprocessor control system will be evaluated using two different CPU's. The performance using the theoretical microprogrammable CPU will be compared to that using the Intel 8080 microprocessor CPU chip. The test control problem will be oriented toward control of a manufacturing robot. Relative advantages and disadvantages of each system will be discussed in light

of the findings.

· ·

## CHAPTER II

#### IDENTIFICATION OF SYSTEM REQUIREMENTS

### Microprocessor System Requirements

In this section, the specific requirements imposed on the Level (1) microprocessor system will be identified under the constraints of the four level hierarchical control system. As these requirements are identified and defined, they will specify the system structure required for Level (1) control. In the past, commercial control systems have often combined Level (1) and Level (2) into a single computer system used to control many separate processes. A number of such minicomputer systems were originally designed as data processing machines, resulting in a bulky software package to allow them to function as a real time control processing system.

In an effort to identify purely Level (1) control requirements, the structure of a purely process control minicomputer system has been examined with regard to its Level (1) functions. The Texas Instruments 960 is a minicomputer control system designed exclusively for process control utilizing an I/O system, operating system and instruction set tailored to the unique control environment [15], [16], [17]. Those features of the TI 960 that are directly applicable to a Level (1) control system, as well as others unique to the hierarchical structure are reflected in the following Level (1) system requirements.

#### Instruction Set

The Level (1) microprocessor CPU should have an instruction set designed especially for the control of machines and processes [16]. Currently available microprocessors have a machine language instruction set, that is, the set of elementary operations specified by software and executed by hardware, designed for general purpose data manipulation. Such an instruction set is suitable for many applications, but exhibits coding inefficiencies when used in implementing process control instructions. For instance, a common process control instruction involves setting an output control line to a high or low state based on the test of a specified input line. Normally, this entire test and set sequence would be specified by a single command in an arbitrary high level process control language such as PROSPRO, which is used on the IBM 1800 system [3]. The actual sequence of machine instructions (object code) necessary to perform this test and set command would then be generated by the process control language compiler. But whether this object code is generated by hand or by a compiler, a relatively large number of machine language instructions will be necessary in order to implement the test and set command. Two approaches to this problem that have been used extensively are inline programming and subroutine programming.

Inline Programming. Each time a high level control instruction must be executed, the machine language instructions necessary for its execution are written sequentially into memory. This approach has the advantage of simplicity but suffers in reduced speed due to the multiple memory accesses needed to fetch the object code. It is felt that inline coding would also be prohibitive from a memory space standpoint due to

economic considerations and limited memory capabilities of microprocessor systems.

<u>Subroutine Programming</u>. In the utilization of this method the section of object code that executes each process control command is written as a subroutine. Thus, instead of writing object code inline, a subroutine call is used to reach a desired section of machine language instructions. Memory must be either permanently allocated to contain the entire set of subroutines corresponding to all process control commands or only those subroutines actually used in a particular program must be passed to the Level (1) memory along with the control program. Subroutine programming has the advantage of requiring less memory than inline programming since each segment of object code is written only once, but a loss of speed due to subroutine linkages is encountered.

These considerations lead to requiring an instruction set designed specifically for process control. In the example given above, there would be a "test and set" machine language instruction included in the CPU's repertoire of instructions. A not necessarily complete listing of the types of instructions to be included in the instruction set is given in Appendix E.

A substantial savings in speed is realized by storing in the control section of the CPU those sequences of operations that implement a process control command rather than storing those sequences as object code in the memory of the Level (1) system. Substantial memory savings are also realized by reducing inline programs or process control subroutines into instructions included in the CPU's instruction set.

## Bit and Byte Oriented System

Industrial sensors are many times bit oriented, i.e., the valve is either open or closed, the switch on or off. Analog-to-digital and digital-to-analog converters are primarily byte oriented devices, frequently requiring additional bytes of information to be used for multiplexing purposes. The overall architecture of the Level (1) computer system should be designed to facilitate both bit and byte I/O operations efficiently.

#### Bit Manipulation at CPU Level

Closely associated with the notion of a bit and byte oriented system is the ability to easily test and set or reset individual bits within a byte at the CFU register level. This ability to easily manipulate individual bits within a register is a feature not found in the present generation of microprocessors. With this feature status words could easily be set up in a prescribed location in memory. This would allow the supervisory computer at Level (2) to check on the status of the Level (1) processor and associated machine or process by performing a direct memory access (DMA) on the status words. This concept is particularly important in assembly line control where the status of adjacent machines on the line must be known for proper overall control [16]. Also, since many of the instructions of a process control computer are bit oriented, this feature will allow for an easier implementation of these instructions by the control section of the CFU.

#### Flexible Input/Output System

As previously stated, the I/O system of a Level (1) processor should possess an architecture that facilitates both bit and byte

operations. The total integration of a flexible I/O system must span I/O hardware design, CPU hardware considerations and firmware/software.

Hardware design includes all hardware considerations of the I/O system that are external to the CPU. The hardware implementing the input function must be capable of accepting addressable inputs from the plant floor. As information about specific inputs is needed by the CPU, this information must be transferred under CPU control. The input system should have the capability to gather information from a single line or a group of lines, i.e., both bit and byte input capability.

Output system considerations are likewise similar. The CFU should be able to set the state of a single output line or a group of lines simultaneously. The hardware implementing this function must contain memory to hold the state of the output line and each output line must be addressable by the CFU.

I/O architecture should be modular in nature, with the ability to arbitrarily change the number of input and output lines. It should be possible to build the I/O system up modularly, adding additional input or output modules as needs dictate. The ability to develop or use special purpose modules such as D/A or A/D converter modules and interrupt modules is also necessary. These requirements strongly suggest a bus oriented I/O architecture.

## Microprogrammable Control Section

The requirement that the Level (1) processor have an instruction set specifically designed for process control points to the need for a microprogrammable control section. The sequence of steps necessary to carry out a process control command, such as "test and set," could then

be stored in the control memory as a microprogram and executed whenever the "test and set" instruction was fetched from memory. This would give the system designer the flexibility to create special purpose process control instructions designed to fit the particular plant environment. The feasibility of building a microprocessor utilizing a microprogrammable control section has already been demonstrated by National Semiconductor in their IMP series microprocessors [18].

It is the control section that sends and receives the control signals that synchronize the memory and I/0 modules with the timing of the CPU. Thus, the control section should have input and output control lines under microprogram control. These lines would provide flexibility in interfacing the CPU with other components of the computer system.

The control section is responsible for handling primary interrupt signals. A primary interrupt indicates to the CPU that an interrupt has been received, but does not identify the interrupting device. After receipt of a primary interrupt, the computer must save the processor state, identify the device causing the interrupt and service the interrupt. Interrupt routines can be handled either by a machine language subroutine (software) or a microprogram routine (firmware). An interrupt routine stored in microprogram memory would provide for faster interrupt servicing than that of a machine language routine, but would be difficult to modify once stored. For this reason, it is felt that the processor state should be saved under microprogram control, and subsequent device identification and servicing be done by a machine language subroutine contained in the operating system. Restoring processor state after interrupt servicing could be done under microprogram control

if desired.

While there are certainly benefits to be gained from implementing a microprogrammable control section, these benefits do not come without their corresponding problems. Notably, two major problems present themselves: pin count and address translation.

If the control ROM is implemented outside the CFU chip, as it must be for a truly microprogrammable control section, then provision must be made for both address and data lines to communicate with the ROM. Consider an 8K control ROM composed of 21 bit microcode words. Without any multiplexing of address and data, 3<sup>4</sup> extra pins must be added to the microprocessor package in order to communicate with the ROM. If address and data were multiplexed over a single bus, then only 21 extra pins would be required. Even if the control section were implemented on a separate chip, the pin count per package would not be changed significantly and the total system pin count would almost double.

The problem of generating the starting address of a microprogram routine from its corresponding op code becomes especially difficult when the set of microprogram routines is subject to user change. Modifying the address of a low ROM routine would tend to change the address of all subsequent routines in higher ROM. Assigning each routine a fixed length block of ROM would tend to eliminate this problem but ROM fragmentation would result. Routines requiring more than one block would eliminate an op code for each additional block used. In an effort to eliminate unused ROM memory, an address translation mechanism could be used to translate the op code to the segment address of the corresponding microprogram routine. But this approach brings us back to the problem of modifying

routines. One solution to this problem is to permanently assign a basic instruction set in low ROM so that corresponding op codes would translate to routine segment addresses. A block or page could then be assigned to remaining unused high address op codes. These high op codes could subsequently be user microprogrammed with special purpose microprogram routines.

#### Interrupt Structure

The interrupt structure of the Level (1) computer system should be modularly expandable and capable of priority interrupt servicing. A modularly expandable structure is necessary because of the multiplicity of different types of industrial machines and processes that will fall under Level (1) control. One machine may be relatively simple, with few possible interrupt conditions and therefore requiring few interrupt lines. The computer system controlling this machine would need only enough interrupt lines to service its machine plus provision for standard interrupts common to all Level (1) systems. In like manner, some Level (1) systems may control relatively complex processes exhibiting a higher number of possible interrupt conditions. With interrupt circuitry packaged modularly, the system needs may be met by using only enough modules to satisfy the particular requirement. The priority nature of the interrupt system is necessary because of the relative importance of the different events that cause interrupts. An important event should be serviced before a less important event, thus the need for a priority interrupt structure.

It should be possible to store interrupts until they are serviced so that an interrupting device need only signal its interrupt once. Each

interrupt line should have an associated mask to disable that line. Interrupts received during the execution of an instruction should not be acknowledged until that instruction has completed its execution. Upon receipt of multiple interrupts, it should be possible to nest interrupt service routines if desired so that the highest priority interrupt is always being serviced.

#### Vertical Communication

An essential requirement placed upon a Level (1) computer system is that it be able to efficiently communicate with the Level (2) Supervisory computer. Why is this necessary? As stated previously, the memory requirements at Level (1) should be minimized as much as possible since a large number of Level (1) computer systems, i.e., one for each machine or process, are necessary. For instance, a particular process may operate under varying conditions over a given time period. Under each set of conditions, a different control program may be necessary for proper operation. If the complete set of control programs for this process were stored at Level (1), a great deal of memory would be necessary to store these temporarily unused programs. On the other hand, with temporarily unused programs stored in mass storage at Level (2), memory requirements at Level (1) are reduced.

Interlevel communication will be necessary to pass other types of data between Level (1) and Level (2). Transferred information may relate to initial machine setup, assembly operations, machine parameters or any other information deemed necessary. Basically, there are two modes of communication possible between the Level (2) and Level (1) systems, active and passive.

<u>Passive Communication</u>. The manner in which data transfers are initiated determines whether a system is operating in the active or passive mode. The situation is depicted in Figure 6. In a passive communication system, all data transfers are initiated by the Level (2) computer. This means that the Level (1) computer must keep current information needed by the Level (2) computer present in its memory at all times since a direct memory access may be initiated by the supervisory computer at any time. This method somewhat simplifies the operating system required at Level (1) but has the disadvantage of limiting overall control flexibility.

Active Communication. A system structure in which data transfers may be initiated either by Level (1) or Level (2) is defined as an active mode system. Interrupts are generated to signal the called processor that information is ready to be recieved or ready to be transmitted. Such an approach offers the systems designer a much greater flexibility in his design and reduces the need for a careful timing sequence for data transfer between levels. For this reason, the Level (1) microprocessor system should be capable of active mode communication.

Additional Requirements. During the time that a data transfer is taking place between Level (1) and Level (2), the Level (1) CPU should not be diverted from normal processing tasks. This restriction is necessary because of the critical real time nature of process control. If the CPU were involved in the actual data transfer, then its attention would have to be diverted from its primary task of process control. As shown in Figure 6, direct memory access is one possible solution to this

problem, but provision must be made so that Level (1) memory can be accessed both by the Level (1) CPU and the Level (2) computer system at the same time. Otherwise, the Level (1) CPU will end up waiting for its own memory while a data transfer is taking place.

### Independant Operation

In the event of a supervisory computer failure at Level (2), the interprocessor communication link for Level (1) computers would be lost along with the overall control and supervision functions performed by the Level (2) computer. Obviously, every possible effort should be taken at Level (2) to prevent a major system failure. If such a failure were to occur though, it would be desirable to continue plant operation to the fullest possible extent allowed by the situation. Some plant situations exhibit a substantial interdependence among individual processes, as in an assembly line. Unless some provision were made for limited direct communication between Level (1) computers in this particular case, a Level (2) failure would probably mean a cessation of control activities. Other process control situations are relatively independent of any other process and would be largely unaffected by a Level (2) failure.

In any case, provision should be made to load control programs into Level (1) systems from a secondary source. It this source is linked into the overall architecture at the supervisory computer level, then Level (1) architecture will be unaffected. Nevertheless, the Level (1) architecture should support a direct link from a remote source such as paper tape in case this approach were taken. Actually, the hardware necessary to implement this requirement has already been specified in the input, output and interrupt systems. The only additions necessary are software routines for input device loading and these may be kept permanently in the operating system. Any type of input device could easily be interfaced to the Level (1) system through the I/O system.

## Environmental Considerations

The Level (1) processor system should be able to operate in a hostile plant environment. Since this requirement is not directly related to the Level (1) architecture problem, only a cursory view of the factors involved in this problem will be examined. Factors of a plant environment usually fall into four categories: atmospheric contamination, thermal factors, mechanical factors and electromagnetic factors. Atmospheric contaminants are usually eliminated with proper system enclosures, but this can intensify the thermal problems. Mechanical factors are usually present in the form of vibration that can degrade circuit connections. Some applications may require a high acceleration resistance. Electromagnetic shielding is essential when operating in a plant environment due to the numerous sources of this interference. Provision may be a backup power supply circuit in each Level (1) computer system. Without this, a short power disturbance could destroy the contents of all Level (1) semiconductor memories.

The essential characteristics of a Level (1) system are given in Table 3.

Table 3. Characteristics of the Level (1) System

٠

.

| Function                    | Requirements                                                                                                                                                    |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction Set             | Oriented toward the process control<br>situation. Must include instructions<br>capable of operating on individual<br>bits and bytes in the range 12-16<br>bits. |

| Data Types                  | Bit, Byte, Word, Fixed Point Binary                                                                                                                             |

| I/O System                  | Capable of sending and receiving all<br>data types to and from the plant<br>floor.                                                                              |

| Interrupts                  | Priority system capable of storing<br>interrupts and nesting to service<br>the highest interrupt.                                                               |

| Interlevel<br>Communication | Capability to communicate with the<br>Level (2) supervisory computer.<br>During data transfer the Level (1)<br>CPU should not be inhibited.                     |

----

### CHAPTER III

#### PROPOSED SYSTEM ARCHITECTURE

# Level (1) System Architecture

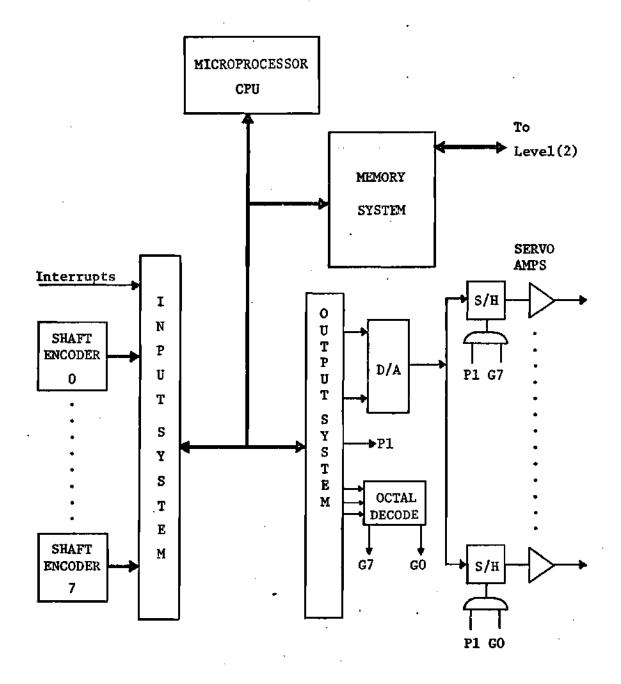

In Chapter II, the specific requirements imposed on a Level (1) microprocessor control system were examined. In order to meet these requirements, what other system components will be necessary in addition to a microporcessor CPU chip? Basically, in addition to the CPU, there are three main system areas that must be covered: the memory system, the output system and the input system which contains the interrupt lines as well as input lines. The overall system architecture proposed for the Level (1) control system is shown in Figure 7.

## System Structure

The major building block of this architecture is the microprogrammable microprocessor CPU and its control section. Contained within the CPU are the arithmetic logic unit, the registers and the internal busses common to all computer CPU's. The control section contains the system timing circuits, the control store memory to hold the microprograms and assorted registers, busses and decoders to carry out the CPU control function [19]. The I/O bus handles all data transfers between the CPU and input, output or memory systems. All three systems are accessed by the CPU as if they were a single large memory system composed of a mix of random access read/write and read only memory elements. Essentially this means that memory space, input system space and output

Figure 7. Level(1) Computer System Architecture

system space must all be disjoint subsets of the CPU address space. That is not to say that the CPU cannot, for example, perform a read operation on the output system. As it turns out just such an operation will have to be done. The essential point to be made here is that any word in any of the three systems must not have the same address as any other word in any other system.

Figure 8 shows one possible partitioning of the CFU address space. Essentially, the address space is subdivided into equal length pages of  $L = 2^p$  words each, p an integer. Assuming that the address bus is capable of handling an n bit address, this results in a total of  $N = 2^{(n-p)}$ pages for the address space.

It is expected that the majority of the CFU address space will be allocated to the memory system. In order to achieve the modular structure discussed in Chapter II, the memory system could be divided into modular memory modules of L words each. Each memory module used in a Level (1) system would occupy one page of memory space. The modular nature of this memory system allows memory capacity to be easily changed in order to meet changing control requirements. Serviceability is enhanced as a result of direct replacement of faulty modules. Each memory module could be composed of either random access read/write semiconductor (RAM), core or read only (ROM) memory elements.

Figure 8 shows that the last page of the address space contains the addresses for both the input and output systems. These two systems utilize a different addressing scheme from the memory system in that absolute addresses are bit addresses, although to the CPU these addresses look like word addresses. For instance, if the CPU were to load a

register with the contents of an input system address, the register would be loaded with a w bit word from the input system in which the bit that was originally addressed is located in a predetermined position within the word. The mechanics of the situation will be discussed in the next section. A bit addressed input and output system is necessary to meet the requirements set for these systems in Chapter II. It must be possible to deal with these systems on either a bit or byte basis.

In light of the preceeding discussion, the following relation must hold.

$$2^{n} \ge 2^{x} + 2^{y} + 2^{z}$$

x, y, z integers (1)

where

Input Address space,

$$I = 2^{x}$$

(2)

Output Address space,

$$0 = 2^{y}$$

(3)

Memory Address space,

$$M = 2^{Z}$$

(4)

This means that the input system will be able to handle a maximum of I input lines and the output system a maximum of O output lines. The memory system will be able to accomodate a total of M words of w bits each.

The choice of page size L is governed by two basic factors. On one hand, the value of L should not be so small as to force the number of pages N to an excessively large number. Restraints on the physical container size of the Level (1) memory system as well as economic factors regarding the number of memory modules in the system dictate that N be

less than some least upper bound. On the other hand, increasing values of L tend to lead toward a large unused memory fragment within the last memory module as well as unused address space within the page assigned to the input and output systems. The value of L should be an integer power of two to aid in address decoding.

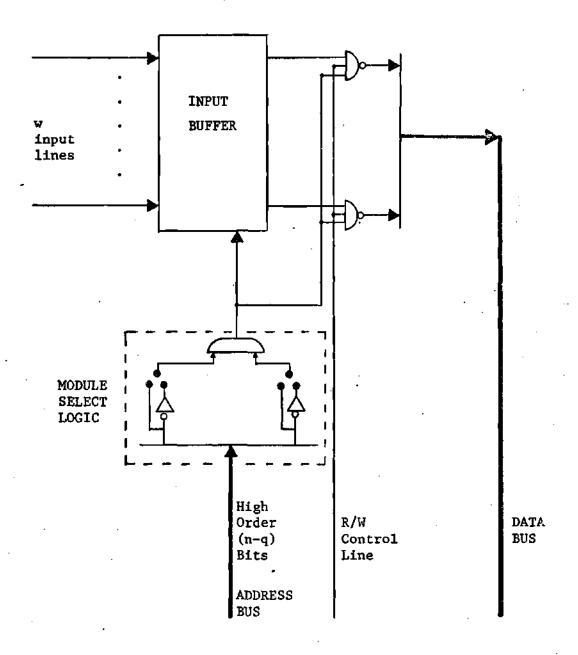

### Input System

Basically the input system is composed of an input bank to which the various input lines from the plant floor or other sources are connected, as shown in Figure 9. Logic level inputs are received at the input ports on the bank. Each port can accept w input signals.

Each input line of each port is addressable by the CFU address register via the address bus. The lower order q bits of the address specify the particular input line within the port and the remaining higher order bits select the correct port, with q given in equation five,

$$q = \left\lceil \log_2(w) \right\rceil$$

(5)

where  $\lceil x \rceil$  denotes the least integer greater than x. Both bit and byte input addressing is afforded using this scheme. During an input system read operation all w bits of the addressed input port are transferred to the CPU. Further, if the condition of a single input line is needed, the bit corresponding to that line may be tested by the CPU using a software or firmware routine. The particular bit within the w bit word is addressed by the low order q bits of the address register. A maximum of  $I_{p} = 2^{(x-q)}$  ports may be accomodated by the input system.

Physically, the input system could be constructed using printed circuit cards which plug into the I/O bus. Each card could contain

several input ports if necessary due to space limitations. Appendix A contains a more detailed discussion of one possible structure of the input port module.

Special purpose input modules may be incorporated into this input system. Modules containing A/D converters and interrupt circuitry are two that immediately suggest themselves.

<u>Interrupt Modules</u>. The need for an expandable priority interrupt structure has already been established. This requirement may be met by using modified input modules to receive incoming interrupt signals. The interrupt module must be capable of accepting either pulse or level interrupt signals. Each interrupt module is plugged into the I/O bus like a standard input module as shown in Figure 9. Internal mask circuitry is contained in each module and mask buffers are set on either a bit or byte basis. Each module contains R interrupt inputs up to a maximum of W inputs, each distinctly addressable.

Four basic operations control the interrupt module. First, a read interrupt buffer (RIB) operation transfers the state of the interrupt flip flops within the interrupt module to the CPU via the data bus. The specified interrupt module is addressed by the high order (n-q) bits of the address bus. In the RIB operation, the low order q bits of the address are meaningless to the interrupt module but can be used by the CPU in identifying the interrupting device. Second, a set mask (SMSK) operation sets the state of the mask flip flops to the state contained on the data bus. Again, only the high order (n-q) bits of the address bus are used to decode the correct module. The third and forth operations are set individual interrupt mask (SIIM) and reset individual interrupt

mask (RIIM). In each of these operations an individual flip flop and mask associated with an interrupt input are addressed by the address bus. The SIIM operation enables the specified interrupt line while the RIIM operation disables the specified individual interrupt line and resets its interrupt flip flop. The application of an interrupt signal to any enabled interrupt line both sets that interrupt flip flop and signals the CPU via the primary interrupt line that an interrupt has occurred. Logic requirements and timing considerations for the interrupt module are discussed in Appendix B.

An interrupt structure like the one described above is needed to meet the requirements placed on interrupt handling set forth in Chapter II. Enabling and disabling of interrupt lines is accomplished by the SIIM and RIIM operations. Each operation could correspond to a machine language instruction. Interrupts are stored (until they are serviced) within the interrupt flip flops contained in each interrupt module. The state of the interrupt flip flops of any module can be read by the CPU via the RIB operation which is simply a memory read operation with the address of an interrupt module. The SMSK operation corresponds to a memory write operation in which the mask flip flops of an addressed interrupt module may be written into as a group.

### Output System

The output system provides the link for data output from the CPU to the external world, that is, the plant. A diagram of the overall output system is given in Figure 10. System structure is similar to that of the input system. Output modules containing w output lines per module are plugged into the I/O bus. Individual modules are addressed

# Figure 10. Output System Block Diagram

by the high order (n-q) bits of the address word. The low order q bits of the address specify a particular output line within the module. A maximum of  $0_p = 2^{(y-q)}$  output modules may be contained within the output system.

Conceptually, the output system may be thought of as a random access memory composed of w bit words. Each word corresponds to an output module. Furthermore, all bits of the memory are simultaneously externally accessable through the output lines. This architecture results in a modular structure that is both bit and byte oriented.

Two basic output system operations are necessary using this structure. The write full word (WFW) operation writes a w bit word from the data bus into the output flip flops driving the addressed output port. The read full word (RFW) operation transfers the state of the addressed output module to the CPU via the data bus. In order to set the state of a single output line, it is necessary to perform a RFW operation on the module housing that line. The CPU then sets the state of the correct bit within the output word using the low order q bits of the address register to identify the correct bit. The output word is sent back to the output module via the WFW operation and the sequence is completed.

A discussion of the logic implementation of the output module may be found in Appendix C.

## Memory System

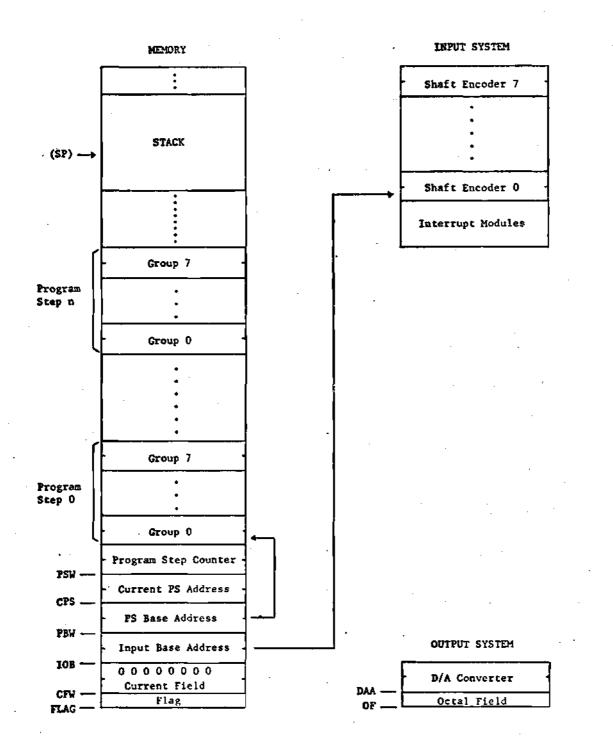

Figures 7 and 8 show that the memory system may be composed of (N-1) memory modules. Each module has an address space of L words composed of w bits per word. Modules may be made up of either core or RAM

or ROM type semiconductor memories. Core memories have the advantage of non-volatility which could prove helpful in case of a power failure, but due to the declining cost per bit of semiconductor memories these will probably be used in the majority of Level (1) memory systems. Those segments of the operating system that are permanent and re-entrant could be stored in ROM for security. Permanent process control programs could also be kept in ROM. Core or RAM semiconductor memories could be used for scratch pad applications and must be used in the memory module shown connected to the multiplex (MEX) circuit in Figure 7. Read/write memory must be used in this transfer module because it is the two way communication link between Level (1) and Level (2). During an information transfer from Level (1) to Level (2), the Level (1) CPU writes the information into the transfer module where it is subsequently read by the Level (2) supervisory computer. The procedure is reversed for Level (2) to Level (1) communication.

Figure 11 gives a block diagram of the memory system. The function of the data and address busses is the same as in the input and output systems. The R/W control line indicates whether a read or write cycle is about to be initiated and the OCP1 control line is used to indicate to the memory during a write cycle that data is stable on the data bus. The Ready line is a wired-OR common connection among the memory modules used to indicate module status to the CFU. This line allows slow cycle time memories to be used in the system by synchronizing the CFU to the memory. Appendix D gives a further discussion of memory module hardware and timing requirements.

Multiplex Circuit. The multiplex circuit connecting the memory

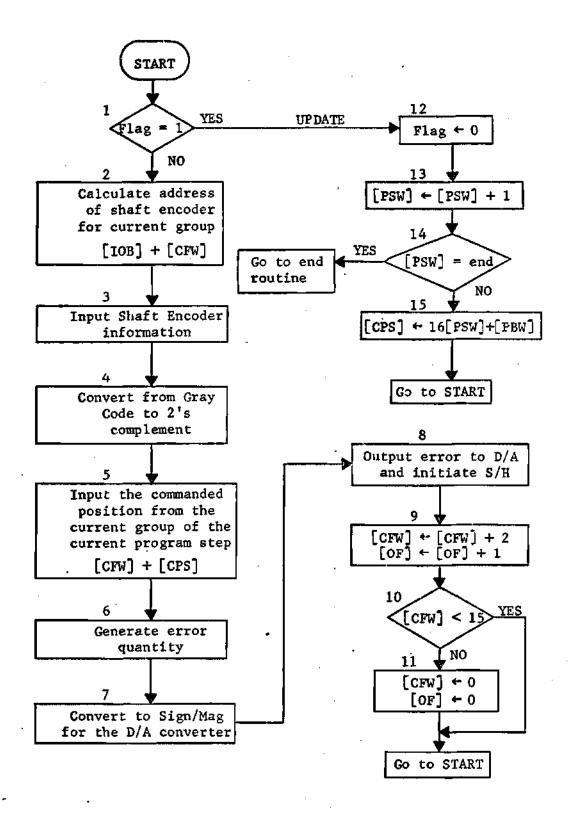

Figure 11. Memory System Block Diagram

module to the I/O bus in Figure 7 serves the purpose of a multi-pole double throw switch. Depending on the state of the output line coming from the output system, the memory module is connected to either the Level (1) I/O bus or an interface to the Level (2) computer system. In this way, verticle communication to and from the Level (2) computer system is possible. Yet, while the actual information transfer is taking place, the Level (1) CPU is free to execute its process control program from any other memory module in the Level (1) system. Allocating and deallocating the transfer memory module is accomplished by the Level (1) CPU through interrupt routines. The normal state of the multiplex circuit is with the transfer module connected to the I/O bus. Figure 12 gives a flow chart of the steps necessary for any information transfers. The format of the transferred information could be either executable statements or binary data.

At this point it may be argued that the multiplex scheme is just a cumbersome method of implementing a dual port memory, so why not use a dual port memory instead? The multiplex scheme is best for several reasons.

First, the cost of building dual port memory modules would be greater than that of single port modules. There is no need for the entire memory system to be dual port. The only time that the Level (2) computer would need to modify the contents of an entire Level (1) memory system would be during a setup operation when new control programs were being sent to the Level (1) memory. During setup, time is not a critical element and the Level (1) CPU is free to move programs and data through the transfer module. Still, it might be argued that the transfer module

Figure 12. Flowchart for Vertical Information Transfer

should be dual port. But this would still require that two separate types of memory modules be built. The multiplex scheme only requires the single port memory module which is used throughout all Level (1) systems. Controlling the state of the multiplex circuit with an output line from an output module provides the CPU with a convenient means of controlling the switching of the transfer module.

The second reason for favoring the multiplex scheme stems from an observation that if dual port memory modules were used in the memory system, then possible memory conflicts could result [23]. Essentially, the problem is that of two processors sharing a common memory. The dual port approach would offer a costly flexibility that is not essential in this application, while the simpler multiplexing of a single port transfer module is economically beneficial and adequate for this application. Summary

In the preceeding sections an architecture for the input, output and memory systems has been proposed. This architecture was developed under two primary constraints. First, it should be modular so that each Level (1) computer system can be built up to the level required by its unique control situation. Secondly, the architecture should support the system requirements identified in Chapter II. The major requirement affecting the design of the input and output systems was the need for a bit and byte oriented system. It is felt that the proposed architecture meets these requirements in a manner that affords easy interface with a microprocessor CPU.

### Level (1) Microprocessor Architecture

In this section, the architecture of an eight bit microprogrammable microprocessor called the GT 1248 will be described. A machine width of eight bits has been chosen so that a valid comparison with the performance of the eight bit Intel 8080 can later be made. In Chapter II the requirements for the overall Level (1) system were set forth. Table 4 compares the projected capabilities of the GT 1248 with those of the Intel 8080 in satisfying the major requirements imposed upon the Level (1) processor.

| Operation                                                  | GT 1248                                                                         | Intel 8080                                              |

|------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------|

| Bit manipulation at the Register level.                    | Available through<br>firmware and sup-<br>ported in the<br>instruction set.     | Available indirectly<br>through software rou-<br>tines. |

| Memory operations at the bit level.                        | Supported in the instruction set.                                               | Available indirectly<br>through software<br>routines.   |

| Double word operations<br>such as load, store,<br>compare. | Supported in the instruction set.                                               | Reduced capability in the instruction set.              |

| Single word operations                                     | Supported in the instruction set.                                               | Supported in the instruction set.                       |

| Special purpose<br>instructions                            | Available as machine<br>language instructions<br>through micropro-<br>gramming. | Available through software routines.                    |

Table 4. Comparison of Microprocessor Capabilities

# GT 1248 Microprocessor CPU Architecture

Figure 13 gives the internal CPU architecture of the GT 1248.

Figure 13. Microprocessor CPU Architecture

Three major internal eight bit busses route data between the arithmetic and logic unit (ALU) and the data registers. Data is transferred to and from the CPU via data bus lines  $D_7 - D_0$  connecting the data port (DP) to external system components. Depending on the state of the I/O flip flop, data is routed from the data bus to Bus R (input mode) or from register D to the data bus (output mode). The address for all memory, input or output system references is carried from the memory address register (MAR) to external components via the address bus,  $A_{15} - A_0$ . The function of the double register arithmetic (DRA) unit is to provide increment, decrement and complement operations on 16 bit double words from the register stack.

<u>CFU Registers</u>. Connected to Bus L are the A register, D register and the data port (DP). Each register is eight bits wide and data flow into and out of all registers is under the control of the microprogram control section. Bit manipulation is accomplished in the A register. Bit address within the A register can be supplied either by the B register or by the microprogram control store. The D register is used for data output in conjunction with the data port and may also be used as a temporary store for intermediate results.

Connected to Bus R are the register stack, the B and A registers, the memory address register (MAR) and the DP. The register stack is made up of 16 eight bit registers. These registers may be accessed as either a single eight bit register via connections to Bus R and the output bus or as a double register composed of 16 bits via connections to the DRA and MAR. Double registers HL, EF, XY, UV and GK are available at the machine language level as general purpose registers. The WM

register is reserved for control section use to store intermediate results. The stack pointer (SP) and program counter (PC) are also available at the machine language level but are reserved for their dedicated functions. The memory address register (MAR) is a 16 bit register made up of two concantenated eight bit registers. The register containing the high order bits, A<sub>15</sub> - A<sub>8</sub>, of the address is referred to as register MARH. Likewise, the low order bits of the address,  $A_{\gamma} - A_{0}$ , are stored in the lower register, MARL. Register B is a three bit special register used to implement addressing for bit manipulation. Only the low order three bits of data from the output bus are loaded into B during its register load operation. When B is gated onto Bus R, high order bits are gated as logic zeroes while the three low order bits come from B. Register B is always loaded whenever register MARL is loaded from the output bus or whenever the MAR is loaded from the DRA or stack. In this manner B always contains the three low order bits of any MAR address.

<u>ALU Components</u>. Associated with the arithmetic and logic unit (ALU) are: a true/complement (T/C) gate array for Bus R, a group of five flag flip flops and an output latch. The T/C array can be used to gate into the ALU the complement of the data contained on Bus R. This is done under microprogram control and is useful in performing one's and two's complement subtraction schemes.

The functions of the five flag flip flops comprising the processor state word (PSW) are given in Table 5. The I/O flip flop is under microprogram control exclusively, while flags P, Z, S and C are loaded during certain ALU operations. The five flags may be thought of

| Flip Flop | Function                                                                                                                                                                                                                      |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| I/O       | Determines the state of the data<br>port. Logic 1 = data port in the<br>input mode. Logic 0 = data port<br>in the output mode. Normally<br>this flip flop is kept in the<br>logic 0 state.                                    |  |

| Р         | Reflects whether the last word<br>gated from the ALU contained even<br>or odd parity. $P = 1$ denotes odd<br>parity, $P = 0$ denotes even parity.                                                                             |  |

| S         | Reflects whether the last word<br>gated from the ALU was positive<br>or negative depending on the state<br>of the MSB. $S = 1$ indicates that<br>the word was negative. $S = 0$<br>indicates that the word was posi-<br>tive. |  |

| Z         | Reflects whether the last word<br>gated from the ALU was equal to<br>zero. $Z = 0$ denotes that the<br>last word was nonzero. $Z = 1$<br>denotes that the word was zero.                                                      |  |

| C         | During certain ALU add operations,<br>the carry generated from the MSB<br>additions is gated into C. During<br>a right or left rotate, the bit<br>rotated is loaded into C.                                                   |  |

# Table 5. Flag Flip Flop Functions

•

as a separate register that may be gated onto Bus R or recieve data from the output bus. When gated as a register, the five flags are right justified in the field of the word. This feature permits the flags to be stored in memory prior to interrupt servicing.

Table 6 gives a description of the operation set of the ALU. During an ADD operation, a binary one may be gated into the carry of the l.s.b. addition by applying a logic one to the LC terminal of the ALU. During an ADD (with carry) operation, the LC terminal is connected to the C flip flop, otherwise it is under microprogram control and is useful in two's complement schemes.

The eight bit output of the ALU is gated into a temporary latch that holds the result long enough to allow it to be gated via the output bus into a register.

<u>CPU Timing</u>. Figure 14 shows the two phase clock used to control all register transfers. The same clock is used for control section timing. During time  $t_1$  data is gated onto Busses L and R, through the ALU and into the latch. Time  $t_1$  must be greater than or equal to the worst case propagation delay through the ALU and into the latch. During time  $t_{f1}$  the data present at the latch is locked in, in much the same way as in the TTL 74100 latch [21]. Flag flip flops are gated and locked according to the same timing as the latch.

The contents of the latch are gated into a selected register via the output bus during time  $t_2$ . Time  $t_2$  must be greater than or equal to the worst case propagation delay through the output bus into the register. During time  $t_{f2}$  the contents of the register are locked in, so that CPU registers may be of the same structure as the latch. Table 6. ALU Operation Set

·

.

| Operation        | Description                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------|

| ADD              | OUTFUT ← Bus L + Bus R (arithmetic<br>sum)<br>(C) ← carry, all flags affected                      |

| ADD (with carry) | OUTPUT $\leftarrow$ Bus L + Bus R + (C)<br>(C) $\leftarrow$ carry, all flags affected              |

| ADD (no flags)   | OUTPUT ← Bus L + Bus R<br>no flags affected                                                        |

| AND              | OUTPUT ← Bus L A Bus R<br>(C) unaffected                                                           |

| OR               | OUTPUT - Bus L V Bus R<br>(C) unaffected                                                           |

| EXCLUSIVE OR     | OUTPUT ← Bus L ¥ Bus R<br>(C) unaffected                                                           |

| ROTATE L         | OUTPUT ← rotate left (Bus L + Bus R)<br>(C) ← m.s.b. before rotate operation                       |

| ROTATE R         | OUTPUT $\leftarrow$ rotate right (Bus L + Bus R<br>(C) $\leftarrow$ l.s.b. before rotate operation |