# DESIGNING HIGH-PERFORMANCE MICROPROCESSORS IN 3-DIMENSIONAL INTEGRATION TECHNOLOGY

A Thesis Presented to The Academic Faculty

by

Kiran Puttaswamy

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2007

# DESIGNING HIGH-PERFORMANCE MICROPROCESSORS IN 3-DIMENSIONAL INTEGRATION TECHNOLOGY

Approved by:

Professor Gabriel H. Loh, Advisor College of Computing *Georgia Institute of Technology*

Professor Hsien-Hsin S. Lee School of Electrical and Computer Engineering *Georgia Institute of Technology*

Professor Sudhakar Yalamanchili School of Electrical and Computer Engineering *Georgia Institute of Technology*  Professor Sung Kyu Lim School of Electrical and Computer Engineering *Georgia Institute of Technology*

Professor Milos Prvulovic College of Computing Georgia Institute of Technology

Professor Douglas Yoder School of Electrical and Computer Engineering *Georgia Institute of Technology*

Date Approved: September 13, 2007

Family,

for being who they are

and

Boy(s) Who Survived,

for not blinking during the duel and for teaching me how to make lemonade

## ACKNOWLEDGEMENTS

I express my sincere gratitude to Professor Gabriel H. Loh for his energy and patience in mentoring me and guiding my thesis. I feel immensely fortunate to have had a chance to work with him and consider my research collaboration with him as one of my best career decisions. I will forever remember him for his enthusiastic and passionate attitude and his superb mentoring skills. I thank Professor Hsien-Hsin S. Lee for agreeing to be my co-advisor and guiding me on various occasions. His energy seems boundless and he has always been a source of information to me on various technical and career-related issues. I thank Professor Sung Kyu Lim for research collaboration and for serving as a reader on my thesis committee. He has provided valuable feedback on various aspects of my research and has helped enrich the content of my dissertation. I thank Professor Sudhakar Yalamanchili for serving as chairman of my thesis proposal committee and for always responding promptly to my requests. I thank my thesis committee members, Professors Douglas Yoder and Milos Prvulovic for their valuable feedback and suggestions to improve my work.

I thank my friends Samantika, Guru, Ioannis, Mrinmoy, Richard, Dong Hyuk, Dean, Eric, Michael, Dae Hyun, Nive, and Raghu for their friendship over the years. I thank Susie and Deborah in the College of Computing for assistance in administrative matters. I thank Marilou in the ECE Graduate Affairs Office for helping and providing information during various points of my graduate student life. I thank the various program committees and reviewers for their constructive feedback on my research papers. I acknowledge Intel Corporation and FCRP for research equipment and funding.

My mom Vanaja, my dad Puttaswamy, my sister Kanchan, and my brother-in-law Suresh have encouraged and supported me to attend graduate school and for that, I express my deepest gratitude and appreciation. Finally, I thank my wife, Rohini for making a tremendous difference to my life.

iv

# TABLE OF CONTENTS

| DED  | ICATI | ION .   | ii                                       | i |

|------|-------|---------|------------------------------------------|---|

| ACK  | NOW   | LEDGE   | EMENTS                                   | V |

| LIST | OF T  | ABLES   | ix                                       | ζ |

| LIST | OF F  | IGURE   | S                                        | i |

| SUM  | MAR   | Υ       | XV                                       | v |

| PAR  | тт    |         |                                          |   |

| IAN  | 11    |         |                                          |   |

| Ι    | INTE  | RODUC   | TION                                     | L |

|      | 1.1   | Motiva  | tion 1                                   | Ĺ |

|      | 1.2   | Curren  | t Technology Challenges                  | 2 |

|      |       | 1.2.1   | Interconnect Delay                       | 2 |

|      |       | 1.2.2   | Power Consumption                        | 3 |

|      |       | 1.2.3   | Power Density                            | 1 |

|      |       | 1.2.4   | Manufacturing Process                    | 1 |

|      | 1.3   | Three-o | dimensional Integration Technology       | 5 |

|      |       | 1.3.1   | State of the Art in 3D-Integration       | 5 |

|      |       | 1.3.2   | Copper Bonding 3D-Integration Topologies | 7 |

|      |       | 1.3.3   | Die-to-Die Vias                          | ) |

|      |       | 1.3.4   | Benefits of 3D-Integration               | l |

|      |       | 1.3.5   | Some Challenges to 3D-Integration        | 3 |

|      | 1.4   | Scope   | of This Dissertation                     | 5 |

| PAR  | ТII   |         |                                          |   |

| П    | SRA   | M COM   | 1PONENTS                                 | 1 |

|      | 2.1   |         | ew of This Chapter                       |   |

|      | 2.2   |         | SRAM Components                          |   |

|      | 2.2   | 2.2.1   | •                                        |   |

|      |       |         |                                          |   |

|      |       | 2.2.2   | Memory Subbanking                        |   |

|      |       | 2.2.3   | Hierarchical Wordlines                   | 3 |

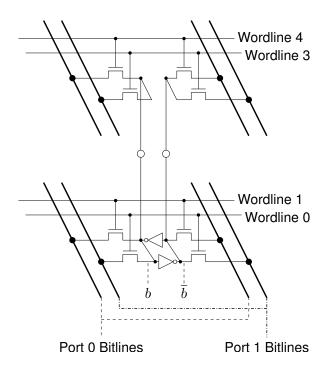

|     |     | 2.2.4   | Multi-Porting Technique                     | 29 |

|-----|-----|---------|---------------------------------------------|----|

|     | 2.3 | 3D-Int  | egrated Large SRAM Components               | 29 |

|     |     | 2.3.1   | Bank-Stacked 3D SRAM Circuits               | 30 |

|     |     | 2.3.2   | Array-Split 3D SRAM Circuits                | 31 |

|     | 2.4 | 3D-Int  | egrated Multi-Ported SRAM Components        | 32 |

|     |     | 2.4.1   | Register-Partitioning (RP) 3D SRAM Circuits | 32 |

|     |     | 2.4.2   | Bit-Partitioning (BP) 3D SRAM Circuits      | 34 |

|     |     | 2.4.3   | Port-Splitting (PS) 3D SRAM Circuits        | 36 |

|     |     | 2.4.4   | Hybrid Partitioning with More Than Two Die  | 37 |

|     | 2.5 | Results | s                                           | 39 |

|     |     | 2.5.1   | Bank- and Array-Stacked 3D SRAM Benefits    | 39 |

|     |     | 2.5.2   | Multi-Ported 3D SRAM Benefits               | 43 |

|     | 2.6 | Summa   | ary of the 3D-Integrated SRAM Components    | 50 |

| III | ASS | OCIATI  | IVE LOGIC COMPONENTS                        | 52 |

|     | 3.1 | Overvi  | ew of This Chapter                          | 52 |

|     | 3.2 | Planar  | CAM Components                              | 52 |

|     |     | 3.2.1   | Planar Instruction Scheduler Circuit        | 53 |

|     |     | 3.2.2   | Other CAM Logic Circuits                    | 55 |

|     | 3.3 | 3D-Int  | egrated CAM Components                      | 56 |

|     |     | 3.3.1   | Entry-Partitioned (EP) 3D CAM Circuits      | 56 |

|     |     | 3.3.2   | Tag-Partitioned (TP) 3D CAM Circuits        | 56 |

|     |     | 3.3.3   | Extending to More Than Two Die              | 58 |

|     | 3.4 | Results | s                                           | 59 |

|     |     | 3.4.1   | 2-Die-Stacked 3D CAM Benefits               | 59 |

|     |     | 3.4.2   | 4-Die-Stacked 3D CAM Benefits               | 61 |

|     | 3.5 | Summa   | ary of the 3D-Integrated CAM Components     | 62 |

| IV  | DAT | A PROC  | CESSING COMPONENTS                          | 63 |

|     | 4.1 | Overvi  | ew of This Chapter                          | 63 |

|     | 4.2 | Planar  | Data Processing Components                  | 64 |

|     |     | 4.2.1   | Adder Circuits                              | 64 |

|     |     | 4.2.2   | Barrel Shifter Circuit                      | 68 |

|     |        | 4.2.3   | Multiplier Circuit                                  | 70  |

|-----|--------|---------|-----------------------------------------------------|-----|

|     | 4.3    | 3D-Int  | egrated Data Processing Components                  | 71  |

|     |        | 4.3.1   | 3D-Integrated Adder Circuits                        | 73  |

|     |        | 4.3.2   | 3D-Integrated Barrel Shifter Circuit                | 75  |

|     |        | 4.3.3   | 3D-Integrated Multiplier Circuit                    | 76  |

|     |        | 4.3.4   | Extending to More Than Two Die                      | 76  |

|     |        | 4.3.5   | Scalability Studies                                 | 78  |

|     | 4.4    | Results | s                                                   | 79  |

|     |        | 4.4.1   | 3D-Integrated Adder Benefits                        | 79  |

|     |        | 4.4.2   | 3D-Integrated Barrel Shifter Benefits               | 82  |

|     |        | 4.4.3   | 3D-Integrated Multiplier Benefits                   | 83  |

|     |        | 4.4.4   | Scalability Results                                 | 83  |

|     | 4.5    | Summa   | ary of the 3D-Integrated Data Processing Components | 88  |

| PAF | RT III | [       |                                                     |     |

| V   | 3D-I   | INTEGR  | RATED PROCESSORS                                    | 93  |

|     | 5.1    | Overvi  | ew of This Chapter                                  | 93  |

|     | 5.2    |         | and 3D-Integrated Processors                        | 93  |

|     |        | 5.2.1   | Baseline Planar Processor                           | 93  |

|     |        | 5.2.2   | 2-Die-Stacked 3D-Integrated Processors              | 94  |

|     |        | 5.2.3   | 4-Die-Stacked 3D-Integrated Processors              | 97  |

|     | 5.3    | Experi  | mental Procedure                                    | 97  |

|     |        | 5.3.1   | Circuit Latency and Energy                          | 97  |

|     |        | 5.3.2   | Temperature Analysis                                | 99  |

|     | 5.4    | Results | s                                                   | 100 |

|     |        | 5.4.1   | Latency                                             | 100 |

|     |        | 5.4.2   | Power Consumption                                   | 102 |

|     |        | 5.4.3   | Temperature                                         | 103 |

|     | 5.5    | Summa   | ary of the 3D-Integrated Processors                 | 107 |

| VI  | THE    | ERMAL   | HERDING 3D-INTEGRATED PROCESSORS                    | 108 |

|     | 6.1    | Overvi  | ew of This Chapter                                  | 108 |

|      | 6.2  | Planar | and 3D-Integrated Dual-Core Processors              |

|------|------|--------|-----------------------------------------------------|

|      |      | 6.2.1  | Baseline Planar Processor                           |

|      |      | 6.2.2  | 4-Die-Stacked Thermal-Herding 3D Processor          |

|      |      | 6.2.3  | 4-Die-Stacked Coarse-Grained 3D Processor           |

|      | 6.3  | Therm  | al-Herding Techniques for 3D Microarchitectures     |

|      |      | 6.3.1  | Register Files                                      |

|      |      | 6.3.2  | Arithmetic Units                                    |

|      |      | 6.3.3  | Bypass Network                                      |

|      |      | 6.3.4  | Instruction Scheduler                               |

|      |      | 6.3.5  | Load and Store Queues                               |

|      |      | 6.3.6  | Data Cache                                          |

|      |      | 6.3.7  | Front-End                                           |

|      |      | 6.3.8  | Thermal Herding Microarchitecture Summary 120       |

|      |      | 6.3.9  | Design Space Exploration                            |

|      | 6.4  | Experi | mental Procedure                                    |

|      | 6.5  | Result | s                                                   |

|      |      | 6.5.1  | Performance                                         |

|      |      | 6.5.2  | Power Consumption                                   |

|      |      | 6.5.3  | Temperature                                         |

|      |      | 6.5.4  | Design Space Exploration                            |

|      | 6.6  | Summ   | ary of the Thermal Herding 3D-Integrated Processors |

| VII  | CON  | ICLUSI | IONS                                                |

| APPI | ENDE | ΧA     | ELECTRIC MODELS OF TRANSISTORS AND WIRES            |

| APPI | ENDE | X B    | DYNAMIC AND STATIC POWER CONSUMPTION 139            |

| REFI | EREN | CES .  |                                                     |

| VITA | L    |        |                                                     |

# LIST OF TABLES

| 1  | 2006 ITRS projections of interconnect delays for a local interconnect (0.1 mm), intermediate interconnect (1 mm), and global interconnect (10 mm)                                                                                                                                                                                                       | 3   |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Impact of the 3D-integration technology on the SRAM array latency.                                                                                                                                                                                                                                                                                      | 39  |

| 3  | Impact of the 3D-integration technology on the SRAM array energy.                                                                                                                                                                                                                                                                                       | 41  |

| 4  | Benefits of 3D multi-ported SRAM configurations with increasing number of entries.                                                                                                                                                                                                                                                                      | 45  |

| 5  | Access latencies of register files for a 4-wide, 64-bit superscalar processor, and<br>the percentage benefit compared to the baseline planar implementation, for<br>increasing entries.                                                                                                                                                                 | 47  |

| 6  | Scheduler latencies for planar, entry partitioned (EP), and tag partitioned (TP)<br>2-die-stacked 3D organizations.                                                                                                                                                                                                                                     | 60  |

| 7  | Scheduler latencies for planar and entry-partitioned (EP) 4-die 3D organiza-<br>tions.                                                                                                                                                                                                                                                                  | 61  |

| 8  | Latency benefits of the 3D-integration technology for other CAM components                                                                                                                                                                                                                                                                              | 62  |

| 9  | Characteristics of planar adder designs.                                                                                                                                                                                                                                                                                                                | 67  |

| 10 | Latency and energy benefits of the 2-die-stacked 3D circuits compared to the planar circuits. The columns marked '%' show the relative reduction in latency and energy. Note that these results are for stand-alone functional units and do not take bypass wiring into account. (The best 64-bit 3D-integrated configurations are shown in bold font). | 80  |

| 11 | Latency and energy benefits of the 3D-integrated shifter compared to the pla-<br>nar shifter circuit. (results do not take bypass wiring into account).                                                                                                                                                                                                 | 82  |

| 12 | Latency and energy benefits of the 3D-integrated multiplier compared to the planar multiplier circuit. (results do not take bypass wiring into account).                                                                                                                                                                                                | 83  |

| 13 | Percent improvement in delays of various 64-bit, 2-die 3D-integrated arithmetic circuits (odd-even partitioned)                                                                                                                                                                                                                                         | 85  |

| 14 | Power benefit due to downsizing the transistors on the 3D-integrated KS adder circuits                                                                                                                                                                                                                                                                  | 87  |

| 15 | Parameters of our baseline planar processor                                                                                                                                                                                                                                                                                                             | 94  |

| 16 | Material properties                                                                                                                                                                                                                                                                                                                                     | 100 |

| 17 | HSpice timing results for various microarchitectural modules for planar, 3D 2-<br>die-stacked and 3D 4-die-stacked implementations, and the largest size imple-<br>mentable for each module without exceeding the latency of the corresponding<br>planar implementation.                                                                                | 101 |

| 18 | Circuit and microarchitecture parameters of the baseline processor.                                                                                                                                                                                                                                                                                     | 101 |

| 19 | Critical path latencies for several microprocessor blocks. We consider the Wakeup-Select and the ALU-Bypass loops (in bold) to be the clock limiting | 102 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | paths                                                                                                                                                | 123 |

| 20 | Most power-consuming benchmarks on our planar baseline, and the corre-                                                                               |     |

|    | sponding power consumed by our Thermal Herding 3D processors                                                                                         | 127 |

| 21 | Total power consumption versus peak temperature                                                                                                      | 132 |

| 22 | Density of d2d vias versus peak temperature (original 3D-integrated processors                                                                       |     |

|    | assume fully-populated via density)                                                                                                                  | 133 |

| 23 | Die thinning versus peak temperature (original 3D-integrated processors have                                                                         |     |

|    | a die-thickness of 9 $\mu$ m)                                                                                                                        | 133 |

# LIST OF FIGURES

| 1  | A MLBS 3D IC with four device layers                                                                                                                                                                                                         | 6  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | A 2-die-stacked 3D integrated-circuit with (a) face-to-face, and (b) face-to-back bonding topologies. (Figures not drawn to scale).                                                                                                          | 7  |

| 3  | A 4-die-stacked 3D integrated circuit with (a) face-to-back , and (b) alternating face-to-face bonding topologies (Figures not to scale).                                                                                                    | 8  |

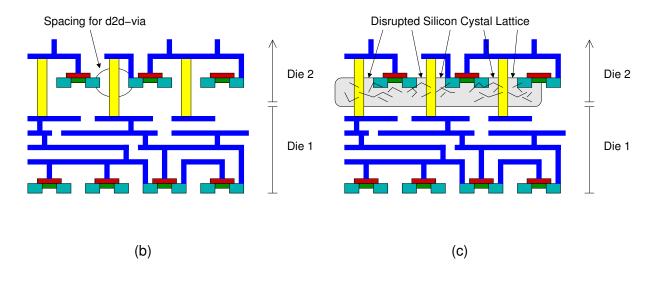

| 4  | (a) Placement of F2F vias may not affect transistor placement. (b) Placement of backside vias interrupt transistor placement. (c) Backside vias may disrupt the crystal structure of the device layer degrading performance.                 | 10 |

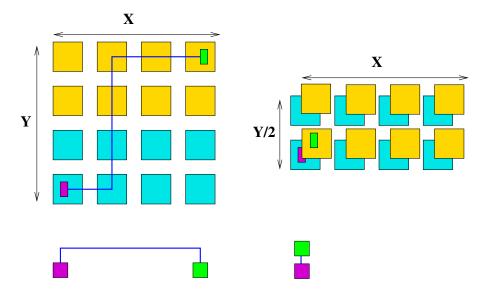

| 5  | Benefits of 3D technology (a) Planar circuit (b) 3D-integrated circuit.                                                                                                                                                                      | 12 |

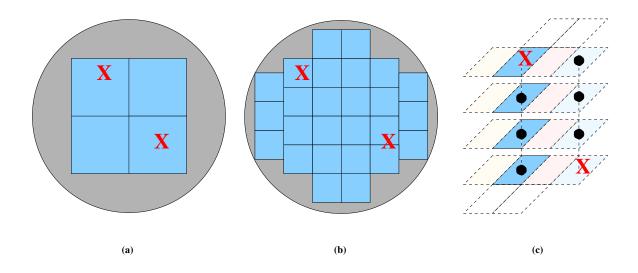

| 6  | Wafer with (a) planar die (b) reduced footprint die (due to 3D-integration) (c)<br>In wafer bonding, defective die may stack on good die, thus reducing yield.                                                                               | 13 |

| 7  | A progression from planar/2D processors to 3D-integrated processors with varying numbers of layers and CPU implementation styles.                                                                                                            | 17 |

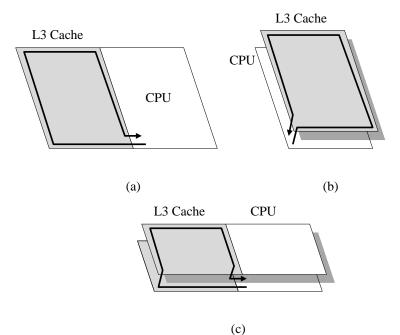

| 8  | (a) A planar layout of a processor and L3 cache with the L3 critical path, and<br>a 3D implementation with (b) the cache stacked on top of the processor, and (c)<br>circuit-stacked processor and cache.                                    | 21 |

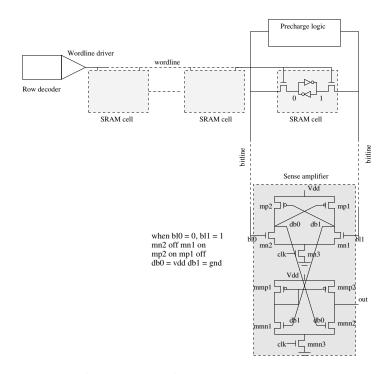

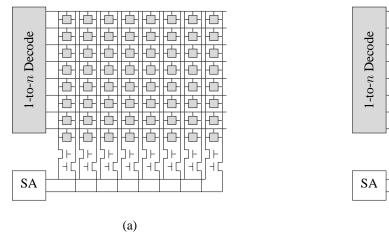

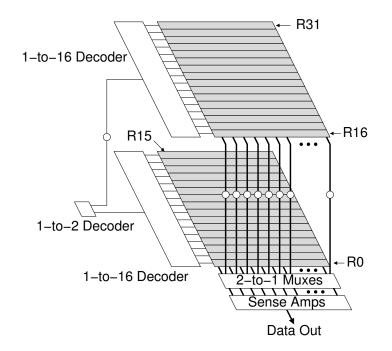

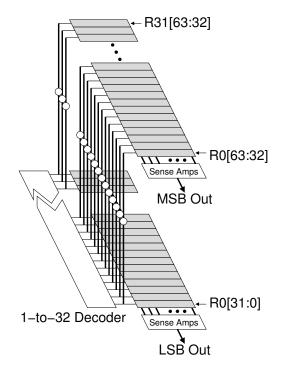

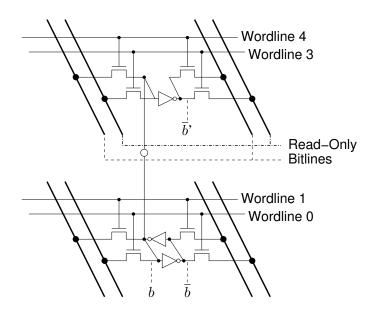

| 9  | Critical path of a cache access (read) operation                                                                                                                                                                                             | 26 |

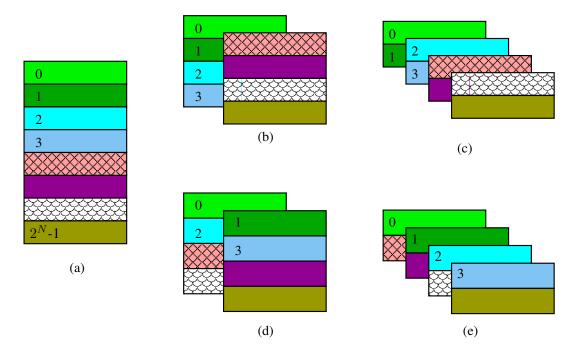

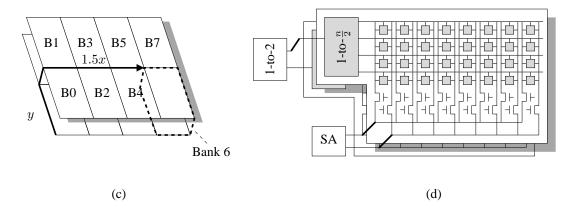

| 10 | Memory banking technique (a) one monolithic array (b) two banks with higher-<br>order interleaving (c) four banks with higher order interleaving (d) two banks<br>with lower order interleaving (e) four banks with lower order interleaving | 27 |

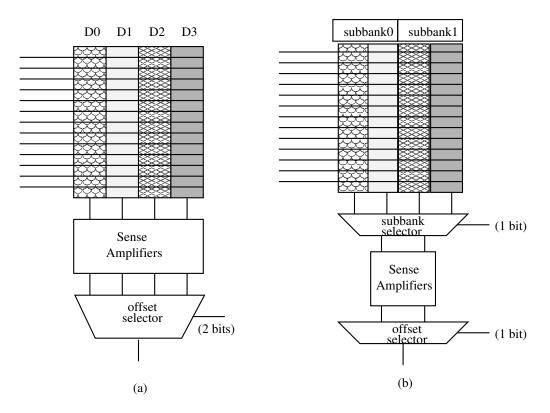

| 11 | Memory subbanking technique: (a) original data array with each cache block consisting of four data words (b) subbanked data array with two subbanks (two data words per subbank).                                                            | 28 |

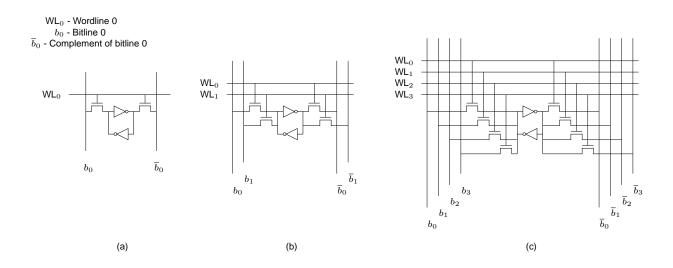

| 12 | Quadratic area increase of an SRAM cell as the number of ports increases from<br>(a) one to (b) two to (c) four ports.                                                                                                                       | 30 |

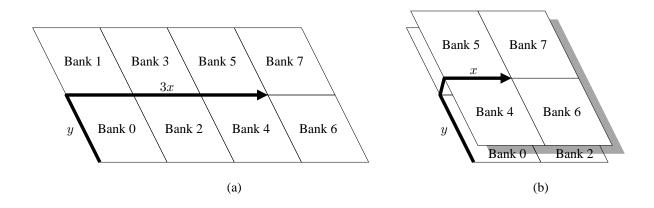

| 13 | (a) A planar 8-banked array showing the worst-case distance to the farthest bank, and (b) a 3D bank-stacked SRAM organization.                                                                                                               | 31 |

| 14 | (a) A banked planar array with 16 banks, (b) a 2-die-stacked 3D array with left-to-right stacking, (c) a 4-die-stacked 3D array with top-to-bottom stacking across the F2F interfaces and left-to-right stacking across the B2B interface .  | 32 |

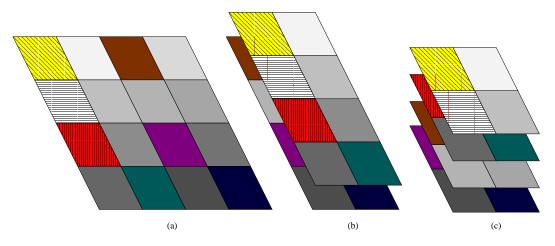

| 15 | (a) A planar SRAM array, (b) a 3D-integrated array with column-on-column array-splitting, (c) the bank-level organization using column-split arrays, (d) a 3D-integrated array using row-on-row array-splitting.                             | 33 |

| 16 | Register-partitioning 3D register file. A $\circ$ represents a die-to-die via.                                                                                                                                                               | 34 |

| 17 | Bit-partitioning 3D register file. A $\circ$ represents a die-to-die via.                                                                                                                                                                    | 35 |

| 18 | Port-split 3D register file with 2 die-to-die vias per bitcell. A o represents a die-to-die via.                                                                                                                                                                                               | 36 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 19 | Alternate port-split 3D register file that uses only one die-to-die via per bitcell.<br>A o represents a die-to-die via.                                                                                                                                                                       | 38 |

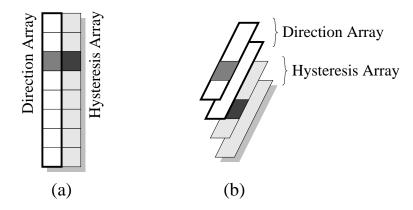

| 20 | (a) A planar branch direction predictor array, and (b) a 3D-integrated branch predictor array partitioned into two separate sub-tables                                                                                                                                                         | 39 |

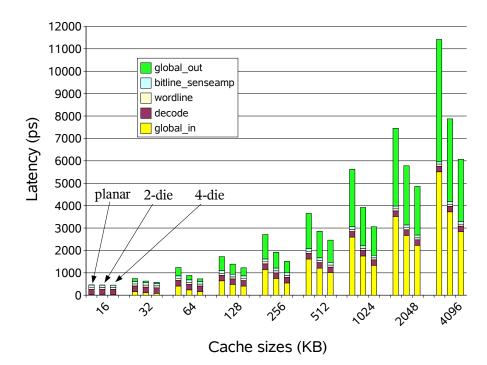

| 21 | Component-wise breakdown of the SRAM array latencies.                                                                                                                                                                                                                                          | 40 |

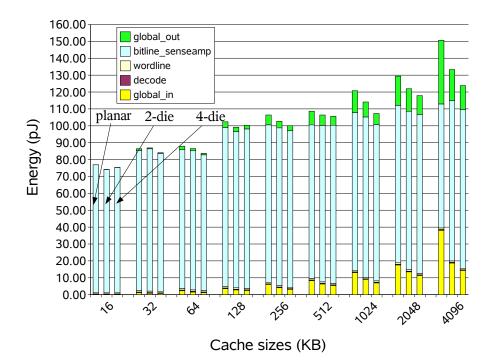

| 22 | Component-wise breakdown of the SRAM energy (cache read operation).                                                                                                                                                                                                                            | 42 |

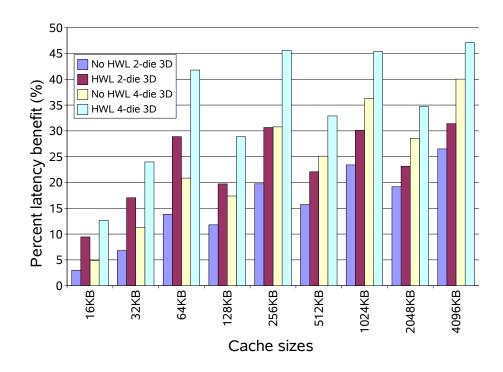

| 23 | 3D-integration benefits with hierarchical wordlines technique                                                                                                                                                                                                                                  | 43 |

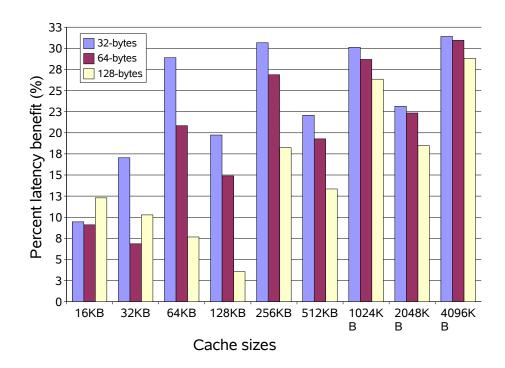

| 24 | 3D-integration benefits with increasing block sizes.                                                                                                                                                                                                                                           | 44 |

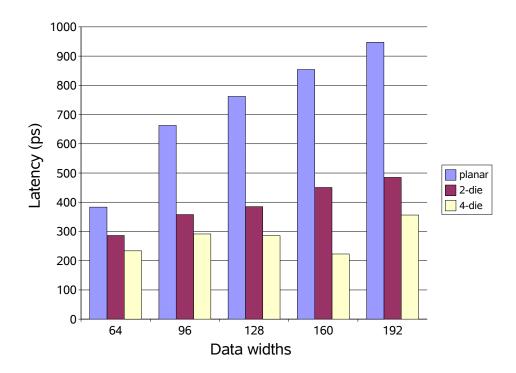

| 25 | Access latencies of a 96-entry register file (4-issue processor) with increasing data widths.                                                                                                                                                                                                  | 48 |

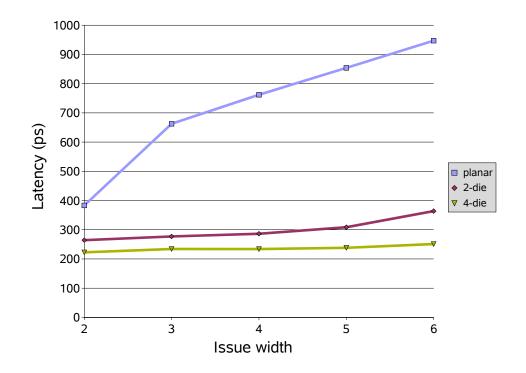

| 26 | Access latencies of a 96-entry, 64-bit register file with increasing issue-widths.                                                                                                                                                                                                             | 48 |

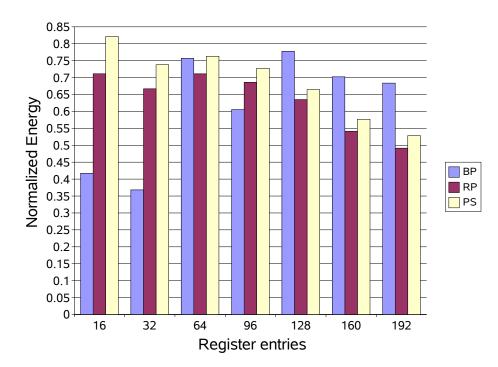

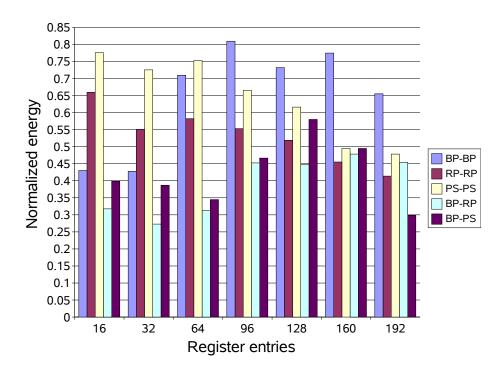

| 27 | Energy benefits of the 2-die-stacked 3D register file designs.                                                                                                                                                                                                                                 | 49 |

| 28 | Energy benefits of the 4-die-stacked 3D register file designs.                                                                                                                                                                                                                                 | 50 |

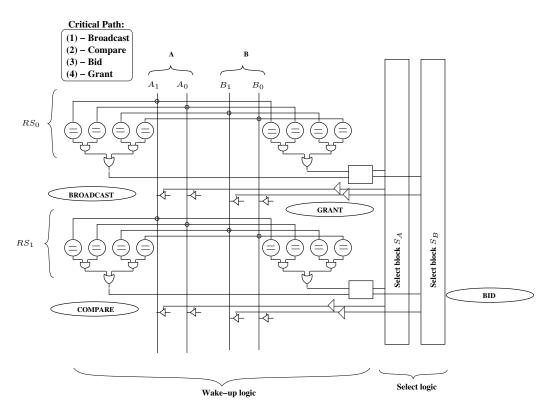

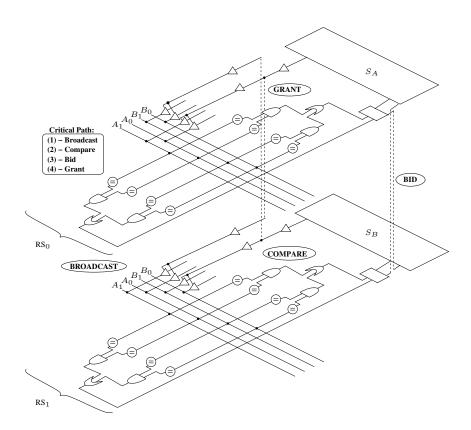

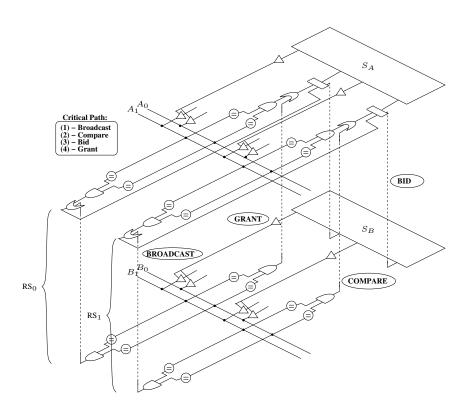

| 29 | A planar dynamic instruction scheduler circuit                                                                                                                                                                                                                                                 | 54 |

| 30 | An entry-partitioned 3D CAM circuit                                                                                                                                                                                                                                                            | 57 |

| 31 | A tag-partitioned 3D CAM circuit                                                                                                                                                                                                                                                               | 58 |

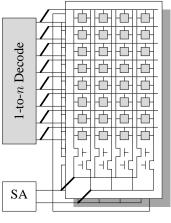

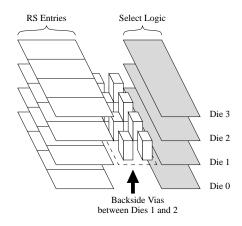

| 32 | A 4-die-stacked EP scheduler with extra space allocated for backside vias. Di-<br>mensions not to scale.                                                                                                                                                                                       | 59 |

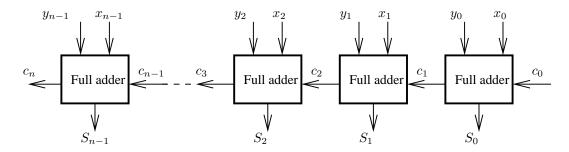

| 33 | Critical path of an n-bit planar ripple-carry adder                                                                                                                                                                                                                                            | 64 |

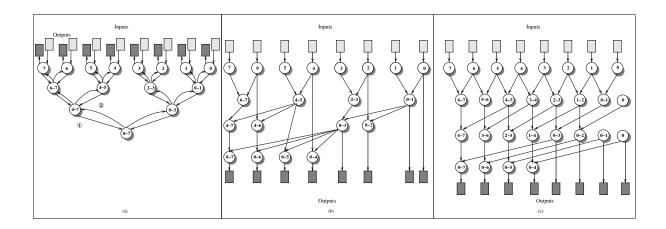

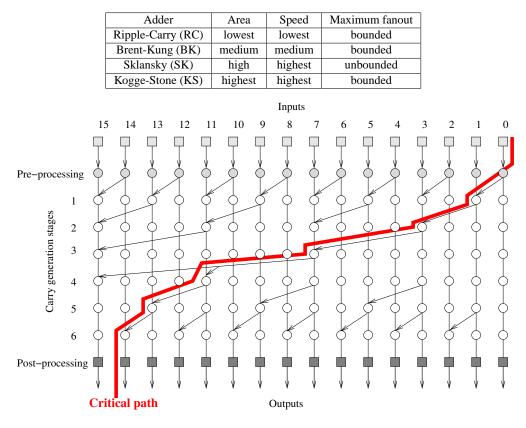

| 34 | 8-bit planar adders (a) Brent-Kung, (b) Sklansky, and (c) Kogge-Stone. The nodes $\circ$ represent the propagate-generate $PG$ components of the parallel-prefix computation for the adder's carry logic, while the wires communicate the different partial-prefix computations between nodes. | 65 |

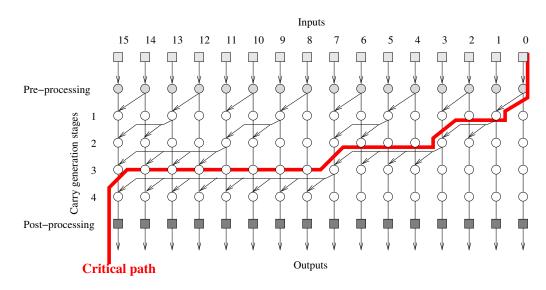

| 35 | Parallel-prefix graph of a 16-bit planar Brent-Kung adder                                                                                                                                                                                                                                      | 67 |

| 36 | Parallel-prefix graph of a 16-bit planar Sklansky adder                                                                                                                                                                                                                                        | 68 |

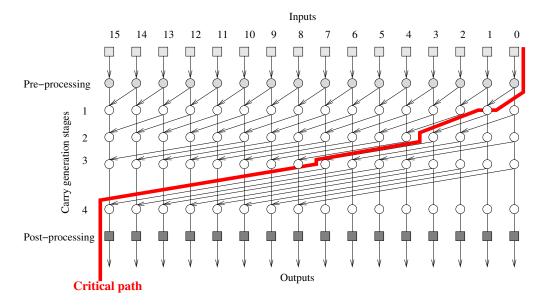

| 37 | Parallel-prefix graph of a 16-bit planar Kogge-Stone adder                                                                                                                                                                                                                                     | 69 |

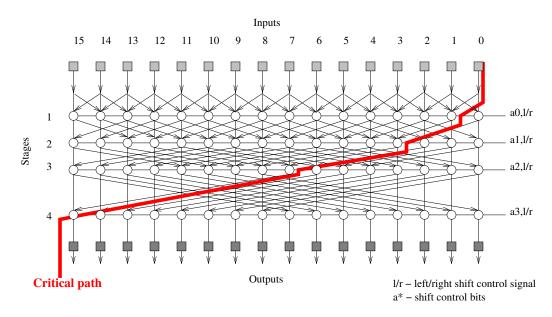

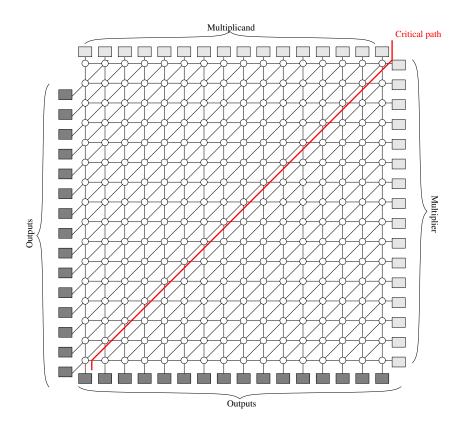

| 38 | Planar implementation of a 16-bit barrel shifter                                                                                                                                                                                                                                               | 69 |

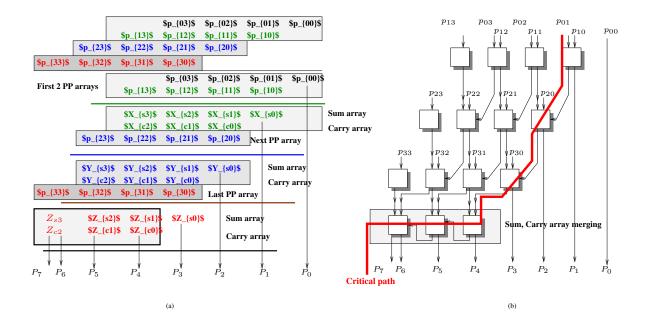

| 39 | Carry-save array (CSA) (a) multiplier algorithm (b) design (critical path high-<br>lighted).                                                                                                                                                                                                   | 70 |

| 40 | Planar graph of a 16-bit carry-save array multiplier                                                                                                                                                                                                                                           | 72 |

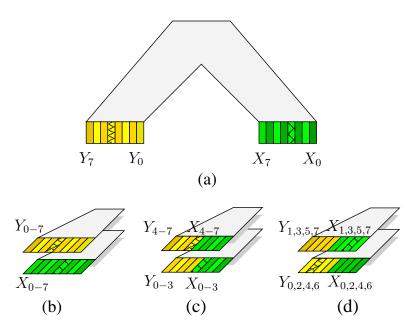

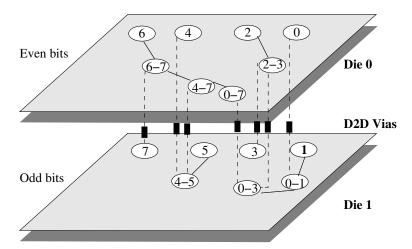

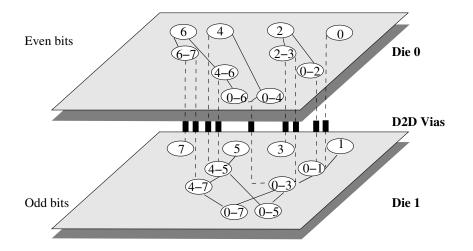

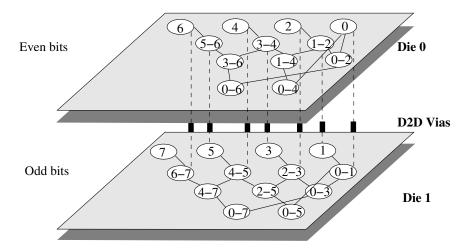

| 41 | (a) An 8-bit planar adder circuit (b) input-partitioned (c) significance-partitioned (d) odd-even partitioned.                                                                                                                                                                                 | 72 |

| 42 | Carry generation graph of an 8-bit significance-partitioned 3D Brent-Kung adder                                                                                                                                                                   | 74      |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 43 | Carry generation graph of an 8-bit odd-even partitioned 3D Brent-Kung adder                                                                                                                                                                       | 74      |

| 44 | Carry generation graph of an 8-bit odd-even partitioned 3D Sklansky adder $\ .$                                                                                                                                                                   | 75      |

| 45 | <b>Carry generation graph of an 8-bit odd-even partitioned 3D Kogge-Stone adder</b> 75                                                                                                                                                            |         |

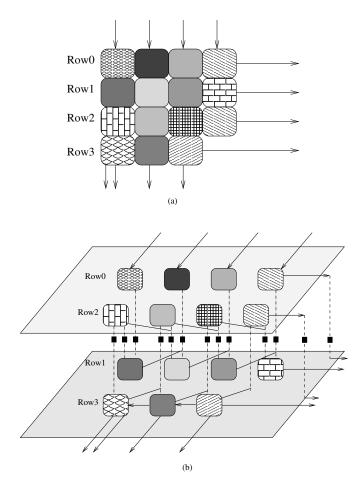

| 46 | (a) Processing nodes and input/output ports of a planar $4 \times 4$ multiplier array (wires within the array not shown for clarity) (b) $4 \times 4$ 3D-integrated carry-save array (CSA) multiplier with the rows partitioned on different die. | 77      |

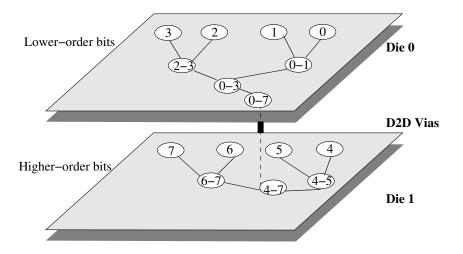

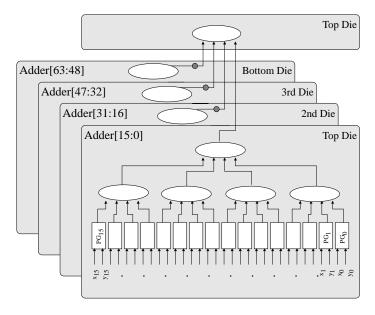

| 47 | Significance partitioned 3D BK adder using a 4-die stack                                                                                                                                                                                          | 77      |

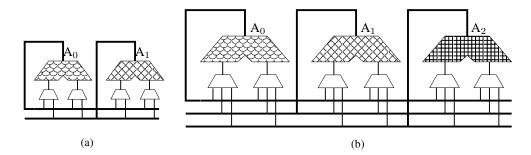

| 48 | Bypass wiring complexity (a) Issue-width $IW = 2$ (b) $IW = 3$                                                                                                                                                                                    | 78      |

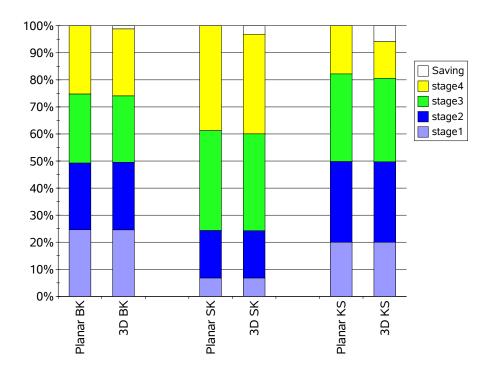

| 49 | Latency distributions and savings for various 64-bit adders.                                                                                                                                                                                      | 81      |

| 50 | Latency for 4-die-stacked 3D implementations of various adders.                                                                                                                                                                                   | 82      |

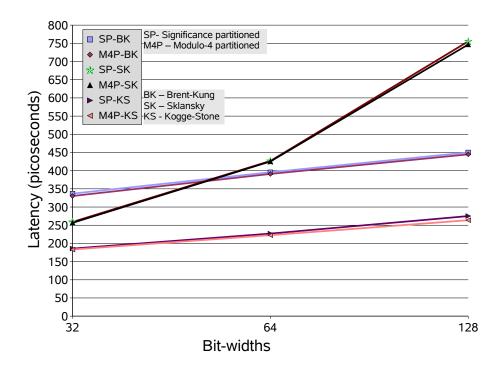

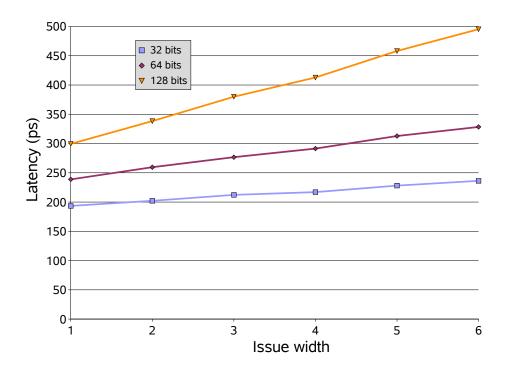

| 51 | Latency versus issue width for the 64-bit planar KS adder.                                                                                                                                                                                        | 84      |

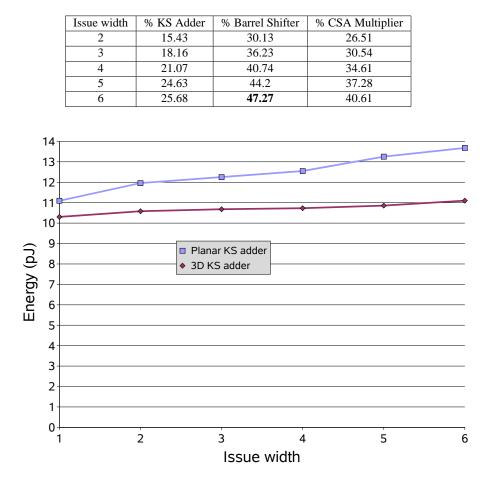

| 52 | Energy comparison of the 64-bit planar and the 64-bit 3D-integrated KS adder circuits with increasing issue-widths.                                                                                                                               | 85      |

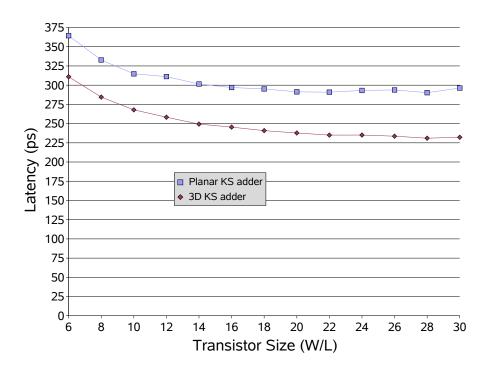

| 53 | Latency versus transistor sizing for the planar and the 3D-integrated KS adder circuits (64-bit, 4-wide issue).                                                                                                                                   | 86      |

| 54 | Effect of transistor sizing on the energy consumption of 64-bit, planar and 3D-<br>integrated KS adders.                                                                                                                                          | 87      |

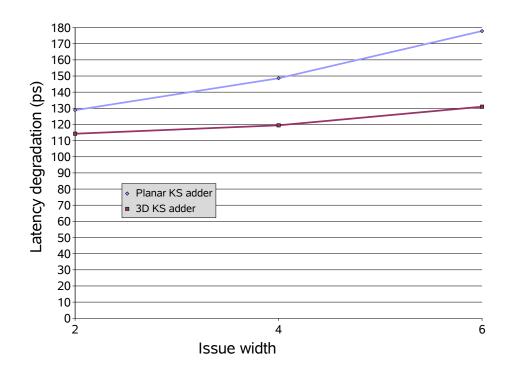

| 55 | Latency degradation of the planar and the 3D KS adder circuits due to tem-<br>perature increase from 25C to 100C.                                                                                                                                 | 88      |

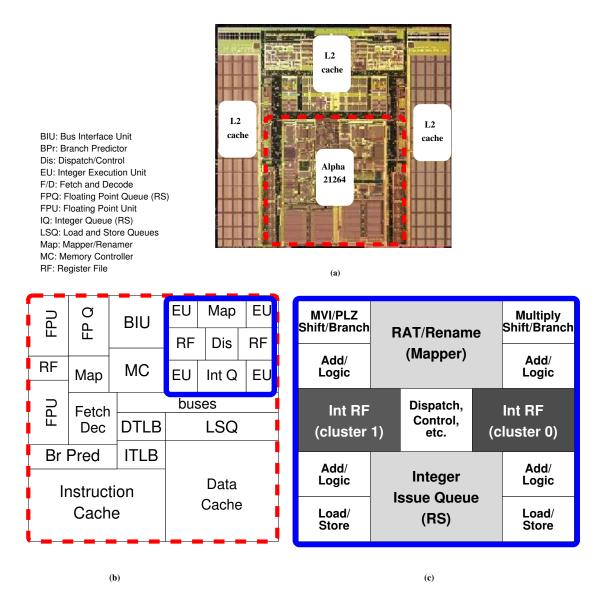

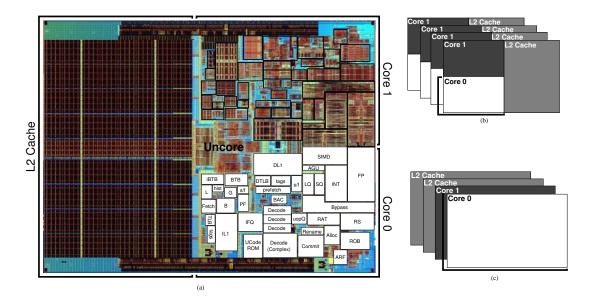

| 56 | Baseline planar processor (a) Die photograph and floorplan of the Alpha 21364 [49<br>The floorplan of (b) the 21264 core [71], and (c) Our floorplan of the 21264 in-<br>teger execution core (EBox).                                             | ]<br>95 |

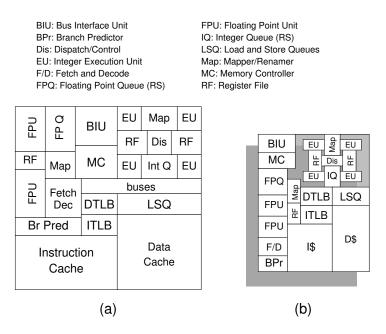

| 57 | (a) Our baseline planar floorplan for the 21364 core, L2 cache not shown, (b) a compacted 3D-integrated 2-die-stacked floorplan.                                                                                                                  | 96      |

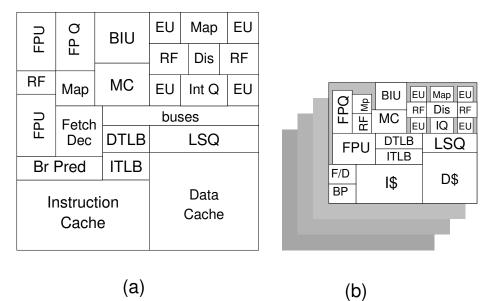

| 58 | (a) Our baseline planar floorplan for the 21364 core, L2 cache not shown, (b) a compacted 3D-integrated 4-die-stacked floorplan.                                                                                                                  | 98      |

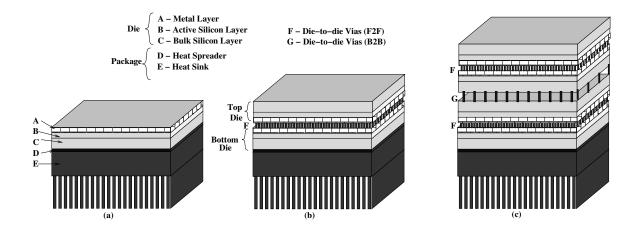

| 59 | (a) A planar integrated circuit (b) A 2-die-stacked 3D-integrated circuit (c) A<br>4-die-stacked 3D-integrated circuit (Figures not to scale)                                                                                                     | 100     |

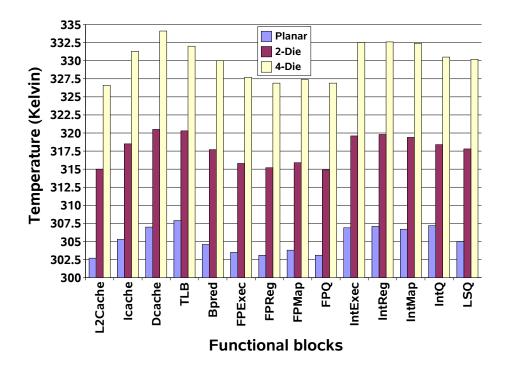

| 60 | Temperatures of components on the planar and the 3D-integrated processors                                                                                                                                                                         | 104     |

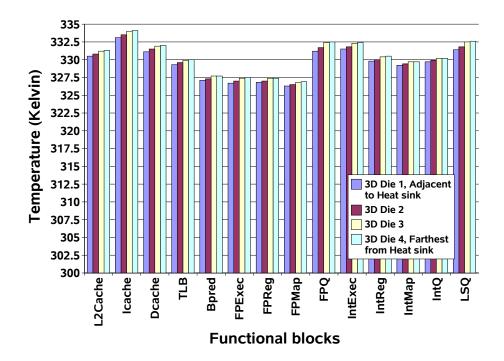

| 61 | Temperatures on each of the four die on a 4-die-stacked 3D processor                                                                                                                                                                              | 105     |

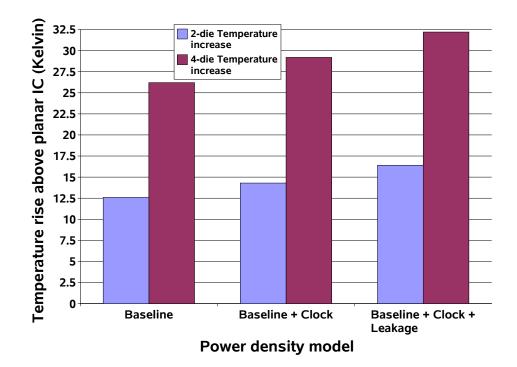

| 62 | Maximum temperature increase with clock and leakage power modeling                                                                                                                                                                                | 106     |

| 63 | (a) Floorplan for the baseline planar processor. (b) 4-die-stacked Thermal Herding 3D processor, and (c) 4-die-stacked coarse-grained 3D processor, (Not to scale)                                                                                                                 | 110 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

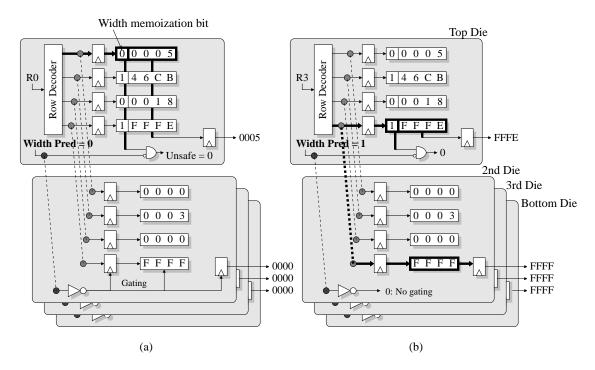

| 64 | Thermal Herding in register files: examples where (a) a low-width value requires access to only the top die, and (b) a full-width value requires access to all four die.                                                                                                           | 112 |

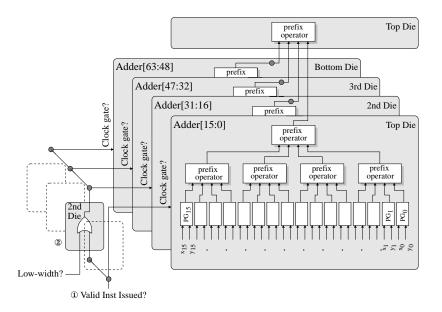

| 65 | Thermal Herding in an integer adder with the most active (lower order) placed<br>on the top die                                                                                                                                                                                    | 114 |

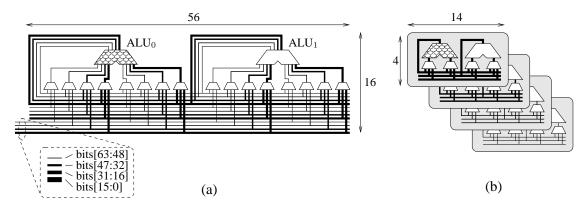

| 66 | (a) A planar bypass network with a register file path and two ALU outputs, and (b) the equivalent 3D bypass network.                                                                                                                                                               | 115 |

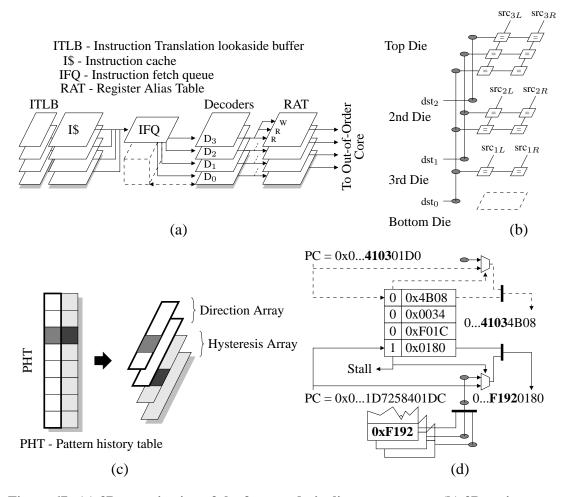

| 67 | (a) 3D organization of the front-end pipeline components, (b) 3D register re-<br>name intra-group dependency checking logic, (c) branch predictor saturating<br>counter array partitioned into two separate 3D sub-tables, and (d) Thermal<br>Herding in the branch target buffer. | 118 |

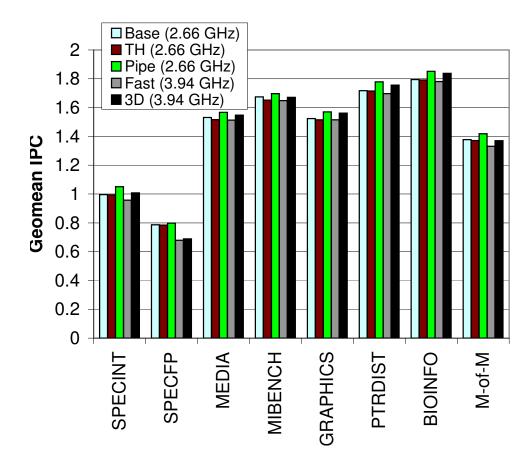

| 68 | IPC results of the planar and the 3D processors. M-of-M is the "mean of means" (geometric mean across all benchmark groups).                                                                                                                                                       | 125 |

| 69 | Performance impact of our Thermal Herding 3D techniques (a) throughput in instructions per nanosecond, and (b) overall performance speedup. M-of-M is the "mean of means".                                                                                                         | 126 |

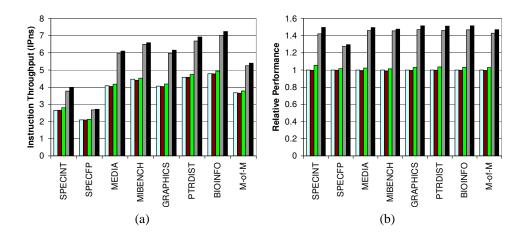

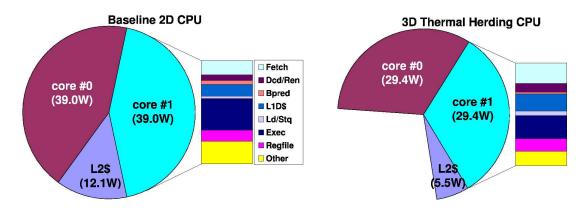

| 70 | Power consumption distribution (Mpeg2 encoding/MediaBench) of the (a) base-<br>line planar processor, and (b) our Thermal Herding 3D processor.                                                                                                                                    | 127 |

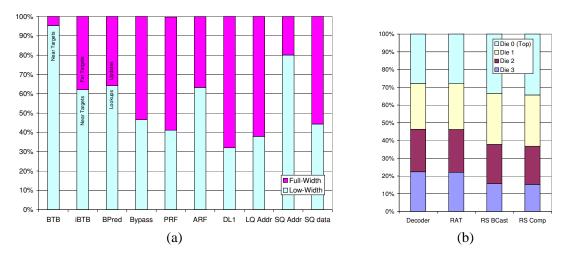

| 71 | (a) Distribution of full-width versus low-width accesses of various components,<br>and (b) per-die distribution of activity.                                                                                                                                                       | 129 |

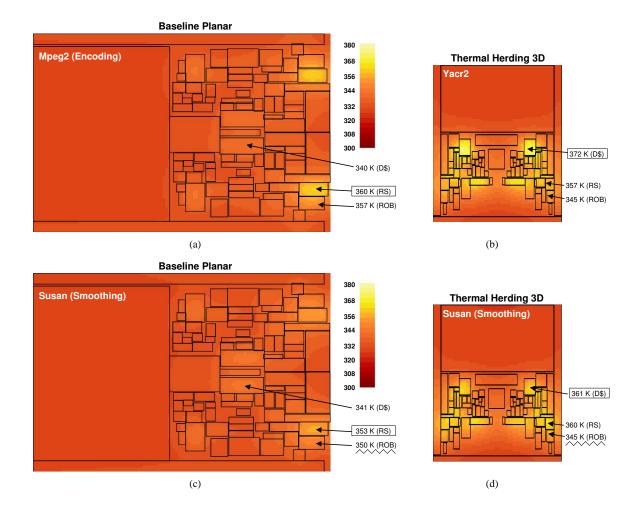

| 72 | Worst-case thermal plots of (a) the baseline planar processor, and (b) the Ther-<br>mal Herding 3D processor. (c-d) Thermal plots of the planar and the Thermal<br>Herding 3D processors for the Susan benchmark from MiBench. Boxes indi-<br>cate hottest blocks.                 | 130 |

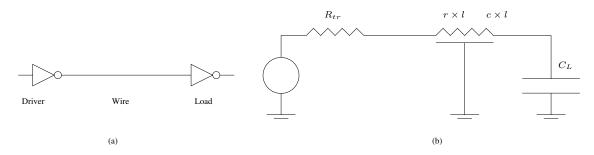

| 73 | (a) Circuit (b) Circuit electrical model.                                                                                                                                                                                                                                          | 137 |

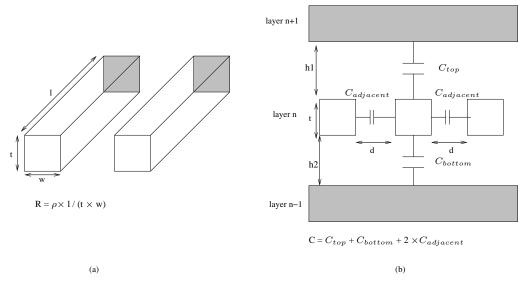

| 74 | Interconnect layer model.                                                                                                                                                                                                                                                          | 138 |

### SUMMARY

Thesis statement: 3D-integration technology provides simultaneous performance and power benefits to build high-performance microprocessors, while keeping the worst-case temperature under control.

The main contribution of this dissertation is the demonstration of the impact of a new emerging technology called 3D-integration technology on conventional high-performance microprocessors. 3D-integration technology stacks active devices in the vertical dimension in addition to the conventional horizontal dimension. The additional degree of connectivity in the vertical dimension enables circuit designers to replace long horizontal wires with short vertical interconnects, thus reducing delay, power consumption, and area.

To adapt planar microarchitectures to 3D-integrated designs, we study several building blocks that together comprise a substantial portion of a processor's total transistor count. In particular, we focus our attention on three basic circuit classes: static random access memory (SRAM) circuits (e.g., caches, register files), associative/CAM logic circuits (e.g., instruction schedulers, load/store queues), and data processing circuits (e.g., adders, shifters, multipliers) in conventional high-performance processors. We propose 2-die-stacked and 4-die-stacked 3D-integrated circuits and demonstrate different designs to deal with the constraints of the conventional planar technology.

Based on the data and the insights gained from the 3D-integrated circuits, we propose highperformance 3D-integrated microprocessors and evaluate the impact on performance, power, and temperature. We propose 3D-integrated microprocessor designs based on the Alpha architecture and demonstrate two different approaches to improve performance: clock speed (3D-integrated processors with identical microarchitectural configurations as the corresponding planar processor run at a higher clock frequency), and IPC (3D-integrated processors accommodate larger-sized modules than the planar processors for the same frequency). These processors demonstrate the simultaneous benefits of the 3D-integration and highlight the power density and thermal issues related to the 3D-integration technology.

Next, we propose 3D-integrated microprocessor designs based on the Intel Core microarchitecture. We propose novel microarchitectural techniques based on significance partitioning and data-width locality to effectively address the challenges of power density and temperature. We demonstrate that our microarchitecture-level techniques can effectively control the power density and temperature issues in the 3D-integrated processors.

The 3D-integrated processors provide a significant performance benefit over the planar processors while simultaneously reducing the total power. The simultaneous benefits in multiple objectives make 3D-integration a highly desirable technology for use in building future microprocessors. One of the key contributions of this dissertation is the temperature analysis that shows that the worst-case temperatures on the 3D-integrated processors can be effectively controlled using microarchitecture-level techniques. The 3D-integration technology may extend the applicability of Moore's law for a few more technology generations.

# Part I

"A beginning is the time for taking the most delicate care that the balances are correct."

- Frank Herbert, Dune, 1965.

## **CHAPTER I**

## INTRODUCTION

#### 1.1 Motivation

Relentless technology scaling has posed some new challenges to the semiconductor industry. Some of the technology challenges in the modern era include poor scaling of interconnect delays [18, 122], increasing power consumption [22, 138], and manufacturing challenges [64, 93, 150, 19]. The semiconductor industry must overcome such challenges to keep pace with Moore's law [102] and industry projections [64, 129]. 3D-integration technology is a new technology that has the potential to address many of the challenges facing the semiconductor industry. In a conventional planar (2D) technology, floorplanning and layout constraints may force two connected circuits to be physically separated, thus requiring global wires for communication. In a 3D organization, these circuits may be stacked on top of each other, thus replacing long global wires with short vertical interconnects. The 3D interconnects may be realized at different levels of the design hierarchy: at the package level (3D system-on-a-package) [84], at the chip level (3D system-on-a-chip) [77], and at the circuit level (3D integrated circuit or 3D IC) [37].

3D integration provides increased device density, reduced latency, and lower power [120, 109, 148, 113, 159, 110, 157, 112]. Each transistor can access a greater number of adjacent transistors (due to vertical connectivity) leading to higher bandwidth [67]. The relative benefits of the 3D-integration technology will increase in future technology generations, making it a very attractive option for future designs. There has recently been a great deal of interest in 3D-integrated circuits. Prior research includes studies on 3D-integrated caches [120, 109, 148, 95, 14], 3D-integrated register files [111], 3D-integrated arithmetic units [95, 112, 154, 114], 3D-integrated CAM circuits [110, 157], clocking schemes for 3D-integrated circuits [101], 3D-integrated processors [13, 157, 90, 88, 115, 105, 72], 3D-integrated systems-on-a-chip [39, 118], 3D-integrated FPGAs [86, 1, 85] and design automation tools for 3D-integrated designs [27, 32, 36, 45, 118, 157].

The microprocessor industry is evaluating the 3D-integration technology for feasibility and applicability [13, 120, 15, 50, 51]. The embedded processor industry is already offering products such as 3D-integrated SRAMs, 3D-integrated DRAMs, and 3D-integrated micro-controllers with SRAMs [145, 125]. 3D-integration also enables heterogeneous technologies (CMOS, DRAM, analog) to be integrated on different layers of a 3D stack, thus providing superior form-factors and greater functionality [88, 72, 128].

The rest of the chapter is organized as follows: Section 1.2 describes some of the current challenges to the semiconductor industry and shows the potential of the 3D-integration technology in addressing these challenges. Section 1.3 provides the background on the 3D-integration technology. Section 1.4 sets up the scope of this dissertation and concludes the chapter.

### 1.2 Current Technology Challenges

#### **1.2.1 Interconnect Delay**

Interconnect delay has become a limiting factor in the integrated circuit performance. In keeping with Moore's law, (1) the transistor sizes decrease, and (2) the transistor switching speeds increase with successive technology scaling generations. The reduced size of the transistor enables higher integration density by providing more transistors in the same area as previous technology generations. The increased switching speed of the transistor enables a higher frequency of operation. The improved integration density and the increased speed together enable higher functionality and consequently higher overall performance of the integrated circuit.

To provide higher functionality, the transistors need to communicate through interconnects, thus increasing the interconnect complexity. Interconnects are required to communicate the clock-, dataand control-signals, and distribute power to the various transistors on an integrated circuit. Unfortunately, the interconnect delays have not improved at the same rate as the transistor delays with technology scaling [18, 122]. The performance improvement gained by transistor scaling may be diminished by the negative effects of interconnect scaling.

Table 1 shows the International Technology Roadmap for Semiconductors (ITRS) projections on delays for three classes of interconnects, namely, local, intermediate, and global interconnects. The interconnect delays continuously increase with technology scaling. As we go from a 65 nm

Table 1: 2006 ITRS projections of interconnect delays for a local interconnect (0.1 mm), intermediate interconnect (1 mm), and global interconnect (10 mm)

| Year of Production                   | 2005 | 2006 | 2007 | 2008  | 2009  | 2010  | 2011  | 2012  | 2013  |

|--------------------------------------|------|------|------|-------|-------|-------|-------|-------|-------|

| Technology (nm)                      | 80   | 70   | 65   | 57    | 50    | 45    | 40    | 36    | 32    |

| Delay (ps) local interconnect        | 44.0 | 61.2 | 76.7 | 104.4 | 138.8 | 179.2 | 239.2 | 285.7 | 345.1 |

| Delay (ps) intermediate interconnect | 355  | 527  | 682  | 1039  | 1413  | 1825  | 2436  | 2784  | 3504  |

| Delay (ps) global interconnect       | 1110 | 1650 | 2090 | 3160  | 4100  | 5230  | 6870  | 7870  | 9770  |

technology to a 32 nm technology, the delays increase by more than  $4 \times$  for each of the local, intermediate, and global interconnects. Thus, the performance of the planar integrated circuit is increasingly limited not by the transistor delay, but rather by the interconnect delay [43, 119, 18, 122]. To ensure the highest performance possible out of the integrated circuit, we need to improve both the resistance and the capacitance of the interconnect.

#### **1.2.2** Power Consumption

Power consumption has become one of the biggest priorities for today's integrated circuits. The total power consumption determines the maximum reliable operating frequency, power-supply sizes, and cooling requirements of the integrated circuit and hence plays a major role in determining its overall performance and reliability. Power consumption depends not only on the technology/circuit parameters (e.g., device sizes, circuit styles, oxide thicknesses) but also on the implementation (e.g., microarchitecture, frequency of operation) [38].

The total power consumption in a CMOS circuit consists of two parts: dynamic power consumption  $P_{dyn}$ , and static power consumption  $P_{stat}$ . The CMOS integrated circuit dissipates dynamic power when the circuit's transistors switch from logic-low to logic-high and vice versa [117]. The dynamic power depends on supply voltage, switching activity of transistors, load capacitance, and frequency of operation. During high-to-low and low-to-high transitions, dynamic power is consumed due to two current flows: (1) switching current flows to/from capacitive loads to charge (or discharge) the loads, (2) short-circuit current flows on the low-impedance path from power supply to ground. Dynamic power continues to increase due to the aggressive pursuing of performance with increasing frequencies and increasing number of transistors.

The CMOS integrated circuit dissipates static power due to leakage currents that flow even while the circuit is inactive. Static power has become a critical issue that gets worse with every new technology generation [64, 123, 55]. Static power is dependent on supply voltage, threshold voltage, and temperature. The reducing supply voltage due to technology scaling requires a corresponding reduction in the threshold voltage. This decrease in the threshold voltage results in an exponential increase in the leakage current. In addition to voltage, static power is dependent on temperature and vice versa. Increasing static power increases the temperature of the integrated circuit, which in turn increases the static power. This creates a leakage-temperature feedback loop that might lead to thermal runaways and cause the circuit to fail in functionality.

#### **1.2.3** Power Density

In addition to the total power, power density is a growing problem in which small, high-activity resources consume a large amount of power, causing hotspots on the processor [157, 13, 113]. Power dissipation can be unevenly distributed in modern microprocessors leading to hotspots with significantly greater temperatures than surrounding regions. Black et al. [13] report the hottest (88 °C) and the coolest spot (59 °C) on a high-performance planar processor with a temperature differential of 29 °C. High temperatures not only degree performance and reduce reliability but also increase static power and can lead to catastrophic failure of circuits. Power density continues to increase with technology generations as clock speeds, switching and leakage currents, and device counts push the limits of cooling mechanisms. Higher temperatures and increasing power densities have brought heat removal and power distribution to the forefront of the problems facing the semiconductor industry.

#### 1.2.4 Manufacturing Process

Apart from the interconnect delay and the power concerns, maintaining the current rate of performance improvement faces increasingly difficult challenges from a manufacturing perspective. Current transistor sizes are already less than the wavelength of light used for photolithography. Advances in optics and shorter wavelength radiation may provide a few more doublings of transistor density [12]. Process variations are becoming increasingly non-deterministic in current and future technology generations. Process variations increase the variance of the circuit delays from their expected (mean) delays, thereby reducing the yields of the integrated circuits [150, 19, 68]. Lithography and etching processes cause variations in gate length (L). Chemical-mechanical-polishing (CMP) processes causes variations in interconnect width and height [93] leading to variations in the interconnect resistance and capacitance. Random dopant fluctuations and poly line-edge-roughness cause threshold voltage variations [152].

## 1.3 Three-dimensional Integration Technology

3D-integration technology [68, 67] greatly reduces the impact of interconnect delays by placing the transistors in stacked layers and providing vertical connectivity. Two functional units connected by a long global wire in a planar circuit can instead be vertically stacked and connected in the third (vertical) dimension, thus drastically reducing the interconnect length. Wire-dominated functional blocks can be stacked on top of themselves to reduce the effects of intra-block wiring. 3D-integration technology provides new ways to design the various processor blocks and even the entire processor microarchitecture. Reducing the amount of interconnect also has a significant impact on power consumption as interconnect power is already estimated to consume about one half of a chip's power [91]. 3D-integration technology provides an alternative means of increasing integration density.

#### **1.3.1** State of the Art in 3D-Integration

This section describes the state of the art in the 3D-integration technology, and outlines the critical parameters.

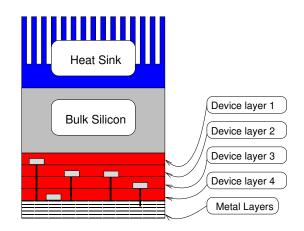

There are currently several proposed methods for vertically integrating multiple circuit layers such as multi-layer buried structures (MLBS) [158, 69] and 3D bonding technologies (e.g., wafer-to-wafer, die-to-wafer, and die-to-die bonding) [76, 104, 121]. Figure 1 shows a multi-layer buried structures (MLBS) 3D design. In the MLBS 3D technology, multiple device layers are successively (sequentially) fabricated in a stacked fashion. Layer-to-layer connections are made from either inter-layer interconnects (vias) or from direct source-drain/source-drain contacts. The advantage of the MLBS technology is that the 3D vias can potentially scale down with the transistor sizes due to the use of local poly-silicon wires for connection. However, the MLBS technology requires extensive changes to the existing manufacturing processes [157].

The 3D bonding technology requires fewer changes in the manufacturing process than the

Figure 1: A MLBS 3D IC with four device layers

MLBS technology [95]. The 3D bonding technology processes the integrated circuits with conventional fabrication processes and provides vertical connectivity between the circuits on stacked layers using *bonding* techniques [104, 121, 65, 76]. The bonding technology could be oxide-tooxide bonding [53], copper-to-copper bonding [13, 104, 121], and dielectric adhesive bonding [53]. In a 3D wafer-bonding technology proposed by Koyanagi et al. [76], a wafer is glued to a supporting material (handle wafer), thinned from the backside by mechanical grinding, and polished to a thickness of a few microns. The thinned wafer is aligned and bonded to another wafer and the handle wafer is removed from the thinned wafer. In another 3D wafer-bonding technology proposed by Lu et al. [65], fully processed wafers (with multilevel on-chip interconnects) are aligned and bonded with a dielectric glue, followed by top-wafer thinning and inter-wafer interconnection. The wafer thinning involves mechanical grinding, chemical mechanical polishing, and wet etching. The advantage of the wafer bonding process proposed by Lu et al. is that it does not require a supporting wafer (handle wafer). Another 3D wafer bonding technology processes the wafers with conventional planar fabrication processes and uses metal vias to bond the planar wafers vertically [13, 104, 121].

In wafer bonding technologies, the yield of the 3D integrated circuit is heavily influenced by the yields of each of the wafers [75]. Thus, wafer-level integration is desirable when the yield of each wafer is very high. 3D integration using die-to-wafer bonding or die-to-die bonding are other promising technologies in which known good dies [73, 11] can be stacked, thus increasing the overall yield. However, wafer-level stacking potentially provides a more cost-effective process compared with die-level stacking [103]. Our proposed designs assume a copper bonding based

Figure 2: A 2-die-stacked 3D integrated-circuit with (a) face-to-face, and (b) face-to-back bonding topologies. (Figures not drawn to scale).

wafer-level stacking technology. We describe the details of the copper bonding 3D technology in Section 1.3.2.

#### 1.3.2 Copper Bonding 3D-Integration Topologies

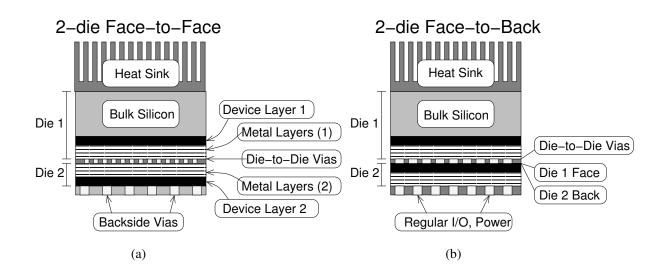

## 1.3.2.1 Two Layer Stacks

Figure 2(a) shows a 3D-integrated circuit using a face-to-face (F2F) wafer-stacking technology with copper metal bonding [13, 104, 121]. The bonding approach of Figure 2(a) involves depositing vias on the top metal layers of each of the two wafers, aligning the two wafers, and bonding them together. Under thermo-compression, the vias fuse together providing both the die-to-die interconnects as well as a physical mechanism to hold the die together. After bonding, one wafer is thinned with chemical-mechanical polishing (CMP) down to  $\sim 10\mu$ m allowing low impedance backside vias to be etched through, which provide input/output and power/ground connections.

Figure 2(b) shows a 3D-integrated circuit using a face-to-back (F2B) bonding topology. The face-to-back bonding requires etching vias through the backside of the silicon (backside vias). The backside vias are challenging to manufacture for two reasons. First, etching through the backsides of the silicon will cause the cross-sectional area and the length of the backside vias to increase (relative to the face-to-face via). Second, the backside vias must pass through the active region of the silicon die, which may disrupt the layout of transistors. Hence, the face-to-back bonding

Figure 3: A 4-die-stacked 3D integrated circuit with (a) face-to-back , and (b) alternating face-to-face bonding topologies (Figures not to scale).

topology may not be able to provide as dense of a via interface as the F2F bonding topology.

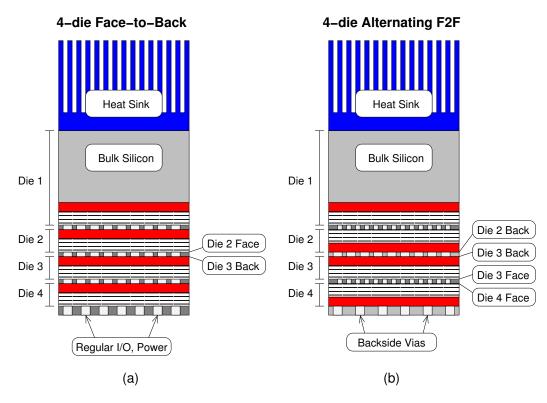

#### 1.3.2.2 Stacks with More than Two Layers

The 3D-integration technology will likely extend beyond stacking two layers to continue scaling performance and integration density. There are many organizations for integrating multiple layers in a 3D stack using both face-to-face (F2F) and backside vias. The bonding process may be repeated in combinations of face-to-face, face-to-back and back-to-back organizations.

Figure 3(a) shows a 4-die face-to-back (F2B) bonding topology. The advantage of the F2B bonding topology is the uniformity and repeatability of the fabrication process since each additional layer requires identical processing steps. Figure 3(b) shows a 4-die-stack that combines two F2F 2-die stacks with a back-to-back (B2B) interface between the pairs of die. After stacking two die in a face-to-face organization, coarser (less dense) die-to-die vias are required at the backside interface. The alternating F2F topology shown in Figure 3(b) may be desirable because the microarchitects and circuits designers can use the denser F2F vias at half of the die-to-die interfaces.

#### **1.3.3 Die-to-Die Vias**

The die-to-die (d2d) vias are perhaps one of the most critical 3D design parameters. The trade-offs between the different organizations have to do with the quality and pitch of the vias implementable at the different interfaces, and whether the vias interrupt the device layer. The pitch and latency of the d2d vias dictate the granularity at which a circuit can be partitioned across the different die.

The distance between the top metal layers on the adjacent die is very small [140, 121], and the size of the d2d vias is of the same order as the top level metal [39]. The thinning of the die reduces the distance that a d2d via must cross to connect the die. As mentioned earlier, the individual die are thinned to  $\sim 10\mu$ m, and in a F2F organization the d2d vias only need to cross the distance separating the two top metal layers. Depending on the technology, the d2d via height may be  $<5\mu$ m to  $\sim 20\mu$ m [36]. A d2d via is much smaller than the planar interconnect it replaces, and thus reduces both the resistance (R) and the capacitance (C). The signal propagation delay between the die is drastically reduced due to the reduced interconnect RC characteristics of the d2d vias. The delay to drive a signal through a d2d via from one die to another is less than one fan-out-of-four (FO4) delay [109], which makes the cost of cross-die communication similar to a short length of traditional metal. Note that the interface between the two d2d vias may present a disruption in the copper lattice structure, thus potentially increasing contact resistance.

Current implementations of the 3D-integrated designs support d2d via sizes from  $\sim 3\mu$ m to 10 $\mu$ m [36]. The embedded industry has reported manufacturing d2d vias of size 2.4 $\mu$ m and expects second-generation d2d vias of size 1.46 $\mu$ m [51]. As alignment technologies continue to improve, via sizes smaller than 1 $\mu$ m may soon be practical. As a point of reference, a recent study on the 3D-integrated caches pointed out that a state of the art 6T SRAM cell takes up 0.7 $\mu$ m<sup>2</sup> (in a 65nm technology) [148] which provides a d2d via density on the order of two d2d vias for every three SRAM cells [109]. IBM has announced d2d vias with a size of 0.2 $\mu$ m [82]. The backside vias require etching through the bulk silicon substrate and as a result require larger structures in the current technology. The embedded processor industry currently manufactures backside vias of size 6 $\mu$ m, and has reported that the next technology generation will provide backside vias <4 $\mu$ m [51].

Apart from providing a dense d2d via interconnect, the F2F organization in Figure 2(a) does

(a)

Figure 4: (a) Placement of F2F vias may not affect transistor placement. (b) Placement of backside vias interrupt transistor placement. (c) Backside vias may disrupt the crystal structure of the device layer degrading performance.

not require the vias to disrupt the active device layer. Figure 4(a) shows how the d2d vias can be built above the top-level metal so that they do not directly affect the floorplanning of the underlying logic. On the other hand, Figure 4(b) shows te bakside vias passing through the device layer which implies that space must be explicitly allocated for these vias. Etching the vias may also disrupt the local crystal structure of the silicon substrate as shown in Figure 4(c). This in turn may degrade the performance of transistors that are adjacent to the backside vias. To guard against this effect, one could consider the performance degradation of the transistors around these backside vias and limit the usage of such transistors to only non-critical path circuits, or define a "keep-out" region and avoid placing the transistors in that region. Note that Morrow et al. [103] have tested individual transistors to preserve their electrical characteristics after bonding, thinning, and etching backside vias.

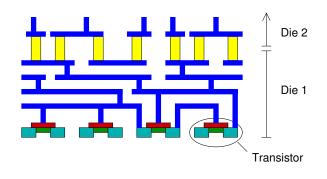

#### 1.3.4 Benefits of 3D-Integration

The 3D-integration reduces interconnect delays because of the additional degree of routability in the vertical dimension. The 3D-integrated circuit designs increase the number of transistors that can be accessed in a single clock cycle. Figure 5(a) shows a planar circuit with a global wire connecting two blocks. Figure 5(b) shows a 3D implementation of the planar circuit where the planar global interconnect has been replaced by a short die-to-die (d2d) via. The additional degree of freedom in the vertical dimension enables a reduction in the interconnect requirements for connectivity.

By shortening the wire lengths, the 3D-integrated circuit can have a dramatic impact not only on improving the performance but also in reducing the power consumption. The power reduction comes from the reduced resistances and capacitances of the shorter wires as well as the reduced repeaters on the global wires. The drastic reduction in wire-length reduces the total power consumption of the 3D-integrated circuit as compared to the planar circuit.

The 3D-integration technology also enables a reduction of circuit footprints as shown in Figure 5. The 3D-integrated design has a reduced footprint compared to the planar design. The reduction in the footprint enables reduced form factor. Reduced form factor is an attractive option to the embedded processor industry, where the market trends continue toward miniaturized products for

Figure 5: Benefits of 3D technology (a) Planar circuit (b) 3D-integrated circuit.

mobile users. This reduction in the footprint has implications in the yield of the integrated circuits. The smaller the footprints, the larger the number of die that can be obtained out of a certain sized wafer, and hence, the higher the yield. Figure 6(a) shows a wafer that yields two large planar die out of four (50% yield) due to manufacturing defects at two spots on the wafer. Figure 6(b) shows an identical wafer with the defects located at the same spots, which yields 23 small die out of 26 die (88% yield). Assuming each of the small die contains a quarter of the planar circuit, we need to stack four such die as shown in Figure 6(c) to obtain the complete 3D-integrated circuit. When the wafers are aligned and bonded, defective die on each wafer may align with good die on the other wafers causing a loss of overall yield. In the worst case, the 3D-integration yields fourteen 4-die-stacked 3D integrated circuits, while the planar fabrication provides eight (2×4) functional planar integrated circuits out of the same number (four) of wafers. Note that this is a qualitative argument that demonstrates that the yields of the 3D-integrated circuits requires further careful consideration and research. We consider the yield analysis to be outside the scope of this dissertation.

Another benefit of the 3D-integration technology is the ability to exploit best-of-breed technologies for each layer of the die-stack. Rather than optimizing a single process technology to fabricate both memory and logic elements on the same die, logic and memory processes can be optimized

Figure 6: Wafer with (a) planar die (b) reduced footprint die (due to 3D-integration) (c) In wafer bonding, defective die may stack on good die, thus reducing yield.

individually and stacked using 3D-integration [88, 72, 128].

### **1.3.5** Some Challenges to 3D-Integration

#### 1.3.5.1 Power Density

The 3D-integration technology increases the number of transistors in a volume, which may exacerbate the thermal profiles by increasing the thermal resistance [113]. Additionally, the 3D-integration reduces the footprint of the die, hence reducing the contact area between the heat sink and the die [115, 13]. The reduction in the contact area decreases the ability of the heat sink to remove heat from the die. Heat degrades performance, reduces reliability and increases static power. The increased power density may require more aggressive cooling mechanisms [108], adding manufacturing cost.

By using techniques such as wafer-thinning [76, 65] and thermal vias [46], we can reduce thermal resistances in the 3D-integrated circuits. Using state-of-the-art cooling solutions [108] such as direct liquid cooling can provide better cooling capability. The microarchitecture can also influence the thermal characteristics. In Part III (Chapter 6) of this dissertation, we describe some of the microarchitectural techniques we have proposed to address the thermal challenge in high-performance 3D-integrated microprocessors.

#### 1.3.5.2 Power Integrity

Power integrity is already a reliability concern in the semiconductor industry [100, 99]. The 3Dintegration may aggravate some of the power integrity issues. The smaller footprints of the 3Dintegrated circuits reduce the area available for power distribution and result in lower pin counts for power supply and ground. In addition to the reduced pin counts, stacking may also cause multiple circuits to draw power from the same pins thus causing abrupt changes in current demands. In highspeed integrated circuits, such abrupt changes in current demands may lead to reliability issues due to inductive (Ldi/dt) noise in the power supply network [100, 99]. Also, some of the die may be further from the decoupling capacitors in 3D-integrated circuits, thus increasing the inductive noise [98, 156]. Hence, power integrity issues may pose a significant challenge to the performance and reliability of the 3D-integrated systems [97].

There has been some recent work in addressing the power integrity issues with respect to the 3Dintegrated circuits. Researchers have proposed physical design [97] and microarchitecture design techniques [100] to mitigate the power integrity concerns related to the 3D-integrated circuits. More research is required to address the power integrity issues with special focus on the 3D-integrated circuits.

#### 1.3.5.3 Design Automation Tools

There is a pressing need for electronic design automation (EDA) tools and methodologies to develop new architectures using the 3D-integration technology. Xie et al. [157] have identified two different categories of design tools essential for 3D microarchitecture designs: early design analysis tools and physical design tools.

There has been a great deal of on-going research in the academic community in the 3D EDA tools. Researchers have proposed different algorithms for early-design-phase automated microarchitectural floorplanning tools [56, 31, 58]. Given a microarchitectural description of a processor (blocks, sizes, interconnections), the floorplanning algorithm devises a 3D organization to optimize a given objective (e.g., performance, power, area, wirelength). Related 3D CAD/EDA work includes automated via placement in 3D-integrated circuits for heat dissipation [33], automated routing in 3D-integrated circuits [32], 3D power grid design, and 3D decoupling capacitor insertion for controlling power supply (di/dt) noise in the 3D-integrated circuits [98].

### 1.3.5.4 Testing

Testing is another substantial challenge in the 3D-integrated circuit designs. Before bonding the wafers, the circuit on each wafer may exist in an incomplete state depending on the partitioning granularity [81], hence posing a challenge to the testing. Lewis et al. [81] have identified the testing challenges to the 3D-integrated designs and present a technique to enable pre-bond testability at a minimal area cost.

Some 3D-integrated design approaches provide an opportunity to test and debug parts prior to assembly [73, 11]. The ability to integrate proven parts shortens the design testing time. The use of redundancy techniques, dynamic repair, and real-time fault detection/isolation may enable low-cost, high-volume 3D-integrated circuits.

#### 1.3.5.5 Manufacturing Cost

3D integration may increase the cost of manufacturing because of the additional processing steps. Multiple wafers have to be manufactured for a given integrated circuit thus requiring multiple masks. After fabrication, the wafers need to be polished and planarized, have their d2d interconnects deposited, thinned and then bonded. Apart from the planar fabrication processes, new technologies such as precision alignment systems and bonding apparatus are needed to successfully build 3Dintegrated circuits. The 3D-integration may also affect yields because an *n*-die stack can be rendered inoperational by a single bad die, even if the other n - 1 are fine (refer to Section 1.3.4).

A full analysis of the economic viability of the 3D-integration is beyond the scope of this dissertation. An open research question is to determine and evaluate the benefits that can be obtained from this new technology. Note that, some of the additional costs of the 3D-integration may be partially recovered. It is possible to share global routing and/or clock layers between multiple die (e.g., run the global portion of the clock tree on only one die, and use local clock trees on each die to complete the clock distribution), thus reducing the number of metal layers required for clock distribution. Each individual die in a 3D-stacked processor has a smaller footprint than in a planar/2D implementation, which in turn may enable more effective packing of the rectangular die on a circular wafer as shown in Figure 6(b).

## 1.4 Scope of This Dissertation

3D-integration technology has the potential to address many of the challenges facing the semiconductor industry. The increased device density and the ability to place and route in the vertical dimension provide new opportunities for microarchitecture design.

The thesis of this dissertation is that the 3D-integration provides simultaneous performance and power benefits to build high-performance microprocessors, while keeping the worst-case temperature under control.

We support this thesis by studying the microarchitectural impact of the 3D-integration technology on the design of high-performance processors and quantifying the benefits. Note that the results presented in this dissertation represent a *conservative estimate* of the value of the 3D-integration technology. We start with conventional planar microarchitectures and adapt to the 3D-integration technology, whereas a microarchitecture explicitly designed to target the 3D-integration may likely provide more benefits.