# **Robust Low-Power Signal Processing and Communication Algorithms**

A Thesis Presented to The Academic Faculty

by

### Muhammad Mudassar Nisar

In partial fulfillment of the Requirement for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology Atlanta, GA 30332

May 2010

## **Robust Low-Power Signal Processing and Communication Algorithms**

Approved by:

Dr. Abhijit Chatterjee, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Sudhakar Yalamanchili School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Hsien-Hsin Sean Lee School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Saibal Mukhopadhyay School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Santosh Pande College of Computing Georgia Institute of Technology

Date Approved: December 07, 2009.

Dedicated to my loving parents, Dr. Nisar Ahmed and Shamim Akhtar.

## ACKNOWLEDGMENTS

I would like to express my sincerest gratitude to Prof. Abhijit Chatterjee for accepting me in his research group; his continuous support and guidance during the course of my research. He has been a source of great inspiration and motivation. His guidance, not just limited to academic research, has been invaluable for me during these years. I also take the opportunity to thank faculty members, Prof. Sudhakar Yalamanchili, Prof. Hsien-Hsin Sean Lee, Prof. Gabriel Rincon-Mora, Prof. Saibal Mukhopadhyay, and Prof. Santosh Pande for agreeing to serve on my proposal and dissertation committees and their valuable recommendations on my work.

I would like to thank Semiconductor Research Corporation (SRC), Giga Scale Research Center (GSRC), and National Science Foundation (NSF) for the support during various stages of my graduate studies at Georgia Tech. I sincerely appreciate the professional and personal support from my colleagues in our research group over the years. I thank Raj, Maryam, Vishwa, Jayaram, Shayam, Shreyas, Sehun, Hyun, and Deuk for their wonderful company.

I am also thankful to my wife Anmber Mudassar for her motivation to complete this dissertation. I am extremely grateful to my parents, brothers, and sisters for their unwavering and continuous support during the course of my life. My family has been the source of great inspiration for me and I am greatly indebted to them for their love and encouragement.

# **Table of Contents**

| ACKNOWLEDGEMENTS                                                   | IV   |

|--------------------------------------------------------------------|------|

| LIST OF TABLES                                                     | VII  |

| LIST OF FIGURES                                                    | VIII |

| SUMMARY                                                            | XI   |

| CHAPTER 1 - INTRODUCTION                                           |      |

| 1.1 MOTIVATION.                                                    |      |

| 1.1 MOTIVATION                                                     |      |

| CHAPTER 2 - NANO-CMOS CHALLENGES: SOFT ERRORS, POWER, PROCESS      |      |

| VARIATIONS                                                         | 5    |

| 2.1 SOFT/TRANSIENT ERRORS                                          | 5    |

| 2.1.1 Soft Error Resilient Design                                  |      |

| 2.2 POWER CONSUMPTION IN DIGITAL CIRCUITS                          | 9    |

| 2.2.1 Power Reduction Techniques                                   | 14   |

| 2.2.2 Power/Performance Adaptive Design                            |      |

| 2.3 PROCESS VARIATIONS                                             |      |

| 2.3.1 Process Variation Tolerant Circuit Design                    |      |

| 2.3.1.1 Design-Level Variation Tolerance                           |      |

| 2.3.1.2 Post-Manufacture Variation Tolerance                       | 23   |

| CHAPTER 3 - SYSTEM DESIGN MODELING                                 | 25   |

| 3.1 OFDM TRX POWER CONSUMPTION                                     | 29   |

| 3.2 SIMULATION SETUP                                               |      |

| 3.2.1 Channel Modeling                                             |      |

| 3.2.2 Baseband TRX Model                                           |      |

| 3.3 FPGA IMPLEMENTATION                                            | 32   |

| CHAPTER 4 - GUIDED PROBABILISTIC COMPENSATION FOR LOW-POWER        |      |

| FILTERS                                                            | 35   |

| 4.1 Overview                                                       | 36   |

| 4.2 STATE VARIABLE SYSTEM REPRESENTATION                           | 39   |

| 4.3 LINEAR DIGITAL SYSTEM AND CHECKSUM-BASED ERROR DETECTION       | 41   |

| 4.3.1 Operator and State Gain – Gain Matrix                        | 43   |

| 4.4 GUIDED COMPENSATION FOR LOW-POWER OPERATION                    | 45   |

| 4.4.1 Shadow-Latches                                               |      |

| 4.4.2 Guided Error Compensation                                    |      |

| 4.4.3 Guided Error Compensation for Shared Hardware Implementation |      |

| 4.4.4 Low Precision Checksum Effects                               |      |

| 4.4.5 Dynamic Supply Voltage Control                               |      |

| 4.5 SIMULATION SETUP                                               |      |

| 4.5.1 Simulation Results at Fixed Voltages                         |      |

| 4.5.2 Simulation Results with DVOS                                 |      |

| 4.5.3 Power Savings and Area Overhead.                             |      |

| 4.6 CONCLUDING REMARKS                                             | 04   |

| CHAPTER 5 - SOFT ERROR MITIGATION AND LOW-POWER OPERATION OF NON-LINEAR FILTERS    |     |

|------------------------------------------------------------------------------------|-----|

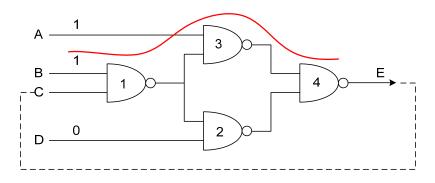

| 5.1 NON-LINEAR CIRCUITS – CHECKSUM BASED ERROR DETECTION                           | 66  |

| 5.2 NON-LINEAR CIRCUITS - PROBABILISTIC SOFT ERROR COMPENSATION                    | 70  |

| 5.2.1 Training Phase – Correction Vector Calculation                               | 73  |

| 5.3 GUIDED PROBABILISTIC ERROR COMPENSATION FOR LOW-POWER                          |     |

| 5.4 EVALUATION                                                                     | 76  |

| 5.4.1 Simulation setup                                                             |     |

| 5.4.2 Probabilistic Compensation                                                   |     |

| 5.4.3 Guided Probabilistic Compensation                                            |     |

| 5.5 CONCLUDING REMARKS                                                             |     |

| CHAPTER 6 - CHANNEL AND VARIATION ADAPTIVE LOW-POWER BASEBAN<br>PROCESSING         |     |

| 6.1 Prior Work                                                                     | 85  |

| 6.1.1 Tuneable Wordlength                                                          |     |

| 6.1.2 Dynamic Voltage Scaling in a Pipeline Architecture                           |     |

| 6.1.3 Power-Frequency Management                                                   |     |

| 6.1.4 Voltage Overscaling and Algorithmic Noise Tolerance                          |     |

| 6.2 MOTIVATION AND OVERVIEW                                                        |     |

| 6.3 CHANNEL DRIVEN ADAPTATION TECHNIQUES FOR LOW-POWER                             | 91  |

| 6.3.1 Locus Based Channel and Variation Tolerant Low-Power Processing              | 91  |

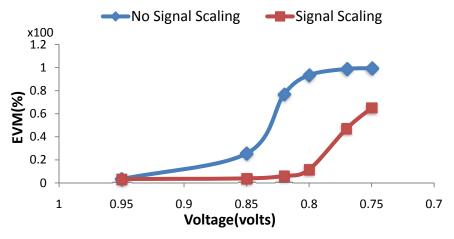

| 6.3.1.1 Adaptation Metric – EVM                                                    | 93  |

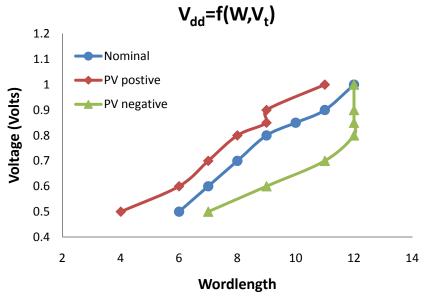

| 6.3.1.2 Input Signal Scaling and Voltage Adjustment                                |     |

| 6.3.1.3 Signal Scaling and Supply Voltage Control                                  |     |

| 6.3.1.4 Effects of Process Variations                                              |     |

| 6.3.1.5 Path Oscillation Timing Tests (POTTs)                                      |     |

| 6.3.1.6 Loci Based Operation: System Design and Characterization Phase             |     |

| 6.3.1.7 Evaluation                                                                 |     |

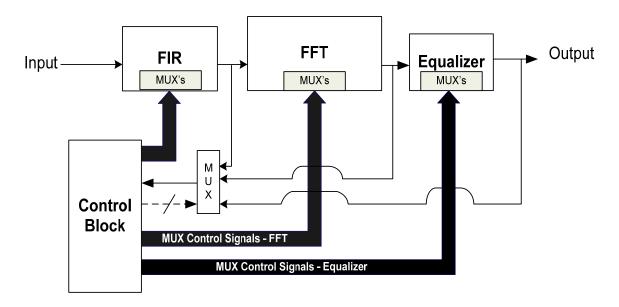

| 6.3.2 Dual Nested Loop Architecture                                                |     |

| 6.3.2.1 Proposed Power Control Methodology: Overview                               |     |

| 6.3.2.2 Guided Probabilistic Compensation for Low-Power Digital-Filters            |     |

| 6.3.2.3 Signal Quality Metrics                                                     |     |

| 6.3.2.4 Error Rate Metric for Modulating Supply Voltage                            |     |

| 6.3.2.5 Nested Loop Architecture                                                   |     |

| 6.3.2.6 Evaluation                                                                 |     |

| 6.4 APPLICATION DRIVEN CHANNEL AND VARIATION TOLERANT LOW-POWER BASEBAND<br>DESIGN |     |

| 6.4.1 Feed Forward - Image Quality Metric                                          |     |

| 6.4.2 Feedback - Channel and System Performance Metric                             |     |

| 6.4.3 Locus based Operation - Design and Characterization Phase                    |     |

| 6.5 EVALUATION                                                                     |     |

| 6.6 Concluding Remarks                                                             |     |

| CHAPTER 7 - CONCLUSIONS AND FUTURE WORK                                            |     |

| REFERENCES                                                                         | 132 |

## List of Tables

| Table 1: Parameter variations (nominal) in different technologies [53]    |    |

|---------------------------------------------------------------------------|----|

| Table 2: Parameter variations (3δ) in different technologies [53].        |    |

| Table 3: Technology parameter variation (3δ/nominal values).              |    |

| Table 4: WLAN access card power consumption in different protocols [84].  |    |

| Table 5: Change in Full-Adder delay with VOS (65nm CMOS technology)       | 55 |

| Table 6: Increase in error rate with VOS in LPF.                          |    |

| Table 7: Control parameter settings of feedback controllers calculated    |    |

| Table 8: A 15-tap LPF implemented in 65nm technology.                     | 64 |

| Table 9: Effect of sampling frequency on system SNR                       |    |

| Table 10: Area overhead of the proposed schemes.                          |    |

| Table 11: Power consumption in baseband demodulator under voltage scaling |    |

|                                                                           |    |

# **List of Figures**

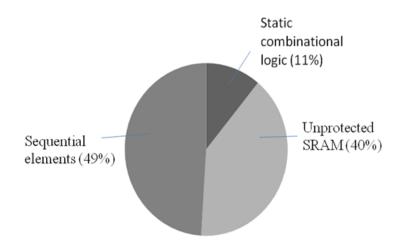

| Figure 1: Soft error rate in different circuit blocks.                                                                                                              | 5    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

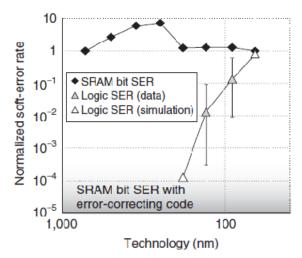

| Figure 2: Comparison of the SRAM bit SER with the flip-flop/latch SER [11].                                                                                         |      |

| Figure 3: (a) SER in different circuits. (b) Qcritical in logic/latches/SRAM [12].                                                                                  |      |

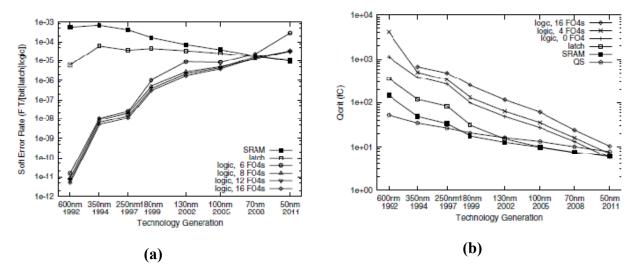

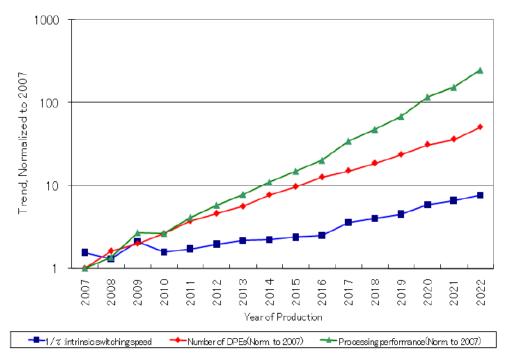

| Figure 4: System complexity trend in non-mobile devices [20]                                                                                                        |      |

| Figure 5: System performance trend in non-mobile devices [20]                                                                                                       | . 10 |

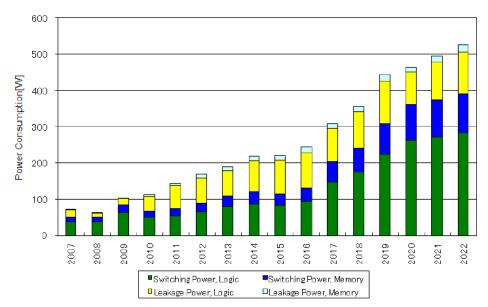

| Figure 6: System power consumption trend in non-mobile devices [20].                                                                                                | . 11 |

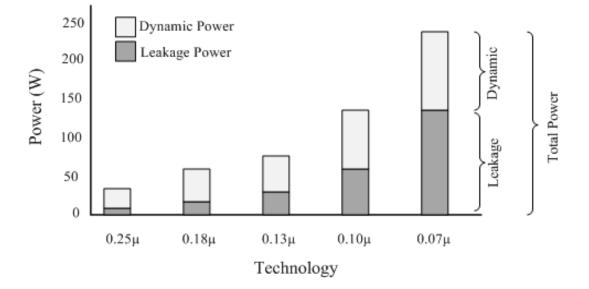

| Figure 7: Leakage and dynamic power contribution in total power.                                                                                                    |      |

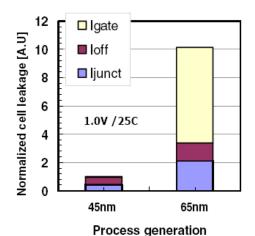

| Figure 8: SRAM cell leakage comparison between 65 nm and 45 nm [26].                                                                                                | . 13 |

| Figure 9: High-K metal gate leakage reduction [27].                                                                                                                 | . 13 |

| Figure 10: Limitation of battery technology.                                                                                                                        |      |

| Figure 11: Average number of dopant atoms in the device channel for different technology no [55].                                                                   |      |

| Figure 12: Frequency and leakage variation in 130 nm technology [58].                                                                                               |      |

| Figure 13: Variation reduction using ABB.                                                                                                                           |      |

| Figure 14: Block diagram of an OFDM baseband transceiver.                                                                                                           |      |

| Figure 15: Bits are mapped to complex numbers representing amplitude and phase (a) QPSK                                                                             |      |

| modulation (b) QAM-16 modulation.                                                                                                                                   |      |

| Figure 16: OFDM symbol power spectrum [83].                                                                                                                         |      |

| Figure 17: Virtual sub-carriers (null sub-carriers) for the out-of-band noise filtering<br>Figure 18: Power distribution in state of the art WLAN transceivers [84] |      |

| Figure 19: OFDM transceiver model                                                                                                                                   |      |

| Figure 20: Altera Stratix II DSP development board                                                                                                                  |      |

| Figure 21: The OFDM TRX implementation in Simulink.                                                                                                                 |      |

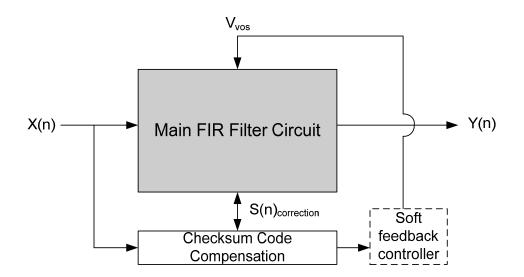

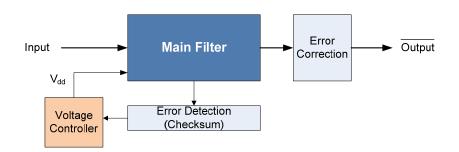

| Figure 22: Proposed linear checksum based voltage overscaling scheme                                                                                                |      |

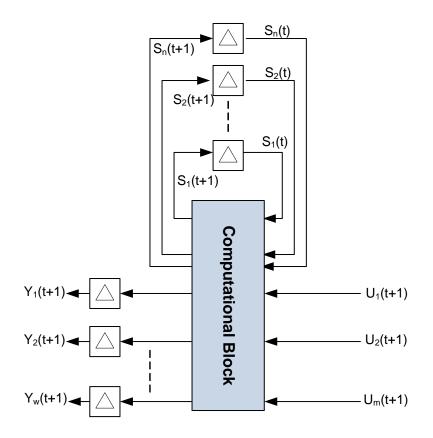

| Figure 23: State variable system representation.                                                                                                                    |      |

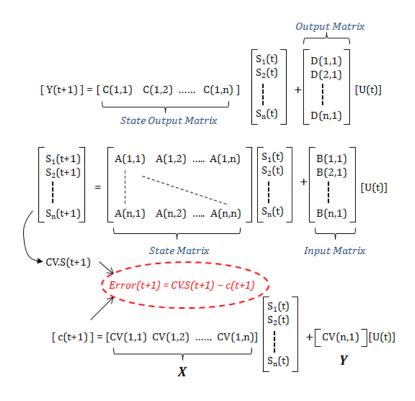

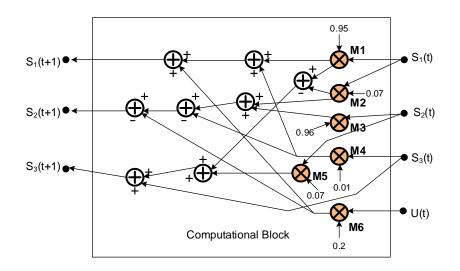

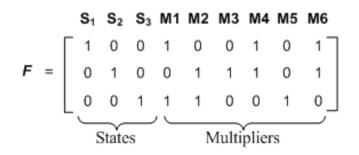

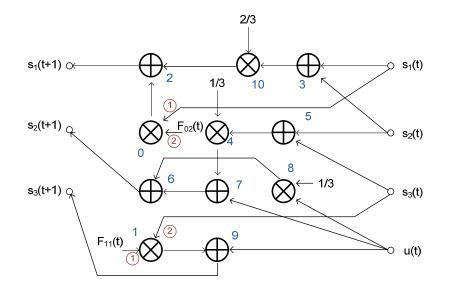

| Figure 24: Linear state matrix representation with a checksum code                                                                                                  |      |

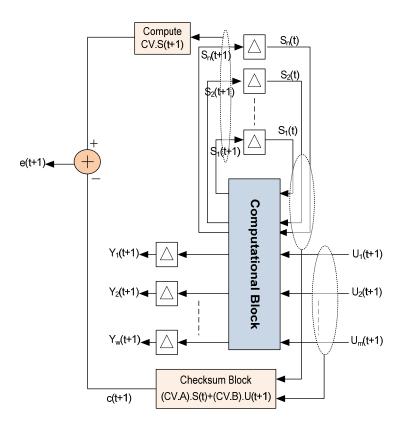

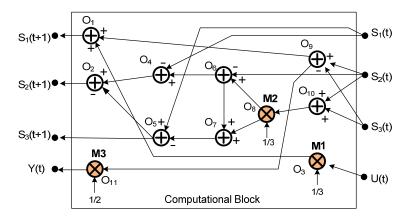

| Figure 25: State variable form representation with checksum based error detection                                                                                   |      |

| Figure 26: Structure of a state-variable system with shared operators.                                                                                              |      |

| Figure 27: Gain Matrix corresponding to the system shown in Figure 26.                                                                                              |      |

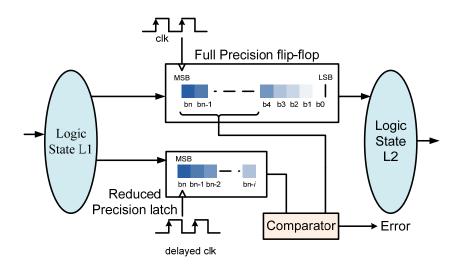

| Figure 28: Reduced precision shadow-latch for error monitoring in MSB bits.                                                                                         |      |

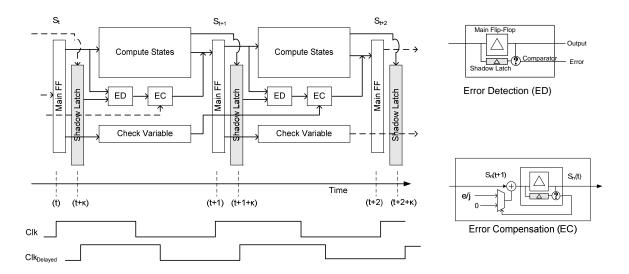

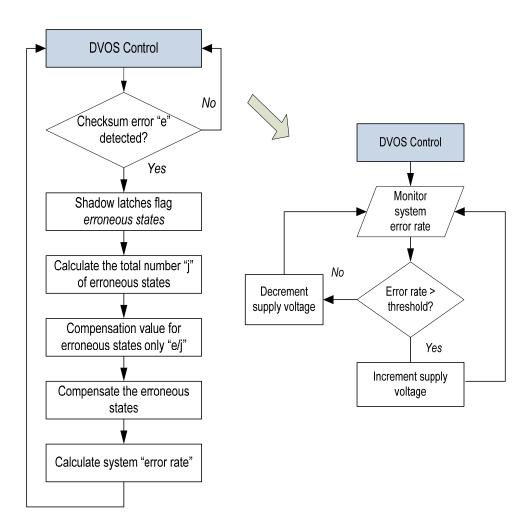

| Figure 29: Guided probabilistic compensation methodology. Error detection and compensation                                                                          |      |

| performed in the next clock cycle.                                                                                                                                  |      |

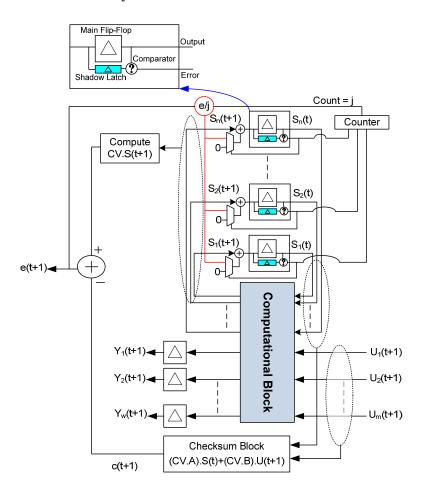

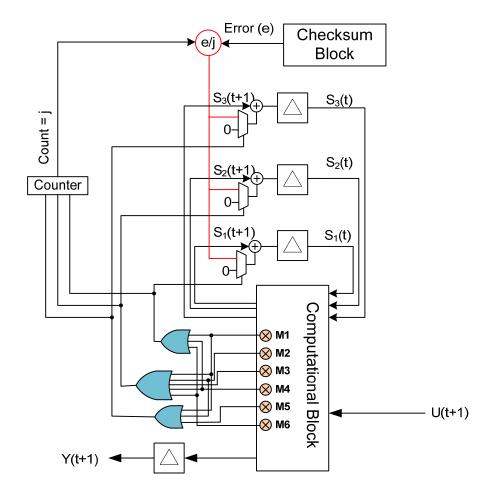

| Figure 30: GPC architecture implementation.                                                                                                                         |      |

| Figure 31: Computational block implementation with shared hardware                                                                                                  |      |

| Figure 32: Guided probabilistic compensation in shared-pipelined architecture.                                                                                      |      |

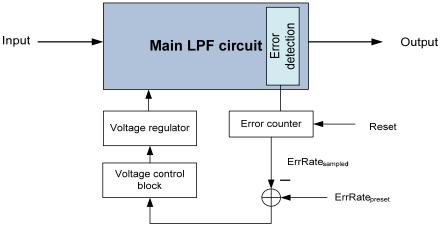

| Figure 33: Supply voltage control                                                                                                                                   |      |

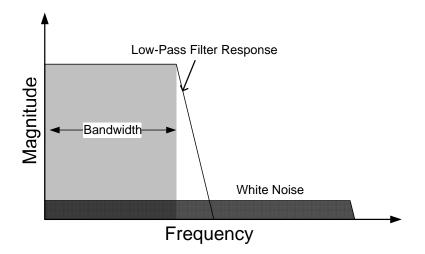

| Figure 34: Frequency spectrum of a low-pass FIR filter.                                                                                                             |      |

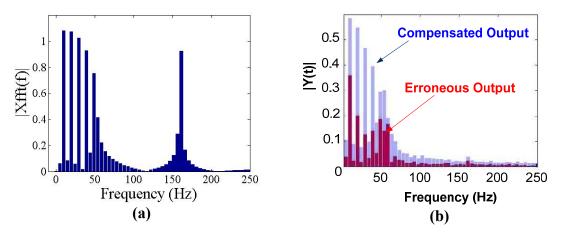

| Figure 35: (a) Frequency spectrum of input applied to the LPF. (b) Frequency spectrum of filt                                                                       |      |

| output with and without probabilistic compensation.                                                                                                                 | . 57 |

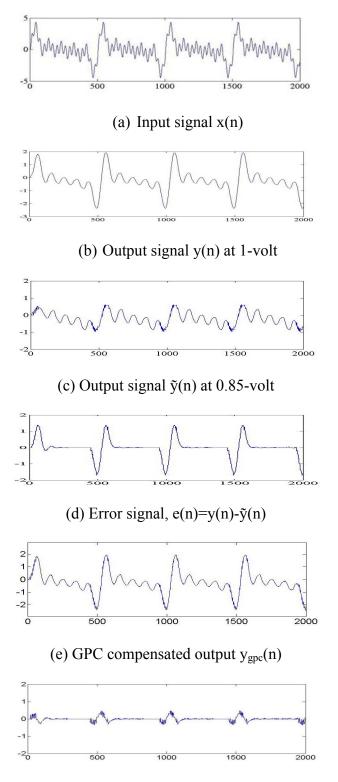

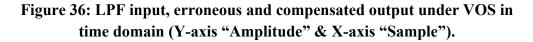

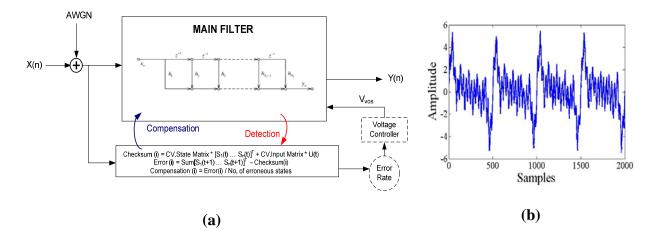

| Figure 36: LPF input, erroneous and compensated output under VOS in                                                                                                 |      |

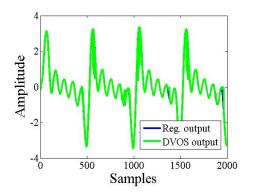

| Figure 37: (a) Simulation setup for DVOS (b) Input to LPF with added AWGN                                                                                           |      |

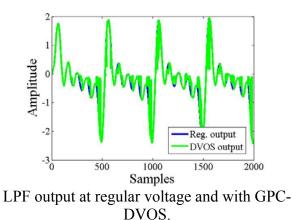

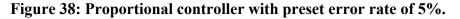

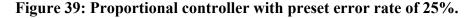

| Figure 38: Proportional controller with preset error rate of 5%.                                                                                                    |      |

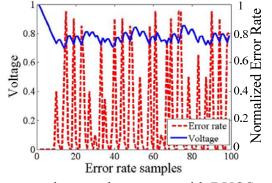

| Figure 39: Proportional controller with preset error rate of 25%.                                                                                                   |      |

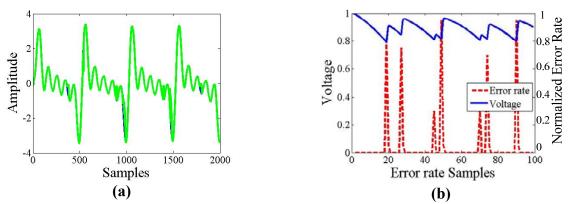

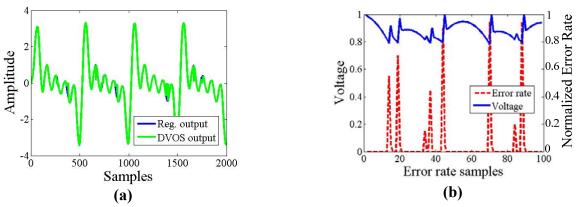

| Figure 40: PI-controller, preset error rate of 5% (a) LPF regular and DVOS output                                                                                   |      |

| Figure 41: PID-controller, preset error rate of 5% (a) LPF regular and DVOS output                                                                                  | . 62 |

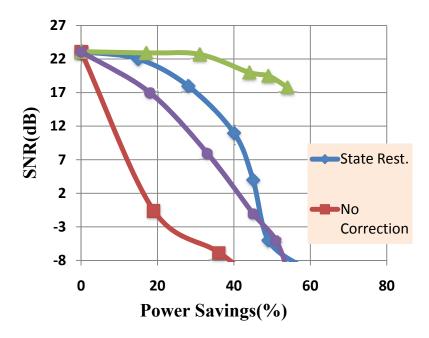

| Figure 42:  | Power savings achieved with guided probabilistic compensation.                                                                                 | . 63     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------|

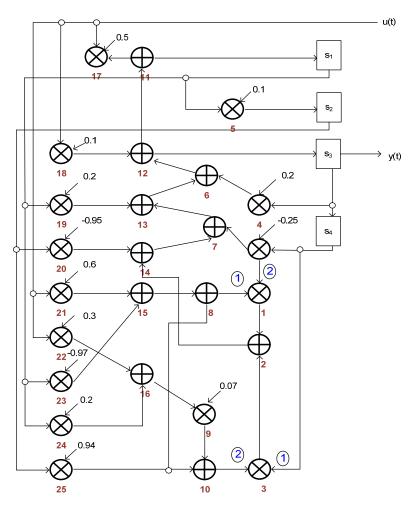

| Figure 43:  | Non-linear digital circuit.                                                                                                                    | . 67     |

| Figure 44:  | Time-freeze linearized circuit.                                                                                                                | . 68     |

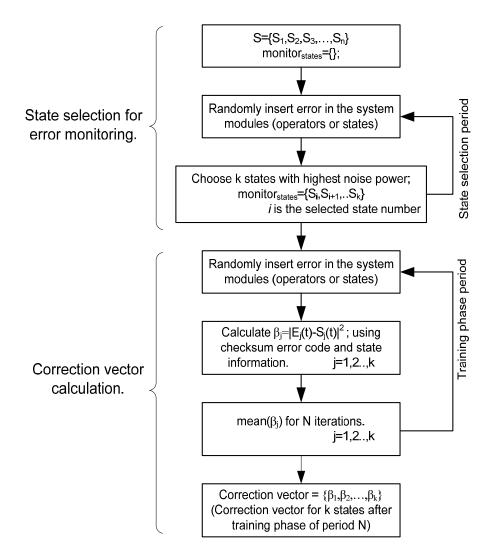

| Figure 45:  | Training phase - Compensation vector selection.                                                                                                | . 74     |

| Figure 46:  | Guided probabilistic error compensation with DVOS control.                                                                                     | . 76     |

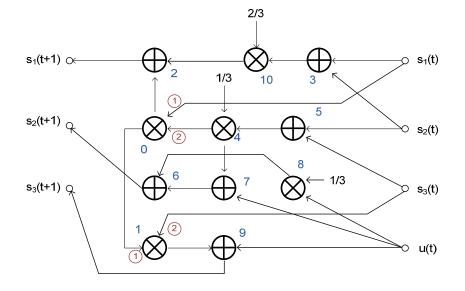

|             | Non-linear circuit used for simulation results.                                                                                                |          |

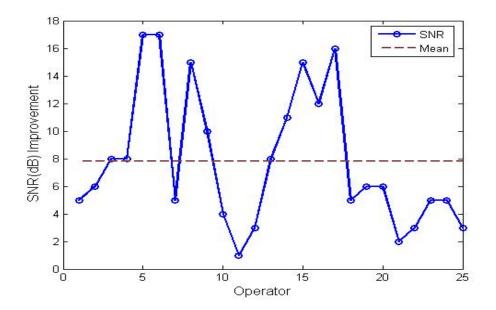

| Figure 48:  | SNR gain by probabilistic error compensation on different operators                                                                            | . 78     |

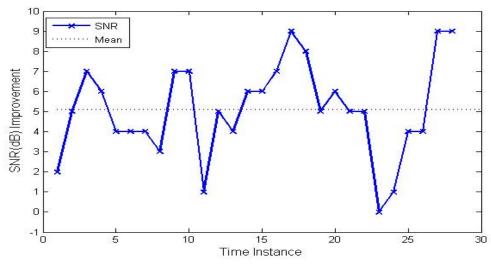

| Figure 49:  | SNR gain at Operator 1 on different time instances                                                                                             | . 79     |

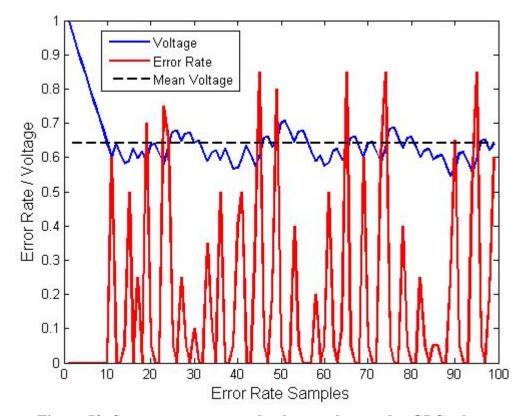

| Figure 50:  | System error rate and voltage values under GPC scheme                                                                                          | . 80     |

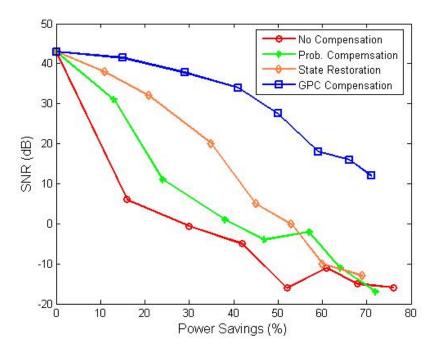

|             | System SNR and power savings using GPC scheme.                                                                                                 |          |

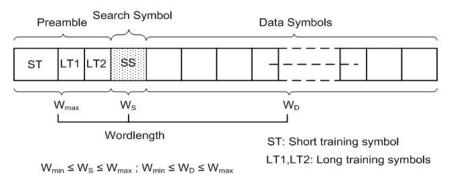

| Figure 52:  | OFDM packet with preamble and added search symbol                                                                                              | . 86     |

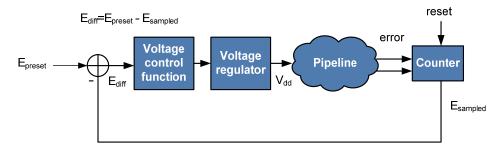

| Figure 53:  | Supply voltage controller based on system preset and sampled error rate                                                                        | . 86     |

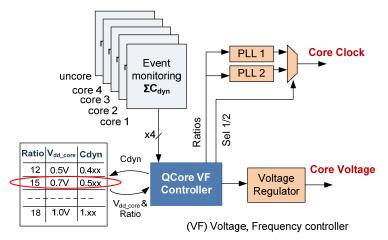

| Figure 54:  | Switching activity based voltage-frequency controller in                                                                                       | . 88     |

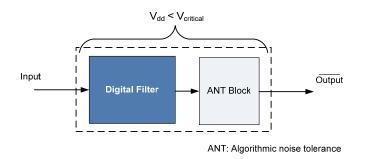

| Figure 55:  | Voltage overscaling for low-power filter operation.                                                                                            | . 89     |

|             | Supply voltage feedback control                                                                                                                |          |

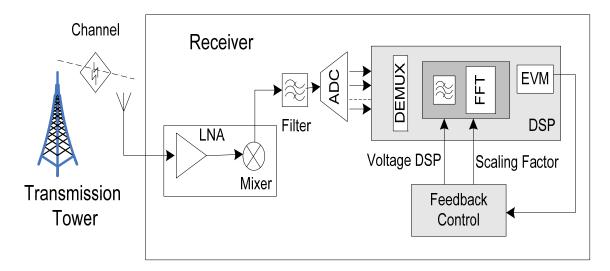

| Figure 57:  | Block diagram of adaptation metric based receiver architecture.                                                                                | . 92     |

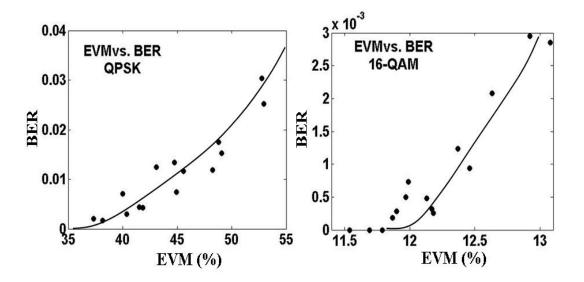

| Figure 58:  | EVM vs. BER relationship [90].                                                                                                                 | . 94     |

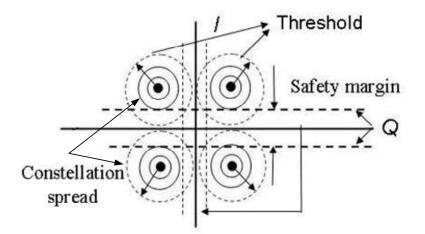

| Figure 59:  | QPSK constellation spread with varying channel conditions.                                                                                     | . 95     |

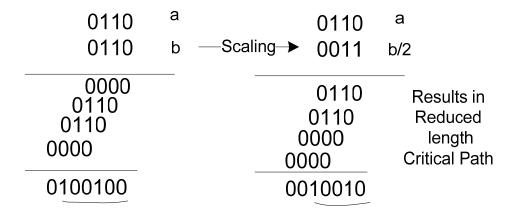

| Figure 60:  | Critical path reduction with signal scaling.                                                                                                   | . 96     |

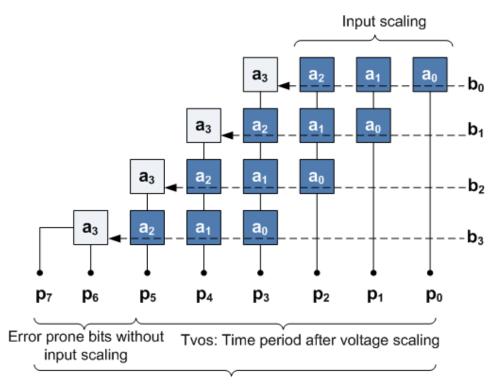

| Figure 61:  | Input (Voltage) scaling for low-power operation in an array multiplier                                                                         | . 97     |

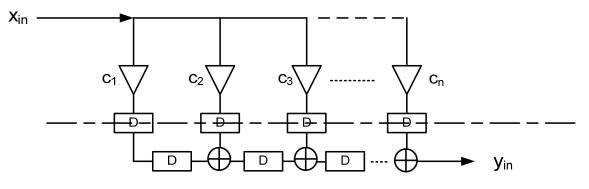

| Figure 62:  | Transposed form pipelined FIR filter                                                                                                           | . 98     |

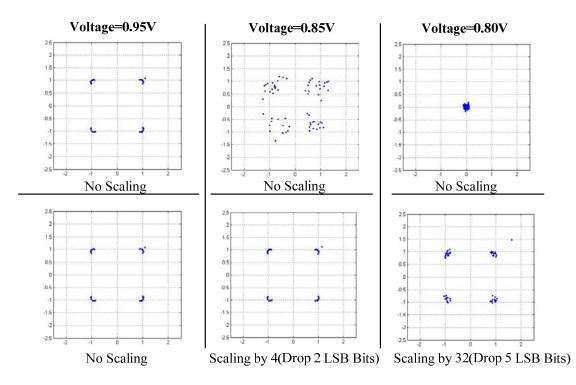

| Figure 63:  | (Top Row) QPSK constellation points with voltage scaling alone. (Bottom Row)                                                                   |          |

| Constellat  | ion points with combined W-V <sub>dd</sub> scaling                                                                                             | . 99     |

|             | EVM degradation with voltage scaling and combined W-V <sub>dd</sub> scaling.                                                                   |          |

|             | Supply voltage as a function of W and V <sub>t</sub>                                                                                           |          |

|             | Path sensitization for oscillation test.                                                                                                       |          |

|             | Block level representation of POTTs scheme.                                                                                                    |          |

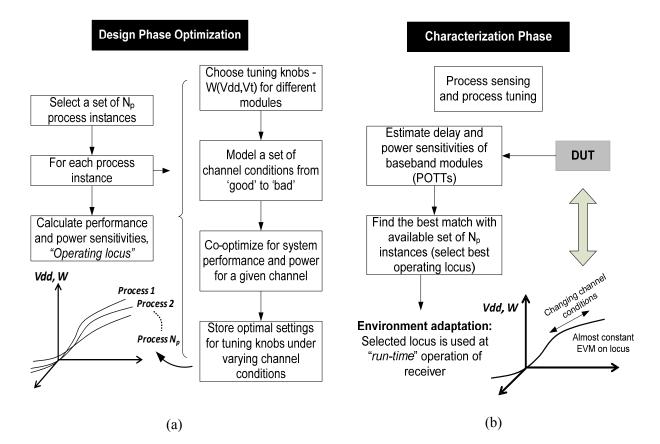

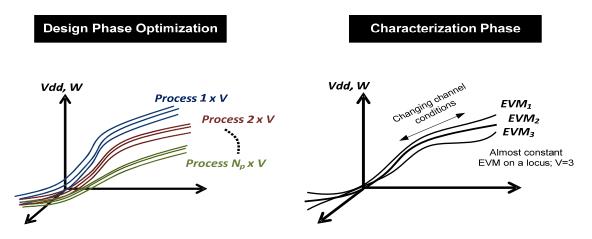

|             | (a) System design phase. (b) System characterization phase                                                                                     |          |

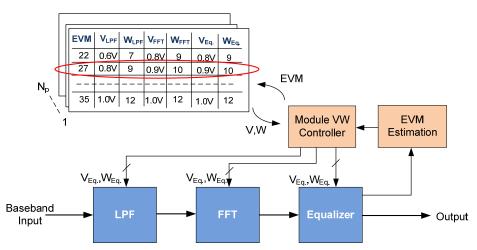

|             | Signal quality based module-level "voltage, wordlength" scaling                                                                                |          |

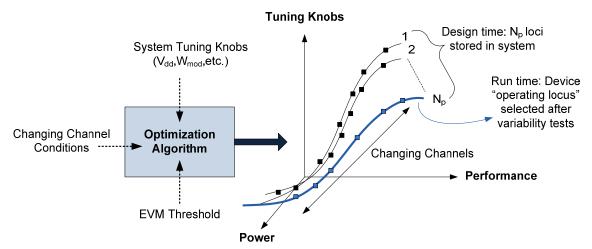

|             | Optimal power locus for a wireless receiver under changing channel conditions                                                                  |          |

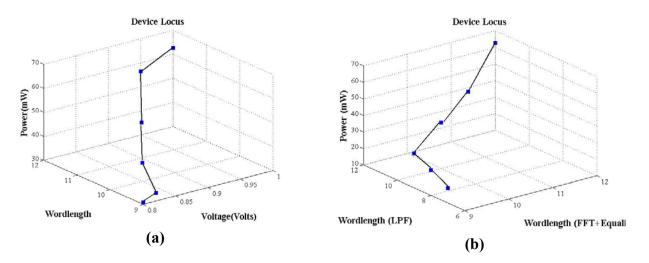

| •           | Device locus for run-time operation (a) symmetric voltage/wordlength modulation                                                                |          |

|             | b) independent voltage/wordlength scaling on baseband modules.                                                                                 |          |

|             | Power distribution of the OFDM baseband receiver under 20% process variations.                                                                 |          |

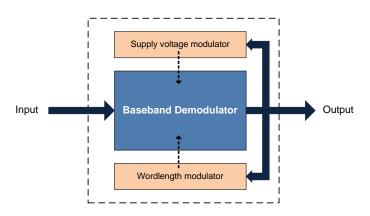

|             | Proposed real time feedback architecture.                                                                                                      |          |

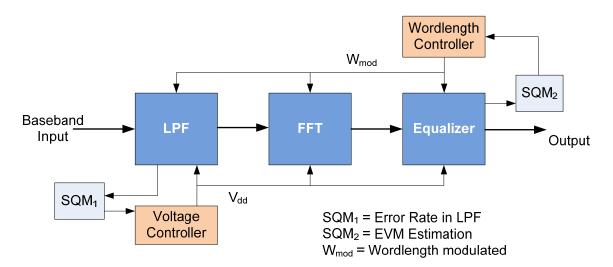

|             | Proposed real-time dual feedback control architecture.                                                                                         |          |

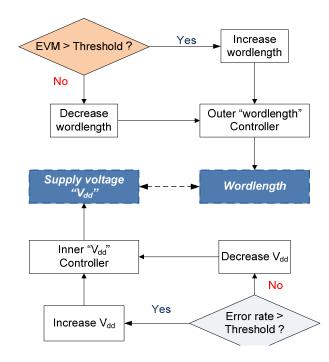

| 0           | Dual nested loop control strategy.                                                                                                             |          |

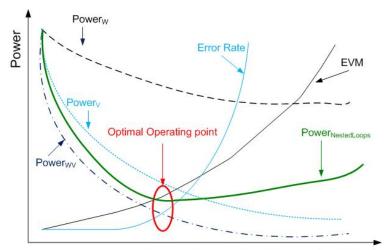

|             | The qualitative relationship between supply voltage, wordlength, EVM and error ra                                                              |          |

| -           | al operating point of nested loops is defined by the quality requirements of end sign                                                          |          |

|             | $\mathbf{F} = 1 (1 0 0 0 1 1 0 0 1 1 1 1 1 1 1 1$                                                                                              | 116      |

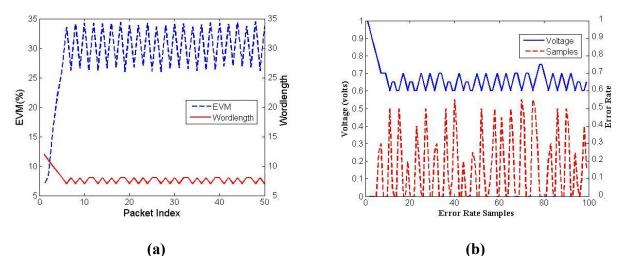

| -           | Fixed Channel (a) Outer loop - Wordlength modulation under EVM constraint. (b)                                                                 | 110      |

|             | - Voltage modulation under Error rate constraint.                                                                                              | 110      |

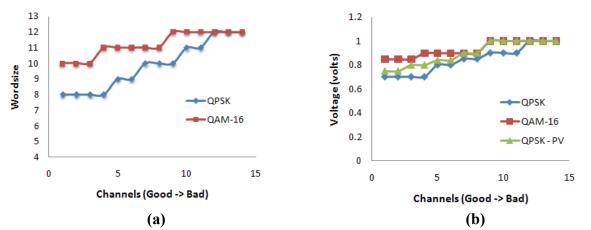

|             | System wordlength and voltage for QPSK and QAM-16 modulation, for different onditions. Process variations result in different voltage settings | 110      |

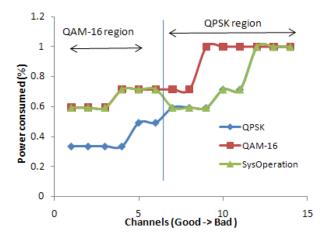

|             | Average power consumption in the baseband demodulator with the proposed nested                                                                 |          |

|             | tecture                                                                                                                                        |          |

| Figure 80.  | (a) Image received at preset EVM=30% and error rate=2%. (b) Image received with                                                                | 117<br>h |

|             | % and error rate=10%.                                                                                                                          |          |

| L V IVI-33/ | 0 and error rate-10/0                                                                                                                          | 140      |

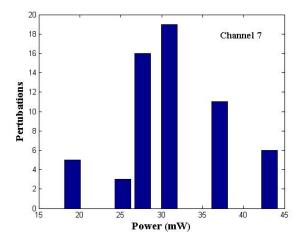

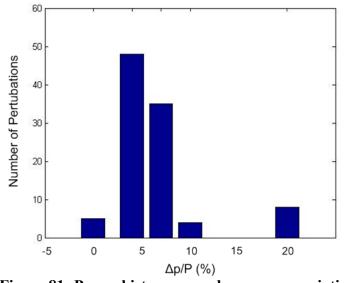

| Figure 81: Power histogram under process variations                                                       | 121  |

|-----------------------------------------------------------------------------------------------------------|------|

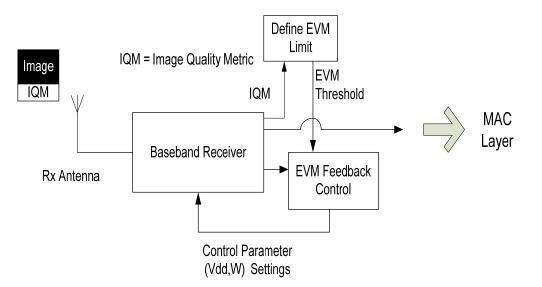

| Figure 82: Application driven power savings methodology                                                   | 122  |

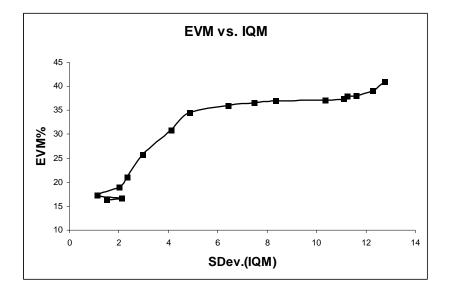

| Figure 83: IQM vs. system EVM                                                                             | 124  |

| Figure 84: N <sub>p</sub> x V number of loci are stored at design time. System selects from a V number of | of   |

| loci at run-time depending upon the end-application performance requirements.                             | 126  |

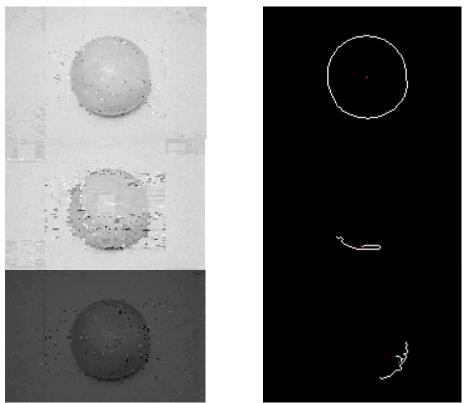

| Figure 85: (Top to bottom) Image X with 7-bit drop, Image X with 8-bit drop, Image Y with                 | 7-   |

| bit drop                                                                                                  | 127  |

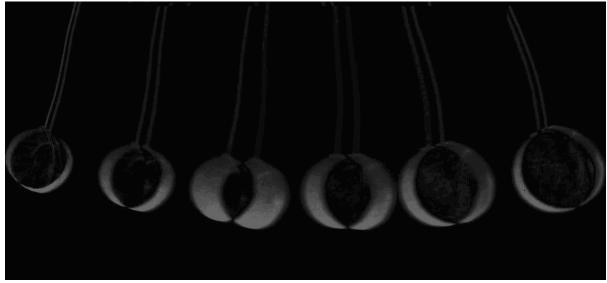

| Figure 86: Object tracking in a swinging ball video                                                       | 128  |

| Figure 87: Proposed soft error mitigation, low-power and process tolerant techniques for robu             | ust, |

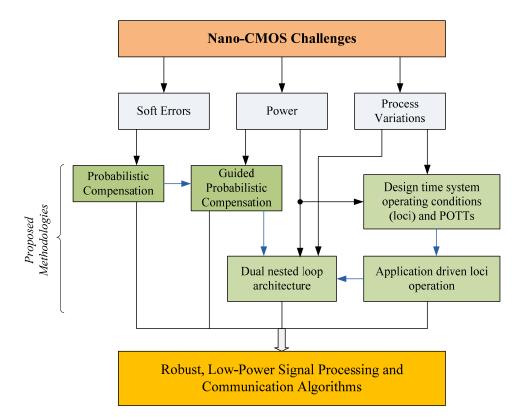

| low-power signal processing and communication algorithms                                                  | 131  |

## SUMMARY

The successful pursuit of the Moore's-law in the semiconductor industry has enabled the integration of highly complex functionalities on a single chip, thus enabling the proliferation of electronic devices in every spectrum of daily life. A new genre of such devices is wireless electronics (smart phones, netbooks, etc.) for mobile applications. However, the advent of Nano-CMOS (CMOS technologies below 90 nm) has brought new challenges for design, process, and test engineers. Soft errors have become a major reliability concern. These errors occur because of the combined effects of atmospheric radiation, and reduced noise margins. Another challenge is process variation that results in large spread in the delay and power distribution of circuits, and results in parametric yield loss. System power consumption is another major design challenge in Nano-CMOS because of high integration of transistors within a single chip and high amount of leakage current.

This thesis presents circuit-level techniques for soft error mitigation, low-power design with performance trade-off, and variation-tolerant low-power design. The proposed techniques can be divided into two broad categories. First, error compensation techniques are presented, which are used for soft error mitigation and also for low-power operation (with the help of guided circuitry as explained in next chapters) of linear and non-linear filters. Second, a framework for variationtolerant low-power operation of wireless devices is presented. This framework analyzes the effects of circuit "tuning knobs" such as voltage, frequency, wordlength precision, etc. on system performance, and power efficiency. Process variations are considered as well, and the best operating tuning knob levels are determined, which results in maximum system wide power savings while keeping the system performance within acceptable limits. Different methods are presented for variation-tolerant and power-efficient wireless communication.

## **CHAPTER 1**

## **INTRODUCTION**

### **1.1 Motivation**

Technology scaling as predicted by Gordon Moore [1][2] has been the driving force behind semiconductor industry growth. The scaling of transistor size in every generation provides advantages in power, performance, and cost. Every new technology generation [3]

- reduces power consumption by about 50% and energy consumption per transistor by about 65%;

- reduces gate delay by 30% thereby increasing operating frequency by 43% (although performance gain per device has decreased for Nano-CMOS because of threshold voltage limitations [4][5]);

- doubles transistor density, thus decreasing the cost per transistor.

However, at the same time that transistor sizes reduced, it became feasible to put more transistors in circuits to achieve complex functionalities, which ushered in an era of portable devices. The power consumption increased in high-performance, functionally complex devices and became a key design parameter in handheld devices. Also, circuits fabricated with these highly scaled technologies undergo a lot of intra-die and inter-die process variations. These variations result in significant circuit delay and power variations and thus affect the overall yield. Moreover, because of scaled node capacitances and supply voltages, circuits are more susceptible to soft errors. Power consumption is a major concern in the design of mobile devices fitted with limited battery life. Power consumption in a device is divided into two main categories, dynamic power consumption when the device is active and leakage power consumption when device is in idle state. Multiple supply voltage, clock gating, and dynamic voltage and frequency scaling are wellknown techniques for dynamic power reduction. Similarly, techniques such as multiple threshold voltages, power gating, and body biasing are employed in circuits to reduce the leakage power consumption. Some of the above-mentioned techniques are employed at the gate level and some at the component level. In many performance tolerant digital signal processing (DSP) applications, significant power savings can be achieved by exploiting the trade-off between system performance and power.

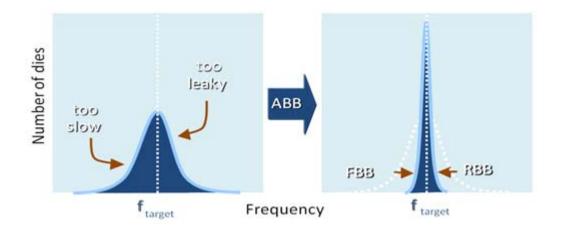

Process variations in Nano-CMOS technologies can cause up to a 20x deviation in the leakage power and a 1.3x variation in the circuit delay. Manufacturing yield is negatively impacted because of such large variations in the leakage power and circuit delay. Many circuits are designed with high process variations tolerance to have high yield at fabrication. The well-known design-time variant-tolerant techniques are gate sizing and supply voltage scaling. Application of forward body bias (FBB), reverse body bias (RBB), or adaptive body bias (ABB) to modulate the threshold voltage ( $V_t$ ) are the widely used post-manufacture circuit tuning techniques that bring the circuit delay and leakage power within an acceptable range.

Nano-CMOS circuits are more susceptible to soft errors because of lower supply voltage, smaller transistor sizes i.e. reduced node capacitances, and shorter depth of pipeline stages in modern VLSI circuits. Module redundancy such as triple module redundancy (TMR), hardened flip-flops, and gate sizing are the commonly practiced techniques for soft error resilient design. Traditionally, soft error tolerant techniques are applied to mission critical systems operating in high radiation environments. However, with the advent of Nano-CMOS soft errors are also a major threat to correct operation of systems at terrestrial level. Therefore, better error mitigation techniques are needed to take full advantage of highly scaled devices than module redundancy that normally has an overhead of more than 200% in terms of area and power.

The objective of this research is to develop soft error resilient techniques with minimum overhead, variation-tolerant low-power techniques and system level low-power techniques. Many of these techniques are presented with a wireless OFDM system as a test vehicle. The organization of the thesis is presented in next section.

## 1.2 Thesis Organization

The focus of this work is on soft error resilient, process variation tolerant, and low-power design techniques in Nano-CMOS. The motivation for this thesis is provided in Chapter 1. Chapter 2 details the above mentioned challenges and state of the art techniques for combating these problems. Quantitative analysis of the Nano-CMOS challenges is also presented to show the current trends in the semiconductor industry.

Chapter 3 details the OFDM transceiver, which is used as a test vehicle for the robust lowpower signal processing techniques presented in this thesis. The OFDM transceiver is chosen as the test circuit as it contains all the modules required for testing of the proposed soft error mitigation, low-power, and process tolerant techniques. A brief introduction on the orthogonal frequency division multiplexing (OFDM) scheme is also provided in the chapter. Wireless channel and the transceiver modeling are explained. The OFDM transceiver implementation in hardware is explained as well.

Chapter 4 introduces the guided probabilistic error compensation (GPC) technique for lowpower operation of the linear digital circuits. Linearized checksum codes are used for the first time along with time-delayed latches (shadow latches) to perform error compensation under dynamic voltage overscaling. Since many DSP circuits are inherently noise-tolerant, the objective of the proposed scheme is to reduce system power with minimal impact on system performance, i.e., output signal quality. The state variable representation of systems is also presented in the chapter, and prior work in probabilistic error compensation in linear systems is summarized.

Chapter 5 presents the soft error mitigation technique in non-linear circuits using the linear error correcting codes. The proposed mitigation technique performs probabilistic error compensation with the minimum hardware overhead. Application of the guided probabilistic compensation method to non-linear filters for low-power operation is also presented.

Chapter 6 introduces channel driven variation tolerant low-power design methodologies, which are implemented in the wireless OFDM transceiver. The proposed schemes always strive to operate the system at the worst-case acceptable performance limit, thus saving considerable power when the operating conditions are not worst-case.

Chapter 7 concludes the major contributions of the thesis and provides a direction for the future work.

## **CHAPTER 2**

# NANO-CMOS CHALLENGES: SOFT ERRORS, POWER, PROCESS VARIATIONS

### **2.1 Soft/Transient Errors**

As feature sizes decrease with new fabrication technologies, single event transient (SET), single event upset (SEU), and multiple bit upset (MBU) effects dominate the radiation response in microcircuits. It is known for a long time that charged particles cause SEU in latches and memory elements (SRAM, DRAM) [6][7]. Moreover, they cause SET in combinational logic, clock lines and circuit control lines. The distribution of soft errors in combinational, sequential and memory elements [8] is shown in Figure 1. SET effects are becoming more prominent in the nanotechnology (<90 nm) as with reduced node capacitances, higher clock frequencies and lower noise margins, many of these transients are captured as errors in the latching circuitry [9][10].

Figure 1: Soft error rate in different circuit blocks.

The strike of a charged particle on a microcircuit results in generation of electron-hole pairs. These pairs are generated as a result of interactions of ion with bounded electrons in material, causing ionization of the material. These electron-hole pairs are of no consequence in bulk silicon since they eventually recombine. However, in presence of electric fields, these electronhole pairs quickly drift in opposite directions to be captured by the voltage sources responsible for the field. In bulk CMOS ICs electric fields are present at every p-n junction. Therefore, if an ion strikes a junction connected to a signal node, a transient current of some duration is observed at the node. In data storage elements such as latches, SRAM and DRAM, the effect of this transient current depends on the circuit response to the charge collected on a signal node. This means that a signal node capacitance (C) determines the amount of voltage swing ( $d_V=d_Q/C$ ) as a result of collected charge ( $d_Q$ ). Whenever, the collected charge reaches a critical value ( $Q_{critical}$ ) sufficient to drive a node voltage past the switching voltage, data value flips at the signal node (causing an error). In fast combinational circuits, a transient can flow to a latching element and can be stored as a valid signal (causing an error).

The effects of SET had been limited in combinational circuits because of three masking techniques, 1) Logical masking; a transient on a gate fails to cause an error at the circuit output as subsequent gates in the path are off, 2) Electrical masking; a transient is attenuated by electrical properties of subsequent gates to a level where it does not affect the circuit output, 3) Latching window masking; a transient reaches the latch but falls outside the latching window period. However, in the nanotechnology these masking mechanisms are becoming inadequate and more of the current transients are causing errors at a circuit output. In recent work [11][12], it is shown that error rate in combinational circuits will reach that of unhardened data storage elements. Figure 2 shows the increasing SER sensitivity in combination logic with scaling, the variation in logic SER is due to the dozens of logic types tested.

Figure 2: Comparison of the SRAM bit SER with the flip-flop/latch SER [11].

Figure 3(a) shows the soft error rate (SER) trend in SRAM, latches and logic for different technology generations. It is obvious from the graph that soft error rates in combinational logic are increasing at a much higher rate than in data storage elements. The primary reason for SER increase in logic circuits is the decrease of Q<sub>critical</sub> with technology scaling as shown in Figure 3(b). Typical sizes of logic gates are larger than memory elements (density is more important in memory), thus making Q<sub>critical</sub> scaling more pronounced in logic circuits as compared to memory with decreasing feature sizes.

Figure 3: (a) SER in different circuits. (b) Qcritical in logic/latches/SRAM [12].

### 2.1.1 Soft Error Resilient Design

Current soft error (radiation) hardening techniques can be categorized as radiation hardening (Rad-hard) by fabrication (RHBF) and radiation hardening by design (RHBD). The RHBF approach includes methods such as substrate engineering, silicon on insulator (SOI), deep-trench isolation and guard ring oscillators. The RHBF techniques are quite effective in mitigating the radiation effects but they come at expense of increased fabrication costs, low yield and much higher ramp-up time to new fabrication technologies. The RHBD techniques include circuit, gate, and transistor level solutions. These techniques aim to reduce the probability of single event effects (SEE) observation at the primary outputs with a minimal impact on the circuit delay, power, and area. In general, error correcting codes and hardened memory cell designs are used in memory elements (SRAM/DRAM). In sequential logic, techniques such as increased capacitive loading at gates, gate resizing, new gate designs (hardened flip-flops [21]) and hardware redundancy (Muller C-elements [8], SET immune latch [13]) are used.

Traditionally, system level fault-tolerant techniques employ redundancy such as hardware, software, time, and/or information. The hardware redundancy techniques, such as TMR (triple module redundancy), have high hardware overhead. The high area and power costs associated with these techniques make them impractical for general applications. At the same time, such high cost is not necessary in most cases, especially in non-real-time systems. Therefore often techniques such as time redundancy, partial duplication, and software redundancy are employed. Such techniques have a less hardware overhead but have a negative impact on the system performance. In the literature, there are many circuit level techniques for the protection of flip-flops (latches) from errors. In [13], it was proposed to replace every latch with two or three latches that are clocked with a fixed phase-delay or their inputs arrive after a fixed phase-delay. A voting circuitry is used to pick the correct latch value. The redundancy of the scan flip-flops is

used along with the Muller C-element to protect the flip-flops against transient errors in [8]. The Muller C-element is a two-input and one-output component, which keeps its output value if its two inputs do not match. A soft error immune latch that keeps its state on three different nodes was proposed in [21]. When the value is destroyed in one of the nodes, the other two nodes still hold the right value. Techniques are present in past work for hardening the combinational circuits against transient errors by optimizing the gate sizes and increasing the gate load capacitances [18].

## 2.2 Power Consumption in Digital Circuits

Power consumption has been increasing in the digital systems because of high device integration to implement complex functions on a single chip and high performance requirements. The successful pursuit of the Moore's Law has continually reduced the cost of silicon devices, thus enabling the implementation of highly complex systems. Figure 4 and Figure 5 shows the system complexity and performance requirements (predicted) trends in non-mobile devices. There is a predicted trend of 30% year-to-year increase in system complexity and performance requirements of up to 70 TFLOPS by the year 2022. Similar trends are predicted for the mobile devices as well. These highly complex and high-performance systems will consume considerable power as shown in the predicted trend of Figure 6.

Figure 4: System complexity trend in non-mobile devices [20].

Figure 5: System performance trend in non-mobile devices [20].

Figure 6: System power consumption trend in non-mobile devices [20].

Power consumption in digital circuits has two main components: dynamic and static. Dynamic power loss is due to the switching activity of the circuit nodes and is proportional to the node capacitances, supply voltage, switching activity of the nodes, circuit operating frequency, and short circuit power. Short circuit power makes roughly 10% of the dynamic power consumption [22][23]. Dynamic power consumption in a digital circuit is given below

$$P_{dvnamic} = 0.5 \times C \times V_{DD}^2 \times \alpha \times f + P_{sc} , \qquad (1)$$

where C is the total capacitance,  $V_{DD}$  is the supply voltage,  $\alpha$  is the switching activity, f is the operating frequency and P<sub>sc</sub> is the short circuit power.

Static power consumption is the power loss in a circuit when the circuit is idle. It is composed of three components: sub-threshold leakage, drain junction leakage and gate leakage. Sub-threshold leakage is the dominant factor and causes power dissipation as given below

$$P_{sub-V_{th}}=V_{DD} \times I_S \times e^{\frac{V_{gs}-V_{th}}{nV_T}} \times (1-e^{\frac{V_{ds}}{V_T}}), \qquad (2)$$

where  $V_{DD}$  is the supply voltage,  $I_s$  is the process and circuit dependent constant, n is the subthreshold swing coefficient,  $V_{th}$  is the threshold voltage, and  $V_T$  is the thermal voltage. Subthreshold power loss has increased drastically in the scaled technologies because of the exponential relationship of sub-threshold current to threshold voltage. Also, since the supply voltage is not scaled down as much as the feature sizes to have high-performance transistors [24], gate leakage has increased because of low gate oxide thickness. As a result, static power consumption has become a critical design parameter in recent technologies. Since recently, the dynamic and static power consumption trend in recent technologies is shown in Figure 7 [25].

Figure 7: Leakage and dynamic power contribution in total power.

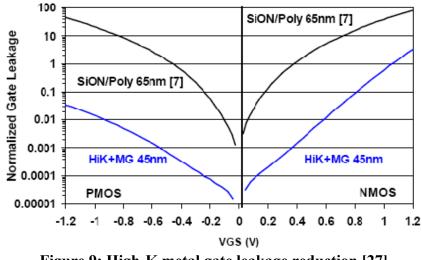

However, the advent of high-k metal gates is promising to drastically decrease the leakage current in the circuits. It is observed in [26] that 45 nm high-k metal gates reduce the leakage current in a SRAM bit cell by 10x as shown in Figure 8. These gates provide dramatic gate leakage reduction as compared to 65 nm CMOS bulk technology, gate leakage is reduced by >25x for NMOS and by 1000x for PMOS devices (see Figure 9). Coupled with other leakage reduction techniques such as the gate length increase, it can be argued that dynamic power will remain the dominant power consumption source in the future digital circuits.

Figure 8: SRAM cell leakage comparison between 65 nm and 45 nm [26].

Figure 9: High-K metal gate leakage reduction [27].

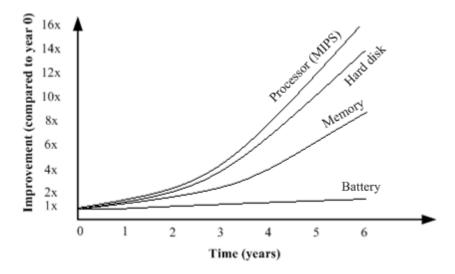

Battery life in handheld devices has always been a design concern. Handheld devices are becoming omnipresent, and with their increased capabilities have found usage in almost every aspect of life. However, battery life is not increasing at the same pace as the energy requirements of handheld electronics. Lithiom-ion batteries offer the highest capacity among today's rechargeable batteries. Their capacity has increased by about 10% per year [28] and lags far behind the increase in computation power. Even the improved battery capacities in the future, probably will not quench the energy needs of handheld devices or diminish the importance of power management. Figure 10 shows the improvement in battery life compared to processor

(MIPS), hard disk, and memory capacity over the years. It is obvious from the figure that battery energy storage capacity is lacking far behind the other technologies [25].

Figure 10: Limitation of battery technology.

### **2.2.1 Power Reduction Techniques**

Power consumption is a major design parameter and a lot of work has been done in the field of power optimization [29]. Power optimization techniques range from system level to circuit level. In the following, some well-known power optimization techniques for leakage and dynamic power are briefly discussed. The focus of the discussion is on energy-efficient systems that provide performance on demand. These energy-efficient systems strive to operate with minimum power while satisfying the minimum system performance requirements.

As is obvious from Figure 7, static power consumption is a major concern in highly scaled technologies. The most natural way to reduce the leakage current is to turn off the supply voltage of a circuit in the standby mode. This is achieved using a power gating technique [30]. In a power gating scheme, one NMOS transistor called the sleep transistor is placed in series with the logic block to create a virtual ground. During normal mode of operation the sleep transistor is on, therefore the circuit functions as usual. However, during the standby mode the sleep transistor is

turned off, thus disconnecting the ground from the circuit. In practice dual threshold voltage (dual-V<sub>t</sub>) or multi-threshold voltage transistors (MTCMOS) are used in power gating. In these technologies, low V<sub>t</sub> transistors are used to implement the logic and high V<sub>t</sub> transistors are used as sleep transistors. Body bias control is another useful technique for reducing the leakage current of a circuit. Reverse body bias is used to increase the threshold voltage of transistors, which in turn decreases the circuit leakage. However, this method is becoming less effective as the supply voltage is scaled down in new technologies [31]. The leakage current of a gate is a strong function of its inputs. For example, the minimum leakage current of a Nand2 gate is in the case when both of its inputs are low. In this case, both the NMOS transistors present in series in the Nand2 gate are off, thus offering maximum effective resistance. This in turn is known as the "stack effect" i.e. the phenomenon when the leakage through a stack of two or more off transistors in series is significantly less than a single device leakage. Different methods such as the Boolean satisfiability problem [31], 2-to-1 multiplexer [32], and gate modification are used to control the gate inputs for maximum leakage control.

The other major source of power, dynamic power consumption as given in equation 1 can be reduced by

- decreasing the switching capacitance,

- decreasing the supply voltage (V<sub>DD</sub>).

Clock gating is a commonly used circuit-level technique for reducing the switching capacitance of a circuit [34][35]. The switching activity in the unused circuit is eliminated by disabling the clock to that portion of the circuit. The method results in power savings by eliminating the switching activity in the flip-flops, gates, and clock tree of a circuit block. Dynamic supply voltage scaling is another very effective technique for reducing the power consumption of a circuit.

### 2.2.2 Power/Performance Adaptive Design

The data wordlength optimization in a circuit decreases the power consumption by reducing the switching activity. Simulation based techniques [36]-[39] have been proposed to find the optimal wordlength for digital signal processing algorithms in wireless communications and filtering applications. Such algorithms optimize the wordlength according to the predetermined system-level performance metrics. Often, the resulting digital circuits are implemented with large wordlength values. A dynamic wordlength tuning technique is presented in [40] for digital baseband OFDM signal processing algorithms. The scheme allows dynamic adjustment of the wordlengths of digital filtering and FFT operations by continuous monitoring of the error vector magnitude (EVM) of the demodulated signal, where EVM is the system performance metric. When the performance of the system is adequate for the required quality i.e. EVM value is higher than a predetermined threshold, data wordlength is reduced. Otherwise, the system uses the longer wordlength. Clock gating is used in the scheme for reducing the data wordlength by halting the redundant portion of the circuit.

Because of the quadratic relationship of the supply voltage with power, voltage scaling is a very effective power savings technique. In the multiple static voltage islands technique, different islands (components) in the circuit are operated at different voltages depending on their timing constraints [41]. The dynamic voltage and dynamic frequency (DVDF) scaling technique is employed in many pipelined architectures [42][43]. Decreasing the supply voltage increases the delay of the circuit. This makes it necessary to reduce circuit clock frequency as well. The core idea behind this power savings technique is to provide performance on demand. In RAZOR [45], the concept of performance on demand with the output quality feedback was presented. The feedback system modulates the supply voltage depending on the error rate in the system. The error rate is calculated with the help of shadow latches. These shadow latches are augmented

with the main flip-flops but are operated at a delayed clock. At a reduced voltage, if the logic path meets the setup time of the main flip-flop, then the main flip-flop and shadow latch will have the same data. However, if the logic path does not complete its computation in time, the main flip-flop will latch an incorrect data, while the shadow latch will latch the late arriving correct value. In such a case, the comparison of shadow latch value with the main flip-flop value will generate an error signal. The incorrect value will be flushed from the pipeline, incurring a one cycle penalty. The supply voltage is modulated by a proportional controller based on system error rate. If the error rate in the system is less, then it means that voltage can be reduced further. However, if the error rate is high, supply voltage is increased to limit the number of errors occurring. The technique exploits the data dependence of circuit delay and results in considerable power savings.

Algorithmic noise tolerant techniques [46][46][47] allow energy efficient digital signal processing (DSP). The core idea is to permit errors to occur in the DSP block and then correct them via a separate error control block. This approach of error/noise tolerance achieves higher energy efficiencies compared to the noise-mitigating techniques. Voltage overscaling is used in the main DSP block to save power. It is observed that even when the circuit logic delay is marginally longer than the critical path delay of the circuit (due to supply voltage reduction), the resulting logic error rate increases marginally because the circuit-critical paths are excited infrequently by the applied stimulus [51]. As the supply voltage is decreased further, this error rate increases rapidly leading to a large deterioration in the output signal quality. Different error control blocks have been presented in previous work. In [46], linear prediction-based output approximation and error cancellation methods are used for error control blocks. In linear prediction schemes, it is assumed that errors are correlated across time and can occur with a frequency that is sufficiently less than 1/2Np, where Np is the number of predictor taps.

accuracy of the error cancellation scheme and the resulting system performance depends on how well the system is "trained" to perform error cancellation for an input signal with specified statistics. A technique that uses reduced precision redundancy is presented in [47]. In this approach, the DSP block is duplicated but with reduced precision. The quantization noise resulting from the reduced precision quickly becomes a bottleneck in such a scheme. To mitigate the quantization noise, a least significant bits (LSB) error estimator is implemented, which compensates for the quantization noise in the system.

## 2.3 **Process Variations**

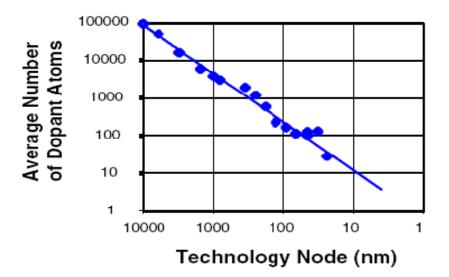

Process variations occur during processing and masking steps of a wafer. Both transistors and interconnects undergo physical process variations because of the imperfections in the processing steps [52][53]. Process variations can be divided into inter-die process variations and intra-die process variations [54]. Inter-die process variations affect all devices on a die in the same way. Intra-die process variations affect devices on a die in a random or locally correlated way. Process variations alter the device geometric characteristics, and the material parameters. The geometric variation in a CMOS transistor consists of oxide thickness ( $T_{ox}$ ), effective channel length ( $L_{eff}$ ) and device width (W). Channel-doping variation is the most significant variation in the materials property of devices and results in the threshold voltage ( $V_{th}$ ) variation. Figure 11 shows the decreasing number of dopant atoms in the channel for different technology nodes.

Figure 11: Average number of dopant atoms in the device channel for different technology nodes [55].

As the number of dopant atoms in the channel decreases with device scaling, the impact of the variation associated with the dopant atoms increases. Nominal and 3 $\delta$  parameter variations of L<sub>eff</sub>, T<sub>ox</sub>, V<sub>th</sub>, and W are summarized in Table 1 and Table 2, respectively. Percentage parameter variation is taken as the ratio of 3 $\delta$  to the nominal value and is given in Table 3. From Table 3, it is obvious that the parameter variations have increased with every technology generation, with the most pronounced affect on L<sub>eff</sub>.

| Parameter               | 1997 | 1999 | 2002 | 2005 | 2006 |

|-------------------------|------|------|------|------|------|

| L <sub>eff</sub> (nm)   | 250  | 180  | 130  | 100  | 70   |

| T <sub>ox</sub> (nm)    | 5    | 4.5  | 4    | 3.5  | 3    |

| V <sub>th</sub> (volts) | 0.5  | 0.45 | 0.4  | 0.35 | 0.3  |

| W(µm)                   | 0.8  | 0.65 | 0.5  | 0.4  | 0.3  |

Table 1: Parameter variations (nominal) in different technologies [53].

| Parameter                | 1997 | 1999 | 2002 | 2005 | 2006 |

|--------------------------|------|------|------|------|------|

| L <sub>eff</sub> (nm)    | 80   | 60   | 45   | 40   | 33   |

| T <sub>ox</sub> (nm)     | 0.4  | 0.36 | 0.39 | 0.42 | 0.48 |

| V <sub>th</sub> (mvolts) | 50   | 45   | 40   | 40   | 40   |

| W(µm)                    | 0.2  | 0.17 | 0.14 | 0.12 | 0.1  |

**Table 2: Parameter variations (3δ) in different technologies [53].**

Table 3: Technology parameter variation (3δ/nominal values).

| 1997 | 1999             | 2002                                                              | 2005                                                                                                   | 2006                                                                                                                                       |

|------|------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|      |                  |                                                                   |                                                                                                        |                                                                                                                                            |

| 32%  | 33%              | 35%                                                               | 40%                                                                                                    | 47%                                                                                                                                        |

| 8%   | 8%               | 9.8%                                                              | 12%                                                                                                    | 16%                                                                                                                                        |

|      |                  |                                                                   |                                                                                                        |                                                                                                                                            |

| 10%  | 10%              | 10%                                                               | 11%                                                                                                    | 13.3%                                                                                                                                      |

| 25%  | 26.2%            | 28%                                                               | 30%                                                                                                    | 33.3%                                                                                                                                      |

|      | 32%<br>8%<br>10% | 32%         33%           8%         8%           10%         10% | 32%         33%         35%           8%         8%         9.8%           10%         10%         10% | 32%         33%         35%         40%           8%         8%         9.8%         12%           10%         10%         10%         11% |

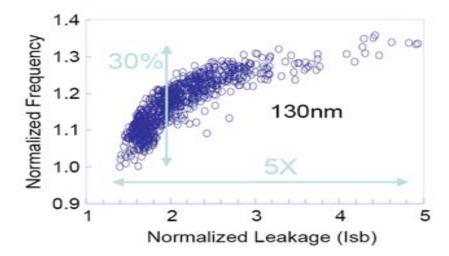

Process variations result in large spread of delay and frequency characteristics of devices. The frequency and leakage variation of circuits in a wafer for 130 nm technology are shown in Figure 12. It can be seen that because of parametric variations, devices undergo a 30% frequency variation and a 5x variation in standby leakage current ( $I_{sb}$ ). This huge variation in frequency and leakage power has resulted in frequency binning and affects the overall yield. High-frequency chips with high  $I_{sb}$  and low-frequency chips with reasonably high  $I_{sb}$  are discarded. Sub-threshold voltage ( $V_{th}$ ) variation is the main contributor in this huge  $I_{sb}$  variation. The  $V_{th}$  relation with sub-threshold current is given as

$$I_{sub-V_{th}} = I_s e^{\frac{V_{GS} - V_{th}}{nV_T}} (1 - e^{\frac{V_{DS}}{V_T}}) \quad , \tag{3}$$

where  $I_s$  is the process and circuit-dependent constant, n is the sub-threshold swing coefficient,  $V_{GS}$  is the gate-to-source voltage,  $V_{DS}$  is the drain-to-source voltage,  $V_{th}$  is the threshold voltage, and  $V_T$  is the thermal voltage. Similarly, supply voltage relation with circuit delay is given as

$$\tau_d = \frac{C_L V_{DD}}{\beta (V_{DD} - V_{th})^{\gamma}} \quad , \tag{4}$$

where  $V_{DD}$  is the system supply voltage,  $\beta$  is the device trans-conductance,  $C_L$  is the circuit load capacitance,  $V_{th}$  is the threshold voltage and  $\gamma$  is the velocity saturation coefficient, which is between 1.2 and 1.5 for the current technologies. As is obvious from equations 3 and 4, sub-threshold voltage  $V_{th}$  has an exponential relationship with the leakage current and a linear relation with the circuit delay. Therefore, variation in  $V_{th}$  affects the circuit leakage power more adversely as compared to the circuit delay.

Figure 12: Frequency and leakage variation in 130 nm technology [58].

### 2.3.1 Process Variation Tolerant Circuit Design

The variation tolerant circuit design techniques can be categorized into two main categories: the design-level optimization techniques and the post-manufacture techniques. The design-level optimization techniques are discussed first.

#### 2.3.1.1 Design-Level Variation Tolerance

Conventionally, a static timing analysis technique is used for designing different circuit parameters such as supply voltage, threshold voltage and transistor sizing for given power, area and delay constraints [61]-[65]. However, many devices designed for the nominal case (using static timing analysis) will fail because of the increased variations in new technologies. Designing the circuits for the worst-case is extremely conservative and is unacceptable in many applications because of high power and delay costs.

Statistical timing analysis techniques striving to optimize the circuit power and performance by gate sizing while considering process variations were recently proposed [66][69]. A Lagrangian-based relaxation is proposed for transistor sizing for circuits under intra-die and inter-die variations in [66]. The objective of the technique is to meet the delay requirements of a circuit with a certain degree of confidence while keeping the area and power within a given set of constraints. The optimization complexity of the procedure is linear and results in a 19% area/power savings compared to the worst-case design. A sensitivity-based heuristic technique for dual-V<sub>th</sub> assignment and gate sizing is proposed in [66]. The objective of the technique is to minimize the leakage power. Each gate in a circuit is assigned two statistical sensitivity metrics, one is the sensitivity of a gate to the gate size and the other is the sensitivity of a gate to the V<sub>th</sub>. The algorithm tries to find the best gates to have the high V<sub>t</sub> and the gates to be sized up, such that the circuit leakage and its variation are minimized. The algorithm has a relatively higher complexity of O(n3) and results in a leakage power reduction of 15-35% compared to deterministic analysis. The statistical gate sizing technique of [68] reduces the delay variation by 72% at a cost of 20% increase in design area. The technique of [69] performs yield improvement with simultaneous delay and leakage constraints. This technique employs a non-linear optimizer and reports a 40% yield improvement compared to the deterministic approach.

#### 2.3.1.2 Post-Manufacture Variation Tolerance

Adaptive body (substrate) biasing is one of the more important post-manufacture techniques to minimize the impact of process variations [70][71]. This technique is used for leakage power reduction and also circuit delay adjustment. For an NMOS device with the substrate connected to ground, a negative bias called the reverse body bias (RBB), increases the threshold voltage ( $V_{th}$ ). On the contrary, a positive bias called the forward body bias (FBB), decreases the  $V_{th}$ . Similarly, for a PMOS device with the substrate connected to  $V_{DD}$ , a voltage lower (higher) than  $V_{DD}$  is used for RBB (FBB). The relationship of source-bulk (substrate) voltage with  $V_{th}$  is given as

$$V_{th} = V_{to} + \gamma(\sqrt{2|\varphi_f| + V_{sb}} - \sqrt{2|\varphi_f|}), \qquad (5)$$

where  $V_{to}$  is the threshold voltage at  $V_{sb} = 0$ ,  $V_{sb}$  is the source-bulk voltage,  $\gamma$  is the body-effect coefficient, and  $\phi_f$  is the substrate Fermi potential. An increase in  $V_{th}$  (RBB) reduces the leakage current at the cost of increased circuit delay, as evident from equations 3 and 4. Similarly, a decrease in  $V_{th}$  (FBB) reduces the circuit delay at the cost of increased circuit leakage.

Adaptive body biasing (ABB) can be used to compensate for both intra-die and inter-die process variations [71]. For dies with frequency higher than the target frequency ( $f_{target}$ ), dies are

reverse body biased to save on leakage power. Similarly, slow devices are FBBed to satisfy the delay constraints. ABB reduces the variations in the target frequency by moving the operating frequency of the slow dies to the right, and fast dies to the left, as shown in Figure 13. It is shown in [71] that as the technology scales, junction tunneling leakage increases under RBB. Therefore, RBB is losing its effectiveness in reducing leakage current by approximately 4x in every technology generation.

The supply voltage scaling, which is a very effective technique for power savings, is also explored as a tool to reduce the variability in circuit delay and power. It is shown in [73] that adaptive supply voltage scaling is as effective as ABB for reducing the circuit delay and power variation. However, it is also shown that applying these two techniques together does not result in significant improvement in performance variability. A leakage sensor and variable size keeper for dynamic logics was proposed in [74][75]. These sensors are placed in different regions of a die to estimate the leakage current. Leakage information is used to choose the best keeper size for the dynamic gates in that region that minimizes the leakage current.

Figure 13: Variation reduction using ABB.

# CHAPTER 3 SYSTEM DESIGN MODELING

In this chapter, the fundamentals of the orthogonal frequency division multiplexing (OFDM) baseband transceiver (TRX) are presented. The OFDM TRX is used as the test platform for the robust, low-power, and variation tolerant system level techniques presented in this work. The simulation model and hardware implementation of the OFDM transceiver (as used in this work) is also summarized. In recent years, a great deal of interest has been shown in the OFDM modulation method because of its high spectral efficiency and ability to cope with high-attenuation channels without the need of complex-equalization filters. The OFDM method has become a fundamental scheme in wideband digital communication over wireless and copper medium and is used in applications such as digital video broadcast, digital audio broadcast, wireless internet (WiFi), and mobile networking (WiMax, LTE).

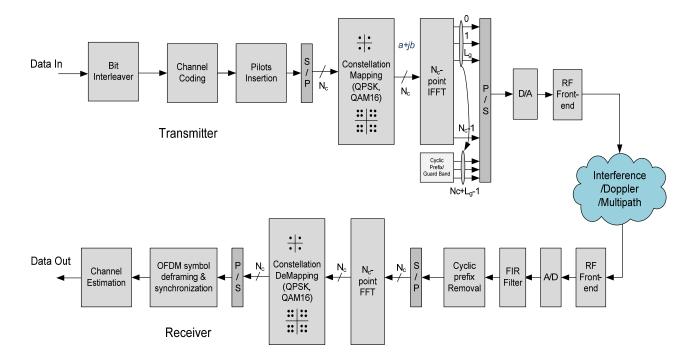

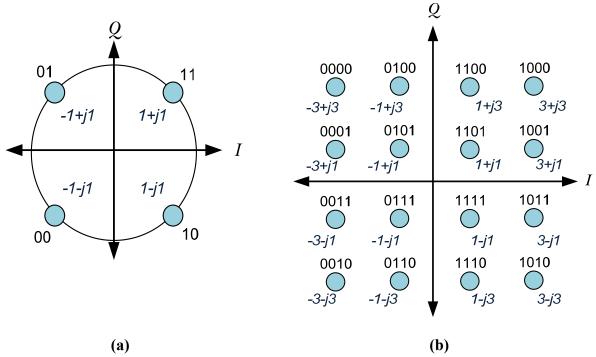

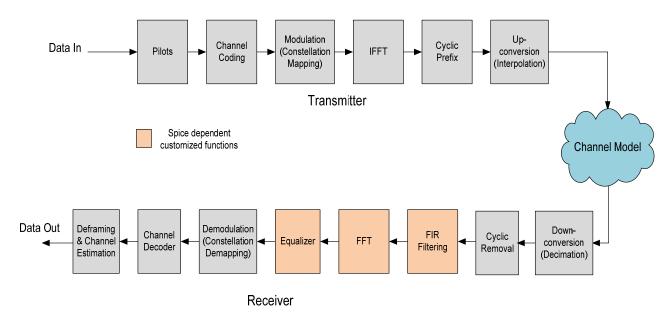

OFDM is a multi-carrier modulation scheme in which a large number of closely spaced orthogonal sub-carriers are used to carry data. Data is divided into several channels and is modulated on orthogonal sub-carriers (one sub-carrier per channel) using modulation schemes such as BPSK, QPSK, QAM-16, etc. The block-level implementation of an OFDM system is shown in Figure 14. In the OFDM transmitter, incoming serial data is optionally bit interleaved and channel coded. Pilots (known data), which are used for the timing and frequency synchronization of an OFDM frame, are inserted into the main data stream. A serial-to-parallel converter (S/P) takes the input-data stream and splits it into  $N_c$  parallel steams, where  $N_c$  is the number of sub-carriers. The data rate of each of these streams is  $1/N_c$  times the original data rate. These parallel streams of bits are mapped to complex-valued symbols ( $S_n=0,1,...,N_c-1$ ) in the constellation-mapping block. One, two, four or more bits are mapped to a complex-valued

symbol depending upon the modulation scheme (BPSK, QPSK, QAM16, etc.), as shown in Figure 15. The IFFT takes the complex-valued symbols representing N<sub>c</sub> frequencies as input and modulates them into a time-domain signal. The N<sub>c</sub> parallel-modulated source symbols at the output of the IFFT block are referred to as an OFDM symbol. In the OFDM scheme, a cyclic prefix, also known as the guard interval, is added to every OFDM symbol to minimize the effects of inter-symbol interference (ISI) and inter-channel interference (ICI). This data is then passed through a digital-to-analog converter (D/A), up converted, and the resultant RF-signal is transmitted in the channel.

Figure 14: Block diagram of an OFDM baseband transceiver.

At the receiver, the incoming data is down converted and is digitized by an analog-to-digital converter (A/D). A low-pass FIR filter is used for decimation and high-frequency noise filtering. The cyclic prefix is removed from the data and a serial-to-parallel converter splits the digitized data into N<sub>c</sub> streams. The FFT block demodulates the incoming time-domain signal symbols into

$N_c$  sub-carriers representing the pilots and data. The pilot symbols are extracted from the OFDM frame for synchronization purposes and the de-framed OFDM symbol is then mapped to bits (depending upon the modulation scheme). These data bits are then processed by the higher layers in the protocol stack.

Figure 15: Bits are mapped to complex numbers representing amplitude and phase (a) QPSK modulation (b) QAM-16 modulation.

In OFDM, the sub-carrier frequencies are orthogonal to each other. The orthogonality of the sub-carriers allows close placement of the sub-carriers in a given spectrum, thus ensuring efficient usage of a given bandwidth. The spacing between the sub-carrier frequencies is

$$F_s = \frac{1}{T_s},\tag{6}$$

where  $T_s$  is the OFDM symbol period. For the N<sub>c</sub> sub-carriers in a system, the source symbol duration (T<sub>d</sub>) before serial-to-parallel conversion is

$$T_d = \frac{T_s}{N_c} \ . \tag{7}$$

The envelope of an OFDM symbol with rectangular pulse shaping has the form

$$x(t) = \frac{1}{N_c} \sum_{n=0}^{N_c - 1} S_n e^{j2\pi f_n t}$$

,  $0 \le t \le T_s$

The N<sub>c</sub> sub-carrier frequencies are located at

$$f_{n=}\frac{n}{T_s}$$

,  $n = 0, 1, ..., N_c - 1$

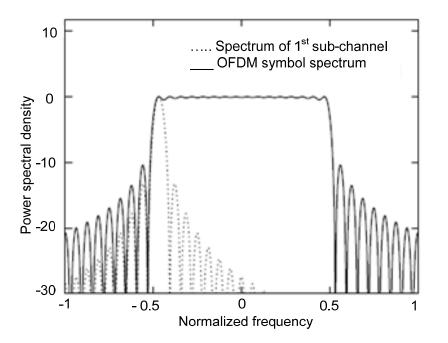

The power spectrum of an OFDM symbol versus the normalized frequency is shown in Figure 16. The dotted curve illustrates the spectrum of the first sub-carrier and the solid line indicates the power spectrum of an OFDM symbol as a sum of the individual power spectrums of the  $N_c$  sub-carriers; each sub-carrier is spaced apart by a frequency of  $F_s$ . Only channels at the band edges contribute to the out-of-band power emission.

Figure 16: OFDM symbol power spectrum [83].

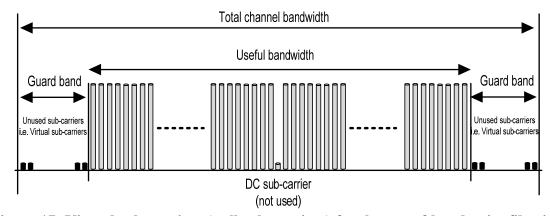

To minimize the out-of-band noise, a straight forward method is to use an FFT of higher size than required for the data transmission and to insert null sub-carriers (virtual sub-carriers/guard band) at the edges of the band spectrum (see Figure 17). Also, a null sub-carrier is placed in the middle of the spectrum to avoid the DC problem.

Figure 17: Virtual sub-carriers (null sub-carriers) for the out-of-band noise filtering.

## 3.1 OFDM TRX Power Consumption

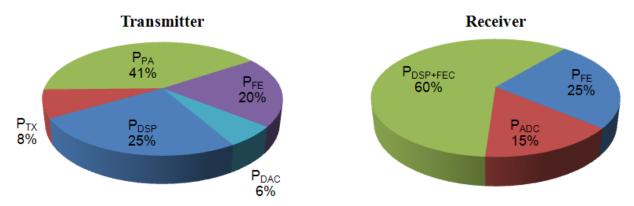

Figure 18 shows typical power consumption in an OFDM TRX. On the transmitter side, the power amplifier (PA) is the most power consuming device, followed by the digital signal processor (DSP). On the receiver side, the receiver DSP along with the forward-error-correction block (FEC) consumes roughly 60% of the total receiver power. Table 4 summarizes the power consumed in different WLAN access cards under different modes of operation. It is obvious from the table that more power (energy per unit time) is consumed in the transmitter than in the receiver. However, in typical applications, the transmitter is active only 12% of the time as compared to the receiver. Therefore, a TRX ends up consuming more energy in the receiver than in the transmitter. Hence, significant energy savings can be achieved by applying power saving techniques in the receiver block.

Figure 18: Power distribution in state of the art WLAN transceivers [84].

Table 4: WLAN access card power consumption in different protocols [84].

| Mode     | 802.11b | 802.11a | 802.11g |

|----------|---------|---------|---------|

| Sleep    | 132 mW  | 132 mW  | 132 mW  |

| Idle     | 544 mW  | 990 mW  | 990 mW  |

| Receive  | 726 mW  | 1320 mW | 1320 mW |

| Transmit | 1089 mW | 1815 mW | 1980 mW |

## 3.2 Simulation Setup

An OFDM baseband TRX is used as a test vehicle for the robust low-power signal processing techniques presented in the following chapters. Two important aspects of the simulation setup are channel modeling and baseband TRX modeling as described next.

## 3.2.1 Channel Modeling

For realistic wireless channel modeling, three major effects related to the OFDM wave propagation are explained below:

• Propagation losses are the incurred attenuations in the radio waves as they travel through the medium. These losses are modeled by simply attenuating the radio signal and adding a white noise to the signal.

- Multipath and fading effects are experienced because of deflections of the radio waves from different obstacles. These effects are modeled using a FIR filter. The length of the FIR filter defines the maximum delay spread in the channel.

- Interference in the channel is modeled as a combined effect of microwave and adjacent channel interference. Adjacent channel interference is due to out-of-band power emission of the neighboring bands and affects the carrier modulated signal. Its effect is modeled as

$$IntAdj(t) = f\{A(t), f_c(t)\}_{OFDM},$$

where A(t) is the time-varying amplitude and  $f_c(t)$  is the carrier frequency of the adjacent channel interferer. The microwave interferer is modeled as an AM-FM source based on the work presented in [85]. The AM-FM modulation is employed on a time-varying sinusoidal signal to generate the microwave interferer. The frequency of the microwave interferer is given by

$$f_d(t) = f_o + f_w sin\left(\frac{2\pi t}{T_w}\right),$$

where  $f_o$  is the initial interferer frequency,  $f_w$  is the maximum frequency wander, and  $T_w$  is the frequency wander period. For this work,  $f_o$  is 2.412GHz,  $f_w$  is 20MHz, and  $T_w$  is chosen as 20ms.

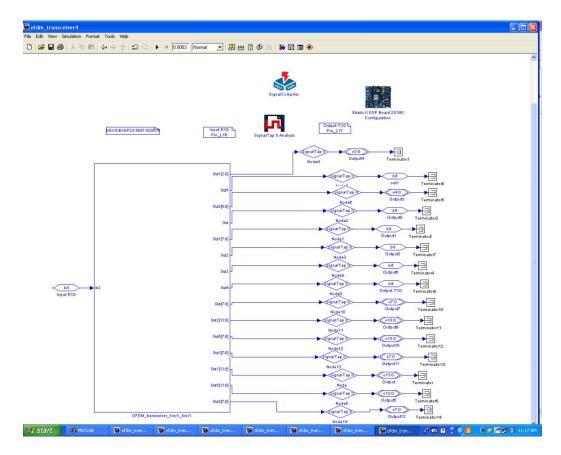

#### 3.2.2 Baseband TRX Model