# ACCELERATION AND OPTIMIZATION OF DYNAMIC PARALLELISM FOR IRREGULAR APPLICATIONS ON GPUS

A Dissertation Presented to The Academic Faculty

by

Jin Wang

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2016

> Copyright © 2016 by Jin Wang

# ACCELERATION AND OPTIMIZATION OF DYNAMIC PARALLELISM FOR IRREGULAR APPLICATIONS ON GPUS

Approved by:

Dr. Sudhakar Yalamanchili, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Hyesoon Kim School of Computer Science Georgia Institute of Technology

Dr. Richard Vuduc School of Computational Science and Engineering *Georgia Institute of Technology*  Dr. Tushar Krishna School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Santosh Pande School of Computer Science *Georgia Institute of Technology*

Date Approved: November 7, 2016

To my husband Haicheng and my parents.

# ACKNOWLEDGEMENTS

First of all, my deepest gratitude goes to my advisor, Prof. Sudhakar Yalamanchili, whose full support, incredible patience as well as deep understanding and perspective in research have always been great guidance during both of my PhD study and personal life.

Prof. Hyesoon Kim, Prof. Richard Vuduc, Prof. Tushar Krishna and Prof. Santosh Pande, thank you for serving on my committee and taking time to provide insightful feedbacks and comments on my research work.

Dr. Norm Rubin, thank you for being a great mentor during my internships as well as for my NVIDIA fellowship. Your experience in various research aspects has generated substantial inspiration for my PhD dissertation.

I would like to express my sincere thankfulness to my husband Haicheng, who is my best friend, life partner and soul mate. As a top researcher himself, Haicheng is also a great professional colleague who has helped me throughout the entire PhD.

I would also like to thank my parents, who have provided nothing but full support, financially and emotionally, for my 30 years of life. Even after my mother passed away, I still learn from her wisdom, passion and positive attitude towards life.

Last but not least, I would like to thank my fellow lab mates and graduate students, faculty members and staff from School of Electrical and Computer Engineering and College of Computing, external researchers from both academia and industry that provide me with great advices during multiple technical events. Their cooperation and assistance were essential for the completion of my PhD study.

# TABLE OF CONTENTS

| AC  | KNO                                               | WLEDO   | GEMENTS                                                      | iv   |

|-----|---------------------------------------------------|---------|--------------------------------------------------------------|------|

| LIS | T OF                                              | TABL    | ES                                                           | viii |

| LIS | T OF                                              | ' FIGUI | <b>RES</b>                                                   | ix   |

| LIS | T OF                                              | SYMB    | OLS AND ABBREVIATIONS                                        | xi   |

| SUI | MMA                                               | RY.     |                                                              | xiii |

| I   | INT                                               | RODU    | CTION                                                        | 1    |

| II  | BACKGROUND AND RELATED WORKS                      |         |                                                              | 6    |

|     | 2.1                                               | Baselii | ne GPU Architecture and CUDA Programming Model               | 6    |

|     | 2.2                                               | Kernel  | , Thread Block and Warp Scheduling on GPUs                   | 7    |

|     | 2.3                                               | Concu   | rrent Kernel Execution                                       | 10   |

|     | 2.4                                               | CUDA    | Dynamic Parallelism and Device-side Kernel Launch            | 11   |

|     | 2.5                                               | GPU P   | Power Modeling                                               | 13   |

|     | 2.6                                               | Relate  | d Works                                                      | 13   |

|     |                                                   | 2.6.1   | Characterization of GPU Workloads                            | 14   |

|     |                                                   | 2.6.2   | Research on Irregular Applications on GPUs                   | 15   |

|     |                                                   | 2.6.3   | Research on Nested Dynamic Parallelism                       | 16   |

|     |                                                   | 2.6.4   | Research on GPU Scheduling                                   | 18   |

|     |                                                   | 2.6.5   | Research on GPU Energy Efficiency                            | 19   |

|     |                                                   | 2.6.6   | Summary                                                      | 20   |

| III | DYN                                               | AMIC    | PARALLELISM IN IRREGULAR APPLICATIONS                        | 21   |

|     | 3.1                                               | Impact  | of Irregular Applications                                    | 21   |

|     | 3.2                                               | Dynam   | nically Formed Pockets of Structured Parallelism             | 22   |

|     | 3.3 Implementation Using CUDA Dynamic Parallelism |         | nentation Using CUDA Dynamic Parallelism                     | 23   |

|     | 3.4                                               | Charac  | eterization of CDP Implementations of Irregular Applications | 25   |

|     |                                                   | 3.4.1   | Benchmarks                                                   | 27   |

|     |                                                   | 3.4.2   | Evaluation and Analysis                                      | 30   |

|    | 3.5 | Charac            | cteristics of DFP                              | 44 |

|----|-----|-------------------|------------------------------------------------|----|

|    | 3.6 | Summ              | ary                                            | 45 |

| IV | DYN | AMIC              | THREAD BLOCK LAUNCH                            | 46 |

|    | 4.1 | Motiva            | ation                                          | 46 |

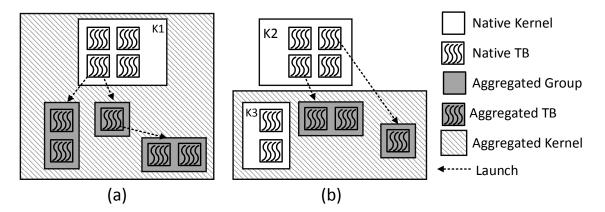

|    | 4.2 | DTBL              | Execution Model                                | 47 |

|    | 4.3 | Archit            | ecture Extensions and SMX Scheduling           | 51 |

|    | 4.4 | Overhead Analysis |                                                | 56 |

|    | 4.5 | Benefi            | ts of DTBL                                     | 58 |

|    | 4.6 | Experi            | iments and Evaluation                          | 58 |

|    |     | 4.6.1             | Methodology                                    | 59 |

|    |     | 4.6.2             | Result and Analysis                            | 61 |

|    |     | 4.6.3             | Discussion                                     | 71 |

|    | 4.7 | Summ              | ary                                            | 71 |

| V  | ОРТ | IMIZI             | NG THE PERFORMANCE OF THE DTBL MODEL           | 73 |

|    | 5.1 | Memo              | ry Locality in Dynamic Parallelism             | 73 |

|    |     | 5.1.1             | Spatial and Temporal Locality                  | 74 |

|    |     | 5.1.2             | Round-Robin TB Scheduler                       | 79 |

|    | 5.2 | LaPerr            | m Scheduler                                    | 80 |

|    |     | 5.2.1             | TB Prioritizing                                | 80 |

|    |     | 5.2.2             | Prioritized SMX Binding                        | 83 |

|    |     | 5.2.3             | Adaptive Prioritized SMX Binding               | 85 |

|    |     | 5.2.4             | Impact of Launching Latency                    | 88 |

|    |     | 5.2.5             | Overhead Analysis                              | 88 |

|    |     | 5.2.6             | Discussion                                     | 89 |

|    | 5.3 | Experi            | iments                                         | 90 |

|    |     | 5.3.1             | Methodology                                    | 90 |

|    |     | 5.3.2             | Result and Analysis                            | 91 |

|    |     | 5.3.3             | Impact of Different Dynamic Parallelism Models | 96 |

|     |      | 5.3.4  | Insights                                                      |

|-----|------|--------|---------------------------------------------------------------|

|     | 5.4  | Summ   | ary                                                           |

| VI  | IMP  | PROVIN | NG THE POWER EFFICIENCY OF THE DTBL MODEL 99                  |

|     | 6.1  | Impact | t of SMX Occupancy Patterns on Power Dissipation              |

|     |      | 6.1.1  | DTBL vs. Persistent Thread (PT) Model                         |

|     |      | 6.1.2  | SMX Occupancy Bubble for DTBL Implementation                  |

|     | 6.2  | SMX (  | Occupancy Bubble-based Power Saving Optimization for DTBL 106 |

|     |      | 6.2.1  | Dynamic TB Diversion and Scheduling                           |

|     |      | 6.2.2  | Opportunistic DVFS                                            |

|     |      | 6.2.3  | Incorporating Dynamic TB Diversion and DVFS                   |

|     |      | 6.2.4  | Architecture Extension                                        |

|     |      | 6.2.5  | Discussion                                                    |

|     | 6.3  | Experi | mental Evaluation                                             |

|     |      | 6.3.1  | Methodology                                                   |

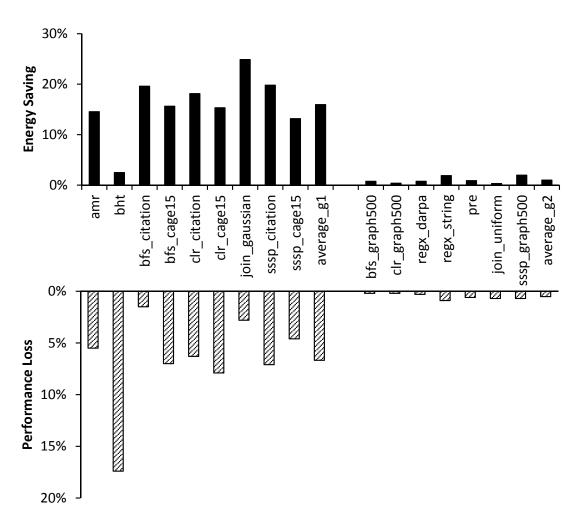

|     |      | 6.3.2  | Energy Savings and Performance Impact                         |

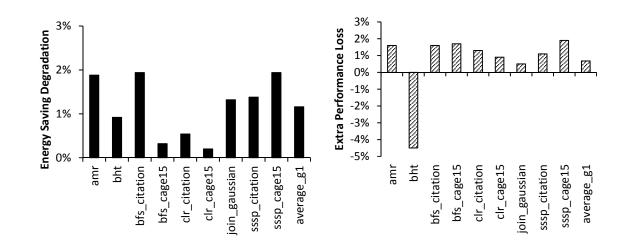

|     |      | 6.3.3  | Sensitivity of DVFS Transition Time                           |

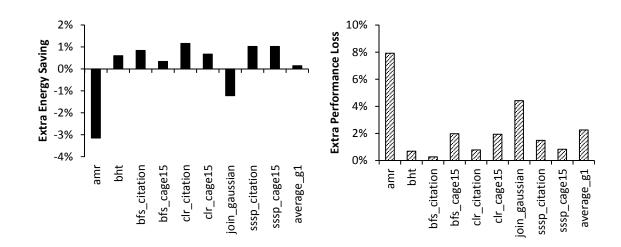

|     |      | 6.3.4  | Impact of SMX Draining                                        |

|     |      | 6.3.5  | Insights                                                      |

|     | 6.4  | Summ   | ary                                                           |

| VII | COI  | NCLUS  | ION                                                           |

| RE  | FERF | ENCES  |                                                               |

# LIST OF TABLES

| 1 | Configurations of the GPUs used for CDP characterization experiments | 26 |

|---|----------------------------------------------------------------------|----|

| 2 | Benchmarks used in the CDP characterization experimental evaluation  | 31 |

| 3 | List of device runtime API calls for DTBL                            | 49 |

| 4 | GPGPU-Sim configuration parameters for DTBL simulation               | 59 |

| 5 | Latency modeling for CDP and DTBL (Unit: cycles)                     | 60 |

| 6 | Benchmarks used in the experimental evaluation of DTBL               | 61 |

| 7 | Benchmarks used in the experimental evaluation for LaPerm scheduler  | 91 |

# LIST OF FIGURES

| 1  | Baseline GPU architecture                                                                                                                                                                                                  | 7  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | GPU programming model, including (a) CUDA thread hierarchy and (b) warps and control divergence                                                                                                                            | 8  |

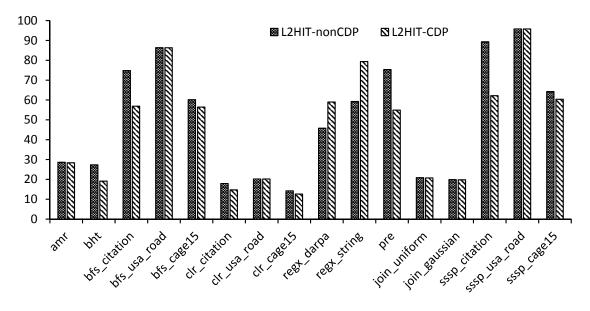

| 3  | Warp Execution Efficiency for non-CDP and CDP implementations                                                                                                                                                              | 32 |

| 4  | Average number of load/store instructions replay.                                                                                                                                                                          | 33 |

| 5  | L2 cache hit rate.                                                                                                                                                                                                         | 35 |

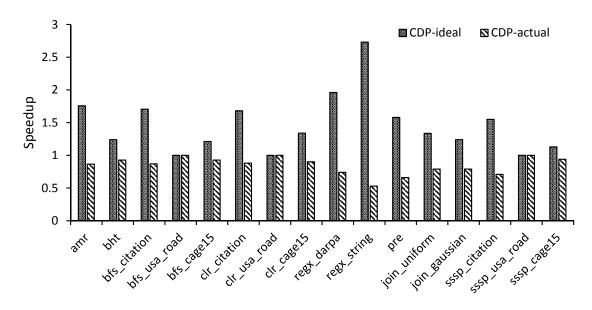

| 6  | Speedup of CDP implementations (ideal and measured) of unstructured applications over non-CDP implementations.                                                                                                             | 37 |

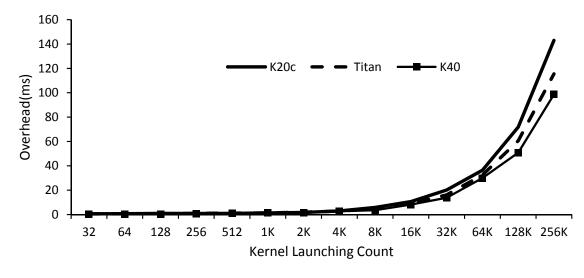

| 7  | CDP launching time.                                                                                                                                                                                                        | 38 |

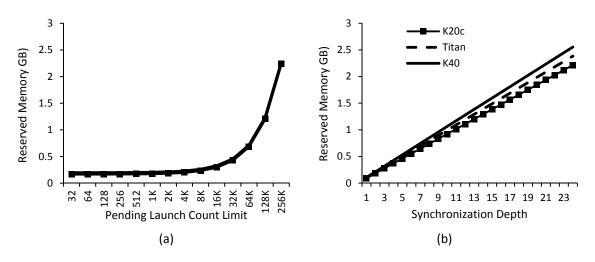

| 8  | Reserved global memory for CDP kernel launch and synchronization                                                                                                                                                           | 39 |

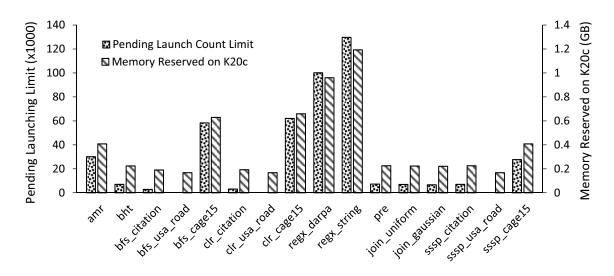

| 9  | Pending launch count limit and reserved memory size                                                                                                                                                                        | 41 |

| 10 | Total child kernel launching count and their average thread count                                                                                                                                                          | 42 |

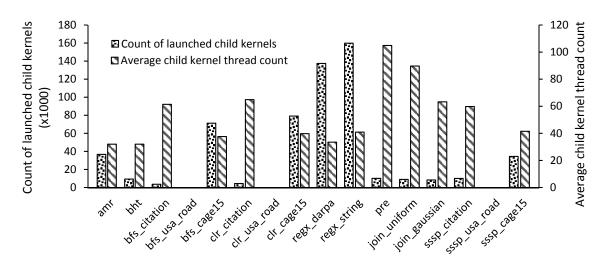

| 11 | Kernel execution trace for BFS_citation iteration 5                                                                                                                                                                        | 43 |

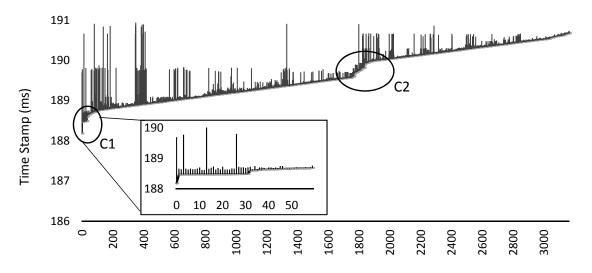

| 12 | DTBL execution model and thread hierarchy where (a) shows the aggregated groups launched by kernel K1 are coalesced to itself and (b) shows the aggregated groups launched by kernel K2 are coalesced to another kernel K3 | 48 |

| 13 | Example code segments for (a) CDP and (b) DTBL                                                                                                                                                                             | 50 |

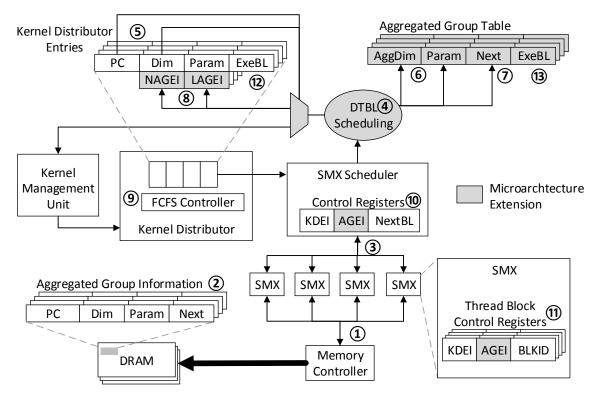

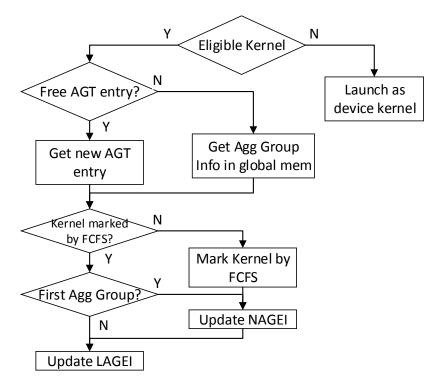

| 14 | Microarchitecture Flow for DTBL                                                                                                                                                                                            | 53 |

| 15 | DTBL scheduling procedure in SMX scheduler                                                                                                                                                                                 | 54 |

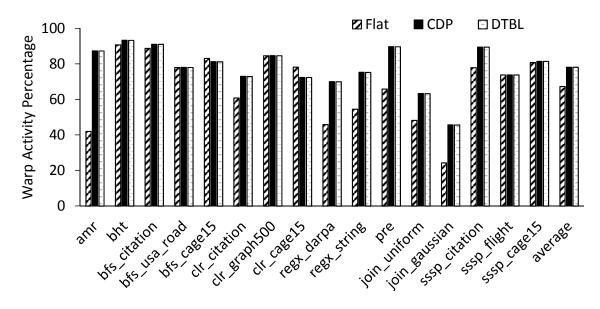

| 16 | Average Percentage of Active Threads in a Warp                                                                                                                                                                             | 63 |

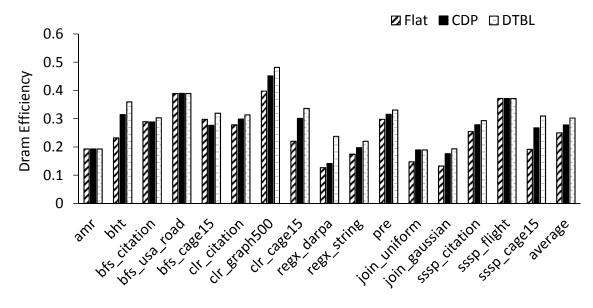

| 17 | DRAM Efficiency                                                                                                                                                                                                            | 64 |

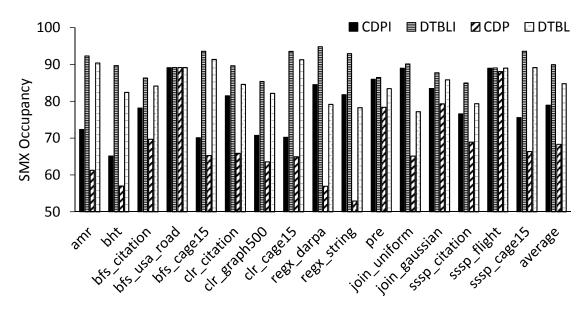

| 18 | SMX Occupancy                                                                                                                                                                                                              | 65 |

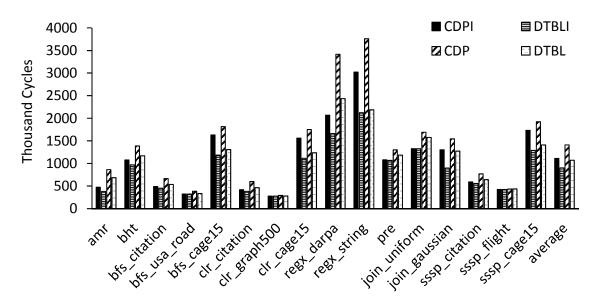

| 19 | Average Waiting Time for a Kernel or an Aggregated Group                                                                                                                                                                   | 66 |

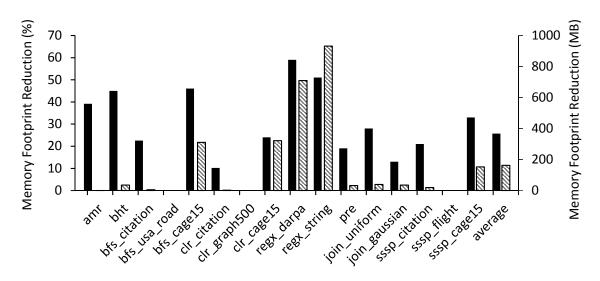

| 20 | Memory Footprint Reduction of DTBL from CDP                                                                                                                                                                                | 67 |

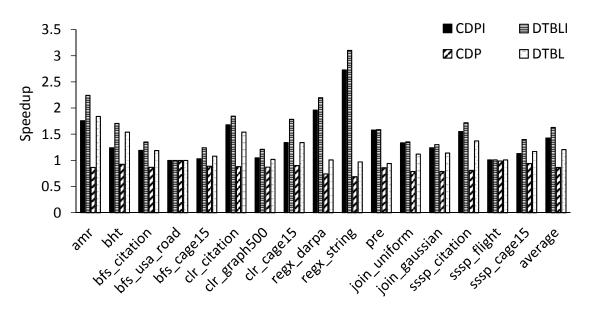

| 21 | Overall Performance in terms of Speedup over Flat Implementation                                                                                                                                                           | 68 |

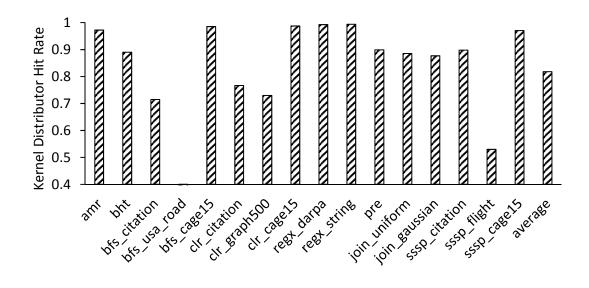

| 22 | KDE Hitrate                                                                                                                                                                                                                | 69 |

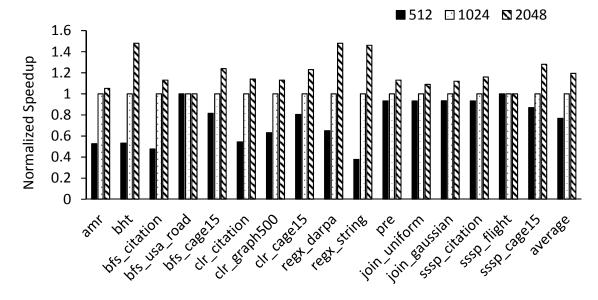

| 23 | Performance Sensitivity to AGT Size Normalized to 1024 Entries                                                                                                                                                             | 70 |

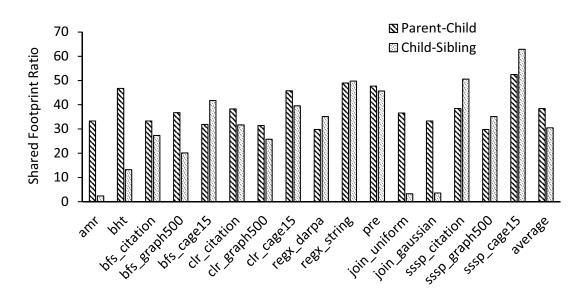

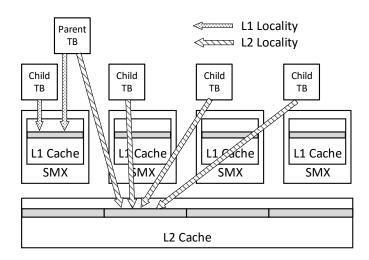

| 24 | Shared footprint ratio for parent-child and child-sibling TBs                                                                                                                                                              | 75 |

| 25 | Parent-Child Locality and Potential Impact on L1 and L2 Cache 76                                                                                                                                                                                                                                |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

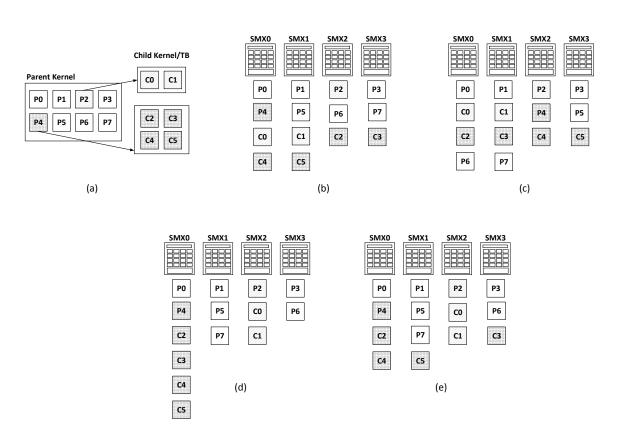

| 26 | <ul> <li>(a) An example of the parent-child kernel/TB launching, (b) its TB scheduling results using the Round-Robin TB scheduler, (c) TB Prioritizing (<i>TB-Pri</i>), (d) Prioritized SMX binding (<i>SMX-Bind</i>) and (e) Adaptive Prioritized SMX Binding (<i>Adaptive-Bind</i>)</li></ul> |

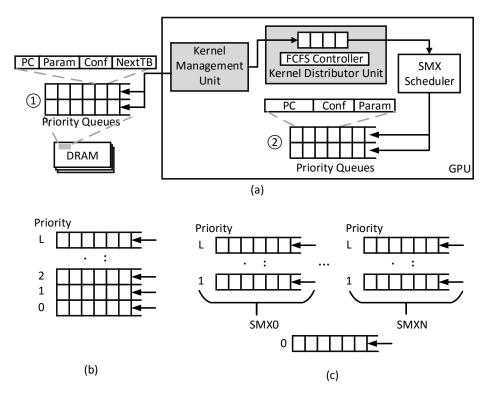

| 27 | Architecture Extension for LaPerm (a), the priority queues used by <i>TB-Pri</i> (b) and the SMX-bound priority queues used by <i>SMX-Bind</i> and <i>Adaptive-Bind</i>                                                                                                                         |

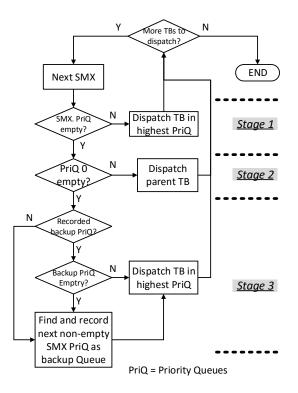

| 28 | LaPerm Scheduler Flow Chart                                                                                                                                                                                                                                                                     |

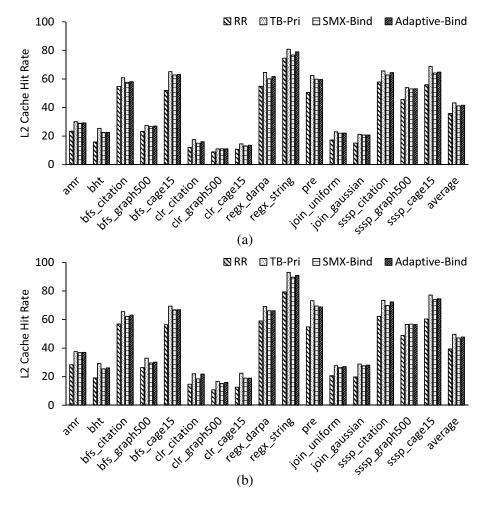

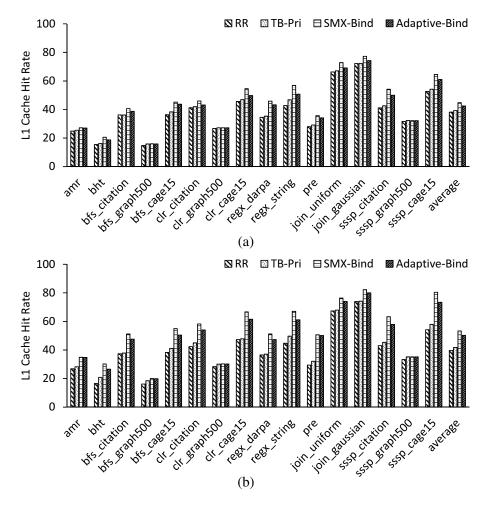

| 29 | L2 cache hit rate when applying LaPerm to (a) CDP and (b) DTBL 92                                                                                                                                                                                                                               |

| 30 | L1 cache hit rate when applying LaPerm to (a) CDP and (b) DTBL 93                                                                                                                                                                                                                               |

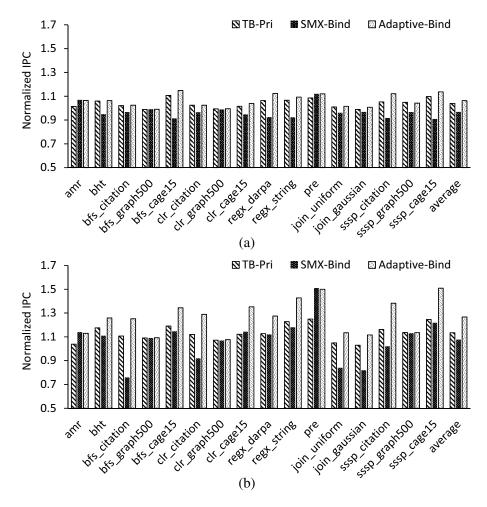

| 31 | Normalized IPC when applying LaPerm to (a) CDP and (b) DTBL 95                                                                                                                                                                                                                                  |

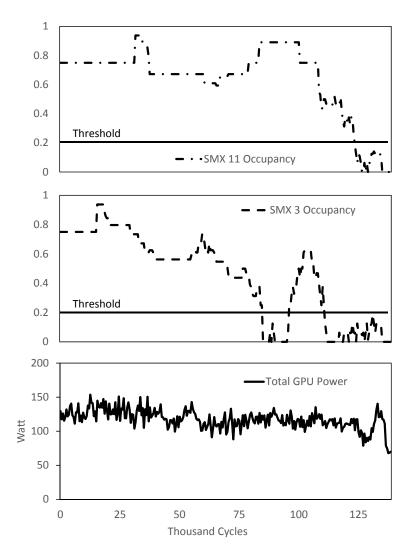

| 32 | A case study for the SMX occupancy and power consumption in one vertex expansion kernel of BFS with DTBL implementation                                                                                                                                                                         |

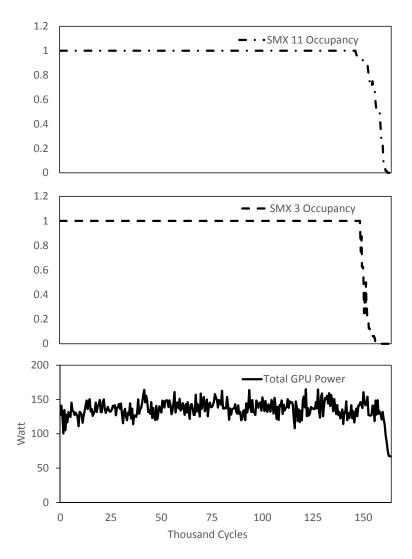

| 33 | A case study for the SMX occupancy and power consumption in one vertex expansion kernel of BFS with PT implementation                                                                                                                                                                           |

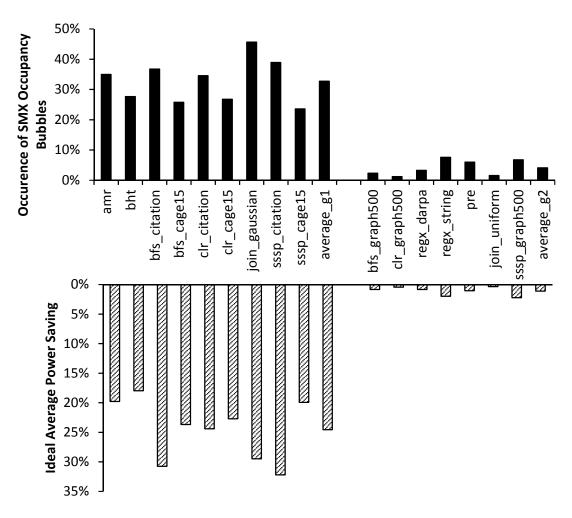

| 34 | The occurrence percentage of <i>SMX Occupancy Bubble</i> for threshold of 0.0625 (4 warps) and ideal average power saving                                                                                                                                                                       |

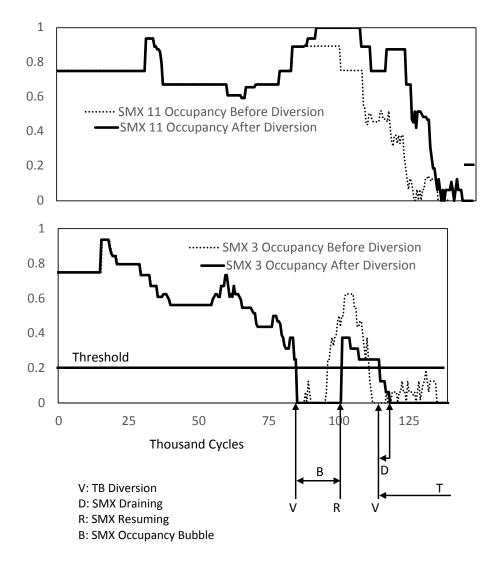

| 35 | A case study for the Dynamic TB Diversion for one vertex expansion kernel<br>of BFS with DTBL implementation                                                                                                                                                                                    |

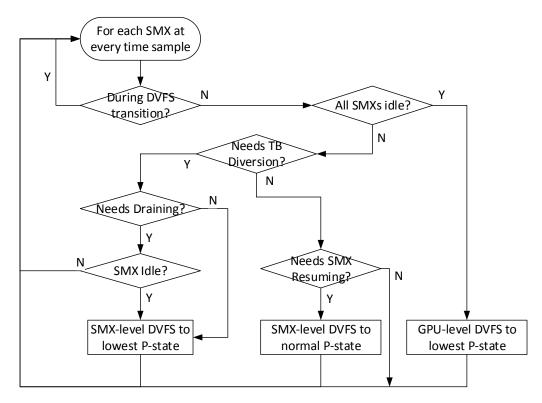

| 36 | High-level Flow Chart for the SMX Occupancy Bubble-based Power Opti-<br>mization for DTBL                                                                                                                                                                                                       |

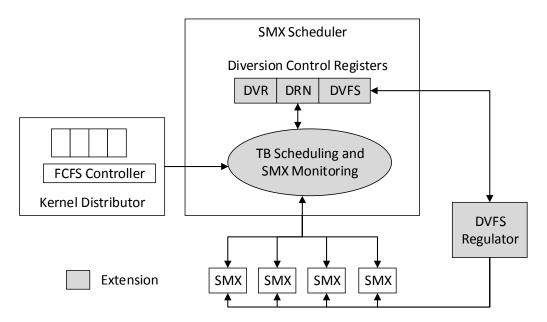

| 37 | Architecture Extension for the SMX Occupancy Bubble-based Power Op-<br>timization for DTBL                                                                                                                                                                                                      |

| 38 | Energy Savings and Performance Loss for the SMX Occupancy Bubble-<br>base Power Optmization ( $P = 500$ cycles)                                                                                                                                                                                 |

| 39 | Energy savings degradation and extra performance loss for off-chip DVFS regulator with the 10000 cycle transition time compared with on-chip DVFS regulator with the fast 500 cycle transition time                                                                                             |

| 40 | Extra Energy savings and extra performance loss when SMX Draining is turned off ( $P = 500$ cycles)                                                                                                                                                                                             |

# LIST OF SYMBOLS AND ABBREVIATIONS

- AMR Adaptive Mesh Refinement

- BFS Breath-First Search

- **BSP** Bulk Synchronous Parallel

- **CDP** CUDA Dynamic Parallelism

- **CTA** Cooperative Thread Array

- **CUDA** Compute Unified Device Architecture

- DFP Dynamically Formed Pockets of Structured Parallelism

- **DTBL** Dynamic Thread Block Launch

- **DVFS** Dynamic Voltage and Frequency Scaling

- GPU Graphics Processing Unit

- **HPC** High Performance Computing

- HWQ Hardware Work Queues

- **IPC** Instruction-Per-Cycle

- **KD** Kernel Distributor

- KMU Kernel Management Unit

- PT Persistent Thread

- SIMD Single-Instruction-Multiple-Data

SMX Stream Multiprocessor

TB Thread Block

# SUMMARY

The objective of this thesis is the development, implementation and optimization of a GPU execution model extension that efficiently supports time-varying, nested, fine-grained dynamic parallelism occurring in the irregular data intensive applications. These dynamically formed pockets of structured parallelism can utilize the recently introduced deviceside nested kernel launch capabilities on GPUs. However, the low utilization of GPU resources and the high cost of the device kernel launch make it still difficult to harness dynamic parallelism on GPUs. This thesis then presents an extension to the common Bulk Synchronous Parallel (BSP) GPU execution model – Dynamic Thread Block Launch (DTBL), which provides the capability of spawning light-weight thread blocks from GPU threads on demand and coalescing them to existing native executing kernels. The finer granularity of a thread block provides effective and efficient control of smaller-scale, dynamically occurring nested pockets of structured parallelism during the computation. Evaluations of DTBL show an average of 1.21x speedup over the baseline implementations. The thesis proposes two classes of optimizations of this model. The first is a thread block scheduling strategy that exploits spatial and temporal reference locality between parent kernels and dynamically launched child kernels. The locality-aware thread block scheduler is able to achieve another 27% increase in the overall performance. The second is an energy efficiency optimization which utilizes the SMX occupancy bubbles during the execution of a DTBL application and converts them to SMX idle period where a flexible DVFS technique can be applied to reduce the dynamic and leakage power to achieve better energy efficiency. By presenting the implementations, measurements and key insights, this thesis takes a step in addressing the challenges and issues in emerging irregular applications.

# CHAPTER I INTRODUCTION

There has been considerable success in harnessing the superior compute and memory bandwidth of Graphics Processing Units (GPUs) to accelerate traditional scientific and engineering computations [7][48][61][60] dominated by structured control and data flows across large data sets using Bulk Synchronous Parallel (BSP) execution models represented by Compute Unified Device Architecture (CUDA) [57] and OpenCL [34]. These applications can be effectively mapped to the rigid 1D-3D massively parallel grid structures underlying modern BSP programming languages for GPUs. However, emerging High Performance Computing (HPC) and enterprise data intensive applications represented by data analytics, graph processing, machine learning and similar applications are dominated by sophisticated algorithms characterized by irregular control, data, and memory access flows challenging the effective harnessing of GPU accelerators.

Despite the above observation, there still exist segments of the computation within many irregular applications that locally exhibit structured control and memory access behaviors. These **D**ynamically **F**ormed Pockets of Structured **P**arallelism (DFP) occur in a data dependent, nested, time-varying manner and their most straightforward implementations usually lead to poor workload balance, control flow divergence, and memory irregularity resulting in poor utilizations and hence lower performance. State-of-the-practice GPU execution models have introduced the device-side kernel launching functionality represented by NVIDIA's CUDA Dynamic Parallelism (CDP) model [58] and OpenCL's device-side kernel enqueue [34] which can be utilized to implement DFP. However, the heavy-weight nature of a GPU kernel, especially the non-trivial *kernel launching overhead*, mitigates the efficiency and effectiveness of such models. This has led to growing demands for a better execution model with lightweight mechanism to support DFP abstractions that more efficiently targets fine-grained dynamic parallelism in irregular applications.

This research seeks to propose such a lightweight execution model based on the investigation and characterization of several irregular applications. The first part of this research characterizes DFP by implementing and evaluating these GPU benchmarks with devicelaunched kernels in CDP [74]. In comparison with the original flat implementations where DFP are processed by individual threads, it is demonstrated that while CDP does address the productivity and algorithmic issues and exhibits potential performance benefit in terms of better control and memory behavior, the ability to harness dynamic parallelism on GPUs is still difficult in most cases due to 1) the low utilization of GPU resources and poor memory latency hiding ability caused by the discrepancy between the fine-grained DFP kernels and limited kernel level concurrency that results in low GPU occupancy and 2) the non-trivial overhead introduced by hardware and software stacks that are associated with the device-side kernel launch functionality and are aggravated by the substantially large number of DFP kernels.

To address the above challenges, the second part of this research proposes an extension to the traditional BSP execution model - Dynamic Thread Block Launch (DTBL) [72], which provides a lightweight mechanism for harnessing dynamic parallelism by spawning Thread Blocks (TBs) from GPU threads on demand and coalescing them with existing native executing kernels. The finer granularity of a TB provides effective and efficient control of smaller-scale, dynamically occurring pockets of structured parallelism during the computation. The TB coalescing process enlarges the pool of TBs that belong to an existing kernel so that they can be scheduled together to the GPU computation units referred as Stream Multiprocessors (SMXs) (using NVIDIA terminology [57]). This effectively increases TB-level concurrency which leads to higher GPU occupancy and utilization. DTBL also introduces substantially more lightweight microarchitecture support, driver and runtime implementations such that the overhead of launching a TB is considerably smaller than launching a kernel. With DTBL, the implementations of irregular CUDA applications launch one or multiple TBs for identified DFP with sufficient parallelism. Benchmark applications implemented with DTBL are evaluated on a cycle-level simulator to demonstrate the improved execution performance compared with the implementations using the flat GPU programming methodology or CDP.

To further explore and develop appropriate optimizations to avail of the potential of the DTBL execution extensions, the third part of this research focuses on the TB scheduling strategies that can effectively exploit spatial and temporal memory reference locality between parent kernels and dynamically launched child kernels, or between child kernels launched from the same parent kernel thread (sibling kernels). Modern GPU microarchitecture schedulers are designed for non-dynamic parallelism settings and are unaware of this new type of locality relationships. Towards this end this research first provides an analysis of parent-child and child-sibling reference locality in a set of benchmark applications. This analysis motivates a locality-aware scheduler referred as LaPerm [73] for dynamic TBs across the SMXs. LaPerm provides multiple levels of prioritization schemes that seek to ensure that child kernels can exploit temporal locality with parent kernels, and spatial and temporal locality with sibling kernels. It also balances overall SMX utilization with effective utilization of the local SMX L1 caches resulting in overall improved system performance. Experimental evaluation on a cycle-level simulator demonstrates that by increasing both the L1 and L2 cache performance, *LaPerm* is able to achieve Instruction-Per-Cycle (IPC) improvement over the original baseline TB scheduler.

The fourth part of this research examines the DTBL from the energy efficiency perspective and proposes an energy saving optimization based on the SMX occupancy phase behavior of DTBL. A comparison is performed between the execution phase behavior of DTBL and the regular GPU programming methodology to handle dynamic workloads such as the Persistent Thread (PT) model where the number of TBs executed on the SMXs are fixed in advance and a global work queue is employed to assign new dynamic work to those TBs. The purpose of such a comparison is to demonstrate the existence of SMX utilization variations when dynamic parallelism evolves and therefore the potential energy saving opportunities brought by the DTBL execution model. Specifically, the SMX occupancy bubbles where the SMX occupancy falls below a threshold are utilized for better energy efficiency, which are performed by 1) designing a new TB diversion and scheduling strategy to convert the SMX occupancy bubbles to SMX idle periods and ii) employing a flexible GPU Dynamic Voltage and Frequency Scaling (DVFS) scheme to reduce energy consumption.

This thesis argues that a GPU execution model with lightweight dynamic spawning of workload and associated scheduling and energy consumption optimizations can efficiently target the fine-grained dynamic parallelism in irregular applications. Specifically, this thesis makes the following contributions.

- Establishing the concept of Dynamically Formed Pockets of Structured Parallelism (DFP) via illustrations of their forms and behavior in emergent irregular GPU applications.

- Characterizing DFP and elaborating insights from implementing multiple data intensive irregular CUDA benchmarks with child kernel launching functionality introduced by the CUDA CDP execution model, specifically in terms of control flow and memory behavior, GPU utilization and hardware/software overhead.

- 3. Designing the Dynamic Thread Block Launch (DTBL) as an effective lightweight execution mechanism for spawning dynamically created parallel work that is able to effectively harness the compute and memory bandwidth of GPUs. This is achieved from two perspectives.

- Fine-grained TB launching and aggregation that increase GPU occupancy and utilization.

- Lightweight microarchitecture and runtime design to alleviate the hardware and software stack overhead.

- 4. Optimizing the scheduling strategy for DTBL to further improve the execution performance by exploring the memory reference locality between the parent TBs and child TBs.

- Exploring energy saving opportunities in DTBL by demonstrating the existence of SMX occupancy bubbles which can be leveraged for better energy efficiency.

The remainder of this thesis is organized as follows. Chapter 2 provides the background and related work of this thesis. Chapter 3 introduces the concept of DFP and its features by characterizing multiple irregular applications with CDP implementations. Chapter 4 proposes the DTBL extension to the current GPU execution model with detailed semantics definition, microarchitecture design, benefits and overhead analysis, and performance evaluation. Chapter 5 describes a memory locality-aware optimization for the DTBL model that is motivated by the memory reference locality relationships between the dynamic TBs in DTBL implementations and efficiently utilizes the GPU memory hierarchy for such locality relationship to achieve overall performance improvement. Chapter 6 examines the DTBL model from the energy and power dissipation perspective and proposes to utilize the SMX occupancy phase behavior for a new energy saving optimization that increases the energy efficiency of DTBL. Chapter 7 is the conclusion of this thesis.

## **CHAPTER II**

# **BACKGROUND AND RELATED WORKS**

This chapter provides the background for this thesis, including an introduction to the GPU execution model and the baseline GPU architecture, the scheduling process on the GPUs, the dynamic parallelism execution model that is supported by the current GPUs and the basic GPU power model adopted by this thesis. The NVIDIA terminology is used throughout the thesis, including its CUDA programming models and the Kepler GK110 architecture as it is the first architecture to support CUDA Dynamic Parallelism (CDP). However, the methodology, analysis and conclusions in this thesis also apply to new architectures and programming models such as AMD's GPUs and the OpenCL [34] programming models. This chapter also reviews the research works from various aspects that are related to this thesis.

## 2.1 Baseline GPU Architecture and CUDA Programming Model

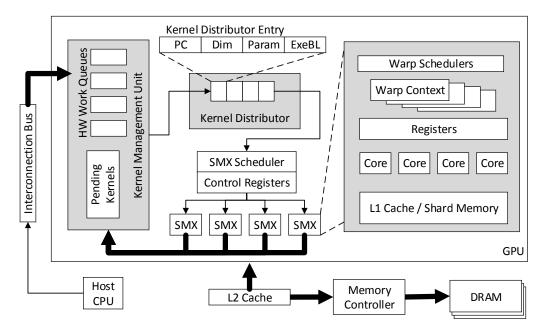

The baseline GPU architecture adopted by this thesis is shown in Figure 1. It is composed of several major functional units: the Kernel Management Unit (KMU), the Kernel Distributor (KD), the computation units referred as Stream Multiprocessor (SMX) and the SMX scheduler which dispatches workload to the SMXs. An NVIDIA Kepler GK110 architecture [54] comprises of multiple SMXs, each of which features 192 single-precision CUDA cores, 64 double-precision units, 32 special function units and 32 load/store units. It also includes 64K, 32-bit registers and 64KB scratch-pad memory that can be used either as a L1 cache or shared memory. An L2 cache is shared across SMXs and connects through one or more memory controllers to the off-chip DRAM which is used as the GPU device memory. The GPU is connected to the host CPU by the interconnection bus and accepts operation commands such as memory copy and kernel launching from the CPU.

Figure 1: Baseline GPU architecture

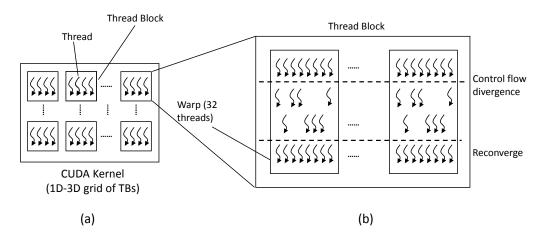

Compute Unified Device Architecture (CUDA) [57] is the programming model introduced by NVIDIA for its GPUs. As shown in Figure 2(a), a CUDA program is expressed as a set of parallel kernels in which threads are grouped together into Thread Block (TB) or Cooperative Thread Array (CTA) and then into 1D-3D grids, all threads executing the same kernel code subject to user-defined synchronization barriers. Multiple memory spaces can be accessed by the GPU threads during their execution, including the global memory which resides in the GPU device memory and is visible to all the threads of a kernel, the shared memory which is visible only to the threads of a TB and holds the data that has the lifetime of a TB, and the local memory that is private to each individual thread. The constant memory and texture memory are two additional memory spaces that are visible to all the threads in the kernel. They reside in the GPU device memory but have different accessing patterns or addressing modes than the global memory.

# 2.2 Kernel, Thread Block and Warp Scheduling on GPUs

The CPU launches GPU kernels by dispatching kernel launching commands. Kernel parameters are passed from the CPU to the GPU at the kernel launching time and stored in

Figure 2: GPU programming model, including (a) CUDA thread hierarchy and (b) warps and control divergence

the GPU global memory with necessary alignment requirements. The parameter addresses are part of the launching command along with other kernel information such as grid/TB dimension configuration and entry PC address. All the launching commands are passed to the GPU through software stream queues (e.g. CUDA stream). Kernels from different streams are independent from each other and may be executed concurrently while kernels from the same stream should be executed in the order that they are launched. The streams are mapped to Hardware Work Queues (HWQ) in the GPU that create hardware-managed connections between the CPU and the GPU. Earlier NVIDIA GPUs combine all streams and map them to only one HWQ, resulting in serialization of kernel launches from different streams. The current generation of NVIDIA GPU introduce Hyper-Q[53] - a technique which constructs multiple HWQs and maps individual streams to each HWQ to realize concurrency. However, if the number of software streams exceeds the number of HWQs, some of them will be combined and serialized. In the baseline GPU architectures, the Kernel Management Unit (KMU) manages multiple HWQs by inspecting and dispatching kernels at the head of the queue to the Kernel Distributor. Once the head kernel is dispatched, the corresponding HWQ stops being inspected by the KMU until the head kernel completes. The KMU also manages all the kernels dynamically launched or suspended by an SMX (e.g. through use of the CUDA Dynamic Parallelism feature) as discussed in section 2.4.

The Kernel Distributor (KD) holds all the active kernels ready for execution. The number of entries in the KD is the same as that of HWQs (32 in the GK110 architecture) as this is the maximum number of independent kernels that can be dispatched by the KMU. Each entry manages a set of registers that record the kernel status including kernel entry PC, grid and TB dimension information, parameter addresses and the number of TBs to complete. The SMX scheduler takes one entry from the KD in first-come-first-serve (FCFS) order and sets up the SMX control registers according to the kernel status. It then distributes the TBs of the kernel to each SMX limited by the maximum number of resident TBs, threads, number of registers, and shared memory space per SMX.

In today's GPU, the SMX scheduler dispatches the TBs of a kernel to the SMX in a round-robin fashion. Each cycle it picks one TB using the increasing order of the TB ID and dispatches it to the next SMX that has enough available resources to execute this specific TB. When a kernel is launched, all SMXs are unoccupied and therefore can accommodate one TB at each cycle, resulting in TBs being evenly distributed across the SMXs. For example, scheduling 100 TBs on a 13-SMX K20 GPU would result in SMX0 being assigned TBs (0, 13, 26, ...), SMX1 being assigned TBs (1, 14, 27, ...) and so on. When all the SMXs are fully occupied by the TBs, the SMX scheduler is not able to dispatch new TBs to the SMXs until one of the older TBs finishes execution. To illustrate it with the same example, suppose each SMX will be fully occupied by 3 TBs. TB 39 cannot be dispatched to SMX0 immediately after TB 38 as there are not enough resources available. At some point, TB 17 on SMX4 becomes the first TB to finish execution so the SMX scheduler can schedule TB 39 to the SMX4 instead of SMX0. This TB scheduling strategy in the baseline GPU architecture is designed to ensure the fairness of occupancy across all the SMXs and thereby execution efficiency. The SMX scheduler keeps updating the control register and the register in each KD entry to reflect the number of TBs that remain to be scheduled as well as those still being executed. When all the TBs of a kernel finish, the KD will release the corresponding kernel entry to accept the next kernel from the KMU.

During execution, a TB is partitioned into groups of 32 threads called a *warp* as the basic thread group executed on a 32-lane Single-Instruction-Multiple-Data (SIMD) unit made of CUDA cores as shown in Figure 2(b). SMXs maintain the warp contexts for the lifetime of the TB. At each cycle, the warp scheduler selects a warp from all the resident warps on the SMX that have no unresolved dependency according to a scheduling policy (e.g. round-robin) and then issues its next instruction to the cores. Each SMX in the GK110 has four warp schedulers and eight instruction dispatch units, allowing four warps to be issued simultaneously. By interleaving the execution of all the issued warps, an SMX is able to achieve hardware multithreading and hide memory latency. All the threads in a warp execute the same instruction in a lock-step fashion. When there is a branch and threads in a warp take different paths, the execution of threads on different paths will be serialized. This is referred to as control flow divergence and results in low SIMD lane utilization. The baseline architecture uses an immediate post-dominator reconvergence technique (PDOM) reconvergence stack [24] to track and reconverge the threads that take different branches. Memory accesses generated by 32 threads in a warp for aligned consecutive word addresses are coalesced into one memory transaction. Otherwise multiple memory transactions are generated to retrieve the data which may increase the memory access latency for the entire warp. This pattern of irregular memory accesses is referred as memory divergence [46].

# 2.3 Concurrent Kernel Execution

Concurrent kernel execution is realized by distributing TBs from different kernels across one or more SMXs. If one kernel does not occupy all the SMXs, the SMX scheduler takes the next kernel and distributes its TBs to the remaining SMXs. When a TB finishes, the corresponding SMX notifies the SMX scheduler to distribute a new block either from the same kernel or from the next kernel entry in the KD if the current kernel does not have any remaining TBs to distribute and the SMX has enough resources available to execute a TB of the next kernel. Therefore, multiple TBs from different kernels can execute on the same SMX [20]. In today's GPU, kernels can be executed concurrently to the limit of 32 (number of entries in KD). Large kernels which either have many TBs or use a large amount of resources are not likely to be executed concurrently. On the other hand, if the kernels in the KD only use a very small amount of SMX resources, the SMX may not be fully occupied even after all the kernels in the KD are distributed, which results in under-utilization of the SMX.

#### 2.4 CUDA Dynamic Parallelism and Device-side Kernel Launch

Recent advances in the GPU programming model and architecture support device-side kernel launches - *CUDA Dynamic Parallelism* [58] - which provides the capability of launching kernels dynamically from the GPU without going back to the host CPU. This new functionality has been provided starting with the Kepler GK110 architecture. The kernel, TB or thread that initiates the device launch is the parent and the kernel that is launched by the parent is the child. Several device-side API calls can be invoked to specify the child kernel configuration, setup parameters, and dispatch kernels through device-side software streams to express dependencies.

When a child kernel is launched, the parameter buffer pointer of the kernel is retrieved through the device runtime API cudaGetParameterBuffer. Then the argument values are stored in the parameter buffer and the kernel is launched by calling cudaLaunchDevice. CDP allows explicit synchronization between the parent and the child through a device runtime API cudaDeviceSynchronize. Launches can be nested from parent to child, then child to grandchild and so on. The deepest nesting level that requires explicit synchronization depth supported on GK110 is 24. Parents will be suspended and yield to child kernels if explicit synchronization is required. If no explicit synchronization is specified, there is no guarantee of the execution order between the child and parent. Concurrent execution of the

child kernels is possible but not guaranteed, depending on the availability of the GPU resources. The 32 concurrent kernels supported on the GK110 architecture include both the host-launched and device-launched kernels. Parent and child kernels have coherent access to global memory with full consistency only at the point when parent kernels launch child kernels or the explicit synchronization is requested. Shared memory and local memory are exclusive for parent and child kernels and are invisible to each other.

In the baseline GPU architecture, there is a path from each SMX to the KMU so that all the SMXs are able to issue new kernel launching commands to the KMU. Similar to host-side launched kernels, parameters are stored in the global memory and the address is passed to the KMU with all other configurations. When a parent decides to yield to a child kernel, the SMX suspends the parent kernel and notifies the KMU to hold the suspended kernel information. The KMU dispatches device-launched or suspended kernels to the KD along with other host-launched kernels in the same manner. Therefore device-launched kernels also take advantage of concurrent kernel execution capability.

Current architecture support of device-side kernel launching comes with non-trivial overhead. The total kernel launching time scales with the number of child kernels, which is composed of the time spent in allocating the parameters, issuing a new launching command from the SMX to the KMU, and dispatching a kernel from the KMU to the KD. Device-side kernel launches also require a substantial global memory footprint. A parent may generate many child kernels which can be pending for a long time before being executed, thus requiring the GPU to reserve a fair amount of memory for storing the associated information of the pending kernels. On the other hand, the device runtime has to save the states of the parent kernel when they are suspended to yield to the child kernels at the explicit synchronization points.

#### 2.5 GPU Power Modeling

This thesis relies on a high-level GPU power model proposed and used in GPUWattch [41]. The model is implemented and integrated with the cycle-level GPU simulator GPGPU-Sim [9] based on the McPAT power model [43].

The GPU power is composed of the leakage power, the idle SMX power, as well as the dynamic power of all the GPU components, including registers, shared memory, execution units, caches, main memory, etc. The dynamic power of the GPU components are computed by collecting the microarchitectural parameters of each component through GPGPU-Sim and then feeding them into the McPAT model with several adapated blocks specifically designed for the GPU microarchitecture. The idle SMX power is determined by executing several microbenchmarks on a real GPU and controlling the number of active SMXs by using different number of TBs and configurations. The leakage power is modeled by measuring the GPU constant power as described in [41].

The GPU has multiple execution performance capability and power consumption states referred as the P-state, each of which has the corresponding voltage and frequency settings [52]. The P-state with the highest performance will also have the highest power consumption, and vice versa. The DVFS technique has been made available on the current NVIDIA GPU to adjust the P-state for the entire GPU. However, P-state of each SMX cannot be controlled separately. The voltages scaling follows the model used in [2] for different frequencies under different technology.

## 2.6 Related Works

There has been considerable effort in developing new GPU algorithms, frameworks and methodologies for the irregular application domain. This section briefly reviews the research works that are related to this thesis.

#### 2.6.1 Characterization of GPU Workloads

Characterization and analysis of GPU applications can be traced to a very early time, mainly focusing on regular applications which have rigid 1D-3D data structures that can be directly mapped to GPU architectures. Kerr et al. [33] characterizes GPU kernels using different metrics and proposes methodologies to write GPU programs with better performance. The benchmark suites Rodinia [17] proposed by Che et al., Parboil [68] proposed by Stratton et al., and SHOC [21] proposed by Danalis are some representative benchmarks used in GPU studies. Research with these benchmarks have focused on approaches to utilize the structured BSP model efficiently.

Recently people have been investigating the performance of new irregular applications on GPUs which exhibit more unstructured control flow and memory behavior. These applications are represented by graph processing, machine learning, relational computing and etc. Examples of these applications implemented by GPUs include 1) Adaptive Mesh Refinement (AMR) used for combustion simulations [36] that operates on grid-like structure and refines each cell in the grid according to certain temperature conditions, 2) graph coloring problem whose goal is to assign a color to each vertex in the graph such that no neighboring vertices have the same color [19], 3) product recommendation systems that use item-based collaborative filtering algorithm to construct a similarity matrix containing the customer purchasing information, and 4) the relational JOIN operator where two input relation arrays are examined to generate a new relation array consisting of the key-value pairs where the keys are present in both of the input arrays [22]. To facilitate the development of new GPU programming methodologies or execution models, many researchers have performed systematic characterization and analysis of these irregular applications. Burtscher et al. [14] study the behavior of irregular applications on GPUs with quantitative metrics for both control flow and memory access irregularity. Che et al. [16] use the Pannotia benchmark suite to illustrate the characteristics of irregular graph applications on GPUs. These works show that implementations of irregular GPUs applications mainly suffer from workload imbalance and scattered memory accesses that cause control flow and memory irregularity.

#### 2.6.2 Research on Irregular Applications on GPUs

Researchers have been investigating and seeking more efficient solutions for the irregular applications, e.g., implementing them using the BSP model but with new programming methodologies. Gupta et al. [27] introduce the Persistent Thread (PT) programming style on GPUs where a number of TBs that occupy all the SMXs are initially launched and stay on the GPU for the life time of the kernel. These TBs dynamically generate tasks that are appended to a globally visible software queue while persistently consuming tasks. The goal of the PT model is to achieve overall GPU workload balance especially across the SMXs while processing evolving irregularity in the programs. Merrill [47] implement Breath-First Search (BFS) on GPUs using fine-grained TBs to adaptively explore the neighbors of vertices in parallel which can utilize the SMXs more efficiently and achieve better fine-grained load balance. However, such effort has not been applied to other irregular applications in a more general form. Other research works on GPU irregular applications include redesigning data structures and re-organizing memory accesses through algorithm, compiler and runtime optimizations to harness the GPU capability. Solomon et al. [66] investigate and change the synchronization behavior of the BFS algorithm as well as that of a Matrix Parenthesization algorithm to improve performance. Zhang et al. [80] present a systematic transformation framework to remove dynamic irregularities in both control flows and memory references by data relocation and memory reference redirection. Wu et al. [77] employ the kernel fusion technique for the implementations of relational algebra operators on the GPU to reduce memory irregularity in all levels of memory hierarchies. The goal of these studies is to decrease the irregularity of the control flow and memory behavior or adapt the algorithm to the GPU architectures.

#### 2.6.3 Research on Nested Dynamic Parallelism

It has been observed that many of the irregularities can be converted or implemented as fine-grained dynamically formed structured parallelism. Improving the performance of irregular applications by handling dynamic parallelism is an important and challenging question in the GPU programming community. Lars et al. [11] implement the nested parallel programming language NESL on the GPU by flattening the nested parallelism semantics using compiler and runtime techniques. Lee et al. [38] propose an auto-tuning framework that efficiently maps the nested patterns in GPU applications using logical multidimensional domain with pruning constraints and adaptive shared memory management. Steffen et al. [67] propose a dynamic micro-kernel architecture for global rendering algorithm which supports dynamically spawning threads as a new warp to execute a subsection of the parent threads code. Orr et al. [59] design a task aggregation framework on GPU based on the channel abstraction proposed by Gaster et al [25]. Each channel is defined as a finite queue in virtual memory (global memory space that is visible to both the CPU and the GPU) whose elements are dynamically generated tasks that execute the same kernel function. Kim et al. [35] implement a hardware work list and investigate several different work distribution schemes to process dynamically generated parallel work elements. All these works have been taking steps toward more effective and efficient solutions for processing dynamic parallelism in irregular applications.

The prevalence of dynamic parallelism execution models on GPUs such as CDP and OpenCL device-side enqueue enables a more general, flexible and productive implementation strategy for the irregular applications by using device-launched kernels for dynamically generated workload. As a newly introduced technology, the utilizations of CDP have been reported by a few research works. Wang et al. [71] propose the CDP implementation of graph-based substructure pattern mining by using device-launched kernels to expand the depth-first search tree in parallel. DiMarco et al. [23] analyze the clustering algorithm including the K-means clustering and the hierarchical clustering with CDP implementation which invokes child kernels directly from GPU for data updating to avoid CPU-GPU interaction. Zhang et al. [81] apply CDP to a set of graph algorithms on the GPU by adapting to their data-driven nature. The idea is to launch a kernel from the CPU to process the outer loop of the graph problems followed by another kernel launched from the GPU to process the inner loop for vertex expansion. Li et al. [42] uses device-side kernel launches for irregular loops and recursive computations. Improved overall performance are reported in these studies when the implementations are carefully tuned to avoid excessive CPU-GPU communications and device kernel launching overhead while taking advantage of the flexibility of the CDP model.

However, the device-launched kernels in the above implementations are applied only for the coarse-grained dynamic parallelism and are able to avoid the CPU-GPU communication overhead in the original non-CDP implementations. In most cases, the fine-grained dynamic parallelism is the major source of irregularity in these applications and can dominate the performance consequences. Device-side kernel launching functionality is still difficult to be fully utilized in its current form for the fine-grained dynamic parallelism due to its non-trivial overhead especially in the scenario where hundreds or thousands of kernels have to be launched. Therefore, researchers have been proposing different extensions and optimizations. Yang et al. [79] analyze the nested parallelism in several benchmarks and observe that CDP implementations dramatically reduce memory bandwidth. They then propose a compiler technique that can dynamically activate or deactivate the GPU threads to adapt to the evolving parallelism in the applications. Chen et al. [18], on the other hand, propose a compiler technique "Free Launch" that reuses the parent threads to process the child kernel tasks and dynamically converts programs written with CDP into the ones that only employ parent threads. This is accomplished by a set of transformations to deal with thread mapping, shared memory usage and synchronizations. All these techniques can apply to the regular BSP execution model and employ compiler and runtime optimizations to avoid the extra overhead introduced by device-side kernel launching.

#### 2.6.4 Research on GPU Scheduling

The SMX scheduling strategy has an essential impact on the overall performance of GPUs, especially when they are incorporated with the cache and memory system performance. Research works in this area include new warp scheduler, TB schedulers and new memory system designs. Rogers et al. [63] employ multiple warp schedulers to achieve optimal cache performance in different scenarios. The schedulers are able to adaptively choose which warp to be dispatched according to the heuristics that are generated from cache behavior. Narasiman et al. [50] propose a two-level warp scheduler to minimize the memory access latency. The basic idea is to divide pending warps into multiple groups so that warps in each group can be scheduled together. Group switching only happens when warps from one group are all stalled because of the long-latency memory operations. Jog et al. [31] advance the two-level warp scheduling technique to make it TB aware so that the memory locality existing in the warps that belong to the same TB can be better accommodated when warp group switching happens. Kayıran et al. [32] demonstrate that the memory contention could be caused by scheduling maximum possible number of TBs as this limit is only determined based on SMX occupancy but does not take into account the memory system performance. They propose to use a dynamic TB scheduling mechanism to minimize such contention. Lee et al. [39] make the argument that consecutive TBs may have memory reference locality which can be better utilized to improve cache and memory system performance when scheduled on the same SMX instead of neighboring SMXs. Rhu et al. [62] design a locality-aware memory hierarchy that is both able to accept coarsegrained memory accesses that are common in regular applications as well as adapt to the fine-grained memory access patterns in irregular applications on GPU. In both cases, the newly designed memory system is able to achieve high bandwidth utilization. While the above works have demonstrated considerable effort in memory system aware scheduling, none of them are directly applicable to the domain of dynamic parallelism in GPUs where new types of locality behaviors are introduced, e.g., spatial and temporal reference locality between parent kernels and child kernels.

#### 2.6.5 Research on GPU Energy Efficiency

Many studies have explored and analyzed the energy efficiency of GPUs. Different power models have been proposed [44][29] to estimate the GPU power consumption more accurately, which could in turn facilitate more research on power-based GPU optimizations. DVFS and power gating technology have been proposed for GPUs on multiple levels. Jiao et al. [30] study the benefit of concurrent kernel execution from the power consumption perspective and combine it with DVFS to improve energy efficiency. Ge et al. [26] investigate the impacts of DVFS on applications executed on the Tesla K20 GPU. Abdel-Majeed et al. [3] propose a tri-modal register access control unit as well as an active mask aware activity gain unit to reduce both the leakage power and the dynamic power of GPU register files. Lee et al. [40] present a warp-compression scheme that reduces the data redundancy within a warp by compressing the register values so that power gating can be applied to unused register banks to save register file power consumption. Abdel-Majeed et al. [4] propose to schedule instructions of the same type together so that the execution units can have a long window of idlenss to be turned off with power gating. They [5] also discover the existence of significant fine-grained pipeline bubbles in warp execution and convert these bubble to potential energy saving opportunities using a specific scheduling startegy so that power-gating can be applied on the idle warp lanes to reduce leakage energy. Xu et al. [78] study the behavior of branch divergence and propose a warp scheduler to schedule warps with similar branch divergence patterns together to create long warp lanes idleness for applying power gating. Wang et al. [76] proposes to power gate GPU caches when there are no cache requests. While the energy saving optimizations proposed by the above works are based on the GPU applications implemented with regular BSP model and may also show benefits in the dynamic parallelism from a general perspective, there is still a lack of new energy efficiency studies that are applicable to the dynamic

parallelism settings on GPU.

# 2.6.6 Summary

In summary, while the earlier studies and research works discuss the irregular applications on GPUs from various aspects, this thesis differs with them in addressing the problem of fine-grained dynamic parallelism in irregular applications and seeks a more efficient solution with new GPU execution model extensions and optimizations.

# **CHAPTER III**

# DYNAMIC PARALLELISM IN IRREGULAR APPLICATIONS

As the first part of this thesis, this chapter explores multiple data intensive irregular CUDA applications on GPUs with CUDA Dynamic Parallelism (CDP) support and establishes the concept of **D**ynamically Formed Pockets of Structured **P**arallelism (DFP) through detailed analysis of the benchmark applications in terms of control flow and memory behavior.

# 3.1 Impact of Irregular Applications

The CUDA and OpenCL programming model is structured around massively parallel threads grouped into TBs organized into 1D to 3D grids. Data parallel computations over multidimensional arrays of data fit well within this model where each thread can be mapped into a logically contiguous partition of the data set.

Emerging data intensive applications are increasingly irregular by operating on unstructured data such as trees, graphs, relational data and adaptive meshes. These applications have inherent time-varying, workload-dependent and unpredictable memory and control flow behavior that may cause severe workload imbalance, poor memory system performance and eventually low GPU utilization. For example, typical GPU implementations for vertex expansion operations that are commonly used in graph problems assign one thread to expand each vertex in the vertex frontier with a loop that iterates over all the neighbors. Since the number of neighbors for each vertex can vary, the implementation may suffer from poor workload balance across threads. Further, vertex expansion can generate (depending on the choice of data structure) non-coalesced memory accesses due to the lack of spatial locality across adjacent vertices leading to multiple memory transactions and increasing memory divergence, e.g., threads finish memory instructions at different times.

Another common strategy for handling unstructured data is to use loop iterations within

each BSP thread to access non-contiguous data elements. This too leads to increased memory divergence and load imbalance. As data structures become more diverse, the mapping of data to threads becomes more complex and variance in memory access patterns and control flow grow accordingly.

## 3.2 Dynamically Formed Pockets of Structured Parallelism

Structured memory accesses and uniform control flow make the best use of the computational and memory bandwidth of GPUs. In spite of the observations in Section 3.1, one can observe **D**ynamically **F**ormed Pockets of Structured **P**arallelism (DFP) in these applications that can locally effectively exploit the GPU compute and memory bandwidth. For example, in vertex expansion common data structures used in graph problems (e.g. Compressed Sparse Row or CSR [65]) store neighbors of one vertex in consecutive addresses and the memory access can be coalesced when neighbors are explored in parallel. In adaptive mesh refinement used in combustion simulations, certain parts of the mesh will be refined in parallel into a finer grained mesh creating hierarchical nested grid structures each of which may be of different dimensions. In general, DFP commonly occurs in one of the following two patterns:

**Static Data Structure Traversal.** Applications have irregular but statically defined data structures while the algorithms that traverse them encounter varying degrees of parallelism. Graph and tree traversal algorithms such as breadth first search (BFS) are examples in this category.

**Dynamic Data Generation.** The application data structures themselves are generated during execution and their form and extent are themselves data dependent. For example, combustion simulation (adaptive mesh refinement), tree generation (indexing) and the relational JOIN operator all start from an initial data set and dynamically generate new irregularly structured data sets in parallel.

Given the preceding view of the behaviors of irregular applications the remainder of

this chapter addresses the characterization and analysis.

## 3.3 Implementation Using CUDA Dynamic Parallelism

The introduction of device-side kernel launching in GPUs enables an implementation scheme that new child kernels are dynamically invoked for any identified DFP in irregular applications. In the vertex expansion example, the original neighbor exploration loop can be replaced by a dynamically launched kernel that employs uniform control flow. The approach can potentially increase the performance by reducing control flow divergence. For some common data structures used in this problem such as Compressed Sparse Row (CSR) where neighbor IDs of each vertex are stored in consecutive addresses, parallel neighbor exploration may also generate coalesced memory accesses.

A common code structure for implementing DFP using device-launched kernels in CDP is shown in Listing 3.1, where a parent thread checks some conditions and determine whether new parallel workload should be launched through childKernel either to traverse a new portion of the data structure or to generate new data sets. A typical condition is that whether the dynamic workload has sufficient parallelism, which is designed to avoid the low utilization of the SIMD lanes in each SMX. A straightforward understanding of CDP implementation is that it replaces the parallel loops performed by threads in the non-CDP implementation by child kernels. Specifically, such implementations consider the following aspects.

```

1 //executed by each thread in parent kernel

2 threadData = getData(threadId);

3 if(condition(threadData))

4 childKernel<<<TBS, THREADS>>>

5 (threadData, ...);

```

Listing 3.1: Common code structure that handles DFP with CDP

**Parallel computation workload.** As defined in DFP, the newly launched kernels handle the parallel computation workload that is discovered dynamically by a parent thread at runtime. This is in comparison to the unbalanced GPU implementations where each thread could use a loop with different iteration count to deal with the computation. Since parent threads only have to issue a child kernel and child kernels handle only parallel computation with little or no control divergence, the CDP implementation can achieve higher GPU utilization. However, it should be noted that sometimes there is not enough parallelism to launch a child kernel. For example, if the neighbor degree in vertex expansion problem is less than the warp size, SIMD lanes cannot be fully utilized if a new kernel is launched for expanding that vertex. In this case, the computation will still be left to the parent kernel.

**Memory access patterns.** The memory access pattern in a CDP implementation can be different from a non-CDP implementation. The memory addresses that are accessed by one thread in different loop iterations in a non-CDP implementation are now accessed by contiguous threads in a child kernel using one memory instruction. This could effectively change the number of coalesced memory accesses as well as cache hit rate.

**Recursion.** Recursive kernel launch is possible with the CDP support on GPUs. For some of the unstructured applications, it is necessary to recursively launch new computation dynamically. Non-CDP implementation tends to either convert the recursive algorithm to loop iterations or manage stack-based data structure at both the host and the device. The CDP implementation simply calls the same kernel recursively.

**Concurrent kernel execution.** Child kernels are launched independently from each other and can be executed concurrently. The implementation uses one stream for each child kernel launch. Although no concurrency can be guaranteed from the perspective of GPU architectural support of CDP [58], the use of CUDA streams can increase the possibility to the most extent.

**Child kernel configuration.** A common practice for GPU programming is to partition workload between TBs and then between threads. The same argument holds true for child

kernels in the CDP implementations. The implementations experiment with different TB sizes and grid sizes to generate optimal performance. TB sizes should be multiple of 32 to eliminate any intra-warp thread divergence for child kernels. When the block size is not a multiple of 32, the remaining threads are executed by the parent kernel. This is analogous to the loop transformation that unrolls a loop k times by creating two loops - one that is unrolled k times and one that has loop bounds of ( $N \mod k$ ) where N is the loop bound.

**Shared memory.** The current form of CDP does not allow the child kernel to access the shared memory declared by the parent kernel. Therefore, if the dynamically launched child kernel needs to access the data stored in the shared memory, CDP implementations either pass the data value directly as the kernel argument or dump them into global memory. The former solution can only deal with small number of arguments and the latter solution could introduce large memory and runtime overhead.

**Synchronization.** CDP supports explicit synchronization between parent and child kernels at the substantial cost of both execution time and memory footprint. Therefore, the implementation would avoid using synchronization as much as possible. However, there are still a few cases that synchronization is necessary to conserve either temporal or spatial ordering consistency.

# 3.4 Characterization of CDP Implementations of Irregular Applications

In order to identify the major characteristics of DFP in the irregular applications, experiments are performed on multiple GPUs with Kepler GK110 architectures, including NVIDIA Tesla K20c, Geforce Titan and Tesla K40. Table 1 shows the features of these GPUs. Both non-CDP implementations and CDP implementations of the unstructured applications are examined. The CUDA 5.5 toolkit is used including the nvcc compiler and the runtime library. For CDP implementations, the compiler also links against CUDA device runtime library, i.e. -lcudadevrt. The CUDA Profiler NVProf 5.5 [55] is used to measure the metrics and the overall execution time of the kernels. Benchmark performance is

|                             | Tesla K20c | Geforce Titan | Tesla K40 |

|-----------------------------|------------|---------------|-----------|

| SMX                         | 13         | 14            | 15        |

| Cores                       | 2496       | 2688          | 2880      |

| Clock Frequency (MHz)       | 706        | 837           | 745       |

| Global Memory Capacity (GB) | 5          | 6             | 12        |

| Memory Bandwidth (GB/s)     | 208        | 288           | 288       |

Table 1: Configurations of the GPUs used for CDP characterization experiments

evaluated on K20c and CDP overheads are compared across all the three GPUs.

The non-CDP implementation are compared with the CDP implementation of the unstructured applications. In both cases, inputs are evenly partitioned among threads and TBs. In the non-CDP case, DFP is handled by individual threads respectively, generally through loops. The CDP implementation uses dynamically launched kernels for parallel computations detected through DFP.

To evaluate the impact of CDP implementations on both the control flow and memory access, the following hardware metrics are used.

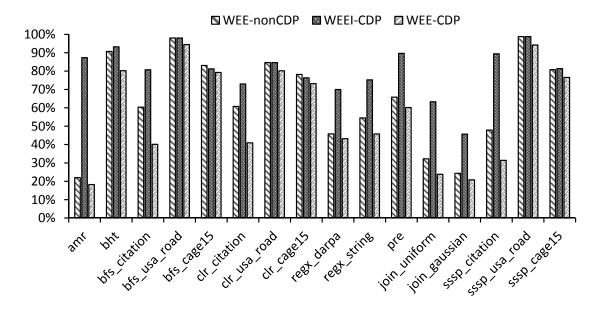

warp\_execution\_efficiency (WEE). This metric measures the ratio of active threads within a warp to the total number of threads in a warp (32) for all executed instructions. It is an indication of the control divergence or workload unbalance in the unstructured applications. Note that NVProf does not allow separate metrics measurement for parent kernels and child kernels in CDP, so the metric measured by NVProf are affected by the parent kernel execution, the child kernel execution and the child *kernel launching overhead* (recall that the overhead includes child kernel parameter passing and device runtime management). The following approach is uesd to measure and compute the warp execution efficiency excluding CDP kernel launching overhead and referred to as the ideal WEE (WEEI) since it represents the ideal efficiency that can be achieved:

$$WEEI = \frac{WEE\_parent * inst\_parent + WEE\_children * inst\_children}{inst\_parent + inst\_children}$$

In the equation, inst\_parent and inst\_children are the effective executed instruction by the parent and children respectively. When measuring WEE\_parent and inst\_parent, the child

kernel launch code are removed from the parent kernel. A warm up kernel is executed before the parent kernel to make sure the parent kernel execution path does not change when child kernels are removed. When measuring WEE\_children and inst\_children, the child kernels are extracted and launched from the hosts using the same configuration and input data as the device launch. By doing this the CDP *kernel launching overhead* is excluded in the measurement. The argument is that this approach is accurate enough to generate WEEI as it only depends on execution path but not any hardware-dependent factors such as warp scheduling and child kernel scheduling policy. The purpose of WEEI is to demonstrate the potential benefit of CDP implementation of DFP by setting up the possible upper bound.

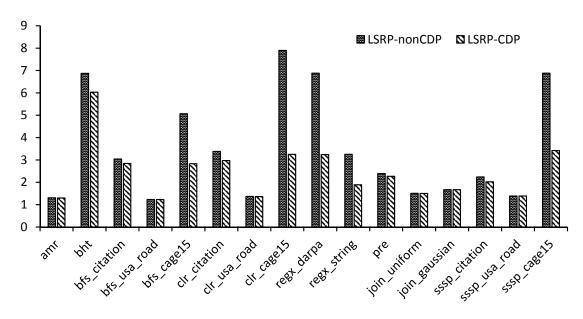

**ldst\_replay\_overhead (LSRP).** This metric measures the average number of replays for each load/store instruction executed. Instructions are replayed when there is bank conflict or non-coalesced memory access. Therefore, LSRP is able to capture the memory irregularity [14]. Since LSRP may be dependent on the execution history (e.g. cache and RAM access history), it is not reasonable to separate the parent kernel and child kernels to measure ideal LSRP for CDP implementations as for WEE. However, measuring the number of load/store instructions separately leads to the conclusion that the load/store instructions from *kernel launching overhead* only comprise a very small percentage of all the load/store instructions, so the directly measured LSRP can still be a good indication for memory divergence affected by CDP.

l2\_cache\_hit\_rate (L2HIT). This metric measures the L2 cache hit rate and captures the memory locality in the program either for a thread or for threads from interleaved warps. Again, L2HIT is measured directly without excluding the child *kernel launching overhead*.

### 3.4.1 Benchmarks

Eight irregular benchmark applications are selected with different input data sets as shown in Table 2. The source code of these applications are from the latest benchmark suites or implemented as described in recently published papers. These applications are reimplemented with CDP. The following is a brief description of these irregular applications.