## MODEL, PREDICT, AND MITIGATE SCALABILITY BOTTLENECKS FOR PARALLEL APPLICATION ON MANY-CORE PROCESSORS

A Dissertation Presented to The Academic Faculty

By

Ching-Kai Liang

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Computer Science

Georgia Institute of Technology

August 2018

Copyright © Ching-Kai Liang 2018

## MODEL, PREDICT, AND MITIGATE SCALABILITY BOTTLENECKS FOR PARALLEL APPLICATION ON MANY-CORE PROCESSORS

Approved by:

Dr. Milos Prvulovic School of Computer Science *Georgia Institute of Technology*

Dr. Hyesoon Kim School of Computer Science *Georgia Institute of Technology*

Dr. Moinuddin K. Qureshi School of Computer Science *Georgia Institute of Technology*  Dr. Sudhakar Yalamanchili School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Christopher J. Hughes Intel Research Intel

Date Approved: July 16, 2018

To my beloved wife and our first daughter whom I have received endless support and love, and to my parents and sister whom I given me strength and guidance to overcome any obstacle in life

#### ACKNOWLEDGEMENTS

I would like to express my deepest appreciation and gratitude to my advisor, Dr. Milos Prvulovic. Without his vision, encouragement, and advice, I would not have been possible to finish this journey. From our first work on synchronization accelerator, to writing the thesis at the end, he constantly providing insightful feedback and directly pointed out any improvements I needed. I would also like to thank my committee members, Dr. Sudhakar Yalamanchili, Dr. Hyesoon Kim, Dr. Moinuddin Qureshi, and Dr. Christopher Hughes for their support and valuable input in improving my thesis.

My Ph.D would also not be successfully finished without the great support and encouragement from my family. My wife, Yi-Ting Tsai, has supported me throughout this journey, even gave birth to our daughter, Kyra. She is marvelously wife and mother and shouldered many responsibilities to relive my pressure and let me concentrate on my PhD. My mother, Sue Wang, whom have given me the greatest love and care any child can ask for and supported my decision to get a PhD degree. My sister, Wendy Liang, whom have pushed me and challenged me to bring out the best in me, and ensured I kept pushing toward the finish line and never give up.

I would also like to thank many friends and colleague. Ioannis Doudalis, Jungju Oh, and Anshuman Goswami, who are senior members of my lab and gave me many helps along the way. Sunjae Park, whom we road side-by-side along the PhD journey, gave me great support for not just work in school, but also navigating the new life as a parent. Chia-Chen Chou, whom reviewed many of my paper submissions and draft run presentations, helped me improve my craft work as an effective researcher. Yu-Shan Lin, whom was a great friend stood by my side during my first few years. Christine Lin, let me stay with her for five years and was a family to me when I first arrived in Atlanta.

Last but not the least, I would like to thank the many people whom have helped me and shaped me to this stage in my life. Many teachers and friends have taught me how to navigate the difficulties in life and how to accomplish my dream by hard work and perseverance.

# TABLE OF CONTENTS

| Acknow    | vledgments                               |

|-----------|------------------------------------------|

| List of ' | Tables    x                              |

| List of ] | F <b>igures</b>                          |

| Summa     | <b>ry</b>                                |

| Chapte    | <b>r 1: INTRODUCTION</b> 1               |

| 1.1       | Multi-core Era and Parallel Applications |

| 1.2       | Scalability challenges                   |

|           | 1.2.1 Synchronization operation overhead |

|           | 1.2.2 Thread Count                       |

|           | 1.2.3 Lock Contention                    |

| 1.3       | Thesis Statement                         |

| 1.4       | Thesis Overview                          |

| Chapte    | r 2: BACKGROUND AND RELATED WORK         |

| 2.1       | Synchronization Accelerators             |

| 2.2       | Performance Modeling 17                  |

|           | 2.2.1 RD analysis                        |

|        | 2.2.2  | Tools for Analysis of Performance Scaling                                        | 19 |

|--------|--------|----------------------------------------------------------------------------------|----|

| 2.3    | Lock ( | Contention Analysis                                                              | 20 |

|        | 2.3.1  | HW/SW lock contention reduction mechanism                                        | 20 |

|        | 2.3.2  | Lock profiling tools                                                             | 21 |

|        | 2.3.3  | Lock contention models                                                           | 22 |

|        | 2.3.4  | Lock contention modeling for database systems                                    | 23 |

| Chapte |        | SAR: MINIMALISTIC SYNCHRONIZATION ACCELERATOR<br>TH RESOURCE OVERFLOW MANAGEMENT | 26 |

| 3.1    | Design | n of MiSAR                                                                       | 26 |

|        | 3.1.1  | Allocate/Deallocate MSA Entry                                                    | 28 |

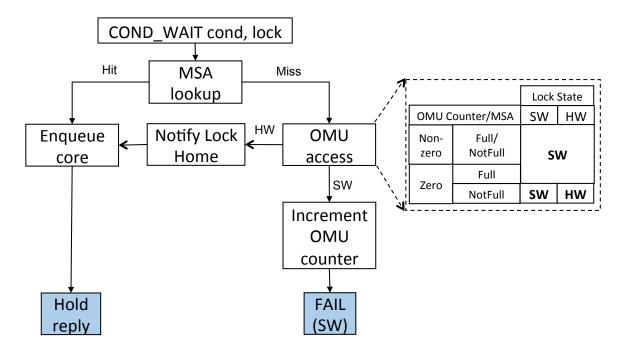

|        | 3.1.2  | Overflow Management Unit (OMU)                                                   | 28 |

| 3.2    | Synch  | ronization Primitives                                                            | 31 |

|        | 3.2.1  | Lock Synchronization                                                             | 31 |

|        | 3.2.2  | Barrier Synchronization                                                          | 34 |

|        | 3.2.3  | Condition Variable                                                               | 36 |

| 3.3    | Optim  | ization                                                                          | 41 |

| 3.4    | Evalua | ntion                                                                            | 43 |

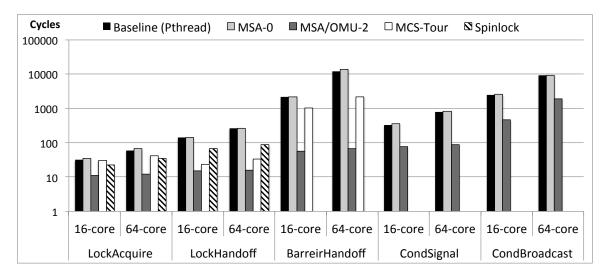

|        | 3.4.1  | Raw Synchronization Latency                                                      | 44 |

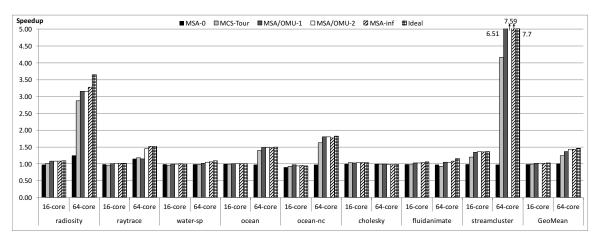

|        | 3.4.2  | Benchmark Evaluation                                                             | 45 |

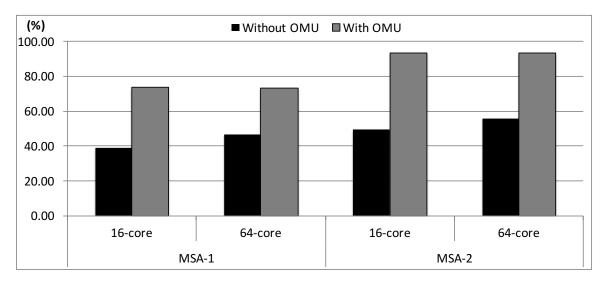

|        | 3.4.3  | Coverage Improvement from OMU                                                    | 47 |

|        | 3.4.4  | Lock Optimization                                                                | 47 |

|        | 3.4.5  | Synchronization Breakdown                                                        | 48 |

| Chapter 4: PARALLEL SPEEDUP PREDICTUON FOR MULTI-THREADED<br>APPLICATION VIA STATISTICAL MODELING OF PROGRAM |        |                                                                   |    |

|--------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------|----|

|                                                                                                              | CH     | ARATERISTICS                                                      | 54 |

| 4.1                                                                                                          | Model  | Structure                                                         | 54 |

|                                                                                                              | 4.1.1  | Instruction count                                                 | 55 |

|                                                                                                              | 4.1.2  | Memory request                                                    | 58 |

|                                                                                                              | 4.1.3  | DRAM latency                                                      | 61 |

|                                                                                                              | 4.1.4  | Cycle-Count Prediction for an Interval                            | 62 |

|                                                                                                              | 4.1.5  | Synchronization Latency                                           | 64 |

|                                                                                                              | 4.1.6  | Cross-Input Prediction                                            | 64 |

| 4.2                                                                                                          | Evalua | tion                                                              | 65 |

|                                                                                                              | 4.2.1  | Speedup prediction                                                | 66 |

|                                                                                                              | 4.2.2  | Estimation of Optimal Thread-Count for an Application Performance | 69 |

|                                                                                                              | 4.2.3  | Error breakdown                                                   | 71 |

|                                                                                                              | 4.2.4  | Interval Analysis                                                 | 74 |

|                                                                                                              | 4.2.5  | Input Scaling                                                     | 74 |

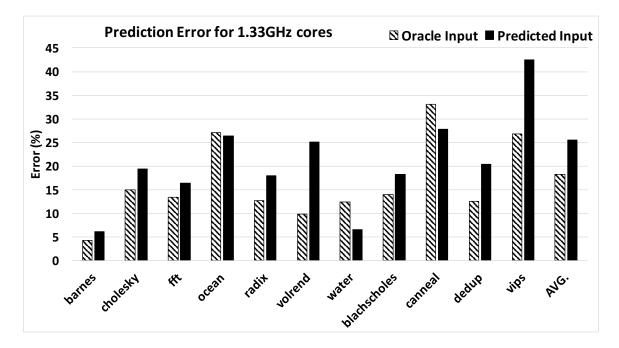

|                                                                                                              | 4.2.6  | Core Frequency Scaling                                            | 75 |

| Chapter                                                                                                      |        | CK CONTENTION PREDICTION USING PC-BASED STA-                      | 70 |

|                                                                                                              | 115    | TICAL MODELING                                                    | /8 |

| 5.1                                                                                                          | Model  | Structure                                                         | 78 |

|                                                                                                              | 5.1.1  | PC-based prediction model                                         | 78 |

|                                                                                                              | 5.1.2  | Arrival rate                                                      | 79 |

|                                                                                                              | 5.1.3  | Critical section                                                  | 81 |

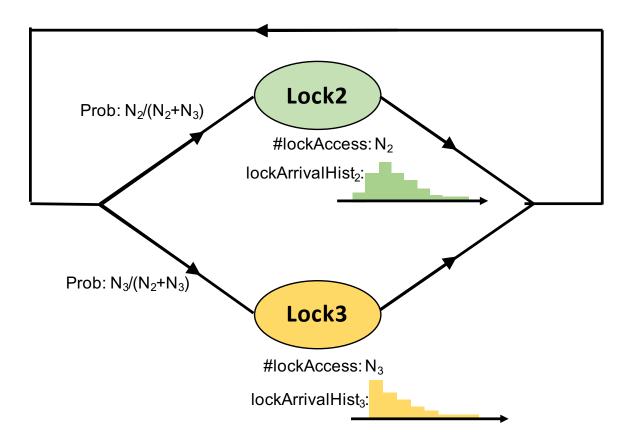

|                                                                                                              | 5.1.4  | Lock access histogram                                             | 82 |

|         | 5.1.5                 | Lock handoff model          | 34             |  |  |

|---------|-----------------------|-----------------------------|----------------|--|--|

|         | 5.1.6                 | Overall model               | 34             |  |  |

| 5.2     | Model                 | Refinement                  | 35             |  |  |

|         | 5.2.1                 | Merge lockPC                | 35             |  |  |

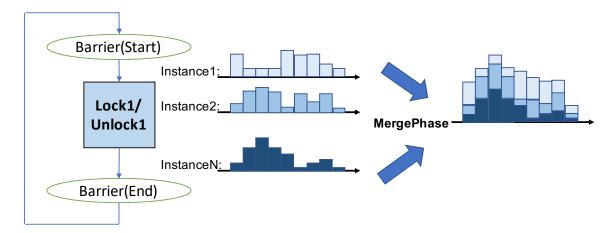

|         | 5.2.2                 | Merge Parallel Section (PS) | 36             |  |  |

| 5.3     | Evalua                | ntion                       | 37             |  |  |

|         | 5.3.1                 | Benchmark summary           | 38             |  |  |

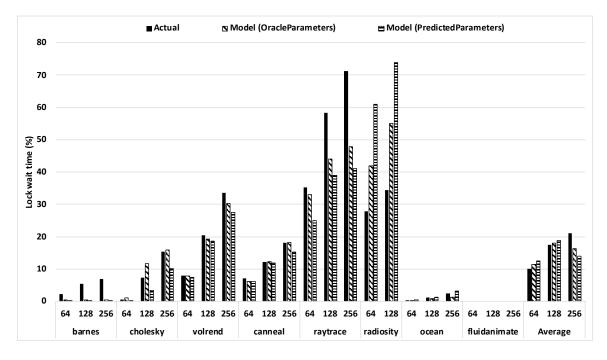

|         | 5.3.2                 | Model prediction result     | <del>)</del> 0 |  |  |

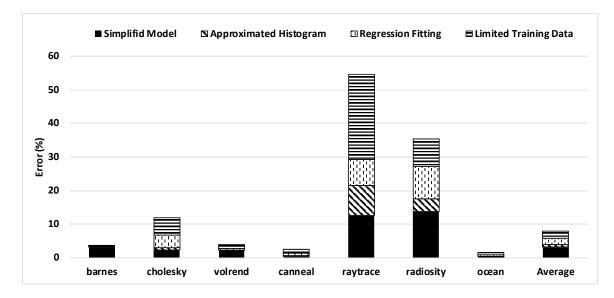

|         | 5.3.3                 | Error breakdown             | <del>)</del> 1 |  |  |

|         | 5.3.4                 | Refinement analysis         | 92             |  |  |

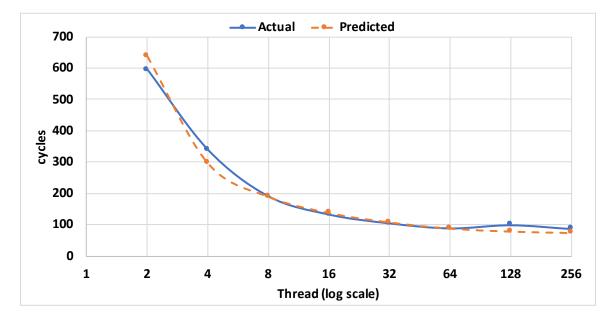

|         | 5.3.5                 | Extended Amdahl's Law       | <del>)</del> 3 |  |  |

|         | 5.3.6                 | Model application           | <del>)</del> 3 |  |  |

| Chapter | Chapter 6: Conclusion |                             |                |  |  |

| Referen | ices .                |                             | 13             |  |  |

# LIST OF TABLES

| 2.1 | Summary of hardware synchronization approaches       | 24  |

|-----|------------------------------------------------------|-----|

| 2.2 | Summary of scalability prediction schemes            | 25  |

| 4.1 | Summary of system configuration                      | 67  |

| 5.1 | Summary of system configuration                      | 88  |

| 5.2 | Summary of benchmark characteristic on lock accesses | 100 |

# LIST OF FIGURES

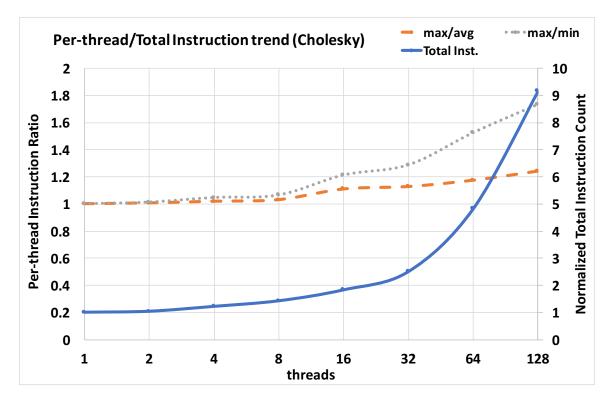

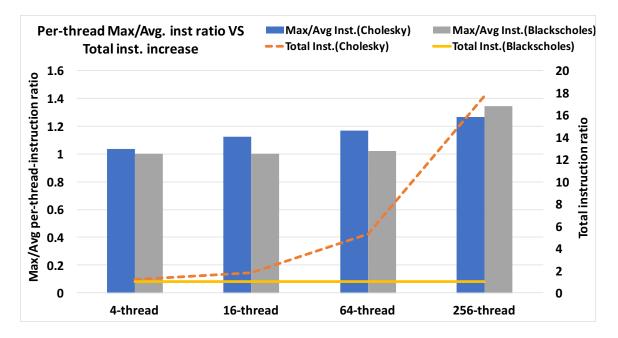

| 1.1 | Per-thread/Total instruction trend for Cholesky                                               | 6  |

|-----|-----------------------------------------------------------------------------------------------|----|

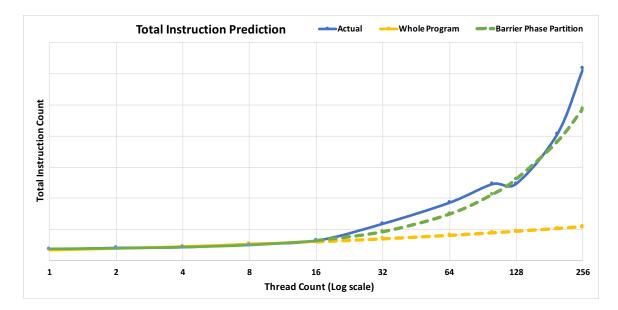

| 1.2 | Instruction Prediction                                                                        | 7  |

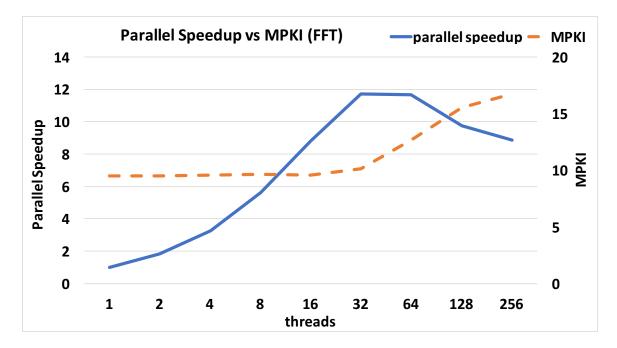

| 1.3 | Parallel Speedup vs. MPKI                                                                     | 8  |

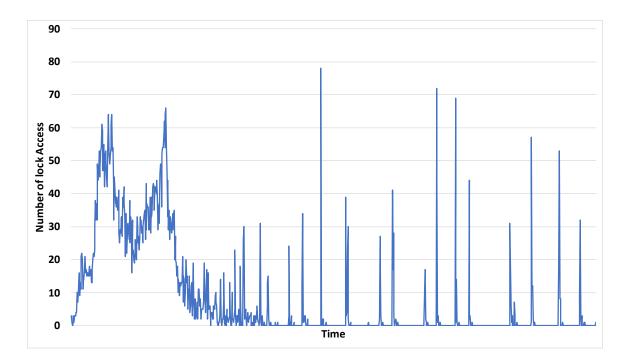

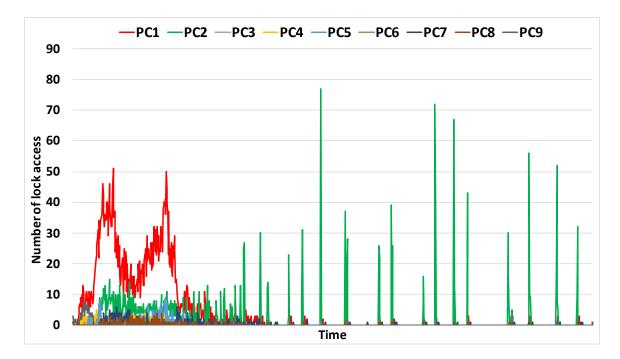

| 1.4 | Number of lock accesses over 1M cycles (1K data points) for 128-thread execution of Radiosity | 12 |

| 1.5 | Per-PC Lock access over time                                                                  | 13 |

| 3.1 | Minimalistic Synchronization Accelerator (MSA)                                                | 49 |

| 3.2 | State Diagram for Lock/Unlock Operations                                                      | 50 |

| 3.3 | State Diagram for the Barrier Operation                                                       | 51 |

| 3.4 | State Diagram for the Condition Wait Operation                                                | 51 |

| 3.5 | Raw Synchronization Latency                                                                   | 52 |

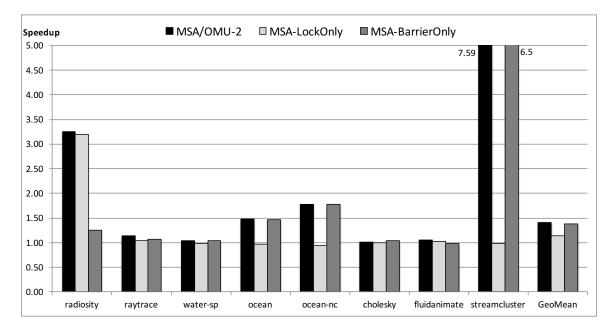

| 3.6 | Overall application performance improvement (Speedup)                                         | 52 |

| 3.7 | Coverage of Synchronization Operations                                                        | 52 |

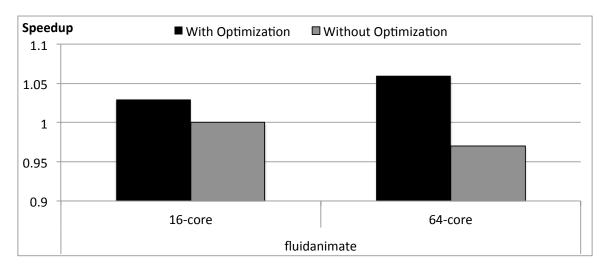

| 3.8 | Effect of HWSync-bit optimization on Fluidanimate                                             | 53 |

| 3.9 | Speedup comparison when MSA only supports lock or barrier operation                           | 53 |

| 4.1 | Performance Modeling for Program Intervals                                                    | 55 |

| 4.2 | Per-Thread Max/Avg Instruction Ratio                                                          | 57 |

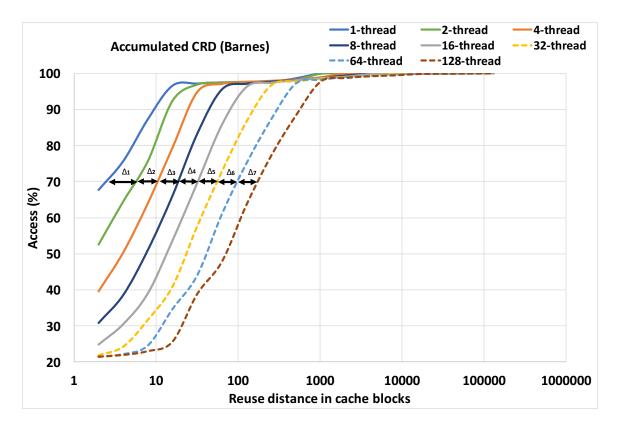

| 4.3  | Accumulated concurrent reuse distance profile for <i>Barnes</i>        | 60 |

|------|------------------------------------------------------------------------|----|

| 4.4  | Average memory queue length vs average service time                    | 64 |

| 4.5  | How barrier phase scale with input for $Lu$                            | 66 |

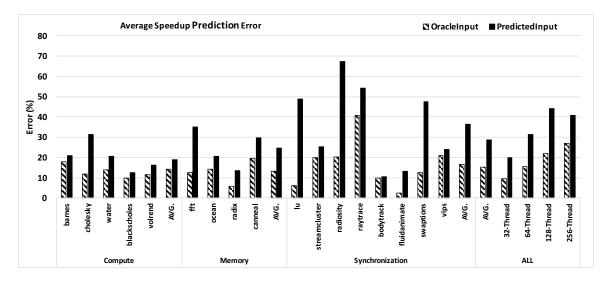

| 4.6  | Average speedup prediction error                                       | 67 |

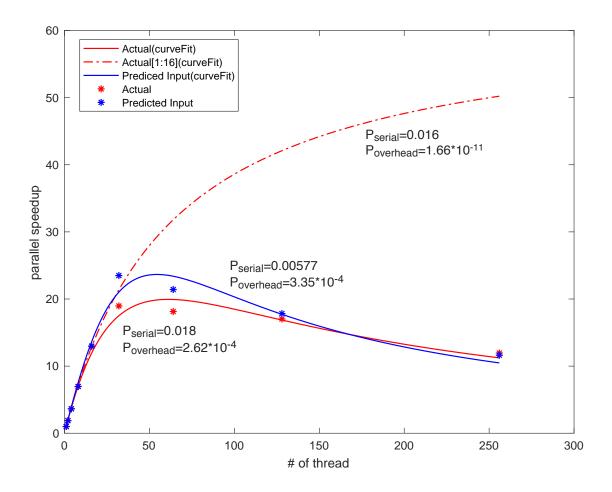

| 4.7  | Curve fitting for Radix using extended Amdahl's law                    | 71 |

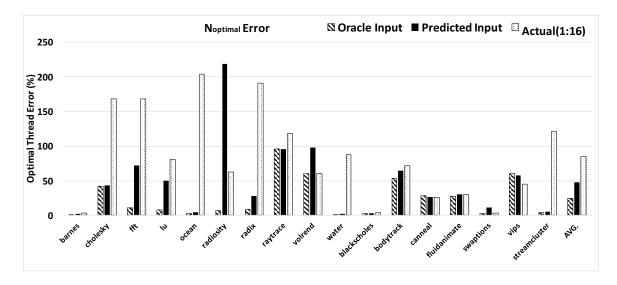

| 4.8  | Error for $N_{optimal}$                                                | 72 |

| 4.9  | Breakdown of speedup prediction error                                  | 73 |

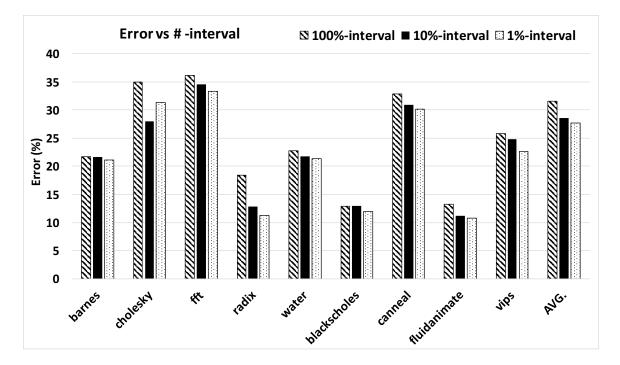

| 4.10 | Number of intervals on the effect of average prediction error          | 75 |

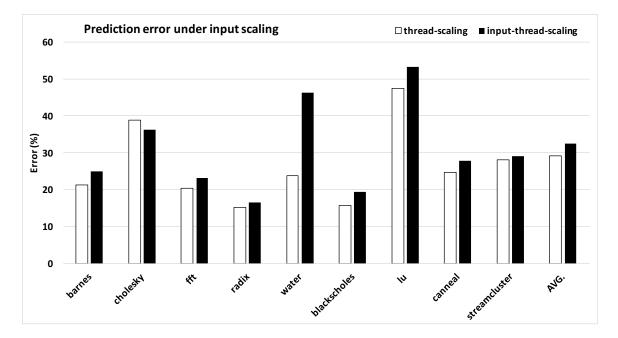

| 4.11 | Average error for thread scaling and input-thread-scaling              | 76 |

| 4.12 | Prediction error under core frequency scaling                          | 77 |

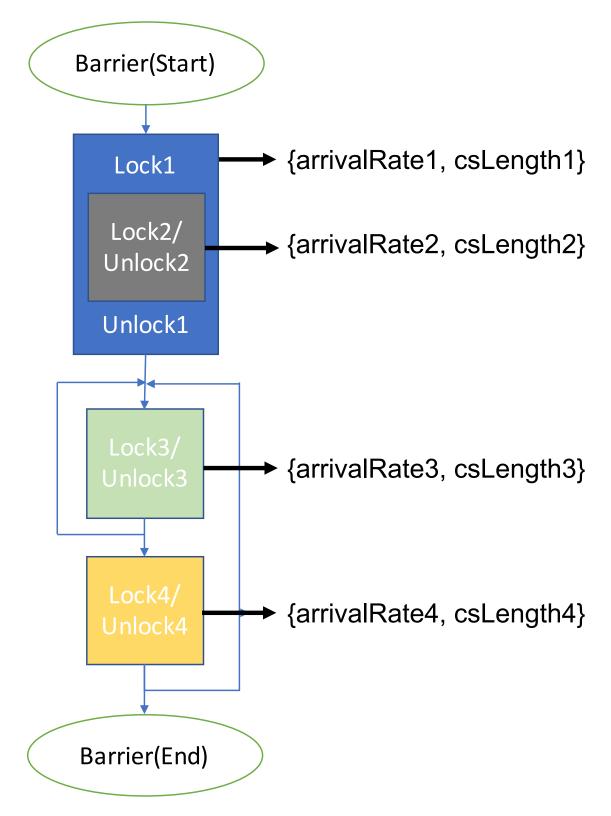

| 5.1  | Parallel section/LockPC prediction scheme                              | 94 |

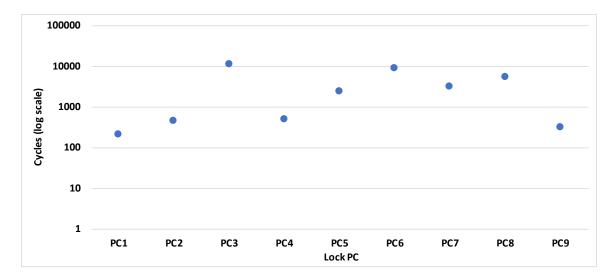

| 5.2  | Average inter-arrival time for different LockPC                        | 95 |

| 5.3  | Predicting average inter-arrival time using regression model           | 95 |

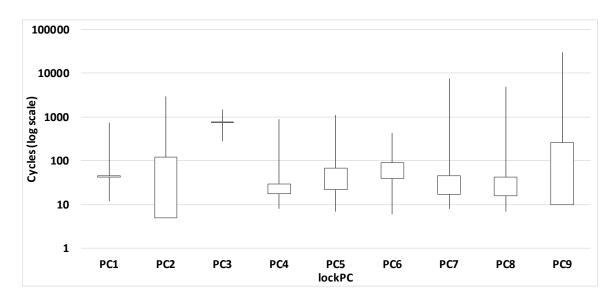

| 5.4  | Critical section size for different lockPC                             | 96 |

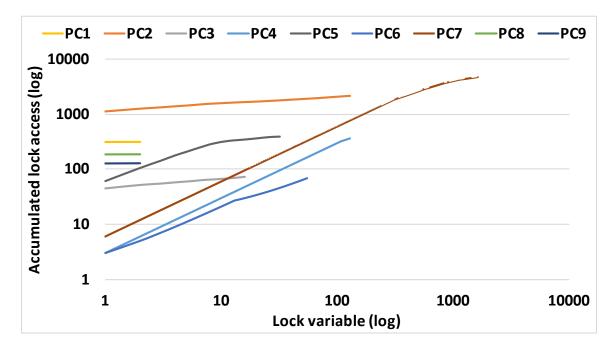

| 5.5  | Lock access histogram for different lockPC                             | 96 |

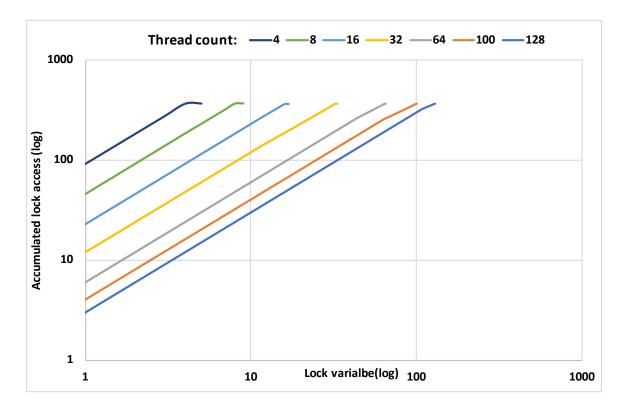

| 5.6  | Prediction of lock access histogram with varying thread count          | 97 |

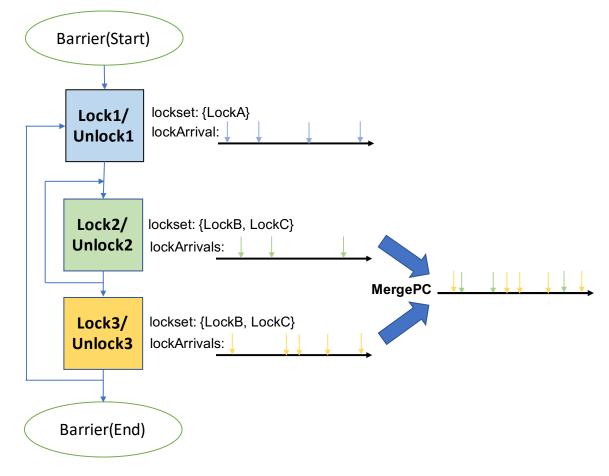

| 5.7  | Merging statistics for various lockPCs                                 | 98 |

| 5.8  | Evaluate merged lockPCs lock contention                                | 99 |

| 5.9  | Merging statistics for different parallel sections                     | 99 |

| 5.10 | Average per-thread lock wait time over total runtime                   | 01 |

| 5.11 | Average peedup prediction error                                        | 01 |

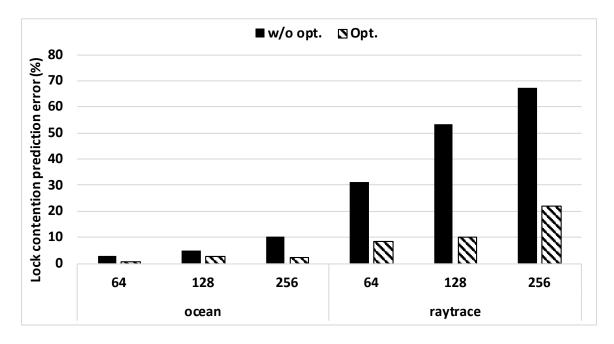

| 5.12 | Effectiveness of optimization on lock contention prediction accuracy 1 | 02 |

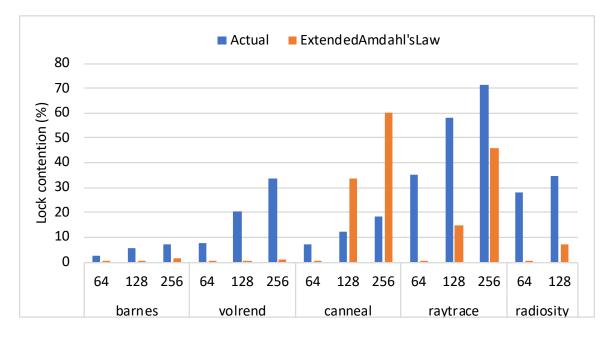

5.13 Lock contention prediction result using extended Amdahl's law . . . . . . 102

#### **SUMMARY**

In recent years, the number of processor cores on a single chip has increased rapidly, ranging from hundreds of cores in server processors to tens of cores on mobile processors. The abundant number of processing cores have led to application developers investing in parallelizing applications in order to extract the maximum performance from many-core processors. However, ensuring the continuous scaling of parallel applications is challenging on many-core processors, due to the complex relationship of available parallelism in application and the limited shared on-chip resources.

Two main bottlenecks that limit the scalability of parallel applications are synchronization and memory bandwidth. Synchronization increases with the number of threads, due to the high lock contention from threads accessing the same lock-protected data that causes increase lock contention, whereas barrier operations ensure each parallel thread are within the same computation phase which limits the available thread-level parallelism. The increase in number of threads also puts more pressure on the memory subsystem in order to provide sufficient memory bandwidth for each active thread.

With this thesis, I propose both statistical models to mitigate the bottlenecks and software/hardware solutions to improve and address the scalability bottlenecks. First, I propose MiSAR, a minimalistic synchronization accelerator (MSA) that supports all three commonly used types of synchronization (locks, barriers, and condition variables), and a novel overflow management unit (OMU) that dynamically manages its (very) limited hardware synchronization resources. The OMU allows safe and efficient dynamic transitions between using hardware (MSA) and software synchronization implementations. This allows the MSA's resources to be used only for currently-active synchronization operations, providing significant performance benefits even when the number of synchronization variables used in the program is much larger than the MSA's resources. Because it allows a safe transition between hardware and software synchronization, the OMU also facilitates thread suspend/resume, migration, and other thread-management activities. Finally, the MSA/OMU combination decouples the instruction set support (how the program invokes hardware-supported synchronization) from the actual implementation of the accelerator, allowing different accelerators (or even wholesale removal of the accelerator) in the future without changes to OMU-compatible application or system code.

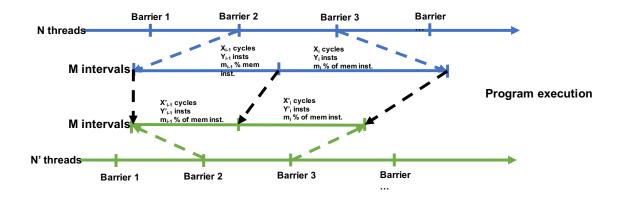

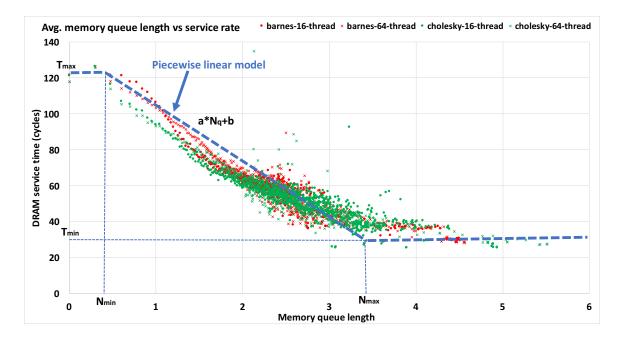

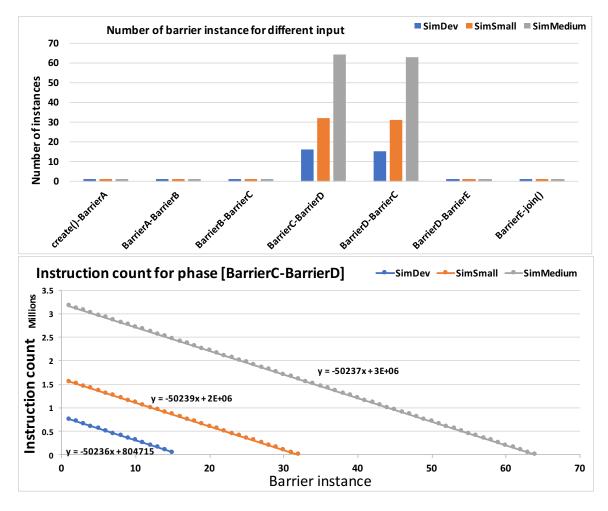

Second, I propose a new performance model that captures program characteristics of multi-threaded applications, allowing it to use few-threaded runs along with small input sets to predict performance of many-threaded runs with large input sets. First, we partition the program execution into barrier phases, and model the scaling trend of the total instruction count and its distribution among threads for each barrier phase in order to account for parallelization overheads. Second, we subdivide each barrier phase into small intervals, and model the cache miss rate of each interval by utilizing the regular shifting of concurrent reuse distance (CRD) profiles. Applying the CRD analysis to small intervals allows the CRD profile to capture behavior and model performance of each phase of the program individually, rather than trying to model the aggregate behavior of potentially many phases that may differ widely in terms of cache capacity and memory bandwidth demand. Third, we use a simplified DRAM model to capture the impact of the memory subsystem on the total execution time. Finally, we model how the number of barrier phases and the model parameters (instruction count and CRD) changes with input size to predict across different input sets.

Last, I propose a PC-based profile and modeling technique to predict the increase of lock contention when scaling the number of threads. Our lock contention model consists of 4 parts. First, we divide the program execution into parallel phases separated by global synchronization (barrier, fork-join, etc.). Second, we collect statistics that represent the synchronicity of thread arrival (lock arrival rate) as well as the functionality of the corresponding critical section (size of the critical section) for each lock PC. Third, we approximate the rates into well-known statistic models (eq. exponential distribution, gaussian

distribution, etc.) in order to reduce the parameters required to model the lock contention. Last, we use regression models to predict how the parameters will change when varying the number of locks and input size.

# CHAPTER 1 INTRODUCTION

#### 1.1 Multi-core Era and Parallel Applications

In recent years, the number of available cores in a processor is increasing rapidly while the pace of performance improvement of an individual core has been lagged. As a result, applications are now required to extract more parallelism and leverage the abundant number of cores to ensure continuous speedup of their applications. However, ensure application scale well over many threads is a challenge task, mainly because scalability bottlenecks such as synchronization will saturate the performance gain if not managed carefully. In addition, finding the optimal thread count to balance the overhead and benefit of parallelization becomes even more critical.

To tackle the challenge of ensuring the scaling of parallel applications, in this work I propose both a synchronization accelerator and performance models to address the issue. The synchronization accelerator reduces the amount of synchronization overhead, specifically handoff overhead. This would allow the efficient execution of synchronization operations such as lock and barriers, while minimizing the overhead. Second, I propose two performance models to predict the scaling trend of an application. This allows application developers to estimate the potential speedup for a given system and identify rather the application would be memory-bound, compute-bound, or synchronization-bound.

#### **1.2 Scalability challenges**

#### 1.2.1 Synchronization operation overhead

Synchronization latency is critical for achieving scalable performance on many-core processors. Numerous hardware mechanisms for low-latency synchronization have been proposed [1, 2, 3] and even used in prototype and commercial supercomputing machines [4, 5, 6, 7, 8, 9, 10]. As general-purpose processors have shifted their focus from solely increasing single-core performance to providing more cores, there has been a renewed interest in hardware support for synchronization [11, 12, 13, 14, 15], this time for a much broader range of systems, programmers, and users. Examples of recently proposed hardware synchronization mechanisms include utilizing a small buffer attached to the on-chip memory controller to perform synchronization and allow trylock support [15], incorporating a lock control unit to both the core and memory controller to allow efficient reader-writer lock [14], or leveraging low latency signal propagation over transmission lines for lock and barrier synchronization [11, 12, 13].

Because previous research on hardware supported synchronization mostly focused on how to reduce synchronization latency, most such work assumed that a sufficient amount of hardware resources is available, with only limited consideration on how to handle limited hardware resources. This, however, limits the adoption of hardware synchronization accelerators both because of high cost (many applications use a large number of synchronization addresses for which resources would be needed) and correctness (some applications can exceed the resources that were considered sufficient at hardware design time).

Most prior work tackles limited hardware resources using one of the following three mechanisms. The simplest mechanism is to have an a-priori partitioning of synchronization addresses into hardware-supported and software-supported ones. Programmers will thus use hardware synchronization instructions for some and software library calls for other synchronization variables. However, this places a heavy burden on programmers because: 1) they must decide which synchronization approach to use for which synchronization variable, 2) debug problems that occur when a synchronization variable erroneously mixes synchronization implementations, and hardware resources are oversubscribed. Another mechanism is to simply stall the synchronization operation until resources are available. Although this does not require any programmer intervention, it can result in great performance loss, or even deadlock if resources are not sufficient. The third mechanism is to treat the insufficient hardware resources as an exception. The exception handler will then decide to wait and try again or use a software synchronization mechanism. Such fallback mechanism results in significant performance penalty, so sufficient resources are needed to keep the number of the fallbacks very low. Furthermore, naively falling back to a software implementation can break the synchronization semantics, and additional overheads (and possibly additional hardware mechanisms) are needed to prevent such problems.

Also, previous proposals have focused on only accelerating (supporting) one type of synchronization. This would result in significant hardware cost/complexity to support the overall synchronization needs of real workloads, where different applications (or even the same application) may use locks, barriers, and/or condition variables. Each hardware synchronization mechanism (e.g. one for locks and another for barriers) may have its own software interface and its own verification complexity, which complicates adoption by both hardware architects and by programmers.

Therefore, in this thesis, I propose a minimalistic synchronization accelerator (MSA). The MSA is a distributed synchronization accelerator for tile-based many-core chips. It follows the POSIX pthread synchronization semantics and supports all three common types of synchronization (locks, barriers and condition variables) but has very few entries in each tile. We also propose a novel hardware overflow management unit (OMU) to efficiently manage limited hardware synchronization resources. The OMU keeps track of synchronization addresses that are currently active in software, so we can prevent these addresses from also being handled in hardware. The OMU also enables the accelerator to rapidly allocate/deallocate hardware resources to improve utilization of its (few) entries. Finally, we propose ISA extensions for hardware synchronization. These ISA extensions facilitate adoption by allowing synchronization libraries to only be modified once (to support the new instructions) and then used with any hardware synchronization implementations that support the ISA's fallback semantics – including trivial implementations with no actual

hardware synchronization support.

#### 1.2.2 Thread Count

With the commercialization of many-core processors, such as Intel's Xeon Phi [16] and Tilera [17], a single-node system can easily exceed hundreds of processing cores. This raises a critical question of how many cores/threads to use in order to obtain close-to-optimal performance for a particular application. Prior work has shown that simply using the same number of threads as cores may not yield the optimal performance, since increases in parallelization overheads can exceed performance gains from additional parallelism [18, 19].

One approach to predict performance scaling is to explore different system configurations using detailed simulators, then use regression methods to build a statistical predictor [20]. However, training a regression model for accurate results require thousands of data points, which is time consuming and therefore cannot quickly identify the scalability trends of an application. Others have proposed methods that dynamically manage the number of active threads at runtime [19, 18], typically by starting with few threads, predicting the thread count that will saturate an available resource (eq. memory bandwidth), and adjusting the thread count accordingly. However, these prediction mechanisms often assume that each thread has identical working-set size and program behavior[19], which does not take into account load imbalance. Furthermore, most dynamic approaches can only provide performance prediction up to the number of available cores, which precludes their use for estimating performance gains that might be obtained with higher-core-count processors (e.g. to determine if performance gains would justify upgrading the processor to a higher-core-count one).

Profiling tools have also been used for identifying potential scalability bottlenecks [21, 22], typically by utilizing hardware performance counters to account for various microarchitectural events such as last level cache (LLC) misses, high-latency instructions, etc., and then components of the execution time that are particularly detrimental to scaling. Such profiling approaches are typically very helpful in situations where the profiled execution is already experiencing substantial performance degradation, but do not provide much insight into how performance will *eventually* degrade at significantly higher thread counts.

For applications that scale well, the total amount of work and its distribution among threads becomes the dominant factor for efficient scaling. Most prior work assumes a constant total instruction count as the thread count increases [23, 19, 18], i.e. that there is no per-thread work that must be done by each thread regardless of how many threads are used. However, even a small amount of per-thread work becomes important when using many threads. For example, Figure 1.1 shows how the total instruction count scales for the Splash-2 benchmark *Cholesky*. While the total instruction count is close-to-constant for low thread counts, it rapidly increases when using many threads, so that a 128-thread execution executes 9X the number of instructions executed by the single-threaded execution. This means that modeling of the per-thread overheads is very important when trying to predict performance scaling of some applications. Figure 1.1 also shows the ratio between the maximum and average instruction count among threads, and also the maximum-tominimum per-thread instruction count. We observe that this ratio increases as the thread count increases, i.e. at higher thread counts the application will experience higher load imbalance. Predicting this load-imbalance can become important when trying to predict overall application performance at higher thread counts.

One challenge for using statistical models to predict performance is the complexity of the model and the required number of data points. Naively predicting the program characteristic would require large amount of data points in order to correctly capture the complex program behavior. However, prior work have shown that synchronization barriers are a natural boundary for a program phases, and consists of homogeneous behaviors across and within barrier phases [24, 25]. Our work extends upon this concept and shows that barrier phase characteristic are also homogeneous across different input, and by leveraging

Figure 1.1: Per-thread/Total instruction trend for Cholesky

such program structure, we can not only reduce the complexity and required data points to achieve better accuracy for modeling program characteristics, but also predict how program scales across larger input sets. Figure 1.2 shows how the accuracy of predicting the total instruction improves by subdividing the prediction on each barrier phase verses over the whole program.

Contention for memory resource is another main bottleneck for application scalability. Increasing the number of active threads increases the demand for data movement bandwidth (both in the on-chip interconnect and in the memory channels), degrades cache locality in shared caches (which further increases memory bandwidth demand), and often increases the total memory footprint by increasing the total amount of tread-private data (which additionally degrades cache performance and results in even more memory bandwidth pressure). Several prior works have studied how thread-count degrades memory locality [26, 27] and increases pressure for off-chip memory bandwidth [21]. However, these works only target a single architecture feature (cache miss rate, memory bandwidth utilization), and do

Figure 1.2: Instruction Prediction

not address the problem of predicting overall performance scaling in general, especially when multiple performance-limiting factors are present and their effects are compounded.

To illustrate how one factor is unlikely to provide a good picture of overall parallel performance, Figure 1.3 shows the overall parallel speedup and MPKI of Splash-2 [28] benchmark *FFT* as the number of threads increases. As shown, MPKI increases by 2X when scaling from 1 thread to 256 threads. However, the parallel speedup peaks at 64 threads, which is beyond the point where MPKI starts to degrade. Beyond 64 threads the MPKI continues to increase, while the parallel speedup degrades. This speedup degradation is actually caused by compounding the effects of cache hit rate degradation (which is accounted for in the MPKI) and the saturation of memory bandwidth (which is not accounted for in the MPKI). Note that cache hit rate degradation alone would be expected to only reduce the slope of the performance growth curve, while the bandwidth saturation alone would be expected to cause saturation of the parallel speedup (making it asymptotically approach a constant value). However, with both effects present simultaneously, bandwidth saturation prevents any parallelism-related gains from thread-count increases while cache hit rate degradation causes each thread to slow down, resulting in degradation

Figure 1.3: Parallel Speedup vs. MPKI

in performance as the thread-count increases.

To predict the interaction between cache hit/miss performance and the limited bandwidth in the memory system, we adopt a mechanism proposed by M.-J. Wu et al. [26] that uses an augmented Reuse Distance (RD) analysis to better account for how cache hit/miss performance changes with the thread count. In addition, we also account for bandwidthrelated considerations (memory access burstiness) and instruction-count trends to model and predict the interaction among these performance-limiting factors. We note that RD analysis was originally applied to sequential programs, and that several works have extended RD analysis to analyze how core-count scaling affects multi-program workloads [29] and parallel programs [30]. However, these studies mainly focus on how the total number of cache miss changes but neglect the changes in the burstiness of cache misses and the overall parallel speedup.

In result, I propose a performance prediction model that consists of 4 main components. First, I partition the program execution into barrier phases, and model the scaling trend of the total instruction count and its distribution among threads for each barrier phase in order to account for parallelization overheads. This identifies how the total work changes and how work distribution among threads changes as the thread count increases. Second, we predict the cache miss rate at small intervals by utilizing regular shifting of concurrent reuse distance (CRD) profiles. By applying the CRD analysis to small intervals, we could associate CRD profile with program phases and capture bursts of memory requests. Third, we use a simplified DRAM model to capture the memory subsystem slowdown and its effect on the total execution time. Last, we model how the number of barrier phases and the model parameters (instruction count and CRD) changes with input size to predict across different input sets.

#### 1.2.3 Lock Contention

Many-core processors, some with 10s or even 100s of processing cores, have become ubiquitous in all sections of computing, ranging from handheld mobile devices [31], to accelerators [16, 17]. As many-core processors become ubiquitous, parallel applications are also gaining increasingly prevalent as developers and users desire to fully utilize the abundant processing power available across the cores in a single system. However, as the number of cores increases, developers and users expect the performance to scale, i.e. the amount of useful computation achieved per unit time should increase with the number of cores used for that computation. Unfortunately, good performance scaling is difficult to achieve in practice, mainly because of various bottlenecks that can each limit performance scaling. One of the common performance scaling bottlenecks is lock contention, which effectively forces serialization of execution and thus prevents all the cores from concurrently doing useful computation.

Prior work have proposed methods to combat the increase of lock contention when scaling applications. Hardware solutions have been proposed to reduce the overhead for performing lock operations, such as a dedicated hardware accelerator for course-grain [32] or fine-grain [15] locking, or micro-architectural features which predicts and opportunisti-

cally executes the critical section in order to reduce serialization [33]. Software solutions such as runtime systems to change the scheduling policy have also been proposed to reduce the contention on lock variables [34][35][36]. However, these approaches mainly focuses on reacting to the serialization of lock contention and does not identify or address the fundamental problem in the program.

Various performance analysis and profiling techniques have been proposed in order to identify and remove the fundamental problem of serialization in the original program. Chen and Stenstrom proposed a mechanism to identify the longest critical path from an execution trace file in order to attribute the cause of the scaling bottleneck [37]. Bois et al. proposed a new criticality metric in order to capture the severity of lock serialization [38]. Others have also proposed light weight mechanisms to identify lock contention [39] and to categorize various type of bad synchronization [40]. Commercially available tools such as Intel vTune[41] and Concurrency Visualizer in Microsoft Visual Studio [42] allows programmers to debug and identify performance bottlenecks in the system. They do not, however, provide insight into if or when a bottleneck would occur in other runs, e.g. if more cores were used.

Analytical models have also been proposed to model lock contention in various systems. Yu et al. [43] proposed a database performance model that assumes a Poisson arrival rate of transactions, with each transaction accessing a set of locks what have uniform access probability. Thomasian [44] generalized such model to incorporate multiple class of transactions, each with different distribution of lock access probability. However, database systems fundamentally differ from homogeneous multi-threaded applications in that, for database systems, transactions arrive independently of each other as a result of external requests, so their arrival rate which can be modeled as a Poisson distribution and their lock contention is a good match for a traditional queuing model. In contrast, in multi-threaded applications threads tend to be, at least to some degree, in lock-step with each other, and therefore threads are not necessary arriving independently. In addition, during the lifetime of a threads, it will access various lock variables during different program phases, which behavior is different than database systems.

To provide insight into the scaling of multithreaded applications, Eyerman and Eeckhout [45] proposed extending Amdahl's law to model the increase in serialization due to scaling. However, the model simply assumes random arrivals to critical sections, which prevents the model from providing accurate quantitative performance predictions. Boyd-Wickizer et al. [46] proposed a lock contention model for ticket locks by using Markov models in order to calculate the expected number of idle cores. However, their model only considers a single lock, with no discussion on how the model can be applied to applications with multiple locks.

In general, one of the main drawbacks of prior lock contention model is the assumption of uniform and random access of lock variables during the whole application. However, these assumptions are violated by many real programs, e.g. because different program execution phases can have very different lock-related behaviors. To illustrate this, Figure 1.4 shows the number of lock access over time for *Radiosity*. As shown, the lock accesses are more prevalent early in the application and, when lock accesses do occur later in the application, they are clustered together (the peaks at several points in the execution timeline).

To model and predict the lock contention of applications, we propose to model the lock contention separately for each static location in the code (PC address) at which the lock is acquired. Our intuition is that the overall lock-related behavior of the application is a combination of behaviors in different program phases. Furthermore, even within each program phase the overall behavior can be a combination of different behaviors as different data structures may be protected by different sets of locks that can substantially differ in locking behavior. Intuitively, we expect that each of these individual behaviors can be modeled more simply and accurately than the entire application, and that these individual models can be combined in a relatively straightforward way into a model for the entire application that will be more accurate than a model that considers the entire application

Figure 1.4: Number of lock accesses over 1M cycles (1K data points) for 128-thread execution of Radiosity

as a homogeneous whole. Since the PC of the lock operation is correlated with both the current program phase and with the set of locks that is used, PC-specific modeling of lock behavior should help capture these individual behaviors.

Additionally, we observe that after global synchronization, such as a barrier, threads tend to have a high degree of synchronicity, i.e. they are close to being in lock-step with each other, and this makes lock contention much more likely than when threads arrive to critical sections randomly.

Figure 1.5 shows the lock access over time for each lock PC. As shown, we can see that during the first peak of lock access, the "red" PC (PC1) is the dominant source of lock accesses, while later in the execution the "green" PC (PC2) is dominant. This is because of during a single parallel phase, threads execute in different regions of code, therefore exhibit different phase behavior. Furthermore, the "green" lock accesses come in bursts, which is the result of threads executing in relatively similar code regions, therefore would access the same lockPC in synchronicity. This shows that lock PC is a useful proxy to capture to

Figure 1.5: Per-PC Lock access over time

phases of thread's lock access. In addition, the characteristic of each lockPC also displays a structural change, such that it allows us better to predict the arrival rate or lock histogram.

In summary, our lock contention model consists of 4 parts. First, we divide the program execution into parallel phases separated by global synchronization (barrier, fork-join, etc.). Second, we collect statistics that represent the synchronicity of thread arrival (lock arrival rate) as well as the functionality of the corresponding critical section (size of the critical section) for each lock PC. Third, we approximate the rates into well-known statistic models (eq. exponential distribution, gaussian distribution, etc.) in order to reduce the parameters required to model the lock contention. Last, we use regression models to predict how the parameters will change when varying the number of locks and input size.

### 1.3 Thesis Statement

With the accelerating technology improvements, the number of available cores in a processor steadily increases. As a result, it is necessary for application developers to exploit parallelism for better application performance. However, mitigating the parallelization

overhead while also determining the optimal thread count is a challenging task. Various scalability bottleneck may occur when scaling application on many-core processors, such as limited parallelism in the application design, poor synchronization algorithm, or even limited memory bandwidth to support all the necessary data movements from all the active threads.

This thesis proposes a performance model to understand the potential scaling trend for a given application, as well as a hardware accelerator to mitigate the scaling bottleneck. The thesis proposes the following statement: **Statistical models and hardware techniques can help understand and improve the scaling of parallel applications on many-core processors**

### 1.4 Thesis Overview

Chapter 2 provides the background and related works on synchronization accelerator design, performance modeling techniques, and lock contention analysis methods. Chapter 3 explains MiSAR, a hardware synchronization accelerator that reduces the synchronization overhead. Then, in Chapter 4, a new statistical model technique is proposed to model how application scales with thread count, and determine the optimal thread count for maximum parallel speedup. Chapter 5 discusses a PC-based statistical lock contention model in order to model and predict how lock contention scales with thread count. I conclude in Chapter 6.

# CHAPTER 2 BACKGROUND AND RELATED WORK

#### 2.1 Synchronization Accelerators

Hardware support for synchronization generally improves synchronization in two ways. First, by implementing the synchronization semantics in hardware, which avoids the inefficiencies in updating the synchronization state in software. Examples include accelerators for barriers [47, 48, 49] that track barrier's arrival state and detect the all-arrived condition without the overhead of updating the arrival count variable in a critical section. Lock accelerators [50, 47, 49, 15] maintain the lock's owned/free state in hardware and thus help arbitrate which requestor is the next to get the lock once it is freed.

The other way is to improve synchronization latency by directly notifying the waiting threads to avoid the coherence "ping-pong" involved in software-only synchronization. For example, a software-only implementation of lock handoff involves sending an invalidation when releasing the lock, waiting for that invalidation to reach all the sharers (typically all cores waiting for that lock), a cache read miss on (at least) the next-to-acquire core, a transfer of the lock's block into that cache, and then sending an upgrade request (invalidation) when actually acquiring the lock. In contrast, a direct-notification lock accelerator [12, 51, 2, 14] typically involves sending a single message from the releasor to the next-acquirer. A similar flurry of coherence activity is involved in signaling barrier release in software, and is avoided in hardware accelerators [11, 1, 13] by directly signaling the barrier release to waiting cores.

Synchronization support has also been used in distributed supercomputer systems, e.g., efficient broadcast networks have been used to accelerate barrier operations [9, 52], and fetch-and-add operations have been used for efficient barrier counting [5, 7, 10]. Our work

focuses on more tightly coupled many-core systems, and provides support for all three common types of synchronization.

In addition to improving synchronization latency, most hardware synchronization accelerators also have to handle what happens when hardware resources of the accelerator are exhausted. Several solutions have been adopted in prior work, such as requiring programmers to manually partition synchronization variables [11, 51, 1, 50, 13] into those that always use software and those that always use hardware, using the memory as a resource buffer [14], or switching to a software exception handler [15]. Unfortunately, programmerimplemented partitioning is not portable to architectures that have fewer resources, use of main memory complicates the implementation and adds latency, and software exception handlers are difficult to implement correctly and can incur large overhead when fallbacks are too frequent. Utilizing the memory as a resource buffer can reduce the amount of software exception events [14], however, still requires the exception handler to resize the resource table. In addition, going to main memory to access the resource buffer increases the overall synchronization latency. In contrast, our approach uses a small OMU local to each tile to efficiently and correctly fall back to an existing (e.g. pthreads) software implementation when needed, while also improving utilization of the (very limited) hardware synchronization resources. A more detail discussion of our scheme verses software exception handler will be discussed in Section 3.1.2.

Table 2.2 summarizes the prior proposals for multi-core synchronization: which synchronization types they support, whether they provide direct notification, the hardware cost (in terms of added state), whether a specialized network is required, and how hardware resources overflow is managed. For resource overflow, SW corresponds to simply falling back to a software handler when resources are exhausted, whereas HW resolves it in hardware. For LCU [14], it will first fallback to the memory and only if memory overflows will it require a software handler, thus we mark it HW/SW.

In general, accelerators that provide direct notification support only one type of syn-

chronization (e.g. only lock or only barrier), and direct-notification barrier proposals mostly rely on dedicated networks. Also, many of the mechanisms require recording state information that is proportional to the number of locks or barriers in the system - potentially many different locations, especially for programs that use large arrays of locks. In addition, so far no barrier accelerator has tackled the problem of resource overflow. In contrast, our proposed approach supports all three types of synchronization (locks, barriers, and condition variables), with direct notification over the existing on-chip interconnect, and with  $O(N_{core})$  hardware resource overhead.

#### 2.2 Performance Modeling

Various regression modeling techniques have been applied to performance modeling. B.C. Lee et al.[20] applied regression modeling technique to develop a non-linear model for reducing the work of design space exploration. The proposed regression model uses 4000 sample points to derive an architectural-application predictor. B.J. Barnes et al. [53] also uses regression modeling to predict the scalability of applications. This model separates computation and communication and then fits the data points into a linear regression model. More general regression models, such as artificial neural networks, were applied by E. Ipek et al. [54] for performance prediction. However, these models do not directly attribute the degradation in speedup to the factors that cause it (per-thread overhead and imbalance, cache hit/miss degradation, and bandwidth limits) nor provide an intuitive model for how these factors interact to produce the overall performance trend.

In addition to regression models, optimization techniques have also been applied to performance modeling. W. Wang et al. [55] use integer programming for optimal core/node placement for NUMA systems by collecting local and inter-node bandwidth usage, along with DRAM bandwidth and contention. Unfortunately, in such schemes the number of input parameters grows exponentially with the number of cores. In contrast, our approach leverages program characteristics to reduce the number of model parameters, uses model parameters that can directly be used to attribute/explain which program and microarchitectural factors are responsible for degradation in application speedup, and can use parameters obtained at lower core counts to predict performance on larger core counts.

Several works have also been proposed to predict the memory subsystem performance by using a detailed analytical DRAM model. DraMon [56] predicts memory bandwidth usage by modeling memory issue rate and row buffer hit/miss/conflict ratio using probability models. The probability for co-running threads to access the same rank/bank/channel is calculated from memory traces and assume that all threads have the same probability. However, this work only predicts memory bandwidth utilization and does not account for its interaction with other factors or its impact on overall execution time. ANATOMY [57] proposed a 3-stage queueing model for memory system performance. The model assumes an arrival rate with exponential distribution and mean  $1/\lambda$ , with memory banks and data bus as M/D/1 queues. To model the processor performance, it utilizes the CPI stack, which assumes the ideal memory CPI and then add the penalty by the memory subsystem. In contrast, our work uses a relatively simple memory bandwidth model, but also uses a model of per-thread overheads and a model of cache hit/miss behavior to predict how these factors jointly affect overall performance of a parallel application.

Dynamic runtime systems have been proposed to determine the optimal number of threads on the fly. FDT [19] predicts the optimal number of threads by first sampling the program characteristic in serial (using only 1 thread). It assumes the program will be either memory bound or synchronization bound, and collects the time spent in critical section and memory utilization to determine if either memory or synchronization is limiting the performance scaling.

CRUST [18] predicts the performance for clustered cache architectures. By sampling the miss rate for different active-cores-per-cluster during the end of each parallel section, it is able to correlate the number of threads with cache miss rate. With such information, it predicts the optimal thread count for each cluster by calculating the number of threads needed to saturate the total memory bandwidth.

M. Kim et al.[23] predict the potential speedup with a non-parallelized serial code That approach predicts DRAM access overheads by assuming that performance can be decoupled into computation and memory, that work is equally partitioned among threads, and that the LLC miss rate will not change when parallelizing the application.

#### 2.2.1 RD analysis

Multicore reuse distance analysis has been applied to study the cache behavior of parallel application. Ding and Chilimbi [30] discussed the construction of concurrent reuse distance (CRD) from per-thread RD by statistically interleaving memory accesses from different threads. It requires modeling each thread's sharing behavior to statically determine the interleaving behavior of memory accesses. M.-J. Wu et al. [26] simplified CRD analysis by leveraging the symmetry of threads for loop-based parallel programs. It utilizes reference group to predict how the CRD profile shifts and scales when increasing thread count. Our work applies CRD analysis to shorter intervals, which allows it to consider not only how the cache size and thread count affect the overall cache miss rate but also how the cache misses are distributed over time and how they interact with memory bandwidth to affect the parallel performance of each interval and, by combining the resulting performance of all the intervals, of the entire application.

D. Chandra et al. [29] and G.E. Suh et al. [58] looked at how CRD analysis can be applied to multi-programing workloads. While our work mostly considers parallel applications, some of our insights, e.g. combining CRD analysis with considerations for cache miss burstiness and memory bandwidth, may be applicable in that domain.

#### 2.2.2 Tools for Analysis of Performance Scaling

Many tools have been developed to identify scaling bottlenecks in multi-threaded applications. S. Eyerman et al. [22] proposed using speedup stack and breakup the performance slowdown into synchronization and resource sharing. W. Heirman et al. [59] proposed using cycle stack to attribute which microarchitecture structure is limiting parallel scaling.

Several other commercial profiling tools, such as Intel VTune<sup>TM</sup> [41] or HPCToolkit [60], identifies scalability bottlenecks by profiling the application's execution. Although these tools offer scaling bottleneck analysis beyond just the memory subsystem, they require executing the application on the target system with the target thread count to identify the scalability bottleneck(s). Hence, does not provide prediction mechanism on when a bottleneck would occur when scaling up thread count.

In summary, Table 2.2 summarizes the prior work on predicting the performance scaling of a parallel program.

#### 2.3 Lock Contention Analysis

#### 2.3.1 HW/SW lock contention reduction mechanism

Various hardware/software mechanisms have been proposed to reduce the severity of lock contention. Hardware solutions such as MiSAR [32] and SSB [15] utilizes on-chip hardware accelerators to reduce the overhead for performing lock operations. These proposals rely on implementing the lock functionality directly in hardware in order to improve the lock access latency. Other proposes such as Lock Elision [33] utilizes speculation techniques to optimistically execute critical sections concurrently, even when the critical sections are protected by the same lock variable. In case of mis-speculation, rollback is performed to ensure the correct execution of conflicting critical sections.

Software techniques have also been proposed to reduce the severity of lock contention based on runtime systems to dynamically controlling the number of active threads. FDT [34] samples the time spent in a critical section for a single threads, and then assumes each thread spends the same amount of time in critical section for each loop iteration, and schedule enough threads to fill the loop iteration with critical sections. Sridharan et al. [35] utilizes a modified Amdahl's law model to take into account serialization caused by lock, and then sample the execution runtime with various degree of threads in order to obtain the parameters for the modified Amdahl's law. Cui et al. [36] monitors the time spend on waiting for locks, and use empirical data to determine a threshold for determining when to stop scheduling more threads.

In summary, these proposals focus on reacting to the increase of lock contention and try to reduce the severity of such contention either through microarchitecture features to accelerator lock operations, or simply reduce the amount of active threads. Note, however, they do not provide a means to predict when a contention will happen, nor do they reveal why such contention exists.

### 2.3.2 Lock profiling tools

Various performance analysis and profiling techniques have been proposed in order to identify and remove the fundamental problem of serialization in the original program. Chen and Stenstrom [37] proposed using critical lock analysis to identify the longest critical path in order to contribute the cause of the scaling bottleneck. They proposed mechanism first collects the trace of all lock events, and then calculating backwards from the end of program execution to determine the longest critical path. Tallent et al. [39] discussed how to profile and attribute performance loss due to lock contention by recording the number of waiting threads when a lock is released, and attributing the lock holder for the idleness of each waiting threads.

Bois et al. [38] proposed a new criticality metric (Criticality stack) in order to model the severity of lock serialization. The criticality of each thread is calculated as the ratio of how many work is done verses how many threads are idle. The more threads are waiting, the more critical a thread is. Hence, the criticality stack can represent the criticality of each thread and identify the possibility of improving performance by accelerating the most critical thread. Alam et al. [40], categorizes lock usage in various applications, and identify why some lock are creating high contention verses the others. They also proposed methods to improve the locking scheme in order to reduce lock contention, such as using atomic instructions for critical sections that only contain simple integer operations.

Commercially available tools such as Intel vTune [41] and Concurrency Visualizer in Microsoft Visual Studio [42] also allows programmers to debug and identify performance bottlenecks in the system. These tools profile the runtime behavior, and reports statistics such as how many active threads are concurrently running, what do the lock wait time, etc., in order to let the programmer better understand the scaling of the application. However, these tools mainly focus on identifying the bottleneck when it actually occurs and does not provide insight into if or when a bottleneck would occur.

#### 2.3.3 Lock contention models

Very few works have tackled the problem of modeling and predicting the scaling of multithreaded applications. Boyd-Wickizer [46] proposed a lock contention model for ticket locks by using Markov models in order to calculate the expected number of idle cores. However, their model only looked at a single lock, and does not discuss how the model can be applied to applications with multiple locks. In addition, their model also did not address how to predict the lock contention when scaling the number of threads.

Eyerman and Eeckhout [45] extended the Amdahl's law model to include the increase in serialization due to lock contention while scaling the number of threads. Their model assumes the execution runtime is either limited by the slowest thread, or the average behavior of all threads, and take the slowest prediction of the two. Since their model focus more on the general scaling behavior of an application, it assumes critical sections happen randomly and uniformly across the whole program execution. In result, their work cannot be used as an accurate quantitative performance prediction.

## 2.3.4 Lock contention modeling for database systems

In addition to multithreaded applications, prior works have also studied how to model lock contention for database and transactional memory systems. Yu et al. [43] proposed a database performance model that assumes a Poisson arrival rate of transactions, with each transaction accessing a set of locks that have uniform access probability. Thomasian [44] generalized such model to incorporate multiple class of transactions, each with different distribution of lock access probability. However, database systems differ from homogeneous multi-threaded applications in one fundamental way such that for database systems, transactions are independent of each other. This results in a arrival rate which can be modeled as a Poisson distribution, and that lock contention is can be modeled with a queueing model. On the other hand, multi-threaded applications tend to execute in lock steps, therefore threads are not necessary arriving independently. In addition, during the lifetime of a threads, it will access various lock variables during different program phases, which behavior is different than database systems.

Xiao et al. [62] discussed how to use a queuing model to analyze the performance for transactional memory systems. Their model assumes transaction arrive and commits according to a linear model, with the probability increases with time. In addition, their model also considers a transaction can abort and retry when a conflict is detected. A conflict is detected when two threads access the same data element, which assumes a uniform distribution of access probability of all data elements. While their works focus on a detail analytical model of a transactional memory system, their model requires many different parameters in order to properly model the system behavior, thus increases the complexity of using it as a performance prediction model when the parameters are unknown.

|                                    | Table 2.1: Summary of hardware synchronization approaches | nardware syne | chronization approa      | Iches                                                              |                   |

|------------------------------------|-----------------------------------------------------------|---------------|--------------------------|--------------------------------------------------------------------|-------------------|

| Work                               | Synchronization Primitives                                | Notification  | <b>Resource overhead</b> | Notification Resource overhead Dedicated Network Resource Overflow | Resource Overflow |

| Lock Table[50]                     | Lock                                                      | Indirect      | $O(N_{lock})$            | No                                                                 | SW                |

| AMO[49]                            | Lock, Barrier                                             | Indirect      | 0                        | No                                                                 | N/A               |

| Tagged Memory[47]                  | Lock, Barrier                                             | Indirect      | $O(N_{mem})$             | No                                                                 | N/A               |

| QOLB[2]                            | Lock                                                      | Direct        | $O(N_{core})$            | No                                                                 | SW                |

| SSB[15]                            | Lock                                                      | Indirect      | $O(N_{activeLock})$      | No                                                                 | SW                |

| LCU[14]                            | Lock                                                      | Direct        | $O(N_{core})$            | No                                                                 | HW/SW             |

| barrierFilter[48]                  | Barrier                                                   | Indirect      | $O(N_{barrier})$         | No                                                                 | Stall             |

| Lock Cache[51]                     | Lock                                                      | Direct        | $O(N_{lock}N_{core})$    | Yes                                                                | Stall             |

| GLocks[12]                         | Lock                                                      | Direct        | $O(N_{lock})$            | Yes                                                                | None              |

| bitwiseAND/NOR[1]                  | Barrier                                                   | Direct        | $O(N_{barrier})$         | Yes                                                                | None              |

| GBarrier[11]                       | Barrier                                                   | Direct        | $O(N_{barrier})$         | Yes                                                                | None              |

| TLSync[13]                         | Barrier                                                   | Direct        | $O(N_{barrier})$         | Yes                                                                | None              |

| MSA/OMU (Our proposal) Lock, Barri | Lock, Barrier, Condition Variable Direct                  | Direct        | $O(N_{core})$            | No                                                                 | HW                |

| approaches                                     |

|------------------------------------------------|

| ation                                          |

| miza                                           |

| synchron                                       |

| Summary of hardware synchronization approaches |

| o<br>N                                         |

| Summa                                          |

| ÷                                              |

| 5                                              |

|                                                |

| ٩f                                             |

| L,                                             |

| Work                    | Inst/Work Cache | Cache              | DRAM                   | Data points             | Predictability     |

|-------------------------|-----------------|--------------------|------------------------|-------------------------|--------------------|

| ANATOMY[57]             | N/A             | N/A                | Arrival rate,          | Memory trace            | Change             |

|                         |                 |                    | row-buffer-hit rate    |                         | $N_{Banks}$        |

|                         |                 |                    | bank level parallelism |                         |                    |

|                         |                 |                    | request spread         |                         |                    |

| Cilkview[61]            | Constant        | N/A                | N/A                    | Call graph              | Upper/             |

|                         |                 |                    |                        |                         | lower bound        |

| Linear Regression[20]   | N/A             | N/A                | N/A                    | 4000 points             | Predict            |

| Integer programming[55] | N/A             | N/A                | N/A                    | $N^2_{core}$            | N                  |

| Parallel Prophet[23]    | Constant        | Constant           | Constant latency       | 1 (Serial run)          | Up to              |

|                         |                 | (miss rate)        |                        | (Anotated program)      | 12-thread          |

| FDT[19]                 | Constant        | Constant           | N/A                    | Several loop iteration  | Up to              |

|                         |                 | (miss rate/thread) |                        | (Bandwidth utilization) | 32-threads         |

| CRUST[18]               | N/A             | Sampled            | Sampled                | $N_{core/cluster}$      | $N_{clusters} *$   |

|                         | N/A             | (Miss rate)        | (Avg. Latency)         |                         | $N_{core/cluster}$ |

| OurProposal             | Regression      | <b>RD</b> Analysis | Linear model           | 5 points                | up to 256 thread   |

|                         |                 |                    |                        | (1-16 threads)          | (16X)              |

|   | schem                 |

|---|-----------------------|

| : | / prediction sche     |

|   | mary of scalability t |

| č | Sum                   |

| ( | 2.7:                  |

| - | ble                   |

# **CHAPTER 3**

# MISAR: MINIMALISTIC SYNCHRONIZATION ACCELERATOR WITH RESOURCE OVERFLOW MANAGEMENT

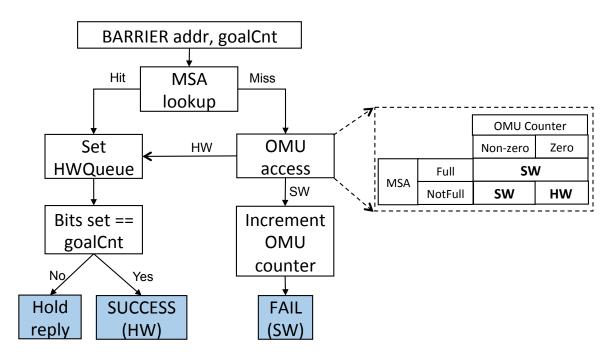

In this chapter, I propose MiSAR, a minimalistic synchronization accelerator (MSA). The MSA is a distributed synchronization accelerator for tile-based many-core chips. It follows the POSIX pthread synchronization semantics and supports all three common types of synchronization (locks, barriers and condition variables) but has very few entries in each tile. We also propose a novel hardware overflow management unit (OMU) to efficiently manage limited hardware synchronization resources. The OMU keeps track of synchronization addresses that are currently active in software, so we can prevent these addresses from also being handled in hardware. The OMU also enables the accelerator to rapidly allocate/deallocate hardware resources to improve utilization of its (few) entries. Finally, we propose ISA extensions for hardware synchronization. These ISA extensions facilitate adoption by allowing synchronization libraries to only be modified once (to support the new instructions) and then used with any hardware synchronization implementations that support the ISA's fallback semantics – including trivial implementations with no actual hardware synchronization support.

# 3.1 Design of MiSAR

Our proposed MSA is designed for a tiled many-core chip, where each tile contains a core and its local caches, a network-on-chip (NoC) router, a slice of the last-level cache (LLC) and coherence directory, and a slice of the synchronization accelerator. However, it can be adapted for use in other settings, e.g. those with broadcast interconnects (buses), centralized instead of distributed LLCs, etc.

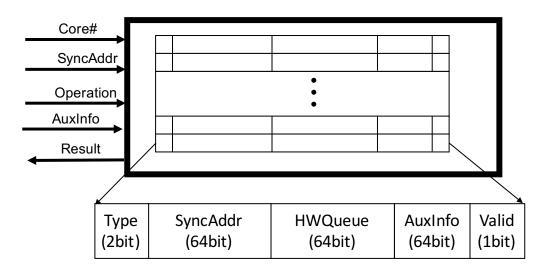

A single slice of our synchronization accelerator is shown in Figure 3.1. It contains a

(small) number of synchronization entries, and each entry tracks synchronization state of a single synchronization address. An entry in the MSA is a global "clearing house" for all synchronization operations for that particular address. To simplify interactions with coherence, we distribute the entire MSA according to the coherence home of the synchronization address: if an MSA entry is associated with a synchronization address, that entry must be in the LLC home tile of that synchronization address.

Each MSA entry contains the synchronization address it is associated with and a valid (V) bit. It also contains what type of synchronization it is currently used for, a bit vector (HWQueue), and an auxiliary information field. The HWQueue utilizes one bit per core to record which cores are waiting on that synchronization address, and also the lock owner in case of locks. The use of the auxiliary field depends on synchronization type, as will be explained later. Here we assume that each core runs only one thread. To support hardware multi-threading, the HWQueue would be augmented to have 1-bit per hardware thread. Note that, even with 64 cores and 2 threads per core, the overall state of a single-entry MSA would be less than 264 bits (33 bytes) in each of the 64 tiles.

Software interacts with the MSA using a set of 6 instructions, each corresponding to a synchronization operation (LOCK, BARRIER, COND\_WAIT, etc.). Each instruction has a return value that is either SUCCESS, FAIL, or ABORT. The instruction returns SUCCESS when the synchronization operation was successfully performed, FAIL when the operation cannot be performed in hardware, and ABORT when the operation was terminated by MSA due to OS thread scheduling. A more detailed discussion of ABORT, and how it differs from FAIL, is provided in Section 3.2. To simplify integration into the processor pipeline and to simplify interaction with memory consistency, each synchronization instruction acts as a memory fence and its actual synchronization activity begins only when the instruction is the next to commit. We fully model the resulting pipeline stalls in our experiments and find that they are negligible in most applications.

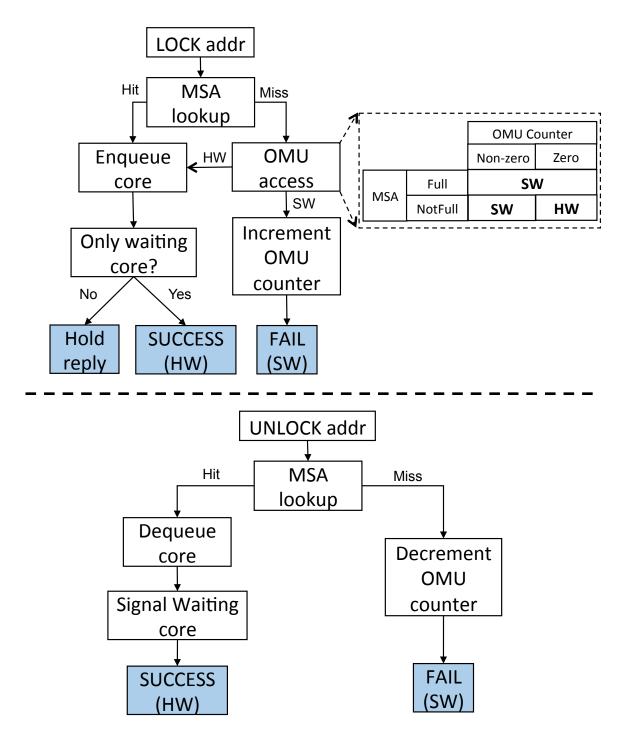

#### 3.1.1 Allocate/Deallocate MSA Entry

An MSA entry is allocated (if available) when a synchronization "acquire" request (LOCK, BARRIER, or COND\_WAIT) is received by the home of the synchronization address. The entry is evicted when its HWQueue becomes empty, i.e. when no thread waits for or owns the lock, when the barrier is released, or when no thread waits for a condition variable. As indicated earlier, if no MSA entry is available, the MSA simply returns FAIL, which results in using software implementation for the synchronization operation.

The MSA does not allocate a new entry for "release" requests (UNLOCK, COND\_SIGNAL and COND\_BCAST), so they fail if a matching entry is not found. This helps ensure that, if an acquire-type operation used a software implementation (LOCK, BARRIER, or COND\_WAIT returned FAIL), a release will also "default-to-software".

#### 3.1.2 Overflow Management Unit (OMU)