# An Inductively Powered Multichannel Wireless Implantable Neural Recording System (WINeR)

A Dissertation Presented to The Academic Faculty

by

Seung Bae Lee

In Partial Fulfillment Of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

Georgia Institute of Technology

August 2014

Copyright © 2014 by Seung Bae Lee

# An Inductively Powered Multichannel Wireless Implantable Neural Recording System (WINeR)

Approved by:

Dr. Maysam Ghovanloo, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Pamela Bhatti School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. John Papapolymerou School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Waymond Scott School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Joseph Manns Department of Psychology *Emory University*

Date Approved: June 11, 2014

To my family

#### ACKNOWLEDGEMENTS

First, I would like to thank my advisor Dr. Maysam Ghovanloo for the insight and inspiration that he has contributed to my research. When I encountered obstacles during my research, I was able to overcome them with his support and valuable advice. He helped me to convert an unrealistic goal into an achievable goal. With his advice, I developed the ability to solve challenging problems while conducting research. I appreciate his support. The GT-Bionics laboratory taught me how to be a real engineer. I am pleased to have had the opportunity to join the GT-Bionics laboratory and work with Dr. Maysam Ghovanloo during my Ph.D. research. I believe the experience in the GT-Bionics laboratory will be valuable for my future career.

Second, I am grateful to Dr. Pamela Bhatti and Dr. John Papapolymerou for their time and consideration in reviewing my Ph.D. thesis and serving as reading committee members. Their valuable feedback has been helpful to my research. I am also grateful to committee members Dr. Waymond Scott and Dr. Joseph Manns for their generosity, expertise and valuable advice.

During my seven years at Georgia Tech, many people assisted me in not only my Ph.D. research but also personal endeavors while residing in Atlanta. I appreciate the GT-Bionics laboratory members for their contributions. They have inspired me in every stage of my research. I consider them to be friends and collaborators who have motivated me.

Finally, I am grateful to Claire Lee, my parents and my sister. Without their endless love and support, I would not have been able to complete my Ph.D.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTSIV                              |

|-------------------------------------------------|

| LIST OF TABLES                                  |

| LIST OF FIGURES IX                              |

| SUMMARYXV                                       |

| CHAPTER I: INTRODUCTION                         |

| 1.1. Motivation                                 |

| 1.2. Background                                 |

| 1.2.1. Neural-Recording Applications            |

| 1.2.2. Neural-Recording Amplifier Design        |

| 1.2.3. Wireless Neural Recording Microsystems   |

| 1.2.4. Inductive Powering                       |

| 1.2.5. Recording and Stimulation                |

| 1.3. Dissertation Outline                       |

| CHAPTER II: WIRELESS NEURAL RECORDING SYSTEM 13 |

| 2.1. WINeR-6 SoC Design                         |

| 2.1.1. System Architecture                      |

| 2.1.2. Neural Signal Flow15                     |

| 2.1.3. Simulation and Measurement Results       |

| 2.2. Receiver and Computer Interface            |

| 2.2.1. Rx Design                                |

| 2.2.1.1. Yagi-Uda antenna                       |

| 2.2.1.2. RF front-end                           |

| 2.2.1.3. Analog signal conditioning             |

| 2.2.1.4. FPGA module                            |

| 2.2.1.5. DAC module                             |

| 2.2.1.6. Graphical user interface                       | 31 |

|---------------------------------------------------------|----|

| 2.2.2. Bench-Top Measurement Results                    |    |

| 2.2.2.1. Antennas                                       | 34 |

| 2.2.2.2. RF front-end                                   |    |

| 2.2.2.3. Complete WINeR-6 Tx-Rx operation               |    |

| 2.2.2.4. WINeR-6 noise performance                      | 40 |

| 2.3. Animal Experiments                                 | 44 |

| 2.3.1. Wideband Neural Recording for Seizure Detection  | 44 |

| 2.3.2. Single Unit Recording for Behavioral Experiments | 45 |

| CHAPTER III: DUAL-SLOPE CHARGE SAMPLING ANALOG FRONT    | Г- |

| END                                                     | 52 |

| 3.1. Introduction                                       | 52 |

| 3.2. DSCS-AFE Architecture                              | 53 |

| 3.2.1. LNA                                              | 55 |

| 3.2.2. OTA                                              | 56 |

| 3.2.3. DSCS and OTA Offset Cancellation                 | 57 |

| 3.3. Measurement Results                                | 58 |

| 3.4. Discussion                                         | 63 |

| CHAPTER IV: WINER-7 SYSTEM WITH A DUAL-SLOPE CHARGE     |    |

| SAMPLING ANALOG FRON-END                                | 64 |

| 4.1. Introduction                                       | 64 |

| 4.2. System Architecture                                | 66 |

| 4.2.1. Transmitter Unit                                 | 66 |

| 4.2.2. Receiver Unit                                    | 66 |

| 4.2.3. Power Management Data Transceiver (PMDT) Unit    | 68 |

| 4.3. Wide-Swing DSCS-AFE Architecture                   | 69 |

|                                                         |    |

| 4.3.1. LNA for Power Scheduling Operations               | 75       |

|----------------------------------------------------------|----------|

| 4.3.2. OTA                                               | 75       |

| 4.3.3. DSCS and OTA Offset Cancellation                  | 76       |

| 4.4. Stimulus Artifact Rejection                         | 77       |

| 4.5. FSK RF Transmitter                                  | 81       |

| 4.6. DSCS FPGA Demodulation for the WINeR-7 System       | 82       |

| 4.7. System Measurement Results                          | 83       |

| 4.7.1. Rx Antenna                                        | 87       |

| 4.7.2. Complete WINeR-7 Tx-Rx Operation                  | 88       |

| 4.7.3. WINeR-7 Noise Performance                         | 91       |

| 4.8. UWB Communication with the WINeR-7 System           |          |

| 4.8.1. UWB Transmitter                                   |          |

| 4.8.2. UWB Receiver                                      | 96       |

| CHAPTER V: ANIMAL EXPERIMENTS WITH THE WINER-7 SY        | STEM 100 |

| 5.1. Battery-Powered Animal Experiments                  | 100      |

| 5.2. Closed-Loop Powering Implementation                 | 101      |

| 5.3. Inductively Powered Freely Moving Animal Experiment | 103      |

| CHAPTER VI: CONCLUSIONS AND FUTURE STUDIES               | 107      |

| 6.1. Conculsions                                         | 107      |

| 6.2. Future Studies                                      | 109      |

| 6.2.1. Animal Experiments                                | 109      |

| 6.2.2. UWB Communication                                 |          |

| 6.2.3. WINeR-8 SoC Design                                | 110      |

|                                                          |          |

| REFERENCES                                               |          |

## LIST OF TABLES

| Table 1.1: State-of-the-art wireless neural-recording systems | .10 |

|---------------------------------------------------------------|-----|

| Table 2.1: Summary of the WINeR-6 system specifications       | .44 |

| Table 2.2: WINeR-6.5 specifications and benchmarking          | .61 |

| Table 4.1: WINeR-7 specifications and benchmarking            | .94 |

### LIST OF FIGURES

| <b>Fig. 1.1.</b> A conceptual view of the inductively powered wireless implantable neural recording system-on-a-chip with for long-term neural recording from small freely behaving animals                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Fig. 1.2.</b> State-of-the-art miniaturized wireless neural recording systems (a) [18], (b) [21], (c) [33], (d) [41], (e) [4], (f) [42], (g) [43], (h) [44]11                                                                                                                                                            |

| <b>Fig. 2.1.</b> WINeR-6 system block diagram with its key new features highlighted: (1)<br>LNA power scheduling, (2) improved RF transmitter, (3) inductive powering, and (4) closed-loop power control                                                                                                                    |

| <b>Fig. 2.2.</b> Schematic diagram of the WINeR-6 analog front-end: (a) two stage LNA, (b) OTA1, and (c) OTA216                                                                                                                                                                                                             |

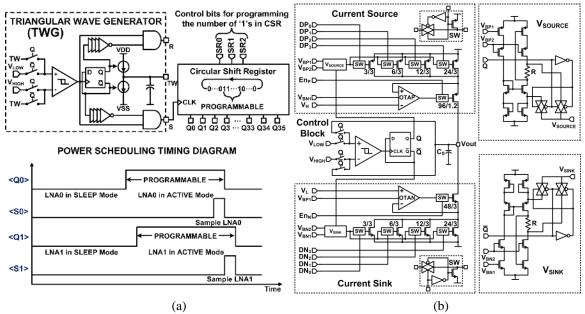

| <b>Fig. 2.3.</b> (a) Block diagram and timing diagram of the power scheduling mechanism.<br>The OTAs in the LNA block are switched between active ( $BW = 10 \text{ kHz}$ ) and sleep ( $BW = 200 \text{ Hz}$ ) modes by changing their bias currents, (b) schematic diagram of triangular waveform generator (TWG) block18 |

| Fig. 2.4. WINeR-6 neural signal flow diagram with emphasis on the transmitter SoC20                                                                                                                                                                                                                                         |

| <b>Fig. 2.5.</b> Die photomicrograph of the 32-ch WINeR-6 SoC fabricated using the ON semiconductor 0.5-µm 3M2P std. CMOS process (size: 4.9 × 3.3 mm <sup>2</sup> )21                                                                                                                                                      |

| <b>Fig. 2.6.</b> Comparison between the power consumption of each block in the WINeR-6 SoC as the percentage of the total power with and without power scheduling, which results in a 17% reduction in the total power consumption: (a) without power scheduling 7.05 mW and (b) with power scheduling 5.85 mW22            |

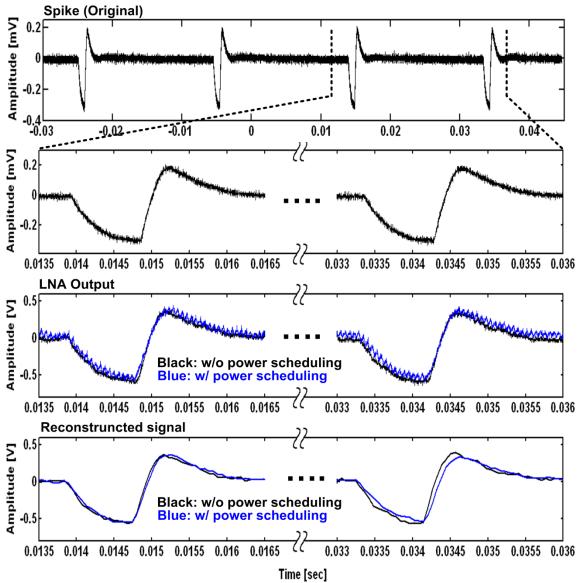

| <b>Fig. 2.7.</b> Measured waveforms from top: original artificial spike waveform, magnified spike waveform, waveforms recorded at the LNA output with (blue) and without (black) power scheduling, reconstructed signal in the PC23                                                                                         |

| <b>Fig. 2.8.</b> Block diagram of the entire wireless implantable neural recording (WINeR-6) system: Rx (top) and Tx (bottom)                                                                                                                                                                                               |

| Fig. 2.9. Three-element Yagi-Uda dipole antenna designed for 433 MHz carrier26                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

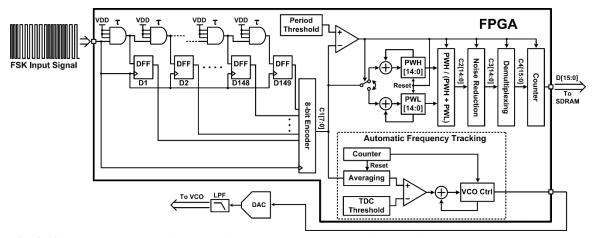

| <b>Fig. 2.10.</b> The FPGA-based high resolution TDC, using a delay cell chain with $\tau = 304$ ps and an automatic frequency tracking (AFT) block29                                                                                                       |

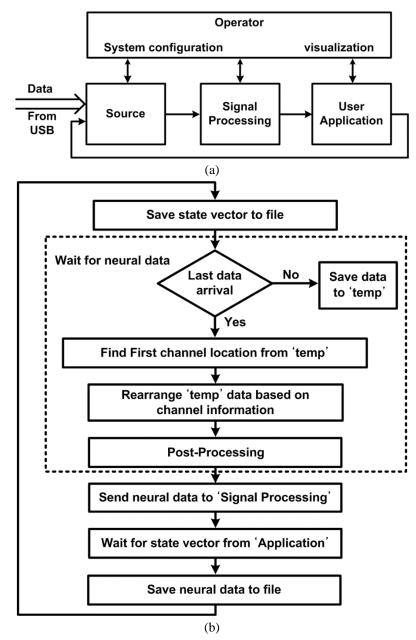

| <b>Fig. 2.11.</b> (a) The core modules and their interactions in the BCI-2000, (b) Data acquisition flowchart of the "Source" module                                                                                                                        |

| Fig. 2.12. WINeR-6 Rx and Tx hardware components                                                                                                                                                                                                            |

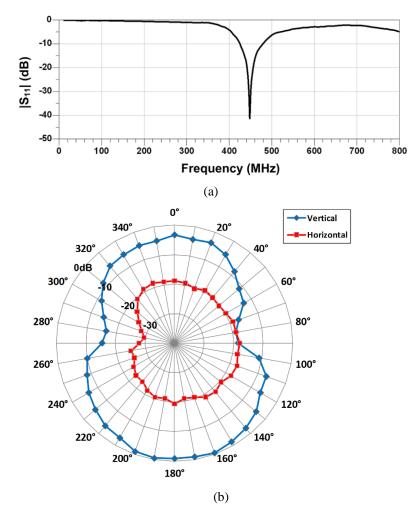

| <b>Fig. 2.13.</b> (a) Measured return loss of the Rx Yagi-Uda antenna. The -10 dB bandwidth was 54 MHz from 424 to 478 MHz frequency range. (b) Relative radiation patterns of WINeR-6 Tx at 433 MHz measured by the Rx antenna35                           |

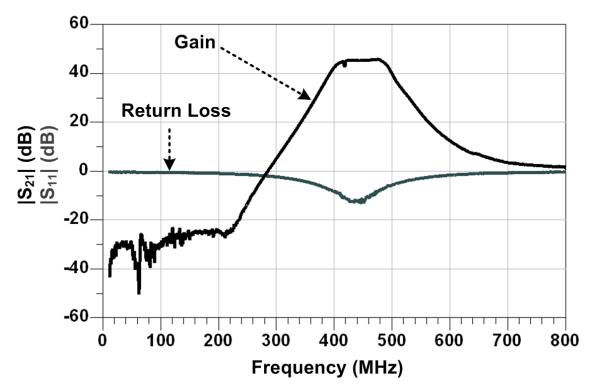

| Fig. 2.14. Measured return loss and gain of the RF front-end (RF module)                                                                                                                                                                                    |

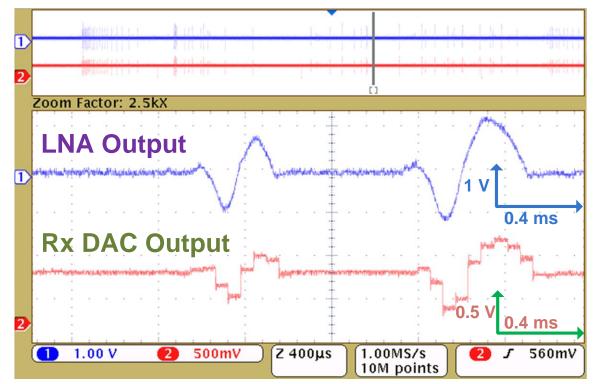

| <b>Fig. 2.15.</b> Top trace: One of the LNA outputs on the WINeR-6 Tx when a pre-<br>recorded neural signal with 1 mV spikes was applied to the input. Bottom<br>trace: DAC output on the WINeR-6 Rx for the same channel at 1.5 m away37                   |

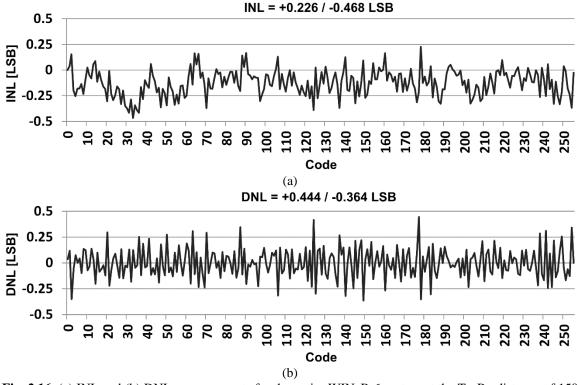

| <b>Fig. 2.16.</b> (a) INL and (b) DNL measurements for the entire WINeR-6 system at the Tx-Rx distance of 150 cm                                                                                                                                            |

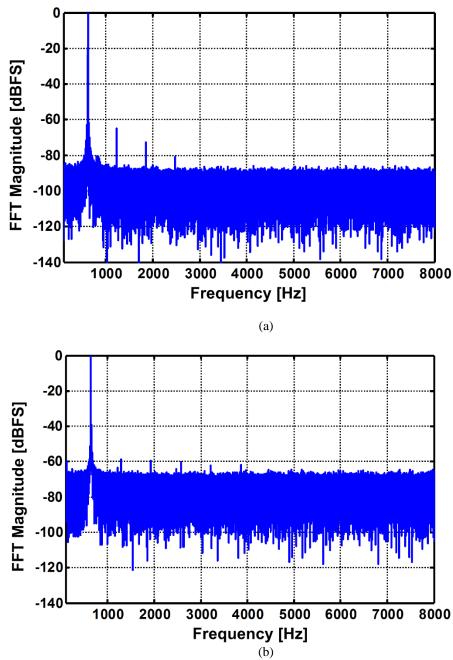

| <b>Fig. 2.17.</b> Tone test measurements of the WINeR-6 system (a) without wireless link, (b) at the Tx-Rx distance of 150 cm40                                                                                                                             |

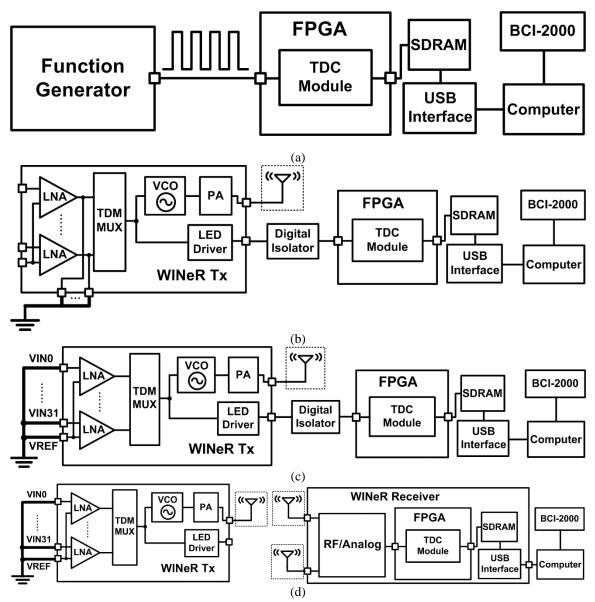

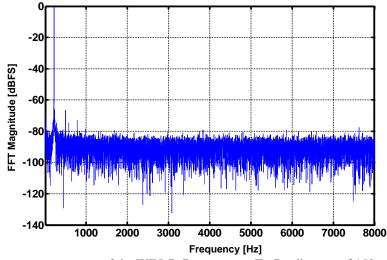

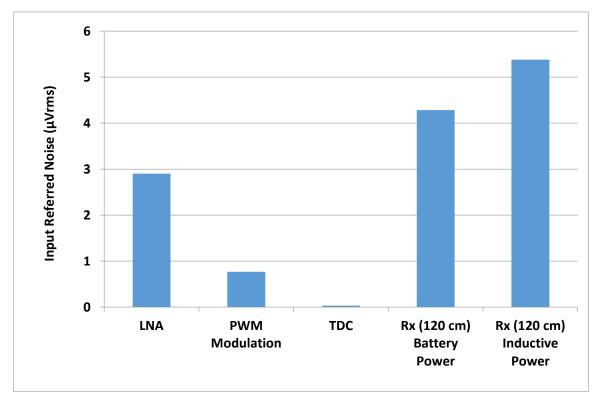

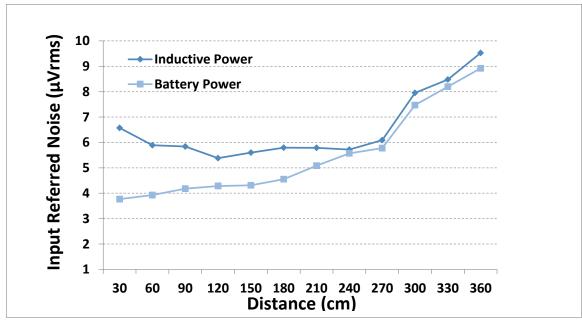

| Fig. 2.18. Various noise measurement configurations to find out the contribution of each major WINeR-6 component: (a) TDC noise, (b) ATC + TDC noise without wireless link, (c) LNA + ATC + TDC noise without wireless link, (d) Noise of the entire system |

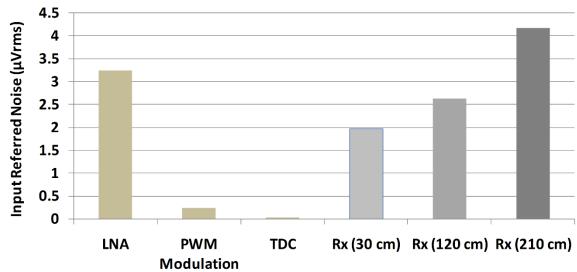

| Fig. 2.19. Noise contributions of different WINeR-6 blocks at 640 kSps43                                                                                                                                                                                    |

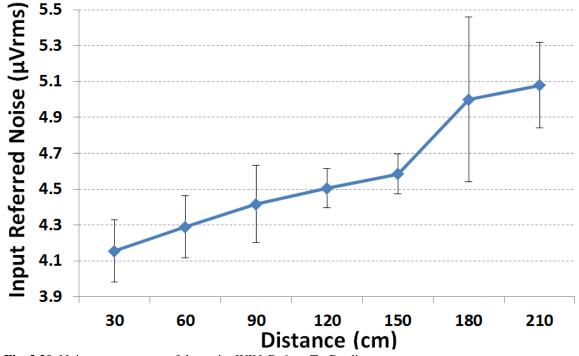

| Fig. 2.20. Noise measurement of the entire WINeR-6 vs. Tx-Rx distance                                                                                                                                                                                       |

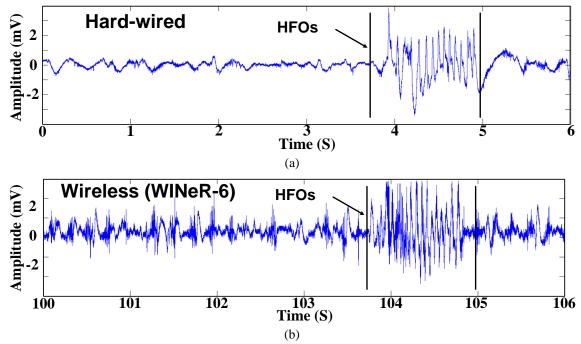

| <b>Fig. 2.21.</b> Epilepsy detection by LFP recording from (a) Hard-wired system and (b) WINeR-6                                                                                                                                                            |

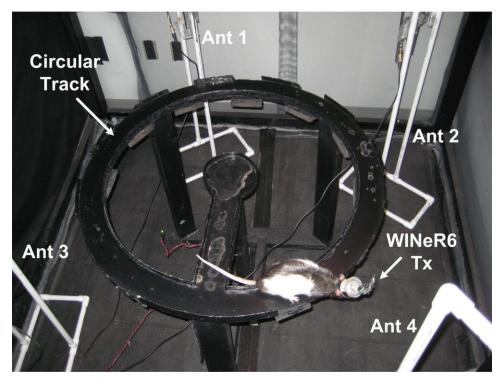

| <b>Fig. 2.22.</b> Awake freely behaving animal experimental setup. The rat completed two sets of 40 laps on a circular track with an outer diameter of ~1 m, while neural signals were recorded simultaneously from 32 channels using the WINeR-6 and a hardwired setup. The quality of the recorded neural signals was observed in real time, but single-unit activities were classified offline and used to construct the place fields in each case after synchronizing and combining the neural activity with the animal position from the recorded video |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

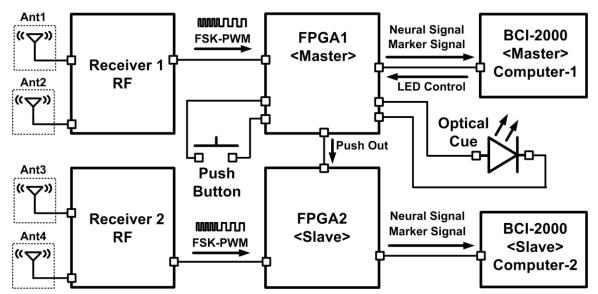

| <b>Fig. 2.23.</b> Synchronization between two WINeR-6 Rxs, each of which has two antennas, with a push button as well as a video stream, using an optical cue48                                                                                                                                                                                                                                                                                                                                                                                              |

| Fig. 2.24. Time domain representation of 32-ch recorded signals in real time using the BCI2000 GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

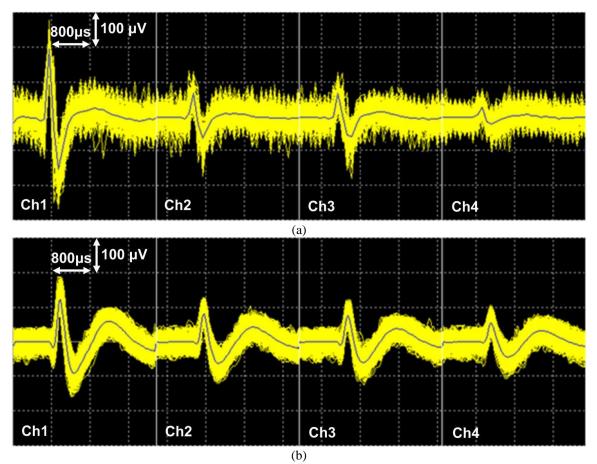

| <b>Fig. 2.25.</b> Spike classification of 4 individual channels in Tetrode 5 from (a) WINeR-6 and (b) NSpike systems using Plexon's Offline Sorter                                                                                                                                                                                                                                                                                                                                                                                                           |

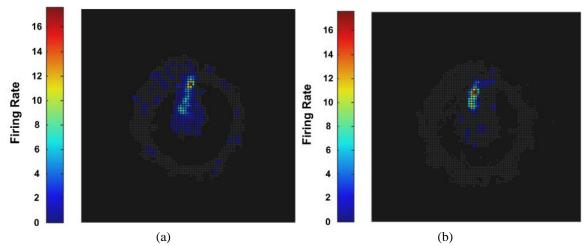

| <b>Fig. 2.26.</b> Comparison between place fields resulted from (a) WINeR-6 wireless and (b) NSpike hardwired recordings                                                                                                                                                                                                                                                                                                                                                                                                                                     |

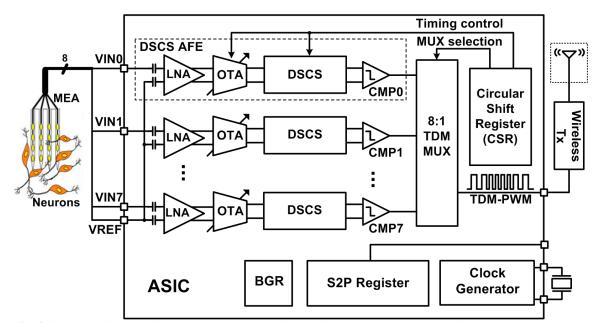

| <b>Fig. 3.1.</b> Block diagram of an 8-ch DSCS-based wireless implantable neural recording (WINeR-6.5) system                                                                                                                                                                                                                                                                                                                                                                                                                                                |

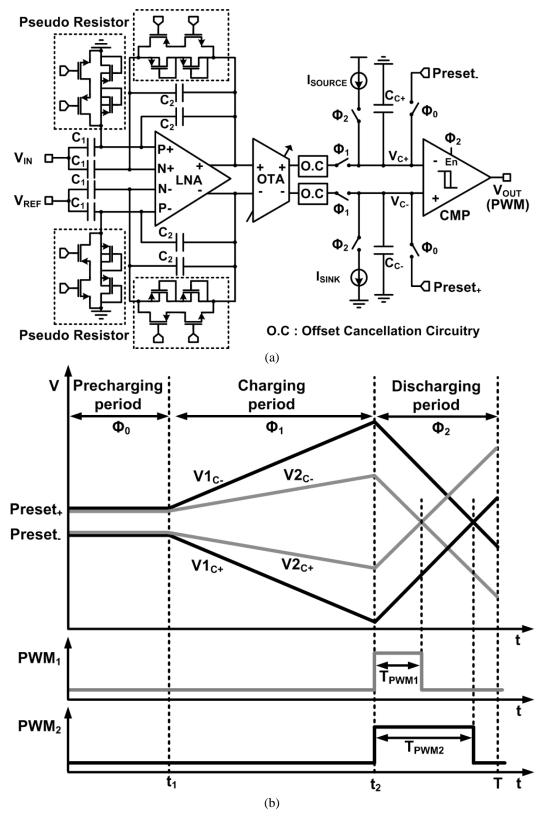

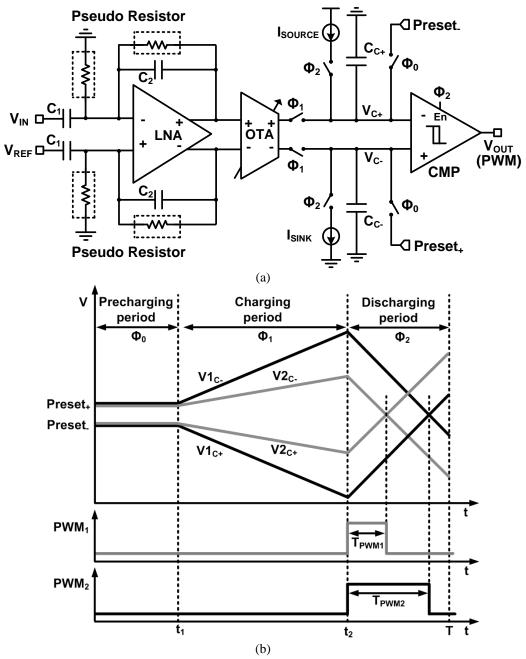

| <b>Fig. 3.2.</b> DSCS-AFE for a single channel: (a) Block diagram, (b) Operating waveforms of the dual-slope integration for two different input voltages54                                                                                                                                                                                                                                                                                                                                                                                                  |

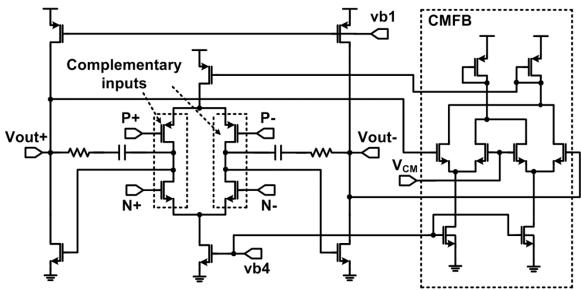

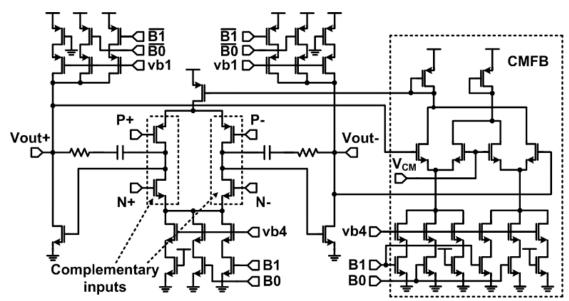

| Fig. 3.3. Schematic diagram of the fully-differential LNA with CMFB56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

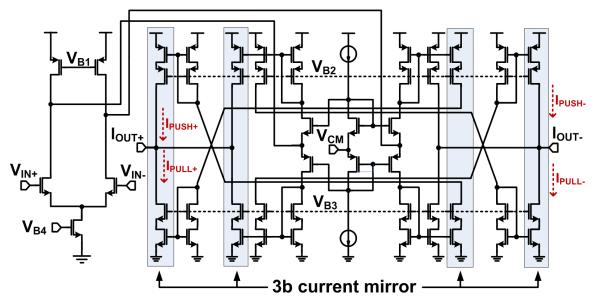

| <b>Fig. 3.4.</b> Schematic diagram of the fully diff. OTA with 3-bit adjustable $g_m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

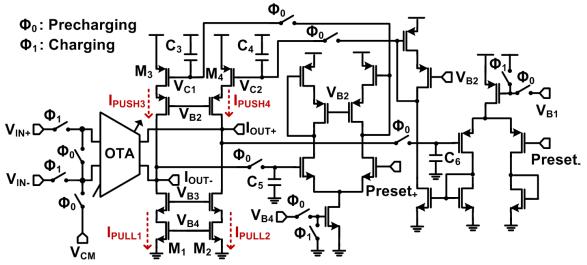

| Fig. 3.5. Schematic diagram of the DSCS block including OTA offset cancellation circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

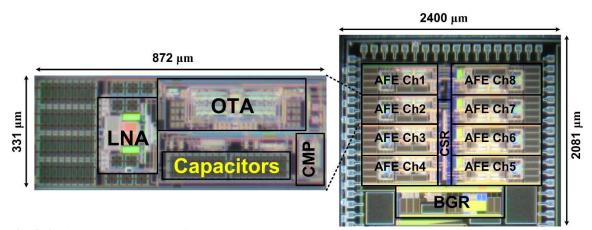

| <b>Fig. 3.6.</b> Die photomicrograph of the 8-channel neural recording SoC with DSCS-AFE, implemented in the TSMC 0.35- $\mu$ m CMOS (size: 2.4 × 2.1 mm <sup>2</sup> )59                                                                                                                                                                                                                                                                                                                                                                                    |

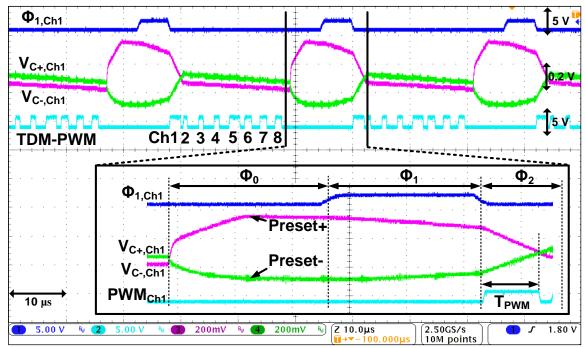

| Fig. 3.7. DSCS-AFE measured waveforms at 250 ksps from 8 channels60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

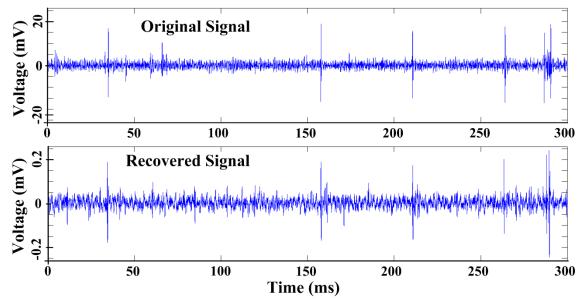

| Fig. 3.8 | • The original and recovered pre-recorded spike signals, sampled at 31.25 kHz62                                                                                                                                                                  |

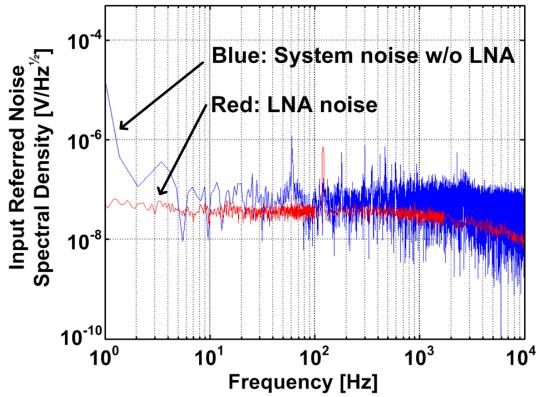

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 3.9 | • Input referred noise of the LNA and the entire system without LNA                                                                                                                                                                              |

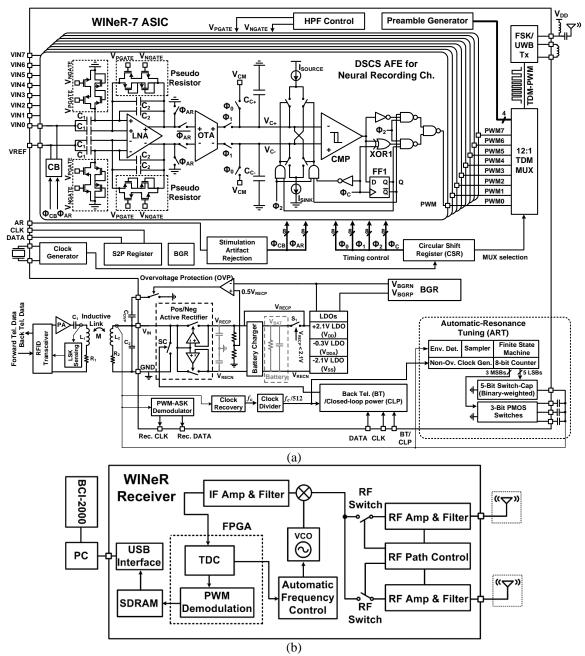

| Fig. 4.1 | <ul> <li>Block diagram of an 8-channel DSCS-based wireless implantable neural<br/>recording (WINeR-7) system, (a) Transmitter unit, (b) Receiver unit</li></ul>                                                                                  |

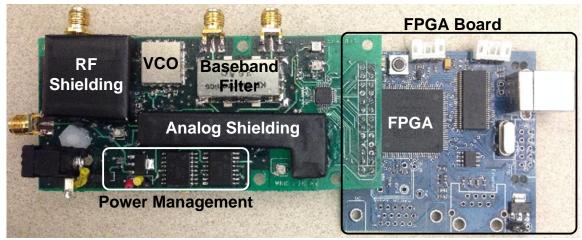

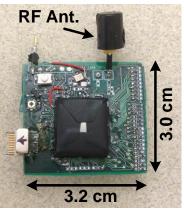

| Fig. 4.2 | • WINeR-7 FSK Rx PCB67                                                                                                                                                                                                                           |

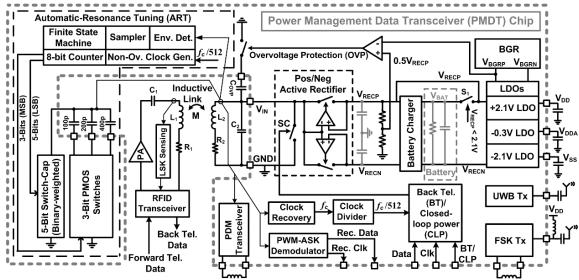

| Fig. 4.3 | Block diagram of the highly efficient and adaptive PMDT block of the WINeR-7 system                                                                                                                                                              |

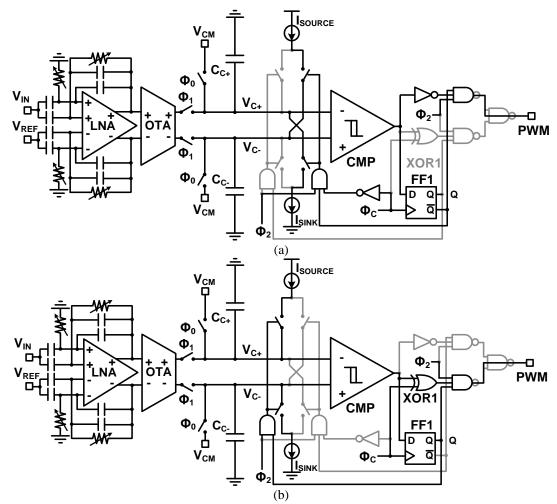

| Fig. 4.4 | • DSCS-AFE prototype I for a single channel: (a) Block diagram, (b) Operating waveforms of the dual-slope integration for two different input voltages70                                                                                         |

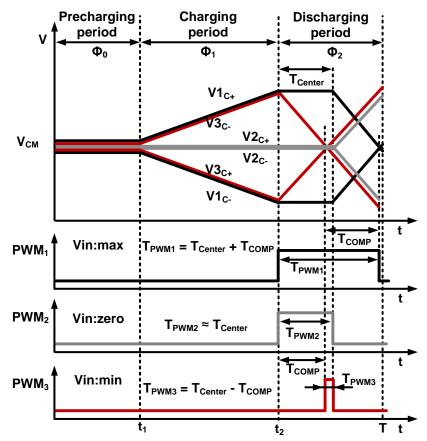

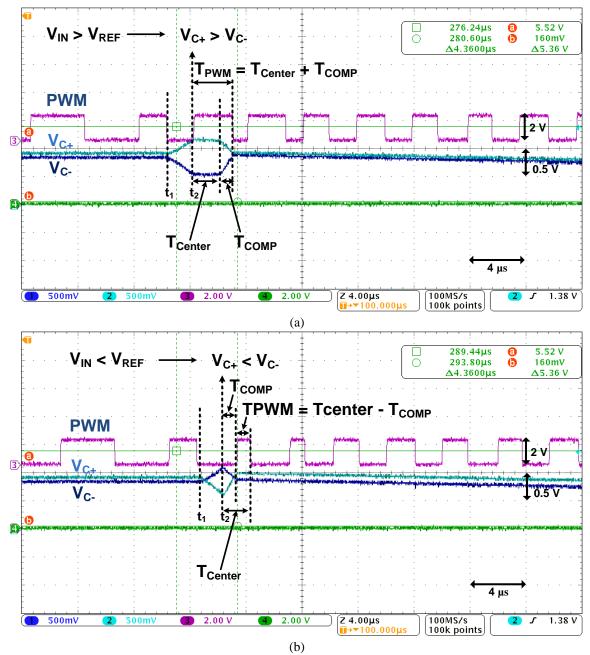

| Fig. 4.5 | • WINeR-7 DSCS-AFE Operating waveforms of the dual-slope integration for two different input voltages                                                                                                                                            |

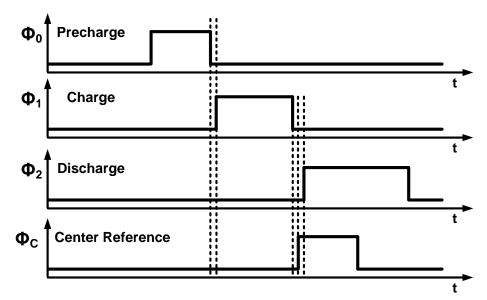

| Fig. 4.6 | • Four clock signals for the WINeR-7 DSCS-AFE73                                                                                                                                                                                                  |

| Fig. 4.7 | • WINeR-7 DSCS-AFE operating block diagrams when (a) $V_{C+} > V_{C-}$ and $Q = 0$ , (b) $V_{C+} < V_{C-}$ and $Q = 1$                                                                                                                           |

| Fig. 4.8 | • Schematic of the fully differential LNA with the CMFB circuitry75                                                                                                                                                                              |

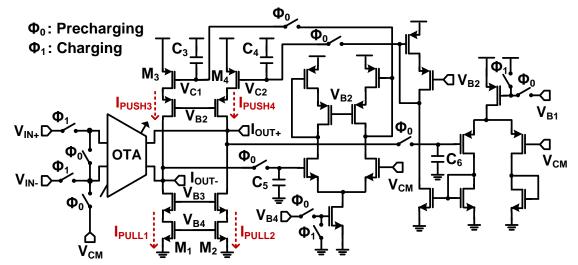

| Fig. 4.9 | • Schematic of the DSCS block including the OTA offset cancellation circuitry.76                                                                                                                                                                 |

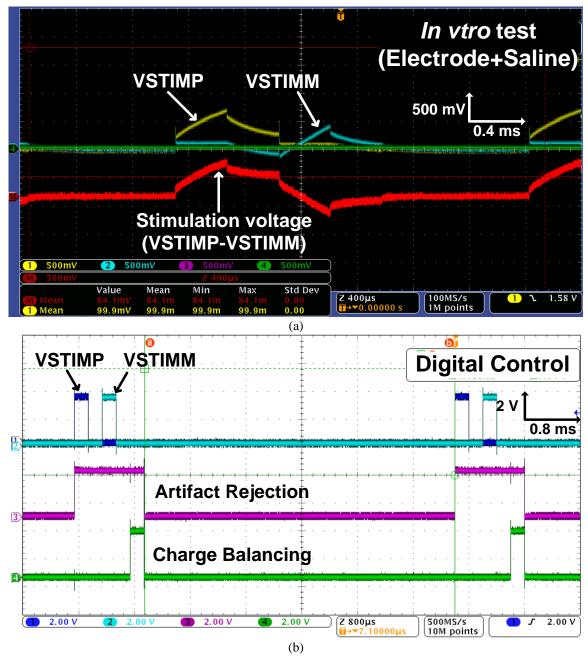

| Fig. 4.1 | <b>0.</b> (a) Measured stimulation waveforms from the <i>in vitro</i> experiments showing different stimulation currents, (b) Digital control signals: differential simulation signals, artifact rejection signal, and charge balancing signal79 |

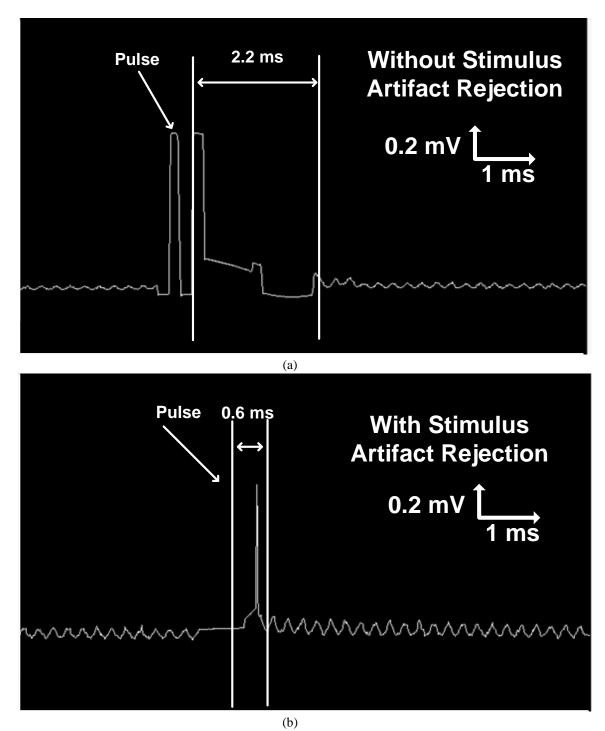

| Fig. 4.1 | <ol> <li>Recorded waveforms in the BCI2000 (a) without stimulus artifact rejection,<br/>(b) with stimulus artifact rejection</li></ol>                                                                                                           |

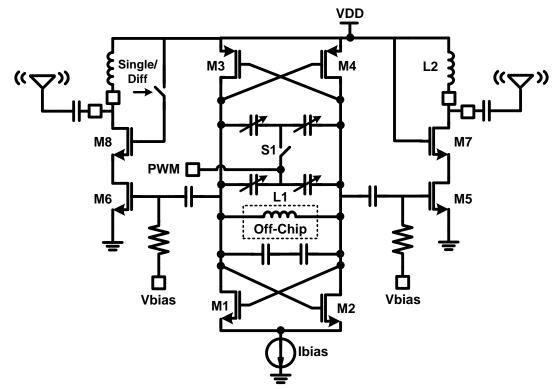

| Fig. 4.1 | 2. Schematic of the FSK Tx81                                                                                                                                                                                                                     |

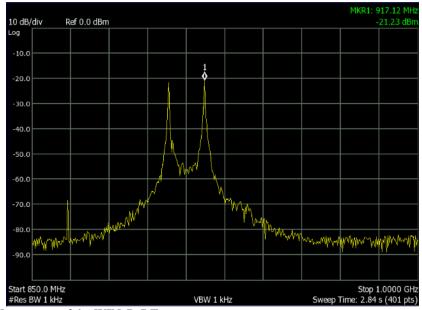

| Fig. 4.13. FSK spectrum of the WINeR-7 Tx                                                                                                                                          | 82 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

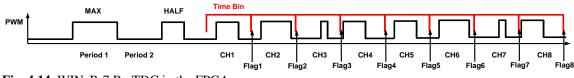

| Fig. 4.14. WINeR-7 Rx TDC in the FPGA                                                                                                                                              | 83 |

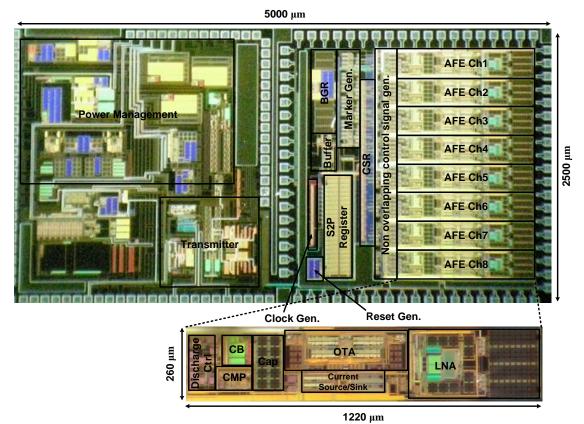

| <b>Fig. 4.15.</b> Die photomicrograph of the 8-channel neural recording SoC with the DSCS AFE, implemented in the TSMC 0.35- $\mu$ m CMOS (size: 2.5 × 2.5 mm <sup>2</sup> )       |    |

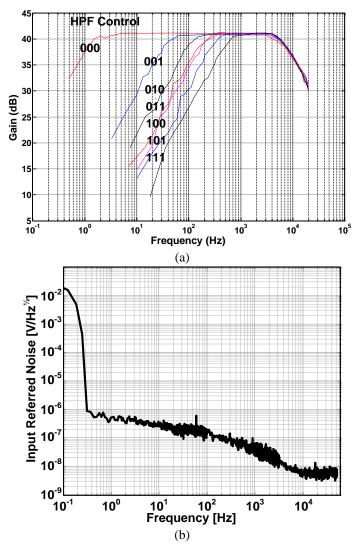

| Fig. 4.16. LNA measurements of (a) the gain and bandwidth and (b) the input referred noise                                                                                         |    |

| Fig. 4.17. DSCS-AFE measurement waveforms from 8 channels                                                                                                                          | 86 |

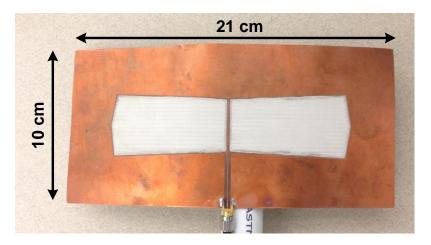

| Fig. 4.18. Bow tie antenna for 915 MHz carrier                                                                                                                                     | 87 |

| Fig. 4.19. Measured return loss of the Rx bow tie antenna                                                                                                                          | 88 |

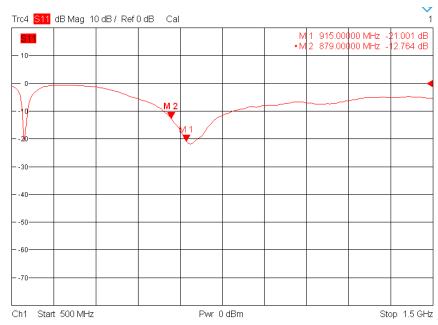

| <b>Fig. 4.20.</b> Recovered signals in BCI2000 GUI from (a) simultaneous 8-channel bench-<br>top hard-wired recording and (b) wireless recording at a Tx-Rx distance of<br>100 cm. |    |

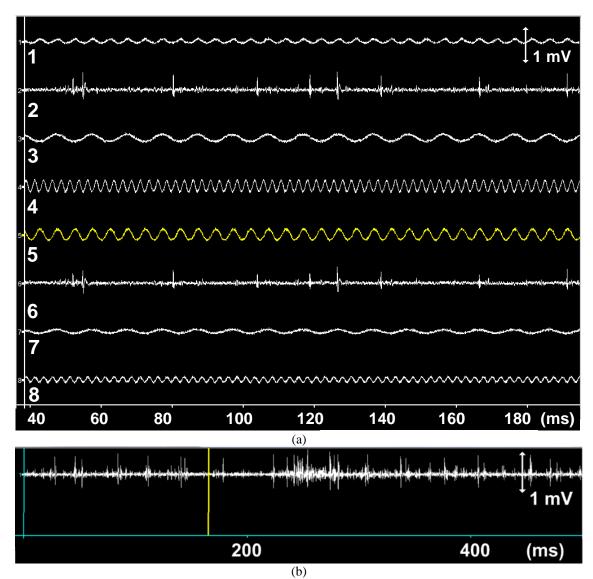

| Fig. 4.21. (a) INL and (b) DNL measurements for the entire WINeR-7 system at a Tx-<br>Rx distance of 200 cm                                                                        |    |

| Fig. 4.22. Tone test measurements of the WINeR-7 system at a Tx-Rx distance of 150 cm.                                                                                             |    |

| Fig. 4.23. Noise contributions of different WINeR-7 blocks at 21 kSps                                                                                                              | 92 |

| Fig. 4.24. Noise measurement of the entire WINeR-7 vs. Tx-Rx distance                                                                                                              | 93 |

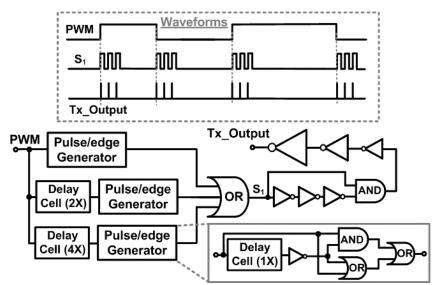

| Fig. 4.25. Schematic of the sub-GHz-range PWM-IR-UWB                                                                                                                               | 95 |

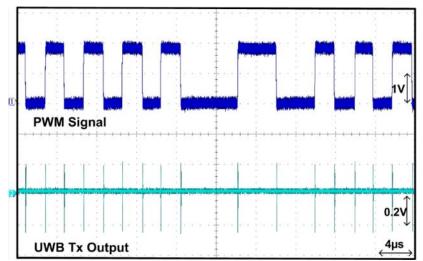

| Fig. 4.26. Measurement results of the sub-GHz-range PWM-IR-UWB                                                                                                                     | 95 |

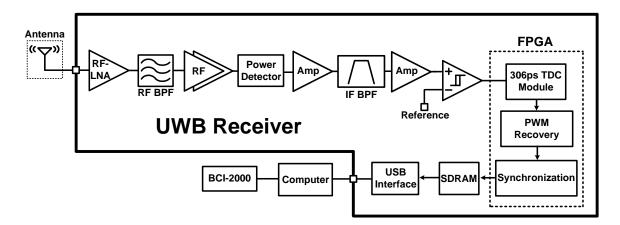

| Fig. 4.27. Schematic of the UWB receiver.                                                                                                                                          | 96 |

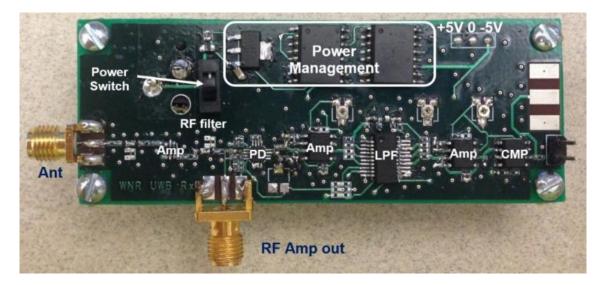

| Fig. 4.28. UWB receiver board                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

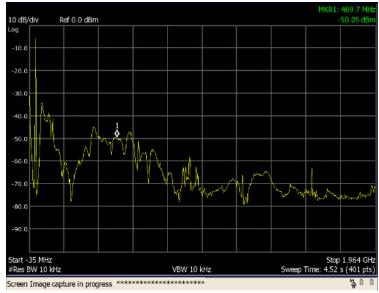

| Fig. 4.29. Received RF spectrum output after the RF Amplifer                                                                                                                                                                      |

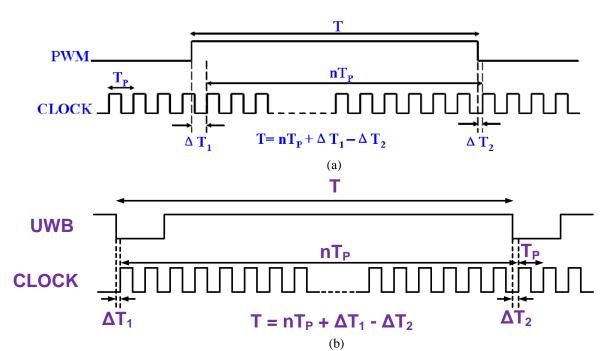

| Fig. 4.30. Two different TDC methods from (a) OOK Rx and (b) UWB Rx                                                                                                                                                               |

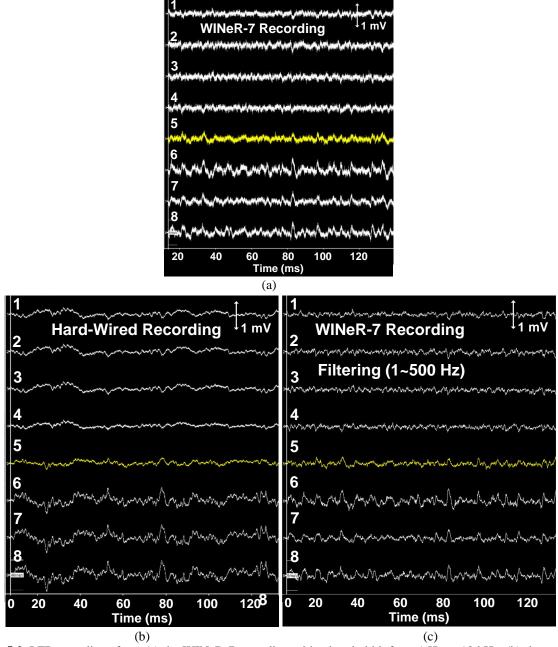

| <b>Fig. 4.31.</b> Simultaneous eight-channel bench-top wireless recording with a WINeR-7 system with the UWB communication at a Tx-Rx distance of 40 cm (BCI2000 GUI)                                                             |

| Fig. 5.1. WINeR-7 headstage for battery-powered animal experiments100                                                                                                                                                             |

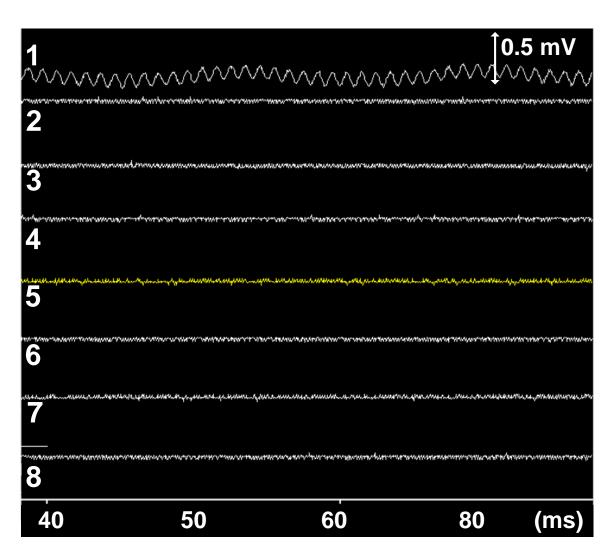

| <b>Fig. 5.2.</b> LFP recordings from (a) the WINeR-7 recording with a bandwidth from 1 Hz to 10 kHz, (b) the hard-wired system, and (c) the offline data process of the WINeR-7 recording with a bandwidth from 1 Hz to 10 kHz101 |

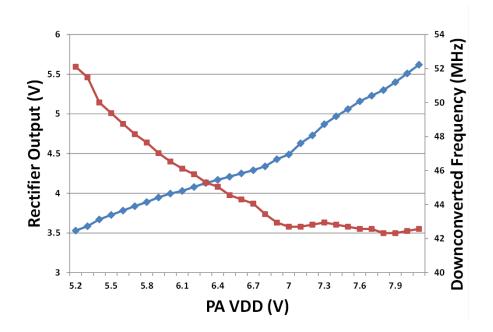

| <b>Fig. 5.3.</b> Rectifier output voltage of the WINeR-7 headstage and the downconverted frequency of the WINeR-7 Rx when the power amplifier voltage for inductive powering varies                                               |

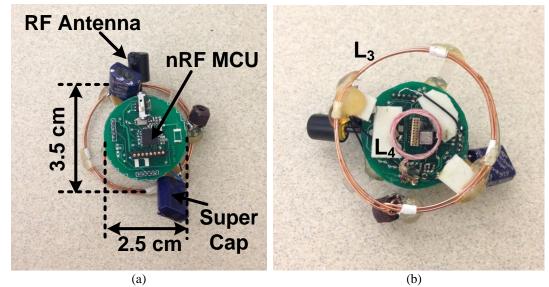

| Fig. 5.4. WINeR-7 headstage for inductively-powered animal experiments, (a) top view, (b) bottom view                                                                                                                             |

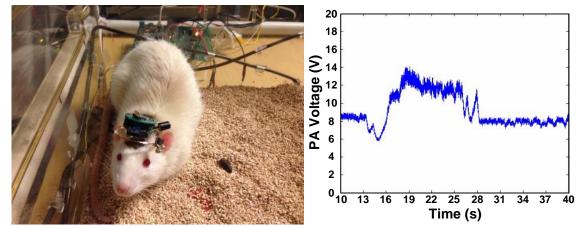

| Fig. 5.5. (a) Animal experiment set-up, (b) The <i>in vivo</i> results for the PA supply voltage during 40 sec                                                                                                                    |

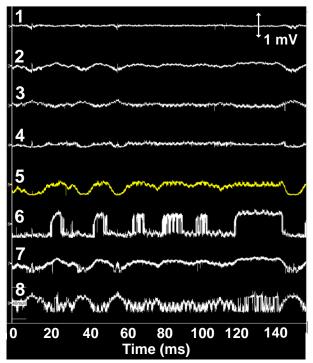

| <b>Fig. 5.6.</b> LFP recordings from the WINeR-7 system operated by inductive powering with a bandwidth of 1 Hz to 10 kHz                                                                                                         |

#### SUMMARY

The objective of this research is to advance a multi-channel wireless implantable neural recording (WINeR) system for electrophysiology and behavioral neuroscience research applications. The system is composed of two units: a system-on-a-chip (SoC) transmitter (Tx) unit and a receiver (Rx) unit. In the Tx unit, the outputs are combined with marker signals and modulated into pulse widths after the neural signals are amplified and filtered by an array of low-noise amplifiers (LNA). The next step involves time-division multiplexing (TDM) of pulse-width modulation (PWM) signals. The TDM-PWM signal drives RF transmitter block and is transmitted by an antenna. To satisfy the needs of neuroscientists during animal experiments, the proposed WINeR system provides long-term recording with inductive powering and stimulus-artifact rejection for closed-loop operations, which requires simultaneous stimulation and recording.

The Rx is another critical unit for wireless-link communication. To increase the area of wireless coverage, multiple antennas are used for the Rx. In addition, the automatic frequency-tracking method is used to track free-running Tx frequencies, and a smart time-to-digital conversion method is used to reduce noise and interference. A high-throughput computer interface and software are also developed to continuously receive and store neural data. The WINeR system is a potential tool for neuroscientists due to several advantages, such as a reliable wireless link with large coverage and no blind spots, low power consumption, an unlimited power source, and a stimulation function.

The contributions from this research are summarized as follows:

- 1. Development of a low-power and low-noise neural recording amplifier

- 2. Development of a power scheduling mechanism for a multi-channel analog frontend (AFE) to conserve power consumption

- 3. Development of a dual-slope charge sampling AFE, which can simultaneously amplify and filter neural signals and easily modulate them into PWM signals

- 4. Development of a wideband multi-antenna receiver for the wireless recording of animals in large arenas

- 5. Development of a real-time data acquisition system for multi-channel neural recordings

- 6. Development of a pulse-width-modulation impulse-radio ultra-wideband (PWM-IR-UWB) receiver for a low-power wireless neural recording system

- Development of a robust closed-loop power transmission system based on RF back telemetry

- 8. Demonstration of a battery-powered WINeR system tested in scientifically meaningful *in vivo* experiments in large arenas

- 9. Demonstration of data acquired from an inductively powered WINeR system from an animal in a home cage

#### **CHAPTER I**

#### **INTRODUCTION**

#### 1.1. Motivation

The multisite monitoring of brain activities is essential to the ongoing development of effective therapies for neurological diseases, such as epilepsy, dementia, and Alzheimer's disease. Over the past few years, researchers have attempted to engineer multichannel neural recording systems with minimum disturbance to the animal subject. Wireless operations possess several distinct advantages compared with wired operations, including the elimination of tethering effects, minimal irritation, a low risk of infection, smaller size, and simplicity. However, hardwired systems remain more popular than their wireless counterparts in the majority of neurophysiology laboratories. Wireless systems continue to experience a variety of problems, such as limited battery lifetime, limited wireless coverage area, and poor connectivity, which render them unreliable for state-of-the-art behavioral neuroscience studies.

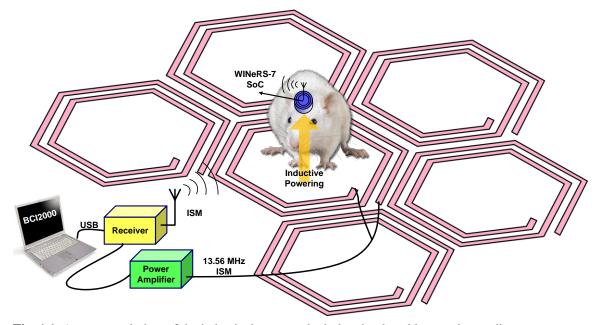

**Fig. 1.1.** A conceptual view of the inductively powered wireless implantable neural recording system-on-achip with for long-term neural recording from small freely behaving animals.

The objective of this research is to develop a multi-channel wireless implantable neural recording (WINeR) system that outperforms existing systems. A WINeR system can provide a reliable wireless link with large coverage without blind spots, low power consumption, an unlimited power source, and a stimulation function with stimulusartifact rejection. Thus, the developed system enables neuroscientists to eliminate cables from their experimental setups and detect high-density and meaningful neural signals.

A conceptual view of the WINeR system is provided in Fig. 1.1, which employs two independent wireless links in the industrial-scientific-medical (ISM) band at 433/915 MHz and 13.56 MHz for wireless neural recording and inductive powering, respectively.

#### 1.2. Background

#### **1.2.1.** Neural-Recording Applications

Neural recording technology has become significant in the medical treatment of neurological diseases and neuroscience research [1]-[4]. Devices that target neurological diseases, known as neuroprostheses, replace sensory or motor functions that may become lost as a result of injury or disease. These devices must be chronically implantable, safe, and highly reliable for use in humans as part of a therapeutic paradigm. Size, power consumption, and carrier frequency are highly constrained in these devices due to implantation requirements. Cochlear implants and deep brain stimulation (DBS) are examples of neuroprostheses that produce undeniably positive outcomes [5].

Devices that target neuroscience research applications are frequently used on animal subjects and do not always have to be implantable. They are frequently used to monitor interactions among large populations of neurons because animals perform specific tasks that involve processing sensory inputs, generating motor control outputs, or performing specific cognitive functions, such as learning and memory [6]. However, these devices must compete with sophisticated instruments that are employed by the neuroscience community [7]. These devices should provide the same quality and quantity of information as their previous counterparts while resolving some of their limitations, such as hardwired interconnects. The tethering effect produced by wires attached to small animals may affect animal behavior. These devices deteriorate rapidly, increase noise and motion artifacts, and require costly motorized commutators as part of the recording setup.

#### 1.2.2. Neural-Recording Amplifier Design

The depolarization of the membrane of a neuron generates extracellular action potentials (AP) that are waveforms in the range of 100 Hz to 10 kHz with amplitudes ranging from 50  $\mu$ Vpp to 1 mVpp. Another important neural signal is the local field potential (LFP) that consists of lower-frequency neural waveforms ranging from mHz to 200 Hz with amplitudes ranging from 500  $\mu$ Vpp to 5 mVpp [8]. It is very important to have a low-noise neural amplifier design to record both neural signals. Indeed, achieving a low-cutoff frequency in the sub-hertz range with a small footprint and low-power consumption on the chip is a challenge for LNA designers. Among them, Harrison et al. have reported a remarkable study [9], in which they presented a topology for a metaloxide-semiconductor (MOS) and bipolar pseudo-resistor with a capacitor feedback amplifier. This topology has been used by many other groups [10], [11]. In addition, Harrison et al. resurrected a figure-of-merit for noise performance known as the noise efficiency factor (NEF), which is defined as

$$NEF = V_{ni,rms} \sqrt{\frac{2I_{tot}}{\pi \cdot U_T \cdot 4kT \cdot BW}},$$

where  $V_{ni,rms}$  is the input-referred rms noise voltage,  $I_{tot}$  is the total amplifier supply current, and *BW* is the amplifier bandwidth in hertz.  $U_T$  is the thermal voltage kq/T, k is the Boltzmann constant, and T is the absolute temperature. An amplifier using a single bipolar transistor (with no 1/f noise) has an NEF of one; all practical circuits have higher values. Using NEF has encouraged designers to invent topologies and techniques with successively lower and improved NEFs.

However, in these designs, the MOS resistance highly depends on the input and output voltages, causing distortion when large signals appear at the output. This is not uncommon, particularly at the output of the second OTA in the presence of local field potentials (LFPs) that are in-band neural signals from large populations of neurons firing in sync and creating low-frequency signals with relatively large amplitudes. To solve this problem, Zou et al. developed a balanced tunable pseudo-resistor to minimize the resistance distortion depending on the output voltage [12]. In addition, although 895 nA of low-power consumption was remarkable, the bandwidth was low for neural-recording applications.

Several interesting LNA architectures have been proposed after Harrison. One of the most interesting circuit configurations that has been developed to improve the NEF is that of the source degeneration resistor, which is proposed in [13]. The noise contribution from a source-degenerated load is mainly from degeneration resistors, whose noise is essentially thermal, whereas MOSFETs in a regular active load contribute a large amount of 1/f noise. Otis et al. proposed a complementary input stage to double the effective transconductance with a given bias current [14]. Muller et al. used a digitally intensive architecture to reduce system area and enable operation from a 0.5 V supply. The architecture replaced AC coupling capacitors and analog filters with a dual mixed-signal servo loop, which allows for the simultaneous digitization of the action and local field potentials. A noise-efficient DAC topology and a compact, boxcar sampling ADC are used to cancel input offset. The prototype occupies 0.013 mm<sup>2</sup> while consuming 5  $\mu$ W and achieving 4.9 µVrms of input-referred noise over a 10 kHz bandwidth [15]. Finally, Gao et al. used switched-capacitor filtering to provide a well-controlled frequency response, and utilized windowed integrator sampling to mitigate noise aliasing, enhancing noise/power efficiency [16].

#### **1.2.3.** Wireless Neural Recording Microsystems

Over the past few years, researchers have been trying to engineer multichannel neural-recording systems with minimum disturbance to animal subjects. To this end, wireless operation has several clear advantages in comparison to wired operation, such as not having tethering effects, exhibiting less irritation or a lower risk of infection, being smaller in size, and being easy to use. However, hardwired systems are still far more popular than their wireless counterparts in the majority of neurophysiology labs. Wireless systems still suffer from problems such as limited battery lifetime, limited wireless coverage area, and poor connectivity, which render them unreliable for state-of-the-art behavioral neuroscience studies.

The majority of ongoing wireless neural interfacing research has been focused on transferring some sort of limited processing capability to the implantable front-end to limit the required wireless bandwidth at the cost of losing some neural information and complicating the implantable unit [2], [17], [18]. However, these data reduction methods are employed only for spike detection. This is not possible for LFP recording, although LFPs are becoming increasingly important in neurophysiological investigations [19]. Moreover, the majority of the research on wireless neural recording performed to date has been focused on the high-density recording front-ends and the transmitting (Tx) side of the system, where the main challenges are miniaturization, low-power consumption, and low noise to the extent that the Tx side could eventually be implanted in the animal or human body. However, in a complete wireless data acquisition system, the wireless link, external receiving (Rx) side, computer interface, data storage, and user interface should be able to support the Tx unit for the entire system to operate smoothly without losing information that is important for the further processing of the recorded signals.

The most challenging problems to address in designing the Rx side are bandwidth, sensitivity, coverage of the experimental arena without leaving blind spots, and continuous streaming of the acquired data to the computer without any losses. In some early designs, analog samples were amplified, filtered, and directly fed into a voltage-controlled oscillator (VCO) on the Tx side to be frequency modulated (FM) after time-division multiplexing (TDM). On the Rx side, commercial FM receivers, such as the WinRadio (Melbourne, Australia) were employed [20]. However, because of the bandwidth limitation (~150 kHz) on the Rx side, such systems suffered considerable crosstalk between channels, which also limited the number of channels to fewer than 10. Increasing the Rx bandwidth can alleviate these problems, as demonstrated in a 32-channel wireless neural-recording system by Triangle Bio-Systems (Durham, NC), which operates at 3.2 GHz using a custom-designed Rx with a bandwidth of 300 MHz [21]. Another advantage of increasing the carrier frequency is reducing the size of the optimal antennas. However, such frequencies are not useful for implantable devices because of the significant absorption of high-frequency electromagnetic fields in the tissue [22].

As a result of the above-mentioned limitations, most recent wireless neuralrecording systems have on-chip analog-to-digital converters on the Tx side followed by amplitude, on/off, frequency, or phase-shift keying (ASK/OOK/FSK/PSK) to transmit digital samples in the industrial, scientific and medical (ISM) band. The HermesD system, for instance, utilized an FSK scheme along with a 24 Mbps custom-designed transceiver [4]. Rizk et al. used a commercial ASK/OOK transceiver at 1 Mbps from RF Monolithics (Dallas, TX) for their 96-ch system [23]. Cheney et al. used a commercial 2.4 GHz FSK transceiver at 1 Mbps from Nordic Semiconductor (Trondheim, Norway) for their 16-ch system [24]. High-data-rate digital systems require frequency-stabilization components, such as crystals and phase locked loops (PLL), to reduce the phase noise and ensure proper synchronization between Tx and Rx, which can increase the size and power consumption of the Tx. Those with lower data rates either have a limited number of channels, low sampling rate per channel (not suitable for single-unit recording), or require an extensive data reduction strategy on the Tx side [25].

Using ultra wideband (UWB) transceivers is quite attractive because of their high data rate, low multipath interference, low-power consumption, and relatively simple circuitry on the Tx side. Chae et al. developed a 128-ch neural-recording system operating over the 3-5 GHz band [17]. They reported a maximum data rate of 90 Mbps; however, neither separation between Tx-Rx nor coverage of the experimental space was reported. Greenwald et al. also developed a 16-ch neural monitoring system with a controllable pulse rate between 90 and 270 MHz [26]. They verified the functionality of the system in vivo. However, a data rate of 1 Mbps was insufficient for neural-recording systems with high channel count. A UWB transceiver is commercially available from Neuralynx (Bozeman, MT) for another 128-ch system, which offers a data rate of 100 Mbps and supports up to 18-bit resolution and 32 kSps for all channels [27]. However, the architecture of the Rx has not been disclosed. Although the UWB offers many advantages, it is prone to interference from other RF sources. In addition, because of the wide spectrum of the device's carrier-less short pulses, a long synchronization time is required to achieve lossless signal acquisition and tracking on the Rx side with complex signal processing methods to recover data in noisy environments [28].

#### 1.2.4. Inductive Powering

A key limitation of common wireless neural recording systems is that the animal subject must carry a large payload of batteries. This requirement may not be an issue in recording from costly primates [3], [29]. However, the majority of laboratories use small animals, such as rats and mice, for which a compromise must be reached between the size and the weight of the headstage and the uninterrupted duration of the experiments. The ability to conduct long-term uninterrupted recording is attractive to neuroscientists because the neural population under analysis frequently changes over time. Therefore, overnight recording is required to track neurons for an extended period of time for learning studies or to combine experimental trials across consecutive days [4].

Cong et al. designed a blood-pressure-monitoring microsystem that was powered by an external RF power source. The received RF power level and blood pressure signals can be sensed and wirelessly transmitted for feedback control of the external RF power [30]. Xiao et al. designed a 20- $\mu$ W neural-recording tag for extremely small implants; the tag can be either remotely powered using a transponder-reader link or operated from a small battery to expand the communication range [31]; however, they did not apply their system to *in vivo* experiments. Sodagar et al. proposed an implantable microsystem that was capable of simultaneously recording neural activity on 64 channels and wirelessly transmitting spike occurrences to an external interface. Although the system is powered and programmed through an inductive RF link, the distance is limited [18].

#### 1.2.5. Recording and Stimulation

Some applications require a system that interacts with the central and peripheral nervous system in a bidirectional manner. For example, DBS which is an effective neuromodulation therapy for Parkinson's disease (PD), requires neural recording for a closed-loop operation. Shahrokhi et al. developed a 128-channel neural recording and stimulation interface [32] that did not operate with a wireless system, featured no stimulus-artifact rejection, and was not used to perform *in vivo* experiments. Lee el al. introduced 64-channel stimulators and an 8-channel neural-recording system [33] with an external wireless micro controller. Azin et al used two identical 4-channel modules in a single SoC [34].

When recording and stimulation are performed simultaneously, a large amount of stimulation current can force the saturation of adjacent recording electrodes and recording amplifiers. Due to the large time constant, the recovery may be time consuming but can prevent immediate neural recording after stimulation, which is referred to as a stimulation artifact [35], [36]. In the case of arrays of chronic microelectrodes, this problem is exacerbated by the close spacing between the electrodes and their mutual

coupling. Although the reduction of artifacts using software is feasible [37], software techniques are not capable of recovering the period during which the amplifiers are saturated, which is frequently longer than 5 ms. Previously reported hardware-based techniques use a low-slew-rate initial amplifier [38] or actively discharge the electrodes immediately after stimulation [39]. These solutions require that electronics be placed on the animal next to the electrodes. To reduce the complexity of hardware-based techniques, Venkatraman et al. used an array of switches between the first and second amplifier stages to disconnect the second stage from the first stage for a short period after the stimulation [40].

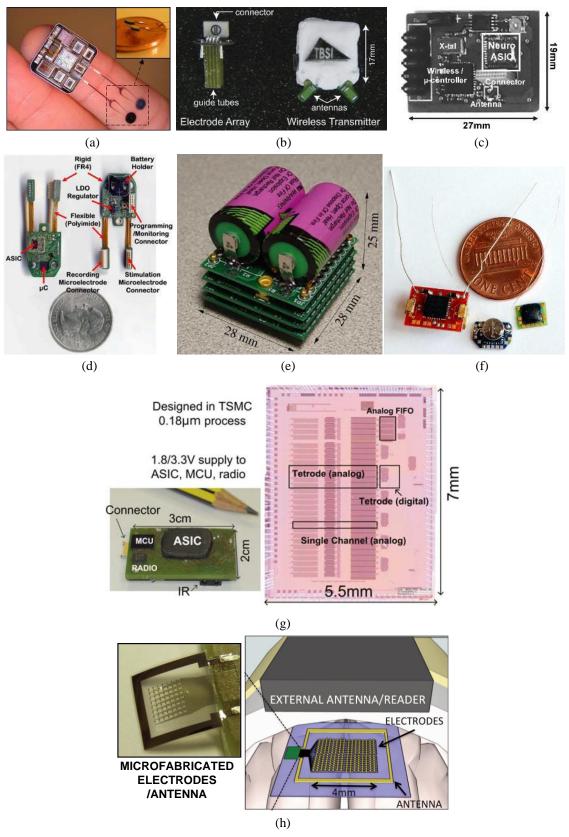

As previously discussed, several issues for wireless neural-recording systems remain unresolved. Important specifications for the state-of-the-art wireless neural recording systems are summarized and compared in Table 1.1. Photographs of recently developed miniaturized wireless neural-recording systems are provided in Fig. 1.2.

| Table 1.1: State-of-the-art wireless heural-recording systems. |                      |                      |                            |                  |                            |                 |                        |                     |

|----------------------------------------------------------------|----------------------|----------------------|----------------------------|------------------|----------------------------|-----------------|------------------------|---------------------|

|                                                                | Sodagar<br>[18]      | Harrison<br>[42]     | Chae<br>[17]               | Miranda<br>[4]   | Azin<br>[41]               | TBSI<br>[21]    | Mitra<br>[43]          | Muller<br>[44]      |

| Year of<br>Publication                                         | 2009                 | 2011                 | 2009                       | 2010             | 2011                       | 2011            | 2013                   | 2014                |

| Total # of<br>Channels                                         | 64                   | 100                  | 128                        | 32               | 8                          | 64              | 24                     | 64                  |

| Simultaneous<br>Channels                                       | 2                    | 1                    | 128                        | 32               | 4                          | 64              | 24                     | 64                  |

| LNA Gain<br>(dB)                                               | 60                   | 60                   | 60                         | 46               | 32                         | 58              | 35.6-75.6              | -                   |

| Power<br>Source                                                | Inductively powered  | Inductively powered  | Battery powered            | Battery powered  | Battery powered            | Battery powered | Battery powered        | Inductively powered |

| Modulation                                                     | OOK                  | FSK                  | UWB                        | FSK              | FSK                        | FM              | -                      | Back-<br>scattery   |

| Data Carrier<br>Frequency                                      | 174 ~ 216<br>MHz     | 915 MHz              | 4 GHz                      | 3.7 ~ 4.1<br>GHz | 433<br>MHz                 | 3.2 GHz         | •                      | N/A                 |

| Power<br>Carrier<br>Frequency                                  | 4 MHz / 8<br>MHz     | 2.765<br>MHz         | N/A                        | N/A              | N/A                        | N/A             | N/A                    | 300 MHz             |

| Data<br>Acquisition                                            | Spike data reduction | Spike data reduction | data<br>reduction<br>/ raw | Raw data         | Spike<br>data<br>reduction | Raw<br>data     | Raw data               | Raw data            |

| Data rate                                                      | 2 Mbps               | 157 kbps             | 90 Mbps                    | 24 Mbps          | 500 kbps                   | 3200<br>kSps    | 1 kSps<br>For LFP      | 1 Mbps              |

| Resolution<br>(bits)                                           | 8                    | 10                   | 9                          | 12               | 10                         | •               | 10                     | 15                  |

| Data link<br>Energy per<br>bit                                 |                      | 3185 pJ/b            | 17.78<br>pJ/b              | 1250<br>pJ/b     |                            |                 |                        |                     |

| Power<br>supply (V)                                            | 1.8                  | 3.3                  | 3.3                        | 5                | 1.5 / 5                    | 2.95            | 1.8/3.3                | •                   |

| Process                                                        | 0.5-μm<br>CMOS       | 0.6-μm<br>BiCMOS     | 0.35-μm<br>CMOS            | Discrete         | 0.35-μm<br>CMOS            | •               | 0.18-μm<br>CMOS        | 65-nm<br>CMOS       |

| Power<br>consumption<br>(mW)                                   | 14.4                 | 8                    | 6                          | 142              | 0.42                       |                 | Activity-<br>dependent | 0.225               |

Table 1.1: State-of-the-art wireless neural-recording systems.

**Fig. 1.1.** State-of-the-art miniaturized wireless neural recording systems (a) [18], (b) [21], (c) [33], (d) [41], (e) [4], (f) [42], (g) [43], (h) [44].

#### **1.3.** Dissertation Outline

The remainder of this dissertation is organized as follows. Chapter 2 presents the preliminary wireless neural recording system WINeR-6, in which neural signals are amplified, filtered, converted to pulse width signals, and transmitted wirelessly through a FSK transmitter. After describing the Tx headstage, the wideband dual-antenna receiver, which demodulates the transmitted neural signals, is described. The results of a biologically meaningful animal experiment are also presented in this chapter. Chapter 3 proposes a dual-slope charge sampling analog front-end, which can simultaneously amplify and filter neural signals and easily modulate them into PWM signals. Chapter 4 describes a WINeR-7 system with a novel dual-slope charge sampling AFE. In this pulse-width-modulation impulse-radio ultra-wideband (PWM-IR-UWB) chapter. communication with a WINeR-7 system is also described for a low-power wireless neural recording system. Chapter 5 presents in vivo animal experiments performed with the WINeR-7 system, which is powered by battery source and near-field wireless power transmission. A robust closed-loop power transmission system based on RF back telemetry was developed for inductively powered freely moving animal experiments. Chapter 6 presents the conclusions of this work and proposes future studies.

#### CHAPTER II

#### WIRELESS NEURAL RECORDING SYSTEM

#### 2.1. WINeR-6 SoC Design

Yin and Ghovanloo presented the WINeR-5 [45], which was a battery-powered 32-channel wireless neural-recording system. The next revision of the SoC, which is called the WINeR-6 was developed. Because the WINeR-6 uses a closed-loop inductive power system, it can simultaneously record from 32 channels for an unlimited period of time without losing any piece of information.

#### 2.1.1. System Architecture

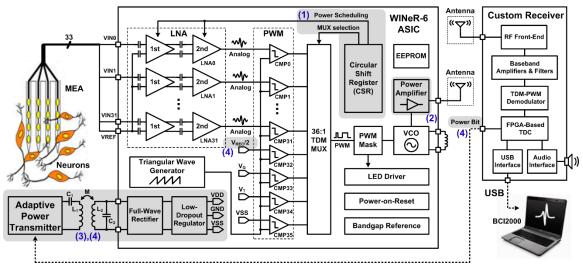

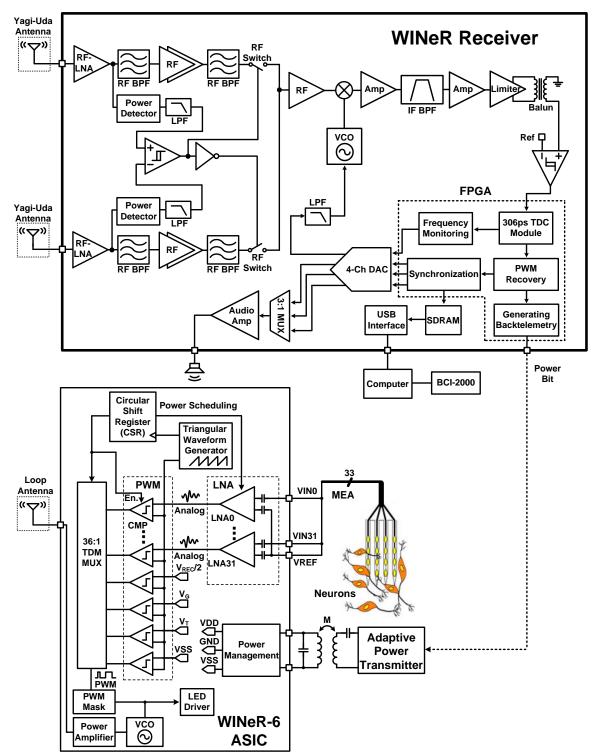

The current WINeR-6 system prototype consists of three key components: (1) a 32-channel transmitter application-specific integrated circuit (ASIC) that is integrated on a chip, (2) a custom-designed wideband receiver unit (Rx), and (3) a wireless power transmitter unit (Reader). The complete WINeR-6 system block diagram is shown in Fig. 2.1. Extracellular neural activity is picked up by a microelectrode array (MEA), which can either be micromachined or operated as an equally spaced bundle of sharpened microwires. An array of two-stage, low-noise amplifiers (LNA) magnifies the neural signals by a gain of up to 8000. An array of high-speed comparators compares the amplified neural signals with a precision triangular waveform to sample and convert the amplitudes of the neural signals to time segments in a step well known as pulse-width modulation (PWM) or analog-to-time conversion (ATC) [46]. The next stage of the WINeR-6 structure involves a time-division multiplexer (TDM), which serializes the PWM samples and combines them with four monitoring signals: half of the rectifier output ( $V_{REC}/2$ ), the bandgap reference voltage ( $V_G$ ), a temperature dependent voltage ( $V_T$ ), and the negative supply rail ( $V_{SS}$ ).

**Fig. 2.1.** WINeR-6 system block diagram with its key new features highlighted: (1) LNA power scheduling, (2) improved RF transmitter, (3) inductive powering, and (4) closed-loop power control.

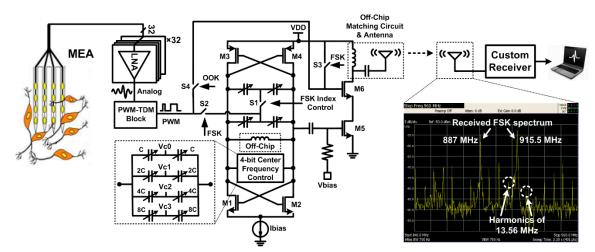

Therefore, every frame of the PWM signal at the output of the TDM block consists of 36 pulses, which pass through a PWM mask to improve their timing accuracy and drive a tunable voltage-controlled oscillator (VCO) that operates at about 915 MHz. The VCO up-converts the baseband PWM-TDM signal by frequency-shift keying (FSK), and finally, the PWM-TDM-FSK signal at the output of the VCO is amplified and transmitted through a miniature wideband monopole antenna.

The WINeR-6 system has four important new features compared to its predecessor (WINeR-5): (1) LNA power scheduling, (2) an improved RF transmitter, (3) inductive powering, and (4) closed-loop power control, which are highlighted in Fig. 2.1 and explained in more detail in the following sections.

The prior experience with the WINeR-5 indicated that although each LNA consumes a small current, because there are 32 of them on-chip, the LNA block quickly becomes one of the major power consumers of the WINeR SoC. To address this issue, a power-scheduling mechanism places most of the LNAs that are not being sampled in sleep mode, which affords very low-power consumption. The power-scheduling mechanism is explained in greater detail in Section 3.1.2.4. In the WINeR-6, a class-AB RF power amplifier (PA) has been added after the VCO to extend the transmission range,

improve the signal to noise ratio (SNR) at the receiver input, and stabilize the operation of the VCO by blocking reflections and back scattering from the antenna. The external adaptive power transmitter, which is shown on the lower left corner of Fig. 2.1, drives a geometrically optimized hexagonal coil that induces power at 13.56 MHz in a receiver LC-tank circuit that is embedded in the animal headstage [47]. The induced power is sent to an on-chip active full-wave rectifier that is followed by a low-dropout regulator. Because of the closed-loop power control mechanism, the WINeR-6 is expected to maintain the power delivered to the headstage at a constant level even when the distance or alignment between the transmitter and receiver coils changes due to animal movements [30], [48].

#### **2.1.2.** Neural Signal Flow

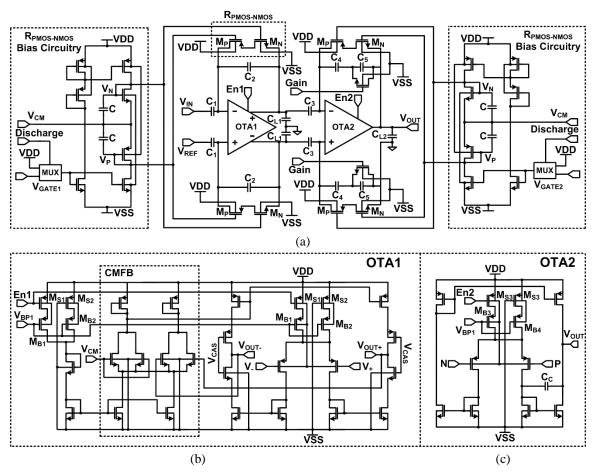

#### 2.1.2.1. Low-noise amplifiers (LNA)

The WINeR-6 analog front-end has been designed using two-stage capacitively coupled LNAs with built-in tunable band-pass filtering. A schematic diagram of the LNA is shown in Fig. 2.2. The first stage of the LNA is a fully differential operational transconductance amplifier (OTA1), shown in Fig. 2.2a and Fig. 2.2b, with a midlands gain of  $C_1/C_2 = 100$ .  $V_{CM}$  is the common mode voltage, which is usually grounded, and  $V_{REF}$  is the reference voltage from the animal reference electrode. Turning OTA1 completely off when it is not in use to reduce power consumption results in a long transient to allow charge to build up in its capacitors before it resumes normal operation. To reduce this transient time, the OTA1 bandwidth is changed from its nominal value of 10 kHz when the current consumption is 16  $\mu$ A (En1 = VSS) and the LNA is in the active mode to 200 Hz when the current consumption is ~0.5  $\mu$ A (En1 = VDD) and the LNA is in sleep mode. The second stage of the LNA (OTA2), shown in Fig. 2.2c, has an adjustable gain of either  $C_3/C_4 = 20$  or  $C_3(C_4 + C_5)/(C_4C_5) = 80$  for a total LNA gain of

2000 or 8000 (66/78 dB). The current in OTA2 also changes from 8.6  $\mu$ A to 2.8  $\mu$ A when the LNA is switched from active to sleep mode and vice versa (controlled by En2).

Fig. 2.2. Schematic diagram of the WINeR-6 analog front-end: (a) two stage LNA, (b) OTA1, and (c) OTA2.

To achieve high resistance(>10<sup>11</sup>  $\Omega$ ) and ultra low cutoff frequencies, both stages of the LNA in Fig. 2.2a are equipped with voltage-controlled PMOS-NMOS pseudo resistors,  $R_{PMOS-NMOS}$ , to create a low-cutoff frequency that can be continuously tuned by  $V_{GATE1}$  and  $V_{GATE2}$ , as presented in [45].  $R_{PMOS-NMOS}$  transistors are biased with a floating bias circuitry such that they can operate as a bidirectional current source. Hence, the impedance seen from either end of the  $R_{PMOS-NMOS}$  remains constant and almost independent of the OTA input and output voltages, causing less distortion.

#### 2.1.2.2. Pulse-width modulator and 36:1 time-division multiplexer

As shown in Fig. 2.1, conditioned neural signals at the 32 LNA outputs join four monitoring signals,  $V_{REC}/2$ ,  $V_{BG}$ ,  $V_T$ , and  $V_{SS}$ , at the input of the PWM-TDM block. These 36 analog signals are fed into the PWM block, which consists of 36 rail-to-rail highspeed comparators, enabled one at a time over one sampling period to convert the analog signals from each channel into a sequence of pulses by comparing them with a precision triangular waveform (TW). To reduce noise and dynamic power dissipation, WINeR-6 does not use any high-frequency clock signal. Instead it uses a low-frequency clock at the sampling rate for TDM, which is generated locally by the triangular waveform generator (TWG) block. As a result during each comparison, the substrate is completely quiet, and there is no digital transition anywhere on the chip. Monitoring signals also play a secondary role by providing a unique pattern that is used for synchronization between the WINeR-6 transmitter and external receiver by marking the beginning of each TDM-PWM 36-pulse frame to be easily detected on the receiver side.

The TDM block consists of a 36-bit circular-shift register (CSR) and a 36:1 multiplexer (MUX) as shown in Fig. 2.3a. The CSR receives a buffered time-base signal at the sampling rate from the TWG block, shown in Fig. 2.3b, for its clock. At the global reset, the CSR is loaded with a 36-bit binary code, "1...10...00", in which the number of "1s" is programmable (*N*). When the system is running, the string of "1s" circulates in the CSR and connects one out of 36 comparator PWM pulses (the last "1") to the MUX output. The resulting signal will be a 36-pulse TDM-PWM frame, which is buffered and trimmed before being fed into the VCO.

**Fig. 2.3.** (a) Block diagram and timing diagram of the power scheduling mechanism. The OTAs in the LNA block are switched between active (BW = 10 kHz) and sleep (BW = 200 Hz) modes by changing their bias currents, (b) schematic diagram of triangular waveform generator (TWG) block.

#### 2.1.2.3. Triangular waveform generator (TWG)

A precision TWG, shown in Fig. 2.3b, is a key building block in accurate amplitude-to-time conversion (ATC). Its performance affects the noise, accuracy, and resolution of the system, as described in [46]. A TWG features binary weighting (DP<sub>0-3</sub> and DN<sub>0-3</sub>), high voltage compliance (-1.4 ~ 1.4 V), large output impedance, and a complementary current source/sink (CCSS) pair, which linearly charges/discharges  $C_S$  (6 pF) to generate the triangular wave [45], [49]. Unlike common designs that require at least two comparators, the new TWG design utilizes only one comparator to reduce power consumption and the negative effects of offset mismatch.  $V_{Source}$  and  $V_{Sink}$  are dynamic, current-limited, bias generator blocks. They provide fast switching waveforms at specific DC biasing nodes to turn the CCSS on and off, while consuming negligible static power.

#### 2.1.2.4. Power scheduling

Although each individual LNA consumes only ~25  $\mu$ A, the 32-channel LNA block is responsible for 42% of the total WINeR-6 power consumption when all channels are active. Unfortunately, this situation is only exacerbated when the number of channels is increased. On the other hand, the TDM-PWM block, only samples one LNA at a time. To address this issue, a power-scheduling mechanism has been employed, depicted in Fig. 2.3b, which places most of the LNAs that are not being sampled in the sleep mode, reducing their power consumption by 86% to ~3.5  $\mu$ A.

The LNAs are not completely turned off to reduce the transient time,  $t_T$ , for a dormant LNA to reach its active state well ahead of the sampling time and thereby be able to track neural signals with high bandwidth and low distortion (10 kHz). Because  $t_T$  cannot be reduced to zero, the number of LNAs that should be activated ahead of sampling, N, depends on the overall sampling rate,  $f_S$ , which in turn depends on the desired neural signal bandwidth, i.e.)  $N > f_S t_T$ . In the power-scheduling schematic, N is programmable by SR0:2, which can change the number of consecutive "1s" in the CSR from 4 to 32. For example, when N = 12, twelve consecutive "1s"circulate in the CSR and each LNA is switched to the active mode 11 times during the sampling period,  $11/f_s$ , before being sampled. In this case, the LNAs remain in the sleep mode during the rest of the sampling periods ( $24/f_s$ ) and reduce the power consumption of the LNA block by 51%.

#### 2.1.2.5. Voltage-controlled oscillator and power amplifier

The WINeR-6 RF transmitter consists of a VCO with an off-chip inductor followed by a PA, as shown in Fig. 2.4. As a result of changes in the antenna loading and reflected RF signal, animal movements in the shielded Faraday cage result in undesired VCO frequency shifts in WINeR-5. To prevent the undesired VCO frequency shifts, a nonlinear class-AB PA is used not only to reduce the frequency shift problem but also to facilitate transmitter output matching with miniature 50  $\Omega$  antennas and extend the transmission range. A complementary negative-Gm structure is used for the VCO core because of its low power and superior phase-noise performance [50]. Coarse and fine VCO tunings are performed using an off-chip inductor and a 4-bit on-chip varactor bank (VC0:3), respectively. VCO varactors are PMOS transistors whose gates are connected to the VCO outputs, bulks are tied to  $V_{DD}$ , and sources and drains are tied together and connected to either the varactor bank control signals (VC0:3) for center frequency tuning or TDM-PWM signal to generate the FSK signal. To finely tune the transmitter frequency, VC0:3 is accessible to the user. Once the VCO frequency is adjusted to the desired band, the external receiver can be tuned to the transmitter frequency.

Fig. 2.4. WINeR-6 neural signal flow diagram with emphasis on the transmitter SoC.

#### 2.1.3. Simulation and Measurement Results

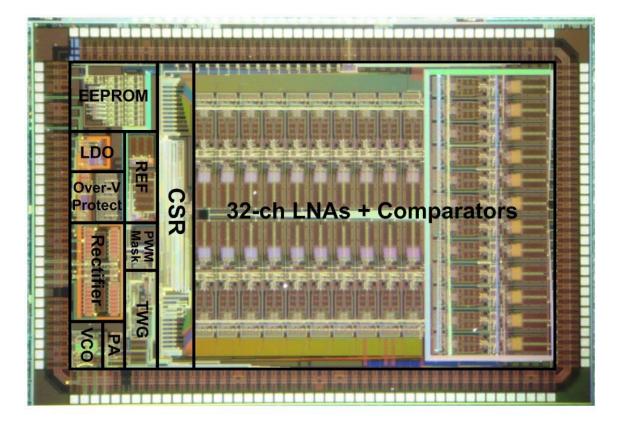

The WINeR-6 SoC was fabricated using the ON Semiconductor 0.5- $\mu$ m 3-metal 2-poly standard CMOS process. A micrograph and floorplan of the chip, which occupies  $4.9 \times 3.3 \text{ mm}^2$  of silicon area including the padframe, are shown in Fig. 2.5.

**Fig. 2.5.** Die photomicrograph of the 32-ch WINeR-6 SoC fabricated using the ON semiconductor 0.5- $\mu$ m 3M2P std. CMOS process (size: 4.9 × 3.3 mm<sup>2</sup>).

### 2.1.3.1. <u>Power-scheduling measurements</u>

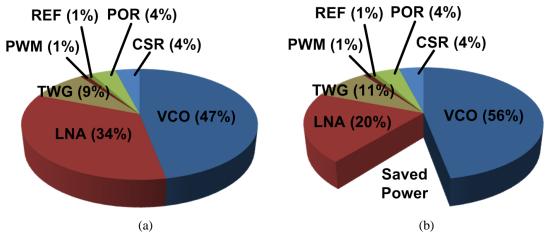

The power consumption of the WINeR-6 with and without power scheduling are compared in Fig. 2.6. When all LNAs are active, the WINeR-6 consumes 7.05 mW from  $\pm 1.5$  V supplies. On the other hand, when 12 LNAs (N = 12) are on at a time and the other 20 are in the sleep mode under power scheduling, the power consumption drops by 17% to 5.85 mW. From a different perspective, as depicted in Fig. 2.6, with power scheduling, the share of the LNA block power consumption in the total power consumption decreases from 34% to 20%. Obviously this power saving become even more significant by decreasing *N*. However, if  $N < f_S t_T$ , the LNA outputs will be sampled before they reach their operational values, which may cause distortion.

**Fig. 2.6.** Comparison between the power consumption of each block in the WINeR-6 SoC as the percentage of the total power with and without power scheduling, which results in a 17% reduction in the total power consumption: (a) without power scheduling 7.05 mW and (b) with power scheduling 5.85 mW.

To evaluate the effect of power scheduling on the quality of the recorded signals, artificial spikes were applied with a 0.5 mV amplitude and 1 ms pulse width to the LNAs inputs and compared the recorded signals with and without power scheduling. The measured waveforms are shown in Fig. 2.7, in which the sampling rate is set to 18 kSps per channel and N = 12. The upper two waveforms show the LNA inputs. In the 3<sup>rd</sup> row, the black trace shows the output signal without using power scheduling, and the blue trace shows the output signal with power scheduling. Even though the LNA output seems to be noisy with power scheduling, because the LNA output reaches its operational value by the time each sample is taken, the effect of this noise on the digitized signal will be negligible. The last row shows the reconstructed signals from the digitized samples. The correlation coefficient between the two reconstructed signals was measured to be 0.97, which demonstrates almost a perfect match between the two conditions.

**Fig. 2.7.** Measured waveforms from top: original artificial spike waveform, magnified spike waveform, waveforms recorded at the LNA output with (blue) and without (black) power scheduling, reconstructed signal in the PC.

## 2.2. Receiver and Computer Interface

# 2.2.1. Rx Design

Resolution of the TDM-PWM based WINeR-6 system is determined by the accuracy of the recovered pulse width. Higher Rx bandwidth corresponds with sharper pulse edges and lower pulse width error [46]. Thus, the WINeR-6 Rx needs high enough bandwidth to receive the FSK-TDM-PWM signal while providing an adequate resolution

of more than 8 bits. Most commercially available ISM-band FSK receivers only provide up to 600 kHz bandwidth [51], which is far below what is required for a neural recording system with data volume in the order of 10 Mbps. Hence, a custom-designed Rx with 18 MHz bandwidth using commercially available off-the-shelf (COTS) components was implemented.

The WINeR-6 Rx block diagram, shown in Fig. 2.8, has four major modules in addition to the antennas: RF front end, analog signal conditioning, FPGA including USB 2.0 interface, and digital- to-analog converter (DAC).

**Fig. 2.8.** Block diagram of the entire wireless implantable neural recording (WINeR-6) system: Rx (top) and Tx (bottom).

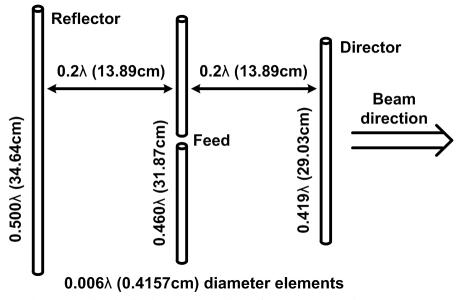

### 2.2.1.1. Yagi-Uda antenna

Like other implantable medical devices (IMD), WINeR-6 Tx has a limited power budget for RF transmission to keep its overall power consumption down. At the same time, it was desired to provide coverage over large experimental arenas in the order of 2  $\times$  2 m<sup>2</sup> without any blind spots. This specification required high Rx front-end sensitivity and high-gain Rx antennas. A Yagi-Uda antenna satisfies these requirements while offering wide bandwidth. Relatively high directivity of the Yagi-Uda antenna was mitigated by the inclusion of two antennas in each WINeR-6 Rx. A 3-element Yagi-Uda antenna was designed based on [52], as shown in Fig. 2.9.

Fig. 2.9. Three-element Yagi-Uda dipole antenna designed for 433 MHz carrier.

### 2.2.1.2. <u>RF front-end</u>

In order to increase the wireless coverage of the experimental arena and eliminate blind spots, the Rx was equipped with two identical RF front-ends, each with its own antenna. As shown in Fig. 2.8, the FSK-TDM-PWM signal from the Tx was picked up by each antenna, and amplified/filtered independently through its parallel RF front-end. Each path has an RF power detector (ADL5513), and depending on the strength of the received RF signal from each path, an RF switch connects the stronger one to the mixer. Depending on the size of the experimental arena, the wireless coverage can potentially be extended even further by increasing the number of antennas and parallel RF front-end paths.

Each RF front-end consists of an RF-LNA (MAX2640) with a gain and noise figure of 15.1 dB and 0.7 dB at 400 MHz, respectively, followed by a gain stage (BGA2712) that provides an additional 24 dB amplification. The RF front-end can provide up to 1.5 GHz bandwidth, while two passive third-order Chebyshev band-pass filters with 403-490 MHz bandwidth are placed before and after the gain stage to provide selectivity around the Tx signal and limit the out-of-band noise. The RF front-end thus provides 45 dB gain and 87 MHz bandwidth.

### 2.2.1.3. Analog signal conditioning

The amplified and filtered FSK signal is fed into a mixer, which is a 50 MHz to 1 GHz quadrature demodulator with 75 MHz bandwidth (AD8348). The mixer has a builtin variable gain amplifier (VGA) that provides –18.5 to +25.5 dB programmable gain. The VGA output drives two (I and Q) double-balanced Gilbert cell down-conversion mixers, which down-convert the RF signal to 43.5/56.5 MHz IF band. The IF-TDM-PWM signal is then further filtered and amplified in the baseband. To create a tunable local oscillator (LO) for the down-converter, a 720-1750 MHz VCO (V585ME41-LF) from Z-Comm (San Diego, CA) has been utilized. The LO frequency is divided by two inside the mixer, resulting in its ability to receive RF frequencies in 360-875 MHz range.

IF amplifiers and filters improve the SNR by eliminating the out-of-band interference. AD4899-1 amplifier was chosen for this block because of its 300 MHz unity gain bandwidth, ultra low distortion, and low noise. Three instances of this amplifier have been implemented with a total IF gain of 46 dB. In order to reject all adjacent channels'

interference, a band-pass filter (KR2850) from KR Electronics (Avenel, NJ, USA) has been included between the second and the third amplifiers. The filter has an 18 MHz bandwidth from 41-59 MHz and a 1 dB pass-band ripple.

The amplified and filtered IF-FSK signal is fed into a logarithmic limiting IF amplifier (AD8309) and a high speed comparator (TLV3501) with 4.5 ns delay. This stage recovers the rail-to-rail baseband FSK-TDM-PWM signal, which is then fed into an FPGA to be FM-demodulated in the digital domain to recover the TDM-PWM signal.

#### 2.2.1.4. FPGA module

A COTS FPGA module, called Xylo-EM [53], was used, which includes an Altera FPGA (EP2C5T144C8), 2 MB of synchronous dynamic random access memory (SDRAM) for data buffering, and the USB interface circuitry.

#### 2.2.1.4.1. FSK demodulation via TDC