## **Storage Management for Embedded SIMD Processors**

A Dissertation Presented to The Academic Faculty

> by Soojung Ryu

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology December 2003

Copyright © 2003 by Soojung Ryu

## **Storage Management for Embedded SIMD Processors**

Approved:

Dr. D. Scott Wills, Chair

Dr. Linda M. Wills, Chair

Dr. Douglas M. Blough

Dr. Sudhakar Yalamanchili

Date Approved December 15, 2003

## Dedication

This work is dedicated to

my husband, Ji-Weon Jeong for his love and patience my son, Daniel for his future my parents, Keun-Jang Ryu and Sun-Sook Park for their love my father-in-law, Han-Young Jeong for his love my sister and brother, Hye-Jung and Jae-woan for their love and my friends for their love

### Acknowledgments

I would like to express my deepest appreciation to my thesis advisor, Dr. Scott Wills and my co-advisor, Dr. Linda Wills. They have contributed the most to my research. During my Ph.D. program at Georgia Institute of Technology, they provided me advice on everything – research, family, and life. Their encouragement made me continue to pursue my Ph. D. I really appreciate their love and also I would like to express my sincere love for them and their lovely children, Rosemary and Frank.

I am also grateful to Dr. Sudhakar Yalamanchili for serving as a thesis reading committee member. I would like to thank Dr. Douglas Blough for his encouragement for my research as well as careful reading of this dissertation. I would like to thank Dr. Bonnie Heck and Dr. Ellen Zegura for serving as committee of my dissertation defense.

I would like to acknowledge all of the members of the PICA group and EASL group at Georgia Institute of Technology for their friendship and useful comments – Mark, Keh, Jong-Myun, Lewis, Hong-Kyu, Jin-Sung, Cameron, Chris, Brett, Cory, Krit, Murat, Roy, Nidhi and Peter. Many thanks are given to Dr. Mondira Deb Pant for her support and friendship. I also would like to thank Dr. Kee-Shik Chung for his valuable advice on my Ph.D. research.

I'd like to also thank to my friends, Chung-Seok Seo, Jiwon Park, Joanne Kim, Seungmin Lee, Hyun-Ah Kim, Hasup Lee, So-Young You, Hyung-Su Lee, Jeongseok Ha, Jungwon Kang, and Jaehong Kim. I would like to give my special appreciation to Ji-Eun Park's family for their love and friendship.

Last, I'd like to express my deepest appreciation to my parents, family, husband, and my son who have continued to support me with love to finish this thesis.

## **Table of Contents**

| Dedication                                                                                                                                                                                                                                                                                                                                                                                   | iii                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Acknowledgments                                                                                                                                                                                                                                                                                                                                                                              | iv                                                   |

| Table of Contents                                                                                                                                                                                                                                                                                                                                                                            | v                                                    |

| List of Tables                                                                                                                                                                                                                                                                                                                                                                               | viii                                                 |

| List of Figures                                                                                                                                                                                                                                                                                                                                                                              | ix                                                   |

| Summary                                                                                                                                                                                                                                                                                                                                                                                      | xiii                                                 |

| CHAPTER 1 Introduction<br>1.1. Introduction<br>1.2. Problem Statement and Contributions<br>1.3. Related Research<br>1.3.1. SIMD Instruction Broadcast<br>1.3.2. Systolic Arrays<br>1.3.3. Instruction Systolic Architecture (ISA)<br>1.3.4. Compilation Techniques for Storage Optimization<br>1.3.5. Summary of Related Research<br>1.4. Thesis Contribution Summary<br>1.5. Thesis Outline | 1<br>3<br>3<br>3<br>                                 |

| <ul> <li>CHAPTER 2 Efficient Storage Usage in Embedded SIMD Systems</li></ul>                                                                                                                                                                                                                                                                                                                | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| CHAPTER 3 Systolic Instruction Broadcast for Embedded SIMD Architectures                                                                                                                                                                                                                                                                                                                     | 37                                                   |

| 3.1. Summary.     |                                                                      | 3            |

|-------------------|----------------------------------------------------------------------|--------------|

|                   | on                                                                   |              |

|                   | 'ork                                                                 |              |

| 3.3.1. Pipel      | ined Instruction Broadcast                                           | 3            |

| 3.3.2. Instru     | action Systolic Architecture (ISA)                                   | 4            |

|                   | lic Instruction Broadcast                                            |              |

|                   | Systolic Instruction Broadcast Architecture                          |              |

|                   | and Structural Hazards                                               |              |

|                   | Nearest Neighbor Communication                                       |              |

|                   | Data and Structural Hazard Analyses                                  |              |

|                   | ementation of Systolic Instruction Broadcast                         |              |

|                   | Software Approach                                                    |              |

|                   | Two Write-port Register File Method                                  |              |

|                   | Instruction Scheduling Techniques for Systolic Instruction Broadcast |              |

|                   | Hardware Approach                                                    |              |

| 3.5. Results an   | d Analysis                                                           | 5            |

|                   | ics                                                                  |              |

|                   | Pil Applications                                                     |              |

|                   | c Count Penalty                                                      |              |

|                   | m Performance                                                        |              |

|                   | ware Overhead                                                        |              |

|                   | Efficiency                                                           |              |

|                   | onclusion                                                            |              |

| 4.2. Introduction | Dn                                                                   | <del>(</del> |

|                   | ork                                                                  |              |

|                   | ar Mapping Technique                                                 |              |

|                   | Prefetching Technique                                                |              |

|                   | SIMD-systolic System with Systolic Virtual Memory                    |              |

|                   | matic Design Approach                                                |              |

|                   | Study of Extended Mapping Techniques: Vector Quantization            |              |

|                   | ory Operations in SIMPil Architecture                                |              |

|                   | lic Virtual Memory (SVM): SIMD-systolic System with Off-Chip Mem     |              |

|                   | Syntalia L and                                                       |              |

|                   | Systolic Load                                                        |              |

|                   | Systolic Store                                                       |              |

|                   | Prefetch                                                             |              |

|                   | Prefetch Instruction                                                 |              |

|                   | action Scheduling                                                    |              |

|                   | d Analysis                                                           |              |

|                   | nel Utilization                                                      |              |

|                   | m Performance                                                        |              |

| •                 | c Count Penalty                                                      |              |

|                   | ication: Matrix Multiplication                                       |              |

|                   | Matrix Multiplication: Execution Time                                |              |

|                   | Memory Requirement                                                   |              |

|                   | Memory Area Efficiency                                               |              |

|                   | onclusion                                                            |              |

| 1.0. Chapter C    | V11V1WU1V11                                                          | 11           |

| CHAPTER 5 Concluding Remarks<br>5.1. Conclusions | 104 |

|--------------------------------------------------|-----|

| 5.2. Future Work                                 |     |

| APPENDIX A SIMPil Architecture                   |     |

| Vita                                             |     |

| Vita                                             | 113 |

## List of Tables

| Table 1: High-level comparisons between Systola and SIMD-systolic system                     | 6  |

|----------------------------------------------------------------------------------------------|----|

| Table 2: Low-level comparisons between Systola and SIMD-systolic system                      | 6  |

| Table 3: Metrics for experiments.                                                            | 26 |

| Table 4: Description of selected workloads                                                   | 30 |

| Table 5: Explored storage configurations.*                                                   | 30 |

| Table 6: Storage area efficiency (x 10 <sup>-6</sup> ).                                      | 31 |

| Table 7: Area efficiency (x 10 <sup>-6</sup> ).                                              | 31 |

| Table 8: Energy efficiency (x 10 <sup>-6</sup> ).                                            | 31 |

| Table 9: Metrics for experiments.                                                            | 57 |

| Table 10: Number of instructions issued by controller                                        | 59 |

| Table 11: Clock count penalties (delay cycles) of SIMD-systolic systems in three approaches. | 59 |

| Table 12: Definitions for linear mapping method                                              | 69 |

| Table 13: Transformation table for each edge.                                                | 77 |

| Table 14: Memory addressing modes for each type of memory operation                          | 79 |

| Table 15: Distances between consecutive off-chip memory operations.                          | 92 |

| Table 16: Metrics for experiments.                                                           | 92 |

# List of Figures

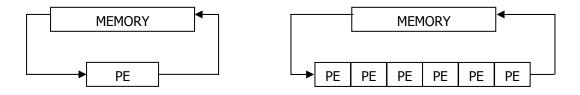

| Figure 1: The principles of memory interfaces for (a) conventional processor and (b) systolic array [12]                                                                                                                    | 3  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

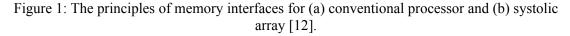

| Figure 2: Relations among related research and our approaches in three contributions                                                                                                                                        | 9  |

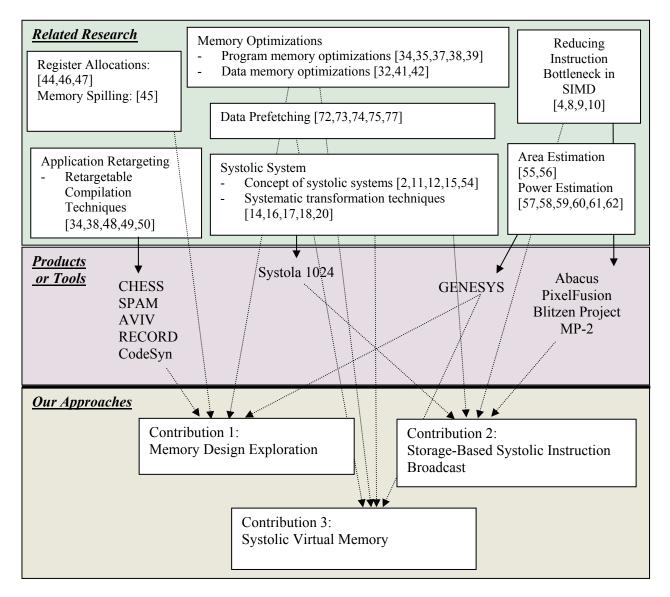

| Figure 3: Chatin's register allocator [45]                                                                                                                                                                                  | 15 |

| Figure 4: Brigg's register allocator [46,47]                                                                                                                                                                                | 15 |

| Figure 5: Overall framework for finding optimal storage configurations by application retargeting.                                                                                                                          | 17 |

| Figure 6: Application retargeting module with register reassignment                                                                                                                                                         | 18 |

| Figure 7: Example of register reassignment.                                                                                                                                                                                 | 20 |

| Figure 8: Application retargeting module with memory optimization.                                                                                                                                                          | 21 |

| Figure 9: Example of memory optimization based on the lifetimes.                                                                                                                                                            | 22 |

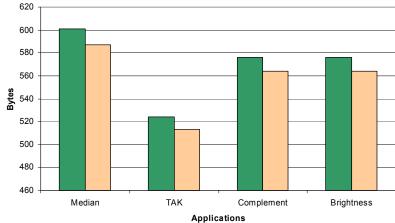

| Figure 10: Results of memory optimization: memory words in byte used in the original progra<br>and in the optimized program for median filtering, TAK, complement, and brightness slicing<br>image processing applications. |    |

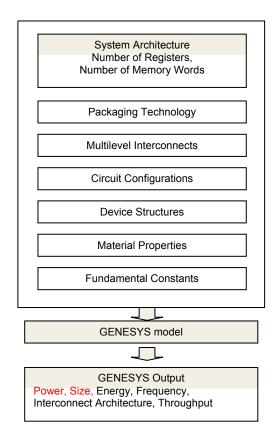

| Figure 11: GENESYS structure [63].                                                                                                                                                                                          | 25 |

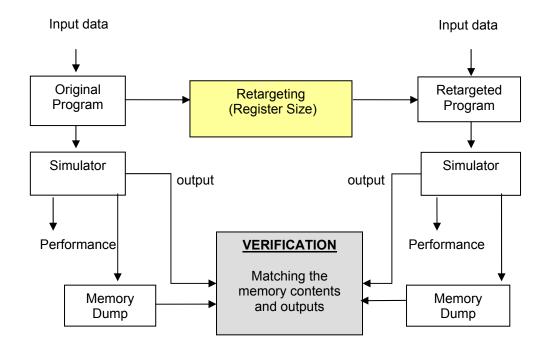

| Figure 12: Verification steps                                                                                                                                                                                               | 26 |

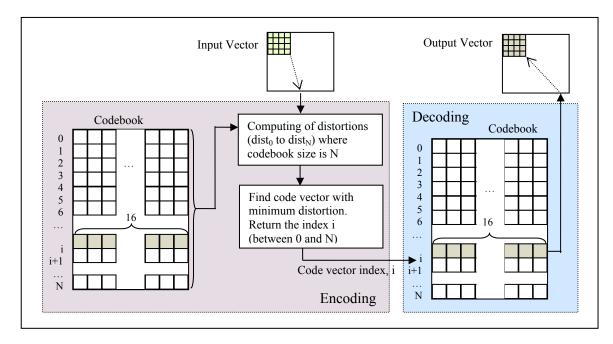

| Figure 13: Overall VQ processes.                                                                                                                                                                                            | 29 |

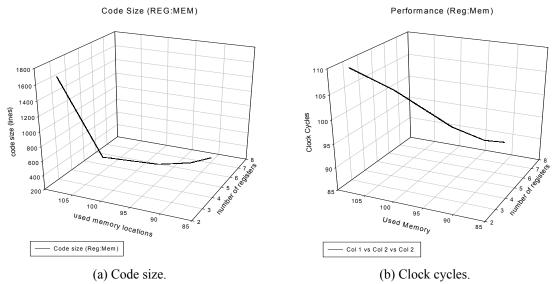

| Figure 14: Results of code sizes and execution time in clock cycles for retargeting VQ applica to different storage configurations.                                                                                         |    |

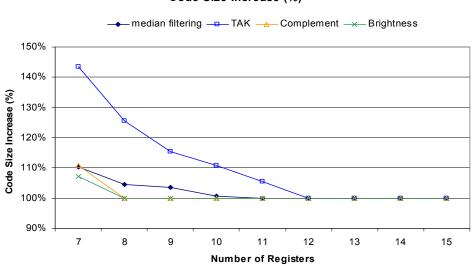

| Figure 15: Code size increase.                                                                                                                                                                                              | 32 |

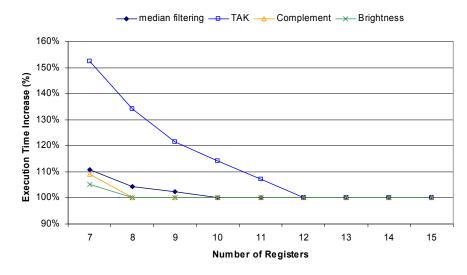

| Figure 16: Execution time increase                                                                                                                                                                                          | 33 |

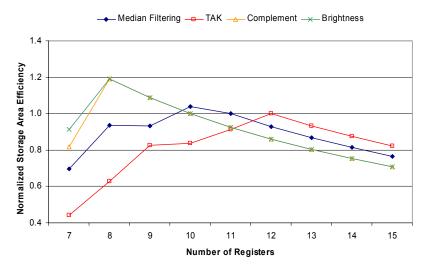

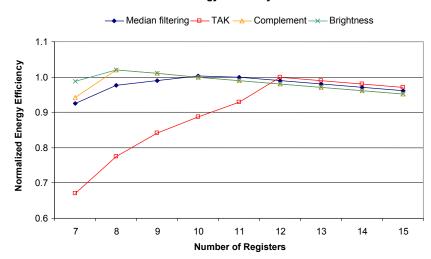

| Figure 17: Normalized storage area efficiency for selected workloads                                                                                                                                                        | 33 |

| Figure 18: Normalized energy efficiency.                                                                                                                                                                                    | 34 |

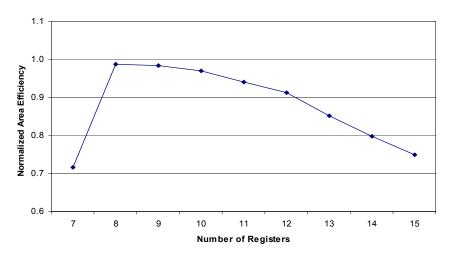

| Figure 19: Average of normalized storage area efficiency.                                                                                                                                                                   | 35 |

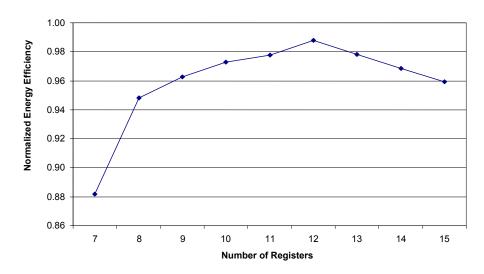

| Figure 20: Average of normalized energy efficiency.                                                                                                                                                                         | 35 |

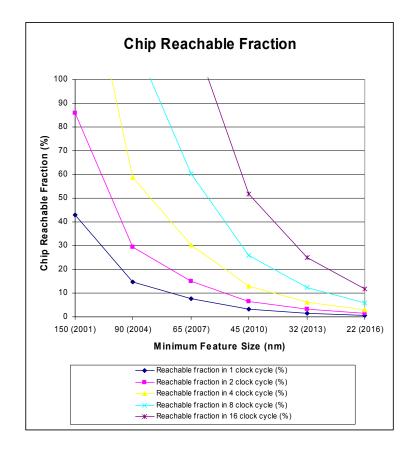

| Figure 21: Reachable fraction of a chip for future VLSI technology (from ITRS).                                                                                                 | 38 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

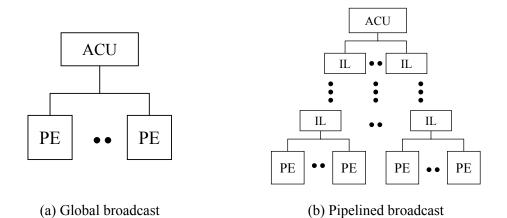

| Figure 22: Two methods for delivering instructions to PEs [4]                                                                                                                   | 39 |

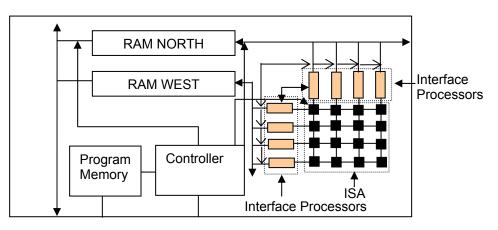

| Figure 23: The architecture of Systola 1024 [30].                                                                                                                               | 40 |

| Figure 24: Control flow in an instruction systolic array [30]                                                                                                                   | 41 |

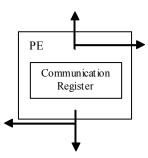

| Figure 25: The structure of the dedicated communication register in Systola 1024 [30]                                                                                           | 41 |

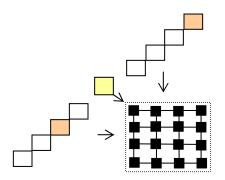

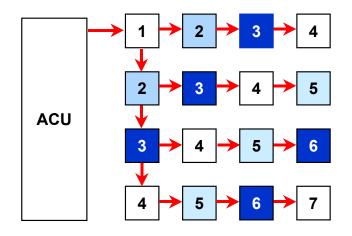

| Figure 26: A 4x4 mesh of PEs showing how instructions are pumped from an ACU to PEs [1]                                                                                         | 42 |

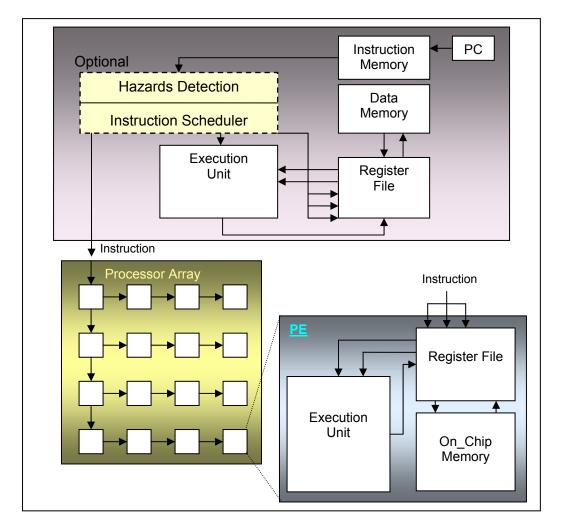

| Figure 27: The overall framework of the SIMD-systolic architecture                                                                                                              | 43 |

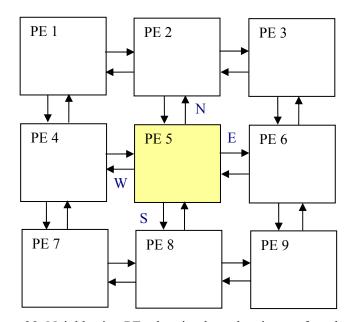

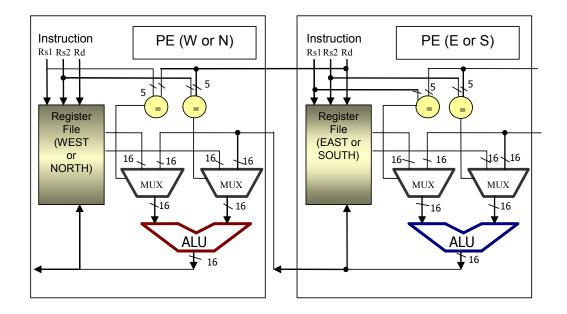

| Figure 28: Neighboring PEs showing how data is transferred                                                                                                                      | 44 |

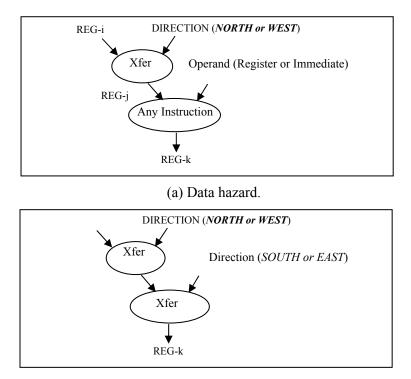

| Figure 29: Conditions causing delays in systolic instruction broadcast.                                                                                                         | 45 |

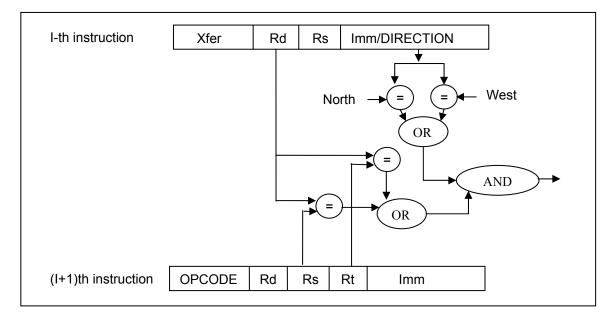

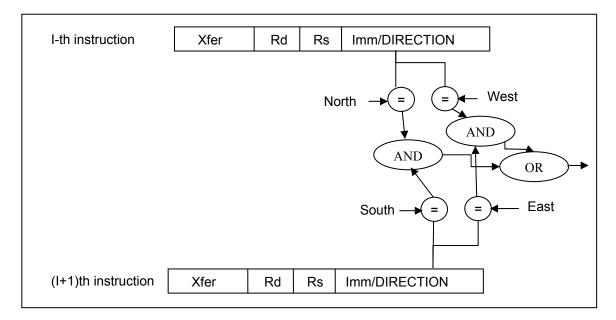

| Figure 30: Hazard detection logic                                                                                                                                               | 46 |

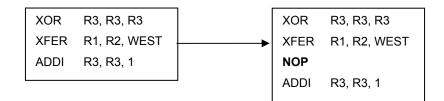

| Figure 31: Sample code that introduces a delay due to a write following a communication instruction.                                                                            | 47 |

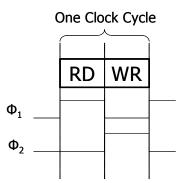

| Figure 32: Clock cycle splitting – RD for a data read from register file and WR for a data writ register file.                                                                  |    |

| Figure 33: An example of an execution of a communication instruction with split clock cycle                                                                                     | 48 |

| Figure 34: Sample codes that eliminate a delay due to a following write after communication instruction by having two write register ports.                                     | 48 |

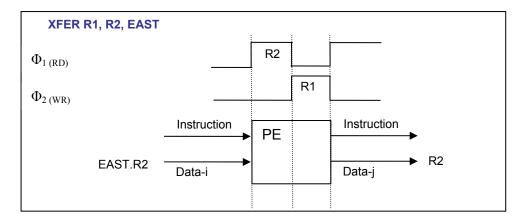

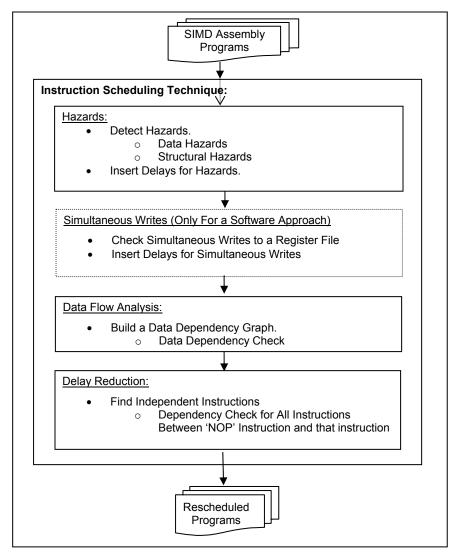

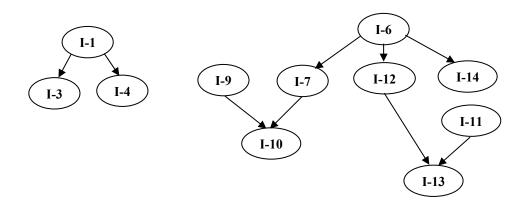

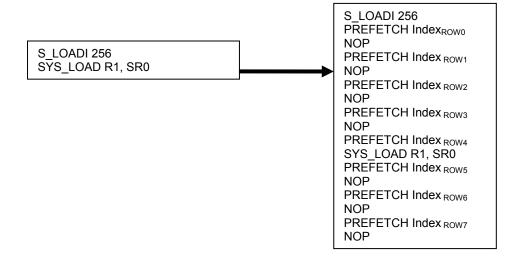

| Figure 35: Framework of an instruction scheduler for systolic instruction broadcast                                                                                             | 50 |

| Figure 36: An example of instruction scheduling technique for software approach.                                                                                                | 53 |

| Figure 37: An example of instruction scheduling technique for two write-port register file approach.                                                                            | 55 |

| Figure 38: Bypass logic.                                                                                                                                                        | 56 |

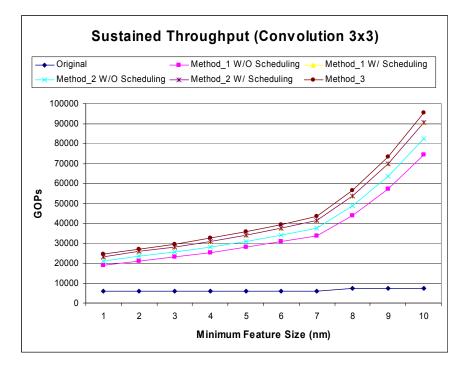

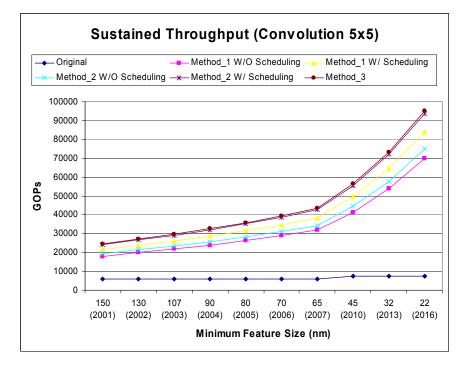

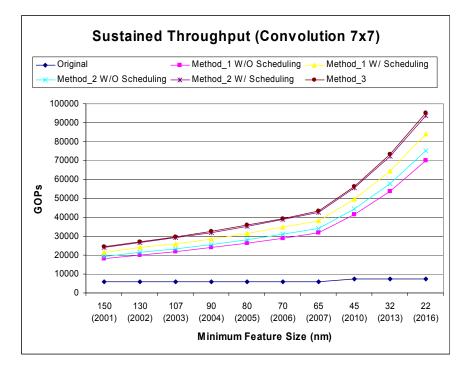

| Figure 39: Projected system performance in sustained system throughput.                                                                                                         | 62 |

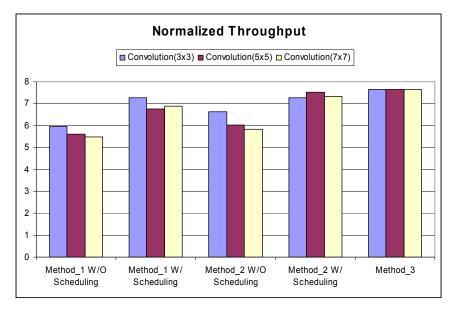

| Figure 40: Normalized sustained throughput                                                                                                                                      | 62 |

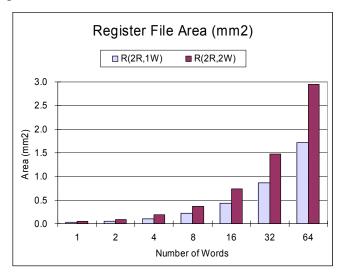

| Figure 41: Register file size increase for an additional write port: $R(2R,1W) - 2$ read-port, 1 write-port register file; $R(2R,2W) - 2$ read-port, 2 write-port register file | 63 |

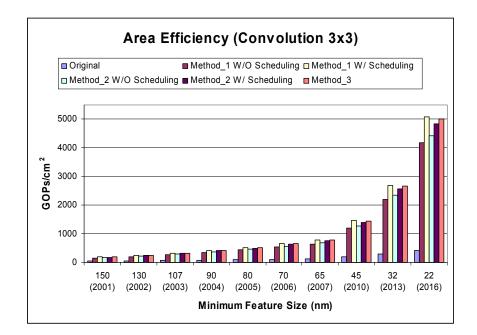

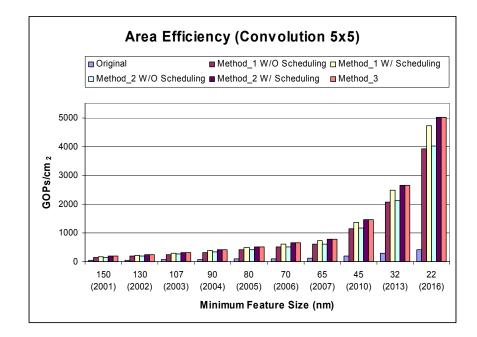

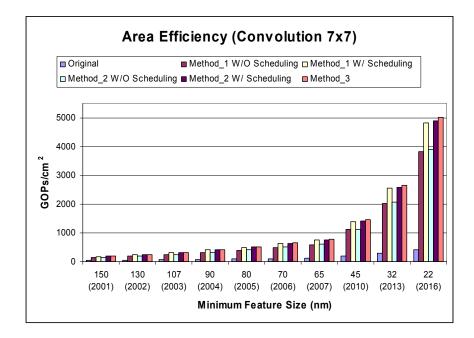

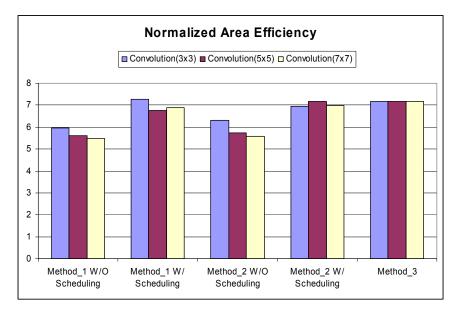

| Figure 42: Area efficiencies in (GOP/mm <sup>2</sup> ).                                                                                                                         | 65 |

| Figure 43: Normalized area efficiency projected in year 2010                                                                                                                    | 66 |

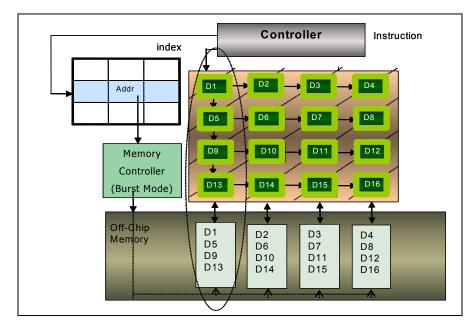

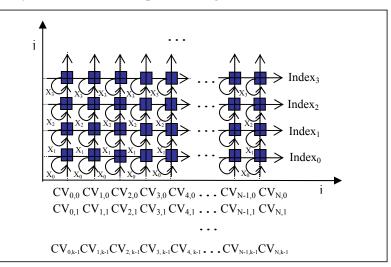

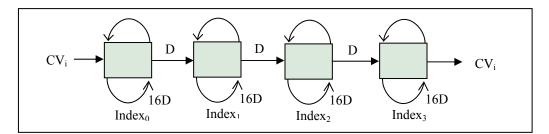

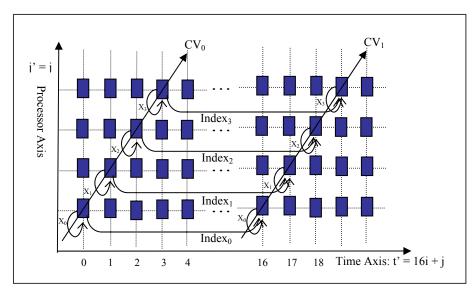

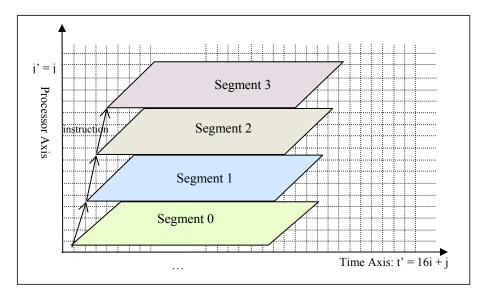

| Figure 44: Mechanism of systolic instruction broadcast and systolic data movement.                                                                                              | 69 |

| Figure 45: An example of data movement with systolic load instruction                                   | . 70 |

|---------------------------------------------------------------------------------------------------------|------|

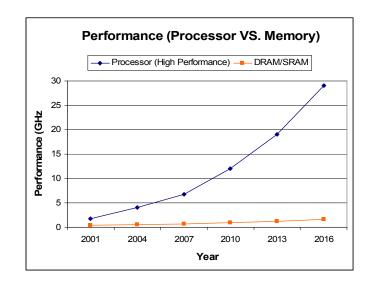

| Figure 46: Performance gap between processor and DRAM (from ITRS)                                       | . 72 |

| Figure 47: Performance increase rates for processor and DRAM (from ITRS).                               | . 73 |

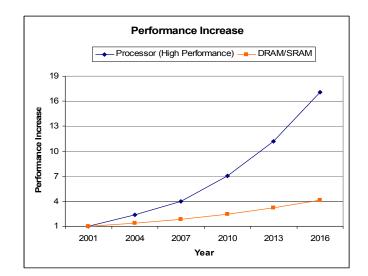

| Figure 48: The overall framework of the systematic design method for a SIMD-systolic system             | ı.75 |

| Figure 49: DG for VQ application.                                                                       | .76  |

| Figure 50: One-Column system designed for VQ based on transformations in Table 13.                      | .77  |

| Figure 51: Space-time representation.                                                                   | . 78 |

| Figure 52: Segment-level system designed for VQ.                                                        | . 78 |

| Figure 53: High level view of space-time diagram assuming 4 x 4 processor array.                        | . 79 |

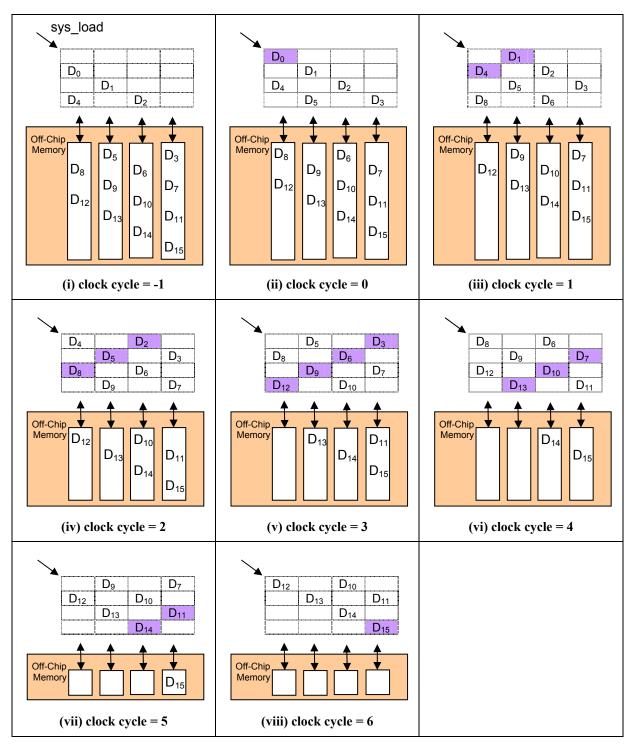

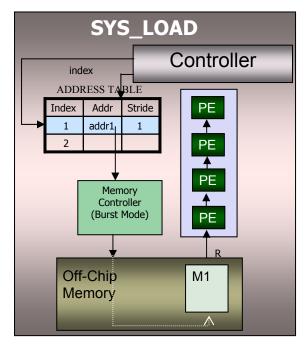

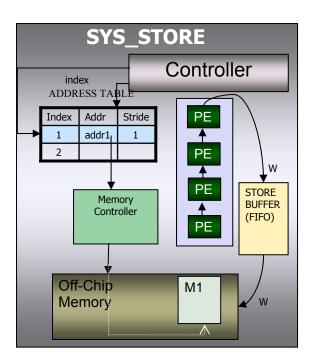

| Figure 54: Systolic virtual memory: systolic load mechanism.                                            | . 81 |

| Figure 55: Systolic virtual memory: systolic store mechanism.                                           | . 81 |

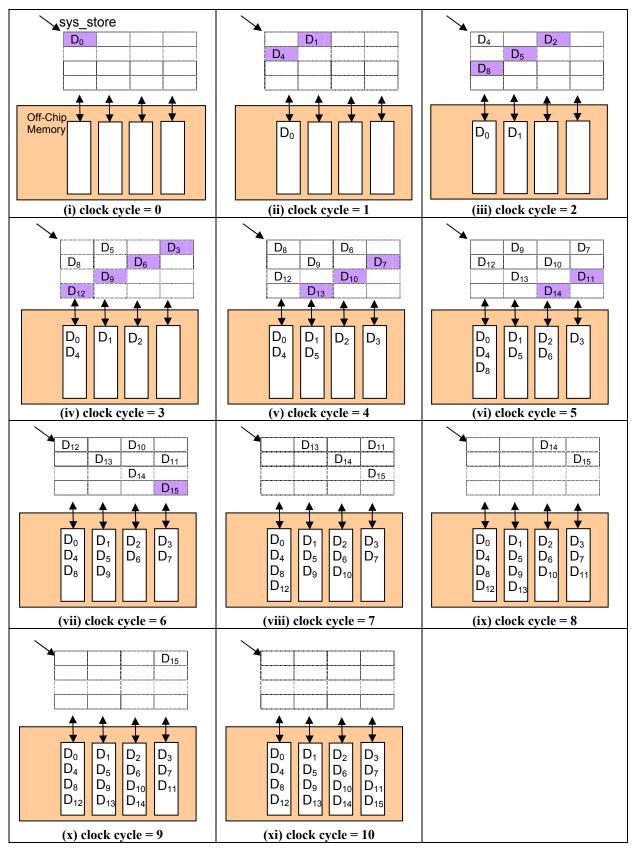

| Figure 56: An Example of Systolic Store.                                                                | . 82 |

| Figure 57: An example of software data prefetching using the 'prefetch' instruction.                    | . 83 |

| Figure 58: Extended instruction format for data prefetching                                             | . 84 |

| Figure 59: An example of an extended instruction format: 'sys_load R1, SR0.'                            | . 84 |

| Figure 60: An example of data movement in one column of an 8 x 8 processor array for a 'sys_load.'      | . 85 |

| Figure 61: Address table.                                                                               | . 85 |

| Figure 62: An example of data prefetching using the address table given in Figure 61                    | . 86 |

| Figure 63: An example of data prefetching.                                                              | . 87 |

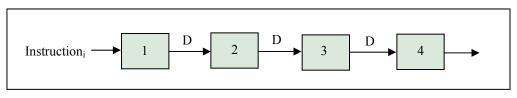

| Figure 64: An example of consecutive systolic load instructions                                         | . 88 |

| Figure 65: An example of consecutive systolic store instructions                                        | . 89 |

| Figure 66: An example of three consecutive systolic load instructions                                   | . 90 |

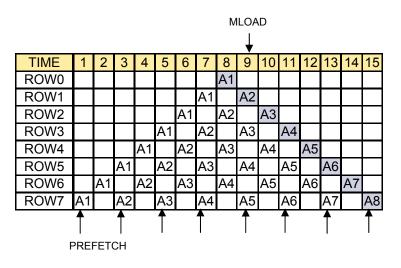

| Figure 67: Framework of an instruction scheduler for systolic virtual memory                            | . 91 |

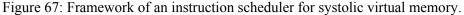

| Figure 68: Channel utilization for a given number of consecutive memory operations                      | .93  |

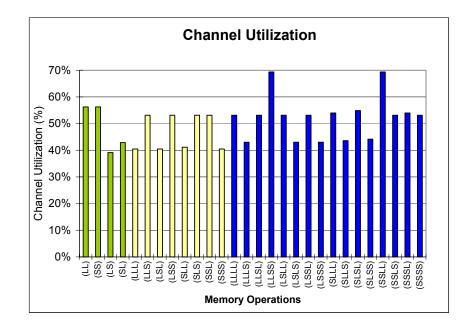

| Figure 69: Channel utilization for a given combination of memory operations. (L:sys_load, S: sys_store) | . 94 |

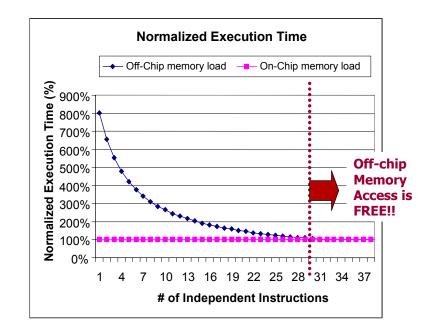

| Figure 70: Normalized execution time of off-chip memory operation relative to the on-chip memory operation                       |

|----------------------------------------------------------------------------------------------------------------------------------|

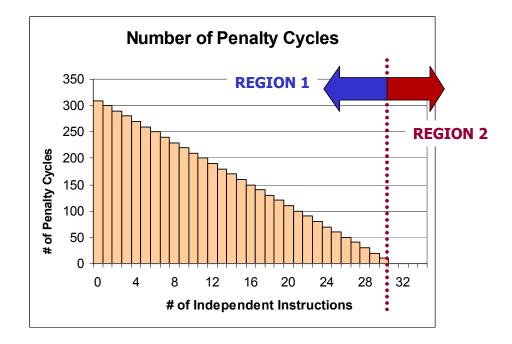

| Figure 71: Clock count penalty for systolic virtual memory                                                                       |

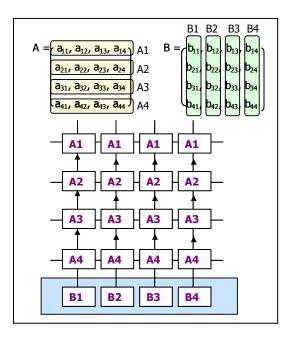

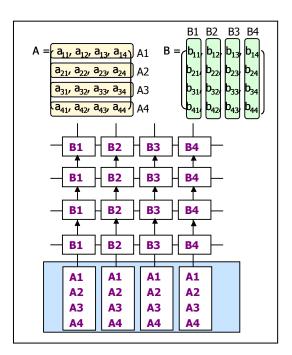

| Figure 72: Matrix multiplication application with shared memory address space                                                    |

| Figure 73: Matrix multiplication application with private memory address space97                                                 |

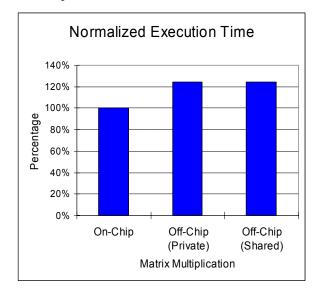

| Figure 74: Matrix multiplication: normalized execution time                                                                      |

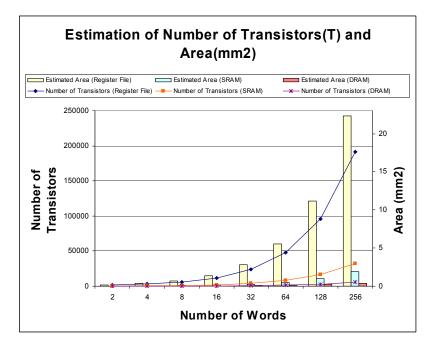

| Figure 75: Estimation of the number of transistors and area for each type of memories: DRAM, SRAM, and register file             |

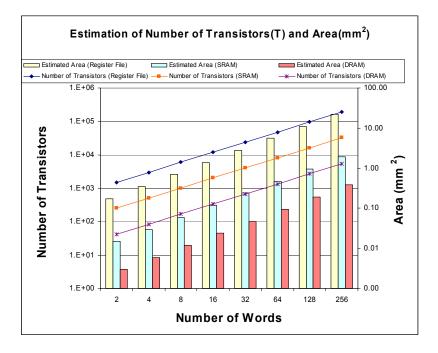

| Figure 76: Estimation of the number of transistors and area for each type of memories: DRAM, SRAM, and register file (log scale) |

| Figure 77: Memory requirements for each implementation in the number of memory words100                                          |

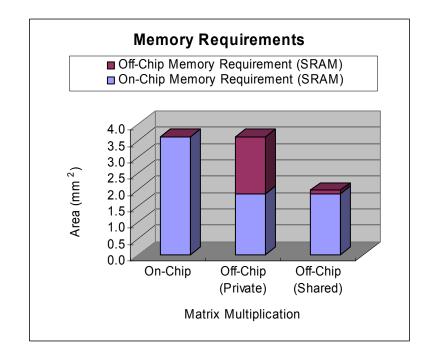

| Figure 78: Memory requirements in area where both memories (on-chip & off-chip) are implemented by SRAM                          |

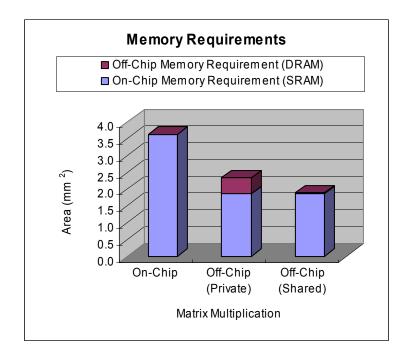

| Figure 79: Memory requirements in area where off-chip memory is implemented by DRAM and on-chip memory is implemented by SRAM    |

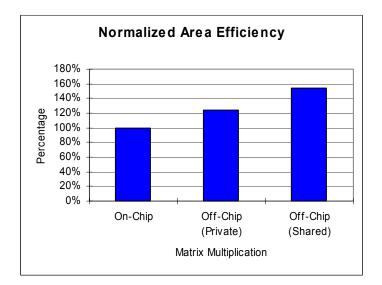

| Figure 80: Normalized area efficiency                                                                                            |

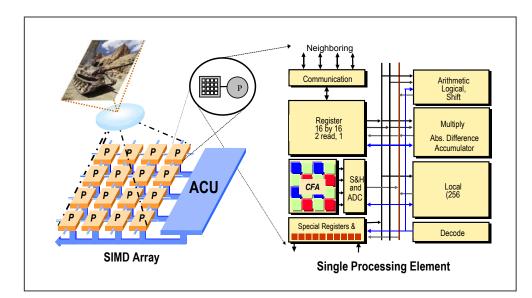

| Figure 81: SIMPil microarchitecture                                                                                              |

## **Summary**

SIMD parallelism offers a high performance and efficient execution approach for today's broad range of portable multimedia consumer products. However, new methods are needed to meet the complex demands of high performance, embedded systems. This research explores new storage management techniques for this focused but critical application. These techniques include memory design exploration based on the application retargeting technique, storage-based systolic instruction broadcast, and systolic virtual memory to improve both the performance and efficiency of embedded SIMD systems. A selection of image processing applications serves as the workload for the study. Code retargeting software, architectural simulation, and technology models are used to evaluate these methods.

### **CHAPTER 1**

### Introduction

#### 1.1. Introduction

Growing consumer demand for portable multimedia products is focusing architectural research on high efficiency, high performance computing architectures. These computing applications exhibit significant data parallelism that can be effectively exploited using well-studied execution models, such as Single Instruction Multiple Data (SIMD) architectures. Limited attempts to harness data parallelism through subword parallelism have already been incorporated in multimedia instruction extensions on general-purpose microprocessors and more recently in DSP processors. Much greater parallelism is available in applications; but SIMD architectures techniques developed in the 1970's and 1980's do not fully address issues that arise in implementing a monolithic SIMD array in an embedded system. One critical area is the handling of storage (registers, local processing element (PE) memory, and off-chip memory). Technology advances in transistors, on-chip interconnects, and packaging have dramatically altered the relative performance, implementation cost, and level of integration of storage.

This thesis presents research on techniques to efficiently handle the storage hierarchy in embedded SIMD processors for multimedia applications. It includes distribution of register and local memory storage, as well as a systolic approach to support off-chip dense memory arrays with minimum latency.

The basic research problems being addressed are defined in the next section.

#### 1.2. Problem Statement and Contributions

There are many research issues to be addressed in the development of an embedded SIMD system. This thesis addresses three basic research problems.

First, in a replicated cell (a SIMD processing element), efficient silicon area usage is critical. Data storage (registers and local memory) is the single largest allocation of silicon area in a PE design. Registers have multiple access ports and the fastest access time whereas local memory can store more bits in a given area. An optimal allocation between registers and local memory requires a methodology for evaluating performance and cost across a set of target applications.

Second, SIMD execution is defined as simultaneous execution of broadcast instructions at every PE. As VLSI technology advances, PEs get smaller and SIMD arrays get larger. To avoid inevitable clock frequency limitations, a segmented, temporally and/or spatially shifted broadcast technique must be employed. This scheme must employ a combination of software reordering and hardware mechanisms to avoid the resulting data hazards.

Third, while local PE memory provides the fastest and most accessible (greatest access bandwidth) operand storage, off-chip dense memories can provide significantly greater density due to their specialized fabrication process and amortized interface circuitry. But accessing off-chip memory is complicated by limited per PE memory bandwidth, especially for large PE arrays. The situation is further exacerbated by SIMD's synchronous instruction execution that creates magnified peak off-chip bandwidth demands.

This thesis research attacks these problems with three related architectural approaches:

#### Approach 1: Improve methods to evaluate storage usage within a PE

Develop automatic techniques to examine application characteristics and explore the space of feasible register and local memory configurations. This includes automatic application retargeting and compilation techniques and technology modeling so cost and efficiency can be accessed.

#### Approach 2: Explore systolic instruction broadcast and resulting data hazard avoidance

Systolic instruction broadcast [1] eliminates long broadcast wires at the expense of execution simplicity. Develop and evaluate techniques for eliminating data hazards with this staggered execution of instructions with minimal performance penalty. Use implementation strategies and technology models to area costs and overall area efficiency.

#### Approach 3: Define and evaluate a systolic virtual memory system for off-chip storage

When local PE memory is insufficient or inefficient to meet application needs, develop an off-chip memory access technique utilizing the staggered instruction execution that results from systolic instruction broadcast. Employ data prefetching and scheduling techniques to minimize

penalties resulting from increased access latency and limited access bandwidth. Technology models are again developed to evaluate cost and efficiency as well as performance.

The following section summarizes related research on which this thesis builds.

#### 1.3. Related Research

#### **1.3.1. SIMD Instruction Broadcast**

As mentioned earlier, long wires for global instruction broadcast in SIMD directly limit clock rates [1,2,4]. Recent designs attempt to address this problem with limited success; a board level instruction issue rate of 100MHz was achieved in 1995 by Bolotski's Abacus [5] and a chip level issue rate of 200MHz is achieved in products from PixelFusion which are currently developed with the clock rate of 400MHz for 256 PEs [6]. This instruction bottleneck limits the scalability of SIMD architectures [1,4,7].

Two alternatives to overcome instruction bottlenecks are pipelined instruction broadcast and the use of instruction caches [4]. The first approach hides the average broadcast latency by pipelined instruction broadcast. The Blitzen project [8] and MasPar's MP-2 [9] employed this method. The disadvantage of pipelined instruction broadcast is the required additional instruction latches. The second approach is proposed by Rockoff which uses a SIMD instruction cache [10]. However, this method consumes significant chip area and depends on temporal instruction locality for its effectiveness.

#### 1.3.2. Systolic Arrays

H. T. Kung and C. E. Leiserson introduced systolic arrays in 1978 [11]. Figure 1 shows the conventional processor with one PE and systolic array with an array of PEs named cells due to their regularities [12,13,14].

(a) Conventional processor with one PE (b) Systolic array with an array of PEs

As shown in Figure 1-(b), systolic array can achieve high throughput with the same I/O bandwidth by having array of many PEs. In a systolic system, data is pumped from the memory module rhythmically, passing through the array of PEs until it returns to the memory module. Though, the systolic array shown in Figure 1 is a linear array, it can be multi-dimensional to achieve a high degree of parallelism.

Systolic architectures have been proposed to design special-purpose systems whose efficiency derives from modular expansibility, simple and regular data and control flows, use of simple and uniform cells, elimination of global broadcasting, fan-in, fast response and balancing computation with I/O [2,12,15]. However, since the I/O problem is also related to the available internal memory, an appropriate memory structure should be designed to achieve a balance between computation time and I/O time [2,12,15]. Later surveys in [2,15] categorize systolic system into specific-purpose systolic system and general-purpose systolic system. Early design efforts in systolic systems were mainly related to solving a specific problem, e.g., matrix multiplication or convolution. These systems can achieve high performance due to application specific hardware. However, application specific architectures are expensive since their cost cannot be amortized across multiple applications. Thus many research efforts on general-purpose systolic architectures are gaining importance. General-purpose architectures can be divided into two categories – programmable models and reconfigurable models. The former can be implemented in SIMD or Multiple Instruction Streams and Multiple Data Streams (MIMD) architectures and the latter can be implemented by Field Programmable Gate Arrays (FPGAs). FPGAs have great advantage in flexibility by allowing system to be reconfigured. However, FPGAs are still more expensive, lower performance, and consume more power than those of Application Specific Integrated Circuits (ASICs). Thus programmable model is more appropriate for the current embedded systems running some set of applications while having some degree of flexibility thanks to the programmability.

Very Large-Scale Integration (VLSI) has revived systolic systems from the early eighties because systolic architectures can be easily implemented with the growing levels of integration. However, systolic architectures remain difficult to design and implement due to the requirements of detailed information such as data and control flows, computation sequences, and spatial and temporal information of all data used by applications [16,17,18]. In addition, formal design methods involving correctness-preserving transformations are required as the complexity of VLSI system design increases [19]. There are several systematic design approaches to design specified systolic arrays algorithmically [14,16,17,18,19,20]. Such techniques, transformation methods based on data flow [21], mathematical transformations based on data dependencies [22], and

mappings for multistage algorithms [23], are well observed for several algorithms in [14,17,18,19]. These design methods start with the representation of systolic algorithms in several formats such as data-flow graphs [19], signal-flow graphs [19], or Regular Iterative Algorithms (RIAs) [24]. These representations basically capture information about data dependencies and functional requirements. A popular graph representation is the Reduced Dependence Graph (RDG) which can be used to determine processor mappings for each task and scheduling of an algorithm based on the computed delays from data dependencies. Resulting processor maps and schedules correspond to the representation of the given algorithm. Usually, space representations depend only on algorithms not on architectures. Thus processor mappings and scheduling methods should be reconsidered to design SIMD-systolic architectures with fixed architecture features to obtain proper mapping of processors while satisfying time-constraints corresponding to systolic instruction broadcast.

This research extends the SIMD architecture by employing systolic instruction broadcast and systolic data movement methodologies to overcome the bottleneck of the memory bandwidth in SIMD architectures and to eliminate long wires which may cause low clock frequency, increased interconnection area and high power consumption. Concerns of efficient sequencing of instructions and scheduling of data movement are addressed for a correctness-preserving system design. A SIMD-systolic architecture simulator is built to run a set of workloads and the current technologies are plugged in the simulator to study the implementation limits.

#### **1.3.3. Instruction Systolic Architecture (ISA)**

In this section, the comparisons between SIMD-systolic system and Systola 1024 (ISATEC Co.) [25,26,27,28,29,30] are presented. In Section 3.3.2, more details of Systola architecture will be explained. The main difference between these two systems lies in the existence of instruction scheduler and data prefetching logic. The differences in high-level design issues between Systola 1024 and SIMD-systolic system are categorized in Table 1.

Table 2 shows several details in comparisons of Systola 1024 with SIMD-systolic system which is defined as target architecture of our research.

|                                                                                       | Systola 1024    | SIMD-systolic                                                      |  |  |  |  |

|---------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------|--|--|--|--|

| Wires                                                                                 | Short           | Short                                                              |  |  |  |  |

| Instruction Distribution                                                              | Systolic way    | Systolic way                                                       |  |  |  |  |

| Systematic design method                                                              | N/A             | Yes (Extended mapping techniques<br>for the data dependency graph) |  |  |  |  |

| Scheduling Responsibility                                                             | Programmer      | Scheduler                                                          |  |  |  |  |

| Methodology to control the data<br>movement based on the<br>corresponding instruction | N/A             | Instruction scheduling and data sequencing                         |  |  |  |  |

| Bandwidth from one memory module                                                      | Serial bit-wise | Word wide (16bits/word)                                            |  |  |  |  |

Table 1: High-level comparisons between Systola and SIMD-systolic system

Table 2: Low-level comparisons between Systola and SIMD-systolic system

|                             | Systola 1024                                                                                                                                                                        | SIMD-systolic                                                                              |  |  |  |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| Flexibility                 | Yes (Programmability + Selectors)                                                                                                                                                   | Yes (Programmability + more general instruction sets)                                      |  |  |  |  |  |

| Simplicity &<br>Scalability | Yes (Simple regular processor array)                                                                                                                                                | Yes (Simple regular processor array)                                                       |  |  |  |  |  |

| Generality                  | Medium (Use of selectors makes<br>possible to run the different set of<br>instructions on different PE. + Small<br>set of instructions restrict the<br>functionality of processors) | Medium-High (Instruction sets are more<br>general to cover a large set of<br>applications) |  |  |  |  |  |

| Suitability for<br>VLSI     | Yes                                                                                                                                                                                 | Yes                                                                                        |  |  |  |  |  |

| Aggregate<br>Function       | Easy and Fast                                                                                                                                                                       | Easy and Fast                                                                              |  |  |  |  |  |

| Diameter                    | High $(2N - 2 \text{ for } NxN \text{ processor array})$                                                                                                                            | High (2N – 2 for NxN processor array)                                                      |  |  |  |  |  |

| Conditional jumps           | N/A                                                                                                                                                                                 | Sleep, Jump, Branch instructions                                                           |  |  |  |  |  |

| Global operation            | N/A                                                                                                                                                                                 | s_vectorize, s_raisehand                                                                   |  |  |  |  |  |

| Value Broadcasting          | Row-wise or Column-wise                                                                                                                                                             | Immediate value can be broadcasted<br>from controller using s_vectorize<br>instruction     |  |  |  |  |  |

| Data Word Length            | 8 bits                                                                                                                                                                              | 16 bits                                                                                    |  |  |  |  |  |

| On-chip Memory              | 32 registers + 2 communication<br>registers (C-registers)                                                                                                                           | 16 registers + 256 memory words                                                            |  |  |  |  |  |

| Special constant            | Registers 0, -1                                                                                                                                                                     | N/A                                                                                        |  |  |  |  |  |

| State flags                 | zero flag, negative flag                                                                                                                                                            |                                                                                            |  |  |  |  |  |

| Number of                   |                                                                                                                                                                                     | 70 instructions (38 PE instructions + 32                                                   |  |  |  |  |  |

| instructions                | 24 instructions                                                                                                                                                                     | controller instructions)                                                                   |  |  |  |  |  |

#### **1.3.4.** Compilation Techniques for Storage Optimization

Compilation techniques have been heavily developed to improve performance. In this sense, memory optimization techniques are developed to minimize memory bottlenecks due to the gap between processor and memory performance. One of them is the design of storage hierarchy which tries to reduce the memory access time by maximizing data locality.

However, storage (data and program) reduction techniques must be considered for resourceconstraint systems, such as embedded systems [31,32,33]. This class of architectures is often used as portable devices in which power consumption and area cost are very important factors to achieve the long battery life and small size, in addition to high performance.

Until the early nineties, memory optimization techniques for embedded systems have been mainly developed to decrease code size, such as addressing optimization [34,35,36,37], mode optimization [38,39,40] and code compression [40]. These techniques utilize special architectural features such as addressing modes for a particular embedded system to minimize the code size. Program memory optimization is not the main concern in this proposed research since PEs will receive an instruction from a central controller without storing it.

Recently, many data memory optimization techniques are being developed as embedded systems flourish. The main effort is to reduce an allocated memory size especially for array data which usually takes a large fraction of data [41,42]. Data memory optimization techniques can be categorized into two approaches – architecture dependent optimizations and architecture independent optimizations [32]. A recent survey on data memory optimizations is available in [32].

Architecture independent optimization techniques are based on source-level transformations such as loop transformation and code rewriting to increase the data reusability. Loop transformation techniques are developed for long periods to increase the performance of the program [43]. However, these techniques also can be used to decrease the number of data accessed by merging two loops which access the same data [32].

Architecture dependent optimization techniques are designed for particular memory architectures. One of effective ways of reducing memory requirements is through better utilization of given registers. This is not only for maximizing memory utilization, and also for reducing power consumption and maximizing performance. The most frequently used variable should get the highest priority to be assigned a register since access to a register is less power consumed, and results in shorter access time. Register allocation is a standard part of the compilation process [44], usually using a common graph-coloring algorithm [45,46,47].

Typically, register allocation is performed on an internal representation (IR) right before code generation.

However, in this research, a cost-based register allocation is performed on assembly code. The result of our technique is assembly code that is retargeted to a given number of registers. If an input assembly code can run with a given number of registers, the input application is rewritten automatically to minimize the number of registers used in the application. Otherwise, the data in registers will be spilled into the data memory [45]. The register allocation and memory spilling are based on a cost model which is used to select the spilling-candidate registers.

Application retargeting is often performed by retargetable compilers [48]. A significant amount of research in this area has been conducted for embedded processors including CHESS [38], SPAM [34], AVIV [49], RECORD [50], and CodeSyn [48]. Since a single retargetable compiler is sufficient for different configurations of architecture, retargetable compilers are gaining popularity as reconfigurable architectures are emerging that can be tailored to a given workload. However, these techniques take high-level programs or some descriptions as an input. Thus hand-coded assembly code cannot be retargeted with these techniques directly. We develop retargeting techniques which can be used for general patterns of assembly applications – handwritten codes and compiler generated codes. Consequently retargeting techniques can play a great role in developing register size dependent embedded applications which still are written in assembly languages to achieve real-time performance requirements.

In this research, memory optimization is performed based on variable lifetimes under the assumption that effective addresses can be determined in compile time. The lifetime based optimizations [52,53] are reassigning the same memory location for different data items of which lifetimes are not overlapped. The resulting memory optimized code is also written in assembly code running on the same architecture as an input platform. Our retargeting techniques for different register sizes may increase memory uses due to the spilling. Thus memory optimization technique, called memory retargeting, is placed after register retargeting to increase data reusability by variable lifetime analysis. In addition, lifetime analysis techniques to place the frequently used data in higher level of memory in a memory hierarchy are useful when off-chip memory is used, to deal with its long access time.

Our retargeting techniques – register retargeting and memory retargeting – can be used to decide the optimal storage configurations for a selected set of workloads by analyzing the resulting retargeted applications in terms of the area efficiency and energy efficiency. This technique is applicable to either SIMD architectures or general architectures.

#### 1.3.5. Summary of Related Research

Related research is described based on categories of techniques from Section 1.3.1 through Section 0. The proposed research is built on this related research. The summary of related research is depicted in Figure 2. In addition, Figure 2 shows the relations among these research efforts to express how this research is built on the previous research works.

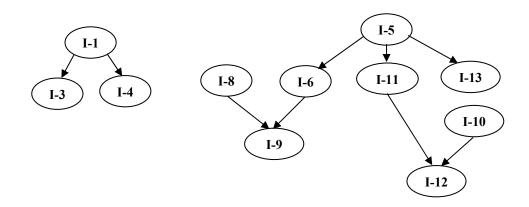

Figure 2: Relations among related research and our approaches in three contributions.

#### 1.4. Thesis Contribution Summary

This outline summarizes the contributions presented in this thesis.

#### Contribution 1: Efficient Storage Usage in Embedded SIMD Systems

An analysis method for assessing storage needs and costs of a given application automatically retargeted across a spectrum of storage configuration designs was developed. Using this technique, a SIMD processing element achieves optimal area and energy efficiency with a register file containing between 8 and 12 words for given workload. This configuration is between 15% and 25% more area and energy efficient than other memory configurations being considered.

#### **Contribution 2: Systolic Instruction Broadcast for Embedded SIMD Architectures**

Systolic instruction broadcast is a high performance and area efficient instruction broadcasting scheme with short-wire interconnects by eliminating of wire latency bottleneck found in global instruction broadcast. In this contribution, we simulated systolic instruction broadcast in three approaches – software method, 2-write port register file method, and bypass method. Each method can result different area efficiencies based on the fraction of communications over a given set of instructions. In our evaluations, due to the system's short clock cycle time and scheduler, a speedup in system performance of up to 7.5 can be achieved by the year 2010. In addition, speedup of area efficiency also can be achieved up to 7.2 for a given workload.

#### **Contribution 3: Systolic Virtual Memory**

The ability of minimizing off-chip memory access latency while maximizing access frequency by scheduling techniques along with data prefetch techniques in systolic virtual memory mechanism was evaluated using our SIMD-systolic architecture simulator. Results show that, systolic virtual off-chip memory with shared address space can achieve over 50% higher area efficiency than that of an on-chip only system for a matrix multiplication application.

| Contributi | on 1: Efficient Storage Usage in Embedded SIMD Systems                          |

|------------|---------------------------------------------------------------------------------|

| •          | Created methods and tools that retarget assembly language applications to       |

|            | different on-chip memory configurations.                                        |

| •          | Developed a memory configuration evaluation framework for performance,          |

|            | technology-model-based costs (area and energy), and area and energy             |

|            | efficiency.                                                                     |

| •          | Exercised and evaluated techniques for a selected application set.              |

|            |                                                                                 |

| Contributi | on 2: Systolic Instruction Broadcast for Embedded SIMD Architectures            |

| •          | Evaluated three approaches (software-only, 2-write port registers and hardware  |

|            | bypass) for systolic instruction broadcasts to support instruction execution at |

|            | local interconnect clock frequency projections.                                 |

| •          | Developed instruction reordering scheduler that minimizes execution time        |

|            | penalties for software hazard avoidance methods.                                |

| •          | Incorporated implementation and technology models for hazard avoidance          |

|            | methods to evaluate area cost for different technology generations.             |

| •          | Evaluated system performance and area efficiency for hazard avoidance           |

|            | methods for a high-communication application workload.                          |

|            |                                                                                 |

| Contributi | on 3: Systolic Virtual Memory                                                   |

| •          | Developed a scheme for utilizing a combination of local PE and off-chip         |

|            | memory in an embedded SIMD system.                                              |

| •          | Adapted a linear mapping algorithm for systolic off-chip memory prefetch        |

|            | scheduling.                                                                     |

| •          | Defined a VLIW-style SIMD instruction format and controller modification to     |

|            | support systolic virtual memory.                                                |

| •          | Evaluated technique using both high memory synthetic and kernel                 |

|            | applications.                                                                   |

| •          | Incorporated technology and memory cell implementation models for memory        |

|            | size, area, and area efficiency evaluation.                                     |

|            |                                                                                 |

#### 1.5. Thesis Outline

The next three chapters of this dissertation discuss the methodology and results of the primary contributions. Chapter 2 presents an analysis method for assessing storage needs and costs of a given application automatically retargeted across a spectrum of storage configuration designs. Chapter 3 presents techniques for short-wire instruction broadcast to eliminate the wire latency bottleneck found in global instruction broadcast. Chapter 4 presents support for off-chip dense memory, called systolic virtual memory. The final chapter, Chapter 5, summarizes the results of this work and discusses future work. The appendix provides brief details about our baseline architecture, the SIMPil system.

### **CHAPTER 2**

## Efficient Storage Usage in Embedded SIMD Systems

#### 2.1. Summary

Operand storage consumes a significant fraction of silicon area in today's processors. For embedded systems, resources are often limited and cost is critical. In an effort to introduce largescale parallelism into embedded systems, new techniques are required to evaluate the effectiveness of each level of the storage hierarchy in order to achieve optimal efficiency in a highly replicated processing node design. This chapter presents a technique for analyzing storage performance and efficiency for a given application workload. It takes a two-prong approach: a) an automated retargeting technique is used in analyzing the storage requirements of a program over a range of storage configurations, and b) cost is estimated in terms of energy, and area efficiency for a given workload and storage configuration. Together these are used to explore storage configurations by analyzing a given workload under a range of different storage configurations with respect to performance, energy consumption, and chip area costs. Using this technique, a SIMD processing element achieves optimal area and energy efficiency with a register file containing between 8 and 12 words. This configuration is between 15% and 25% more area and energy efficient than other memory configurations being considered.

#### 2.2. Introduction

Energy and area efficiency are critical metrics for embedded systems where battery life and cost are the central product parameters. Because storage (on-chip memory, caches, and register files) typically occupies half the chip area [3] and consumes a significant fraction of chip energy, exploring designs for effective storage utilization is vital.

This chapter presents a two-prong approach to support this design exploration. One, an automated retargeting technique is used in analyzing storage requirements of programs over a

range of storage configurations. This type of retargeting is too expensive and labor-intensive to perform manually during design exploration, particularly for hand-coded assembly programs that are optimized for specific embedded processor memory designs. Second, cost estimation is performed to assess the energy and area efficiency based on a given workload and storage configuration. This is used to extract a characterization of storage costs for a given program. Three factors, performance, energy, and area are used to decide an optimal storage configuration for a given workload.

In this chapter related research is presented first, followed by a description of our approach to explore the memory design space. Finally, results are given along with conclusions.

#### 2.3. Related Work

#### 2.3.1. Application Retargeting

Application retargeting is often done by retargetable compilers [33,34,35,38,48,49,50]. A significant amount of research in this area has been performed for embedded processors, including CHESS [35], SPAM [34], AVIV [49], RECORD [50], and CodeSyn [48]. Since a single retargetable compiler is sufficient for different configurations, retargetable compilers are gaining popularity as reconfigurable architectures are emerging that can be tailored to a given workload. These compilers take high-level programs and a target processor model description as input to generate assembly programs for the target processor. However, real-time embedded systems often run hand-coded assembly programs for efficiency. As a result, retargetable compilers cannot be utilized in the design phase.

Rewriting assembly programs by hand for new target architectures requires a massive modification effort, particularly since they are notoriously less portable and maintainable [51]. Thus, manually rewriting assembly programs during design exploration is not feasible. For these reasons, the presented technique applies automated application retargeting techniques to assembly programs to adapt them for different storage configurations.

These retargeting techniques extend traditional register allocation and memory optimization techniques described in the next two sections.

#### 2.3.2. Register Allocation

One of the back-end compilation processes is register allocation [44], usually using a common graph-coloring algorithm [45,46,47]. As a standard part of compilation processes,

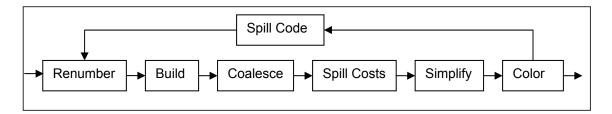

register allocation takes an internal representation (IR) as input to allocate a given set of registers to variables. Processes in register allocations proposed in [45,46] are depicted in Figure 3 (Chatin's register allocator) and Figure 4 (Brigg's register allocator), respectively, and each step in the process is described as follows.

**Renumber:** Assign a unique name to each symbolic register during its live ranges.

> Build: Build the interference graph for the renamed registers based on the live ranges.

Coalesce: Delete "copy" instructions if the destination and source live ranges do not interfere.

> Spill Costs: Compute the spill cost for each live range by estimating the weighted number of loads, stores and other instructions needed to spill them.

Simplify: Recursively remove unconstrained nodes from the graph and push them onto a coloring stack. If there are only constrained nodes in the graph, remove the nodes, mark them for spilling, and continue.

> Spill Code: Insert spill code for marked nodes.

Color: Pop all the nodes off the coloring stack and give each node a color different from its neighbors.

Figure 3: Chatin's register allocator [45]

Figure 4: Brigg's register allocator [46,47]

Brigg's allocator modifies Chatin's allocator such that registers are allocated for variables more optimistically by deferring a decision of node colorability until the last stage, 'Color'.

Our technique extends Chatin's allocator to support register allocation technique across a range of file and memory sizes. Typically, register allocation is performed on an internal representation (IR) just before code generation. However, in our research, a register reassigning process takes an assembly program as input and retargets it to operate within a given register file limit. If an assembly program can run with a given number of registers, it is rewritten automatically to minimize the number of registers used in an application. Otherwise, register values will be spilled into memory based on a cost model [47].

#### 2.3.3. Memory Optimization

Memory optimization techniques for embedded systems have been mainly developed to decrease code size, such as addressing optimization [34,48], mode optimization [40], and code compaction [37]. These techniques utilize special architectural features for particular embedded systems to minimize code size. Program memory optimization tends to be simpler than data memory optimization since data memory optimization must compute an effective address of data which is sometimes difficult or impossible to do unambiguously at compile time. Data memory optimization techniques that reduce the size of data memory are considered by placement and indexing of an array, which usually takes a large fraction of data in multimedia applications [41,42]. There are two main allocation strategies for array data – static and dynamic strategies [42]. In this chapter, we take a dynamic memory allocation strategy based on live ranges of memory words, with the assumption that the effective address can be determined at compilation time. Since compilation time in embedded systems is less critical than that in general systems, we compute all effective addresses at compile time. In addition, since our approach is applied to assembly programs, there is no difference between array data and non-array data.

#### 2.4. Approach: Application Retargeting for Different Memory Configurations

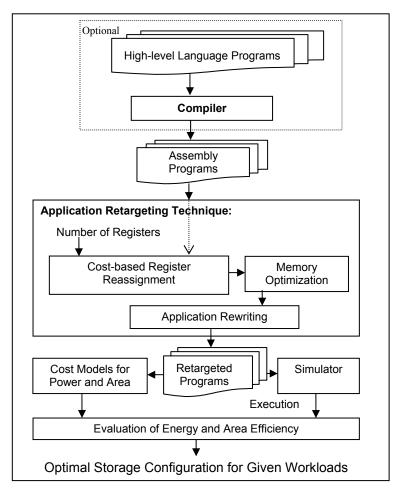

The overall retargeting procedure, depicted in Figure 5, is discussed in this section. A significant number of applications for embedded processors are still hand-coded to meet real-time constraints. Since rewriting assembly code for several different configurations is error-prone and laborious, the development of automatic retargeting techniques for assembly programs is necessary for efficient design exploration. These assembly programs can be either hand-coded or generated by compilers. Once applications are retargeted, a simulator is used to run them to estimate their performances in executed clock cycles under the assumption that each instruction takes one clock cycle to execute. Since we are assuming that both on-chip memory and registers can be accessed in one clock cycle, differences in execution clock cycles are from the overhead of register spilling.

Figure 5: Overall framework for finding optimal storage configurations by application retargeting.

There are two main steps to retarget applications for given storage requirements. The first step is register reassignment, followed by memory optimization.

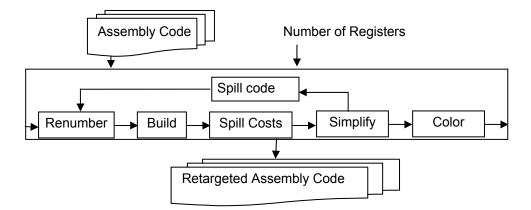

#### 2.4.1. Register Allocation

Register allocation techniques are used to generate register-optimized applications with a limited number of registers by analyzing variable lifetimes. If there is a lack of registers, register spilling techniques [47] are applied to use memory instead of registers until a resulting application can run on the given number of registers. Figure 6 shows the register allocation module used in our approach. This register allocation technique is composed of processes in Chaitin's register allocator [45]. However, a typical register allocator usually takes the intermediate representation (IR) as an input of the back-end compilation process, while our approach takes either hand-written or compiler-generated assembly programs. In addition, our output programs can be run on target architectures directly. This can maximize code reusability.

Figure 6: Application retargeting module with register reassignment

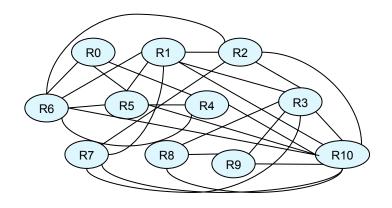

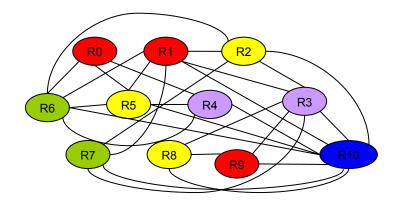

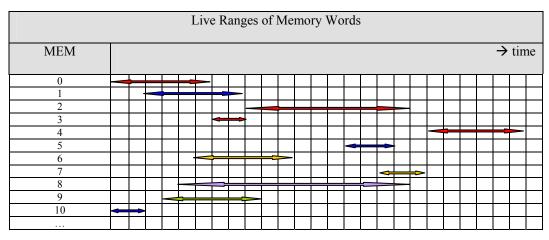

Since spilling costs are computed based on register usage, less frequently used register values are spilled. An example of register reassignment based on lifetimes is depicted in Figure 7. Assembly programs are written in the SIMPil assembly language and the description of each instruction is explained in the 'Comment' column in Figure 7. As in Chatin's allocator, an interference graph is built such that each register is represented by a node in the graph, and edges are drawn between nodes when there is an overlap in the registers' lifetimes. The resulting graph is shown in Figure 7 (b) and the colored graph is shown in Figure 7 (c). Finally, register reassigned assembly code is shown in Figure 7 (d).

| Source Code     |                             | Live Ranges of Registers |    |    |    |    |    |    |    |    |    |     |

|-----------------|-----------------------------|--------------------------|----|----|----|----|----|----|----|----|----|-----|

| Code            | Comment                     | R0                       | R1 | R2 | R3 | R4 | R5 | R6 | R7 | R8 | R9 | R10 |

| Loadi 10        | R0 ← 10                     |                          |    |    |    |    |    |    |    |    |    |     |

| Addi R4, R0, 0  | $R4 \leftarrow R0 + 0$      |                          |    |    |    |    |    |    |    |    |    |     |

| Addi R5, R0, 1  | R5 ← R0 + 1                 |                          |    |    |    |    |    |    |    |    |    |     |

| Addi R6, R0, 2  | R6 ← R0 + 2                 |                          |    |    |    |    |    |    |    |    |    |     |

| Addi R10, R0, 3 | R10 ← R0 + 3                |                          |    |    |    |    |    |    |    |    |    |     |

| Load R1, R4     | $R1 \leftarrow MEM[R4]$     |                          |    |    |    |    |    |    |    |    |    |     |

| Load R2, R5     | $R2 \leftarrow MEM[R5]$     |                          |    |    |    |    |    |    |    |    |    |     |

| Load R3, R6     | $R3 \leftarrow MEM[R6]$     |                          |    |    |    |    |    |    |    |    |    |     |

| Sub R7, R1, R2  | R7 ← R1 – R2                |                          |    |    |    |    |    |    |    |    |    |     |

| Addi R8, R2, 0  | R8 ← R2 + 0                 |                          |    |    |    |    |    |    |    |    |    |     |

| Slti R7, 0x01   | If $(R7 < 0)$ then sleep    |                          |    |    |    |    |    |    |    |    |    |     |

| Addi R8, R1, 0  | Else R8 $\leftarrow$ R1 + 0 |                          |    |    |    |    |    |    |    |    |    |     |

| Wakeupi 0x01    | Wakeup                      |                          |    |    |    |    |    |    |    |    |    |     |

| Sub R9, R3, R8  | R9 ← R3 – R8                |                          |    |    |    |    |    |    |    |    |    |     |

| Slti R9, 0x02   | If $(R9 < 0)$ then sleep    |                          |    |    |    |    |    |    |    |    |    |     |

| Addi R8, R3, 0  | Else R8 $\leftarrow$ R3 + 0 |                          |    |    |    |    |    |    |    |    |    |     |

| Wakeupi 0x02    | Wakeup                      |                          |    |    |    |    |    |    |    |    |    |     |

| Store R10, R8   | $MEM[R10] \leftarrow R8$    |                          |    |    |    |    |    |    |    |    |    |     |

(a) Source code and live ranges of registers.

(b) Interference graph.

(c) Graph coloring with colors = { $\mathbf{R}$ , G, B, Y, V}.

| Source Code                         |                     |

|-------------------------------------|---------------------|

| Register in Original<br>Source Code | Reassigned Register |

| R0                                  | R0                  |

| R1                                  | R0                  |

| R2                                  | R3                  |

| R3                                  | R4                  |

| R4                                  | R4                  |

| R5                                  | R3                  |

| R6                                  | R1                  |

| R7                                  | R1                  |

| R8                                  | R3                  |

| R9                                  | R0                  |

| R10                                 | R2                  |

| Source Code     |                 |

|-----------------|-----------------|

| Original Code   | Reassigned Code |

| Loadi 10        | Loadi 10        |

| Addi R4, R0, 0  | Addi R4, R0, 0  |

| Addi R5, R0, 1  | Addi R3, R0, 1  |

| Addi R6, R0, 2  | Addi R1, R0, 2  |

| Addi R10, R0, 3 | Addi R2, R0, 3  |

| Load R1, R4     | Load R0, R4     |

| Load R2, R5     | Load R3, R3     |

| Load R3, R6     | Load R4, R1     |

| Sub R7, R1, R2  | Sub R1, R0, R3  |

| Addi R8, R2, 0  | Addi R3, R3, 0  |

| Slti R7, 0x01   | Slti R1, 0x01   |

| Addi R8, R1, 0  | Addi R3, R0, 0  |

| Wakeupi 0x01    | Wakeupi 0x01    |

| Sub R9, R3, R8  | Sub R0, R4, R3  |

| Slti R9, 0x02   | Slti R0, 0x02   |

| Addi R8, R3, 0  | Addi R3, R4, 0  |

| Wakeupi 0x02    | Wakeupi 0x02    |

| Store R10, R8   | Store R2, R3    |

(d) Register reassigning for each color:  $R \rightarrow R0$ ,  $G \rightarrow R1$ ,  $B \rightarrow R2$ ,  $Y \rightarrow R3$ ,  $V \rightarrow R4$ .

Figure 7: Example of register reassignment.

The source operand and destination operand can use the same register in this example. Thus if two lifetimes are overlapped only in one instruction, that is a defined instruction of one register value is also the last-use instruction of another register value, the same register can be allocated for these two registers. For example, R1 and R4 in Figure 7 (a) can be assigned to one register. As a result, there is no edge between these two registers in an interference graph that represents the interference between variables (registers in our case). This example shows an instruction level

register allocation not a basic block level. Since our approach is applied to basic blocks based on the control flow of applications, there are possible false overlaps of lifetimes of registers when two registers are used in the same basic block. However, control flow analysis line by line requires too much memory space to keep that information throughout the compilation phases or retargeting processes.

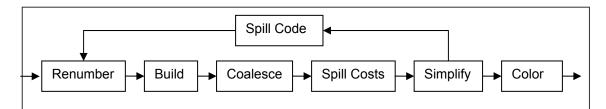

#### 2.4.2. Memory Optimization

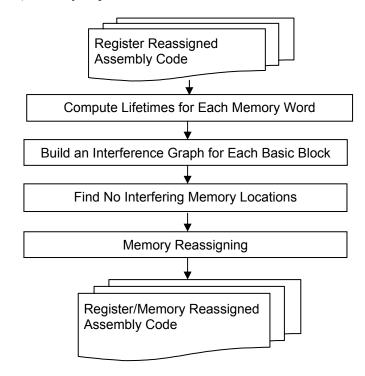

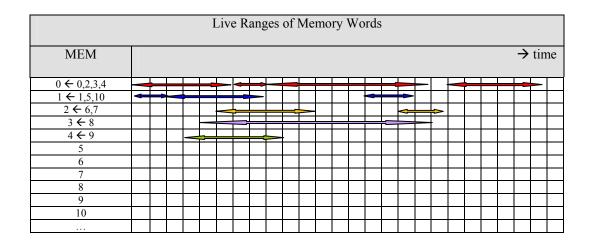

After register reassignment, memory accesses in applications are optimized to reduce memory requirements. By computing memory variable lifetimes, the same memory location can be reused for different memory data. The processes in this technique are depicted in Figure 8.

The memory reassigning phase also utilizes variable lifetime. For a given assembly program, lifetimes for each memory variable are computed for each basic block. After that, memory words are identified that can share the same memory location with other memory words, where the lifetimes of these memory words do not interfere. Then, memory addresses for selected data words are reassigned in a given application to share the memory location as much as possible. Finally, the retargeting module rewrites the application with reassigned memory addresses for memory data to achieve maximum reusability of memory locations, resulting in lower (or at least same, in the worst case) memory requirements.

Figure 8: Application retargeting module with memory optimization.