## **EXPLORATION OF LIQUID CRYSTAL POLYMER PACKAGING**

# TECHNIQUES FOR RF WIRELESS SYSTEMS

A Dissertation Presented to The Academic Faculty

by

Chad E. Patterson

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

Georgia Institute of Technology August 2012

## **EXPLORATION OF LIQUID CRYSTAL POLYMER PACKAGING**

## **TECHNIQUES FOR RF WIRELESS SYSTEMS**

Approved by:

Dr. Gary S. May, Advisor School of ECE *Georgia Institute of Technology*

Dr. John Papapolymerou, Co-Advisor School of ECE *Georgia Institute of Technology*

Dr. John D. Cressler School of ECE *Georgia Institute of Technology*  Dr. Andrew F. Peterson School of ECE *Georgia Institute of Technology*

Dr. Hua Wang School of ECE *Georgia Institute of Technology*

Dr. Christos Alexopoulos School of ISyE Georgia Institute of Technology

Date Approved: August 26, 2012

"I find that the harder I work, the more luck I seem to have." -Thomas Jefferson

"Insanity: doing the same thing over and over again

and expecting different results."

-Albert Einstein

To my family and friends for their unwavering faith and support.

### ACKNOWLEDGEMENTS

I would first like to thank Dr. John Papapolymerou and Dr. Gary May for their guidance and exemplary role as my Ph.D. advisors. John has taught me not only what it takes to become a research engineer but also the drive necessary to become successful in whatever endeavors I may encounter. Gary selflessly took me under his advisement so that I could pursue additional opportunities that invaluably expanded my breadth of research and business knowledge. I would like to thank them both for their faith and trust, which gave me freedom to pursue ideas in a creative manner.

I would also like to thank the additional members of my Ph.D. advisory committee, Dr. John Cressler, Dr. Andrew Peterson, Dr. Hua Wang and Dr. Christos Alexopoulos, who provided significant support and advisement during my graduate studies.

It has been a great honor and experience working with the entire MIRCTech team. I owe a debt of gratitude to the graduated members, Dr. Yuan Li, Dr. David Chung, Dr. Negar Tavassolian, Dr. Arnaud Amadjikpè, Dr. John Poh, and Dr. Eric Juntunen, for taking time to train me on cleanroom and laboratory equipment, and providing an invaluable depth of knowledge accessible in a moment's notice. I would also like to acknowledge the current team members, Dr. Benjamin Lacroix, Carlos Donado, Aida Vera, Wasif Khan, Spyridon Pavlidis, Fan Cai and Outmane Lemtiri, whose new ideas and problems have helped reinforce my current knowledge as well as inspired me to further explore innovative and interesting topics. Lastly of the MIRCTech team, I would like to thank Dr. Swapan Bhattacharya for taking me under his wing at an early stage and instilling the hands-on fabrication knowledge required to propel my research activities.

I am also thankful to the members of Dr. Cressler's SiGe research group, with extra thanks to Dr. Tushar Thrivikraman. It was a wonderful experience working together and jointly developing projects into great successes. I must also add that the overlygenerous access to their laboratory equipment was immensely helpful in expediting my work for a timely graduation.

I wish to acknowledge those individuals whom I closely collaborated with throughout the many projects I have been involved. I would like to especially thank Jack Ajoian from Lockheed Martin and Bill Wilson, Ted Heath, Sean Begley and Greg Hampton from the Georgia Tech Research Institute. I believe the milestones we achieved were a direct result of these highly talented individuals and an excellent synergy of technical backgrounds.

I want to recognize Lisa Gardner and Craig Cotton for finding time to assist me despite their busy schedules. I also wish to thank the cleanroom staff at Georgia Tech for fighting a never-ending battle to keep equipment functional and maintaining a pleasant work environment amid seeming chaos.

I would like to extend my most sincere thanks to the Beta Pi chapter of Tau Kappa Epsilon Fraternity at Georgia Tech for providing a positive personal and academic influence on my life. I would not be in the position I am today without the resources provided by my fraternity brothers and Board of Trustees.

I am grateful to my friends in Georgia and Maryland for providing a social outlet that seems all too vacant in the life of a graduate student. I would like to give a special shout out to the *born ballas* and *steak night'ers* for their relentless complaints when I was too busy to hang out and for their 'positive' encouragement to shed my Peter Pan complex. I hope this dissertation serves as evidence to my excuse for sporadic absences and confirmation of my newly developed maturity.

Finally and most importantly, I would like to thank my family for believing in my determination to complete this seemingly endless feat. They have supported me emotionally and financially throughout my entire academic career. I am forever indebted to my mother, Gail Patterson, for literally giving me the clothes on my back. She has been an unwavering fan and personal confidante. I also owe my siblings, Sarah Patterson, Shannon Palik and Brian Patterson, a great deal for always taking an interest in my endeavors and offering their encouragement throughout the years. I would like to especially thank my father, Michael Patterson, and uncle, Col. Jerry Patterson, for inspiring me to excel in academia and encouraging me to follow it through to completion. I am also grateful to my beautiful girlfriend, Robyn, for her patience and support. Like a true chip off the old block, I needed someone to push me out of my comfort zone and to compel me into bringing my graduate studies to a conclusion, which she seemingly did all too easily.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTSv                                                | CKNOWLE    | ACF       |

|------------------------------------------------------------------|------------|-----------|

| IST OF TABLESx                                                   | JST OF TAI | LIST      |

| IST OF FIGURES                                                   | JST OF FIG | LIST      |

| IOMENCLATURE                                                     | IOMENCLA   | NON       |

| List of Symbolsxviii                                             | List of Sy | Ι         |

| List of Abbreviationsxix                                         | List of Ab | Ι         |

| UMMARYxxiii                                                      | UMMARY.    | SUN       |

| <u>CHAPTER</u>                                                   | CHAPTER    | <u>CH</u> |

| 1 INTRODUCTION                                                   | 1 INTRO    | ]         |

| 1.1 Background on Advanced Package Technologies2                 | 1.1        |           |

| 1.2 Radio-Frequency Substrates for System-on-Package Technology5 | 1.2        |           |

| 1.3 Background on LCP Fabrication                                | 1.3        |           |

| 2 SYSTEM-ON-PACKAGE MODULES ON LCP13                             | 2 SYST     | 2         |

| 2.1 Embedded Wire Bond Package at K <sub>a</sub> Band13          | 2.1        |           |

| 2.2 Embedded Via Interconnect Package at X Band                  | 2.2        |           |

| 2.3 Encapsulated Flip-Chip Package at X Band                     | 2.3        |           |

| 2.4 Encapsulated Flip-Chip Package at W Band                     | 2.4        |           |

| 2.5 Summary                                                      | 2.5        |           |

| 3 INTEGRATION OF BAW FILTERS ON LCP                              | 3 INTEG    |           |

| 3.1 Background on BAW Filter Devices                             | 3.1        |           |

| 3.2 C-Band Filter Package44                                      | 3.2        |           |

| 3.3 K <sub>u</sub> -Band Filter Package                          | 3.3        |           |

| 3.4 Summary58                                                    | 3.4        |           |

| 4    | X-BANI  | D ACTIVE RECEIVING PHASED-ANTENNA ARRAY                      | 59  |

|------|---------|--------------------------------------------------------------|-----|

|      | 4.1     | Antenna Array Overview                                       | 59  |

|      | 4.2     | 4 x 1 Antenna Array                                          | 63  |

|      | 4.3     | 8 x 1 Antenna Array                                          | 71  |

|      | 4.4     | 8 x 2 Antenna Array                                          | 80  |

|      | 4.5     | Summary                                                      | 90  |

| 5    | 60 GHZ  | SWITCHED-BEAM RECEIVER FRONT END                             | 92  |

|      | 5.1     | System Layout                                                | 94  |

|      | 5.2     | Integrated Components Design                                 | 96  |

|      | 5.3     | System Results                                               | 110 |

|      | 5.4     | Summary                                                      | 114 |

| 6    | CONCL   | USION                                                        | 115 |

|      | 6.1     | Contributions                                                | 115 |

|      | 6.2     | Future Work                                                  | 117 |

| 7    | PUBLIC  | CATIONS TO DATE                                              | 119 |

|      | 7.1     | Journal Publications                                         | 119 |

|      | 7.2     | Conference Publications                                      | 120 |

| APPE | NDIX A: | CONSIDERATION OF FABRICATION TOLERANCES FOR<br>LCP PLATFORMS |     |

|      | A.1     | Transmission Line Structures                                 | 123 |

|      | A.2     | Via Interconnect Structures                                  | 126 |

| APPE | NDIX B: | ITERATIVE N-PORT MATCHING NETWORK DESIGN                     | 128 |

|      | B.1     | Development of Preliminary Designs                           | 128 |

|      | B.2     | Design Verification & Feedback                               | 133 |

| REFE | RENCES  |                                                              | 135 |

| VITA |         |                                                              | 146 |

# LIST OF TABLES

| Page  |

|-------|

| 1 450 |

| Table 1.1: Comparison of material properties for RF substrates             | .7 |

|----------------------------------------------------------------------------|----|

| Table 1.2: Design rules for commercial multilayer fabrication              | 10 |

| Table 2.1: Performance summary of the packaged and unpackaged VCO          | 19 |

| Table 4.1: 4x1 antenna array comparison of half-power beamwidths @ 9.5 GHz | 70 |

| Table 4.2: 8x1 antenna array comparison of half-power beamwidths @ 9.5 GHz | 79 |

| Table 4.3: Comparison of pattern beam steering @ 9.5 GHz                   | 38 |

| Table 4.4: 8x2 antenna array comparison of half-power beamwidths @ 9.5 GHz | 39 |

# LIST OF FIGURES

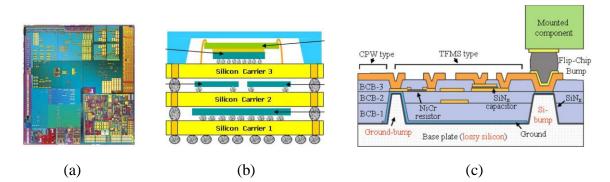

| Figure 1.1: Advanced packaging techniques: a.) system-on-chip [9], b.) stacked ICs and packages [10], c.) system-on-package [11]3        |

|------------------------------------------------------------------------------------------------------------------------------------------|

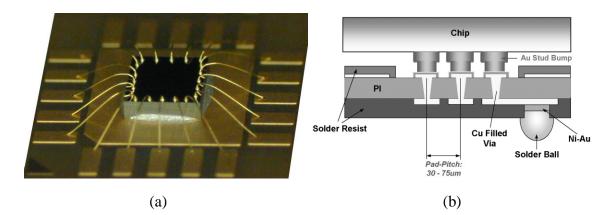

| Figure 1.2: Package interconnects utilized in IC integration: a.) wire bonds, b.) flip chip with HDIs [22]                               |

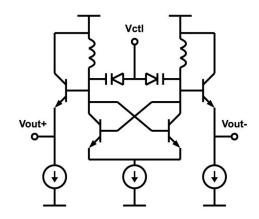

| Figure 2.1: Schematic of the negative resistance oscillator                                                                              |

| Figure 2.2: Simulation of the LCP package16                                                                                              |

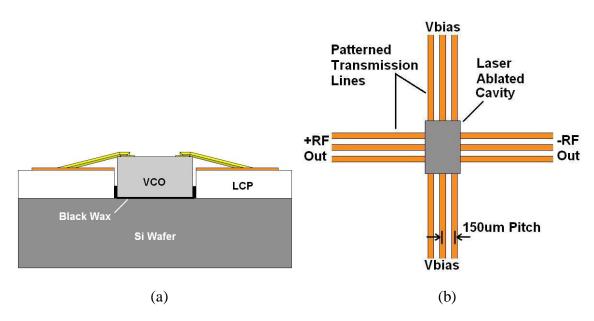

| Figure 2.3: a.) Cross-section and b.) Overhead view of the wire bond VCO package                                                         |

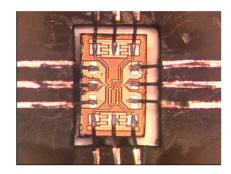

| Figure 2.4: Die photograph of the packaged oscillator17                                                                                  |

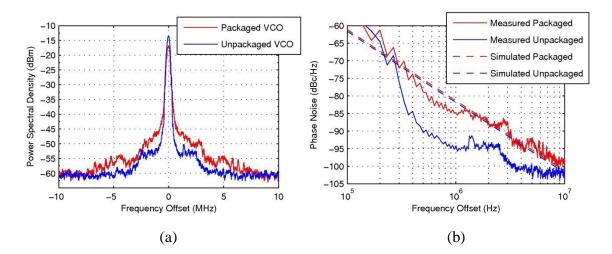

| Figure 2.5: a.) Output spectrum and b.) Phase noise of the packaged and unpackaged VCO                                                   |

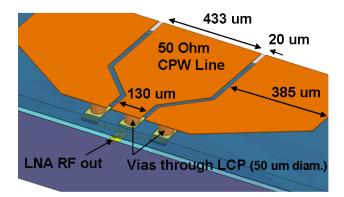

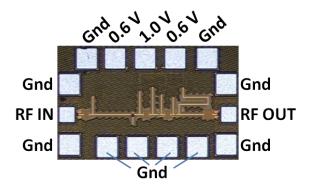

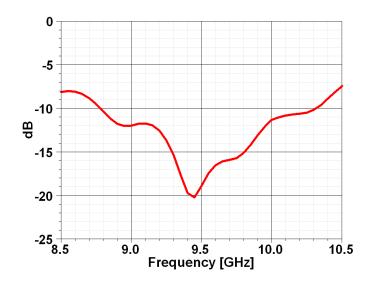

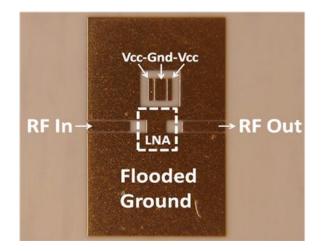

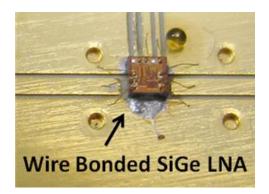

| Figure 2.6: Photo of the X-band SiGe LNA                                                                                                 |

| Figure 2.7: Simulation of the CPW transition lines with via interconnects                                                                |

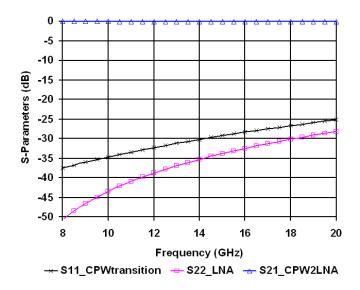

| Figure 2.8: S-parameters of simulated CPW transition lines with via interconnects22                                                      |

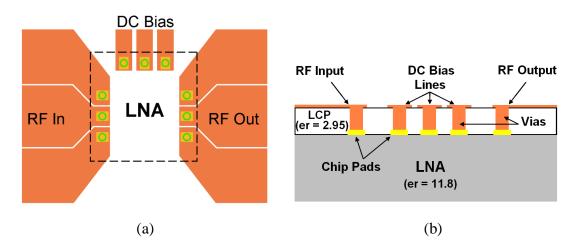

| Figure 2.9: a.) Over-head and b.) cross-section view of the package design with via interconnects and patterned CPW lines                |

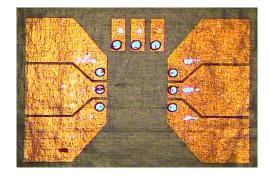

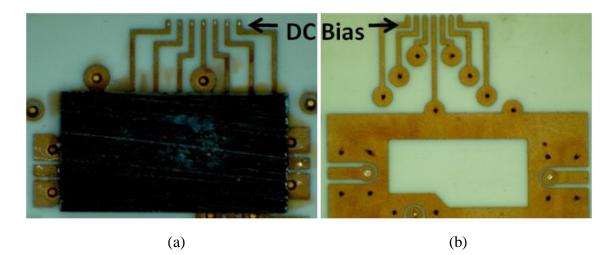

| Figure 2.10: Photograph of the packaged LNA                                                                                              |

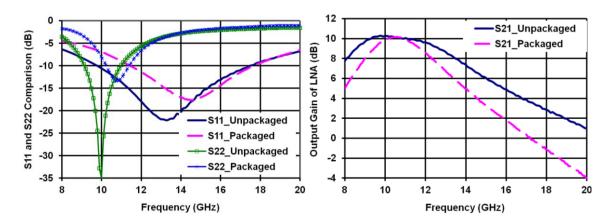

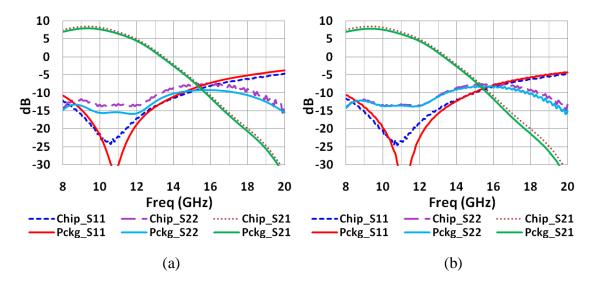

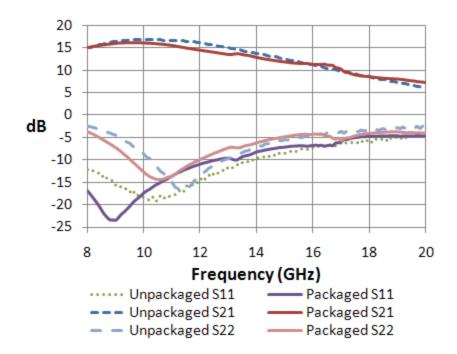

| Figure 2.11: Comparison of S-parameters before and after packaging24                                                                     |

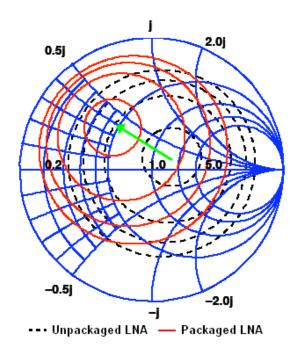

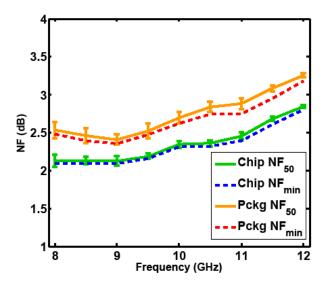

| Figure 2.12: Smith chart showing noise circles of the unpackaged and packaged LNA                                                        |

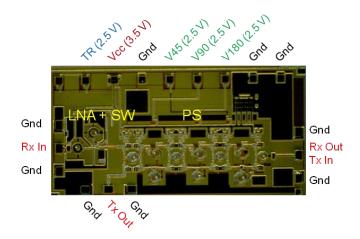

| Figure 2.13: Photo of SiGe TRM27                                                                                                         |

| Figure 2.14: Picture of Au bumps bonded on SiGe die                                                                                      |

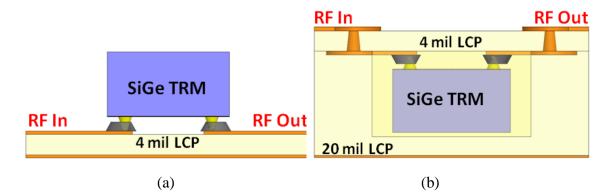

| Figure 2.15: LCP package stackup for T/R module using the a.) conventional exposed flip-chip and b.) fully embedded flip-chip approaches |

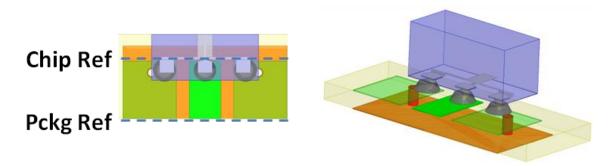

| Figure 2.16: HFSS model of the standard flip-chip transition29                                                                           |

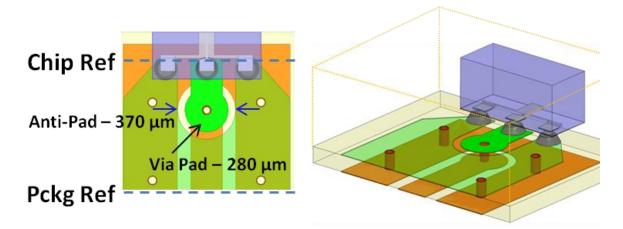

| Figure 2.17: HFSS model of embedded flip-chip transition                                                                                 |

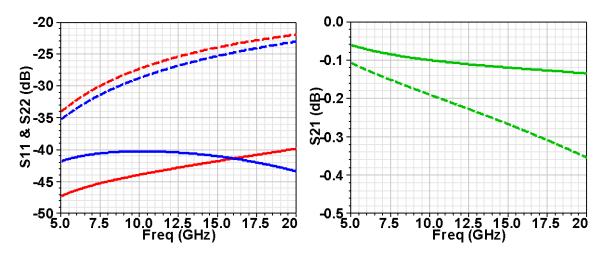

| Figure 2.18: Simulated S-parameters of the standard flip-chip package (solid) and fully embedded flip-chip package (dashed)                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.19: Fabricated and assembled a.) standard flip-chip package and b.) embedded flip-chip package                                           |

| Figure 2.20: Comparison of S-parameters before and after a.) standard flip-chip packaging, and b.) fully embedded flip-chip packaging             |

| Figure 2.21: Noise figure measurement of fully embedded flip-chip package32                                                                       |

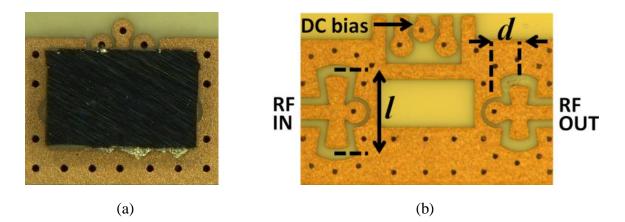

| Figure 2.22: Die photo of the W-band 45 nm SOI CMOS 3-stage power amplifier 34                                                                    |

| Figure 2.23: Picture of a gold stub bump with height of 40µm35                                                                                    |

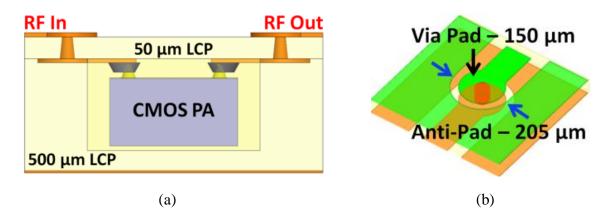

| Figure 2.24: a) LCP package stack-up for PA using a fully encapsulated flip-chip approach, b) Model of the via interconnect transition            |

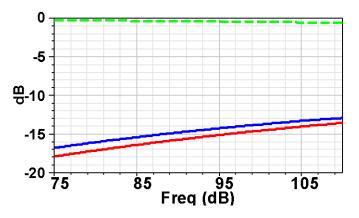

| Figure 2.25: Plot of the S11 & S22 (solid) and S21 (dashed) for the encapsulated flip-chip transition                                             |

| Figure 2.26: Model of the encapsulated flip-chip transition with a single open radial butterfly stub                                              |

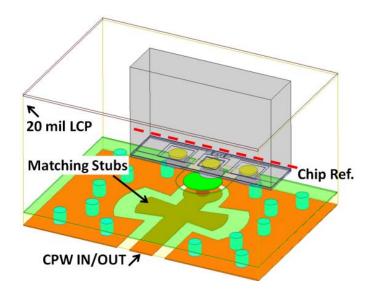

| Figure 2.27: Photos of a) the flip-chipped die on package b) the encapsulated flip-<br>chipped die in LCP with input and output matching networks |

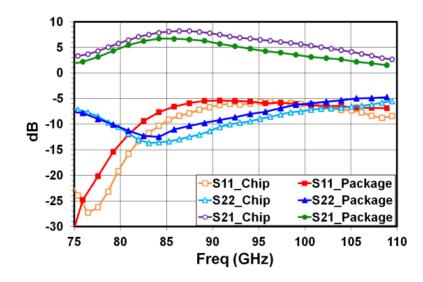

| Figure 2.28: Comparison of measured S-parameters before and after encapsulated flip-chip package without matching networks                        |

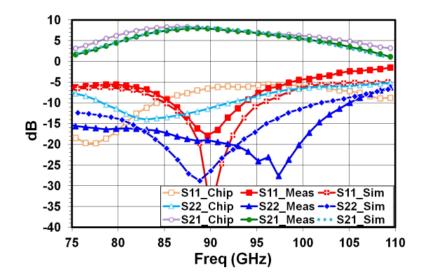

| Figure 2.29: Comparison of S-parameters before and after encapsulated flip-chip package with matching network                                     |

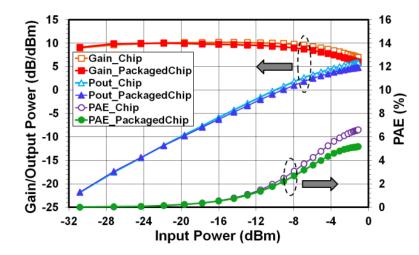

| Figure 2.30: Comparison of PA output power before and after fully encapsulated flip-chip package with matching network                            |

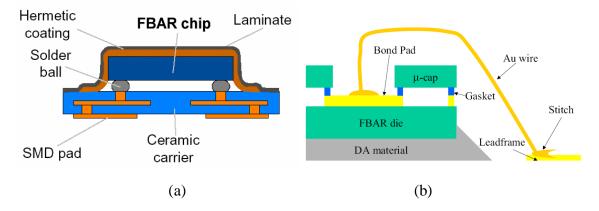

| Figure 3.1: Conventional package configurations for BAW filters using a.) ceramic packaging [66] and b.) wafer-level packaging [67]43             |

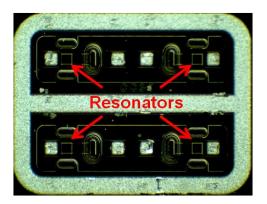

| Figure 3.2: Picture of the C-band BAW die                                                                                                         |

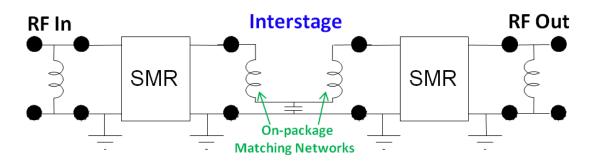

| Figure 3.3: Schematic of single channel filter showing necessary matching for each SMR                                                            |

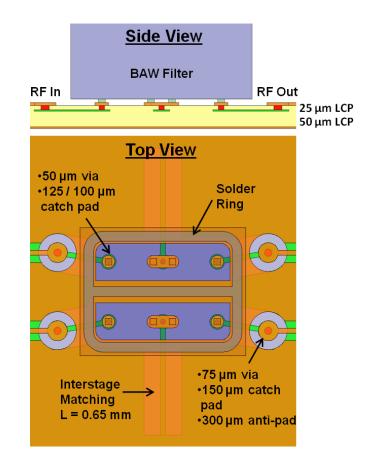

| Figure 3.4: Layout of via interconnects for dual-channel filter package46                                                                         |

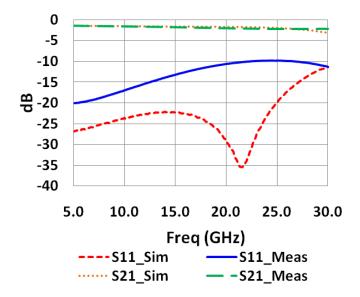

| Figure 3.5: Measured and simulated results for microstrip thru fabricated on the BAW substrate and packaged on LCP with the 3-D transition        |

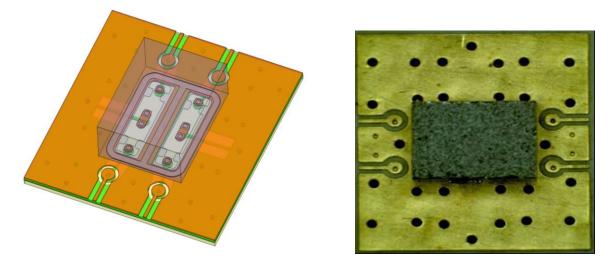

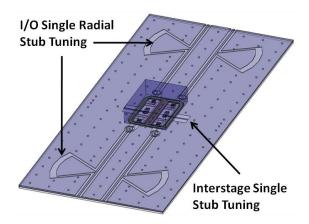

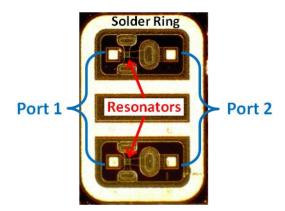

| Figure 3.6: Model and photo of the C-band BAW filter with interstage matching but without input/output matching networks                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

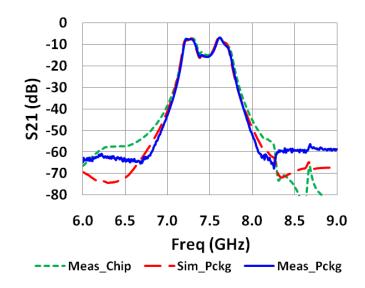

| Figure 3.7: Simulated and measured results (on-chip and on-package) for the C-<br>band BAW filter without input/output matching networks                                             |

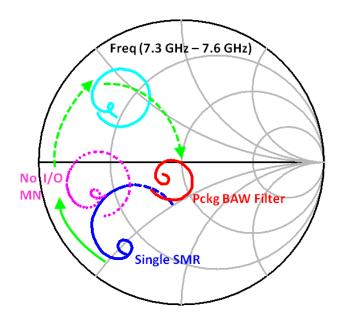

| Figure 3.8: Smith chart illustrating the progression of the unmatched impedance on die to the matched filter response on package                                                     |

| Figure 3.9: Model of the C-band filter package with integrated matching networks49                                                                                                   |

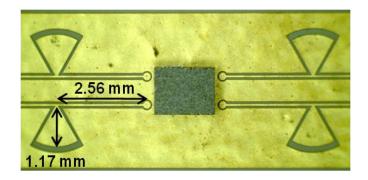

| Figure 3.10: Photo of the C-band BAW filter packaged on the multilayer LCP substrate                                                                                                 |

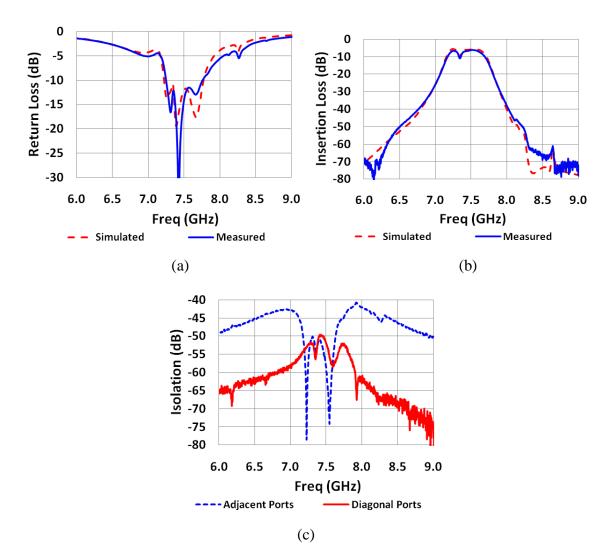

| Figure 3.11: Simulated and measured on-package a.) return loss and b.) insertion<br>loss of the matched filter; c.) Isolation measurement between channels of<br>the packaged filter |

| Figure 3.12: Picture of the dual-channel Ku-band BAW die                                                                                                                             |

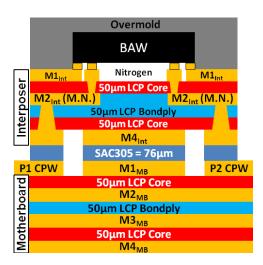

| Figure 3.13: Material stack-up of the packaged and mounted BAW filter interposer<br>on motherboard                                                                                   |

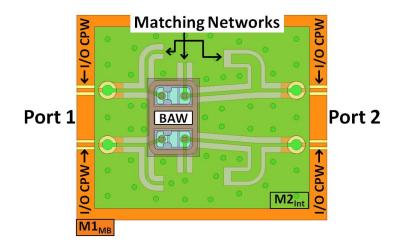

| Figure 3.14: Top view showing the embedded matching networks on layer M2 of the interposer, and the I/O CPW lines on the motherboard                                                 |

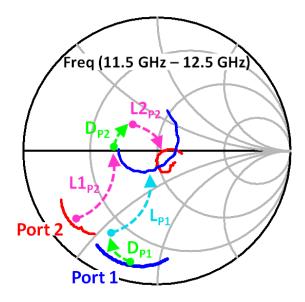

| Figure 3.15: Smith chart illustrating the progression of the unmatched impedance<br>on die to the matched filter response on package                                                 |

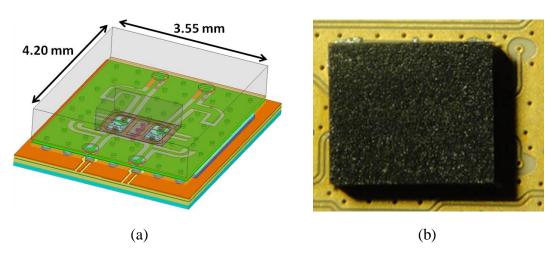

| Figure 3.16: a) Full simulated package with matching networks, b) Picture of the packaged BAW filter interposer mounted on motherboard                                               |

| Figure 3.17: Comparison of the simulated and measured on-package performance<br>of the Ku-band BAW filter                                                                            |

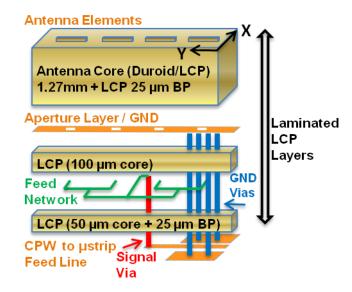

| Figure 4.1: Stack up of multilayer antenna array showing only one column with four elements                                                                                          |

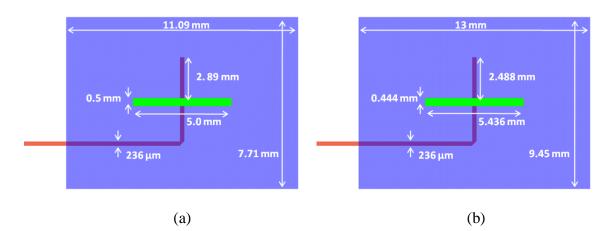

| Figure 4.2: Dimensions of each aperture coupled patch for the a.) 4x1 and 8x1<br>antenna array using an LCP antenna layer and b.) 8x2 antenna array<br>using a Duroid antenna layer  |

| Figure 4.3: HFSS model of passive 4x1 antenna array64                                                                                                                                |

| Figure 4.4: Simulated S11 plot of passive 4x1 antenna array65                                                                                                                        |

| Figure 4.5: Layout for the packaged LNA                                                                                                                                              |

| Figure 4.6: Comparison plot of the unpackaged and packaged LNA                                                                                                                       |

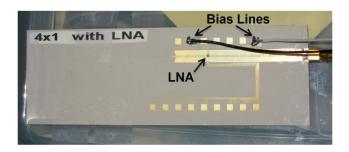

| Figure 4.7: Picture of the packaged LNA on antenna array.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 67                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

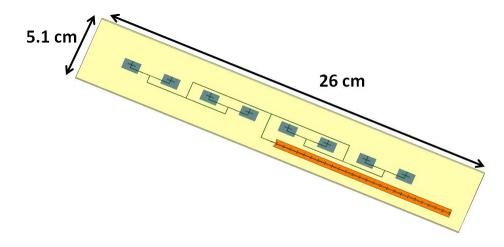

| Figure 4.8: Picture of the antenna array with integrated LNA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68                               |

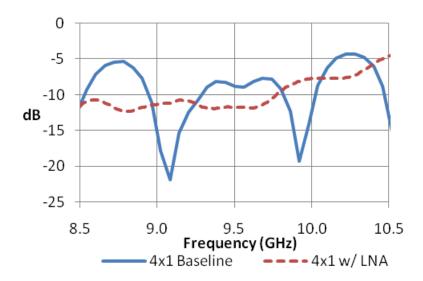

| Figure 4.9: S11 plot for the baseline and packaged LNA 4x1 antenna array.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 68                               |

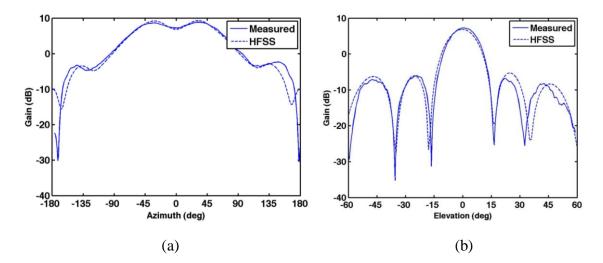

| Figure 4.10: Measured a.) E-Plane and b.) H-Plane at 9.5 GHz of the baseline 4x1 array.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 69                               |

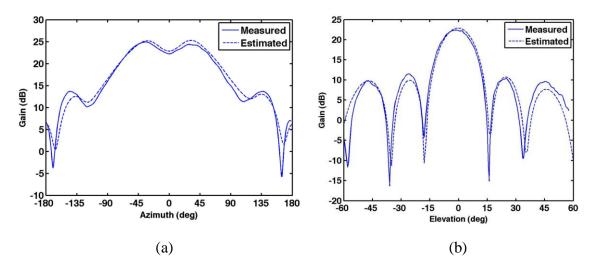

| Figure 4.11: Measured a.) E-Plane and b.) H-Plane at 9.5 GHz of the 4x1 array with integrated LNA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70                               |

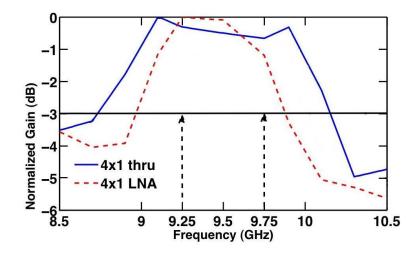

| Figure 4.12: Normalized gain plot comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70                               |

| Figure 4.13: Model of the 8x1 antenna array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71                               |

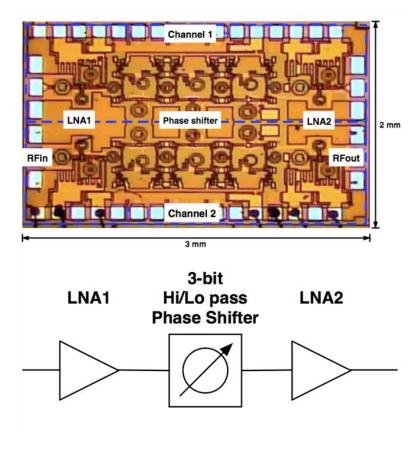

| Figure 4.14: Picture and schematic of the SiGe phase shifter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 72                               |

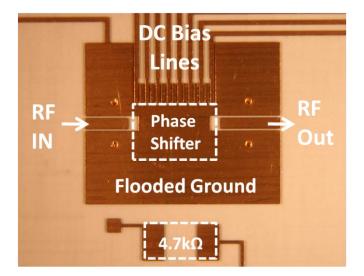

| Figure 4.15: Layout for the packaged phase shifter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73                               |

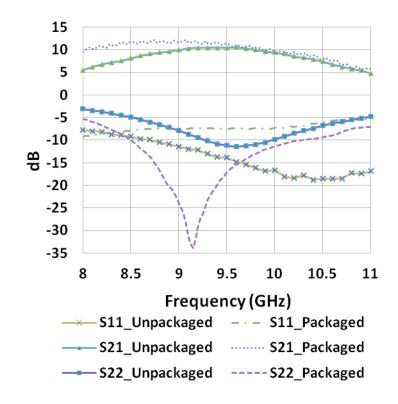

| Figure 4.16: Comparison of S-parameters for the unpackaged and packaged phase shifter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74                               |

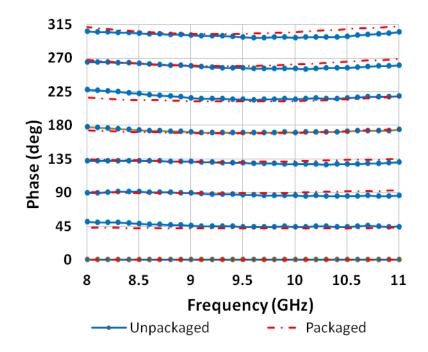

| Figure 4.17: Comparison of unpackaged and packaged phase shifter for each phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7 4                              |

| state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | /4                               |

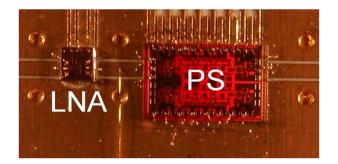

| Figure 4.18: Picture of the packaged SiGe LNA and PS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75                               |

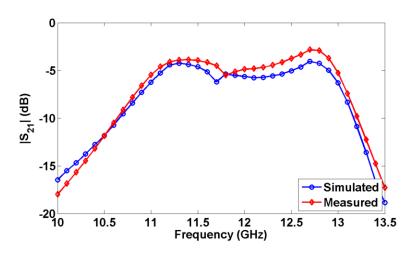

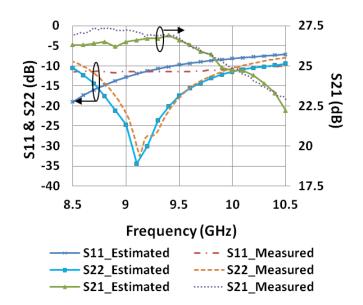

| Figure 4.18: Picture of the packaged SiGe LNA and PS<br>Figure 4.19: Comparison of measured and simulated S-parameters for LNA and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 75<br>76                         |

| <ul><li>Figure 4.18: Picture of the packaged SiGe LNA and PS</li><li>Figure 4.19: Comparison of measured and simulated S-parameters for LNA and phase shifter packaged in series on LCP</li><li>Figure 4.20: Front and back picture of the assembled 8x1 antenna array with</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                | 75<br>76<br>76                   |

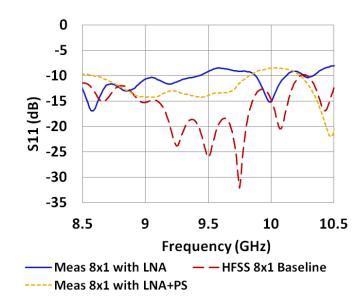

| <ul> <li>Figure 4.18: Picture of the packaged SiGe LNA and PS</li> <li>Figure 4.19: Comparison of measured and simulated S-parameters for LNA and phase shifter packaged in series on LCP</li> <li>Figure 4.20: Front and back picture of the assembled 8x1 antenna array with integrated LNA and PS.</li> <li>Figure 4.21: Return loss of the simulated baseline array and measured active</li> </ul>                                                                                                                                                                                                                                                                                               | 75<br>76<br>76<br>77             |

| <ul> <li>Figure 4.18: Picture of the packaged SiGe LNA and PS</li> <li>Figure 4.19: Comparison of measured and simulated S-parameters for LNA and phase shifter packaged in series on LCP</li> <li>Figure 4.20: Front and back picture of the assembled 8x1 antenna array with integrated LNA and PS.</li> <li>Figure 4.21: Return loss of the simulated baseline array and measured active arrays.</li> </ul>                                                                                                                                                                                                                                                                                       | 75<br>76<br>76<br>77<br>78       |

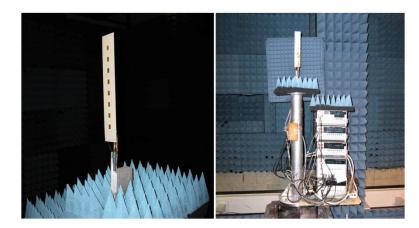

| <ul> <li>Figure 4.18: Picture of the packaged SiGe LNA and PS</li> <li>Figure 4.19: Comparison of measured and simulated S-parameters for LNA and phase shifter packaged in series on LCP</li> <li>Figure 4.20: Front and back picture of the assembled 8x1 antenna array with integrated LNA and PS</li> <li>Figure 4.21: Return loss of the simulated baseline array and measured active arrays</li> <li>Figure 4.22: Antenna chamber setup of 8x1 array with SiGe LNA and PS</li> <li>Figure 4.23: Measured a.) E-Plane and b.) H-Plane at 9.5 GHz of the 8x1 array</li> </ul>                                                                                                                    | 75<br>76<br>76<br>77<br>78       |

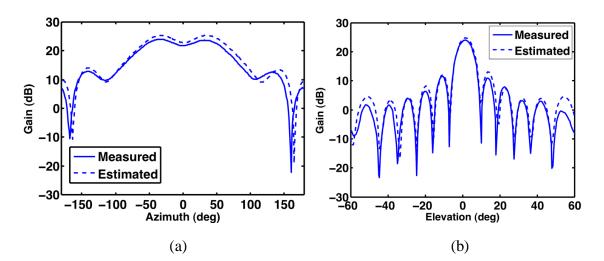

| <ul> <li>Figure 4.18: Picture of the packaged SiGe LNA and PS</li> <li>Figure 4.19: Comparison of measured and simulated S-parameters for LNA and phase shifter packaged in series on LCP</li> <li>Figure 4.20: Front and back picture of the assembled 8x1 antenna array with integrated LNA and PS.</li> <li>Figure 4.21: Return loss of the simulated baseline array and measured active arrays</li> <li>Figure 4.22: Antenna chamber setup of 8x1 array with SiGe LNA and PS.</li> <li>Figure 4.23: Measured a.) E-Plane and b.) H-Plane at 9.5 GHz of the 8x1 array with integrated LNA only.</li> <li>Figure 4.24: Measured a.) E-Plane and b.) H-Plane at 9.5 GHz of the 8x1 array</li> </ul> | 75<br>76<br>77<br>78<br>78<br>78 |

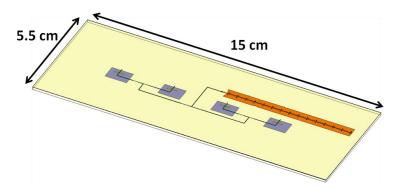

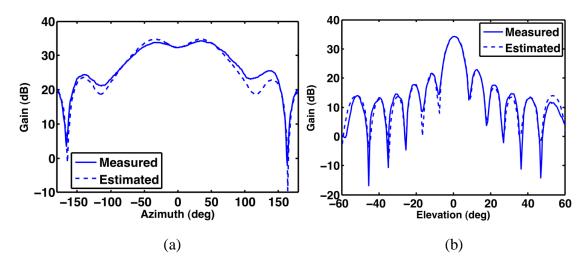

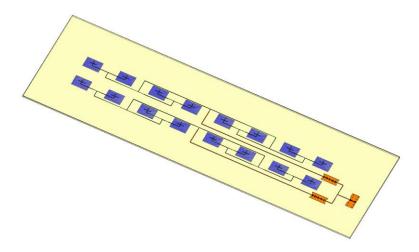

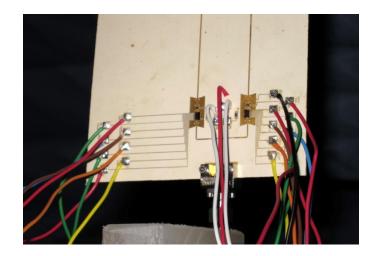

| Figure 4.27: Picture of the packaged LNA and phase shifter on the 8x2 antenna array                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

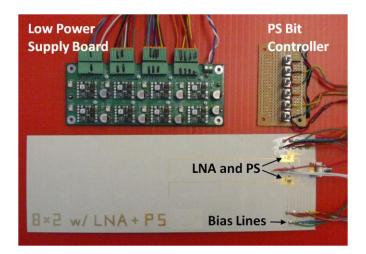

| Figure 4.28: Picture of the assembled antenna array with low power supply board<br>and phase shifter bit controller                                                                          |

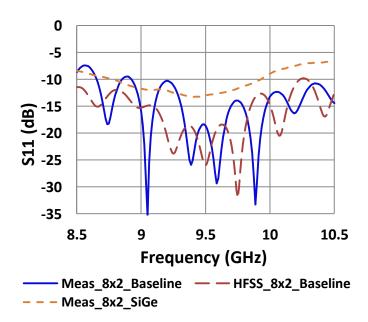

| Figure 4.29: S11 plot of the simulated and measured 8x2 antenna arrays                                                                                                                       |

| Figure 4.30: Picture of the 8x2 antenna array being measured in the anechoic chamber                                                                                                         |

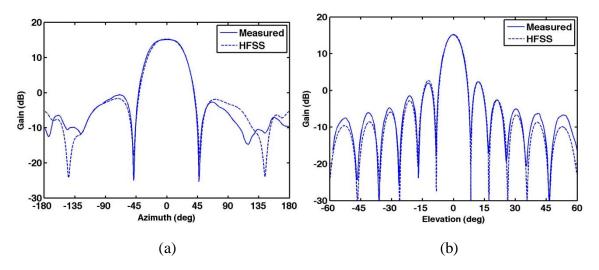

| Figure 4.31: Measured a.) E-Plane and b.) H-Plane at 9.5 GHz of the 8x2 baseline antenna array                                                                                               |

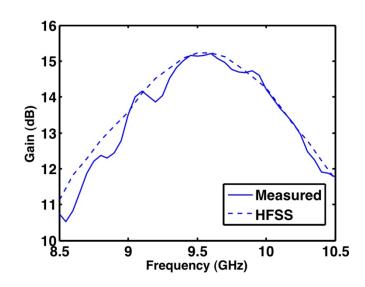

| Figure 4.32: Gain versus frequency of the 8x2 baseline antenna array                                                                                                                         |

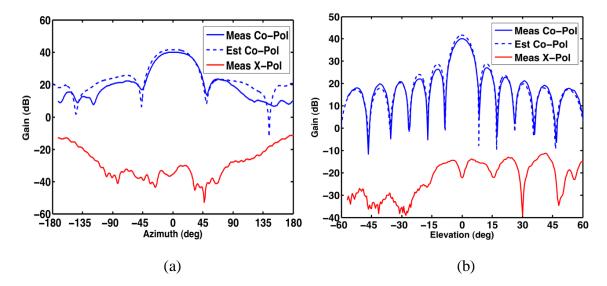

| Figure 4.33: Measured a.) E-Plane and b.) H-Plane at 9.5 GHz for the 8x2 antenna array with packaged SiGe LNA and phase shifter                                                              |

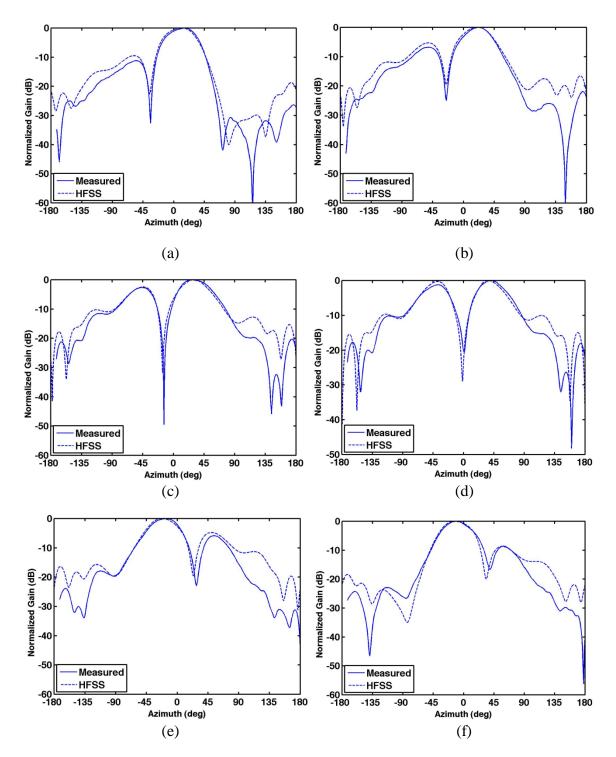

| Figure 4.34: Normalized E-plane at 9.5 GHz of the 8x2 antenna array with a.) 44 degrees, b.) 87 degrees, c.) 129 degrees, d.) 170 degrees, e.) 257 degrees, and f.) 299 degrees phase change |

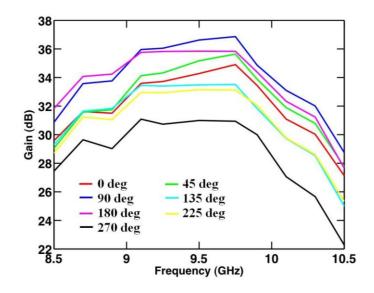

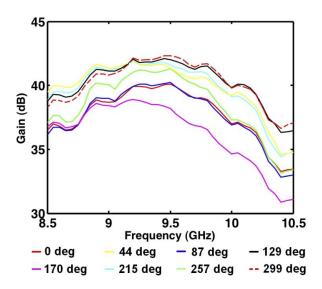

| Figure 4.35: Gain versus frequency of the 8x2 antenna array for all phase changes 88                                                                                                         |

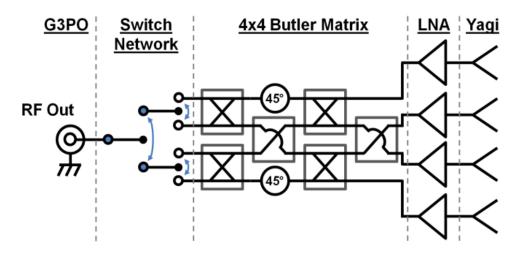

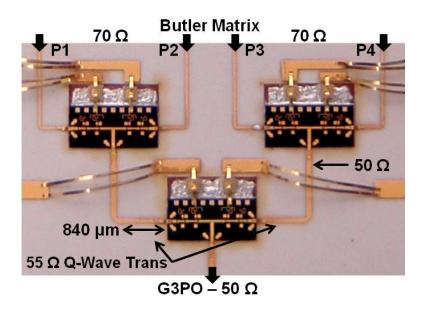

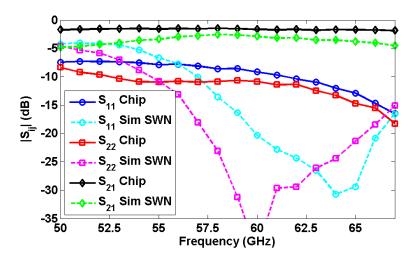

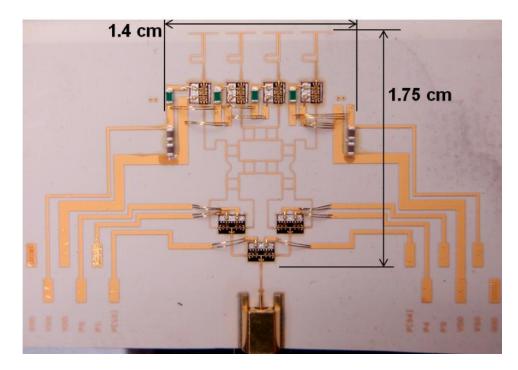

| Figure 5.1: Schematic layout of the switched-beam array95                                                                                                                                    |

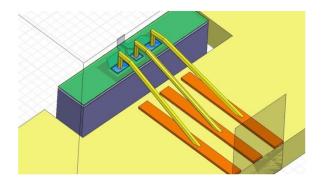

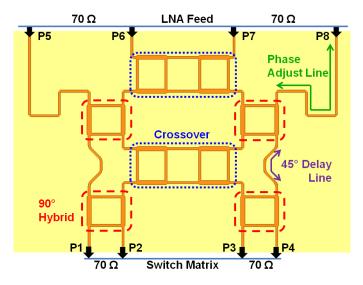

| Figure 5.2: Model of the 4x4 Butler matrix97                                                                                                                                                 |

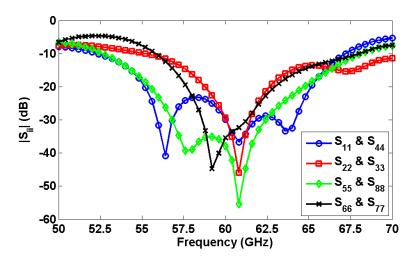

| Figure 5.3: Simulated reflection coefficient for each port of the Butler matrix                                                                                                              |

| Figure 5.4: Simulated transmission coefficients of the Butler matrix for a.) P1& P4<br>and b.) P2 & P3                                                                                       |

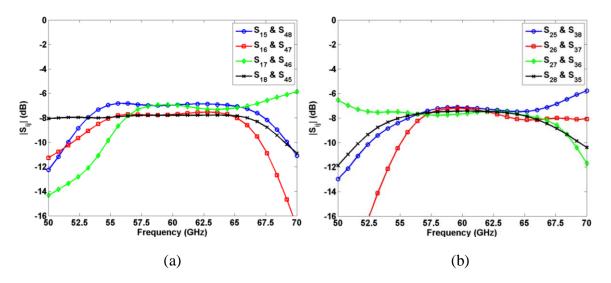

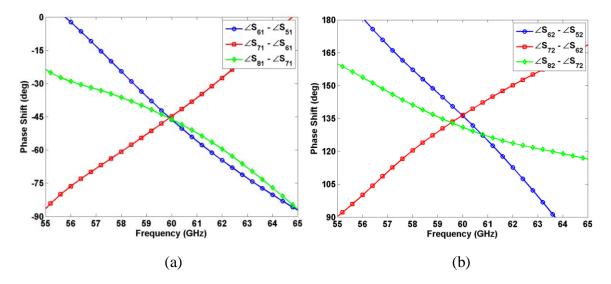

| Figure 5.5: Simulated phase shift between adjacent antenna elements for a.) P1 and b.) P2                                                                                                    |

| Figure 5.6: Model of the single antenna element illustrating feature dimensions 100                                                                                                          |

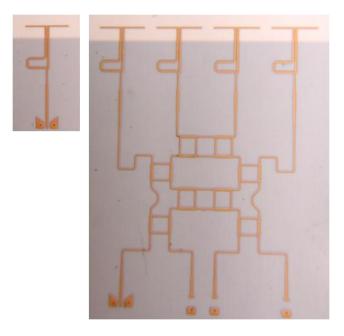

| Figure 5.7: Fabricated a.) single Yagi element and b.) 4x1 array with Butler matrix101                                                                                                       |

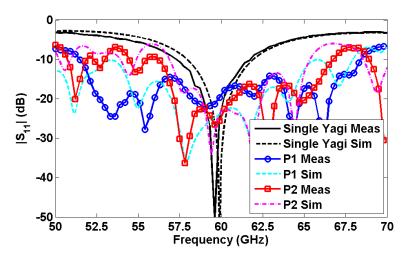

| Figure 5.8: Simulated and measured S11 of the single dipole antenna and the 4x1 phased array with incorporated Butler matrix                                                                 |

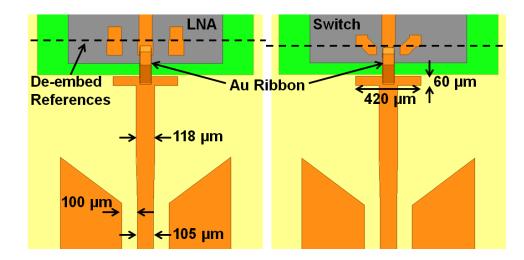

| Figure 5.9: Simulated package of the LNA and SPDT switch assuming 50 $\Omega$ on-<br>die matching                                                                                            |

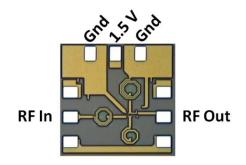

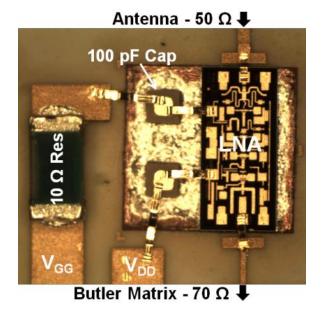

| Figure 5.10: Picture of the packaged LNA integrated on the antenna                                                                                                                           |

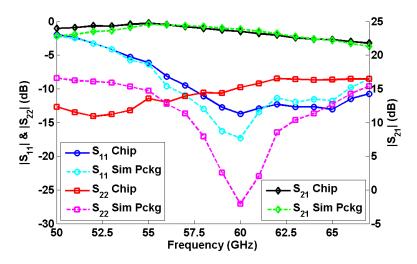

| Figure 5.11: Comparison plot of the measured and simulated LNA package                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.12: Picture of the packaged switch network integrated on the antenna                                                                                                               |

| Figure 5.13: Comparison plot of the measured and simulated switch package                                                                                                                   |

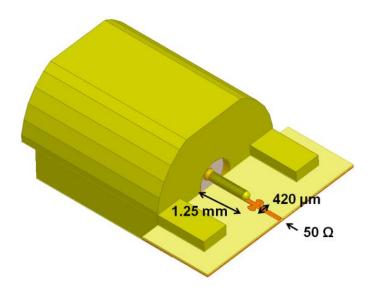

| Figure 5.14: Simulated G3PO connector modeled with impedance tuning stub 108                                                                                                                |

| Figure 5.15: Fabricated and assembled 4x1 active receiving switched-beam array 109                                                                                                          |

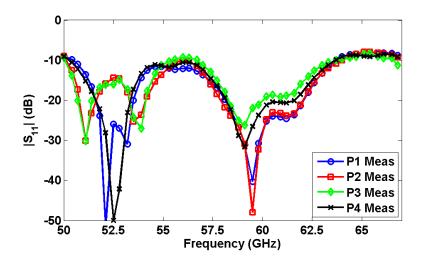

| Figure 5.16: Measured S11 for each beam state of the 4x1 active switched-beam array                                                                                                         |

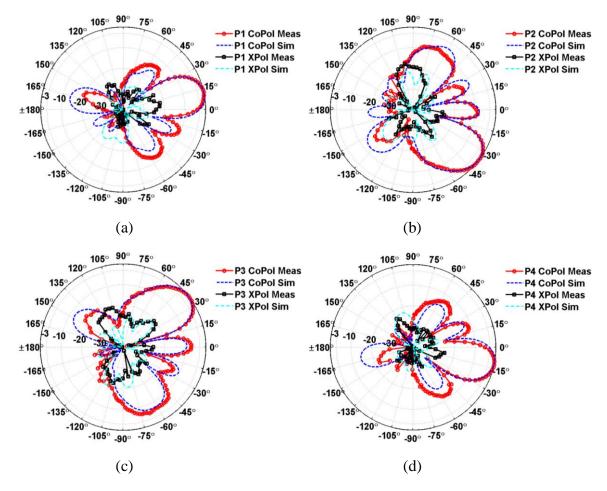

| Figure 5.17: Normalized E-Plane of co-polarization and cross-polarization at 60 GHz for each beam scan in dB                                                                                |

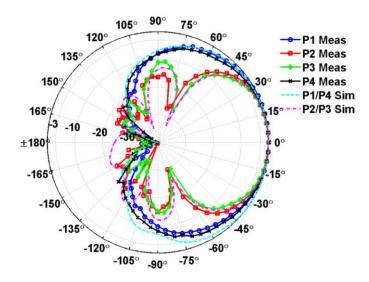

| Figure 5.18: Normalized H-Plane at 60 GHz for each beam scan in dB112                                                                                                                       |

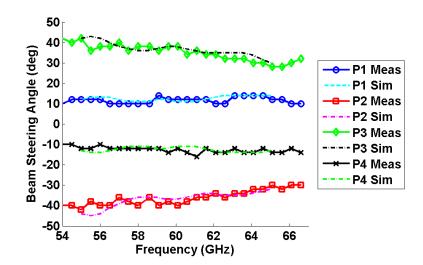

| Figure 5.19: E-plane beam steering versus frequency of the 4x1 active switched-beam array                                                                                                   |

| Figure 5.20: Gain versus frequency of the 4x1 active switched-beam array113                                                                                                                 |

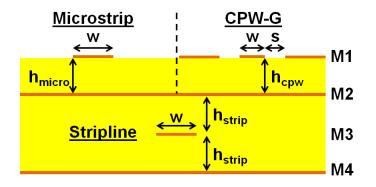

| Figure A.1: Cross-section of transmission line structures on CSLP stack-up using LCP                                                                                                        |

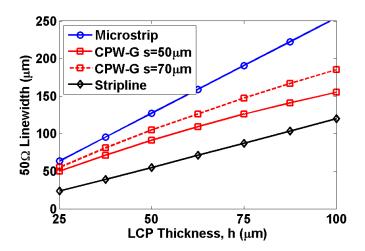

| Figure A.2: Calculated 50 $\Omega$ line width for each transmission line structure                                                                                                          |

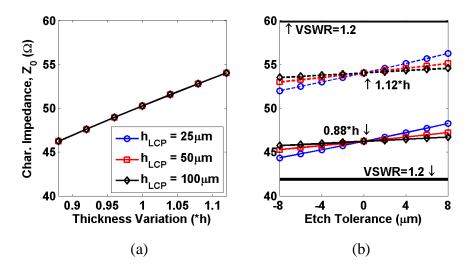

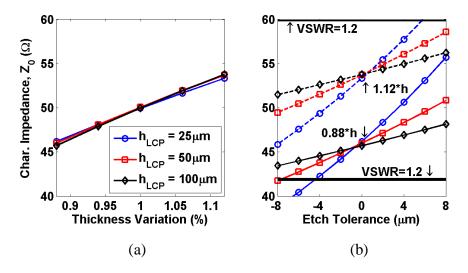

| Figure A.3: Microstrip transmission line characteristic impedance for a) substrate thickness variations, b) and worst-case etch tolerance variations                                        |

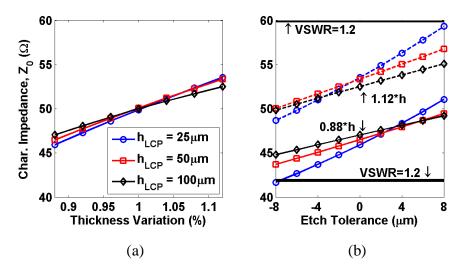

| Figure A.4: CPW-G transmission line characteristic impedance with fixed line gap,<br>$s = 50 \mu m$ , for a) substrate thickness variations, b) and worst-case etch<br>tolerance variations |

| Figure A.5: Stripline characteristic impedance for a) substrate thickness variations,<br>b) and worst-case etch tolerance variations                                                        |

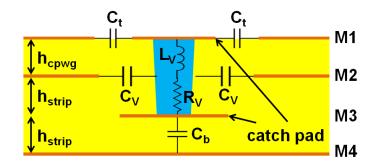

| Figure A.6: Cross-section of M1-M3 via transition and model parasitics                                                                                                                      |

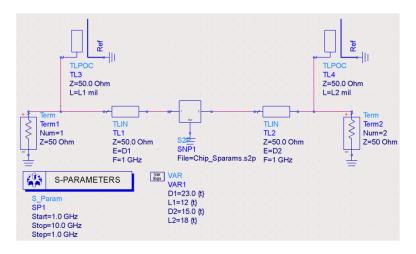

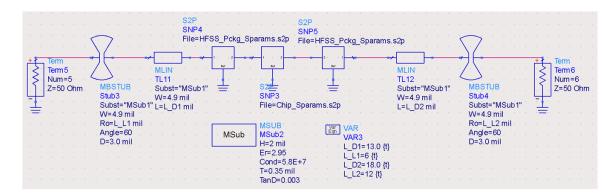

| Figure B.1: ADS schematic of ideal MN components with device S-parameter block                                                                                                              |

| Figure B.2: ADS schematic of lossy package with butterfly stub MN components130                                                                                                             |

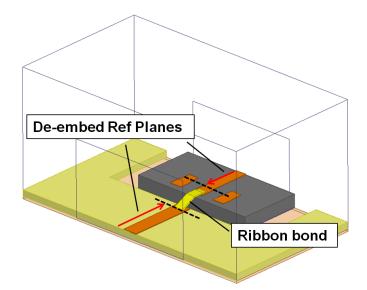

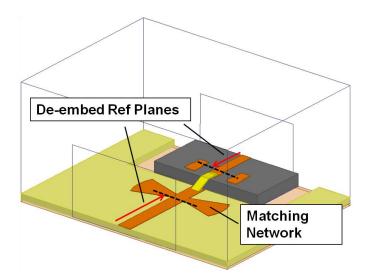

| Figure B.3: HFSS model of the packaged device without MN components                                                                                                                         |

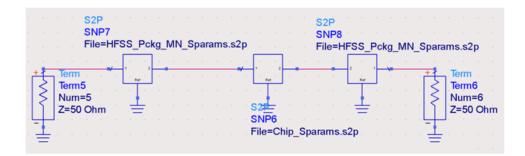

| Figure B.4: ADS schematic of lossy package with HFSS extracted S-parameters for package interconnects                                                                                       |

| Figure B.5: HFSS model of the packaged device with MN components          | 132 |

|---------------------------------------------------------------------------|-----|

| Figure B.6: ADS Schematic block simulation of extracted S-parameters from |     |

| HFSS modeled MNs.                                                         | 133 |

## NOMENCLATURE

## List of Symbols

| Angstrom (1 x 1           | $0^{-10}$ m)         |

|---------------------------|----------------------|

| Degree                    | Celsius              |

| Relative Perm             | nittivity            |

| Micr                      | rometer              |

| Mic                       | rofarad              |

|                           | Ohm                  |

| Condu                     | uctivity             |

|                           | Amp                  |

| Cen                       | timeter              |

| Ι                         | Decibel              |

| Decibel referenced to 1 m | illiwatt             |

| Gi                        | gahertz              |

|                           | Hertz                |

| Ki                        | ilohertz             |

|                           | Kelvin               |

|                           | Meter                |

| Mil                       | llimeter             |

| Μ                         | lilliwatt            |

| Meg                       | gahertz              |

|                           | Ounce                |

| Pounds Pe                 | er Inch <sup>2</sup> |

| S     | Siemens                  |

|-------|--------------------------|

| tanδ  | Loss tangent             |

| V     | Volt                     |

| W     | Watt                     |

| $Z_0$ | Characteristic Impedance |

### List of Abbreviations

| 2-D    | Two Dimensional                                 |

|--------|-------------------------------------------------|

| 3-D    | Three Dimensional                               |

| 3G     | Third Generation                                |

| Ag     | Silver                                          |

| ADS    | Advanced Design System                          |

| AoC    | Antenna on Chip                                 |

| Au     | Gold                                            |

| AUT    | Antenna Under Test                              |

| AWG    | American Wire Gauge                             |

| BAW    | Bulk Acoustic Waveguide                         |

| BCB    | Benzocyclobutene                                |

| BFN    | Beam Forming Network                            |

| BiCMOS | Bipolar Complementary Metal Oxide Semiconductor |

| BP     | Bondply                                         |

| BT     | Bismaleimide-Triazine                           |

| BW     | Bandwidth                                       |

| C4     | Controlled Collapse Chip Connection             |

| C band | 4 GHz to 8 GHz                                  |

| СММ    | Coordinate Measuring Machine                    |

| CMOS   | Complementary Metal Oxide Semiconductor           |

|--------|---------------------------------------------------|

| CPS    | Coplanar Strip                                    |

| CPW    | Coplanar Waveguide                                |

| CPW-G  | Grounded Coplanar Waveguide                       |

| CSLP   | Chip Scale Level Package                          |

| CTE    | Coefficient of Thermal Expansion                  |

| Cu     | Copper                                            |

| DC     | Direct Current                                    |

| DUT    | Device Under Test                                 |

| ESD    | Electrostatic Discharge                           |

| FOM    | Figure of Merit                                   |

| FR-4   | Flame Retardant 4                                 |

| GaAs   | Gallium Arsenide                                  |

| GPS    | Global Position System                            |

| GSG    | Ground-Signal-Ground                              |

| GSGSG  | Ground-Signal-Ground-Signal-Ground                |

| HBT    | Heterojunction Bipolar Transistor                 |

| HDI    | High Density Interconnect                         |

| HFSS   | High Frequency Structure Simulator                |

| HTCC   | High Temperature Co-Fired Ceramic                 |

| IC     | Integrated Circuit                                |

| IEEE   | Institute of Electrical and Electronics Engineers |

| I/O    | Input/Output                                      |

| IPA    | Isopropyl Alcohol                                 |

| K band | 18 GHz to 26.5 GHz                                |

| K <sub>a</sub> band | 26.5 GHz to 40 GHz               |

|---------------------|----------------------------------|

| K <sub>u</sub> band | 12 GHz to 18 GHz                 |

| KrF                 | Krypton Fluoride                 |

| LCP                 | Liquid Crystal Polymer           |

| LNA                 | Low-Noise Amplifier              |

| LTCC                | Low Temperature Co-Fired Ceramic |

| МСМ                 | Multi-Chip Module                |

| Мо                  | Molybdenum                       |

| NF                  | Noise Figure                     |

| NHA                 | Next Higher Assembly             |

| Ni                  | Nickel                           |

| P <sub>1dB</sub>    | 1 dB Power Compression Point     |

| PA                  | Power Amplifier                  |

| PAE                 | Power-Added Efficiency           |

| РСВ                 | Printed Circuit Board            |

| Pout                | Output Power                     |

| PS                  | Phase Shifter                    |

| P <sub>sat</sub>    | Saturated Output Power           |

| PTFE                | Polytetrafluoroethylene          |

| Q                   | Quality                          |

| RIE                 | Reactive Ion Etching             |

| RF                  | Radio Frequency                  |

| RMS                 | Root Mean Square                 |

| RRP                 | Risk-Reduction Panel             |

| SiC                 | Silicon Carbide                  |

|                     |                                  |

| SiGe         | Silicon Germanium                      |

|--------------|----------------------------------------|

| SIP          | Stacked Integrated Circuit and Package |

| SIW          | Substrate Integrated Waveguide         |

| SMR          | Surface Mounted Resonator              |

| Sn           | Tin                                    |

| SoC          | System on Chip                         |

| SoP          | System on Package                      |

| S-Parameters | Scattering Parameters                  |

| SPDT         | Single Pole Double Throw               |

| T/R          | Transmit/Receive                       |

| Ti           | Titanium                               |

| TRM          | Transmit/Receive Module                |

| TSV          | Through-Silicon Via                    |

| UV           | Ultra Violet                           |

| VCO          | Voltage-Controlled Oscillator          |

| V band       | 55 GHz to 75 GHz                       |

| VSWR         | Voltage Standing Wave Ratio            |

| W            | Tungsten                               |

| W band       | 75 GHz to 110 GHz                      |

| X band       | 8 GHz to 12 GHz                        |

### SUMMARY

In the past decade, there has been an increased interest in low-cost, low-power, high data rate wireless systems for both commercial and defense applications. Some of these include air defense systems, remote sensing radars, and communication systems that are used for unmanned aerial vehicles, ground vehicles, and even the individual consumer. All of these applications require state-of-the-art technologies to push the limits on several design factors such as functionality, weight, size, conformity, and performance while remaining cost effective. There are several potential solutions to accomplish these objectives and a highly pursued path is through the utilization of advanced integrated system platforms with high frequency, versatile, multilayered materials.

Many new materials are being explored for advanced package design that are thinner, lighter, and have better high frequency characteristics that make a wider range of applications possible. Liquid Crystal Polymer (LCP) has been established as an excellent microwave organic dielectric due to its key performance and packaging advantages. It has been shown that LCP is a prime candidate for integration of active circuits in 2-D and 3-D packaging configurations. Additionally, its large processing format and compatibility with the build-up process in a printed circuit board foundry allows for a smooth transition to commercialization of products.

This work intends to explore advanced 3-D integration for state-of-the-art components in wireless systems using LCP multilayer organic platforms. Several packaging techniques are discussed that utilize the inherent benefits of this material. Wire bond, via interconnect, and flip-chip packages are implemented at RF and millimeter-wave (mm-wave) frequencies to explore the benefits of each in terms of convenience, reliability, cost, and performance. These techniques are then utilized for the

xxiii

demonstration of bulk acoustic waveguide (BAW) filter applications and for the realization of highly integrated phased-array antenna systems.

A combination of flip-chip and via interconnects are applied to the integration of state-of-the-art BAW filter technology with LCP packaging. The hermetic nature of LCP is utilized to prevent moisture absorption from degrading RF performance by use of a solder ring die attachment. Additionally, via interconnects route the signal directly from the chip interface to matching networks implemented on package for a 50  $\Omega$  impedance matching. For the first time ever, this packaging approach is demonstrated at C-band and K<sub>u</sub>-band frequencies.

This work also investigates the possible applications for LCP platforms where the benefits of this material can be exploited for highly integrated wireless antenna systems. Active and passive components are incorporated on LCP using a system-on-package approach to improve performance and enhance capability of the antenna. Wire bond interconnects are utilized as a convenient, low-cost packaging solution, ideal for prototype development. The demonstration of several prototype antennas at X-band and V-band frequencies provide substantial evidence as to the broad range of potential applications for LCP.

## CHAPTER 1

## **INTRODUCTION**

The current pace of RF technology development and innovation is in response to market pressures for miniaturization, with increased functionality at lower costs. This rapidly growing facet of the electronics industry is especially apparent in wireless systems. In the last decade, there has been substantial growth in communication devices, anti-collision radars, remote sensing, and satellite communication and navigation systems. Many of these technology advancements have now become fundamental components of day-to-day operation for the average consumer. These include global positioning system (GPS) devices (1 GHz to 2 GHz), smart phones (0.6 GHz to 2.7 GHz), automobile collision avoidance radars (24 GHz and 77 GHz), and satellite television (10 GHz to 13 GHz).

Portable wireless devices have experienced a boom in consumer popularity with an overwhelming necessity for instant data, voice, and video access. This spark in demand has been met by the electronics industry with new and innovative technologies that push the current state-of-the-art performance and functionality in a cost-effective manner. For example, in 2001, third-generation (3G) mobile telecommunication networks gave birth to wireless internet access, video calling and media streaming to cell phones, personal digital assistants, and laptop computers. Since then, smart phones, iPads, and tablet personal computers have been developed that are not only smaller than their predecessors in size and profile, but also packed with additional functionality, such as multitask software applications, GPS, high-definition photo/video cameras, and data storage. With the growth in smart phone sales up to over 303 million units in 2010 and a forecasted 49 % growth in sales for 2011, there is a clear financial interest driving the RF component in this market [1]. In addition to packed functionality, the electronics industry is coming up with innovative ways to replace current radar and communication systems with ones that are lighter, lower power, and more adaptable [2]. In the past, these have consisted of heavy, bulky, and expensive waveguide feed networks and antenna arrays [3]-[5]. This type of system is costly and impractical for applications where mobility is required. Added weight and bulk to airborne and ground vehicles reduces maneuverability, increases air drag, and raises gas consumption. An innovative way to eliminate a large portion of the weight, size, and cost is by utilizing microstrip technology on lightweight, flexible, high frequency substrates.

Products of this complexity require advanced RF designs and highly integrated system platforms that can be manufactured at low costs. Hundreds of electronic components must be seamlessly interconnected into a low form factor device, which presents an enormous challenge from an electrical and mechanical standpoint. In addition to dense complex interconnections, concerns of weight, reliability, and RF performance must be addressed. Response to these hurdles has fostered advanced packaging techniques utilizing low-cost, high frequency, versatile materials [6]-[8].

#### 1.1 Background on Advanced Package Technologies

The primary focus of today's wireless systems are component integration, size miniaturization, cost reduction, reliability increase, and performance enhancement; all of which are largely handled in part by the system package design. In order to achieve these objectives, advanced packaging techniques have been developed that replace traditional bulky package configurations. These concepts include system-on-chip (SoC), stacked integrated circuits (ICs) and packages (SIP), and system-on-package (SoP) technologies, illustrated in Figure 1.1. The term "system" refers to everything required for device operation, including the digital and analog circuitry, embedded software, thermal coupling structures, and power sources.

Figure 1.1: Advanced packaging techniques: a.) system-on-chip [9], b.) stacked ICs and packages [10], c.) system-on-package [11].

The simplest packaging approach is the integration of the system onto a single chip (SoC). This offers compact size and high performance functionality capable of mass production. However, this technology limits the system to a single substrate platform, which causes long design times due to complex function integration, noise coupling issues, and mixed-signal processing complexities [12]. Additionally, the inclusion of passive circuitry on chip significantly increases the die footprint; inflating fabrication costs.

SIP and SoP technologies address many of these disadvantages through multifunctional integration at the package level, rather than at the chip level. The degree of freedom realized at the package level allows for multi-chip integration at a higher performance/cost index than SoC technologies [13]. With SIP technology, multiple ICs or chip packages are integrated into a single package through chip stacking and are interconnected using wire bonds, flip-chip bonding, or through-silicon vias (TSV). This approach enables differing semiconductor platforms to be exploited in the system, greatly simplifying design complexity [14]. SIP uses the package solely for inter-chip connection; however, SoP technology takes system integration even further by incorporating functionality into the package itself. In this manner, the system platform is utilized as the IC packaging substrate. Many system components, traditionally integrated on chip, are embedded into the package, taking advantage of the substrate high frequency electrical properties [15]. By utilizing low-loss packaging substrates, high quality-factor (Q-factor) passive components can be achieved, which is not easily realized on lossy chip substrates. The relocation of system components off chip greatly reduces the chip size, saving fabrication costs significantly. Furthermore, this packaging technology enables the inherent benefit of chip and package substrates to be better utilized and co-designed for their respective strengths. Traditionally, the advantages of IC design reside within transistor integration, while the advantages of package design are in analog and digital component integration [16], [17].

There are several technologies available for integration of passive and active ICs into the system platform. Conventional methods make use of wire bonds and flip chip, which are proven to be easy and effective, with relatively low loss [18]-[20]. Wire bonding remains the most commonly used and flexible type of interconnecting technology, shown in Figure 1.2(a). It is low cost and very easily re-worked; however, it incurs high parasitic losses due to large loop inductances caused by long wire lengths. It is also limited to a 2-D package topology, which restricts input/output (I/O) interconnect density, taking up valuable real estate. These limitations can be overcome through the use of flip-chip technology, shown in Figure 1.2(b). Parasitic losses and package footprint sizes are reduced by replacing long wire lengths with solder bumps. Additionally, high density interconnects (HDIs) are used on package to achieve very fine pitched traces and micro-vias down to 30 µm [21], [22]. This increase in number of chip interconnects has become critical in supporting higher power requirements, bandwidths, and data rates. However, the disadvantages of this technology are higher costs, limited re-workability, and its susceptibility to interconnect failure from thermal and mechanical stresses [23], [24].

Figure 1.2: Package interconnects utilized in IC integration: a.) wire bonds, b.) flip chip with HDIs [22].

One possible option for further improvement in parasitic losses and miniaturization for these package technologies is embedding chips within the core of the package. Conceptually, embedding active components can be encompassed by three major categories: (i) cavity formation to the dimension of the chip, (ii) lamination of chips within multilayer laminated sheets, and (iii) over-molding upon placement of the chips on the surface of the package. Significant research has been published in the past 5 years toward embedding chips using ceramic substrates and other platforms [25]. Aside from the improvement in parasitic losses, a clear advantage in embedding actives is the reduced thickness of the package and slim form factor.

### 1.2 Radio-Frequency Substrates for System-on-Package Technology

For SoP design, the platform substrate must not only maintain excellent high frequency electrical properties, but also be suitable for versatile package integration and remain cost effective. There are two categories of materials fitting this profile that have become leaders in the packaging industry: ceramic substrates and organic substrates. Until recently, ceramic substrates have been widely established as the leading material in microelectronic packages, sensors, and passive components. Ceramic materials have long been favored because of their high reliability, multilayer thin-film processing (>50

layers), endurance to harsh environments, and low fabrication costs [26]-[28]. These substrates are typically comprised of multilayered aluminum oxide material, engineered to co-fire at temperatures around 1500 °C. Lamination occurs in one fluent step, which hardens and bonds the substrate and metal layers together into a planar rigid platform. Ceramics of this composition are known as high temperature co-fired ceramics (HTCC). Due to the high firing temperatures of HTCC, high temperature metals such as tungsten (W) and molybdenum (Mo) are used, which limits this material to low RF applications because of their low conductivity [27]. As the electronics market pushed for high frequency applications, low temperature co-fired ceramics (LTCC) were developed from a hybrid ceramic-organic composition, which lowered the firing temperature to 850 °C [29]-[30]. This allowed highly conductive metals like silver (Ag) and gold (Au) to be used, which in conjunction with low-loss LTCC, enabled high RF performance up to millimeter-wave (mm-wave) applications. LTCC has since become the favored ceramic substrate; however, this material is twice the cost of HTCC and has additional complexities of design and fabrication due to a 10 % to 20 % size shrinkage that occurs after firing [31].

In the last decade, organics have become a primary candidate, as they are a lowcost replacement of the standard high performance ceramic materials, exhibiting potential as the next generation technology for SoP wireless systems. Several disadvantages inherent in LTCC technology are resolved by the use of organic substrates. These include the high material costs, material shrinkage after lamination, and high processing temperatures that are incompatible with active chip embedding. For this reason, there have been studies on embedding active circuits with low-cost organic materials that have excellent performance up to mm-wave frequencies and do not have the manufacturing and cost limitations of ceramic substrates. Table 1.1 shows a comparison of material properties for LTCC with several alternative organic materials: Flame Resistant 4 (FR-4), Polytetrafluoroethylene (PTFE or Teflon), and Liquid Crystal Polymer (LCP).

| Material Characteristics            |          | LTCC       | FR-4        | PTFE        | LCP         |

|-------------------------------------|----------|------------|-------------|-------------|-------------|

| ε <sub>r</sub> @ 10 GHz             |          | 4.3 to 9.1 | 3.8 to 4.5  | 2.08 to 2.3 | 2.9         |

| tanδ (1x10 <sup>-3</sup> ) @ 10 GHz |          | 1 to 4.5   | 16          | 0.6 to 1.1  | 2.5         |

| Min Layer Thickness (µm)            |          | 12.5       | 60          | 125         | 25          |

| CTE (ppm/°C), [x,y,z]               |          | 3 to 7     | 14, 13, 175 | 25, 35, 260 | 17, 17, 150 |

| Conductor Material                  | Internal | Ag         | Ag, Au, Cu  | Ag, Au, Cu  | Ag, Au, Cu  |

|                                     | External | Ag, Au     | Ag, Au, Cu  | Ag, Au, Cu  | Ag, Au, Cu  |

| Processing Temperature (°C)         |          | 850        | 185         | <285        | <300        |

| Thermal Conductivity (W/m·K)        |          | 2 to 4     | 0.27        | 0.62        | 0.5         |

| Moisture Absorption (%)             |          | <0.1       | <0.25       | 0.02        | 0.04        |

| Density (g/cm <sup>3</sup> )        |          | 3.1        | 1.85        | 1.9         | 1.4         |

Table 1.1Comparison of material properties for RF substrates

Sources: [29]-[32], [34], [36]

FR-4 is a commonly used printed circuit board (PCB) material. It is very low cost with high mechanical strength and good electrical insulation suitable for applications up to 10 GHz [32]-[33]. However, for applications above 10 GHz, this material exhibits very high losses, which can quickly outweigh its low-cost advantages. PTFE is a low-loss material also used in PCB manufacturing [34]. While this material has excellent RF performance, it is more expensive than the other organic materials and has difficulties in multilayer processing. Additionally, there are issues with circuit failure due to the high coefficient of thermal expansion (CTE) for this material, which causes de-lamination of metal layers during thermal cycling.

In recent years, LCP has been established as an exceptional microwave organic dielectric due to its key performance and packaging advantages [35]-[36]. It has many

favorable characteristics that make it easy to employ while maintaining excellent performance. There is an abundance of literature investigating the benefits of LCP including [37]-[44]; some key advantages are listed below:

- Superior cost/performance index

- Flexibility for application in conformal flex circuits

- Low permittivity and dielectric loss with minimum dispersion up to 110 GHz

- Low CTE compatible with Ag, Cu, and Au

- Near-hermetic

- Naturally flame retardant

- 3-D multilayer integration

- Compatible with sequential build up process in a PCB Foundry

LCP is now established as a low-cost material with excellent high frequency electrical properties extending well into the mm-wave band. Its low dielectric constant ( $\epsilon_r$  = 2.9 @ 10 GHz), low loss tangent (tan $\delta$  = 0.0025), and near-hermetic nature make it an outstanding material for high frequency applications. Its strong packaging properties also give it an edge over competing materials. It is a lightweight, conformal composition with density of 1.4 g/cm<sup>3</sup>, which is less than half that of ceramics. It is also naturally flame retardant, which allows for convenient laser patterning of vias and cavities, and requires low temperature (less than 300 °C) processing for multilayer lamination, making IC embedding possible. The combination of these inherent properties allows a 3-D packaging capability on a conformal platform capable of being mounted to almost any surface (aircraft wing, boat hull, car roof, etc.).

### **1.3 Background on LCP Fabrication**

In addition to evaluating the substrate electrical and mechanical properties optimal for a given application, fabrication limitations must also be considered. The product size, reliability, performance, and cost will all be greatly affected by the capability of the fabrication vendor. This becomes especially apparent at mm-wave frequencies where the physical dimensions of the module tend to shrink in size to maintain acceptable performance. Optimally, very thin substrates with a low permittivity are desired to provide small feature sizes for reduced module size and, ultimately, reduced cost, while also providing the highest performance. Additionally, for high-quantity productions, fabrication can quickly become a dominant cost contributor, which makes the number of units produced per fabrication run a very important issue. Large-panel processing compatible with a PCB infrastructure enables a low cost solution with inexpensive fabrication and fewer production runs.

Table 1.2 shows state-of-the-art commercial fabrication capabilities for multilayer ceramic and organic stackups. LTCC and FR-4 materials have been developed over the last two decades into very mature technologies, while LCP is a relatively newer technology that has entered into commercial fabrication only in the last decade. LCP has a limited number of layers compared to other materials because it is an unfilled material with no reinforcement (fiberglass weave or ceramic particles); however, this also allows the creation of high-aspect ratio vias. The fabrication design rules for this material maintain very small line widths/spaces and via diameter/pitch, which allows highly condensed line routing and via interconnects. Additionally, LCP is processed in large-panels comparable to FR-4. This not only allows batch production of devices, but also the realization of large area, multi-element antenna arrays not feasibly fabricated on the limited panel size of LTCC.

| Guidelines                           |          | LTCC      | FR-4      | LCP       |

|--------------------------------------|----------|-----------|-----------|-----------|

| Minimum Layer Thickness (µm)         |          | 12.5      | 60        | 25        |

| Minimum<br>Line Widths / Spaces (µm) | External | 75 / 75   | 75 / 75   | 50 / 50   |

|                                      | Internal | 75 / 75   | 50 / 75   | 40 / 50   |

| Minimum Via Diameter / Pitch (µm)    |          | 100 / 300 | 150 / 250 | 25 / 200  |

| Panel Size (mm <sup>2</sup> )        |          | 200 x 200 | 570 x 570 | 450 x 600 |

| Maximum Layer Count                  |          | 25        | 70+       | 7         |

| Technology Maturity                  |          | High      | High      | Medium    |

| Sources: [36], [45], [46]            |          |           |           |           |

Table 1.2Design rules for commercial multilayer fabrication

LCP has been proven as a viable substitute for competing substrates; however, fabrication limitations have not yet been fully analyzed with regard to RF performance yield. There is currently very little published on large-scale LCP manufacturability. The following sections outline the fundamental considerations of substrate fabrication and describe the added complexities when implementing LCP.

### **1.3.1 Material Thickness**

LCP core material (ULTRALAM® 3850), double clad, is available in 25  $\mu$ m, 50  $\mu$ m, and 100  $\mu$ m thicknesses with copper foil available down to 9  $\mu$ m thick. LCP Bondply (ULTRALAM® 3908) is available in 25  $\mu$ m and 50  $\mu$ m thicknesses and is used to bond core layers together. The material manufacturer of LCP used in this thesis, Rogers Corporation, guarantees the product to be within ±12.5 % of the specified thickness. During the lamination process, the material stack-up is brought to a temperature of 285 °C under a pressure of 300 pounds per inch<sup>2</sup> (PSI), allowing the Bondply layers to flow and adhere to the adjacent core layers. Consequently, during this

process it has been observed that the LCP core layers will slightly compress, yielding a thickness less than what is expected. In addition, as the material stack-up increases in thickness, a larger temperature gradient across the layers will occur, causing the external layers to be exposed to higher temperatures than the internal layers. This temperature gradient can ultimately cause varying compression in the z-axis between layers. Considering all variations, it is expected that increasing the number of LCP layers during lamination will make the total thickness tolerance greater and more difficult to predict.

### 1.3.2 Registration Error

Layer-to-layer registration is a challenge using any substrate technology process and/or material. This obstacle is exacerbated when using LCP because of its inherent unfilled, un-reinforced state, which enables its excellent electrical properties (low loss, low dielectric constant, and high moisture resistance) but consequently allows the material to 'swim' during the lamination cycle. This results in a steep learning curve for process development; the amount of controllable registration error between layers directly impacts the sizing of via catch pads, which can have degrading effects on RF performance in layer-to-layer transitions. Catch pad sizing, and even more so, RF via transition designs can ultimately be the limiting factors in routing density; isolation also being of primary concern.

#### **1.3.3 Minimum Feature Size**

Utilizing thin LCP laminates of 25  $\mu$ m, 50  $\mu$ m, or 100  $\mu$ m thicknesses for package substrates requires maintaining a 50  $\Omega$  system impedance. It has been shown in Table 1.2 that commercial fabrication is limited to lines and spaces down to 50  $\mu$ m. These capabilities are heavily dependent on copper thickness and typically presume <sup>1</sup>/<sub>4</sub> or <sup>1</sup>/<sub>2</sub> oz copper. For optimized performance and producibility, it is essential to design all transmission lines to be as wide as possible while maintaining 50  $\Omega$  system impedance. Furthermore, as 50  $\mu$ m or smaller lines and spaces are approached, the fixed etch tolerance becomes a significant percentage of the feature size and the RF performance must sustain fabrication tolerances. As the minimum feature size is pushed to its limit, the accuracy of line widths and gaps becomes harder to control. Small variations can have a large effect on line impedances and overall matching in the design. Finish plating will also play an important role in feature resolution and assembly compatibility at the package level and should be considered early in the design phase.

Another important feature for wide-band RF transitions and increased routing density is the use of micro-vias. Aspect ratio, the measure of via diameter with respect to drill depth, for micro-vias is 2:1 across the industry for laminate PCB substrates. Micro-vias are drilled using either a UV or CO<sub>2</sub> laser, or often combinations of both, yielding precision depth-controlled interconnect vias and cavities. Decreasing the aspect ratio enables two key parameters: 1) reduced via diameter, which favorably increases inductance and concurrently reduces via catch-pad diameters that are the dominant capacitive features allowing for a better RF match, and 2) ground stitching (fence of ground vias) between adjacent RF transmission lines for isolation, thus smaller via sizes can accommodate finer RF IC interconnect pitch.

# **CHAPTER 2**

# SYSTEM-ON-PACKAGE MODULES ON LCP

Comprehensive research and prototypes have been published leading to the realization of embedded RF components and devices in LCP packages [43], [47]-[49]. In an effort to better understand the extent of LCP packaging capabilities at microwave and mm-wave frequencies, several packaging methods have been explored. Special techniques are utilized to minimize RF parasitics incurred through the package interconnects. The aim is to offer high performance integration for low-cost and lightweight applications. The advantages of silicon-based chips, combined with the packaging versatility of LCP, provide a unique opportunity for organic based RF SoP solutions. These investigations are discussed in this chapter.

#### 2.1 Embedded Wire Bond Package at K<sub>a</sub> Band