An Optimization Framework for Embedded Processors with Auto-Modify Addressing Modes

> A Dissertation Presented to The Academic Faculty

> > By

ChokSheak Lau

In Partial Fulfillment Of the Requirements for the Degree Master of Science in Computer Science

Georgia Institute of Technology December 2004 An Optimization Framework for Embedded Processors with Auto-Modify Addressing Modes

Approved by:

Dr. Santosh Pande, Committee Chair College of Computing, Georgia Tech

Dr. Hsien Hsin S. Lee, School of Electrical and Computer Engineering, Georgia Tech

Dr. Gang-Ryung Uh, Computer Science, Boise State University

Date Approved: November 2004

He has made everything beautiful in its own time; also He has put eternity in their heart, yet so that man does not find out what God has done from the beginning to the end.

-- King Solomon, the son of King David, Ecclesiastes 3:11

This dissertation is dedicated to the one and only true God.

## ACKNOWLEDGEMENTS

My greatest gratitude would be towards my professor, Dr. Santosh Pande, who has directed my studies and work in compiler research the past two years. Without him, I would not be where I am today. Special thanks to Xiaotong Zhuang, a fellow student, who contributed greatly to part of the work presented.

Also thanks to the One who commanded that life should be lived without any anxiety, bringing peace and rest to me who never had peace and rest. The same One who created heaven and earth, light, the Sun and the Moon, all the planets, and all of life.

| Ackn               | owledgements                                                                                                                                                                                                                            | V                                                                         |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|

| Table              | e of Contents                                                                                                                                                                                                                           | vi                                                                        |  |  |

| List of Tablesviii |                                                                                                                                                                                                                                         |                                                                           |  |  |

| List c             | of Figures                                                                                                                                                                                                                              | ix                                                                        |  |  |

| Abbr               | eviations                                                                                                                                                                                                                               | xi                                                                        |  |  |

| Sumr               | mary                                                                                                                                                                                                                                    | .xii                                                                      |  |  |

| 1.                 | Introduction.1.1Address Generation in DSP Processors1.2The Offset Assignment Problem.1.3Motivating Examples1.3.1Variable Coalescence.1.3.2Post-pre Optimization1.3.3Inter-basic-block Offset Assignment1.4Offset Registers Optimization | 4<br>6<br>.11<br>.11<br>.14<br>.15                                        |  |  |

| 2.                 | Overall Framework2.1Outline2.2Assumptions                                                                                                                                                                                               | .18                                                                       |  |  |

| 3.                 | <ul> <li>Coalescence-Based Offset Assignment</li></ul>                                                                                                                                                                                  | .22<br>.23<br>.24<br>.25<br>.26<br>.26<br>.28<br>.28<br>.34<br>.36<br>.36 |  |  |

| 4.                 | <ul> <li>Post-Pre Optimization</li></ul>                                                                                                                                                                                                | .41<br>.43<br>.43<br>.47                                                  |  |  |

# TABLE OF CONTENTS

| 5.  | Furt       | her Optimizations                                              |    |

|-----|------------|----------------------------------------------------------------|----|

|     | 5.1        | Inter-Basic-Block Offset Assignment                            |    |

|     |            | 5.1.1 Algorithm for Inter-Basic-Block Offset Assignment        |    |

|     | 5.2        | Offset Registers Optimization                                  |    |

|     |            | 5.2.1 Characteristics of Offset Registers                      |    |

|     |            | 5.2.2 Algorithm for Offset Registers Optimization              |    |

|     |            |                                                                |    |

| 6.  | Imp        | lementation Details                                            | 58 |

|     | 6.1        | Implementation Environment                                     | 58 |

|     |            | 6.1.1 Register Set                                             | 58 |

|     | 6.2        | Implementation Details for SOA                                 | 59 |

|     |            | 6.2.1 Reserving an Address Register                            |    |

|     |            | 6.2.2 Identifying All Variables Suitable for Offset Assignment |    |

|     |            | 6.2.3 Constructing Webs and Access Graph                       |    |

|     |            | 6.2.4 Running SOA Algorithm on Access Graph                    |    |

|     |            | 6.2.5 Rearranging Stack Variables Physically                   | 62 |

|     |            | 6.2.6 Using the Reserved AR to Access these Variables          | 63 |

|     |            | 6.2.7 Conclusion for SOA Implementation                        | 65 |

|     | 6.3        | Implementation Details for Coalescing                          |    |

|     |            | 6.3.1 Building the Interference Graph                          |    |

|     |            | 6.3.2 Renumbering Coalesced Virtual Registers                  | 67 |

|     |            | 6.3.3 Rearranging Stack Variables Physically                   |    |

|     | 6.4        | Implementation Details for Using Offset Registers              |    |

|     |            | 6.4.1 Example of Using an Offset Register                      | 68 |

|     |            | 6.4.2 Methodology for Using Offset Registers                   |    |

|     |            | 6.4.3 Recent Trends in Offset Registers                        | 69 |

|     | 6.5        | Implementation Notes for Other Optimizations                   | 70 |

|     | 6.6        | Conclusion for Implementation Details                          | 71 |

| 7.  | Dorf       | ormance Evaluations                                            | 70 |

| 1.  | 7.1        | Measuring LDAR Counts                                          |    |

|     | 7.1        | Benchmarks Description                                         |    |

|     |            | Results for Stack Size Reduction                               |    |

|     | 7.3<br>7.4 | Results for Single-AR                                          |    |

|     | /.4        | 7.4.1 Results for Single-AR LDAR Count                         |    |

|     |            | 7.4.2 Results for Single-AR Code Size                          |    |

|     |            | <ul><li>7.4.2 Results for Single-AR Code Size</li></ul>        |    |

|     | 7.5        | Results for Multiple-AR                                        |    |

|     | 7.6        | Results for Overall Performance Comparison                     |    |

|     | 7.0        | Compilation Time                                               |    |

|     | 7.8        | Access Sequence Lengths                                        |    |

|     | 1.0        | Access sequence Lenguis                                        | 02 |

| 8.  | Rela       | ted Work and Conclusion                                        | 84 |

|     | 8.1        | Related Work                                                   |    |

|     | 8.2        | Conclusion                                                     |    |

|     |            |                                                                |    |

| Ref | erence     | S                                                              | 87 |

## LIST OF TABLES

| Table 1. Percentage of Optimal Solutions for Multiple-AR | 40 |

|----------------------------------------------------------|----|

| Table 2. Statistics for the Benchmarks                   | 73 |

| Table 3. Compilation Time (in seconds)                   | 81 |

| Table 4. Average and Longest Access Sequence Lengths     | 82 |

## LIST OF FIGURES

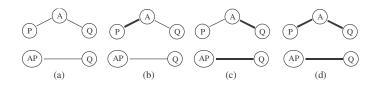

| Figure 1. Generic AGU Model                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

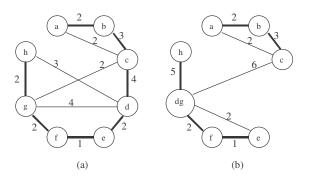

| Figure 2. Example of SOA and Access Graph7                                                                                                    |

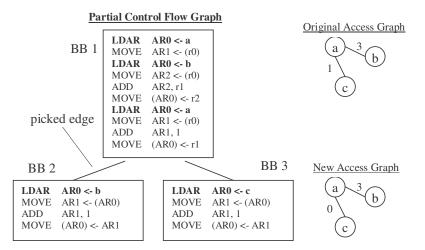

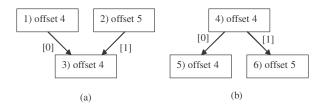

| Figure 3. Motivating Example                                                                                                                  |

| Figure 4. Assembly Code (a) Before, and (b) After Coalescence                                                                                 |

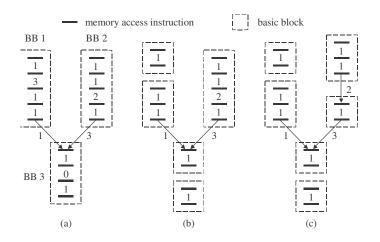

| Figure 5. Example for Post-pre Optimization (a) Original Code and Offsets (b) Without<br>Post-pre Optimization (c) With Post-pre Optimization |

| Figure 6. Example of Access Graph being Modified16                                                                                            |

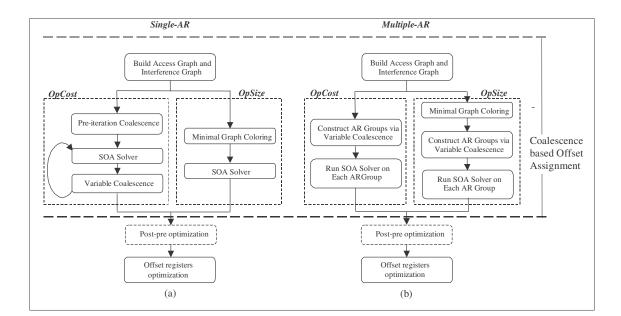

| Figure 7. Optimization Framework                                                                                                              |

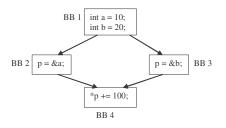

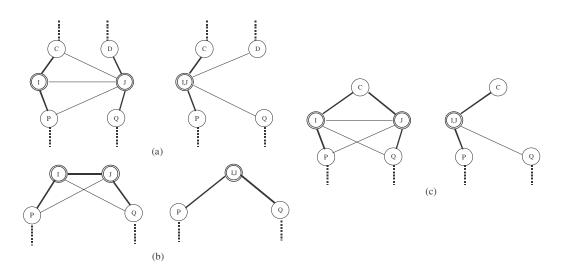

| Figure 8. Illustration of Possible Multiple Aliasing                                                                                          |

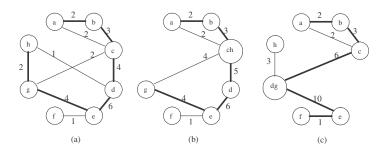

| Figure 9. Profitability of Variable Coalescence                                                                                               |

| Figure 10. Profitability of Rule 3 Coalescence                                                                                                |

| Figure 11. Cases to Calculate the Savings                                                                                                     |

| Figure 12. Coalescence Cases Based on Previous C-PC                                                                                           |

| Figure 13. Coalescence-based Offset Assignment for Single-AR                                                                                  |

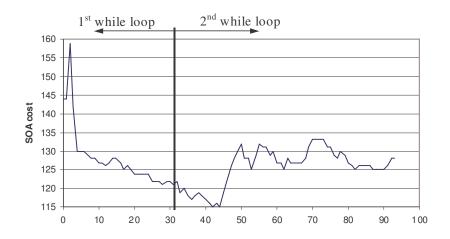

| Figure 14. SOA Cost Fluctuation Along with Iterations for Twolf Procedure 'findcost'.34                                                       |

| Figure 15. Coalescence Algorithm for Multiple-AR                                                                                              |

| Figure 16. Example for Offset Distance                                                                                                        |

| Figure 17. Addressing Modes between Two Adjacent Memory Access Instructions43                                                                 |

| Figure 18. Requirement for Offset Distance to Split only within a Basic Block45                                                               |

| Figure 19. Example for Canonical Form Transformation (a) Original Code (b) After Step 1 (c) After Step 2                                      |

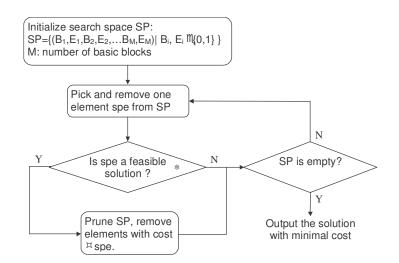

| Figure 20. Flow Graph for Solving the Canonical CFG                                                                                           |

| Figure 21. Illustrations for Feasibility Checking                                                                                             |

| Figure 22. Algorithm for Inter-Basic-Block Offset Assignment                                                                                  |

| Figure 23. Algorithm for Offset Registers Optimization                    | .57 |

|---------------------------------------------------------------------------|-----|

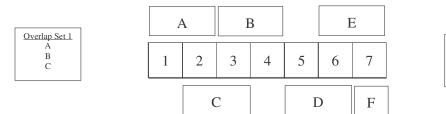

| Figure 24. Illustration of Overlap Sets                                   | .63 |

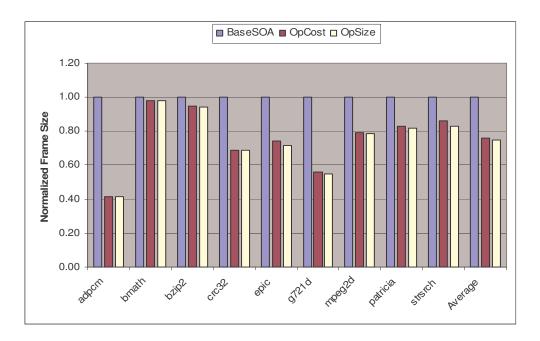

| Figure 25. Stack Size Reduction                                           | .74 |

| Figure 26. Results for Single-AR LDAR Count                               | .76 |

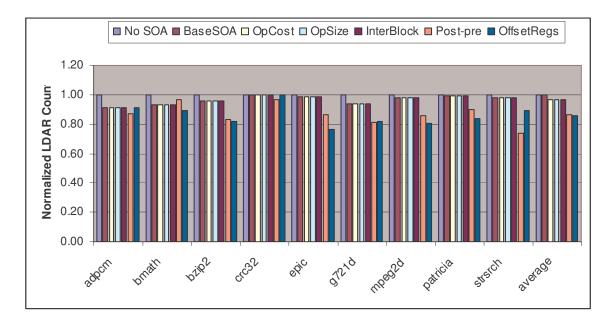

| Figure 27. Results for Single-AR Code Size                                | .77 |

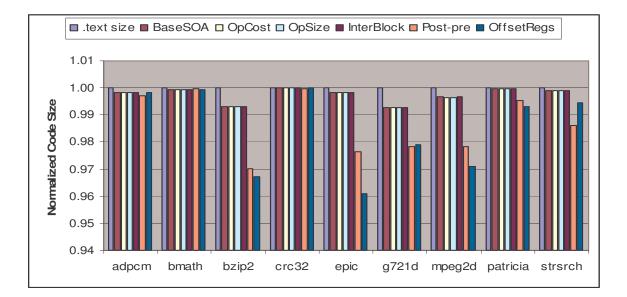

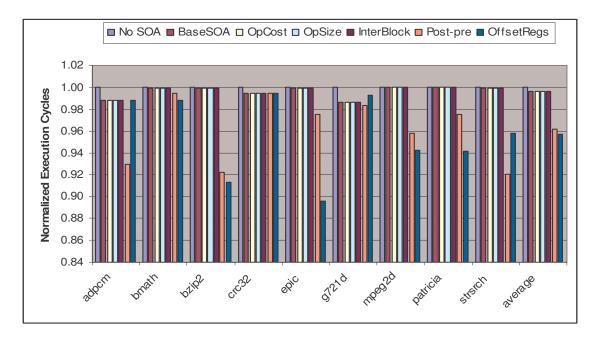

| Figure 28. Results for Single-AR Execution Cycles                         | .78 |

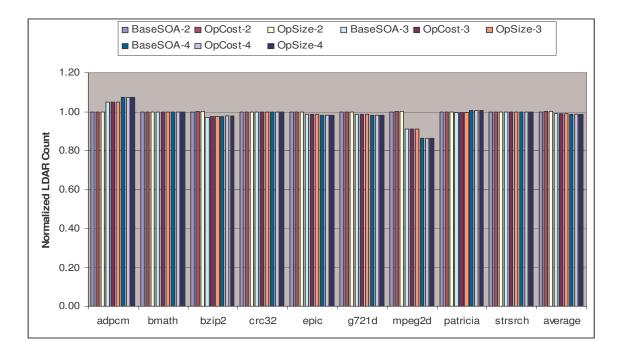

| Figure 29. Results for Multiple-AR LDAR Count – 2 to 4 ARs                | .79 |

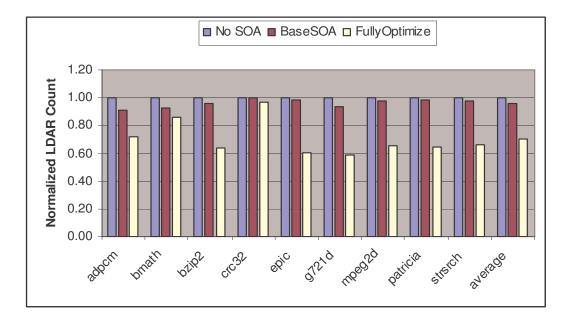

| Figure 30. Overall LDAR Comparison between BaseSOA and Full Optimizations | .80 |

## ABBREVIATIONS

| AG | Access Graph |   |

|----|--------------|---|

| AG | Access Graph | L |

- AR Address Register

- ARA Array Reference Allocation

- AGU Address Generation Unit

- BB Basic Block

- CFG Control Flow Graph

- CG Coalescence Graph

- DAG Directed Acyclic Graph

- DSP Digital Signal Processing

- GCC GNU Compiler Collection

- GNU GNU's Not UNIX

- GOA General Offset Assignment

- IG Interference Graph

- MWPC Maximum Weight Path Cover

- LDAR Load Address instruction, or any AR modification instruction

- PC Path Cover

- SOA Simple Offset Assignment

#### SUMMARY

Modern embedded processors with dedicated address generation unit support memory accesses using indirect addressing mode with auto-increment and autodecrement. The auto-modify mode, if properly utilized, can save address arithmetic instructions, reduce static and dynamic footprint of the program and speed up the execution as well.

[Liao 1995; 1996] categorized this problem as the simple offset assignment (SOA) problem and the general offset assignment (GOA) problem which involve storage layout of variables and assignment of address registers respectively. He proposed heuristic solutions to these problems based on graph-theoretic algorithms. Later work proposed improvements in the performance of Liao's solution by undertaking other heuristics for offset assignment and also by undertaking program transformations which rearrange the sequence of accesses (called access sequence) to the memory locations.

Since techniques based on devising efficient graph covering algorithms have limited impact given the density of the underlying access graph, this work proposes a new direction to explore the solution space for this problem. The work proposes a framework to simplify the access graph using coalescence-based offset assignment, postpre optimizations and using offset registers. Variables not interfering with other (not simultaneously live at any program point) can be coalesced into the same memory location. Coalescing allows simplifications of the access graph yielding better SOA solutions or can perhaps lead to such a small number of non-coalesceable memory locations that GOA solutions for them are optimal. Moreover, it can reduce the program footprint both statically and at runtime (for stack variables) in terms of data segment size. Besides, variable coalescence is orthogonal to other heuristics proposed by early work. We have seamlessly incorporated our framework with an SOA solver. Our framework can work with any SOA solvers, making the scheme more flexible. Post-pre optimization considers how to do most effective code generation using both post-modify and premodify modes to solve the challenge of utilizing this mode within basic blocks as well as across basic block boundaries. Making use of both addressing modes further reduces effective SOA/GOA cost and our post-pre optimization phase is optimal in selecting post or pre mode after variable offsets have been determined.

Our experiments conducted on benchmark programs from MediaBench, MiBench and Spec2000Int showed improved code performance in terms of stack size, the number of address arithmetic instructions and execution cycles. We were able to obtain an average of 12.0% reduction in dynamic stack size in a compiler that reuses stack slots, so the actual savings could have been greater if the compiler were to not reuse stack slots. We base our comparisons against a base SOA algorithm, which is Liao's SOA with Leupers and Marwedel's tie-breaker. By using offset registers, we achieved a 36.5% reduction in address arithmetic instructions, compared to 2.77% for base SOA algorithm. For code size, we saved 2.27% compared to 0.32% for base SOA. For execution cycles, we saved 4.10% while base SOA saved 0.38%.

#### 1. INTRODUCTION

The rapid evolution in embedded processors and DSP architectures has raised new challenges for compilers to generate efficient and small footprint code for the everincreasing demands on user applications. Reducing the code size also reduces the amount of memory traffic for instruction fetching and data fetching, which can further speed up the program execution.

Memory is often a scarce resource in embedded systems because of their small size. Therefore, we want to optimize code with respect to both code size and stack size, because both of them consume memory.

Most modern embedded architectures have specialized address generation units (AGUs) to facilitate the memory address generation in different modes. The AGU normally provides auto-modify mode, i.e. simple Address Register (AR) operation (typically, plus or minus a small constant value) before or after the memory access operation, so that the address register operation is executed for free without dilating the clock cycle on the critical path. However, due to constraints on instruction size, traditional register-plus-offset addressing mode is either not supported (e.g. TMS320C25) or requires more instruction words (Motorola DSP56300). Therefore, transforming address arithmetic into auto-modify mode can help to generate compact and efficient code and speed up execution as well.

Most modern DSP processors have at least 8 address registers. For example, each of the Motorola DSP56300 processor [Motorola 2000] and the Sony pDSP processor has 8 address registers. StarCore's SC140 has 16 address registers [Motorola 2001]. Analog Devices' ADSP-21020 has 8 address registers (32 bit) for data memory and 8 address

registers for program memory (24 bit). Post-modify is supported for all these processors, and pre-modify is supported for some processors like DSP56300. The hardware support reflects the designers' expectation for heavy usage of these instructions; however the actual usage of them is still quite limited. In our experiments, we counted the number of instructions with auto-modify modes generated by GCC compiler retargeted for the Motorola DSP56300 processor. For most benchmark programs, less than 3% of the generated address instructions make use of the auto-modify mode before our optimizations. A recent study [Udayanarayanan 2001] also shows that on some embedded processors up to 55% of operations could potentially use address register operations to reduce cycle counts and code size. Therefore, significant opportunities exist for optimizing address register assignments.

Bartley [1992] and Liao et al [1995; 1996] first modeled this problem as offset assignment (also known as storage assignment). They identified the problem as two classes: simple offset assignment (SOA) and general offset assignment (GOA). They modeled the problem as an access graph and the objective is to find the maximum weight path cover (MWPC) on the graph. Liao proved that finding the MWPC is NP-complete; therefore heuristics are used to solve both SOA and GOA. Later, Leupers and Marwedel [Leupers 1996] extended Liao's work by proposing a Tie-break heuristic for SOA and a variable partitioning strategy for GOA to reduce the SOA and GOA costs. Atri, Ramanujam and Kandemir [Atri 2000] further improved the heuristics by an algorithm called Incremental-Solve-SOA, which requires much more running time in solving the same graph problem. Sudarsanam et. al. [1997] studied the offset problem in the presence of an auto-modify feature that varies from -1 to +1 with k address registers. [Rao 1998; Rao 1999] extended beyond offset assignment with memory access sequence reordering (or program reordering) through algebraic transformations on the expression trees. [Kandemir 2003] proposed a more aggressive access sequence reordering scheme with both intra-statement and inter-statement transformations. Program reordering can better utilize the auto-modify mode by rearranging not only the variables' offsets but also the order of memory access instructions. An approach based on a genetic algorithm (GA) for SOA was presented in [Leupers 1998]. It uses a simulation of natural evolution process, which is relatively time-consuming. Finally, [Leupers 2003] did a comprehensive comparison among several existing algorithms (except program reordering) and proposed a combined algorithm based on Tie-break and incremental-Solve-SOA. He also found that the qualities of the solutions obtained are quite close among these algorithms.

Another type of problem is known as the Array Reference Allocation (ARA), which optimizes the access to array variables using auto-modify mode [Araujo 1996; Gebotys 1997; Leupers 1998; Ottoni 2001].

In this work, we propose an optimization framework for compiler-managed code generation based on the auto-modify mode on embedded processors. Previous approaches to offset assignment optimization concerns dealing with graph-theoretic algorithms and algebraic transforms to find a good memory layout, but do not provide any stack size savings. We want to optimize stack memory and also simplify the solution by making use of other techniques. Our framework consists of two parts. First, we enhance the effectiveness of offset assignment with a new technique called variable coalescence. We start with identifying webs, and then we coalesce them aggressively into fewer memory locations. Our study shows that the access graph of the atomic variables is sparse, and coalescence can effectively reorganize them to generate simpler access sequences with high-weighted path covers. Besides, aggressive coalescence can significantly reduce the static and dynamic memory space requirements of a program for SOA and GOA based optimizations. Variable coalescence can be combined with most previous approaches to further boost the performance. Second, to further reduce the AR modification instructions (written as "LDARs" for short), we add a post-pre optimization phase to decide whether post- or pre-modify mode should be used for each access. Our post-pre optimization phase can optimally select post or pre mode after variable offsets have been determined. We also propose additional optimization methods to consider SOA as an inter-basicblock problem, and to scavenge the offset registers which can be used to save LDARs and execution cycles.

## 1.1 Address Generation in DSP Processors

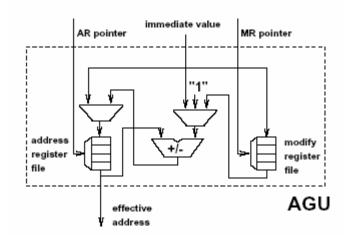

Address generation hardware in DSP processors differs from that of standard processors [Leupers 1996]. Usually, several ARs are available, which can be updated in parallel to other machine operations, thereby introducing no code size or speed overhead. On the other hand, addressing may be quite restricted. In order to avoid long combinational delay, many DSPs do not permit indexing with an offset, but only postmodification, i.e. additions or subtractions involving ARs take place only at the end of a machine cycle. Besides high code quality, retargetability is another primary goal in DSP code generation, due to the growing diversity of DSPs in form of application-specific designs (ASIPs). Therefore, we consider a generic AGU architecture, which reflects a subset of AGU capabilities of many contemporary DSPs. Our AGU model (Figure 1) is parameterized by the number K of ARs and the number N of Offset Registers (ORs). In case of multiple memory banks we assume separate AGUs for each bank. Typical AGU configurations are K = 4; N = 4 (ADSP-210x), or K = 8; N = 1 (TMS320C2x). The ARs provide effective memory addresses, while ORs store integer modify values for AR updates. AR and OR files are indexed by designated pointers, which select the current AR and OR for each machine cycle. AR and OR pointer updates usually does not contribute to code size [Leupers 1996]. Figure 1 shows a generic AGU model taken from Leupers and Marwedel's paper [Leupers 1996].

Figure 1. Generic AGU Model

The AGU model permits execution of the following primitive AGU operations in each machine cycle: 1) Immediate AR load: The current AR is loaded with an immediate value supplied by the instruction word. 2) Immediate AR modify: An immediate value is added to or subtracted from the current AR. 3) Auto-increment/decrement: The constant 1 is added to or subtracted from the current AR. 4) Immediate OR load: The current OR is loaded with an immediate value. 5) Auto-offset-modify: The contents of the current OR are added to or subtracted from the current AR.

### 1.2 The Offset Assignment Problem

Compiler optimizations for auto-modify addressing modes can be classified into two types: single-AR and multiple-AR, depending on the number of available address registers.

An AR modification instruction is written as "LDAR" for short. "LDAR" means "load address" and it means an instruction that sets an AR to a certain immediate address value. There are two other kinds of address arithmetic instruction, "ADAR" and "SBAR". "ADAR" is an instruction that adds an immediate integer to an AR. "SBAR" is an instruction that subtracts an immediate integer to an AR. To simplify writing, we use "LDAR" to mean any one of the LDAR/ADAR/SBAR instructions.

Traditionally, it is studied as the Offset Assignment Problem. Offset assignment is to assign offsets (memory layout) to variables so that the number of address arithmetic instructions can be minimized by using auto-modify modes of register indirect addressing instructions. Accordingly, Simple Offset Assignment (SOA) assumes single-AR, while General Offset Assignment (GOA) tackles multiple-AR. For example, Figure 4(a) shows the memory layout for 6 variables (address grows upwards) and generated code corresponding to Figure 3(a)—we assume one address register AR0, so it is an SOA problem. Here, we assume that variables on the right-hand-side of the equation must be loaded one-by-one from left to right, then, after the evaluation, the result is stored into the left-side variable. For the time being, all variables are stored in memory (in case they are not, the access graph will show the order of only those accesses corresponding to memory accesses, i.e. load/stores). For the first instruction c=a+b, after accessing b, i.e. ADD \*(AR0)-, we use auto-decrement to point AR0 to the memory location of variables c

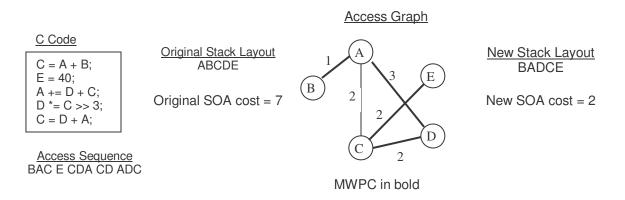

thus saving one AR modification instruction. In principle, all ADARs and SBARs can be replaced by LDAR in usage. Therefore, the problem of maximizing the use of automodify instructions is to find a good memory layout such that a maximum number of consecutively accessed variables are adjacently stored in memory. To apply the offset assignment optimization, we need to find out the access sequence first. An access sequence is defined as an ordered linear sequence of variable accesses [Liao 1995; Liao 1996]. For example, in Figure 2, we show the access sequence below for the code segment. From the access sequence, we can build an access graph based on the access sequence (Figure 2). An access graph is a weighted undirected graph, on which each node is a variable, while the edge weight is the number of transitions in the access sequence between the two end nodes (variables). In other words, the edge weight represents the number of times the two nodes are accessed consecutively in the access sequence.

Figure 2. Example of SOA and Access Graph

After the access graph is constructed, our optimization objective is to find a maximum weight path cover (MWPC) [Liao 1995]. An MWPC is simply a path cover (PC) with maximum weight. Here, path cover is defined slightly differently from that in graph theory. The path cover here means an edge set such that 1) each node adjacent to

any edge in the edge set can only have either one or two neighbors in the edge set; 2) no cycle can be constructed solely with edges in the edge set. Intuitively, the subgraph with only edges in the edge set must consist of one or more linear path(s) so that the variables can be laid out linearly in memory. Weights covered on the PC is proportional to the number of times auto-modify modes can be used to access the next variable in memory, while the sum of the weights of all edges not on the PC is proportional to the number of times LDARs should be inserted, and this sum is called the SOA cost ([Liao 1995] gives details on the SOA cost. Intuitively, for uncovered edges, LDARs must be inserted and the edge weights now represents how many times these instructions are executed). The thick lines in the access path in Figure 2 shows one of the PC and also an MWPC solution. The weight for the MWPC is 7 and the SOA cost is 2. Earlier approaches [Liao 1995; Leupers 1996; Atri 2000] have shown that the MWPC problem is NP-complete and tried to find a good path cover with a weight close to the MWPC.

For example, in Figure 2, the original SOA cost of 7 means that in the access sequence, we can count 7 times for which we go from one variable to another for which the variables are not placed right next to each other in the stack layout. For the sequence BACECDACDADC, the 7 breaks in the access sequence are: AC, CE, EC, DA, AC, DA and AD. Using the MWPC solution, we can get a new SOA cost of only 2.

On the other hand, General Offset Assignment (GOA) is typically solved in two steps. During the first step, a heuristic algorithm assigns each variable to an address register, thus a variable assigned to an AR uses that AR only. Next, for all variables assigned to the same AR, the problem is solved as SOA. GOA cost is actually the sum of SOA costs associated with each address register. For GOA, the access sequence for variables handled by one AR is derived from the all-variable access sequence but considering only the variables using that AR. For example, in Figure 3(a), if we have two address registers AR0 and AR1, and {a,b,c} is handled by AR0 and {d,e,f} is handled by AR1, then the access sequence for AR0 is abcacaaccb, the access sequence for AR1 is defddf.

In real programs with branches, the access sequence cannot be simply derived from static code during compilation time, because the compiler has little knowledge about the runtime execution trace. However, we can still construct the access graph in other ways. Notice that, on the access graph, the edge weight between two variables should indicate the frequency these two variables are accessed consecutively. In other words, as adopted in our experiments, we can use profile information to get the execution frequency for the path between two consecutive memory accesses to the variables. In case profile information is not available, we can roughly estimate the execution frequencies of the paths based on their loop depth [Muchnick 1997].

In addition to offset assignment, other approaches are possible to harness the auto-modify modes or to improve the effecti`veness of offset assignment. [Rao 1998; Rao 1999] proposed program reordering. Program reordering reschedules instructions according to the algebraic laws (like from a+b to b+a) so that a higher weight path cover solution can be obtained during offset assignment and more variable accesses can be covered with auto-modify mode.

In this work, we observe that the access graph is sparse in general, therefore coalescing nodes on the access graph might lead to a better MWPC solution based on offset assignment. After variable coalescence, the access graph can be much different,

9

inducing an improved solution even superior to the optimal MWPC that can be achieved without variable coalescence. Furthermore, variable coalescence can be combined with and improve all previously mentioned offset assignment approaches and it is applicable to both SOA and GOA. Secondly, our post-pre optimization comes after offset assignment and finds chances for both and post and pre addressing mode. In the next section, we will show a few examples to illustrate these optimizations.

## **1.3 Motivating Examples**

## **1.3.1** Variable Coalescence

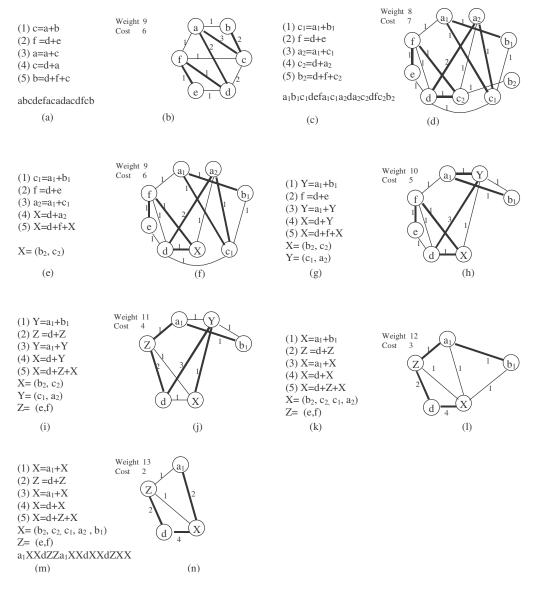

In Figure 3, we give an example to illustrate how variable coalescence works and how it can reduce the SOA and GOA cost.

Figure 3. Motivating Example

The code segment in Figure 3(a) (taken from [Rao 1999] with minor changes) contains 5 instructions. We assume this code segment is the entire program itself. In real programs, we need to do liveness analysis and variable renaming/coalescing.

The coalescence algorithm actually first separates variables into atomic units called webs (explained in Chapter 3.2) [Muchnick 1997] through variable renaming. A web is a du/ud chain closure of a variable and allows independent allocation of values in memory.

\*Note: variables on the right of semicolon is what AR0 points to after the instruction.

Figure 4. Assembly Code (a) Before, and (b) After Coalescence

Figure 3(c) shows how we separate each of variables a, b and c into two webs. Intuitively, in instruction (3), defining variable a starts a new web. We thus rename the variable a, then use that new name in later references. Similarly, b and c are renamed in instructions (4) and (5). In this code segment, c1, which is live from instructions (1) to (3), constitutes a closed web, c1 can be arbitrarily renamed regardless of other parts of the program. Figure 3(c) and Figure 3(d) show the access sequence and access graph after variable separation. The weight of the MWPC is 1 unit smaller than the one before variable separation. In Figure 3(e) and Figure 3(f), we coalesce b2 with c2, i.e. we combine these two variables into one variable, putting them into the same memory location. Because the last use of c2 ends before the definition of b2, they can be safely coalesced as one variable X. Their edges are coalesced accordingly as shown in Figure 3(f). After coalescing, the cost is reduced by one (notice when we coalesce two variables, the weight of the edge between them is saved, since we do not need to modify the address register when consecutively accessing the same memory location). From Figure 3(g) to Figure 3(n), we coalesce 4 other nodes. The final MWPC weight is 13 (including edges between nodes that were coalesced together) with an improvement of 44%. Also, the data segment size is reduced from 6 variables to 4 variables (a 33% reduction). The final variable layout and modified code are listed in Figure 4(b). After saving 4 ADAR/SBAR instructions, we achieve a 17% code size reduction and 17% speedup (assuming all instructions require the same number of cycles).

We now discuss the effect of coalescing on GOA. Suppose 2 address registers AR0 and AR1 are available, for the code in Figure 3(m), we can simply assign two variables to each of them, e.g. {X, a1} to AR0, {Z, d} to AR1. The access sequence for {X, a1} as derived from the whole access sequence in Figure 3(m) is a1XXa1XXXXXX, thus the access graph has only one edge with weight 3, which is on the MWPC. Similarly, for {Z, d}, the solution is also optimal (SOA cost of 0). We will show in Chapter 3.7 that coalescence can often generate an optimal solution for GOA.

Figure 3(b) already shows the optimal solution of MWPC for the case of no coalescence, and therefore no heuristic can reduce the cost below 6 without variable

coalescence. For GOA, since variable coalescence already obtained the optimal solution, no other algorithm can do any better.

This example shows that by separating and coalescing the variables, we get better performance (fewer execution cycles) and code size. Using coalescing can often produce a solution with a lower SOA cost than the best MWPC that could possibly be obtained without coalescing. Also, coalescing gives a stack size savings which the other algorithms cannot give.3

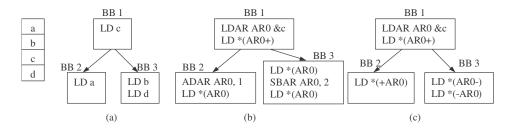

## **1.3.2** Post-pre Optimization

This example illustrates post-pre optimization. As mentioned previously, both post- and pre-modify are supported for some embedded processors. However, current research on offset assignment does not consider pre-modify modes altogether. In Figure 5(a), assume that after offset assignment, the four variables are laid out sequentially as d,c,b,a (address grows upwards). Meanwhile, the four load instructions are distributed in 3 basic blocks. Based on the variable offsets, we can generate the final code as in Figure 5(b), where auto-address mode is only used once. 3 LDAR instructions have to be used to set the address register AR0. However, in Figure 5(c), we give another solution with the post-pre optimization. Although the two successors of variable c, i.e. a and b, have different offsets, with both post- and pre-modifies, we can avoid any LDARs. After accessing c, AR0 is post-incremented to point to variable b. On the path to BB2, AR0 is pre-incremented before accessing variable a. In the meantime, the SBAR instruction in BB3 can be avoided as well. AR0 is post-decremented and then pre-incremented before accessing variable d, so SBAR AR0, 2 can be removed. Notice that, post-pre

optimization is done after variable offsets have been assigned by the offset assignment algorithms.

Figure 5. Example for Post-pre Optimization (a) Original Code and Offsets (b) Without Post-pre Optimization (c) With Post-pre Optimization

#### 1.3.3 Inter-basic-block Offset Assignment

In a typical CFG, a basic block can have multiple predecessors and/or successor basic blocks. Therefore, the access sequence does not terminate along basic block boundaries. The problem of considering the continuation of access sequence even across basic block boundaries is called inter-basic-block offset assignment. In the case when a basic block P has a unique successor S, where S has a unique predecessor P, we can merge two access sequences into one longer access sequence. However, the problem becomes more complicated when an access sequence can take one of several different paths. In such a case, we try to continue the access sequence along the path which could possibly save an LDAR.

Figure 6 shows the case when the variables' stack layout is (a, b, c) and variable a can be followed by either b or c in a CFG split point. In the original access graph, we have only two edges that we can pick from, either (a, b) or (a, c). Since edge (a, b) has a greater weight, we pick it. However, note that the weight of edge (a, b) overlaps with the weight of edge (a, c). This means that we can either count edge (a, b), or count edge (a, c),

but not both at the same time. Why is this so? This is because of the CFG split. The topmost basic block, BB1, has two successors BB2 and BB3. The last memory access in BB1 is variable a. The first memory access in BB2 is b, while the first memory access in BB3 is c. Therefore, we have two different access sequences at the bottom of BB1. It could be either a-b, or a-c, but not both.

Since we pick (a, b), edge (a, c) loses a weight of one. This is because we chose to realize the address of variable b at the bottom of BB1, which is the access sequence from BB1 continuing on to BB2. b has a different address from c, so if we realize the address of b, we cannot realize the address of c at the bottom of BB1. Therefore, BB3 needs an LDAR at the top of the basic block. If we had picked (a, c) instead, the weight of edge (a, b) would not be 3 anymore, but would become 2. Vice-versa, if we choose to go from BB1 to BB3, then that will break the access sequence from BB1 to BB2.

Figure 6. Example of Access Graph being Modified

Thus, the access graph changed as we picked edges during offset assignment. In this way, the access graph dynamically evolves during the process of selecting access graph edges and by so doing, we take into account access sequence across basic block boundaries. In the case when we do not consider any inter-basic-block access sequences, we need one LDAR for each of variables b and c because they appear as the first load/store instruction in the basic block, which is the worst case possible. This worst case corresponds to the case of intra-basic-block offset assignment. In general, any intra-basic-block offset assignment scheme always needs at least one LDAR at the top of each basic block in which at least one offset-assigned variable exists.

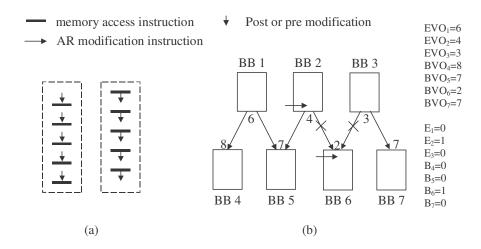

#### 1.4 Offset Registers Optimization

Offset registers are the special set of registers in typical DSP processors that allow an offset to be applied to an address register without incurring any additional execution cycles. Therefore, when we want to access a particular memory location with a known offset from the current address register value, we can either modify the address register directly, or modify an offset register and use it with a base address register. The offset register is particularly useful when referring to stack memory because by modifying the offset register, we do not have to modify the stack pointer register. Also, unaliased stack variables always have a fixed, pre-known offset from the stack pointer, and hence we can reuse the same offset value to point to the same stack variable.

Since DSP instructions only support a modification by one offset in auto-modify modes, offset registers can be used to reach those variables which are placed more than one offset location away in memory. This is especially useful when the offset register is pre-assigned a small fixed value, typically 2 or 3, and this makes it possible for us to save LDARs even when the access sequences are separated by fixed offsets that are not reached by using auto-increment or auto-decrement.

#### 2. OVERALL FRAMEWORK

#### 2.1 Outline

Figure 7 shows the overall framework for the optimizations with auto-modify mode. Figure 7(a) shows the optimization flowchart for single-AR and Figure 7(b) shows the one for multiple-AR. In both cases, two optimization objectives are considered during coalescence and offset assignment, leading to two kinds of algorithms. We propose two kinds of heuristics to minimize the SOA or GOA cost, which corresponds to address modification code (LDAR/ADAR/SBAR). Algorithm "OpCost" targets the incremental minimization of SOA or GOA cost, while algorithm "OpSize" aims to minimize the nodes on the access graph (or the runtime memory space these variables take) through aggressive coalescence. As a starting point, we need to build the access graph (AGs) and interference graphs (IGs). These two graphs are necessary to guide the coalescence and offset assignment process.

Figure 7. Optimization Framework

In Figure 7(a), both OpCost and OpSize invoke an SOA solver, which could be any one of the previous offset assignment algorithms without variable coalescence. The SOA solver only assigns offsets for given variables and attempts to minimize the SOA cost. For the OpCost algorithm, a heuristic approach is chosen to iterate over MWPC searching and variable coalescence after the pre-iteration coalescence is done (explained in Chapter 3.6). In each iteration, the heuristic algorithm finds 2 nodes to coalesce if possible. Then, the two nodes are coalesced and the access graph and interference graph are changed accordingly. The solution with the least cost ever achieved is saved and used as the final solution. On the other hand, OpSize simply coalesces the nodes maximally through a graph coloring algorithm, then runs the SOA solver to obtain a solution.

In Figure 7(b), with multiple ARs, the algorithm classifies variables into several AR groups, so each group can be assigned to one AR and solved with a single-AR algorithm. The OpCost algorithm constructs AR groups together with variable coalescence, then runs the SOA solver afterwards on each AR group. In contrast, the OpSize algorithm aggressively coalesces the nodes by minimally coloring the IG, since the minimal number of nodes can lead to optimal solutions in many cases. In case the optimal solution cannot be given out after graph coloring, we apply the coalescence algorithm as in OpCost.

After variable coalescence and offset assignment, we optionally perform post-pre optimization if both post- and pre-modify modes are supported. This is a cheap operation and the algorithm does not take much more time to run than SOA itself. Finally we use the offset registers as far as we can to cover the rest of the remaining breaks in access sequences so that we can further save LDARs. Clearly, our framework incorporates more optimizations than solely assigning offsets for variables. Coalescence-based offset assignment is the phase in which we perform variable coalescence together with offset assignment. We will discuss this in detail in Chapter 3. We will make use of an SOA solver from early "offset assignment only" approaches. Post-pre optimization will be discussed in Chapter 4.

#### 2.2 Assumptions

Most of the basic assumptions are followed from previous work [Bartley 1992; Liao 1995; Liao 1996; Rao 1998; Rao 1999; Leupers 1996]. We list some specific ones as follows:

1) This work only considers auto-modify addressing with stride 1, which means the address register can only be increased or decreased by 1 in each instruction that has the auto-modification. Auto-modify with stride 1 only is the most widely supported auto-modify mode on state-of-the-art embedded architectures.

2) Not all address register operations can be converted into auto-modify mode addressing. For instance, some address registers can point to multiple variables depending on the direction of the control flow or due to multiple aliasing; thus, we cannot bind it to one single variable since it would be unsafe to optimize it as auto-increment or auto-decrement for a given layout. Thus, in a multiple alias case, one has to use explicit address register modification (like LDAR, ADAR, SBAR in Figure 4) operations.

3) In addition, array index based optimizations have been an active area of research and there are techniques to analyze array-indexed memory accesses, esp. in loops [Ottoni 2001; Araujo 1996; Gebotys 1997; Leupers 1998; Zhang 2003]. However, such research work is entirely different from offset assignment optimizations for scalar

variables in terms of the problem formulation and approaches. Currently, we consider it beyond the scope of this article.

#### 3. COALESCENCE-BASED OFFSET ASSIGNMENT

#### 3.1 Use of Alias Analysis

The framework starts with performing a simple alias analysis [Aho 1986] to determine the variables that might be referenced via pointers. For a given variable P, where P is a pointer, we can determine what P points to if P is locally assigned across all reaching paths in the CFG of the function before P is first used. Consider the CFG in Figure 8. P is a pointer to an integer, and A and B are two local variables. The CFG then splits into two possible paths, with one path into BB 2 setting P to the address of A, and the other path into BB 3 setting P to the address of B. Therefore, in BB 4. we know that P can point to either A or B, and no other locations. We also know that A and B do not have the same stack memory address. Therefore, P is multiply-aliased.

Figure 8. Illustration of Possible Multiple Aliasing

Another case is when a pointer P is first used before its definition in the function, or P is assigned a value which came through as a function argument value or from some external unknown value. In these cases, we cannot determine an alias for P. But we do not treat any unknown aliases as possibly pointing to any local stack variable. Rather, we know that an unknown alias value can never point to a local stack variable, and hence, we ignore such aliases in our optimizations. We consider using an address pointed to by a pointer only when we can determine a unique target alias for it. Otherwise, we simply cannot optimize for it because we will have to use an load the AR with a value that cannot be known at compile time, and is only known at runtime. In Figure 8, P may point to either A or B. We cannot save any LDARs here because we have to load the AR with the address of either A or B at runtime, and speculating that P will point to A only or B only does not help to save any LDARs. We still have to use at least one LDAR to cover for the memory access in BB 4.

### 3.2 Variable Renaming, Webs and Variable Separation

In order to separate memory references, which can be independently considered for allocation, we rename variables and construct webs (as in Figure 3(c) and Figure 3(d)). A web [Muchnick 1997] or live range is defined as the maximal union of du-chains. Each web builds a separate variable after renaming, i.e. one must bind all the definitions and uses within a web to a single memory location. In this manner, we are able to achieve effective value separation at different program points. Value separation is extremely important as the compiler normally generates lots of temporaries that are reused repeatedly. Decoupling these variables that are disjoint in terms of values through renaming gives us more freedom to coalesce them in a proper way to maximize the profit of offset assignment optimizations.

Our results show that over 80% local variables in the backend that can make use of the auto-modify instructions are recycled temporaries and the data segment size for them can increase after web identification. However, coalescing phase which follows greatly reduces the data segment size and brings about an overall size reduction when compared to the original data segment size. To avoid interfering with a good register allocator and other optimizations before register allocation, our optimizing pass comes after register allocation, when all virtual registers that will be on the stack are identified. Also, for user-defined variables and temporaries, webs are built to achieve value separation.

# **3.3** Interference Graph and Coalescence Graph

After values separation, our coalescence algorithm needs to determine which variables are coalesceable.

An interference graph (IG) is built to represent the overlapping of the live ranges between different variables. The IG is defined as a graph where each node is a live range and an edge between a pair of nodes means that at a certain program point, the two nodes are simultaneously live, so they cannot be coalesced. It is perhaps most-used in register allocation.

A coalescence graph (CG) is a graph in which two nodes can be coalesced if and only if there is an edge between them. The CG is simply the complementary graph of the IG, which means, any two nodes connected by an edge on the IG will not be connected by an edge on the CG, and same vice-versa. In actual implementation, we only use the IG.

In our 10 benchmark programs, the IGs after value separation are sparse. Intraprocedurally, the average degree for each node is 8.17 on the IG and 210 for the CG. The strong connectivity on the CG means live ranges have plenty of chances to be coalesced with one another. The high average degree on the CG and the low average degree for the IG are probably due to the large amount of temporaries generated by the compiler. These temporaries are initially generated as virtual registers and then spilled. Most of the temporaries are defined once and used only a few times within the same basic block.

# 3.4 Profitability of Variable Coalescence

The high connectivity of nodes on CG grants us ample freedom to make good coalescing decisions to simplify the access graph (AG) considerably. Simplifying access sequence through judicious choice of coalescing is a non-trivial problem. Coalescence must be performed so that the resulting MWPC solution is improved. A key observation is that increasing edge weights through coalescence does not always lead to a better MWPC solution. In other words, coalescence may worsen the solution for offset assignment if not properly conducted. Coalescence seems to impact graph topology more than the edge weights as far as MWPC is concerned. This is due to the fact that in a final MWPC solution, there can be at most two incident edges on each node and thus, attempting to increase edge weights does not seem to impact the MWPC as much as reduction in node degrees which is a function of graph topology more than edge weights.

Figure 9. Profitability of Variable Coalescence

Figure 9(a) shows the original access graph and the current status of MWPC, i.e., a-b-c-d-e-g-h and f with total weight 21. If the coalescence graph permits the coalescing of nodes c and h, we can coalesce the two nodes and get an MWPC (a-b-ch-d-e-g and f) in Figure 9(b), the weight is 20. After coalescence, the MWPC is worse. The reason is because node c already has 4 neighbors. Adding more neighbors from h is not going to be

profitable. In contrast, in Figure 9(c), we coalesce node d and g. The MWPC is a-b-c-dge-f and h with a total weight of 22. This example shows that coalescence cannot be done arbitrarily without consideration of the topology of the IG and the AG.

#### 3.5 Problem Formulation

The objective of offset assignment based on variable coalescence is to find both the coalescence scheme and the MWPC on the coalesced graph. We start with a few definitions and lemmas for variable coalescence.

# 3.5.1 Definitions

**Coalesced Node (C-Node)**: A C-node is a set of live ranges (webs) in the AG or the IG that are coalesced. Nodes within the same C-node cannot interfere with each other on the IG. Before any coalescing is done, each live range is a C-node by itself.

**Coalesced Edge (C-Edge)**: The C-edge is an edge set defined for a pair of C-nodes. A C-edge <c1,c2> between two C-nodes  $c_1$  and  $c_2$  on graph G is a set defined as:

$\{ < n_1, n_2 > | n_1 \in c_1, n_2 \in c_2, < n_1, n_2 > \text{ is an edge on } G \}$

C-edges apply to either the AG or the IG. A C-edge exists only when this set is not empty. C-AG (Coalesced Access Graph): The C-AG is the access graph after node coalescence, which is composed of all C-nodes and C-edges.

**C-IG** (**Coalesced Interference Graph**): The C-IG is the interference graph after node coalescence, which is composed of all C-nodes and C-edges. A C-edge between two C-nodes means the two C-nodes has interfering live ranges, therefore cannot be coalesced.

**Coalesced Path Cover (C-PC)**: On a C-AG, a C-PC consists of a sequence of C-nodes  $c_1, c_2, ..., c_k$ , where  $\langle c_i, c_{i+1} \rangle$  is a C-edge between C-node  $c_i$  and  $c_{i+1}$ . The C-PC covers all

C-nodes exactly once, contains no cycles, and no C-node has a degree larger than two in the C-PC.

**Weight of a C-Edge**: The weight of a C-edge is the sum of all edge weights in the C-edge. C-edges with weight zero are C-edges that do not exist.

**Weight of a C-Node**: The weight of a C-node is the sum of all edge weights between any two nodes contained in this C-node.

**Weight of a C-PC**: The weight of a C-PC is the sum of weights of all the C-nodes and C-edges along the path.

**C-MWPC** (**Coalesced Maximum Weight Path Cover**): The C-MWPC is the C-PC with the maximum weight for all possible C-PCs on the C-AG. This maximum weight does not necessarily produce a unique path cover.

The algorithm starts with the original, uncoalesced AG, where each node is labeled as a C-node and by using the IG, the algorithm updates the C-nodes in both graphs through coalescing leading to the C-AG and the C-IG which keeps on changing dynamically as we coalesce more and more C-nodes. We first show that finding the best MWPC for a coalesced graph (called C-MWPC) is a hard problem. Next we attempt two heuristic solutions.

#### **LEMMA 1**: *The C-MWPC problem is NP-complete.*

**Proof**: C-MWPC can be easily reduced to the MWPC problem assuming a coalescence graph without any edge or a fully connected interference graph. Therefore, each C-node is an un-coalesced live range after value separation and C-PC is equivalent to PC. A fully

connected interference graph is possible, when all live ranges interfere with each other. Thus, the C-MWPC problem is NP-complete because the MWPC problem is NPcomplete [Liao 1995; 1996].

**LEMMA 2**: *The solution to the C-MWPC problem is no worse than the solution to MWPC.* **Proof**: Any solution to the MWPC is also a solution to the C-MWPC. But some solutions to the C-MWPC may not apply to the MWPC (if any coalescing were made).

### 3.6 Coalescence-based Offset Assignment for Single-AR

Since the C-MWPC problem is NP-complete, heuristic algorithms must be applied to seek solutions in a reasonable amount of time. As mentioned in Chapter 2.1, two types of heuristics can be introduced to achieve different objectives: either to reduce the cost on the access graph (using OpCost) or to get a smaller memory footprint (using OpSize).

### **3.6.1** OpCost, a Heuristic Algorithm to Minimize Cost

Our first heuristic algorithm, OpCost, is separated into 2 parts. First, a set of preiteration coalescence rules are applied to capture cases that are definitely profitable. Then, in an iterative loop, coalescing is done incrementally. In each iteration, two C-nodes are selected for coalescing and the base SOA solver (we use Liao's SOA algorithm [Liao 1995; 1996] with the tie-break rule [Leupers 1996]) is run repeatedly, until no more coalescing is possible. Finally, the minimal SOA cost is returned together with a node to C-node mapping and the memory layout assignment. We call this base SOA solver "BaseSOA" for short.

#### Pre-Iteration Coalescence Rules

The pre-iteration rules are applied before we do iterative coalescing. Applying these rules will not worsen the SOA cost in all cases. All these rules are with respect to the access graph (AG). Note that we can coalesce a pair of C-nodes only if the C-nodes do not have an interference edge between them.

**RULE 1**: Coalesce all degree-0 C-nodes with any other C-node. Doing so will not affect the SOA cost.

**RULE 2**: Coalesce all degree-1 C-nodes with its neighbor. If its C-edge is already on the C-PC, the SOA cost is not affected, otherwise we reduce the SOA cost by the weight of this C-edge.

**RULE 3**: Coalesce all degree-2 C-nodes with the neighbor having a higher weight C-edge connected to it.

Rule 3 is explained in Figure 10. For C-nodes A, P, and Q, suppose the C-edge  $\langle A, P \rangle$  is heavier than the C-edge  $\langle A, Q \rangle$ . According to Rule 3, we should coalesce A with P. Assume there is a C-PC solution without coalescing A with P. Figure 10(a) to Figure 10(d) show 4 cases of that C-PC for C-edge  $\langle A, P \rangle$  and  $\langle A, Q \rangle$ . In Figure 10(a), none of the 2 C-edges is a part of C-PC, so the coalescence will reduce the cost of the SOA solution by Weight( $\langle A, P \rangle$ ). In Figure 10(b),  $\langle A, P \rangle$  is already on the C-PC and the cost remains unchanged. Similarly, when only  $\langle A, Q \rangle$  is on the C-PC (Figure 6.c), we improve the SOA solution by Weight( $\langle A, P \rangle$ ). And, if both of them are on the C-PC (Figure 10(d)), the cost is unchanged. Therefore, in each case, coalescing A with P can only improve (or cause no change to) the total weight of the C-PC before A and P are coalesced but will never worsen the solution.

Figure 10. Profitability of Rule 3 Coalescence

# Saving Due To Coalescence

After applying pre-iteration rules, we start to iterate. In each step of the iteration, we pick two C-nodes with maximum calculated saving and coalesce them. The basic idea is to use the current C-PC offset assignment to estimate savings if the 2 C-nodes were coalesced. For example, Figure 11(a) shows a C-AG with 8 nodes. The thick line is the current C-PC of the C-AG. If we coalesce d with g, C-edge <h,d> will now be on the C-PC, and C-edges <c,d> and <d,e> will be eliminated. C-edge <g,d> is also saved after d is merged with g. So, the total saving is W(h,d)+W(g,d)-W(d,e)-W(d,c) = 1, where W(<i,j>) is the weight of a C-edge <i,j>. In other words, the SOA cost is reduced by 1 if we coalesce d with g. In Figure 11, we illustrate 3 different cases to coalesce J with I. Figure 11(a) is a general case.

We save:

- The weight of the C-edge between I and J.

- The weight of all C-edges from I's neighbors (on the path cover) to J, i.e. C-edges <C,J> and <P,J> if they exist.

We lose:

• The weight of all C-edges from J's neighbors (on the C-PC) to J, i.e. C-edges <D,J> and <Q,J> if they exist.

Figure 11. Cases to Calculate the Savings

Figure 12(b) is a special case where if I and J are already neighbors on the C-PC, then the weights of both C-edges  $\langle I,Q \rangle$  and  $\langle J,P \rangle$  are saved. In Figure 12(c), I and J have a common neighbor C. Then, the weight of the C-edge  $\langle C,J \rangle$  is not a loss.

Figure 12. Coalescence Cases Based on Previous C-PC

# Tie-Break for the Same Savings

If two or more pairs of C-nodes have the same coalescence savings, we apply a tie-break rule. This tie-break rule is similar to the one used in [Leupers 1996] to select

edges with the same weight during the construction of path covers. In our case, for each coalescence candidate  $\{c_1, c_2\}$ , the tie-break weight T is calculated as:

### $T = \Sigma$ weight (all C-edges joined to $c_1$ and/or $c_2$ )

A smaller T has higher priority, as explained in [Leupers 1996]. T reflects the graph density, and we want a smaller graph density because that would more likely bring about a better MWPC solution. C-edge  $\langle c_1, c_2 \rangle$  (if it exists) is only counted once. In our benchmarks, this rule breaks all ties and improves the results slightly.

#### The Coalescence Algorithm

The whole coalescence algorithm is shown in Figure 13. Coalesce\_OA\_Single\_AR takes a C-AG and a C-IG as input (here, the original AG and IG are passed to this function), and returns the minimal SOA cost and a node to C-node mapping. From the node mapping, we can easily generate the final C-AG, C-IG and C-PC solution.

Coalesce\_OA\_Single\_AR contains two while loops. The first while loop tries to coalesce C-node pairs that are neighbors on the C-AG, until the largest calculated saving is zero, or when no more C-nodes pairs can be coalesced. The second while loop then exploits all remaining coalesceable C-node pairs, until no coalesceable C-node pairs can be found. Our coalescence framework works aggressively to reduce the number of C-nodes. Function Soa\_Cost runs BaseSOA to find the SOA cost for the current C-AG. Notice that, the second loop coalesces even when the calculated saving is not positive. This is because our savings calculation is only a heuristic formula. After re-running the SOA solver, we may get a different C-PC, which may have an even lower SOA cost.

```

Input: C-AG, C-IG

Output:

a. The minimal soa cost.

b. A node map from original node to its C-node.

1. Coalesce_OA_Single_AR(C-AG, C-IG) {

2.

Apply_Pre_Iteration_Rules();

3.

min_soa_cost = Soa_Cost (C-AG);

4.

min_node_map = a one to one map

5.

do {

6.

find two C-nodes satify: a.Do not interfere

b.Connected on C-AG

c.With max_saving

7.

if(max_saving>0) {

coalesce C-nodes, update C-AG, C-IG

8.

9.

if(Soa_Cost(C-AG) < min_soa_cost)</pre>

record as min_soa_cost, min_node_map.

10.

}

11. } while(max_saving>0)

12. while (there are C-nodes we can coalesce) {

find two C-nodes satisfy: a.Do not interfere

13.

b.With max_saving

coalesce C-nodes, update C-AG, C-IG,

14.

coalesce C=noues, update

if(Soa_Cost(C=AG)< min_soa_cost)</pre>

15.

record as min_soa_cost, min_node_map.

16.

17.

}

18.

19. }

return min_soa_cost, min_node_map;

```

Figure 13. Coalescence-based Offset Assignment for Single-AR

The reason we have two separate while loops is that usually, a lower node degree density gives a lower SOA cost; thus, coalescing neighboring C-node pairs will less likely increase the node degree density. In this manner, we try to drive coalescence via a limited graph topology property i.e. the node degree; more complicated solutions are possible but may not yield much benefit due to the complexity of the problem.

# SOA Cost Fluctuation During Algorithm Execution

To illustrate how SOA cost fluctuates during the two while loops, we show the SOA cost vs. iteration steps in Figure 14. Data in the figure are collected from one of the procedures called "findcost" in benchmark Twolf. In our experience, the SOA cost progression is very random and fluctuates greatly. This figure only gives its trend roughly.

It takes 90 coalescences for procedure 'findcost' to finish the two while loops. The thick vertical line at iteration 31 marks the end of the first whole loop and the start of the second while loop. 'findcost' has a starting SOA cost of 144, and a minimum SOA cost of 115 achieved at iteration 44. Therefore, the minimum SOA cost is achieved during the early part of the second while loop, which is commonly observed in most procedures.

Figure 14. SOA Cost Fluctuation Along with Iterations for Twolf Procedure 'findcost'

Note that the final SOA cost achieved might not be the lowest SOA cost ever achieved by the algorithm. If we want to place emphasis on optimizing for code size rather than stack size, we can remember the information for the case when the lowest SOA cost was ever achieved, and then revert to that solution at the end of all coalescing.

# 3.6.2 OpSize, a Heuristic Algorithm to Minimize Size

The second heuristic algorithm attempts to minimize the number of C-nodes so the program will have a small memory footprint at runtime. The heuristic consists of two distinct phases. The first phase is minimal coloring of the IG. Nodes with the same color are coalesced on both the AG and the IG. The following lemma says minimal coloring of the IG is equivalent to achieving minimal number of C-nodes after coalescence.

**LEMMA 3**: The minimal number of C-nodes after node coalescence is equal to the minimal number of colors required to color the IG. Furthermore, a coloring scheme of the IG is equivalent to a legal C-node formation.

**Proof:** A coloring scheme of the IG can be directly applied to a C-node formation by assigning nodes with the same color in the IG to the same C-node. The number of C-nodes is the number of colors for the IG. Similarly, a C-node formation can be directed to a coloring scheme by coloring the nodes in the same C-node with the same color and nodes in different C-nodes with different colors. Since nodes in the same C-node do not interfere with each other, i.e. no edge exists between them on the IG. Therefore, the two problems are equivalent and minimal coloring is the same as minimal number of C-nodes we can get.

We use a simple coloring algorithm similar to the one used for the Chaitin style register allocation [Chaitin 1981; Chaitin 1982]. When removing nodes from the IG and pushing them onto the coloring stack, we always remove the one with lowest degree first. Since coloring is performed on the IG, nodes with the same color are guaranteed to be coalesceable. After the coloring phases, an SOA solver (no coalescence) is applied on the resulting C-AG and C-IG to assign offsets for coalesced nodes.

Aggressive coalescing might possibly lead to higher SOA costs. However, our experiments show the OpSize heuristic still performs better than the baseline SOA solver

without variable coalescence. Compared with OpCost, OpSize is less effective in lowering the SOA cost but achieves greater stack size reduction.

#### 3.7 Coalescence-based Offset Assignment for Multiple-AR

The Multiple-AR model allows more than one AR to utilize the auto-modify mode. With the trend in embedded processor design to increase the number of ARs, multiple-AR model is playing a more and more important role in optimizing compilers to generate efficient code. In Motorola DSP56300, the AR is the general purpose register, and one of the 8 ARs is used as stack pointer. The other 7 ARs can be allocated for other purposes to hold variables. If one could solve the problem of address register assignment with fewer registers, the remaining address registers can be used for other purposes.

Generally, previous work on offset assignment for Multiple-AR (or GOA) [Liao 1995; Leupers 1996] all attempts to separate variables into several group, so that each group can be served with one AR. Here, we define *AR Group* as a group of variables that are allocated to one AR. With variable coalescence, our algorithm not only needs to partition variables into AR Groups, but also should coalesce them properly.

As Single-AR, Multiple-AR can be optimized towards two objectives. Both OpCost and OpSize require a heuristic algorithm to coalesce and partition variables into AR Groups, however as shown in 4.b, OpSize has an additional phase to minimally color the IG. We will discuss these phases in the following sections.

### 3.7.1 Coalescence Algorithm for Multiple-AR

Figure 15 shows the algorithm called Coalesce\_OA\_Multiple\_AR. This algorithm is invoked by both OpCost and OpSize. The only difference is, for OpSize, a graph

coloring algorithm first coalesces nodes on the graphs aggressively, and then Coalesce\_OA\_Multiple\_AR works afterwards if an optimal solution cannot be obtained immediately.

```

Input: AG, IG, K-number of ARs

Output:

a. The minimal GOA cost.

b. A mapping from node to its C-node.

c. A mapping from C-node to AR number.

V: node set, contains all nodes initially

G_1, G_2, ..., G_k: AR Groups, i.e. a set of C-nodes

1. Coalesce_OA_Multiple_AR(AG, IG, K) {

2.

G_1 = G_2 = ... = G_k = \Phi;

з.

//add each node to an AR Group

while(V is not empty) {

4.

mini_set=$\Phi; min_cost=MAX_INT;

5.

6.

//build mini_set

foreach node v in V{

7.

8.

cost=minimal add-on cost to put in one of

9.

the G<sub>i</sub> by running Coalese_OA_Single_AR on G<sub>i</sub>.

if (cost == min_cost) {

10.

11.

add (v,i) to mini_set;

}else if(cost<min_cost) {</pre>

12.

mini_set={(v,i)}; min_cost=cost;

13.

14.

}

15.

}

//tiebreak

16.

17.

foreach pair (v, i) in mini_set{

w1(v) = sum(weight < u, v > on AG) u M_G_1 G_2 ... G_k - G_i

18.

19.

w2(v) = number of v's neighbors on the IG

20.

21.

keep only pairs with maximal w1 in mini_set(tie break on w1)

22.

if(|mini_set|>1)

keep only pairs with smallest w2 in mini_set(tie break on w2)

23.

if(|mini_set|>1)

24.

25.

still have tie, pick one randomly.

26.

27.

for selected pair (v, i) add v to G_i

28.

remove v from AG and IG

29.

30.

run Coalese_OA_Single_AR on all G<sub>i</sub>

31.

return 1) the GOA cost as the sum of all SOA costs

32.

2) mapping from node\rightarrowC-node, C-node\rightarrowAR number

33. }

```

Figure 15. Coalescence Algorithm for Multiple-AR

Initially, the algorithms stores all nodes in set V and all AR Groups  $G_1,G_2...G_k$  are empty. In the while loop from line 4 to line 29, during each iteration, one node in V is assigned to an AR Group. The while loop has two main parts. The first part builds up the mini\_set. It attempts to put each node to each AR Group and calculate the extra cost that

will be incurred by calling Coalesce\_OA\_Single\_AR (Figure 13) on that AR Group. We should find a (v, i) pair so that assigning node v to AR Group Gi incurs minimal add-on cost, however it may happen that several pairs have the same minimal add-on cost. If so, there will be multiple entries in mini\_set and the second part picks one entry through a 3-step tie-break scheme.

The tie-break scheme we use shares some features with the tie-break GOA algorithm in [Leupers 1996]. We calculate two values for tie-break. Value  $w_1$  is calculated for each entry in mini\_set. If v is selected for Gi, we sum all the edges on the AG from v to a node that is in  $G_1 \cap G_2$ ..  $\cap G_k$  -  $G_i$ . Since, the edge from v to any node in AR Groups other than G<sub>i</sub> are eliminated as we illustrated in the motivation example, we prefer a larger w<sub>1</sub>. If this still cannot break all ties, we try another value w<sub>2</sub>. w<sub>2</sub> is calculated for each node v as the number of neighbors that are still on the IG. Larger w<sub>2</sub> means more interference with the nodes that have not been added to one of the ARs. We prefer a smaller w<sub>2</sub>, which means more nodes on the IG later can be coalesced with v. If both tie-breaks fail, we just randomly pick one from the remaining entries in mini\_set. Our experiments show this rarely happens. Finally, the algorithm calls Coalesce\_OA\_Single\_AR (Figure 13) for each AR Group. It returns a node to C-node mapping and a C-node to AR Group number mapping.

#### 3.7.2 OpSize Algorithm for Multiple-AR

Since aggressive variable coalescence can greatly reduce the number of C-nodes on the graph, with multiple ARs, in many cases, we can actually get the optimal solution. The following lemmas specify when the optimal solution can be achieved. **LEMMA 4**: *If there are only two C-nodes on the C-AG, then the SOA cost is optimal.* **Proof:** Since there is only one C-edge on the C-AG, so this C-edge must be on the C-MWPC. Hence, the SOA cost is 0.

**LEMMA 5**: If there are K address registers available for use and the number of C-nodes is no more than 2K, we can get the optimal solution, i.e. GOA cost=0 by assigning no more than two C-nodes to each address register.

**Proof:** Following the Lemma, the SOA problem for each address register is optimal zero SOA cost. The GOA cost is equal to the sum of the SOA cost for all address registers, so the GOA cost is also 0. Therefore, the solution is optimal.

As we know, the IG constrains the nodes from being coalesced (AG affects the cost but can be disregarded when minimizing the C-node number). From Lemma 3 and Lemma 5, we have the following corollary.

**COROLLARY 1**: If we can color an IG with 2K colors, then there is an optimal solution, i.e. GOA cost=0 with K address registers.

Notice that, Corollary 1 is only a sufficient condition. Even when the color number is greater than 2K, we may still get an optimal solution by first aggressively coalescing the nodes followed by the coalescence algorithm (the Coalesce\_OA\_Multiple\_AR algorithm in Figure 15) on the resulting C-AG and C-IG.

Like Single-AR, we use a simple coloring algorithm similar to the one used for Chaitin style register allocation.

To quantify the number of times we can get optimal solutions with certain number of address registers, we did experiments on 10 benchmark programs. All data pertains to local variables. We count the number of procedures that can be optimally solved in cases of 1) after IG coloring, and 2) after both coloring and Coalesce\_OA\_Multiple\_AR. This count gives the final number of optimal solutions. As mentioned earlier, Corollary 1 only gives a sufficient condition, i.e. even if an AG has more than two nodes, its SOA cost can still be zero, or the GOA cost can still be zero if the IG is not 2K-colorable. So, the final number of optimal solutions could be larger than the one obtained from IG coloring.

Table 1. Percentage of Optimal Solutions for Multiple-AR

| #AR       | Epic  | Gsm   | G721  | Mpeg2d | Mpeg2e | Bzip2 | Gzip  | Mcf   | Twolf | Vpr   | Average |

|-----------|-------|-------|-------|--------|--------|-------|-------|-------|-------|-------|---------|

| 2 (color) | 84.9  | 85.56 | 76.92 | 82.68  | 63     | 52.38 | 85.15 | 80    | 62.94 | 65.83 | 73.94   |

| 2 (final) | 86.8  | 90    | 96.15 | 90.55  | 77.23  | 87.18 | 90.1  | 93.33 | 79.19 | 82.01 | 87.25   |

| 3 (color) | 90.57 | 93.33 | 96.15 | 91.34  | 81     | 87.2  | 90.1  | 93.34 | 76.1  | 85.25 | 88.44   |

| 3 (final) | 94.34 | 97.78 | 100   | 94.49  | 88.12  | 92.31 | 96.04 | 100   | 89.85 | 94.24 | 94.72   |