## COMPREHENSIVE VARIATION-AWARE AGING SIMULATOR FOR LOGIC TIMING AND SRAM STABILITY

A Dissertation Presented to The Academic Faculty

by

Taizhi Liu

In Partial Fulfillment of the Requirements for the Degree Ph.D. in the School of Electrical and Computer Engineering

> Georgia Institute of Technology May, 2017

## **COPYRIGHT © 2017 BY TAIZHI LIU**

## COMPREHENSIVE VARIATION-AWARE AGING SIMULATOR FOR LOGIC TIMING AND SRAM STABILITY

Approved by:

Dr. Linda Milor, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Azad Naeemi School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Sung Kyu Lim School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Abhijit Chatterjee School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Jye-Chyi (JC) Lu School of Industrial and Systems Engineering *Georgia Institute of Technology*

Date Approved: [April 3rd, 2017]

Dedicated to my loving parents, who guided me to where I am today.

And to my wife and my daughter, who made me a better person.

## ACKNOWLEDGEMENTS

I would like to express my special thanks to my advisor, Professor Linda S. Milor, for her guidance and advice during my Ph.D. study. I would also like to thank Professor Azad Naeemi and Professor Sung Kyu Lim for their helpful suggestions and for their time being on my reading committee. I am also very grateful to Professor Abhijit Chatterjee and Professor Jye-Chyi Lu, both of whom have agreed to serve on my dissertation committee.

I would like to express my thanks to all the lab members, Dr. Fahad Ahmed, Dr. Chang-Chih Chen, Dr. Woongrae Kim Dr. Soonyoung Cha, Kexin Yang, Rui Zhang, Daehyun kim for their collaboration, and valuable comments and feedback.

I would like to extend special thanks to my wife and my best friend, Jing Lu, for her unconditional love and support. I would also like to thank my newly born daughter, Natalie Liu, who made me a dad and a better person. I am also very thankful to my parents, Xinglai Liu and Jinfeng Zhu, who have always been on my side, for their love and encouragement throughout my life.

Last but not least, I would like to thank all the professors, teachers, families, and friends who guided me to become the person that I am today.

# **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | iv                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | vii                                                         |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |

| LIST OF SYMBOLS AND ABBREVIATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             |

| SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xiii                                                        |

| 1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                           |

| <ol> <li>Related Work</li> <li>Gate-Delay Modeling</li> <li>Statistical Timing Analysis</li> <li>Aging Analysis of Circuit Timing Due To BTI, HCI and GOBD</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8<br>8<br>9<br>11                                           |

| <ol> <li>Device-Level Wearout Mechanisms</li> <li>Bias Temperature Instability (BTI)</li> <li>Hot Carrier Injection (HCI)</li> <li>Gate Oxide Breakdown (GOBD)</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13<br>13<br>14<br>15                                        |

| <ul> <li>4. Standard Cell Characterization and RC Interconnect Characterization</li> <li>4.1 Standard Cell Characterization <ul> <li>4.1.1 Variation Modelling</li> <li>4.1.2 Input Capacitances of Standard Cells</li> <li>4.1.3 Approximations of Interconnect RC Networks Using Moments Matching</li> <li>4.1.4 Sensitivity of the Pi-Model and the H'(s)-Model to Variations of Input Capacitances in the Fanout Gates</li> <li>4.1.5 Gate-Delay Characterization using Multivariate Adaptive Regression Spline (MARSP)</li> <li>4.1.6 Experimental Results</li> </ul> </li> <li>4.2 Interconnect Characterization</li> </ul> | 22<br>22<br>23<br>27<br>33<br>es<br>34<br>38<br>43          |

| <ul> <li>5. Monte Carlo Based Framework for Circuit-Level Statistical Timing Anlays</li> <li>5.1 Block-Based Statistical Timing Analyzer</li> <li>5.1.1 Implementation</li> <li>5.1.2 Experimental Results</li> <li>5.1.3 Complexity analysis</li> <li>5.2 Paths-Based Statistical Timing Analyzer</li> <li>5.2.1 Implementations</li> <li>5.2.2 Experimental Results</li> <li>5.2.3 Complexity</li> <li>5.3 Block-Based and Path-Based Combined Statistical Timing Analyzer</li> <li>5.3.1 Implementations</li> </ul>                                                                                                            | is 44<br>44<br>45<br>48<br>48<br>49<br>50<br>51<br>52<br>52 |

| 5.3.2 Experimental Results                                              | 53  |

|-------------------------------------------------------------------------|-----|

| 5.3.3 Complexity                                                        | 56  |

| 6. Aging Simulation For State-Of-Art Microprocessors                    | 58  |

| 6.1 Extraction of the Stress, Thermal, IR-Drop and Process profiles     | 58  |

| 6.2 Proposed PVT-Aware Aging Simulator                                  | 63  |

| 6.3 Lifetime Analysis Considering Realistic Workloads                   | 66  |

| 6.4 APPLICATION: Finding Optimum Operating Voltages Using Propose       | ed  |

| Aging Simulator                                                         | 72  |

| 7. SRAM Lifetime Analysis for Different Cache Configurations            | 79  |

| 7.1 SRAM Stability                                                      | 81  |

| 7.2 SRAM Lifetime Characterizations                                     | 83  |

| 7.3 Activity Extraction of SRAM cells                                   | 84  |

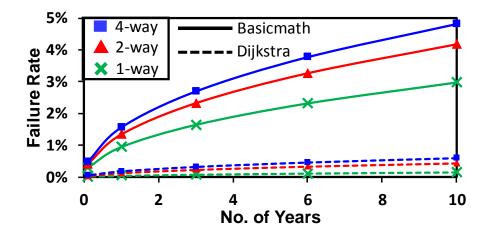

| 7.4 Performance-Reliability Analysis for Different Cache Configurations | 91  |

| 7.4.1 Associativity                                                     | 92  |

| 7.4.2 Cache Line Size                                                   | 96  |

| 7.4.3 Cache Size                                                        | 97  |

| 7.4.4 Replacement Algorithm                                             | 97  |

| 7.4.5 Error Correcting Codes (ECC)                                      | 98  |

| 7.5 Conclusions                                                         | 99  |

| 8. Conclusions                                                          | 101 |

| 8.1 Conclusions of This Research                                        | 101 |

| 8.2 Future Work                                                         | 102 |

| REFERENCES                                                              | 103 |

# LIST OF TABLES

| Table 1  | – Variations and corners of PVT parameters                                                                       | 22 |

|----------|------------------------------------------------------------------------------------------------------------------|----|

| Table 2  | <ul> <li>Accuracy comparison using fixed input capacitance vs. variational<br/>input capacitance.</li> </ul>     | 26 |

| Table 3  | - Variations and Corners of Pi-model and H'(s)-model                                                             | 38 |

| Table 4  | - Comparison of MARSP and quadratic models on representative standard cells.                                     | 39 |

| Table 5  | <ul> <li>Experimental results of validating the proposed gate-delay models<br/>on ISCAS85 benchmarks.</li> </ul> | 42 |

| Table 6  | – Comparison of the first 10 circuit paths extracted from our Block-<br>Based StTA and STA                       | 46 |

| Table 7  | - Implementation of Path-Based StTA                                                                              | 50 |

| Table 8  | - Implementation of Block-Based and Path-Based Combined StTA                                                     | 53 |

| Table 9  | – Experimental results of the proposed StTA analyzer on ISCAS85 benchmarks.                                      | 55 |

| Table 10 | - Experimental results of the proposed StTA analyzer on large circuits.                                          | 55 |

# LIST OF FIGURES

| Figure 1  | – The framework of the proposed PVT-aware aging simulator.                                                                        | 3  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2  | - Stress-time windows of NBTI, PBTI and HCI for an inverter.                                                                      | 15 |

| Figure 3  | – Defect generation in the gate dielectric layer based on a 2D percolation model for SBD and HBD paths.                           | 17 |

| Figure 4  | - Time distribution of defect generation in SiO2.                                                                                 | 18 |

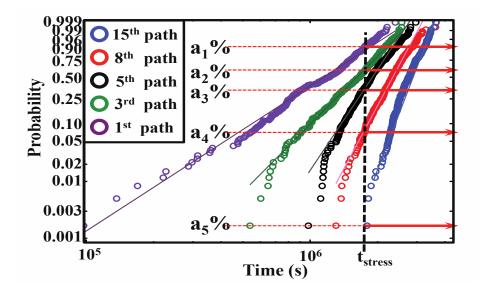

| Figure 5  | – Probability of the kth SBD path for a fixed gate size and as a function of time.                                                | 19 |

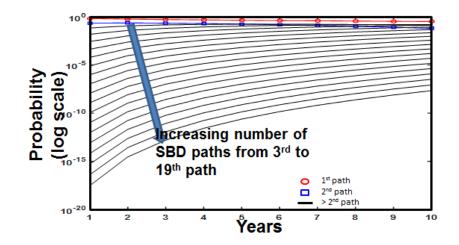

| Figure 6  | – SBD resistance as a function of the number of SBD paths.                                                                        | 20 |

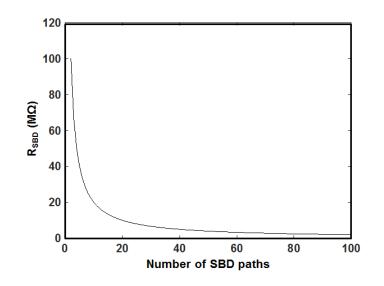

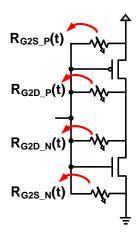

| Figure 7  | - Device-level GOBD soft breakdown model used in this work.                                                                       | 21 |

| Figure 8  | - The impact of SBD on ring oscillator performance.                                                                               | 21 |

| Figure 9  | - Input capacitances of standard cells, as well as the interconnect network, construct the load of previous gate.                 | 24 |

| Figure 10 | - Circuit used to characterize input capacitances of standard cells.                                                              | 25 |

| Figure 11 | – Y'(s) in Pi-model as an approximation of original input admittance function Y(s).                                               | 28 |

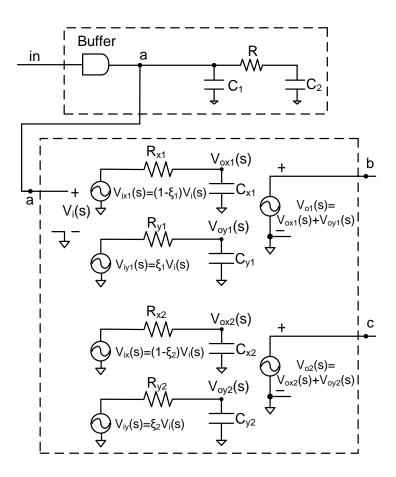

| Figure 12 | – An illustration of single-stage timing analysis with a Pi-model for gate analysis and an H'(s)-model for interconnect analysis. | 31 |

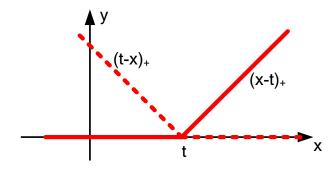

| Figure 13 | - The solid line denotes the form of the hinge function $(x-t)$ + while the dashed line denotes the hinge function $(t-x)$ +.     | 35 |

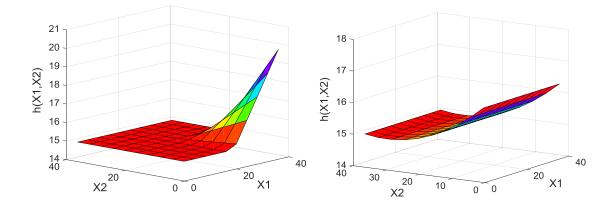

| Figure 14 | – The efficiency and accuracy of MARSP model is shown for a non-<br>linear case.                                                  | 38 |

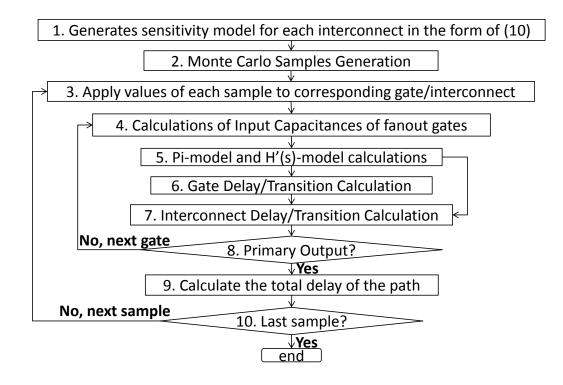

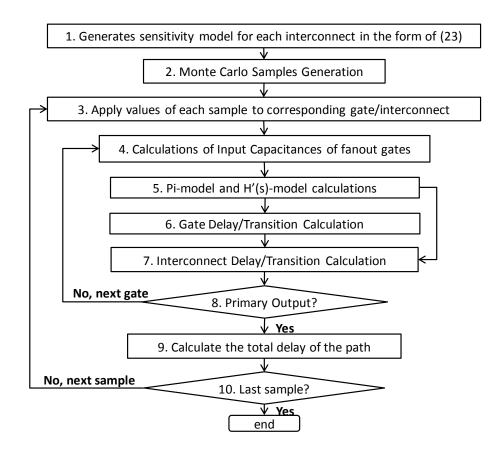

| Figure 15 | – Flow graph of the implementation which applies gate-level models to path-delay analysis.                                        | 41 |

| Figure 16 | - Experimental results of validating the proposed gate-delay models on a 43-stage test path.                                      | 42 |

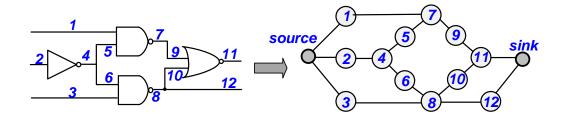

| Figure 17 | – Abstraction of a timing graph from a combinational circuit.                                                                     | 45 |

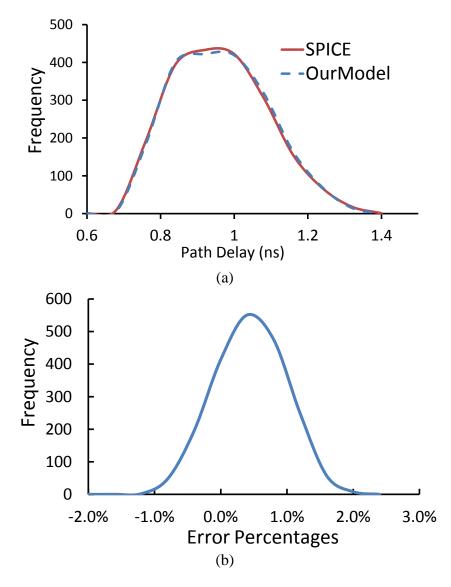

| Figure 18 | - Comparison of the circuit delay distributions of circuit c499 from SPICE using STA and our block-based StTA. (2000 samples were run.)                                                                   | 47 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 19 | – The runtime per sample versus the number of gates and interconnects in block-based StTA.                                                                                                                | 48 |

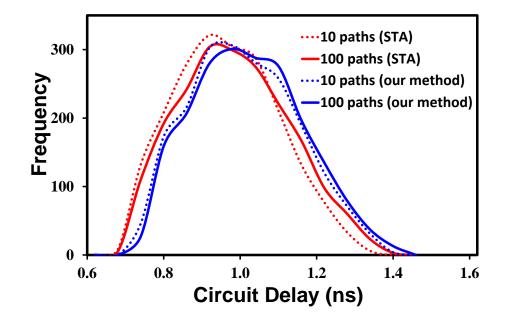

| Figure 20 | – Flow graph of the implementation which applies gate-level models to path-delay analysis.                                                                                                                | 49 |

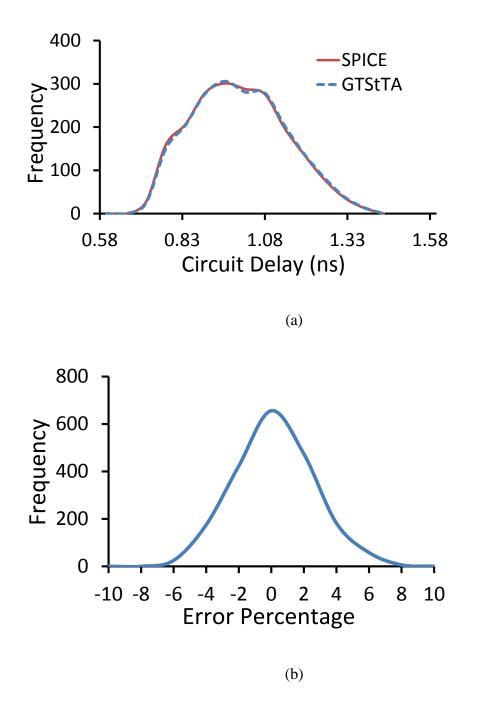

| Figure 21 | <ul> <li>– (a) Comparison of the circuit delay distributions of circuit c499 from SPICE (using different critical path pools). (2000 samples were run.). (b) The error distribution.</li> </ul>           | 51 |

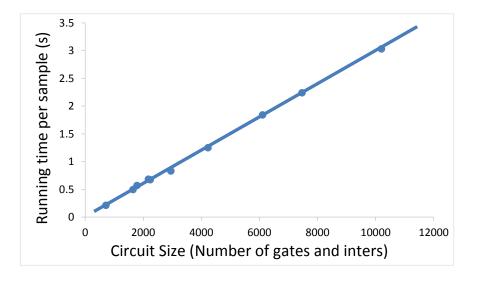

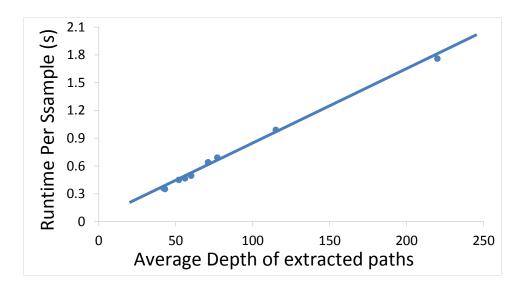

| Figure 22 | – The runtime per sample versus the number of gates and interconnects in paths-based StTA.                                                                                                                | 52 |

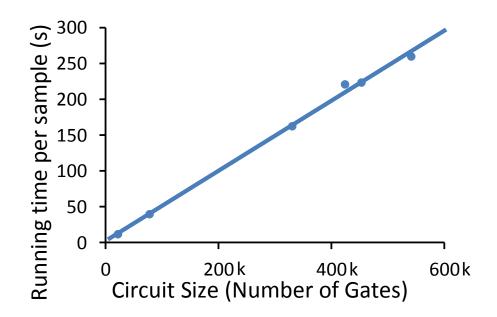

| Figure 23 | - The runtime per sample versus the number of gates and interconnects in the proposed block-based and paths-based combined StTA.                                                                          | 56 |

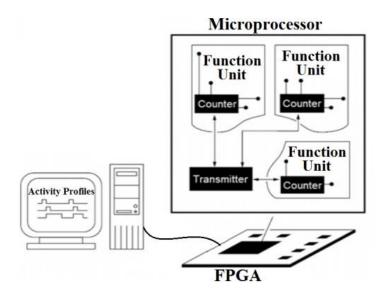

| Figure 24 | – The system used to collect activity profile of the microprocessor<br>contains an FPGA board that implements the microprocessor system<br>and exports data on the activity profile to a PC.              | 59 |

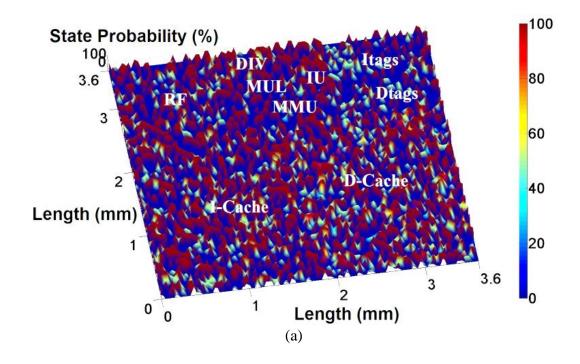

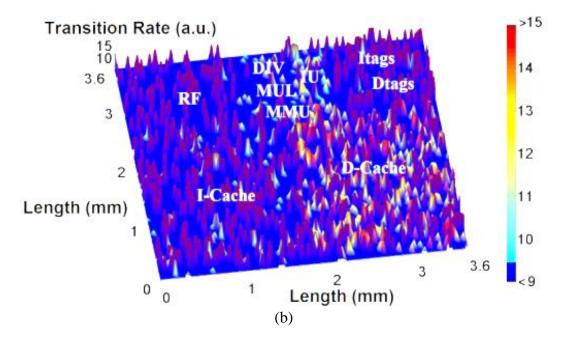

| Figure 25 | - (a) The distributions of the DC stress probability and (b) the transition rate (toggle rate) for the LEON3 microprocessor while running a standard benchmark.                                           | 61 |

| Figure 26 | – (a) The temperature and (b)VDD distribution of the LEON3 microprocessor running a standard benchmark.                                                                                                   | 62 |

| Figure 27 | - The flow chart of proposed aging simulator.                                                                                                                                                             | 63 |

| Figure 28 | – The framework of the PVT-aging-aware timing engine.                                                                                                                                                     | 64 |

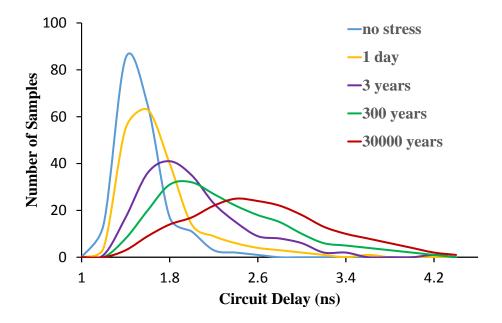

| Figure 29 | – The delay distributions of a RISC microprocessor due to the combined effect of PVT and aging under a variety of stress times.                                                                           | 65 |

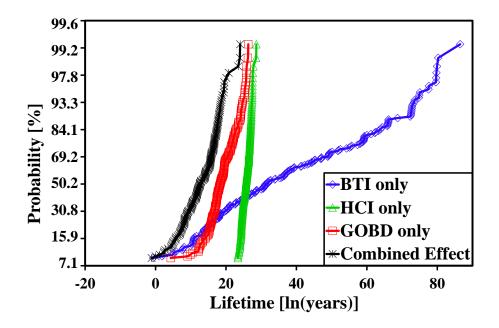

| Figure 30 | – The lifetime distributions of the LEON3 microprocessor due to BTI, HCI, GOBD and the combined effect.                                                                                                   | 66 |

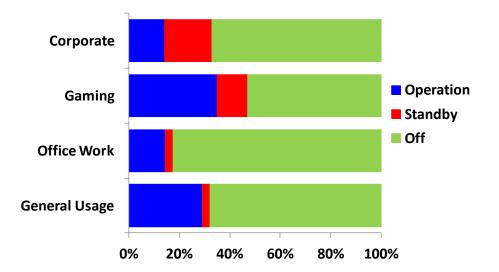

| Figure 31 | - The use scenarios provided by Intel are shown [87].                                                                                                                                                     | 67 |

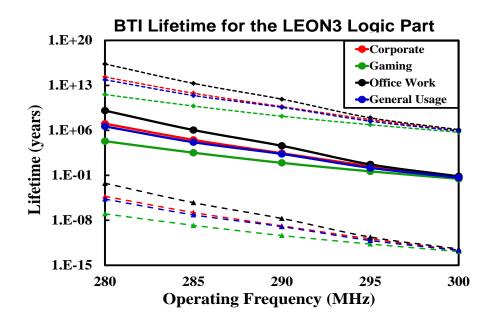

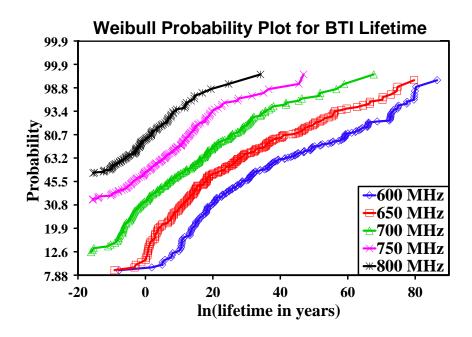

| Figure 32 | – The estimated lifetimes of the LEON3 microprocessor due to BTI<br>for different use scenarios and different system frequencies. Dotted<br>lines show the boundaries when considering process variation. | 68 |

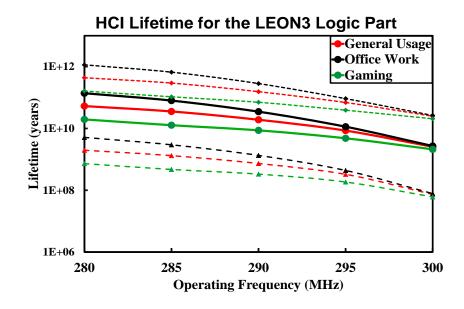

| Figure 33 | – The estimated lifetimes of the LEON3 microprocessor due to HCI<br>for different use scenarios and different system frequencies. Dotted<br>lines show the boundaries when considering process variation.                                              | 68 |

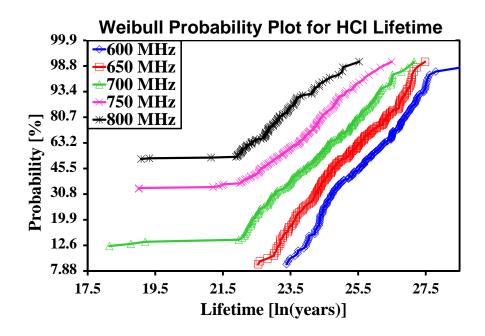

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

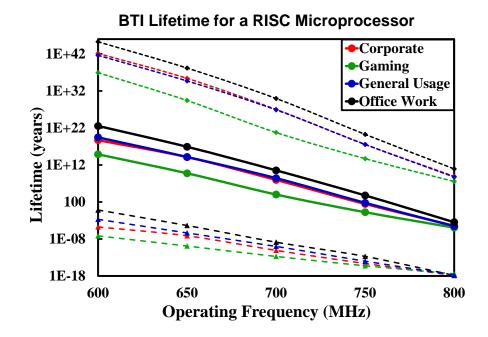

| Figure 34 | - The estimated lifetimes of the RISC microprocessor due to BTI for<br>different benchmarks and different system frequencies. Dotted lines<br>show the boundaries when considering process variations.                                                 | 69 |

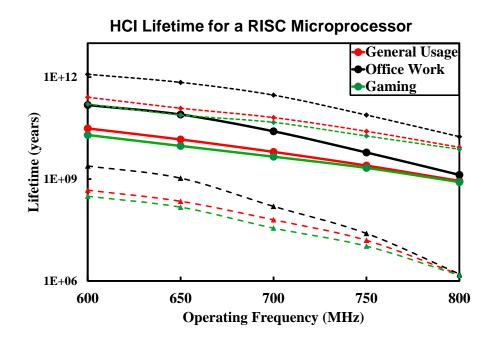

| Figure 35 | - The estimated lifetimes of the RISC microprocessor due to HCI for<br>different benchmarks and different system frequencies. Dotted lines<br>show the boundaries when considering process variations.                                                 | 70 |

| Figure 36 | – The statistical lifetime distribution of the RISC microprocessor due to BTI for different system frequencies, for the gaming use scenario.                                                                                                           | 70 |

| Figure 37 | – The statistical lifetime distribution of the RISC microprocessor due to HCI for different system frequencies, for the gaming use scenario.                                                                                                           | 71 |

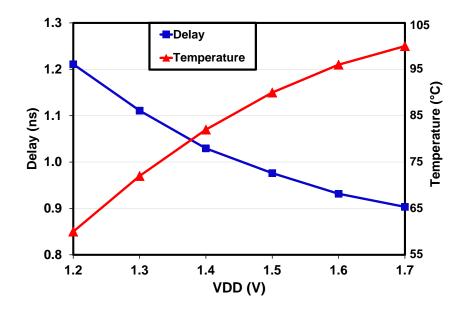

| Figure 38 | - Chip temperatures while LEON3 is running at different voltages and circuit delays at each corresponding VDD/Temperature condition.                                                                                                                   | 73 |

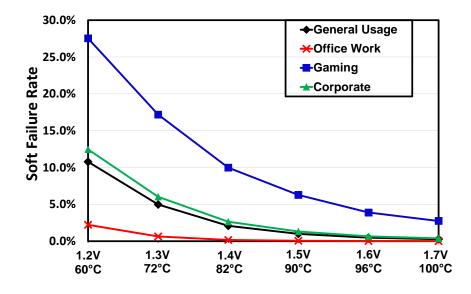

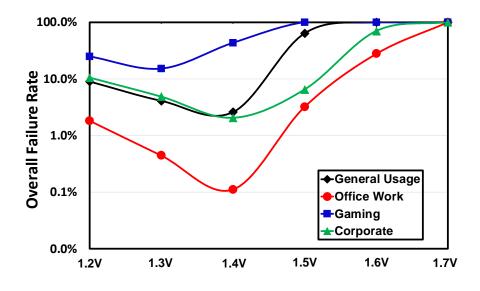

| Figure 39 | – The soft failure rate in 10 years due to timing violations for different operating voltages and for different usage scenarios when ambient temperature is set to 27 $^{\circ}$ C.                                                                    | 74 |

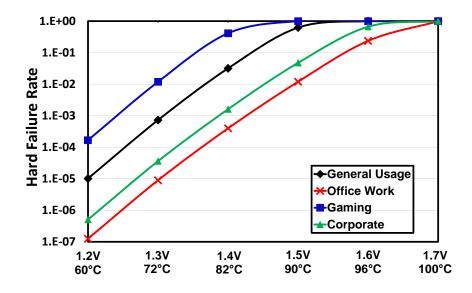

| Figure 40 | – The hard failure rate in 10 years due to the permanent GOBD hard breakdown are shown for different operating voltages and for different usage scenarios when ambient temperature is set to 27 $^{\circ}$ C.                                          | 74 |

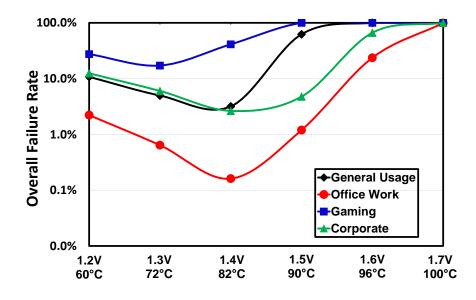

| Figure 41 | – The overall failure rate in 10 years due to both soft failure and hard failure is shown for different operating voltages and for different usage scenarios when ambient temperature is set to 27 $^{\circ}$ C.                                       | 76 |

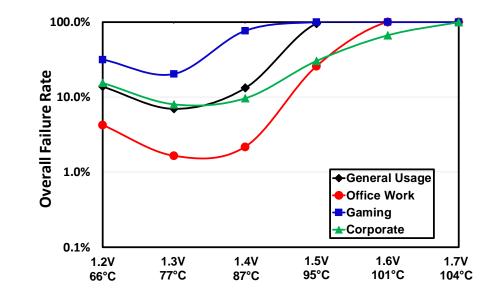

| Figure 42 | – The overall failure rate in 10 years due to both soft failure and hard failure is shown for different operating voltages and for different usage scenarios when the ambient temperature is set to 40 $^{\circ}$ C.                                   | 76 |

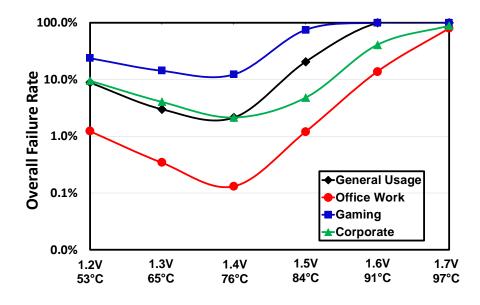

| Figure 43 | – The overall failure rate in 10 years due to both soft failure and hard failure is shown for different operating voltages and for different usage scenarios when the ambient temperature is set to 15 $^{\circ}$ C.                                   | 77 |

| Figure 44 | – The overall failure rate in 10 years due to both soft failure and hard failure is shown for different operating voltages and for different usage scenarios when the ambient temperature is set to 27 $^{\circ}$ C and the IR-drop effect is ignored. | 77 |

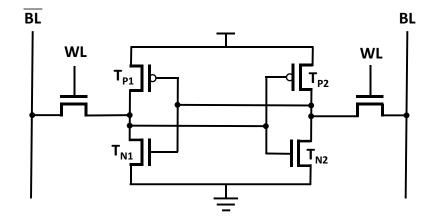

| Figure 45 | – A typical 6T SRAM cell.                                                                                                                                                                                                                                               | 82 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

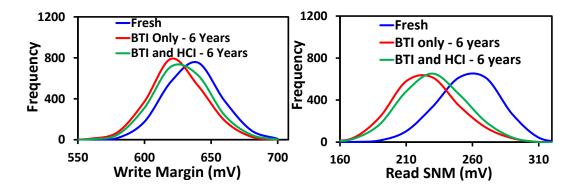

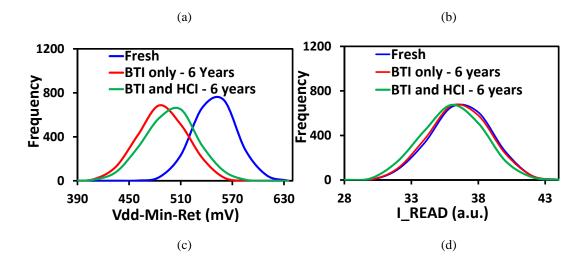

| Figure 46 | – The degradation of the write margin, the read SNM, the Vdd-min-<br>ret, and the IREAD of a memory cell due to BTI, BTI and HCI,<br>shown in (a)-(d), respectively.                                                                                                    | 84 |

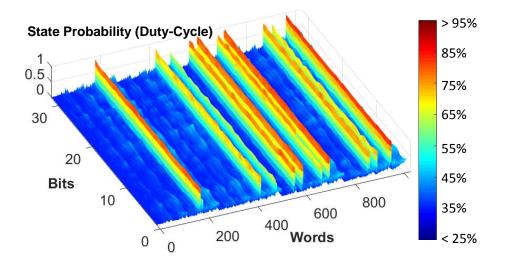

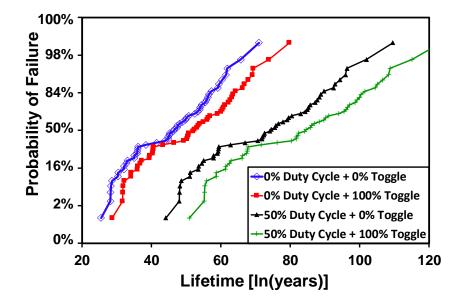

| Figure 47 | <ul> <li>(a) The distribution of state probability for the 32KB data cache shown in 1024 words; (b) The histogram of the state probability distribution in the number of SRAM cells.</li> </ul>                                                                         | 85 |

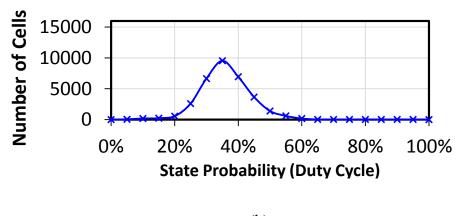

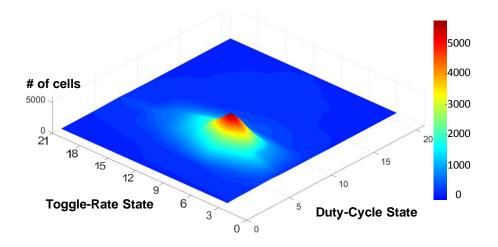

| Figure 48 | <ul> <li>(a) The distribution of transition rate for the 32KB data cache shown in 1024 words; (b) The histogram of the transition-rate distribution in the number of SRAM cells.</li> </ul>                                                                             | 86 |

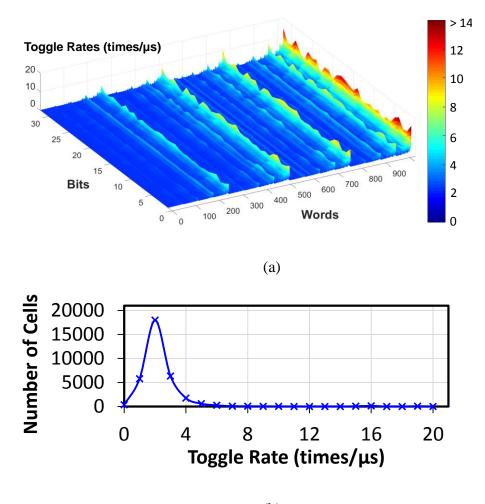

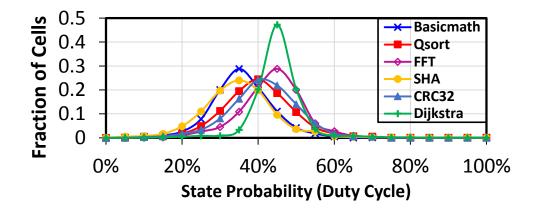

| Figure 49 | – An example of a stress-state distribution for a 32KB memory is shown. A stress state is a combination of the duty-cycle state and the toggle-rate state, when the combined effect of BTI and HCI is considered. The z axis is the number of cells.                    | 88 |

| Figure 50 | - The lifetime distribution of a SRAM cell when it's in a specific stress state. Each stress state is a combination of the duty-cycle state and the toggle-rate state. Four stress states are shown in this figure.                                                     | 89 |

| Figure 51 | – The duty-cycle distributions of SRAM cells in a 2-way 32KB data cache, while the microprocessor is running six different benchmarks.                                                                                                                                  | 92 |

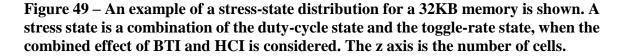

| Figure 52 | – The failure probability as a function of time for the three different associativities and two benchmarks.                                                                                                                                                             | 93 |

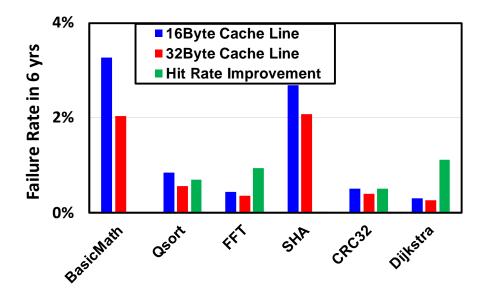

| Figure 53 | - The failure probabilities in 6 years for a 16 Byte cache line and a<br>32 Byte cache line for six applications. The hit-rate improvement is<br>also shown, defined as the improvement of using a 32 Byte cache<br>line compared to a 16 Byte line.                    | 94 |

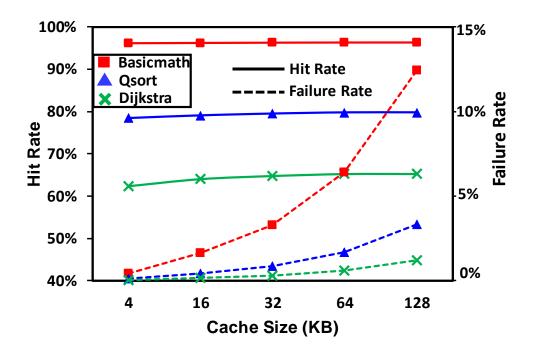

| Figure 54 | – The hit rate and the failure probability in 6 years are shown for five different cache sizes and for three applications.                                                                                                                                              | 94 |

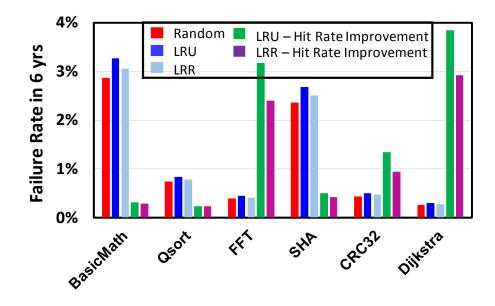

| Figure 55 | - The failure probabilities in 6 years for three different replacement<br>algorithms for six benchmarks, as well as the hit rate improvements<br>of LRU and LRR. The hit-rate improvement is defined as the<br>improvement compared to the 'Random' replacement policy. | 95 |

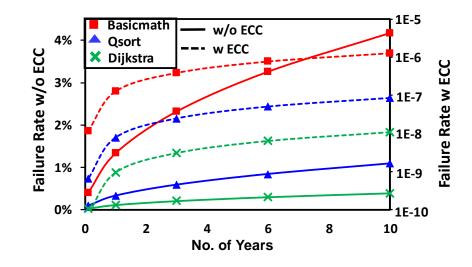

| Figure 56 | – The failure probabilities of the 2-way 32KB data cache with and without ECCs are shown as a function of time for three applications.                                                                                                                                  | 95 |

## LIST OF SYMBOLS AND ABBREVIATIONS

- BTI Bias Temperature Instability

- CAD Computer-Aided Design

- CRC Cyclic Redundancy Check

- ECC Error Correcting Codes

- FEOL Front-End-Of-Line

- FPGA Field-Programmable Gate Array

- GCV Generalized Cross Validation

- GOBD Gate Oxide Breakdown

- HCI Hot Carrier Injection

- L1 First-Level

- MARSP Multivariate Adaptive Regression Splines

- PDK Process Design Kit

- PVT Process-Voltage-Temperature

- **RISC** Reduced Instruction Set Computing

- RSM Response Surface Methodology

- RV Random Variable

- SPICE Simulation Program with Integrated Circuit Emphasis

- SRAM Static Random Access Memories

- STA Static Timing Analysis

- StTA Statistical Timing Analysis

- TDDB Time-Dependent Dielectric Breakdown

### SUMMARY

The purpose of this research is to develop a framework which analyzes circuit-level reliability and evaluates the lifetimes of complex systems like state-of-art microprocessors. The novelty of the proposed work lies on its statistical timing analyzer and the ability to handle the combined effect of a variety of front-end-of-line (FEOL) wearout mechanisms, while including both the manufacturing process variability and the real-time uncertainties in workload and ambient conditions like operating temperature and IR drops. Overall, the proposed framework presents the correlation between circuit performance (speed) and circuit lifetime, which enables circuit designers to avoid excessive guard-banding, by using a better understood reliability budget to achieve higher performance.

Historically, research work on aging effect is active mainly within the communities of device and reliability physics. The relative lack of design knowledge and aging-aware CAD tools further creates a barrier for managing the impact of device degradation on circuit performance. This work not only bridges the gap between device-level wearout mechanisms and circuit-level performance degradations, but also takes into account the impact of software usage on hardware reliability 0–[14]. The timing analyzer in this work is the first attempt in the literature to achieve a comprehensive process-voltage-temperature-aging-aware statistical timing analysis (StTA) while considering the effect of several FEOL wearout mechanisms (bias temperature instability (BTI), hot carrier injection (HCI), gate oxide breakdown (GOBD)) simultaneously. Because of this contribution, one paper of this research received the Best Paper Award at ESREF 2015 (European Symposium on Reliability of Electron Devices, Failure Physics, and Analysis).

Front-end-of-line (FEOL) wearout mechanisms (BTI, HCI, GOBD) degrade transistor characteristics as a function of stress probability. A FPGA-based emulation platform has been developed to determine the activity and stress-state profiles while the emulated systems are running benchmarks. The activity and stress-state profiles are then used to determine the IR-drop profiles and the thermal profiles of a system. Taking into account the detailed voltage, thermal and electrical stress profiles, the degradations of transistor characteristics for each device within the system are calculated according to the device-level wearout models. More specifically, BTI and HCI are modeled as degradations of transistor threshold voltage while GOBD is modeled as degradations of gate-to-source and gate-to-drain resistance.

Then, a unified gate-delay model is proposed to link device-level degradations and the gate delays. The gate-delay model includes the following parameters: channel length, threshold voltage, GOBD breakdown resistances, supply voltage, temperature, input slew and Pi-model parameters (for the RC load). Among them, the threshold voltage of each transistor combines the effect of process variation, BTI, and HCI, while the GOBD breakdown resistances of each transistor represent the GOBD effect. A method, called multivariate adaptive regression splines (MARSP), is employed to characterize the gate delay as a function of these parameters. MARSP is well-suited for capturing essential nonlinearities and interactions in a high-dimension parameter space.

Based on the unified gate-delay models, a statistical timing engine is developed to estimate the variability of circuit-performance degradation due to the aging effect when PVT variations are present. The proposed timing engine consists of two parts: a blockbased analyzer and a path-based analyzer. The block-based analyzer performs PVT-agingaware critical path extraction, and the path-based analyzer performs accurate circuit-delay estimation of the extracted paths.

Using the statistical timing engine, a framework of circuit-level aging assessment has been constructed. The proposed framework determines the detailed electrical stress profiles, thermal profiles and IR-drop profiles of each device within the system under study. Combining these profiles and device wearout models, the statistical timing engine is applied to characterize microprocessor performance degradation and assess system lifetime. Moreover, the lifetime estimates take into account realistic use scenarios which include active, standby, and sleep modes.

Overall, this work presents cross-layer solutions that enable aging analysis of large complex microprocessors, which run realistic workloads. Additionally, this work addresses challenges that arise to attain accurate aging-aware gate-delay models especially when the dimension of the involved parameters is high. It's the first attempt to have a comprehensive aging simulator which handles the effect of BTI, HCI and GOBD simultaneously while also taking into account the workloads, ambient conditions and manufacturing variability 0–[5]. The framework presented here manages to assess aging of the entire design under realistic usages, and enables designers to tighten excessive guard-banding while still meeting the reliability requirements 0–[13].

## 1. INTRODUCTION

The aggressive scaling of CMOS technology not only brings benefits of speed and power, but also poses challenges to circuit designers because of the ever-increasing manufacturing variability and reliability issues. The challenge is further compounded by the real-time uncertainties in workload and ambient conditions, which dynamically influence the circuit degradation rate. To improve design predictability and guarantee system lifetime, it's essential to have accurate aging simulation tools for reliability.

It is very challenging to accurately characterize circuit performance degradation due to device reliability in the presence of Process-Voltage-Temperature (PVT) variations for a complex system. A common way to deal with this in industry is to add an extra guardband for aging on top of the worst PVT corners. The guard-band is set by assuming that all the transistors receive the worst-case stress conditions. However, adding excessive guard-banding sacrifices the performance of microprocessors and creates headaches in timing closure.

The purpose of this research is to present a solution to assess the lifetimes of complex systems like state-of-art microprocessors, while taking into account the effect of PVT variations and a variety of Front-end-of-line (FEOL) device wearout mechanisms. The proposed aging simulator achieves accurate statistical timing analysis to study the combined impact of aging effect, manufacturing variability, ambient conditions and realistic workloads 0–[13]. It presents the relationship between circuit performance (speed) and circuit reliability, and gives insights for designers to achieve optimal tradeoff between performance and reliability. Moreover, circuit designers can benefit from the proposed

work to avoid excessive guard-banding to achieve higher performance while still maintaining the required reliability.

The device wearout mechanisms studied in this work are Bias Temperature Instability (BTI), Hot Carrier Injection (HCI), and gate oxide breakdown (GOBD). BTI is a wearout mechanism which causes the threshold voltage, Vth, of CMOS transistors to increase over time under voltage stress, resulting in a temporally-dependent degradation of digital circuit delay. HCI also degrades the threshold voltage of the transistors under stress. From the perspective of circuit operation, HCI and BTI stress have different time windows. HCI stresses devices only during the dynamic switching period when current flows through the device, whereas BTI stresses devices as a function of logic state.

GOBD, also time-dependent dielectric breakdown (TDDB), is another reliability concern for CMOS devices. When the gate dielectric layer abruptly loses its insulating properties, it's called hard breakdown (HBD), and HBD can be detected as a large jump in the current versus time curve. Prior to hard breakdown, GOBD involves soft breakdown (SBD) where the leakage current in the gate dielectric slightly increases with time, while the gate dielectric still retains its insulation property. It's well understood that GOBD causes gate delay degradation as the transistors gradually weaken before hard breakdown happens. Eventually, the degraded circuit will fail to work when the delay exceeds the clock period.

To take into account the susceptibility of circuit performance to reliability and variations, statistical timing analysis (StTA) is needed to be PVT and aging aware to assure the design meets timing specifications and the reliability requirements before committing

a design to manufacture. The objective of StTA is to determine the distribution of the circuit delay with acceptable accuracy and reasonable runtime. In the circuit, each transistor undergoes different workload, different temperature and different voltages, which means that each transistor ages differently. In order to achieve accurate timing analysis, the gate-delay model has to be properly characterized to take into account the effect of different PVT parameters and different aging conditions of transistors in the gate. As circuit integration increases dramatically, the complexity of large circuits make it very challenging to perform accurate PVT-aging-aware timing analysis.

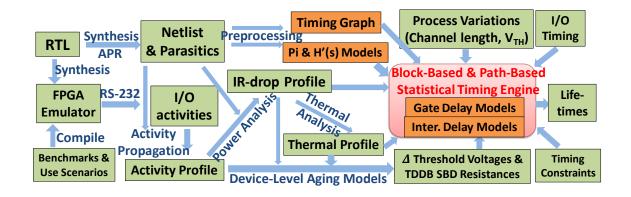

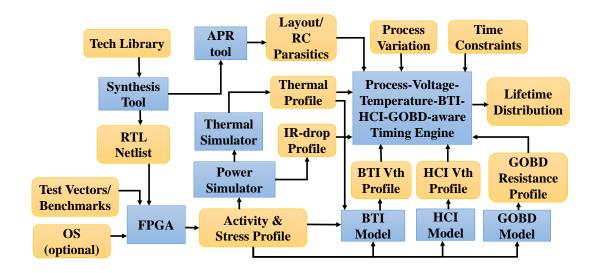

Figure 1 – The framework of the proposed PVT-aware aging simulator.

The big picture of the proposed aging simulation framework is shown in Figure 1. Because the wearout mechanisms being studied are activity, supply voltage (VDD) and temperature dependent, the research has utilized FPGA emulation to efficiently acquire electrical, thermal and IR-drop profiles for large systems like microprocessors. Simulating a large system on FPGA emulation platform takes only a few minutes to complete, while running Register-Transfer Level (RTL) simulations to extract the activity profiles of each net might take a few months to simulate a single benchmark. The RTL is firstly synthesized and loaded to the FPGA with the Xilinx ISE (Integrated Software Environment). Once the FPGA is programmed, the activity can be collected by placing counters at the I/O ports to track the state probabilities and the toggle rates of the ports during application runtime. Since the I/O ports for each unit can be found on the top of each module, the counters are attached to the ports automatically with a scripting language. The activity transportation unit is inserted into the RTL automatically as well. The RTL is also synthesized for layout generation. Using the RC information from the layout, the net activities, and the computed power profile (via a power simulator), the thermal profile throughout the microprocessor is computed using a thermal simulator. The net activities and layout are also used to determine the IR-drop profile throughout the microprocessor.

For process variations, the proposed work includes inter-die, intra-die, and intra-gate variations supporting any distribution and any correlation profile between different parameters. The process variations due to channel length ( $\Delta L$ ) and threshold voltage ( $\Delta Vth$ ) for each transistor are considered. Because BTI and HCI also impact the threshold voltage, the threshold voltage for each transistor is a combination of variation due to the process, BTI and HCI, while  $\Delta L$  is only due to process variations.

The degradations of each transistor in the circuit are calculated according to the device-level wearout models and the extracted electrical stress, thermal, IR-drop, and process profiles. As BTI and HCI both cause threshold voltage shifts, it's straightforward to combine their effect. However, it's not straightforward to further include GOBD as there is a clear gap between circuit timing and GOBD. This research bridges this gap by using a unified gate-delay model based on Multivariate Adaptive Regression Splines (MARSP)

method 0–[3]. MARSP is well suited for capturing essential nonlinearities and interactions in a high-dimension space. The proposed gate-delay model links device-level wearout models and the gate delays. The gate-delay models include many parameters, including PVT and wearout parameters. Among them, the threshold voltage of each transistor combines the effect of process variation, BTI, and HCI, while the GOBD breakdown resistances of each transistor represent the GOBD effect.

The electrical stress, thermal, IR-drop, and process profiles. and RC parasitics, and the degradation profiles, generate all the parameters for each gate which are needed to calculate the gate delays. Based on the unified gate-delay models, a statistical timing engine is developed to estimate the variability of circuit-performance degradation due to the aging effect when PVT variations are present. The proposed timing engine consists of two parts: a block-based timing analyzer and a path-based timing analyzer. The blockbased timing analyzer performs PVT aging-aware critical path extraction, and the pathbased timing analyzer performs accurate circuit-delay estimation of the extracted paths.

The statistical timing engine proposed in this work is achieved based on the Monte Carlo (MC) method. Monte Carlo StTA sufficiently samples the random parameter domain based on the Metropolis sampling algorithm. For each sample, the circuit delay is computed using traditional static timing analysis (STA) based on gate-delay models. If a sufficient number of samples are drawn, the circuit-delay distribution is obtained. The Monte Carlo approach has the advantage of being completely general, having the ability of handling any kind of parameter distribution, and any correlations between different parameters. Monte Carlo StTA also has the advantage of accuracy, and it is universally used as a reference to validate the accuracy of probabilistic StTA implementations. The disadvantage of MC StTA is the high runtime cost due to the required sample size. There have been some existing efforts to reduce the large sample size of MC StTA using reduced sampling techniques, such as quasi-Monte Carlo [15], Latin hypercube [16], importance sampling [17], and the Karhunen-Loeve expansion model [18]. Moreover, the Monte Carlo method intrinsically facilitates parallel computation, like multi-threading. As nowadays a great deal of computational resources is available, many computation-intensive approaches become practical. As it's shown in this thesis, the runtime of the proposed aging-aware StTA framework is very acceptable.

The proposed PVT-aging-aware statistical timing engine performs the analysis of circuit timing degradation. The timing engine generates the delay degradation at a variety of stress times. Lifetimes can then be calculated according to the specified operating frequency. When the circuit delay of the aged circuit exceeds the clock period, the amount of stress time is marked as the chip lifetime.

Overall, this research work has proposed a framework of aging simulation to estimate the lifetimes of complex systems like state-of-art microprocessors while considering the combined effect of process variations, workloads, ambient conditions, and a variety of FEOL wearout mechanisms. The results of this aging simulators can present some insights to circuit designers for them to get the optimal trade-offs between performance and reliability. This thesis also applies the proposed aging simulator for finding the optimum operating voltage which can achieve the best lifetime for reliability-critical applications

The rest of the thesis is organized as follows. Chapter 2 gives some background knowledge followed by a survey of the related work. Chapter 3 presents the device-level

wearout models that are used in this research. Chapter 4 gives the flow of standard cell characterization and how the MARSP method is used in the gate-delay modeling. Chapter 5 utilizes the MARSP-based delay models to construct a Monte-Carlo based Statistical Timing Analyzer which combines the advantages of both block-based method and path-based method. Chapter 6 presents the framework of the proposed aging simulator, and presents the methodology of how to efficiently evaluate performance degradation of a microprocessor due to BTI, HCI and GOBD, simultaneously. In Chapter 7, the proposed aging simulator is extended to study the relationship between performance and reliability of the cache memory for different cache configurations. Chapter 8 concludes this thesis.

## 2. RELATED WORK

This chapter surveys prior related work in three aspects: gate-delay characterizations for standard cells, statistical timing analysis, and aging analysis due to BTI, HCI and GOBD.

### 2.1 Gate-Delay Modeling

There are many existing works on standard cell characterization using both the traditional method [19]–[23] and the emerging current source-based method [24]–[28]. Except for [20],[21], all methods evaluate only the accuracy in characterizing a single cell. And [20],[21] consider only a single benchmark circuit, without determining the accuracy of their method with respect to SPICE.

This research uses a method of standard cell characterization consisting of three models: an input capacitance model for standard cells, a sensitivity model for variational resistive-capacitive loads, gate delay and interconnect delay models via multivariate adaptive regression splines (MARSP). This is the first time that MARSP has been applied to standard cell characterization.

MARSP is an adaptive procedure for multivariate nonparametric regression. That is, it doesn't take a predetermined form, but it constructs the model structure according to the information derived from the data. The MARSP technique is well suited for high-dimensional problems while capturing essential nonlinearities and interactions. Due to its adaptive nature, MARSP can 'filter out' the negligible parameters without manual intervention. For a complex cell containing over 40 devices, the categorization (or

clustering) of switching/non-switching devices and on-transition/off-transition/nontransition devices used in [19],[22] is cumbersome. MARSP can reduce this effort by automatically capturing essential parameters and removing negligible parameters through its intelligent process.

#### 2.2 Statistical Timing Analysis

Statistical timing Analysis can be categorized into two board classes: Monte Carlo (MC) method and Probabilistic method. Monte Carlo method is based on sample-space enumeration while Probabilistic method is based on statistical operations between random variables (RVs).

Probabilistic StTA models gate delay and arrival times as RVs and propagates arrival time through the circuit via statistical sum and maximum operations. Probabilistic StTA has drawn much attention and research effort due to its runtime advantages. However, it has proven to be challenging to efficiently model skewness in the arrival-time distribution which results from nonlinearity of gate delays and the statistical maximum operation. Much effort [29]–[34] has tried to address these issues.

Monte Carlo StTA sufficiently samples the probability regions based on the Metropolis sampling algorithm [35]. For each sample, the circuit delay is computed using gate-delay models in which canonical first-order or quadratic model is usually used. Although for each sample the computed circuit delay can be either an overestimate or an underestimate, the error in estimating the circuit-delay distribution is acceptable if a sufficient number of samples are drawn. Monte Carlo StTA has the advantage of being completely general. [36] has shown that Monte Carlo StTA is accurate even in scenarios

with high dimensionality and non-Normal distributions in the process variation space, where Probabilistic StTA has difficulties.

Monte Carlo based StTA is universally used to validate the accuracy of all practical probabilistic StTA implementations, but never used as a practical StTA method itself. The accuracy of Monte Carlo StTA relies on its large sample size, because the root-mean-square error in the estimate of circuit delay decreases as  $O(n^{-0.5})$  where n is the sample size [18]. The high runtime cost due to its required sample size has been the main hurdle preventing Monte Carlo StTA from being practical.

There have been some existing efforts to reduce the large sample size of Monte Carlo StTA using reduced sampling techniques, such as quasi-Monte Carlo [15], Latin hypercube [16], importance sampling [17], and the Karhunen-Loeve expansion model [18]. In this work, it proposes to reduce the sample size and the overall runtime cost by estimating the circuit delay of each sample with significant accuracy. In other words, the standard deviation of the error for each estimate is a function of the standard deviation of the error of each component, and if we reduce the standard deviation of the errors of the components, it becomes possible to reduce the sample size while achieving the same standard deviation of the error for the system.

The difficulties of extending gate-level characterization to circuit-delay approximation are from two sources. First, the output transition time of each gate propagates to be used as the input transition time of the subsequent gate. The transitiontime error is accumulated and magnified stage by stage, which further undermines the accuracy of circuit delay. Second, input capacitances of standard cells are part of the loads of previous stage cells. With process variations present, these input capacitances are variational, which causes the loads of previous stage gates to also be variational. If this variability of loads is neglected, this will cause transition time error and the error will be magnified stage by stage. This work proposes a framework consisting of sophisticated gate-level models to solve these difficulties. The proposed framework has significantly smaller error in estimating circuit delay, with accuracy verified with SPICE. Because of the accuracy of our framework for each sample, only limited samples are needed to get the circuit delay distribution and thus the runtime efficiency is improved significantly.

#### 2.3 Aging Analysis of Circuit Timing Due To BTI, HCI and GOBD

Many prior works have studied the impact of BTI on circuit timing [37]–[42]. [37] considers the effect of voltage, temperature and node switching activity, without considering process variations. [38] and [39] propose a framework to study the BTI effect using an iterative scheme to deal with the interdependence between temperature and power profiles, together with BTI degradation. [40] provides a probabilistic method to study the BTI effect using both the Reaction-Diffusion (R-D) and the Trapping-Detrapping (T-D) models. [41] and [42] analyze the impact of Negative Bias Temperature Instability (NBTI) on circuit timing using a Monte Carlo analysis technique and first order models of variation.

HCI stresses devices only during the dynamic switching period when current flows through the device, whereas BTI stresses devices as a function of logic state. The impact of HCI on circuit timing has been studied in several research efforts. [43] studies the impact of the HCI effect on the soft-error rate of small-scale digital circuits. [44] proposes a scalable approach for HCI degradation analysis using the Gaussian model for process variations and a first-order model for timing degradation.

Gate Oxide Breakdown (GOBD) involves soft breakdown (SBD) where the leakage current in the gate dielectric slightly increases with time, while the gate dielectric still retains its insulation property. It's well understood that GOBD causes gate delay degradation as the transistors gradually weaken before hard breakdown happens. GOBD has been widely studied at the transistor-level. However, less study has been focused on the gate level. In [45], an analytical model is presented to predict the delay of logic gates subject to GOBD. [46] analyzes the impact of GOBD on a 41-stage ring oscillator. Unfortunately, only small circuits, like ring oscillators, are studied.

As BTI and HCI both cause threshold voltage shifts, it's straightforward to combine their effect. [47] studied the combined effect of BTI and HCI on circuit timing. However, it's not straightforward to further include GOBD as there is a clear gap between circuit timing and GOBD. This work bridges this gap by using a unified MARSP-based gate-delay model. Therefore, the proposed framework can study the combined aging effect of BTI, HCI and GOBD.

## **3. DEVICE-LEVEL WEAROUT MECHANISMS**

#### **3.1** Bias Temperature Instability (BTI)

Bias Temperature Instability (BTI) includes Negative Bias Temperature Instability (NBTI) and Positive Bias Temperature Instability (PBTI). NBTI is the degradation of a pMOS device under negative gate stress, and PBTI is the degradation of an nMOS device under positive gate stress. BTI results in shifts in device parameters, such as threshold voltage, transconductance, device mobility, etc., but is generally associated with shifts in the threshold voltage.

The initial distribution of threshold voltages is generally assumed to be Normal. Recent experimental work has shown that the threshold voltage shift ( $\Delta V_{th}$ ) as a function of time under DC stress ( $t_{DC}$ ) is best modeled with trapping/de-trapping theory [48]:

$$\Delta V_{tp/tn}(DC) = \phi(T, E_F)(A + Bln(t_{DC}))$$

(1)

where, *A*, *B*, and  $\phi$  are constants.  $\phi$  is proportional to the number of available traps and is a function of temperature, *T*, and the Fermi level,  $E_F$ . The temperature dependence is incorporated in  $\phi(T, E_F)$ . The duty cycle,  $\alpha$ , impacts the shift and is incorporated as an effective Fermi level [49], where  $E_{F,eff} = \alpha E_{F,on} + (1 - \alpha)E_{F,off}$ , and  $E_{F,on}$  and  $E_{F,off}$  are Fermi levels when the device is on and off, respectively. The duty cycle accounts for the percentage of the time that the transistor is under stress, i.e., when the gate terminal of the NMOS device is at a HIGH voltage or the gate terminal of the PMOS device is at a LOW voltage. More specifically, if the duty cycle,  $\alpha$ , for a transistor is given, then the time under stress,  $t_{stress}$ , and the recovery time,  $t_{rec}$ , can be obtained as  $t_{stress} = \alpha \cdot t_{total}$ ,

$t_{rec} = (1 - \alpha) \cdot t_{total}$ , respectively, where  $t_{total}$  is the total time that the circuit is aging. Hence, overall,

$$\Delta V_{tp/tn} = \phi_0 e^{-E_F/kT} g(t_{stress} / (t_{stress} + t_{rec})) \cdot (A \qquad (2)$$

$$+ Bln(t_{stress} + t_{rec}))$$

where  $\phi_0$  is a constant. The constants were obtained from the experimental results in [50].

### 3.2 Hot Carrier Injection (HCI)

HCI describes the phenomenon by which carriers at a MOSFET's drain gain sufficient energy to be injected into the gate oxide and cause degradation of some device parameters. This occurs as carriers shoot out from the source of a MOSFET, accelerate in the channel, and experience impact ionization near the drain end of the device. Damage can occur at the interface, within the oxide and/or within the sidewall spacer. Interfacestate generation and charge trapping induced by this mechanism result in degradation of some MOSFET parameters, such as the threshold voltage, transconductance, channel mobility, and drain saturation current.

Historically, HCI was only a major concern for nMOS devices, with pMOS devices showing comparatively negligible degradation because (a) holes have a smaller impact ionization rate and (b) holes face a higher  $Si - SiO_2$  barrier than electrons. However, subsequent reports have revealed that HCI effects on pMOS devices have also been observed [51]. Since hot electrons are generated during logic transitions, the impact of HCI is directly proportional to the switching frequency. In this research, predictive HCI lifetime models under dynamic stress are used for long term performance-degradation simulations. The threshold voltage degradation due to HCI during stress time is modeled as [52]:

$$\Delta V_{tp/tn} = A_{HCI} (r_{trans} t_{stress} t_{trans})^n \tag{3}$$

where  $r_{trans}$  is the frequency-dependent transition rate,  $t_{stress}$  is the stress time,  $t_{trans}$  is the transition time, and  $A_{HCI}$  is a technology dependent constant that depends on the inversion charge, the trap generation energy, the hot electron mean free path, and other process-dependent factors. The data used in our study of HCI comes from the experimental data in [53],[54].

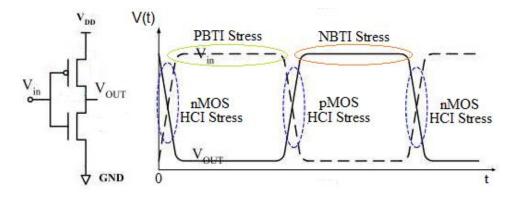

Figure 2 – Stress-time windows of NBTI, PBTI and HCI for an inverter.

From the perspective of circuit operation, HCI and BTI stress have different time windows. HCI stresses devices only during the dynamic switching period when current flows through the device, whereas BTI stresses devices as a function of logic state. The stress time windows of BTI and HCI for an inverter circuit are illustrated in Figure 2 as an example.

#### **3.3** Gate Oxide Breakdown (GOBD)

GOBD is one of the key reliability issues for CMOS devices. Stress induced leakage current (SILC) is induced by trap-assisted tunneling mechanisms where electrons pass from the cathode to the anode via defect sites (neutral traps) in the gate dielectric by the electrical field [55]–[58]. When the gate dielectric experiences partial breakdown, it is known as soft breakdown (SBD) [55],[59].

Experimental observations indicate that the mean time to failure is a function of the total gate oxide surface area, temperature, and gate voltage due to the weakest-link character of gate dielectric breakdown [60]. However, when abstracting this relationship to the system level, it is important to take into account details of circuit operation, not just the surface area. Moreover, circuits have been known to operate during breakdown [61]. In order to model circuit performance degradation under breakdown, time-dependent resistance models [62],[63] and time-dependent leakage current models [64] have been proposed for SPICE simulation. This research work uses time-dependent resistance models.

Using emulation, described in the next section, the devices are partitioned into groups that experience equivalent stress and temperature. More specifically, for an nMOS device, the time under stress is the time that the gate has the supply voltage applied. This time depends on the input patterns and the propagation of these patterns to each MOSFET. For each group of devices, the next step is to determine the number of devices experiencing different numbers of soft breakdown paths. This is done using the percolation model.

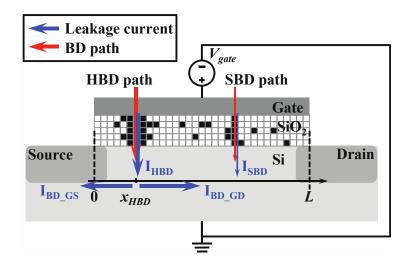

Figure 3 – Defect generation in the gate dielectric layer based on a 2D percolation model for SBD and HBD paths.

The percolation model (PM) concept involves placing neutral traps randomly within the gate dieelctric and analyzing the number of resistive conduction paths in a 2D matrix representing the gate dielectric layer [65], as shown in Figure 3. The 2D model have been expanded to 3D to count an accurate number of conduction paths in this research.

In the percolation model, the defect generation rate depends only on the gate voltage ( $V_G$ ) and temperature (T). Therefore, during electrical stress, the trap density in the gate dielectric increases with stress time t as a power law in the anode hole injection model. Stress is converted to a number of traps [66],[67]:

$$N_{trap}(t, V_G) = A \exp(BV_G) t^{\beta} \cdot \tau_{ox} WL \cdot \exp(-\theta T)$$

(4)

where *A*, *B*, and  $\beta$  are fitting constants, and  $\tau_{ox}$ , *W*, and *L* are oxide thickness, gate width, and length, respectively, and  $\theta \approx 0.01^{\circ}C^{-1}$  [67].

(b)

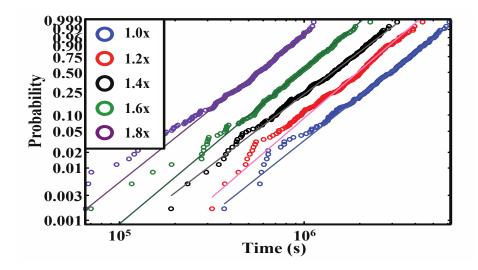

Figure 4 – Time distribution of defect generation in SiO2. (a) The probability distribution of the time of occurrence of the kth SBD path for different gate sizes. (b) The probability distribution of the number of SBD paths for a fixed gate size as a function of time.

Figure 4 shows the PM simulation results and the probability distribution of the time of occurrence of conduction paths in the oxide layer as a function of gate size (Figure

4(a)). It also shows the number of SBD paths as a function of time (Figure 4(b)). Then, as it's seen in Figure 4(b), if we know the stress duration of an applied gate voltage to a MOSFET, the probability of a fixed number of conduction paths can be estimated.

The results in Figure 4 indicate the probability that at least *n* paths are observed in the oxide. To find the probability that there are exactly *n* paths, it is necessary to subtract the  $n - 1^{st}$  curve from the  $n^{th}$  curve. A result is illustrated in Figure 5.

Figure 5 – Probability of the kth SBD path for a fixed gate size and as a function of time.

Note that the number of breakdown paths in the gate depends on the operating conditions. Hence, given a time under operation, the emulator determines the time under stress for each group of devices. This is used to look up probabilities of different numbers of SBD paths. The number of devices in the group multiplies the probabilities to estimate the expected number of devices with each number of breakdown events in the group.

The time under stress for the *i*<sup>th</sup> device is a function of bias. Let  $\alpha_i$ , where  $0 \le \alpha_i \le 1$ , be the fraction of time under stress for the *i*<sup>th</sup> device. Then,  $t_{stress,i} = t\alpha_i$ , where

*t* is the time under operation. Let  $p_i = f_{SBD(n)}(t_{stress,i})$  be a probability of *n* SBD paths for the *i*<sup>th</sup> device. Therefore,  $p_i = f_{SBD(n)}(t\alpha_i)$ . If the group of devices has *N* devices, then  $Np_i$  devices are randomly selected to have *n* breakdown paths at time *t*. Each sample randomly selects the devices experiencing SBD.

Next, for each breakdown path, the SBD leakage resistance is calculated with the QPC model [68],

$$R_{SBD} \cong V_G / \left[ \frac{4e}{h\alpha} N \cdot exp(-\alpha \Phi) \cdot sinh\left( \frac{\alpha e(V_G - V_0)}{2} \right) \right]$$

(5)

where  $\Phi = 3 \sim 4eV$ ,  $V_0 = 0 \sim 0.5V$ ,  $\alpha = 2 \sim 3eV^{-1}$ , *h* is Plank's constant, *e* is the electron charge, and *N* is number of SBD conduction paths [68]. The location of SBD, gate-to-drain vs. gate-to-source, is randomly selected. The resistance as a function of the number of SBD paths is illustrated in Figure 6.

Figure 6 – SBD resistance as a function of the number of SBD paths.

Figure 7 – Device-level GOBD soft breakdown model used in this work.

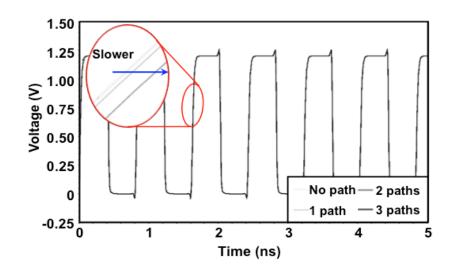

Figure 8 – The impact of SBD on ring oscillator performance.

In summary, the device-level GOBD model used in this work introduces two timedependent resistances for each transistor, shown in Figure 7. The impact of SBD on a ring oscillator is illustrated in Figure 8. It shows the waveform comparison of the case with no SBD path, one SBD path, two SBD paths and three SBD paths. It can be seen that more SBD paths result in larger delays, while not degrading signal swing.

## 4. STANDARD CELL CHARACTERIZATION AND RC INTERCONNECT CHARACTERIZATION

This chapter introduces the method for standard cell characterization and interconnect characterization. The proposed method incorporates three sophisticated gate-level models: an input capacitances model, a sensitivity model of variational resistive-capacitive loads, and gate and interconnect delay models via the multivariate adaptive regression splines (MARSP) method.

### 4.1 Standard Cell Characterization

### 4.1.1 Variation Modelling

| Var.            | Random<br>Variations    | Corners                     | Var.            | Random<br>Variations  | Corners     |  |

|-----------------|-------------------------|-----------------------------|-----------------|-----------------------|-------------|--|

| $\Delta L_p$    | Gaussian,<br>3σ=20%     | [-20%, 20%] ΔL <sub>n</sub> |                 | Gaussian,<br>3σ=20%   | [-20%, 20%] |  |

| $\Delta V th_p$ | Gaussian,<br>3σ=20%     | [-20%, 20%]                 | $\Delta V th_n$ | Gaussian,<br>3σ=20%   | [-20%, 20%] |  |

| ΔVdd            | Uniform, (-10%,<br>10%) | [-10%, 10%]                 | ΔT (°C)         | Uniform, (-50,<br>50) | [-50,50]    |  |

| Slope           | Uniform, (10ps,<br>3ns) | [10ps, 3ns]                 |                 |                       |             |  |

Table 1 – Variations and corners of PVT parameters

Table 1 presents the PVT parameters, where  $\Delta L$  denotes channel length variation,  $\Delta Vth$  denotes threshold voltage variation,  $\Delta Vdd$  denotes supply voltage variation,  $\Delta T$  is temperature variation, *Slope* is the input transition time, and the subscripts *p* and *n*  correspond to PMOS and NMOS devices, respectively. The percentages given in Table 1 are percentages of nominal values of the corresponding parameters. Corner information is given to facilitate later explanations.

The process parameters, namely  $\Delta L_p$ ,  $\Delta L_n$ ,  $\Delta Vth_p$ ,  $\Delta Vth_n$  in Table 1, correspond to each transistor. The value can be a combination of inter-die, intra-die, and intra-gate variation. The examples in this thesis consider inter-die variation for channel length and intra-gate variation for threshold voltage because lithography/etch has the strongest impact on channel length and random dopant fluctuations have the strongest impact on the threshold voltage. However, any process model with any between and within-die variation model can be implemented, including measured distributions and correlation profiles.

The voltage, temperature and slope parameters, namely  $\Delta V dd$ ,  $\Delta T$ , *Slope*, are applied to each cell. As will be shown in later sections, our method supports a temperature profile from a thermal simulator and a voltage profile from a power grid simulator which takes into account the IR-drop effects. Again, the temperature profile and voltage profile don't have to be a specific distribution. They could be any form of distribution with a correlation structure.

### 4.1.2 Input Capacitances of Standard Cells

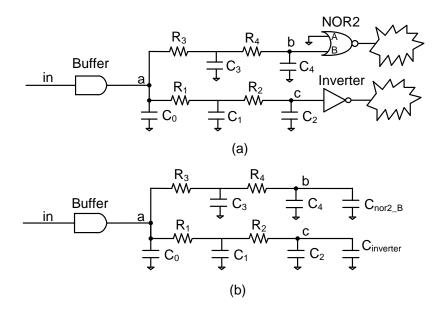

Figure 9 – Input capacitances of standard cells, as well as the interconnect network, construct the load of previous gate. (a) A buffer and its interconnect load. (b) The buffer with the variational model of the input capacitance of the next stage incorporated into its load.

Figure 9(a) illustrates a small patch of a gate-level circuit. The buffer gate in this example has two fanout gates, an inverter gate and a NOR2 gate. The load seen by the buffer is the interconnect network together with the input capacitances of its fanout gates, as shown in Figure 9(b). With fanout gates modeled as corresponding input capacitances, circuit-level timing analysis can be done stage by stage, in the way that each stage contains a standard cell and its connecting load as Figure 9(b) shows.

Figure 10 – Circuit used to characterize input capacitances of standard cells.

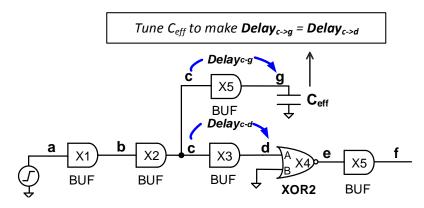

With PVT variations in consideration, it is not satisfactory to model input capacitances as fixed values [4]. The variations of standard cell input capacitances must be taken into account. This work presents a modeling method to get variation-aware equations of input capacitances of standard cells. Firstly, a test circuit is used to characterize the actual input capacitance. Figure 10 shows the case of input A of XOR2 gate, where  $C_{eff}$  is tuned until the delay from node c to node g is equal to the delay from node c to node d. The acquired value of  $C_{eff}$  is the input capacitance of input A of gate X4. X1 and X2 are used to produce a reasonable input slope at node c, and X5 is used as a load to prevent node e from switching excessively fast.

When PVT variations of gate X4 are present, the acquired values of  $C_{eff}$  vary. The PVT parameters in Table 1 are considered. That is, seven parameters are considered for an inverter gate, while eleven parameters are considered for a two-input gate. Central Composite Design [69], which uses the parameter corners in Table 1, is employed to design the experiments.

After the input capacitance of input A of gate X4 has been characterized with each experiment, a first-order linear regression equation can be found as follows:

$$C_{input\_cap} = k_0 + \sum_{i=1}^{n} k_i X_i$$

<sup>(6)</sup>

where *n* is the number of considered PVT parameters,  $k_0$  is the constant term,  $X_i$ , i=1,2,...,n denote considered PVT parameters, and  $k_i$ , i=1,2,...,n are the first-order sensitivity coefficients.

The input-capacitance model is tested in the context of Figure 9(b). Random variations of PVT parameters in Table 1 are applied to the three gates in Figure 9(a). *Slope* is only applied to the Buffer. Two methods are implemented to get the input capacitance used in Figure 9(b): one uses a fixed value for the pin capacitance from the standard cell library and the other uses the variational model in (6). The simulations were done using hSPICE [70], and the errors were obtained by comparing to the results from the circuit in Figure 9(a). Table 2 lists the average error of these two methods.

|                                     | Gate Delay Error<br>(node in to node a) | Interconnect Delay Error<br>(node a to node b) |

|-------------------------------------|-----------------------------------------|------------------------------------------------|

| Fixed Input<br>Capacitance model    | 5.88%                                   | 6.91%                                          |

| Proposed Input<br>Capacitance model | 0.32%                                   | -0.07%                                         |

Table 2 – Accuracy comparison using fixed input capacitance vs. variational input capacitance.

Please note that every input of a gate has its input capacitance. For example, a NOR2 gate has two input-capacitance models, for input *A* and input *B*, respectively. And for each input capacitance, scenarios for the rising-edge and the falling-edge are considered separately.

### 4.1.3 Approximations of Interconnect RC Networks Using Moments Matching

An RC interconnect is a linear system with one input and one or multiple outputs. The interconnect input could be a primary input or a gate output, while the interconnect outputs could be a primary output or inputs of its loading gates. Consider the interconnect network in Figure 9(a), node a is the interconnect input and node b and c are the outputs.

For an interconnect network, we denote its input admittance function as Y(s) and its transfer functions as  $H_1(s)$ ,  $H_2(s)$  ..., for each output. They can be expanded at s=0 using a Taylor series as follows (only showing one transfer function):

$$H(s) = m_0 + m_1 s + m_2 s^2 + m_3 s^3 + \cdots$$

(7)

$$Y(s) = y_0 + y_1 s + y_2 s^2 + y_3 s^3 + \cdots.$$

(8)

Here,  $m_0$ ,  $m_1$  ... are called the moments of H(s), while  $y_0$ ,  $y_1$  ... are the moments of Y(s). Please note that  $y_0$  is zero and  $m_0$  is one for RC trees [70]. The first, second and third moments of Y(s) are  $y_1$ ,  $y_2$  and  $y_3$  respectively, and  $m_1$ ,  $m_2$  and  $m_3$  are those for H(s) similarly. We use the modified nodal analysis (MNA) [70] method to generate moments in (7) and (8) via Matlab.

Reduced-order models are routinely used to replace the original large-order models. We will introduce the reduced-order model of Y(s) first, and then the reduced-order model of H(s).

### 4.1.3.1 Pi-model as an Approximation of Y(s)

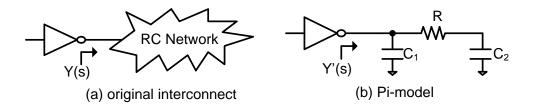

The Pi-model is the most popular reduced-order model to estimate the input admittance of RC interconnects. Figure 11 gives the structure of the Pi-model, where Y(s) denotes the input admittance of the original network and Y'(s) denotes the input admittance of the Pi-model.

# Figure 11 - Y'(s) in Pi-model as an approximation of original input admittance function Y(s).

The values of  $C_1$ , R, and  $C_2$  are obtained by equating the first, second, and third moments of Y(s) to the first, second and third moments of Y'(s), respectively. The equations for the Pi-model are as follows:

$$C_2 = y_2^2 / y_3 \tag{9}$$

$$R = -y_2/C_2^2 \tag{10}$$

$$C_1 = y_1 - C_2 \tag{11}$$

where  $y_1$ ,  $y_2$  and  $y_3$  are the first three moments of Y(s) in (8).

Thus, the sample space of the input admittance function of interconnect is reduced down to a three-parameter space. These three parameters  $C_1$ , R and  $C_2$ , plus PVT parameters in Table 1, construct the parameter space of standard cell characterization which is introduced later in Section 4.1.4. Specifically, ten parameters are included for the characterization of an inverter, while fourteen parameters are needed for the characterizations of BUF, NOR2 and NAND2.

### 4.1.3.2 <u>H'(s)-model as an Approximation of H(s)</u>

This work employs a stable two-pole (S2P) approximation [72] to get the reducedorder model of H(s). S2P preserves the first three moments of H(s) and more importantly guarantees the generated model is stable. The obtained model, H'(s), is a second-order model with two stable poles, where

$$H'(s) = \frac{k_1}{s+p_1} + \frac{k_2}{s+p_2}$$

(12)

and where

$$p_1 = -\frac{m_2}{m_3}$$

(13)

$$p_2 = p_1 \left| \frac{\frac{1}{m_1} - \frac{m_1}{m_2}}{\frac{m_1}{m_2} - \frac{m_2}{m_3}} \right|$$

(14)

$$k_1 = \frac{1 + m_1 p_2}{p_1 - p_2} p_1^2 \tag{15}$$

$$k_2 = -\frac{1 + m_1 p_1}{p_1 - p_2} p_2^2. \tag{16}$$

It can be easily deduced from (13) and (16) that

$$k_1 p_2 + k_2 p_1 = p_1 p_2. (17)$$

H'(s) in (12) cannot be directly included in a netlist for circuit-level simulation. Therefore, this work implements it as a two-port network with the same transfer function, as shown in Figure 12.

Figure 12 – An illustration of single-stage timing analysis with a Pi-model for gate analysis and an H'(s)-model for interconnect analysis.

In Figure 12,  $V_i(s)$  is the input of this network while  $V_o(s)$  is the output.  $R_x$  and  $C_x$  constitute a low-pass RC filter fed by a  $V_i(s)$ -controlled voltage source  $V_{ix}(s)$  with gain (1- $\xi$ ), while  $R_y$  and  $C_y$  form the other low-pass RC filter fed by a  $V_i(s)$ -controlled voltage source  $V_{iy}(s)$  with gain  $\xi$ . The output voltages of the two filters,  $V_{ox}(s)$  and  $V_{oy}(s)$ , are added to form  $V_o(s)$ .

Now, it's time to show how the transfer function in Figure 12 is exactly the same as in (12). The transfer function in Figure 12 is as follows:

$$H'(s) = \frac{V_{o}(s)}{V_{i}(s)} = \frac{V_{ox}(s) + V_{oy}(s)}{V_{i}(s)}$$

$$= \frac{\frac{1}{C_{x}s}}{\frac{R_{x} + \frac{1}{C_{x}s}}{(R_{x} + \frac{1}{C_{x}s})}} (1 - \xi)V_{i}(s) + \frac{\frac{1}{C_{y}s}}{R_{y} + \frac{1}{C_{y}s}} \xi V_{i}(s)$$

$$= \frac{1 - \xi}{V_{i}(s)}$$

(18)

$$= \frac{\frac{1-\xi}{R_{x}C_{x}}}{s+\frac{1}{R_{x}C_{x}}} + \frac{\frac{\xi}{R_{y}C_{y}}}{s+\frac{1}{R_{y}C_{y}}}.$$

(18)

By mapping (18) to (12), we get

$$\frac{1}{R_x C_x} = p_1 \tag{19}$$

$$\frac{1}{R_y C_y} = p_2 \tag{20}$$

$$\frac{1-\xi}{R_x C_x} = k_1 \tag{21}$$

$$\frac{\xi}{R_y C_y} = k_2 \,. \tag{22}$$

It is easily seen that (17) still holds for (13)–(16), so that H'(s) in (18) is exactly the same as in (12).

As can be seen from (19) and (20),  $R_x C_x$  is determined by  $1/p_1$  while  $R_y C_y$  is similarly determined by  $1/p_2$ . In our work, we set  $C_x$  and  $C_y$  to a fixed value,  $10^{-15}$ F, leaving  $R_x$  and

$R_y$  to be calculated according to (19) and (20), respectively. Therefore, we actually have three parameters in the H'(s)-model,  $R_x$ ,  $R_y$  and  $\xi$ , which means H(s) is simplified to a three-parameter space.

### 4.1.4 Sensitivity of the Pi-Model and the H'(s)-Model to Variations of Input Capacitances in the Fanout Gates

As input capacitances of fanout gates are included as part of the interconnect, the variations of these capacitances cause the Pi-model and the H'(s)-model to vary. Here we denote the variational input capacitances of fanout gates of one interconnect network as  $\overline{C_{fanout}} = [C_{fanout\_1}, C_{fanout\_2}, \dots, C_{fanout\_N}]$  where *N* is the number of fanout gates at the output of this interconnect network. It is impractical to run the whole process, i.e., moment generation and calculations of  $C_I$ , R,  $C_2$ ,  $R_x$ ,  $R_y$ , and  $\zeta$ , for every variational sample of  $\overline{C_{fanout}}$ . Thus, we expand a first-order Taylor-series at nominal values of  $\overline{C_{fanout}}$ . Let's take  $C_I$  of the Pi-model as an example, since the other parameters (R,  $C_2$ ,  $R_x$ ,  $R_y$  and  $\zeta$ ) are similar.

$$C_{1} = C_{1\_nominal} + \sum_{i=1}^{N} \alpha_{i} (C_{fanout\_i} - C_{fanout\_i\_nominal})$$

(23)

where  $C_{fanout\_i\_nominal}$  is the nominal value of  $C_{fanout\_i}$ ,  $\alpha_i$  is the first derivative of  $C_1$ with respect to  $C_{fanout\_i}$ ,  $i \in \{1, 2, ..., N\}$ , and  $C_{1\_nominal}$  is the nominal value of  $C_1$ .

The errors in using (23) to calculate the Pi-model and the H'(s)-model parameters are all less than 0.1% in our test RC interconnects. Please note that (23) is unique for each interconnect in a circuit, but needs to be characterized only once and the characterization

time is negligible because the interconnect network size in our experiments throughout this thesis is not large (less than 100 RC segments).

### 4.1.5 Gate-Delay Characterization using Multivariate Adaptive Regression Splines (MARSP)

As mentioned in Section 4.1.2, with fanout gates being modeled as corresponding input capacitances, a circuit can be divided into gate-level stages for timing analysis as shown in Figure 9(b). The timing analysis of each stage incorporates two parts: gate delay/output-slew modeling and interconnect delay/output-slew modeling. The output of the buffer in Figure 9(b), node a, is also the input of the interconnect network. The delay of the buffer is the delay from node *in* to node a, while the delay of the interconnect network is the delay from node a to node b or from node a to node c. The output slew of the buffer is used as the input slew of the interconnect. The total delay of each stage is the sum of the gate delay and the interconnect delay.

Using the Pi-model and H'(s)-model, the circuit in Figure 9(b) is transformed into Figure 12. The upper box in Figure 12 represents gate timing analysis, while the lower box represents interconnect timing analysis. In this section, MARSP is used to characterize the delay and slew models of standard cells.