### INTEGRATION OF OPTOELECTRONICS INTERCONNECTS ON GLASS INTERPOSERS FOR HIGH SPEED COMMUNICATIONS

A Dissertation Presented to The Academic Faculty

By

Rui Zhang

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

Georgia Institute of Technology

Dec 2020

© Rui Zhang 2020

### INTEGRATION OF OPTOELECTRONICS INTERCONNECTS ON GLASS INTERPOSERS FOR HIGH SPEED COMMUNICATIONS

Thesis committee:

Dr. Rao R. Tummala, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Gee–Kung Chang School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Muhannad S. Bakir School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Eric M. Vogel School of Materials Science and Engineering *Georgia Institute of Technology*

Dr. Mohanalingam Kathaperumal School of Electrical and Computer Engineering *Georgia Institute of Technology*

Date approved: Nov. 6, 2020

#### ACKNOWLEDGMENTS

It wasn't smooth sailing during the course of my PhD odyssey. At the beginning, I didn't know I was venturing into this uncharted territory. In the second year, my research went into a cul–de–sac, and I had no control over it. In the third year, my advisor retired and my mentor left, and for a while the last of us weren't sure about our future. Things happen during the PhD journey, but the halo at the end makes them all worth it.

I would like to thank my advisor, Prof. Rao R. Tummala, and my research mentors, Dr. Fuhan Liu, Dr. Mohanalingam Kathaperumal, and Dr. Venky Sundaram, for their support and guidance throughout my time at Georgia Tech Packaging Research Center (GT– PRC). I would also like to thank Prof. Gee–Kung Chang, Prof. Muhannad S. Bakir, and Prof. Eric M. Vogel for serving as members of my committee and providing valuable feedback.

Completing this research would not have been possible without the help and support from the staff at GT–PRC and GT–PRC's industry sponsors. Specifically, I am grateful for the technical discussions I had with Dr. Michael Gallagher, Dr. Edgardo Anzures, and Dr. Rosemary Bell from DuPont Electronics & Imaging, Martin Orrick from ESI, Kimiyuki Kanno and Hirokazu Itou from JSR Corp., Satomi Kawamoto from NAMICS Inc., Kakutani Takenori from Taiyo Inc., and Ryuta Furuya from Ushio Inc..

I am also indebted to everyone who helped me in lab conduct experiments. I would like to thank Richard Shafer, Eric Woods, Todd Walters, and Yolande Berta from Georgia Tech IEN, Brent Wagner from Georgia Tech Research Institute, Dr. Daniel Guidotti, Dr. Chin– Wei Hsu, and Shuyi Shen from Prof. Gee–Kung Chang's group, and Rakesh Vangapandu from Prof. Ali Adibi's group.

A special thanks is deserved for the students come and gone at GT–PRC. In particular, I would like to thank my office mates, Bartlet DeProspo, Brett Sawyer, Bruce Chou, Chintan Buch, Nithin Nedumthakady for making it fun at work with their wittiness and our constant rants about PhD life.

Lastly, I would like to thank my family, my friends, my therapists, and all the dogs and cats I patted and snuggled with over the years, Bailey, Black Cat, Dobby, Ella, Lola, Lucky, Oscar, Poppy, Princess, Professor Chaos, Puck, Ruby, Stuart, Wasabi, and Wukong, for their support, and for keeping me sane.

## TABLE OF CONTENTS

| Acknow    | ledgme        | e <b>nts</b>                           | ii |

|-----------|---------------|----------------------------------------|----|

| List of 7 | <b>Tables</b> | •••••••••••••••••••••••••••••••••••••• | ii |

| List of I | igures        | i                                      | x  |

| List of A | Acrony        | <b>ms</b> x                            | v  |

| Summa     | ry            |                                        | ii |

| Chapter   | : 1: Int      | roduction                              | 1  |

| 1.1       |               |                                        | 3  |

|           | 1.1.1         |                                        | 4  |

|           | 1.1.2         |                                        | 5  |

|           | 1.1.3         |                                        | 8  |

|           | 1.1.4         | 1                                      | 9  |

| 1.2       | Uniqu         |                                        | 0  |

| 1.3       | 1             |                                        | 2  |

| 1.4       |               |                                        | 3  |

| Chapter   | : 2: Lit      | erature Survey                         | 5  |

| 2.1       |               |                                        | 5  |

| 2.2       |               |                                        | 8  |

|           | 2.2.1         |                                        | 8  |

|           | 2.2.2         |                                        | 21 |

|           | 2.2.3         |                                        | 2  |

| 2.3       | High F        | 5                                      | 3  |

|           | 2.3.1         | ε                                      | 4  |

|           | 2.3.2         |                                        | 27 |

| 2.4       |               | •                                      | 27 |

| Chapter   | : 3: Ult      | ra–Fine Electronic Interconnects       | 28 |

| 3.1       |               |                                        | 0  |

|           | 3.1.1         |                                        | 1  |

|           | 3.1.2         |                                        | 6  |

|           | 3.1.3         | Embedded Trenches for Routing Wires    |    |

| 3.2       | Vertica       | al Interconnects: Microvias            | .2 |

|         | 3.2.1 Microvia Fabrication by Photolithography                           | 44  |

|---------|--------------------------------------------------------------------------|-----|

|         | 3.2.2 Fundamentals of Laser Ablation for Microvias                       | 46  |

|         | 3.2.3 Laser Ablated Microvias on ABF–GX92P                               | 51  |

|         | 3.2.4 Laser Ablated Microvias on ABF–GX92P with a Thin Metal Bar-        |     |

|         | rier Layer                                                               | 57  |

|         | 3.2.5 Laser Ablated Microvias on JSR GT–N01 with a Thin Metal Barrier    |     |

|         | Layer                                                                    | 60  |

| 3.3     | Summary                                                                  | 65  |

| Chapte  | r 4: Low Loss Optical Interconnects on Glass                             | 67  |

| 4.1     | The Limitation of Electronic Interconnects for On-Package Communications | 70  |

| 4.2     | Modeling and Design of Polymer–Based SMWGs on Glass                      | 76  |

|         | 4.2.1 Material Selection                                                 | 76  |

|         | 4.2.2 SMWG Geometry Design                                               | 79  |

|         | 4.2.3 Coupling Analysis between Adjacent Waveguides                      | 81  |

| 4.3     | Process Development and Fabrication                                      | 86  |

|         | 4.3.1 Elimination of Defects                                             | 87  |

|         | 4.3.2 Shape Control of Waveguide Cores                                   | 93  |

|         | 4.3.3 Fabrication of SMWGs on Glass                                      | 96  |

| 4.4     | Characterization of SMWGs on Glass                                       | 102 |

|         | 4.4.1 Sample Preparation for Characterizations                           | 103 |

|         | 4.4.2 Measurement of Propagation Losses                                  |     |

|         | 4.4.3 Measurement of Data Rates                                          | 112 |

| 4.5     | Summary                                                                  | 116 |

| Chapte  | r 5: Fiber Coupling and Integration on Glass                             | 118 |

| 5.1     | Flip V-groove Approach for Fiber Integration on Glass Interposers 1      |     |

|         | 5.1.1 Glass-to-Glass Bonding                                             |     |

|         | 5.1.2 Fibers Assembled in a V–groove Chip                                |     |

| 5.2     | Summary                                                                  |     |

| Chapte  | r 6: Conclusions                                                         | 125 |

| 6.1     | Summary of Results                                                       | 126 |

|         | 6.1.1 High–Density Electronic Interconnects                              |     |

|         | 6.1.2 Low Loss Optical Interconnects on Glass                            | 127 |

|         | 6.1.3 Fiber Coupling and Integration on Glass                            | 128 |

| 6.2     | Technical and Scientific Contributions                                   |     |

| 6.3     | Recommendations for Future Work                                          | 129 |

| 6.4     | List of Publications                                                     | 130 |

|         | 6.4.1 Journal Publications                                               | 130 |

|         | 6.4.2 Conference Publications                                            | 131 |

|         | 6.4.3 Book Chapter Publications                                          |     |

| Referen | nces                                                                     | 133 |

|         |                                                                          |     |

## LIST OF TABLES

| 1.1  | Properties of glass and silicon.                                                | 9  |

|------|---------------------------------------------------------------------------------|----|

| 1.2  | Research objectives, challenges, and tasks.                                     | 12 |

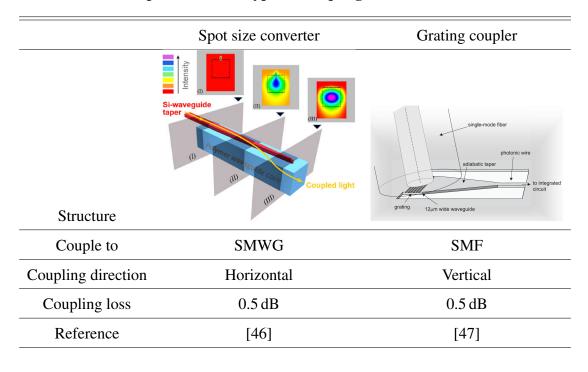

| 2.1  | Comparison of two types of coupling for silicon-based SMWGs                     | 21 |

| 2.2  | Comparison of different materials for SMWGs.                                    | 23 |

| 3.1  | Embedded trench fabrication process with CYCLOTENE <sup>TM</sup> 6505           | 41 |

| 3.2  | Material properties of ABF-GX92P. © 2019 IEEE                                   | 53 |

| 4.1  | Material properties of glass, ILDs, and the solder resist                       | 71 |

| 4.2  | Transmission line parameters at 1 GHz                                           | 73 |

| 4.3  | Transmission line parameters and attenuation coefficients from 1 GHz to 40 GHz. | 75 |

| 4.4  | Waveguide material properties.                                                  | 79 |

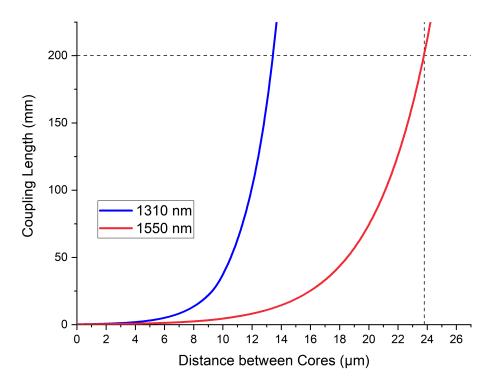

| 4.5  | Refractive indices of the even mode and the odd mode for 1310 nm and 1550 nm    | 85 |

| 4.6  | The process of record on waveguide fabrication.                                 | 88 |

| 4.7  | Optimized waveguide core patterning process                                     | 94 |

| 4.8  | Optimized cure process                                                          | 95 |

| 4.9  | Optimized waveguide fabrication process.                                        | 97 |

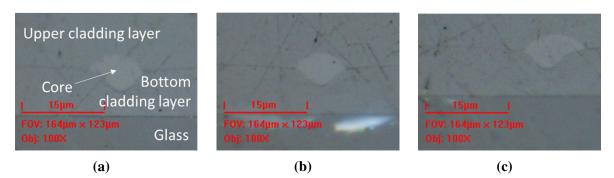

| 4.10 | Cross sections of fabricated waveguides.                                        | 98 |

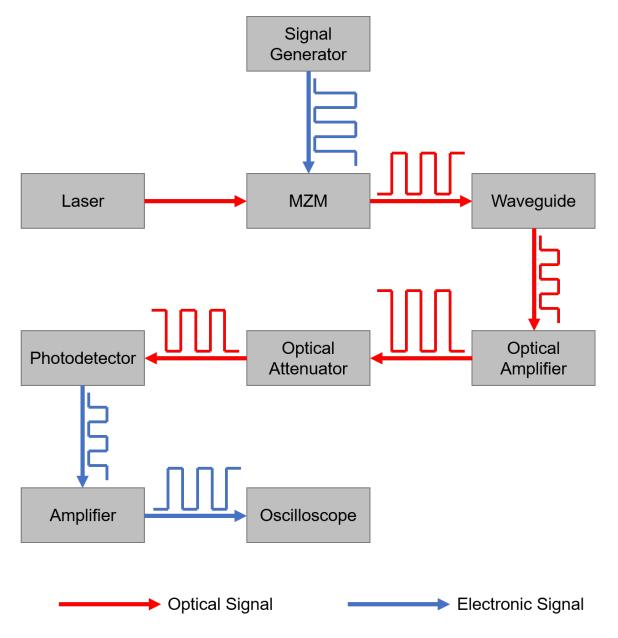

| 4.11 | Devices used in the data rate measurement           | 113 |

|------|-----------------------------------------------------|-----|

| 5.1  | Die shear test results on three adhesive materials. | 123 |

| 6.1  | Summary of research tasks, targets and results      | 126 |

## LIST OF FIGURES

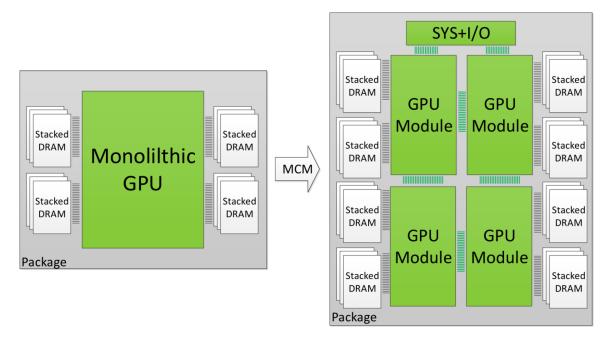

| 1.1 | MCM-GPU: Aggregating GPU modules and DRAM on a single package [2].                                                                                                                                                                                                                                          | 2  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

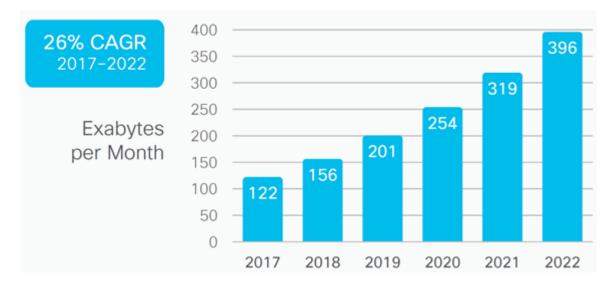

| 1.2 | Cisco VNI forecasts 396 EB per month of IP traffic by 2022 [6]                                                                                                                                                                                                                                              | 3  |

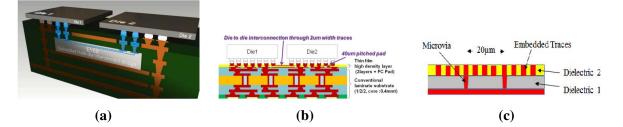

| 1.3 | (a) Schematic showing the EMIB concept [8]. (b) Schematic cross sectional image of i–THOP [9]. (c) The schematic of novel ViT interconnect configuration for $20 \mu\text{m}$ bump pitch interposer and package application. The traces are embedded in the dielectric layer and surrounded by polymer [10] | 4  |

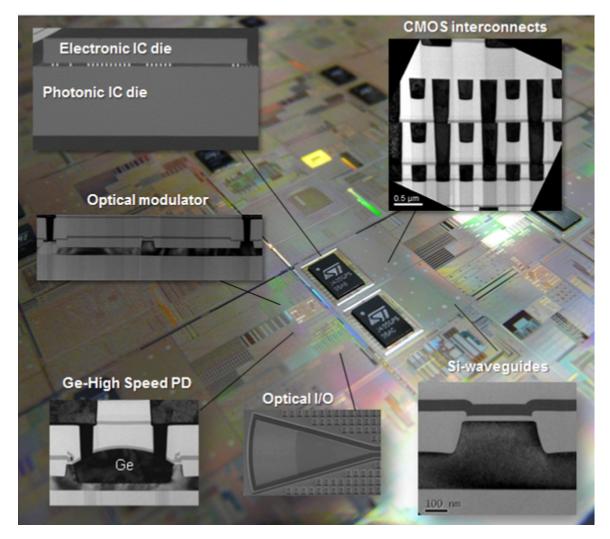

| 1.4 | Overview of current fully integrated silicon photonics technology using a 3D electronic IC [12]                                                                                                                                                                                                             | 6  |

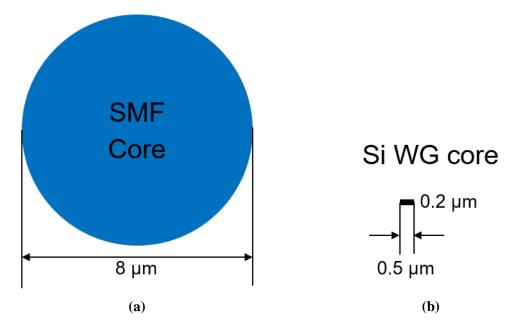

| 1.5 | Schematics of (a) a single mode fiber (SMF) core and (b) a silicon waveg-<br>uide core.                                                                                                                                                                                                                     | 7  |

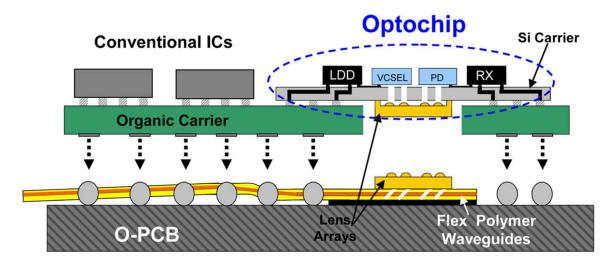

| 1.6 | Schematic representation of the Terabus vision of an OE–MCM (or opto-<br>module) incorporating an 850 nm transceiver optochip as well as conven-<br>tional ICs [23].                                                                                                                                        | 8  |

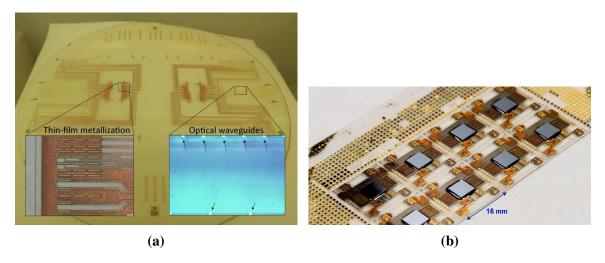

| 1.7 | (a) Optical dual-layer waveguide integration and thin-film metallization on a 200 mm wafer level [24], and (b) The top half of glass panel after ENIG and chip assembly [25]                                                                                                                                | 10 |

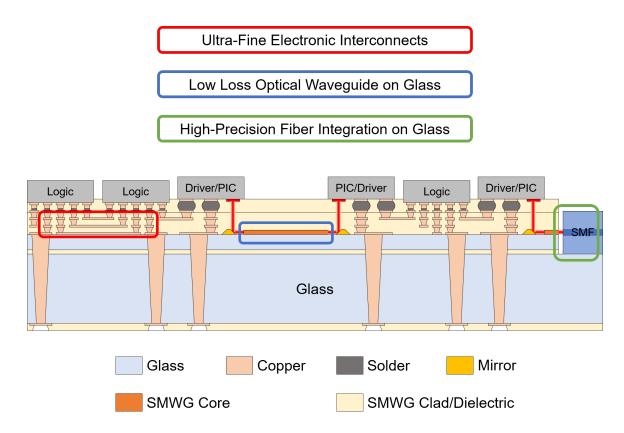

| 1.8 | A schematic of glass interposers with high–density electronic interconnects and low loss single mode optical interconnects with fiber integration                                                                                                                                                           | 11 |

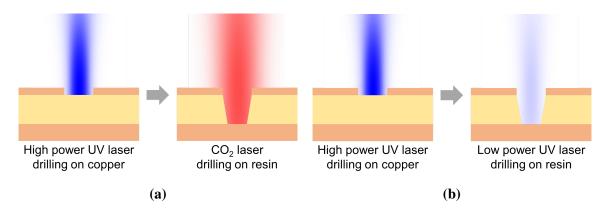

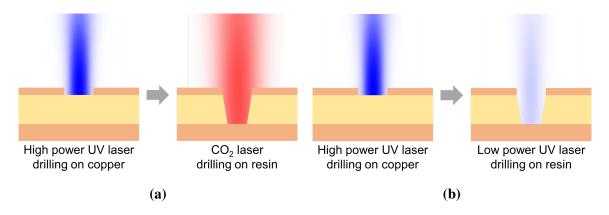

| 2.1 | Schematics of laser drilling on RCC with (a) a hybrid laser system and (b) two—step UV laser drilling system. © 2020 IEEE                                                                                                                                                                                   | 17 |

| 2.2 | Optical absorption coefficient of silicon [37]                                                                                                                                                                                                                                                              | 18 |

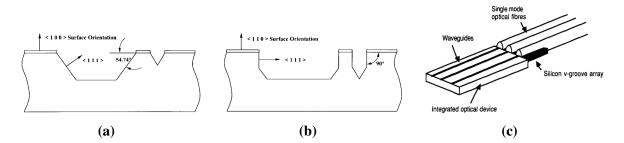

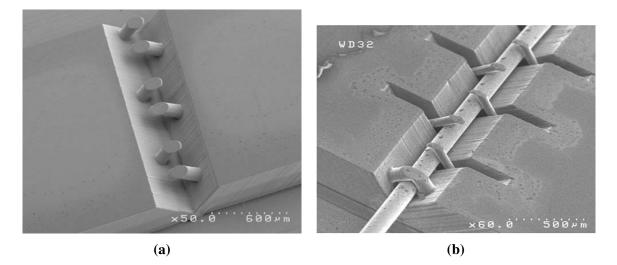

| 2.3 | (a) Silicon v–groove on <100> wafer and (b) silicon v–groove on <110> wafer [64]. (c) Fibers in silicon v–grooves [65]                                                                                                                                                                                      | 24 |

| 2.4  | (a) A polymer v-groove and (b) a polymer beam with fiber insertion [69].                                                                                                                                                                                           | 25 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.5  | (a) Configuration diagram of core monitoring method and (b) an microscopic image of the alignment [73]                                                                                                                                                             | 26 |

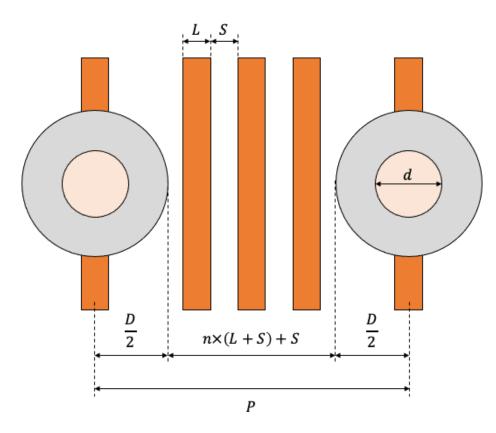

| 3.1  | Electronic interconnect density parameters in a typical RDL configuration                                                                                                                                                                                          | 29 |

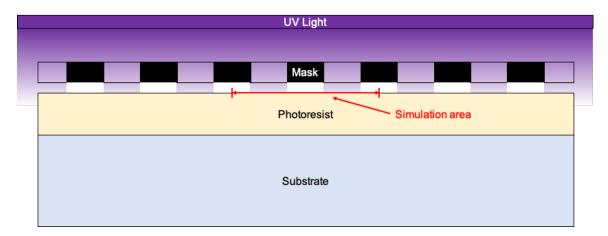

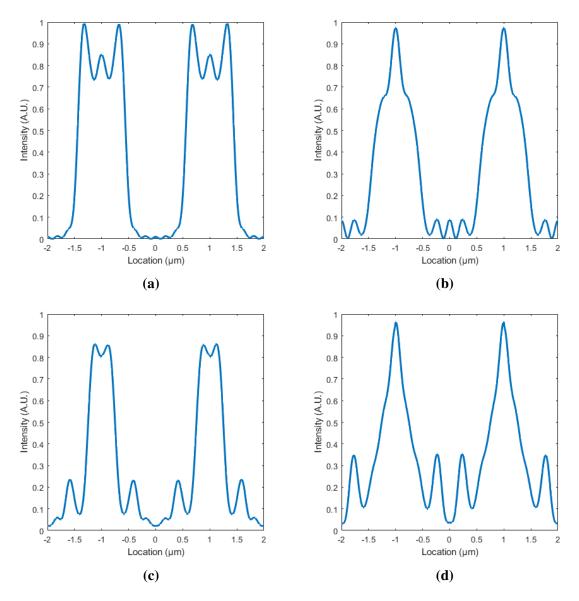

| 3.2  | Near-field Fresnel diffraction simulation                                                                                                                                                                                                                          | 32 |

| 3.3  | Diffraction patterns after the photomask with a gap of (a) $0.1 \mu m$ , (b) $0.5 \mu m$ , (c) $1.0 \mu m$ , and (d) $3.0 \mu m$ .                                                                                                                                 | 33 |

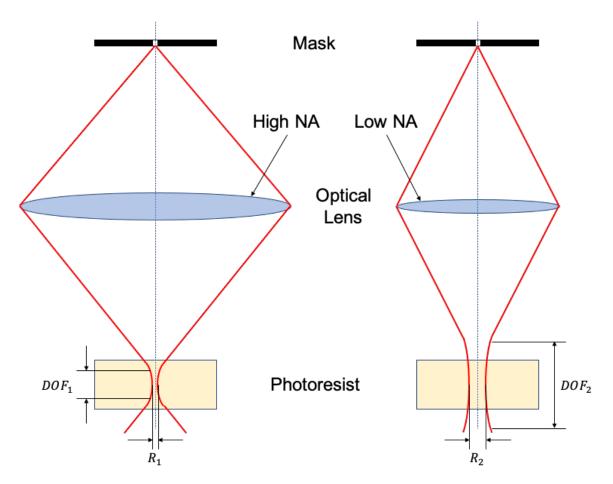

| 3.4  | A schematic of the impact of NA on the resolution and DOF                                                                                                                                                                                                          | 35 |

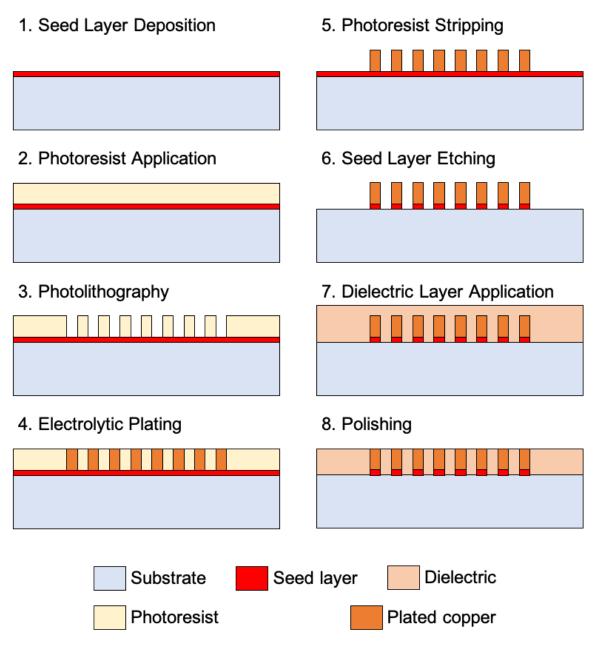

| 3.5  | A schematic of SAP                                                                                                                                                                                                                                                 | 37 |

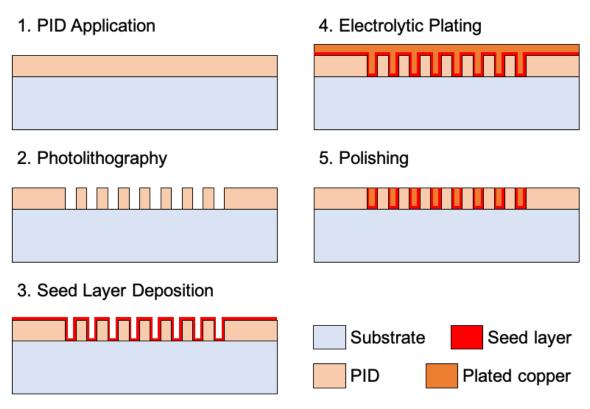

| 3.6  | A schematic of the embedded trench method.                                                                                                                                                                                                                         | 39 |

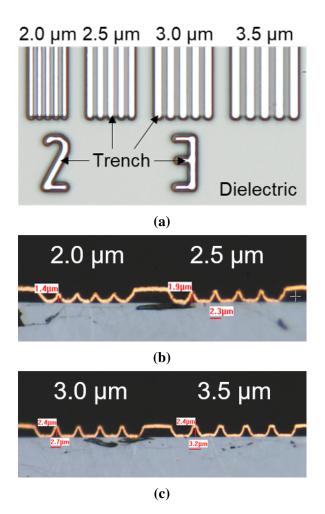

| 3.7  | (a) Top view of dielectric lines and trenches. (b) Cross-sectional image of 2.0– and 2.5– $\mu$ m 1:1 line and space structure after copper deposition. (c) Cross-sectional image of 3.0– and 3.5– $\mu$ m 1:1 line and space after copper deposition. © 2020 IEEE | 42 |

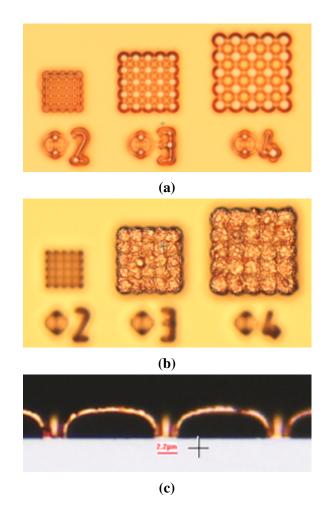

| 3.8  | 2–, 3–, and 4– $\mu$ m microvias with 4–, 6–, and 8– $\mu$ m pitch, respectively, (a) before and (b) after copper plating. (c) Cross–sectional image of 2– $\mu$ m microvias with 12.5– $\mu$ m pitch. © 2020 IEEE                                                 | 45 |

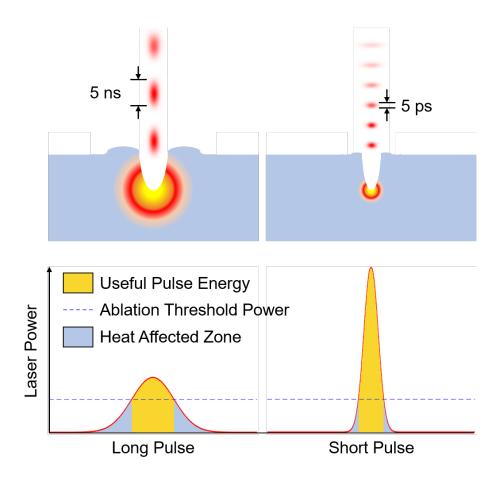

| 3.9  | UV laser interaction with dielectric materials. Left: nanosecond pulse.<br>Right: picosecond pulse. Peak power of a picosecond pulse is about 1000× of a nanosecond pulse. © 2019 IEEE                                                                             | 47 |

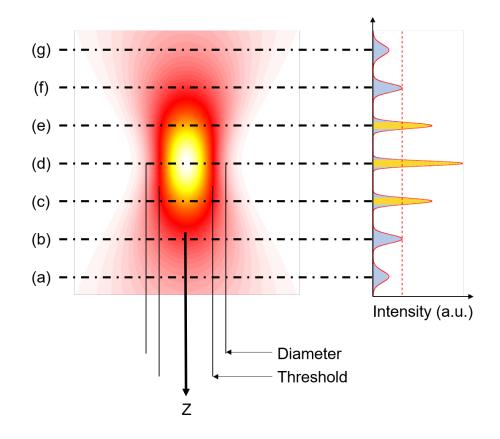

| 3.10 | A schematic of the laser beam profile and the intensity distribution at dif-<br>ferent z locations around the focal plane                                                                                                                                          | 48 |

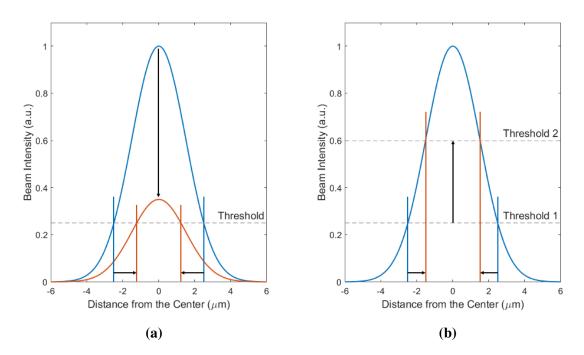

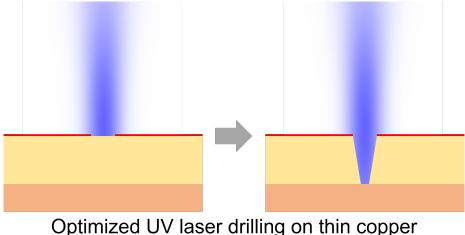

| 3.11 | Reducing the size of microvias by (a) using lower laser power and (b) increasing the ablation threshold.                                                                                                                                                           | 50 |

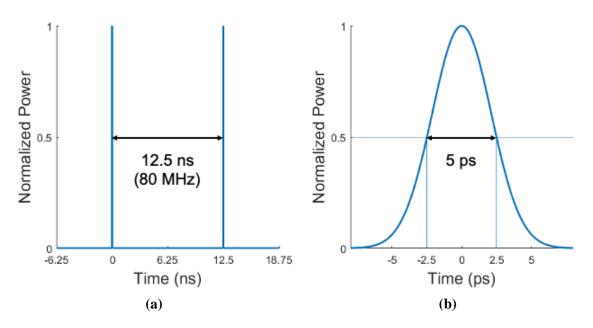

| 3.12 | (a) Pulses at 80 MHz, and (b) a pulse with 5 ps pulse width                                                                                                                                                                                                        | 52 |

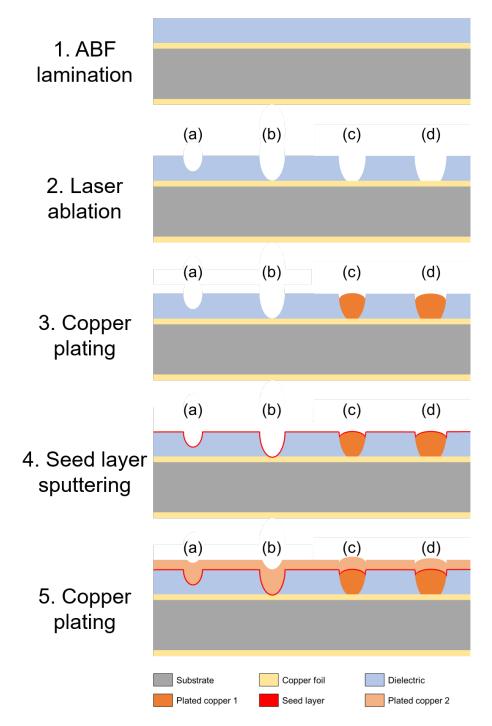

| 3.13 | Process development flow of ultra-small microvia fabrication. © 2019 IEEE                                                                                                                                                                                          | 54 |

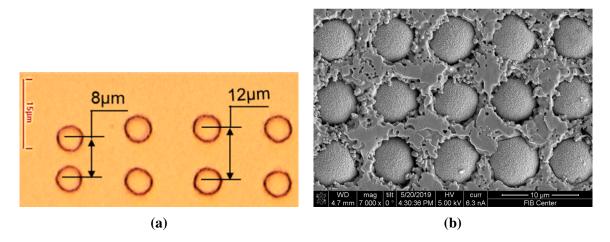

| 3.14 | (a) 5– $\mu$ m microvias by ps UV laser with 8– and 12– $\mu$ m pitches. (b) SEM image of microvias after copper plating. © 2019 IEEE                                                                                                                              | 56 |

| 3.15 | Schematics of laser drilling on RCC with (a) hybrid laser system and (b) two-step UV laser drilling system. © 2020 IEEE                                                                                             | 57 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.16 | Smaller microvias fabricated in thin copper and resin by optimized UV laser drilling without changing laser or power. © 2019 IEEE                                                                                   | 58 |

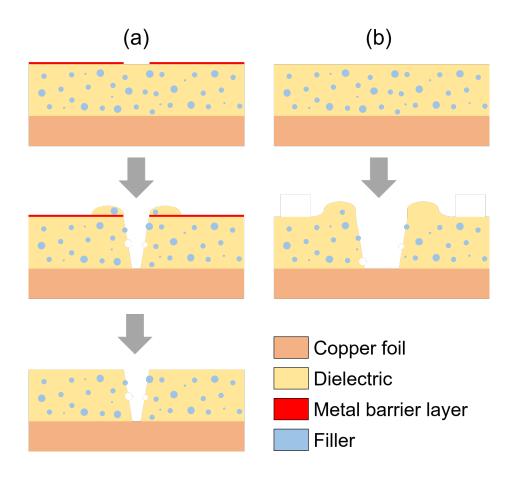

| 3.17 | Schematics of redeposition on (a) ABF with a metal barrier layer and (b) bare ABF. © 2020 IEEE                                                                                                                      | 59 |

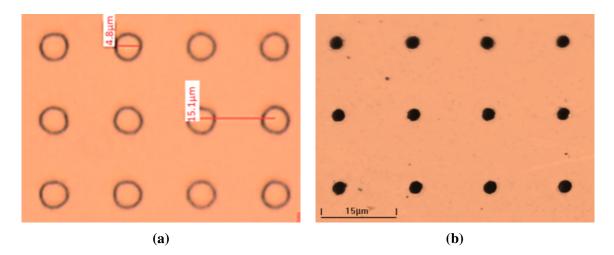

| 3.18 | 0.1–W laser fabricates (a) 5–µm openings in ABF and (b) 2–µm openings in copper. © 2020 IEEE                                                                                                                        | 60 |

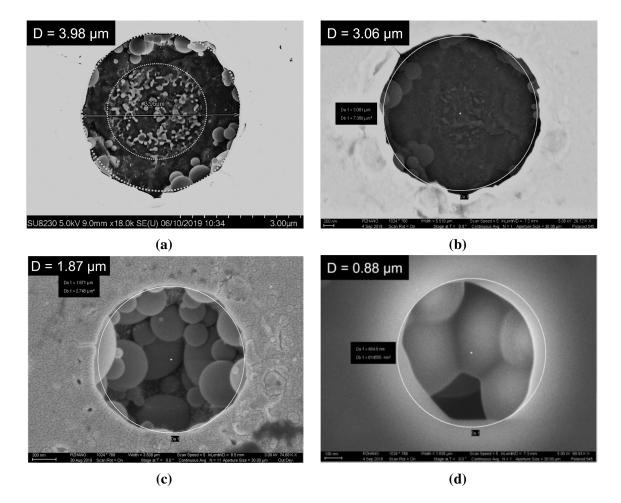

| 3.19 | SEM images of microvias with a diameter of (a) $4 \mu m$ , (b) $3 \mu m$ . (c) $0.1 - W$ laser ablates $2 - \mu m$ opening with fillers inside. (d) A submicrometer opening and fillers trapped inside. © 2020 IEEE | 61 |

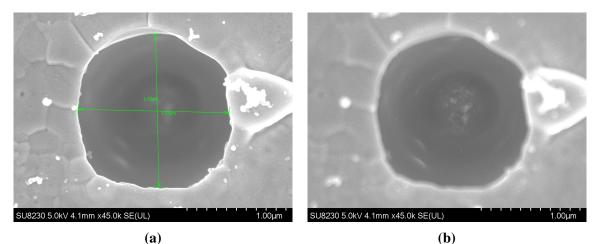

| 3.20 | SEM images of a 1.5 $\mu$ m microvia in a 3 $\mu$ m film focused on (a) top opening<br>and (b) bottom opening. (c) An SEM image of a 1.3 $\mu$ m microvia in a 2 $\mu$ m<br>film                                    | 62 |

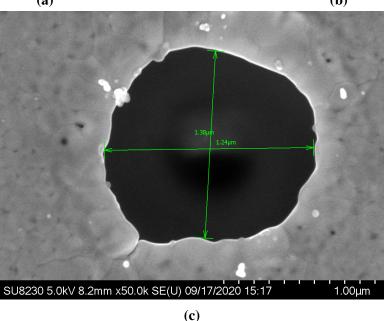

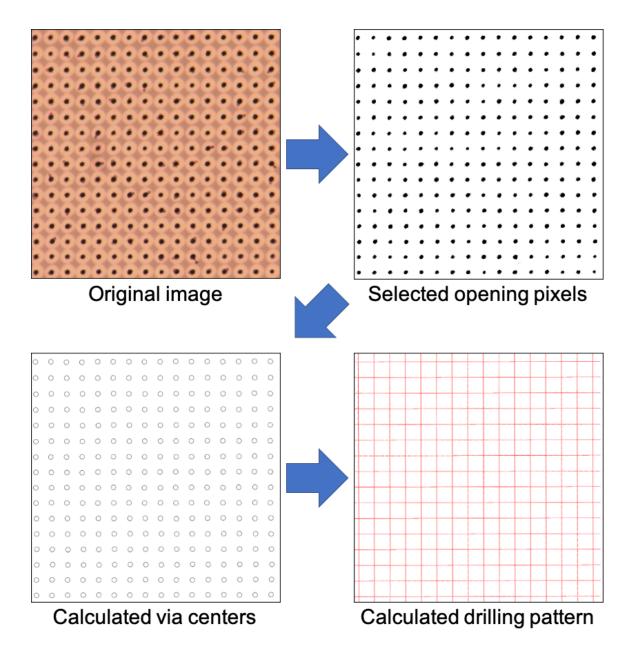

| 3.21 | Drilling pattern calculation process.                                                                                                                                                                               | 63 |

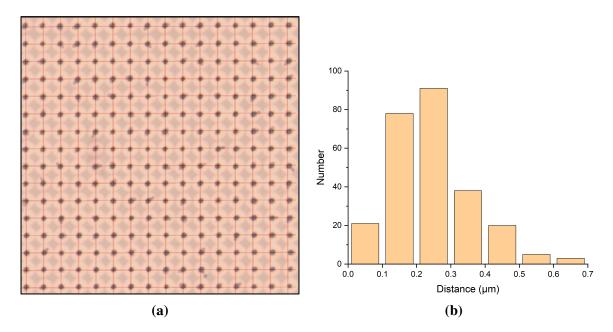

| 3.22 | (a) Drilling pattern combined with drilled microvias. (b) Landing accuracy distribution.                                                                                                                            | 64 |

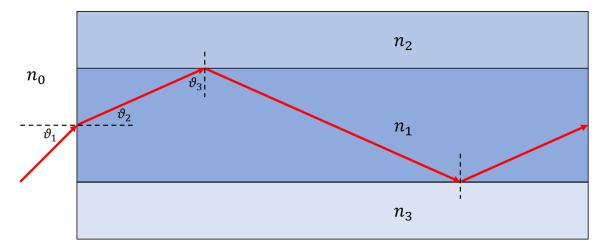

| 4.1  | Total internal reflection in a waveguide.                                                                                                                                                                           | 68 |

| 4.2  | Guided modes in a waveguide.                                                                                                                                                                                        | 69 |

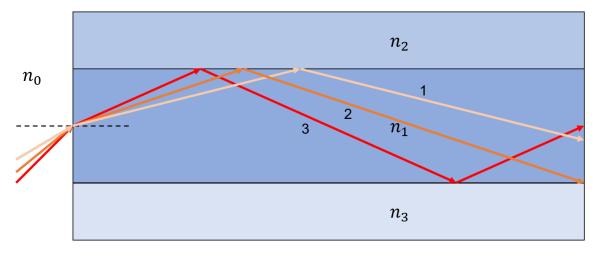

| 4.3  | Three–metal layer stack RDL and signal layer assignment                                                                                                                                                             | 71 |

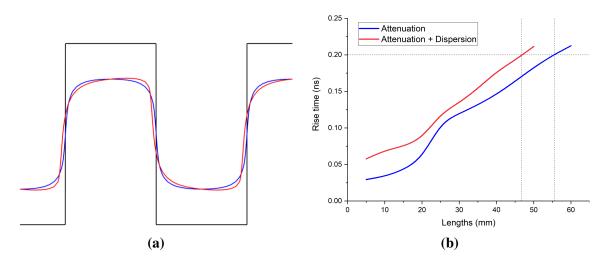

| 4.4  | Original signal (black), attenuated signal (blue), and attenuated and dispersed signal (red).                                                                                                                       | 76 |

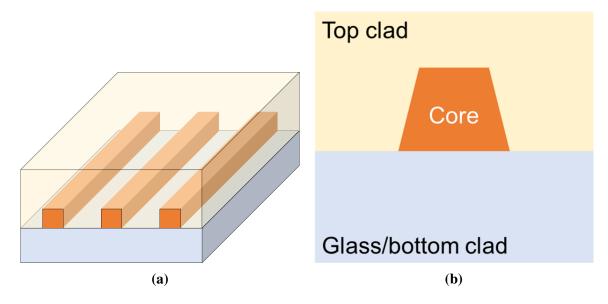

| 4.5  | (a) A stack–up of waveguides on glass and (b) the cross section of a waveg-<br>uide                                                                                                                                 | 77 |

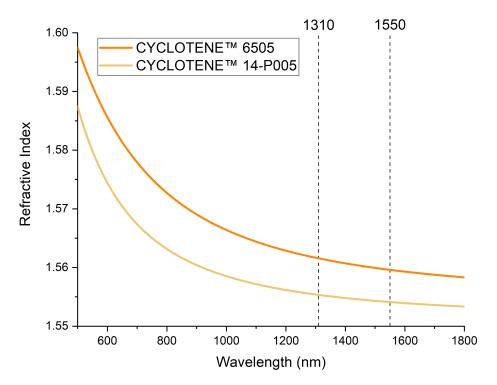

| 4.6  | Refractive indices of the core and the clad materials                                                                                                                                                               | 78 |

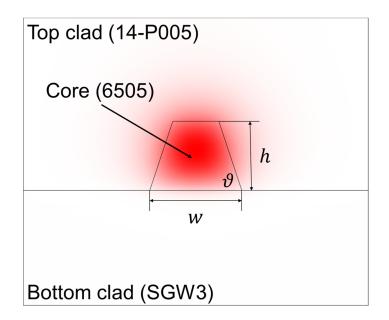

| 4.7  | Simulation setup with the bottom width $(w)$ , height $(h)$ , and sidewall angle $(\theta)$                                                                                                                         | 80 |

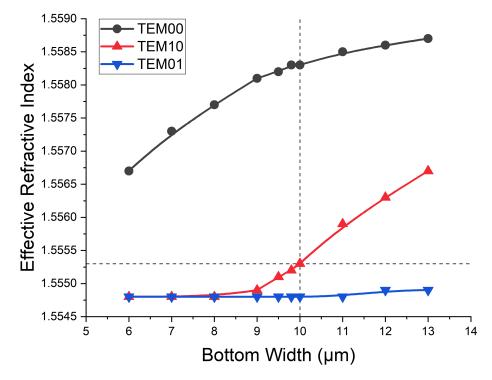

| 4.8  | Effective refractive indices of the lowest three modes                                                                                                                                                              | 81 |

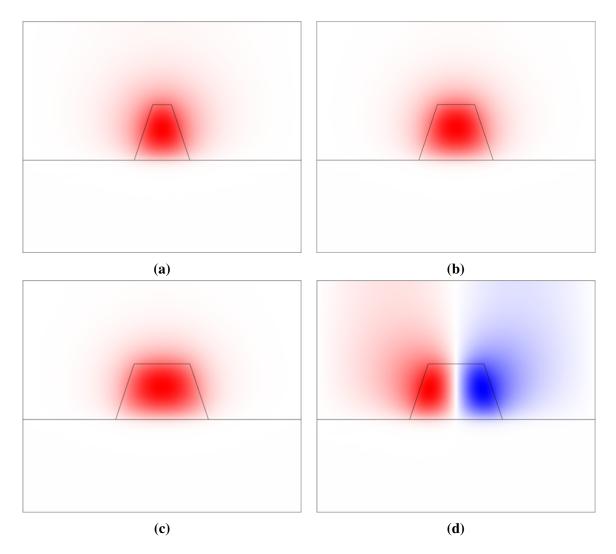

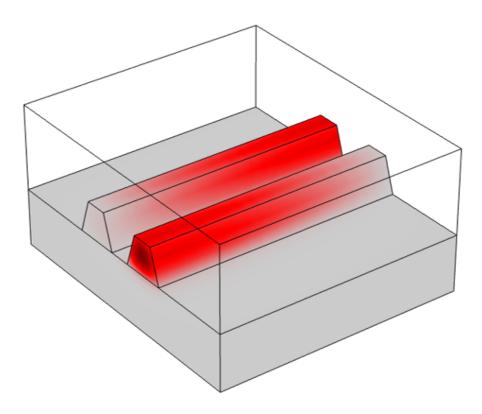

| 4.9  | Electromagnetic fields of (a) the fundamental mode when $w = 6 \mu\text{m}$ , (b) the fundamental mode when $w = 8 \mu\text{m}$ , (c) the fundamental mode when $w = 10 \mu\text{m}$ , and (d) a higher mode when $w = 10 \mu\text{m}$ | 82 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.10 | Coupling between adjacent waveguides.                                                                                                                                                                                                  | 83 |

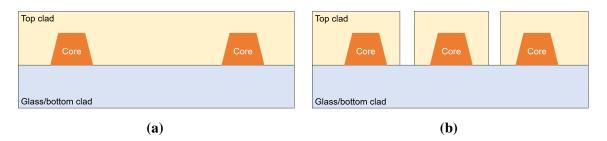

| 4.11 | Isolate waveguide cores by (a) increasing the pitch between cores, and (b) introducing air gap between clad                                                                                                                            | 83 |

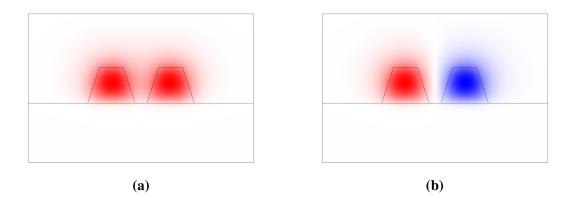

| 4.12 | (a) Even mode and (b) odd mode propagating in two coupled waveguides with a distance of $2\mu m$ .                                                                                                                                     | 84 |

| 4.13 | Maximum coupling lengths vs the distance between cores for 1310 nm and 1550 nm                                                                                                                                                         | 86 |

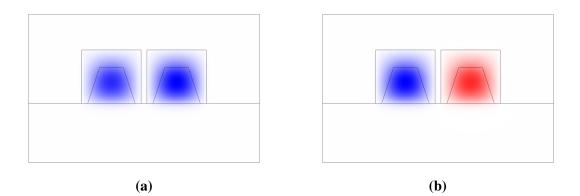

| 4.14 | (a) Even mode and (b) odd mode propagating in two coupled waveguides with an air gap of $1 \mu m$ .                                                                                                                                    | 86 |

| 4.15 | (a) Peeling after exposure. (b) Comparison of peeling on unexposed and exposed areas.                                                                                                                                                  | 87 |

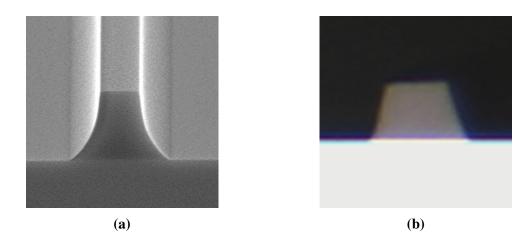

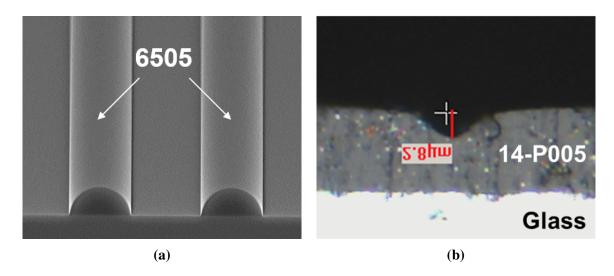

| 4.16 | (a) An SEM image of a polymer line with curved sidewalls, courtesy of DuPont Electronics & Imaging, and (b) a cross-sectional optical image of a polymer line with straight sidewalls.                                                 | 89 |

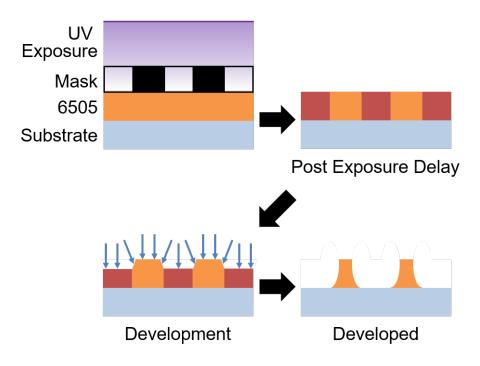

| 4.17 | A schematic of the development process                                                                                                                                                                                                 | 90 |

| 4.18 | (a) A cross section of a developed pattern with residues, and (b) a cross section of a developed pattern without residues after optimization                                                                                           | 91 |

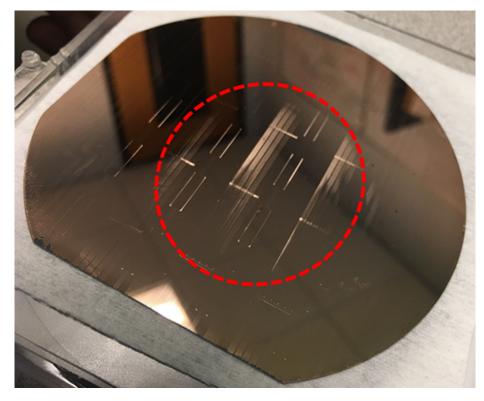

| 4.19 | Patterns inside the red circles show diffuse reflection                                                                                                                                                                                | 92 |

| 4.20 | (a) An optical image of the undeveloped region (bottom) and the developed region (top), and (b) an optical image of the undeveloped region (top) and the overdeveloped region (bottom).                                                | 93 |

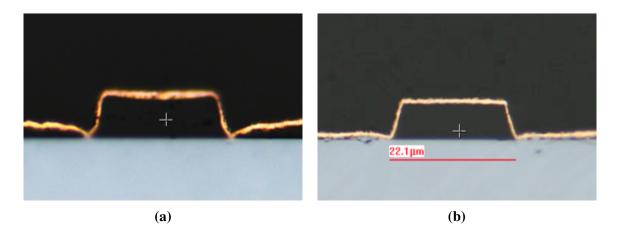

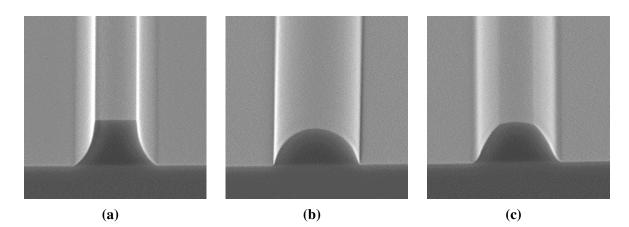

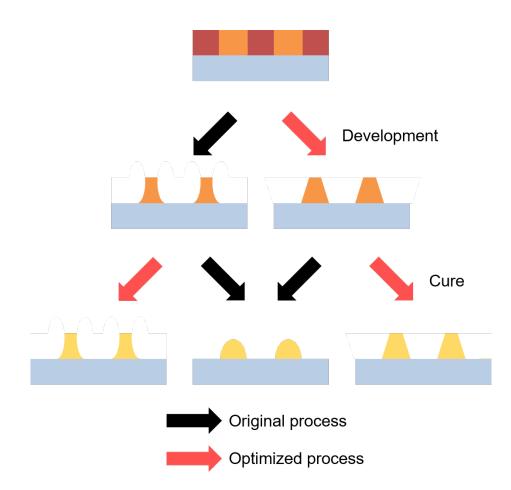

| 4.21 | A 10 µm wide polymer line (a) after development, (b) after the original cure process, and (c) after an optimized cure process. Courtesy of DuPont Electronics & Imaging.                                                               | 93 |

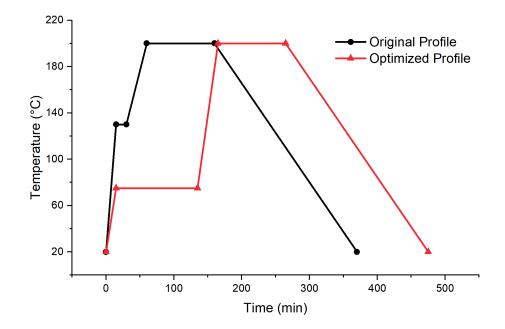

| 4.22 | The temperature profiles of the original cure process and the optimized cure process.                                                                                                                                                  | 95 |

| 4.23 | Impacts of process conditions on shape control of the waveguide cores                                                                                                                                                                  | 96 |

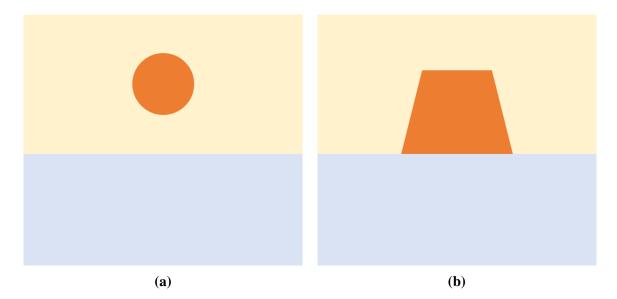

| 4.24 | Schematic cross sections of (a) a circular core waveguide and (b) a trape-<br>zoidal waveguide.                                                                                                                    | . 98  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.25 | Two crucial parts for circular core SMWGs, (a) round top of the core, courtesy of DuPont Electronics & Imaging, and (b) semi-circular trench from the clad.                                                        | . 99  |

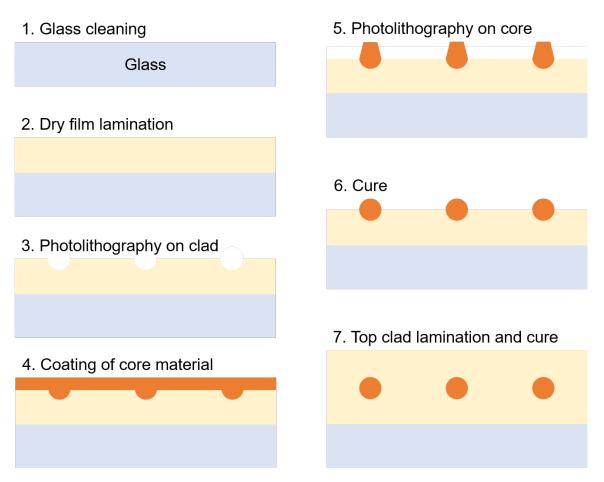

| 4.26 | Process flow of circular core waveguide fabrication.                                                                                                                                                               | . 100 |

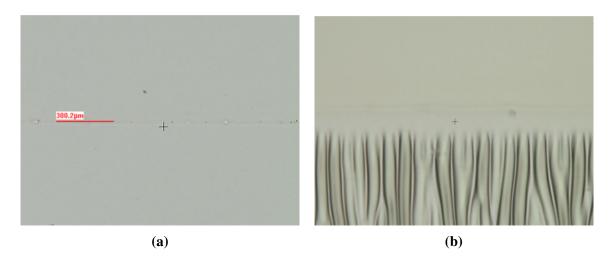

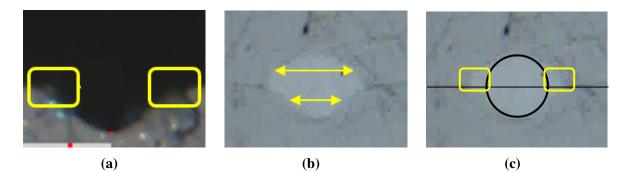

| 4.27 | (a) Long tails on both sides of the trench, (b) difference in widths between<br>the top half of the core and the bottom half of the core, and (c) width ex-<br>pansion of the core.                                | . 101 |

| 4.28 | Cross sections of a waveguide at different locations. (a) A right-skewed core, (b) a no-skew core, and (c) a left-skewed core. $©$ 2017 IEEE                                                                       | . 101 |

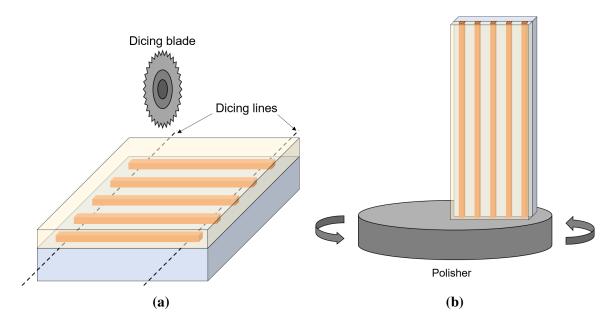

| 4.29 | Sample preparation for waveguide characterization: (a) dicing of waveg-<br>uides to expose ends for coupling, and (b) polishing of the edge to improve<br>coupling                                                 | . 103 |

| 4.30 | Process flow of circular core waveguide fabrication.                                                                                                                                                               | . 104 |

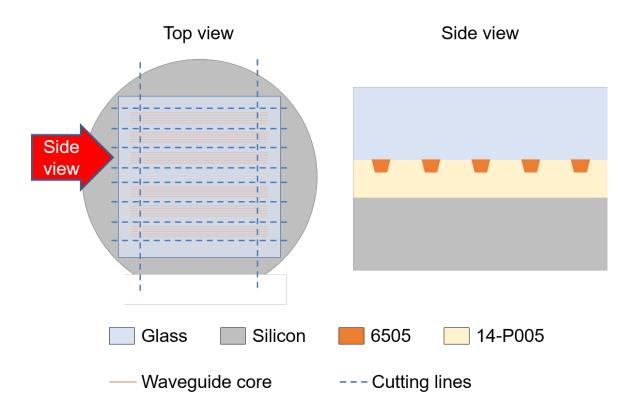

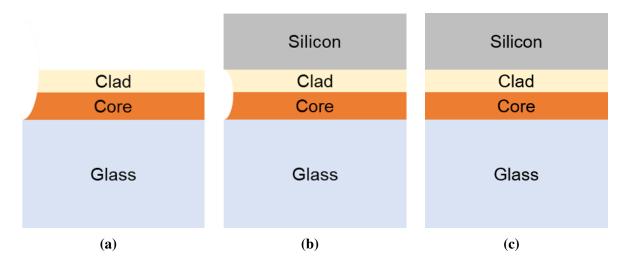

| 4.31 | Schematics of side views of (a) a concave edge on a polymer–on–glass sample, (b) a concave edge on a sandwiched waveguide sample, and (c) a flat edge on a sandwiched waveguide sample.                            | . 105 |

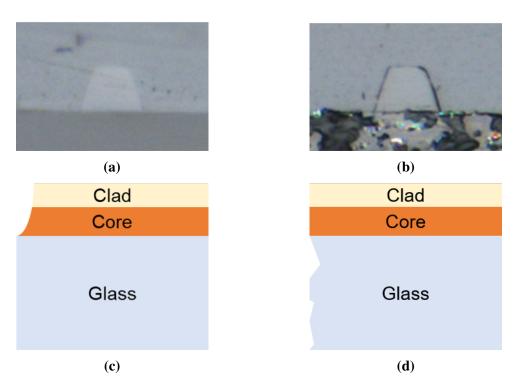

| 4.32 | (a) A cross section of a diced and polished sample, (b) a cross section of a diced only sample, (c) a schematic side view of the diced and polished sample, and (d) a schematic side view of the diced only sample | . 106 |

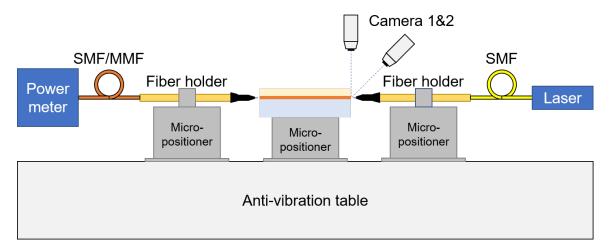

| 4.33 | A schematic of the insertion loss measurement setup                                                                                                                                                                | . 107 |

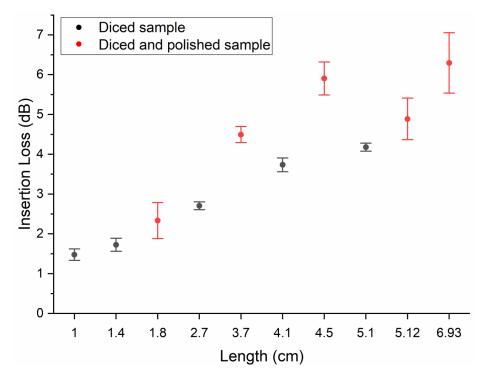

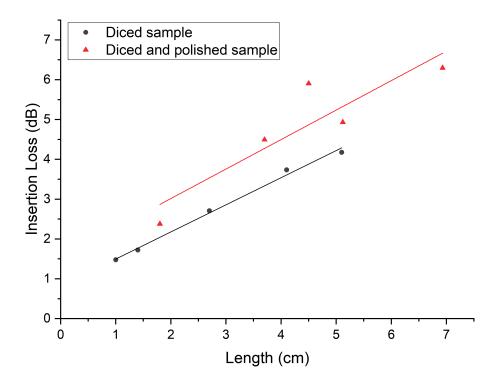

| 4.34 | Measured insertion losses of waveguide samples.                                                                                                                                                                    | . 109 |

| 4.35 | Calculated propagation losses and coupling losses of waveguide samples.                                                                                                                                            | . 110 |

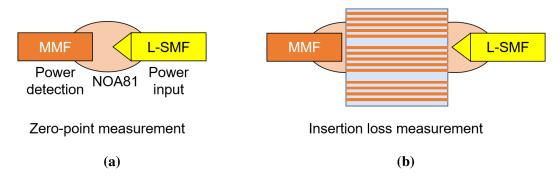

| 4.36 | (a) Zero–point measurement with the index matching liquid, and (b) inser-<br>tion loss measurement with the index matching liquid                                                                                  | . 111 |

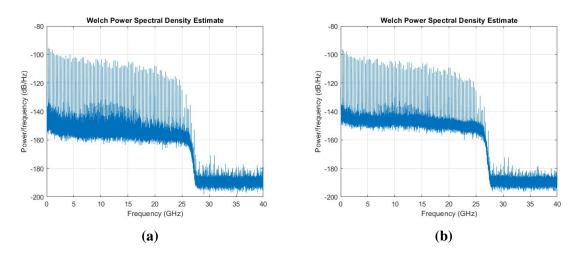

| 4.37 | Device setup for data rate measurement.                                                                                                                                                                            | . 112 |

| 4.38 | Sample preparation for waveguide characterization: (a) dicing of waveg-<br>uides to expose ends for coupling, and (b) polishing of the edge to improve<br>coupling                                                 | . 114 |

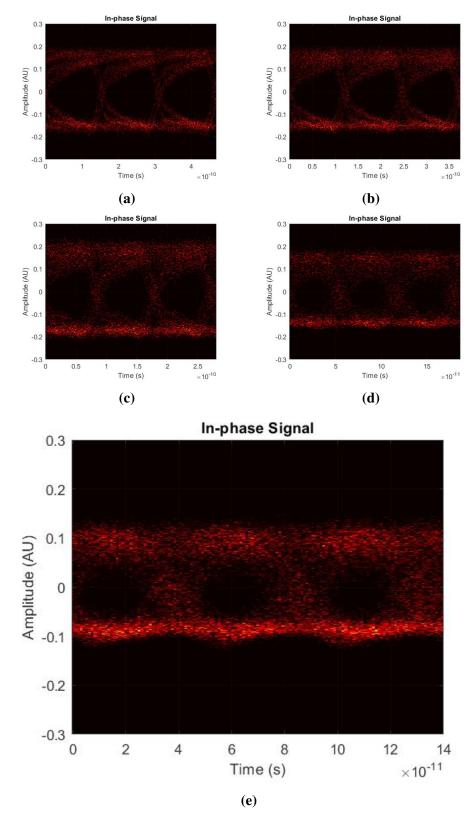

| 4.39 | Eye diagrams at data rates of (a) 6.4 Gbps, (b) 8.0 Gbps, (c) 10.7 Gbps, (d) 16.0 Gbps, and (e) 21.3 Gbps                                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

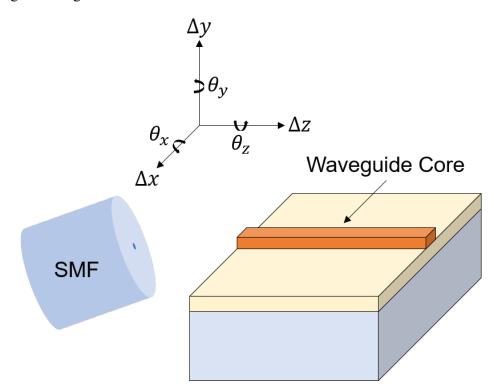

| 5.1  | Fiber alignment and its six degrees of freedom                                                                                                                                                                               |

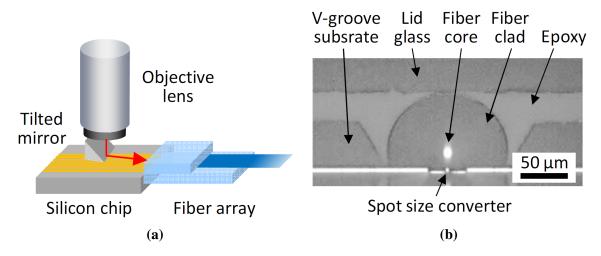

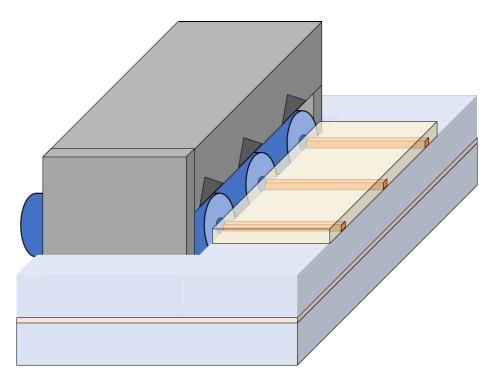

| 5.2  | A schematic of the flip v–groove approach for fiber integration on glass 120                                                                                                                                                 |

| 5.3  | A cross section of the fiber alignment stack-up                                                                                                                                                                              |

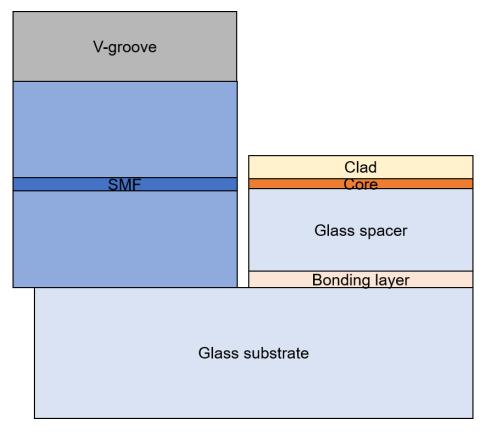

| 5.4  | (a) A schematic cross section of the testing structure, and (b) a top view image of the testing structure                                                                                                                    |

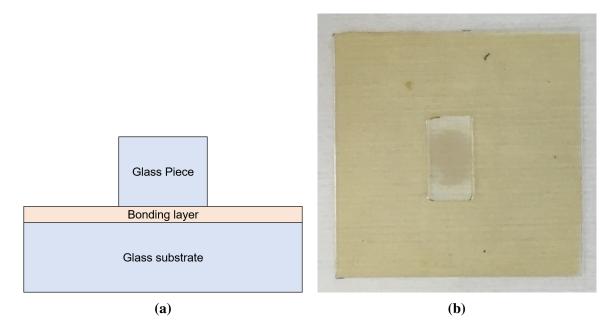

| 5.5  | (a) A glass v–groove chip with four fibers assembled, (b) a magnified im-<br>age of the edge of the v–groove chip, and (c) the cross section of a fiber<br>assembled v–groove chip flipped and bonded on the glass substrate |

## LIST OF ACRONYMS

| 3DGP   | 3D glass photonics                        |

|--------|-------------------------------------------|

| ABF    | Ajinomoto buildup film                    |

| AI     | artificial intelligence                   |

| BCB    | benzocyclobutene                          |

| BEOL   | back end of line                          |

| BSE    | backscattered electron                    |

| CMOS   | complementary metal-oxide-semiconductor   |

| CTE    | thermal expansion coefficient             |

| DOF    | depth of focus                            |

| EDS    | energy–dispersive X–ray spectroscopy      |

| EMIB   | embedded multi–die interconnect bridge    |

| i–THOP | e e                                       |

| I/O    | inputs/outputs                            |

| IC     | integrated circuit                        |

| ILD    | interlayer dielectric                     |

| InFO   | integrated fan-out                        |

| LPCVD  | low pressure chemical vapor deposition    |

| MMF    | multimode fiber                           |

| MZM    | Mach–Zehnder modulator                    |

| NA     | numerical aperture                        |

| OOK    | on–off keying                             |

| PAC    | photoactive compound                      |

| PCB    | printed circuit board                     |

| PECVD  | plasma enhanced chemical vapor deposition |

| PET    | polyethylene terephthalate                |

| PID    | photoimageable dielectric                 |

| PMMA   | poly(methyl methacrylate)                 |

| PS     | polystyrene                               |

| PU     | polyurethane                              |

| PVD    | physical vapor deposition                 |

| PZT    | lead zirconate titanate                   |

| RCC    | resin coated on copper                    |

| RDL    | redistribution layer                      |

| RGB    | red, green, and blue                      |

| RPM    | round per minute                          |

| SAP    | semi-additive process                     |

| SEM    | scanning electron microscope              |

| SiOB   | silicon optical bench                     |

|        | X X 1                                     |

| SMF  | single mode fiber             |

|------|-------------------------------|

| SMWG | single mode waveguide         |

| SNR  | signal-to-noise ratio         |

| SOI  | silicon-on-insulator          |

| TMAH | tetramethylammonium hydroxide |

| UHD  | ultra-high-definition         |

| UI   | unit interval                 |

| UV   | ultraviolet                   |

| VR   | virtual reality               |

| WLP  | wafer-level processing        |

#### SUMMARY

The development and application of artificial intelligence and augmented reality as well as billions of new devices connected to the network have resulted in unprecedented demands on high computing power and high speed communications. The focus has shifted from Moore's law on the transistor density of semiconductor chips to post–Moore's–law on the interconnect density of packages to continue improving the computing power and data rates. As the demand for data rates increases, electronic interconnects are limited to short–distance chip–to–chip communications by signal integrity issues at high frequency, which sheds a light on bringing optical interconnects onto the package for on–package long–distance communications.

The key technology to enhance electronic interconnect performance on a package is the redistribution layers, with the 2.5D interposer package with ultra–fine wiring to improve the density of interconnects. Challenges emerge as the density of lines increase with this approach such as poor adhesion due to small contacting areas. The density of microvias has not progressed as much to match the density of wires. On the other hand, silicon photonics and board–level optoelectronics have been studied and developed intensively to achieve high speed optical communications on chip. However, silicon photonics suffers from the high costs of silicon–on–insulator substrates and the back end of line fabrication processes, and the board–level optoelectronics is limited by the multimode operation and the mismatch on thermal expansion coefficients between different modules.

The objective of this research was to integrate high density electronic interconnects for chip-to-chip communications and low loss single mode optical interconnects for onpackage communications, as well as fiber coupling and integration, on glass interposers. Glass as the substrate material offers a unique combination of superior properties compared to silicon and polymer substrates. It also has a low optical absorption at telecommunication wavelengths for optical applications. This research included the following topics: 1) development and optimization of ultraviolet laser ablation process for ultra–small microvia fabrication to match the density of ultra–fine routing wires; 2) modeling, design, processing, and characterization of high–quality low loss single mode waveguides on glass interposers; 3) high–precision passive fiber coupling and integration on glass interposers.

Laser ablation on polymer dielectrics was intensively studied for the fabrication of ultra-small microvias. A picosecond UV laser drilling system was used in this study, and microvias were scaled down to  $5 \,\mu\text{m}$  in diameter from the state-of-the-art  $20 \,\mu\text{m}$  microvias by laser ablation. By adding a nanometer metal barrier layer with a high ablation threshold, the fully opened microvias were scaled down to  $1.3 \,\mu\text{m}$  in diameter, which is one fifteenth of the state of the art. Laser landing accuracy was also analyzed since the smaller microvias required multiple punches to fabricate. The average difference between the designed drilling spot and the actual landing spot was  $0.24 \,\mu\text{m}$ .

Polymer–based single mode waveguides using glass as the bottom clad was modeled, fabricated and characterized. After process optimization, defects were eliminated, hence, the measured propagation loss of fabricated waveguides was around 0.6 dB/cm, half of the previously reported value. Data rates were also measured. However, the maximum data rate was limited by the electronic components in the measurement setup to be 21.3 Gbps. The potentially supported data rates could be much higher.

High accuracy passive fiber coupling and integration on glass were also investigated. A flip v–groove approach was proposed and developed to confine degrees of freedom of fibers. Using the surface of the glass substrate as a reference and the diameter of the fiber as the core height control brought the center of the fiber core to be  $62.8 \pm 0.1 \,\mu\text{m}$ , which is very close to the height of the fabricated waveguide cores which is 63  $\mu$ m. Alignment in only one direction is needed.

# CHAPTER 1 INTRODUCTION

As the emerging technologies like cloud computing, artificial intelligence (AI), virtual reality (VR), and ultra-high-definition (UHD), gaming and streaming are developed and applied, demands for higher computing power and higher data rates between chips keep increasing. The number of transistors on a semiconductor chip doubles every two years according to the famous observation, Moore's law [1], which increases the computing power of semiconductor chips dramatically. However, as the size of transistors is scaled down to 7 nm and even smaller, Moore's Law is beginning to hit the limit of physics, and slowing down in transistor performance. Continuous scaling of transistors on semiconductor chips is no longer economical to achieve the same level of improvement on performance as well.

The focus has shifted from Moore's law with semiconductor chips to post–Moore's– law with what Prof. Tummala calls Moore's law for Packaging or Interconnects [3, 4]. This resulted in integrating multiple chips on one package to increase computing power for many applications [2, 5], as shown in Figure 1.1, and such an architecture requires advanced packaging technologies to support high data rate chip–to–chip communications. The key technology to enhance interconnect performance on a package is the redistribution layer (RDL)s, with the 2.5D interposer package with ultra–fine RDL wiring to improve the density of interconnects and performance of a package. Challenges emerge as the density of lines and microvias increase with this approach. The semi–additive process (SAP) is currently the primary technique for copper trace fabrication in panel size RDL processing. When the line width of the copper trace is scaled down to less than 2  $\mu$ m, poor adhesion due to small contacting area leads to reliability issues. Meanwhile, as the line width is scaled down to 5  $\mu$ m and less, microvias connecting thin lines in different layers has not scaled down to support high density lines. Electronic interconnects with fine copper traces

Figure 1.1: MCM-GPU: Aggregating GPU modules and DRAM on a single package [2].

and microvias are limited by signal integrity and interconnect delay issues caused by high frequency electromagnetic effects such as crosstalk, delay, resistance and capacitance when facing high data rate demands.

Fiber optics has advanced significantly over the past several decades due to the exceptional data transport ability of fibers over copper wires across long distances. Compared to copper wires, fibers have lower loss, immunity to electromagnetic interference, light weight, and they could provide extremely high data rates. Fibers are now the backbone of ever–increasing global internet traffic in modern communications. With the development and application of technologies like cloud computing and UHD streaming, as well as billions of new mobile devices that are interconnected every year, they have resulted in ever–increasing global internet traffic, which is projected to be 396 exabytes (10<sup>18</sup> bytes) per month by 2022 [6, 7], as shown in Figure 1.2. Not only telecommunication demands higher data rates, but also other demands from on–device applications such as AI and VR. Traditionally, single mode optical components are placed on a silicon optical bench (SiOB) as individual chips, which requires a large substrate to integrate. As the single mode optics

Figure 1.2: Cisco VNI forecasts 396 EB per month of IP traffic by 2022 [6].

is applied for shorter distances like chip-to-chip communications, packaging especially optical interconnects becomes the bottleneck. There are several factors contributing to this bottleneck; 1) Alignment requirement of fibers to waveguides at micron size level, and 2) optical structures fabricated on substrates to reduce coupling loss.

To address these issues for high data rate demands of on-package chip-to-chip communications, glass interposers with a combination of high-density electronic interconnects for chip-to-chip communications and single mode optical interconnects for on-package communications were proposed and developed in this work.

#### 1.1 Current Trends on High Speed Interconnects

Several approaches have been investigated and developed to optimize the cost, performance, and integration density of high–speed interconnects at a system level. The current integration approaches are high density inputs/outputs (I/O) for electronics, silicon photonics, glass photonics, and board–level optoelectronics.

Figure 1.3: (a) Schematic showing the EMIB concept [8]. (b) Schematic cross sectional image of i–THOP [9]. (c) The schematic of novel ViT interconnect configuration for 20 µm bump pitch interposer and package application. The traces are embedded in the dielectric layer and surrounded by polymer [10].

#### 1.1.1 High–Density I/O for Electronics

Increasing data traffic demands high bandwidth to transport data as well as high speed electronics to process data. Increasing I/O and component density in electronic systems requires higher density packaging and higher level of integration. Over the years, the wiring technologies for RDL have evolved from subtractive etching to SAP. Challenges emerge as the width of the copper trace is scaled down to less than 5 µm. Large areas of the sidewalls compared to the seed layer at the bottom will be etched away in the seed layer removal process, which leads to smaller contact area of copper to the substrate, and subsequent adhesion and reliability issues. The current trend is to push the line width down to submicron level with high aspect ratio to achieve high–density I/O with appropriate resistance, capacitance, and characteristic impedance.

There are three popular substrate materials used for high–density I/O in packaging: silicon, organic, and glass, as shown in Figure 1.3. Silicon interposers, led by Intel's embedded multi–die interconnect bridge (EMIB) [8], were developed using back end of line (BEOL) process. RDLs could be built directly on silicon wafers without a substrate as well, like the integrated fan–out (InFO) wafer–level processing (WLP) technology developed by TSMC [11]. The line width achieved is less than a micron, and the interconnect density is in the range of 500–1000 I/O/mm/layer. However, the cost of BEOL process is high due to primarily the small 300 mm wafer size. Organic interposers, such as integrated thin film

high density organic package (i–THOP) by Shinko [9], have a relatively low cost due to large panel processing, but the line width achieved is  $2 \mu m$ . Glass interposers, developed by 3D Packaging Research Center at Georgia Tech [10], have achieved copper traces with  $1 \mu m$  in line width with panel processing capability.

When copper traces are scaled down to increase I/O density, microvias to electrically connect copper traces in different layers must be scaled down as well to accommodate the smaller sizes of copper traces. Previously, laser drilling was widely used for microvia fabrication until the diameter of microvias was scaled down to  $40 \,\mu$ m. Microvias by photolithography replaced laser ablation when the size of microvias was lowered to  $8 \,\mu$ m, which hasn't matched the line width of copper traces developed in recent years.

#### 1.1.2 Silicon Photonics

Silicon photonics is a promising candidate to realize high density on-chip integration of electronics and photonics. A photo of such a silicon photonic chip is shown in Figure 1.4. By adopting mature complementary metal-oxide-semiconductor (CMOS) technology for high-volume semiconductor manufacturing, silicon photonics could be a low-cost solution [13], and waveguides on silicon photonic chips could have an extremely low propagation loss at around 0.1 dB/m [14]. However, there are some drawbacks with silicon photonics.

First, the light sources are a huge challenge in silicon photonics. The integration of laser on silicon photonic chips could be monolithic or heterogeneous. For monolithic integration, silicon is an obvious choice, but silicon does not have a direct bandgap, which means photons generated from the combination of electrons and holes in silicon is too low in efficiency. Silicon is able to serve as a light source through Raman scattering, which is inelastic scattering of a photon upon interaction with matter. The first pulsed Rama laser was demonstrated in 2004 by a group in UCLA [15], and the first continuous–wave Raman laser was demonstrated in 2005 by Intel [16], but the efficiency was still low, approximately one in ten million photons. Erbium doped silicon materials and erbium compound materials

Figure 1.4: Overview of current fully integrated silicon photonics technology using a 3D electronic IC [12].

use erbium as an atomic emitting center for monolithic integration. Optical-pumped Erdoped lasers were demonstrated [17] but not electrical pumped lasers. Germanium exhibits a pseudo-direct gap behavior. The band gap could be engineered so that the direct recombination of electrons and holes could happen [18]. It could be a candidate for monolithic integration of laser source. Currently the most practical on-chip light source for silicon photonics is III–V–based lasers like InP. It could be monolithically integrated via epitaxial growth [19], but the high density dislocations from large differences in thermal expansion coefficients between III–V compounds and silicon may cause reliability issues. III–V compound lasers could also be directly mounted on silicon [20], which allows pre-testing

Figure 1.5: Schematics of (a) a SMF core and (b) a silicon waveguide core.

before integration to maintain superior characteristics of the laser chips.

The other issue with silicon photonics is silicon–based waveguides and their coupling. Due to the surface roughness (around 5 nm) of the side walls of silicon waveguide cores, the propagation loss of silicon was huge compared to polymer or glass waveguides. But as the fabrication process improved, the propagation loss of silicon waveguide has been lowered to less than 1 dB/cm [21]. Even though it's still large compared to polymer and glass waveguides, it's not an obstacle for application since the lengths of the silicon waveguides are generally short. Silicon also has a relatively large refractive index. The size of the silicon waveguide core is extremely small (around  $0.5 \,\mu$ m by  $0.2 \,\mu$ m) compared to the size of the fiber core (around 8.4  $\mu$ m in diameter) as shown in Figure 1.5, so direct coupling from a fiber to a silicon–based waveguide would have a huge mode mismatch loss ( 20 dB). Additional couplers are needed to couple light from a fiber to a waveguide. For horizontal coupling, different spot size converters and couplers have been designed and tested for low coupling loss. For vertical coupling, grating couplers have been studied intensively for wide band low loss coupling.

Figure 1.6: Schematic representation of the Terabus vision of an OE–MCM (or optomodule) incorporating an 850 nm transceiver optochip as well as conventional ICs [23].

#### 1.1.3 Board–Level Optoelectronics

Traditional board–level optical systems use discrete integration of optical components and electronic chips. In a typical optical transceiver package, there are laser diodes, lenses, drivers, amplifiers, photodetectors, etc. These discrete components are placed on a SiOB [22]. Precise alignment structures for fiber positioning and coupling could be fabricated on SiOB due to its crystallinity.

The Terabus project, developed by IBM, focuses on highly integrated high density low– power and high speed optical interconnect technologies [23]. A schematic of Terabus project is shown in Figure 1.6. Optochips are mounted on a silicon carrier, and then assembled on an organic carrier with other conventional integrated circuit (IC)s. The organic carrier is then soldered to an optical printed circuit board (PCB). However, the system operates with multimode optics, and the mismatch in thermal expansion coefficient among silicon carriers, organic carriers, and optical PCBs might lead to reliability issues. Also, the silicon carrier for optochips might introduce high speed electrical losses, which leads to degradation of energy efficiency.

#### 1.1.4 Glass Photonics

Glass photonics, which emerged in recent years as a superior option over organic and silicon interposers for microelectronics applications, has been drawing tremendous attention. Glass offers a unique combination of superior properties compared with traditional silicon and organic packaging for both electronics and photonics. Some of the properties of glass and silicon are listed in Table 1.1. For optical applications, the optical absorption of glass at telecommunication wavelengths is low, and the refractive index of glass matches that of SMFs, which enables glass to be integrated as part of waveguide structures. For electronic applications, the loss tangent of glass is relatively low compared to that of silicon. The thermal expansion coefficient (CTE) of glass could also be tailored to match either silicon– or III–V–based photonic chips.

| Material Properties                                       | Glass       | Silicon     |

|-----------------------------------------------------------|-------------|-------------|

| Optical absorption $\alpha$ (cm <sup>-1</sup> ) @ 1550 nm | 0.007       | 8.2         |

| Refraxctive index $n @ 1550 \text{ nm}$                   | 1.49        | 3.48        |

| Electrical loss $\tan \theta @ 10 \text{GHz}$             | 0.006       | 0.015       |

| Thermal expansion coefficient (CTE) (ppm/K)               | 3-8.5       | 3           |

| Microscopic structure                                     | Amorphous   | Crystalline |

| Finest feature size (µm)                                  | 1           | 0.005       |

| Processing capability                                     | Panel-level | Wafer-level |

Table 1.1: Properties of glass and silicon.

The PhoxTroT project [24], developed by Fraunhofer IZM and TU Berlin, used ion exchange to modify refractive index of glass to create waveguides in the glass, with extremely low propagation losses (0.043 dB/cm at 1.31  $\mu$ m and 0.059 dB/cm at 1.55  $\mu$ m). It is shown in Figure 1.7(a). It also enables low loss coupling of glass waveguides to fiber. 3D glass photonics (3DGP) interposers, developed by Georgia Tech Packaging Research Center [25], is another candidate for glass photonics, as shown in Figure 1.7(b). Unlike

Figure 1.7: (a) Optical dual-layer waveguide integration and thin-film metallization on a 200 mm wafer level [24], and (b) The top half of glass panel after ENIG and chip assembly [25].

PhoxTroT, 3DGP interposers enable light traveling in the horizontal direction, as well as vertical directions with turning structures, vertical optical vias through glass interposers, and optical lenses, by using low loss optical polymers with the glass interposer.

#### 1.2 Unique Approach Proposed and Developed

Organic interposers do not address high–density integration need, and they are not compatible with optical interconnects on interposers. Although silicon interposers support high– density integration, and are transparent at telecommunication wavelengths, they are not able to address on–package communications, owning primarily to the huge electrical loss and the size of the chip.

In order to address the challenges of combining single mode optics with high speed electronics for high speed communications, the proposed research investigated integration of high density electronic interconnects and single mode optical interconnects, as well as fiber integration on glass interposers. A cross–sectional view of the proposed glass interposer with high density electronic interconnects and low loss single mode optical interconnects interconnects with fiber integration is shown in Figure 1.8.

Figure 1.8: A schematic of glass interposers with high–density electronic interconnects and low loss single mode optical interconnects with fiber integration.

Glass as the substrate material offers a unique combination of superior properties compared to silicon and polymer substrates. The refractive index of glass matches that of SMFs, so optical polymer waveguides on glass substrates enable direct coupling without fabricating additional coupling structures. Low optical absorption and low loss polymers could also be used as high–performance dielectric for electrical interconnects. Glass's CTE could be tailored to match either silicon based chips or III–IV based compound photonic chips. Double side fabrication and panel–level processing also reduce costs. Thus, high bandwidth communications could be achieved by integrating single mode waveguide (SMWG)s on glass interposers and passive alignment of single mode fibers. Glass with its excellent surface finish also has a low surface roughness and high dimensional stability, which enables 1 µm features similar to silicon interposers for high density integration. With ultra–fine copper traces and microvias recently developed on glass substrates, high–density electrical interconnects could be integrated on the same glass interposers.

#### 1.3 Research Objectives, Challenges, and Tasks

The objective of the research is to integrate high–density electronic interconnects with low loss single mode optical interconnects along with fiber coupling and integration on glass interposers for high speed communications. The research can be broken into three aspects, electrical interconnects, optical interconnects, and fiber integration. Detailed research objectives are listed in Table 1.2.

|                                      | Objective                                                                | Prior Art                                           | Challenges                                                             | Tasks                                                                                          |

|--------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Electronic<br>interconnects          | 5 μm in diameter<br>microvias and<br>ultra-fine copper<br>traces for RDL | 20 µm in diameter                                   | Development and<br>optimization for<br>smaller microvia<br>fabrication | Embedded trenches<br>for high–density<br>RDLs<br>Process optimization<br>for smaller microvias |

| Optical interconnects                | ≤ 0.3 dB/cm<br>SMWGs on glass<br>interposers                             | Propagation loss<br>of 0.3 dB/cm at<br>1310/1550 nm | High–quality<br>polymer SMWG<br>fabrication and<br>characterization    | Modeling, design, and<br>process optimization<br>Characterization on<br>losses and data rates  |

| Fiber<br>coupling and<br>integration | <ul> <li>≤ 1 µm high<br/>accuracy<br/>positioning</li> </ul>             | Active alignment                                    | Precise alignment structure                                            | Glass-to-glass bond-<br>ing                                                                    |

|                                      |                                                                          | Passive alignment                                   | fabrication on glass interposers                                       | Fibers in v–groove<br>chips on glass                                                           |

Table 1.2: Research objectives, challenges, and tasks.

Electrical interconnects pose many issues: traditional SAP technology to fabricate copper traces scaling down to less than 5  $\mu$ m creates adhesion challenges between copper traces and the substrate. New fabrication techniques need to be developed to address this issue. The other issue is to do with the size of microvias. Even though the width of copper traces is being scaled down to 5  $\mu$ m and below, the currently available microvia technology connecting copper RDL traces is still at around 20  $\mu$ m in diameter (fabricated by laser ablation). Smaller microvias are needed to match the size of copper traces that are less than 5  $\mu$ m. The research tasks to address the challenges to high density electronic interconnects are: 1) Development and optimization of embedded trenches for high density copper traces, and 2) Development and optimization of ultraviolet (UV) laser ablation process for ultra–small microvia fabrication.

Optical interconnects have a set of their own challenges. One challenge is to do with low loss optical interconnects with single mode waveguide fabrication, and characterization. Optical polymers were studied and developed intensively 20 years ago by research groups and chemical companies, but the development of new and low loss optical polymers basically stopped due to lack of customers and applications. The main challenges for low loss optical interconnects on glass are identifying and developing optical polymers to be used with glass and silicon substrates as well as their fabrication and reliability of high– quality single mode waveguides. To address these challenges, the tasks include modeling, design, processing, and characterization of high–quality low loss single mode waveguides.

The other challenge in optical interconnects that needs to be addressed is precise fiber positioning. To minimize coupling loss, fiber alignment accuracy must be less than  $\pm 2 \,\mu m$  (more toward  $\pm 1 \,\mu m$ ). For traditional silicon optical benches, precise positioning of fiber could be achieved with the advanced etching technologies available such as polishing and creating tapered structures in silicon along with its inherent advantages from the crystallinity of silicon. However, with glass being an amorphous and brittle material, it is extremely challenging to fabricate structures for precise positioning either with chemical etching or physical machining. Additional structures must be introduced to achieve high accuracy alignment. So, the tasks include glass–to–glass bonding, and fibers in v–groove chips assembled on glass.

#### **1.4 Dissertation Overview**

The dissertation document is organized as follows. Chapter 1 provided the necessary background and strategic need for the research topic. It also defined the research objectives, identified three main challenges for integrating optical interconnects and electrical interconnects on a single package for high data rate communications. It also outlined the unique approach and research tasks to address the challenges. Chapter 2 summarizes the literature describing the scaling down of microvias for high density electrical interconnects, the materials used for fabrication of single mode waveguides, board–level photonic and electronic integration, and fiber integration. Chapter 3 describes the modeling, process development, fabrication, and characterization of ultra–short (picosecond) pulsed laser ablation for ultra– small microvia fabrication. Chapter 4 describes the modeling, design, fabrication, and characterization of polymer SMWGs on glass. Chapter 5 describes the design and analysis of fiber integration on glass substrates. The research results and possible future work beyond the scope of this dissertation are summarized in Chapter 6.

# CHAPTER 2 LITERATURE SURVEY

This chapter reviews the most recent work in three areas of research which are the focus of this thesis work. The first section discusses high-density I/O for electronics including ultra–fine routing wires and microvias, followed by the second section summarizing low loss optical interconnects including SMWGs fabricated using different types of materials. The last section covers fiber coupling techniques and methods.

#### 2.1 High–Density I/O for Electronics

As the feature size of transistors is scaled down to 7 nm and below, Moore's law is approaching its limit, and the industry and the academia have shifted their focuses from shrinking the transistor sizes to increasing the packaging density. The key technology to improve electronic interconnect density is RDLs, and microvias are one of the crucial elements of RDLs. As a result, reducing the dimensions of routing lines and spaces in RDLs to increase I/O density has been widely recognized and studied. Interposer technologies to address this issue have been evolving, from high–cost but high–density silicon–based interposers, to organic and panel–glass–based interposers, whose densities have been developed to try to match silicon while the costs wouldn't be as high. As the sizes of routing wires and spaces on package RDLs are scaled down to 2–1  $\mu$ m [26, 27], microvias to connect routing wires between layers haven't been progressed much to match the wiring density. To meet the requirement of the next generation packaging for high performance computing, the scaling of microvias plays the critical role.

There are two major technologies to fabricate microvias, photolithography (photovias), and laser ablation. Photolithography drew attention in fabricating microvias due to its ease to use and the ability to form small microvias. The dimension of microvias in polymer has evolved from  $10 \,\mu\text{m}$  in diameter in a 5  $\mu\text{m}$  thick film with a 40  $\mu\text{m}$  pitch [10], to 4  $\mu\text{m}$  in diameter in a 3  $\mu\text{m}$  thick film [28]. With the development of photoimageable dielectric (PID) materials, 2–3  $\mu\text{m}$  microvias were also demonstrated [29, 30]. As the size of microvias is scaled down even further, new PIDs are needed to meet the critical dimension requirement. However, the availability of the suitable PID materials limits the development of even smaller microvias.

Laser ablation as a competing technology to fabricate microvias has been developed in parallel with photovias. It is the most economical method for mass production. Unlike photolithography, laser ablation is not limited to the substrate material to be drilled, which promotes the widespread use of laser ablation in packaging industry. The basic principle of laser ablation is to use high concentration photons in the laser beam to vaporize or ionize the material to be drilled. The intensity of the laser beam has to reach a certain level for the ablation to happen, which is called the ablation threshold of the material. If the intensity of the beam doesn't reach the threshold, the laser beam could only heat the material up or melt it, but it won't remove it away from the substrate.

Different laser systems have their own advantages and disadvantages for certain applications. Widely used lasers with regards to wavelengths are  $CO_2$  lasers (infrared), UV lasers, and excimer lasers (deep–UV). In terms of the laser operation mode, lasers could also be categorized as continuous–wave lasers, and pulsed lasers, whose pulse width could be several nanoseconds, or on the picosecond level, or on the femtosecond level.  $CO_2$  lasers have longer wavelengths among the aforementioned laser systems and they operate in a continuous wave mode, which limit  $CO_2$  lasers to fabricate microvias with the diameter of 60–80 µm and above [31]. As the wavelength of the laser systems becomes shorter and into the UV range, it helps the laser system focus the beam into a smaller size. The state–of–the–art microvias fabricated by a nanosecond UV laser are 20 µm in diameter [32]. As the pulse width of the UV laser becomes shorter, photons in a laser beam could be more concentrated, which reduces the heat affected zone surrounding the drilling area.

Figure 2.1: Schematics of laser drilling on RCC with (a) a hybrid laser system and (b) two—step UV laser drilling system. © 2020 IEEE

So picosecond and femtosecond UV lasers are favored over nanosecond UV lasers in terms of the micromachining quality and the cost of the lasers [33]. Excimer lasers have even shorter wavelengths compared to general UV lasers. Excimer laser ablation could achieve microvias of 5 µm in diameter [34]. However, excimer lasers suffer from high costs and high maintenance like femtosecond laser systems.

Using a single laser might not achieve microvias with the desired dimensions. Hybrid laser systems were also developed to create smaller microvias by using resin coated on copper (RCC) foil instead of bare polymer. One type of hybrid laser ablation includes a high–power UV laser drilling on the top copper layer, and subsequently a  $CO_2$  laser drilling polymer through the opening in the copper layer, as shown in Figure 2.1(a). Copper has a high ablation threshold than polymer in general, so when the UV laser beam with the same power hit the copper, it will result in a smaller opening, which then serves as a mask for the following ablation in the polymer by  $CO_2$  lasers. Since  $CO_2$  lasers won't remove copper, the microvia would stay small after the ablation and copper removal. The other type of hybrid laser ablation is a two–step UV laser ablation [35, 36], as shown in Figure 2.1(b). Copper drilling is accomplished by the first step high–power UV laser ablation. The drilling time and drilling power are controlled in a way that it only ablates copper but not the resin underneath. The same laser is then adjusted to a lower power to drill through the resin without damaging the copper on top or underneath.

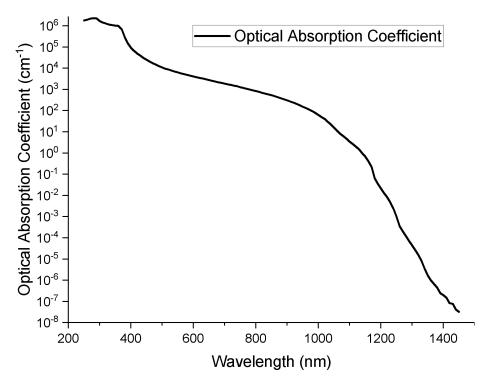

Figure 2.2: Optical absorption coefficient of silicon [37].

This thesis attempts to make contribution to fabricate ultra–small microvias for high density electronic interconnects using a picosecond UV laser in traditional and novel dielectric materials.

## 2.2 Low Loss Optical Interconnects

This section discusses selected publications in the area of SMWG materials, integration methods, and applications along with three categories of SMWG materials that are based on silicon, glass, and polymer.

#### 2.2.1 Silicon–Based SMWGs

Silicon-based SMWGs are the key component of silicon photonics. The most commonly used material platform is silicon-on-insulator (SOI), which is a thin silicon layer on a buried oxide  $(SiO_2)$  layer on bulk silicon. There are three major silicon-based materials for waveguide cores, silicon, silicon nitride, and silicon germanium. Silicon is used as a

waveguide core material due to three reasons. First, the absorption of silicon at telecommunication wavelengths is low, as shown in Figure 2.2, as a result of which the propagation loss of silicon waveguides is tremendously reduced. The second reason is the electro– optical effects in silicon, which make it possible to modulate signals in silicon waveguides [38]. The third reason is that the large contrast between silicon and silicon dioxide makes the size of silicon waveguides small and compact which enables high density optical interconnects on chip.

The propagation loss of SOI waveguides was not great at the beginning of the development. Due to the traditional fabrication process, dry etching, the sidewalls of the silicon cores were extremely rough, around 7 nm, which contributes to the propagation loss as high as 5-12 dB/cm. Various techniques have been developed to address the roughness issue and then reduce the propagation loss. By using wet etching instead of dry etching, the sidewall roughness could be reduced down to 1.2 nm, and the propagation loss could be lowered to 0.85 dB/cm [39]. By adding a  $SiO_2$  hard mask in the dry etching process, the propagation loss of silicon waveguide could also be reduced since the sidewall roughness was reduced to 0.7 nm, and the measured propagation loss was 0.89 dB/cm [40]. The performance of silicon waveguides were also improved by using CMOS platform and optimized etching process to lower the propagation loss down to 0.45 dB/cm [41].

Silicon nitride is a widely used material in CMOS fabrication. It is usually deposited by either low pressure chemical vapor deposition (LPCVD) at high temperature or plasma enhanced chemical vapor deposition (PECVD) at low temperature. Compared to silicon, silicon nitride has low optical absorptions including most of the visible spectral range. Silicon nitride as core material provides a low index contrast system compared to silicon cores, which makes the performance of silicon nitride waveguides not as sensitive to the roughness of the sidewall as silicon waveguides. By fabricating high aspect ratio silicon nitride cores, the scattering loss due to sidewall roughness could be greatly reduced compared to silicon core, which leaded to several orders of magnitude lower in propagation loss, as low as 0.1 dB/m [14, 42]. Silicon nitride could be an alternative to silicon as the waveguide core material due to the extremely low propagation loss, but this is at the expense of lateral or vertical confinement owing to the low index contrast.

Silicon–germanium alloy has been drawing considerable attention in silicon photonics due to the capability of band gap engineering and lattice parameter engineering on the material. Germanium has a relatively high absorption at telecommunication wavelengths, and hence it is mostly used as a photodetector material but not a waveguide material. Germanium could enhance silicon's nonlinear response but it's at the expense of increasing propagation loss at telecommunication wavelengths. Silicon germanium as a waveguide core material does show low propagation loss at mid–infrared wavelength [43]. It could also be developed as modulators [44], photodetectors [45], and even on–chip light sources due to Raman scattering [18].

The propagation loss of waveguides in silicon photonics does not significantly impact the performance of the chip since the propagation length on a chip tends to be shorter compared to chip-to-chip or on-package interconnects. However, since the sizes of siliconbased cores are an order of magnitude smaller than the core sizes of SMFs or polymerbased SMWGs, direct coupling from silicon-based SMWGs to optical interconnects outside of the silicon photonic chip will cause up to 20 dB loss due to mode mismatch. Two major techniques to improve coupling efficiencies are spot size converters and grating couplers. A comparison table of these methods is shown in Table 2.1.

Spot size converters use adiabatic coupling to convert the spot size of the propagating mode confined in silicon to a relatively large mode comparable to SMF. Adiabatic coupling uses a tapered silicon waveguide to convert first–order mode propagating in the waveguide to higher–order modes or radiation modes, so when a polymer–based waveguide core is placed in close proximity of the tapered silicon core or in direct contact, light will be coupled into the polymer core, as shown in Table 2.1. The coupling loss between a silicon waveguide to a polymer waveguide could be less than 1 dB [46, 48]. Various designs for

Table 2.1: Comparison of two types of coupling for silicon–based SMWGs.

spot size converters could reduce the coupling loss further down to 0.5 dB [49, 50]. Spot size converters could be then coupled to other SMWGs or SMFs.

Grating couplers are large periodic structures designed to couple waves or match phases in and out of the structure, as shown in Table 2.1. Grating couplers enable vertical coupling from silicon waveguides directly to SMFs unlike vertical coupling which requires couplers to be placed at the edge and polishing of facets. Vertical coupling is also beneficial to wafer–scale testing. However, grating couplers suffer from backscattering and enlarged mode compared to SMFs, which cause high coupling loss. Different designs and fabrication methods could lower the coupling loss down to 1–3 dB [51, 52]. By introducing metal mirrors in the structure, coupling loss could be significantly reduced to 0.5 dB [53].

#### 2.2.2 Glass–Based SMWGs

Glass has been drawing attention as a promising candidate in optoelectronics packaging due to its low optical absorption coefficient at visible and telecommunication wavelengths, the composition of glass is similar to SMFs, and its panel–level processing capability. Changing refractive index of certain area of the glass could create index contrast between the area and its surroundings, which forms a waveguide in glass. Two popular techniques to modify refractive indices are laser writing and ion exchange. The former uses ultra–fast laser pulses to locally melt and recrystallize glass in a certain region so that the crystal structure and the concentration of glass components change in that area and its surrounding [54]. Laser–written glass waveguides could achieve extremely low propagation loss of 0.062 dB/cm [55].

Ion exchange to modify refractive index of a local area of glass has been studied for decades. The increase or decrease of refractive index is caused by two major effects, the size difference of the replacing and replaced ion, and the difference in electron polariz-ability of the two ions. Smaller ions replacing larger ions result in the collapsing of glass network, which in turn makes the area denser, and the refractive index larger. Ions with larger polarizability replacing ions with smaller polarizability increase the refractive index as well. Fraunhofer IZM developed a two–step high temperature ion exchange process to fabricate graded index SMWGs in glass, which has a low propagation loss of 0.059 dB/cm [24].

#### 2.2.3 Polymer–Based SMWGs