# TRADE-OFFS BETWEEN PERFORMANCE AND RELIABILITY OF SUB 100-NM RF-CMOS TECHNOLOGIES

A Thesis Presented to The Academic Faculty

by

Rajan Arora

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology Dec 2012

# TRADE-OFFS BETWEEN PERFORMANCE AND RELIABILITY OF SUB 100-NM RF-CMOS TECHNOLOGIES

Approved by:

Professor John D. Cressler, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Shyh-Chiang Shen School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Jeffrey A. Davis School of Electrical and Computer Engineering Georgia Institute of Technology Professor John Papapolymerou School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Paul A. Kohl School of Chemical and Biomolecular Engineering Georgia Institute of Technology

Date Approved: 11 September 2012

To my mother Mrs. Raj Arora

For having confidence in my abilities and supporting me through all those difficult times

## ACKNOWLEDGEMENTS

I would first like to express my deepest gratitude to Prof. John D. Cressler for his guidance and support as my doctorate advisor. His teaching and research are instrumental in my decision to pursue a Ph.D. in the field of silicon based microelectronics. Thank you Sir for being so patient with me, and working so hard to bring us the best opportunities and resources for research!

I would like to acknowledge Prof. John Papapolymerou, Prof. Shyh-Chiang Shen, Prof. Jeff Davis, and Prof. Paul Kohl for serving in my dissertation committee and offering invaluable insights into my research.

I have benefitted from the guidance and knowledge provided by Prof. Ron Schrimpf, Prof. Dan Fleetwood, and Dr. Enxia Zhang during my master's education at Vanderbilt University and throughout my Ph.D. program. They remain great mentors and awesome friends.

A big thank you to all members of the SiGe team at Georgia Tech. Without their support and friendship this work could not have been possible. I must thank the infamous "Dunkin" run group for all those life related discussions on the way to buy coffee. It was probably the company of those cool friends that took me to the shop every day rather than the quality of the coffee (No offense Dunkin!).

I must thank the GEDC support staff Lisa and Roosevelt for their friendship and support.

Big thanks to Stewie, Peter, Meg, Bryan, Chris, Louis, Quagmire, Joe, and Cleveland for making me laugh through all these years. I would also like to thank all friends over the past 27 years whom I have not mentioned above.

Last, but not least, I have to thank my family for their love and being there for

any sort of help whenever I needed it. Love you all!

# TABLE OF CONTENTS

| DE  | EDIC        | ATION  | •                                                          | iii           |

|-----|-------------|--------|------------------------------------------------------------|---------------|

| AC  | CKN         | OWLEI  | DGEMENTS                                                   | $\mathbf{iv}$ |

| LIS | <b>ST O</b> | F TAB  | BLES                                                       | x             |

| LIS | <b>ST O</b> | F FIG  | URES                                                       | xi            |

| SU  | MM          | ARY .  |                                                            | xx            |

| Ι   | IN          | TROD   | UCTION                                                     | 1             |

|     | 1.1         | Origin | and History of the Problem                                 | 1             |

|     | 1.2         | Sub 10 | 00-nm CMOS Technologies                                    | 4             |

|     |             | 1.2.1  | Strained-Silicon CMOS                                      | 4             |

|     |             | 1.2.2  | Silicon-on-Insulator Technology                            | 4             |

|     |             | 1.2.3  | Digital-CMOS vs. RF-CMOS                                   | 6             |

|     |             | 1.2.4  | BEOL in Short-Channel CMOS Technologies                    | 7             |

|     | 1.3         | Reliab | ility Mechanisms in a CMOS Technology                      | 8             |

|     |             | 1.3.1  | Hot-Carrier Effects                                        | 8             |

|     |             | 1.3.2  | Negative/Positive Bias Temperature Instability (NBTI/PBTI) | 9             |

|     |             | 1.3.3  | Dielectric Breakdown                                       | 9             |

|     |             | 1.3.4  | Large RF Stress Effects in CMOS                            | 9             |

|     |             | 1.3.5  | Latchup                                                    | 10            |

|     |             | 1.3.6  | Ionizing Radiation Damage                                  | 10            |

|     |             | 1.3.7  | Single-Event Effects (SEE)                                 | 11            |

|     |             | 1.3.8  | Low- or High- Temperature Effects                          | 12            |

|     |             | 1.3.9  | Electro-Migration                                          | 12            |

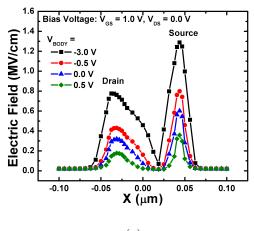

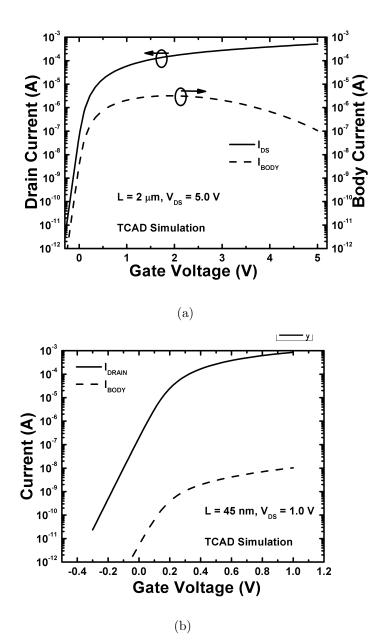

|     |             | 1.3.10 | Electro-Static Discharge (ESD)                             | 12            |

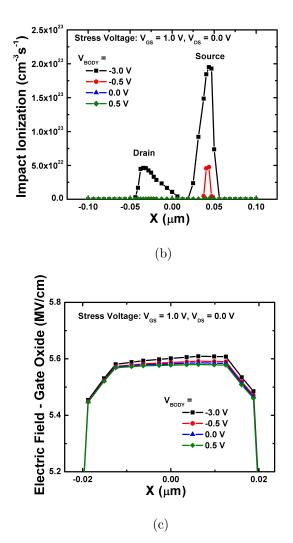

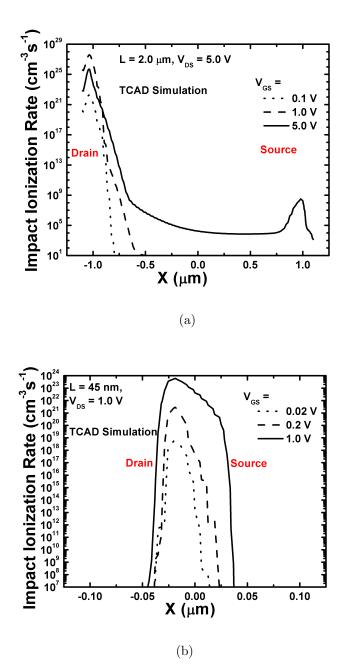

|     |             | 1.3.11 | Antenna Effects                                            | 13            |

|     | 1.4         | Organi | ization and Contributions of the Dissertation              | 14            |

| Π   | -   | -      | ING VOLTAGE CONSTRAINTS IN 45-NM SOI NFETS<br>SCODE CORES                                           | 17      |

|-----|-----|--------|-----------------------------------------------------------------------------------------------------|---------|

|     | 2.1 | Overv  | iew                                                                                                 | 17      |

|     | 2.2 | Motiv  | ation                                                                                               | 17      |

|     | 2.3 | Device | e Technology and Experimental Details                                                               | 19      |

|     | 2.4 | Device | e Voltage Constraints                                                                               | 21      |

|     |     | 2.4.1  | Impact of Gate and Drain Bias on the Power-Gain and Single-<br>Tone Linearity of a FB and BC Device | 21      |

|     |     | 2.4.2  | Hot-Carrier Reliability of a Single FB and BC Device                                                | 21      |

|     | 2.5 | Circui | it Voltage Constraints                                                                              | 25      |

|     |     | 2.5.1  | Cascode Cores in 45-nm CMOS-on-SOI                                                                  | 25      |

|     |     | 2.5.2  | Impact of Gate and Drain Bias on the Power-Gain and Linearity of a Cascode Core                     | 25      |

|     |     | 2.5.3  | Hot-Carrier Reliability of the Cascode Cores                                                        | 26      |

|     |     | 2.5.4  | Voltage Drop Across the Cascode and the Common-Source<br>Device in a Cascode Core                   | 30      |

|     | 2.6 | Summ   | nary                                                                                                | 31      |

| III |     |        | BODY-BIAS TO MODULATE PERFORMANCE AND<br>LITY OF SOI MOSFETS AND CIRCUITS                           | 33      |

|     | 3.1 | Overv  | iew                                                                                                 | 33      |

|     | 3.2 | Introd | luction                                                                                             | 33      |

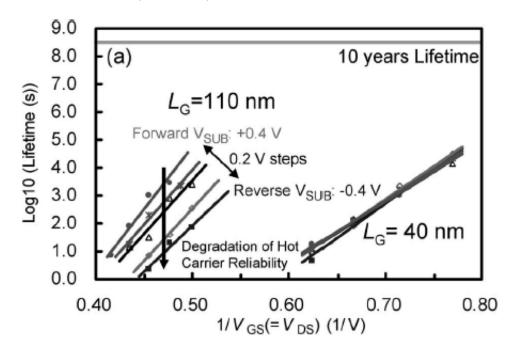

|     | 3.3 | Impac  | et of Body Bias on the Device Performance and Reliability                                           | 35      |

|     | 3.4 | Using  | Body-Contact to Mitigate Ionizing Radiation Damage                                                  | 39      |

|     | 3.5 | -      | et of Body Bias on the Performance and Reliability of Single-<br>Double-Throw (SPDT) Switches       | 43      |

|     | 3.6 | Summ   | nary                                                                                                | 52      |

| IV  |     |        | OF DEVICE WIDTH ON PERFORMANCE AND RE                                                               | -<br>53 |

|     | 4.1 | Overv  | iew                                                                                                 | 53      |

|     | 4.2 | Introd | luction                                                                                             | 53      |

|     | 4.3 | Effect | of Finger Width on Device RF Performance                                                            | 57      |

|    | 4.4        | Effect of Finger Width on Device Reliability                                                                             | 58  |

|----|------------|--------------------------------------------------------------------------------------------------------------------------|-----|

|    | 4.5        | Model for Hot-Carrier Degradation in CMOS Technologies $\ldots$ .                                                        | 63  |

|    | 4.6        | Summary                                                                                                                  | 67  |

| V  | INC        | PACT OF CMOS SOURCE/DRAIN METAL CONTACT SPAC<br>G AND GATE-FINGER TO GATE-FINGER SPACING ON<br>RFORMANCE AND RELIABILITY |     |

|    | 5.1        | Overview                                                                                                                 | 68  |

|    | 5.2        | Introduction                                                                                                             | 68  |

|    | 5.3        | Impact on RF Performance and DC Reliability                                                                              | 70  |

|    | 5.4        | Impact on RF Reliability                                                                                                 | 73  |

|    | 5.5        | Mechanisms                                                                                                               | 78  |

|    | 5.6        | Impact of Asymmetric Halo Doping on the Performance and Reliability of Sub 100-nm CMOS                                   | 82  |

|    | 5.7        | Summary                                                                                                                  | 85  |

| VI |            | YOGENIC LATCHUP IN SHORT-CHANNEL CMOS TECH-<br>LOGIES                                                                    | 86  |

|    | 6.1        | Overview                                                                                                                 | 86  |

|    | 6.2        | Introduction                                                                                                             | 86  |

|    | 6.3        | Latchup Fundamentals                                                                                                     | 88  |

|    | 6.4        | Latchup Device Physics                                                                                                   | 88  |

|    | 6.5        | Latchup Characterization at Room Temperature                                                                             | 91  |

|    | 6.6        | Latchup Characterization Across Temperature                                                                              | 94  |

|    | 6.7        | Single-Event Latchup at Cryogenic Temperature                                                                            | 95  |

|    | 6.8        | TCAD Modeling of Latchup in CMOS Technologies                                                                            | 98  |

|    | 6.9        | Summary                                                                                                                  | 101 |

| VI | USI<br>HB' | NG TCAD TO MODEL MIXED-MODE DAMAGE IN SIGE                                                                               | 102 |

|    | 7.1        | Overview                                                                                                                 | 102 |

|    |            |                                                                                                                          |     |

|    | 7.2        | Introduction                                                                                                             | 102 |

# LIST OF TABLES

| 1 | Voltage and current across the cascode devices                                                                                       | 29 |

|---|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | Devices used to study the impact of width on performance and reliability                                                             | 58 |

| 3 | Devices used to study the impact of source/drain metal contact and gate-finger to gate-finger spacing on performance and reliability | 70 |

# LIST OF FIGURES

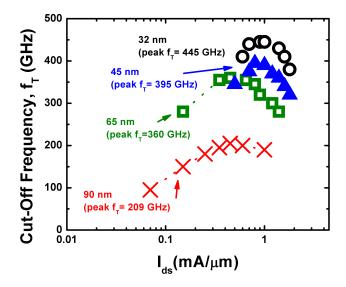

| 1  | Cut-off frequency $(f_T)$ as a function of drain current for the nFETs from different sub 100-nm RF-CMOS technologies [10]                                                                                                                         | 2  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

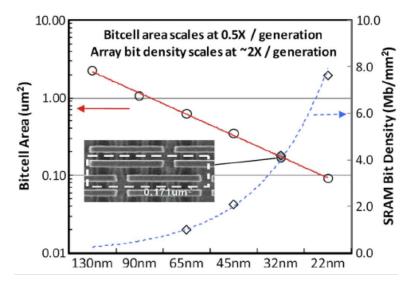

| 2  | SRAM bit cell area and bit density as a function of CMOS technology node [10].                                                                                                                                                                     | 2  |

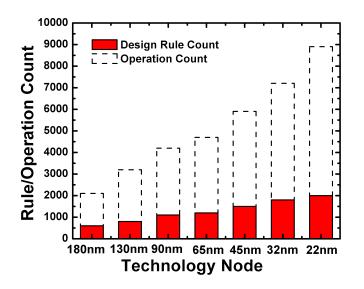

| 3  | Operation count and the design rule count of a single integrated circuit as a function of technology scaling [20]                                                                                                                                  | 3  |

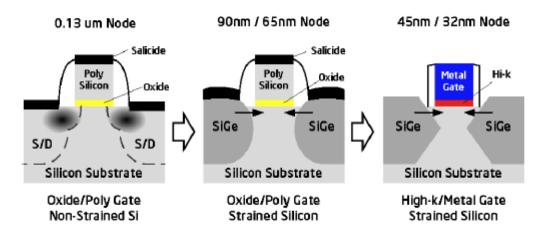

| 4  | Evolution of CMOS transistor architecture in the last decade, from a non-strained oxide/poly gate structure to a high-k/metal-gate strained-silicon transistor at the 32-nm node.                                                                  | 5  |

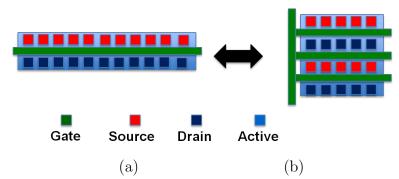

| 5  | Top-view layout comparison of (a) single-finger digital nFET and (b) multi-finger RF nFET.                                                                                                                                                         | 7  |

| 6  | Side-view layout of a multi-finger RF nFET                                                                                                                                                                                                         | 7  |

| 7  | SEM images of 130-nm six layer metal stack vs. 32-nm eight layer metal stack [10]                                                                                                                                                                  | 8  |

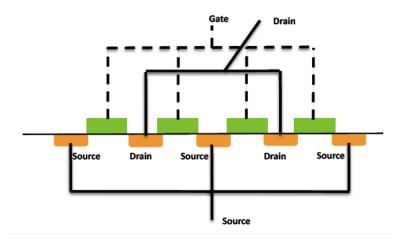

| 8  | Schematic representing the fundamental radiation induced electron-hole pair generation with bulk hole trapping and movement of the charge centroid to the interface under bias [38].                                                               | 11 |

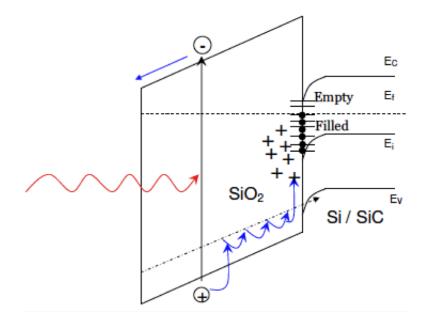

| 9  | Possible radiation-induced leakage paths along the (a) surface of buried-<br>oxide (BOX) and (b) STI sidewalls                                                                                                                                     | 12 |

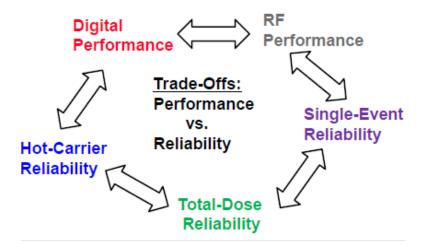

| 10 | Trade-offs between performance and reliability in sub 100-nm CMOS technologies.                                                                                                                                                                    | 14 |

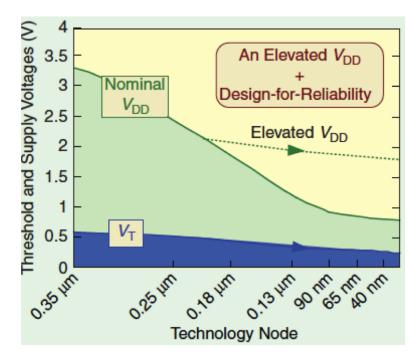

| 11 | Transistor threshold voltage and supply voltage as function of technology node [48].                                                                                                                                                               | 18 |

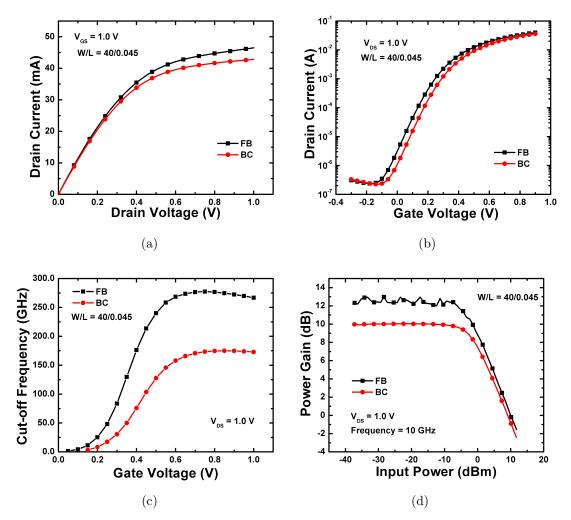

| 12 | Measured (a) drain current as a function of drain voltage, (b) drain<br>current as a function of gate voltage, (c) cut-off frequency as a function<br>of gate voltage, and (d) power-gain as a function of RF input power of<br>a FB and BC device | 20 |

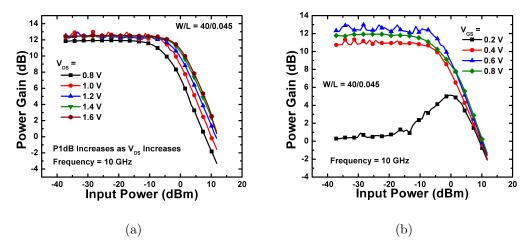

| 13 | Measured (a) power-gain as a function of RF input-power of a FB device with varying drain voltage ( $V_{GS} = 0.6$ V) and (b) power-gain as a function of RF input-power of a FB device with varying gate voltage ( $V_{DS} = 1.0$ V).             | 22 |

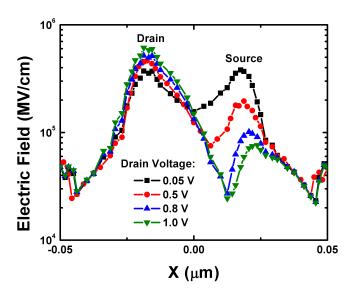

| 14 | Electric field in the channel region of a 45-nm nMOSFET for varying drain bias.                                                                                                                                                                    | 22 |

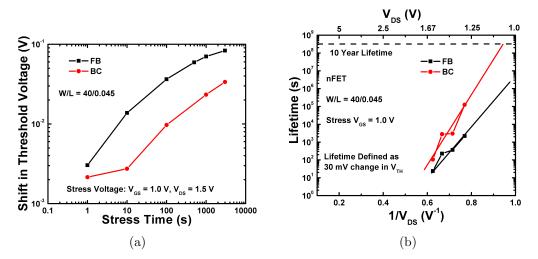

| 15 | (a) Shift in threshold voltage as a function of stress time of FB and BC devices. (b) Lifetime (in seconds) as a function of the inverse of drain voltage of FB and BC devices                                                                                                                                                                                                                                                                             | 23 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

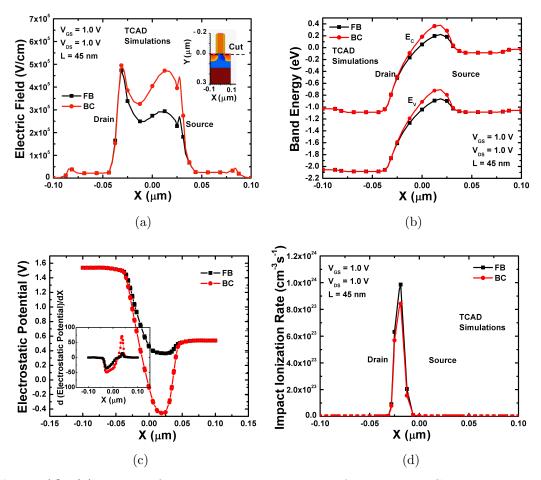

| 16 | (a) Electric field in the channel region of a FB and BC device at constant gate and drain voltage ( $V_{GS} = 1.0 \text{ V}$ , $V_{DS} = 1.0 \text{ V}$ ). (b) Conduction band energy in the channel region of a FB and BC device. (c) Electrostatic potential in the channel region of a FB and BC device. (d) Impact ionization induced avalanche generation rate in the channel region of a FB and BC device.                                           | 24 |

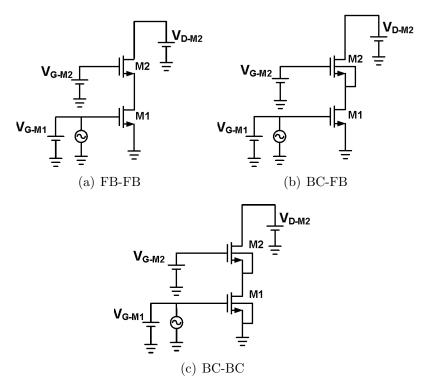

| 17 | Cascode test structure with (a) FB common-source and cascode device<br>(b) FB common-source and BC cascode device (c) BC common-source<br>and BC cascode device                                                                                                                                                                                                                                                                                            | 26 |

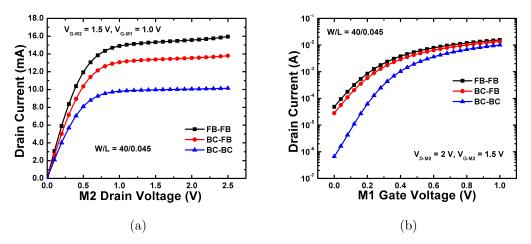

| 18 | (a) Measured drain current as a function of the drain voltage and (b) drain current as a function of M1 gate voltage of the FB-FB, BC-FB and BC-BC cascode cores.                                                                                                                                                                                                                                                                                          | 27 |

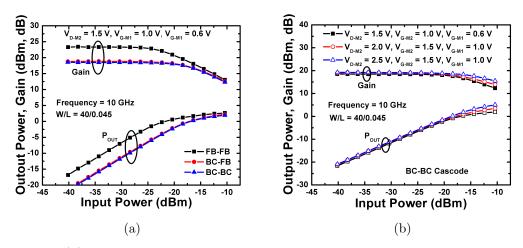

| 19 | Cut-off frequency as a function of M1 gate voltage of the FB-FB, BC-FB and BC-BC cascode cores.                                                                                                                                                                                                                                                                                                                                                            | 27 |

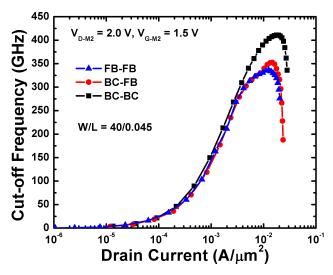

| 20 | (a) Power-gain as a function of RF input-power of FB-FB, BC-FB, and BC-BC cascodes ( $V_{D-M2} = 1.5 \text{ V}$ , $V_{G-M2} = 1.0 \text{ V}$ , $V_{G-M1} = 0.6 \text{ V}$ )).<br>(b) Power-gain as a function of RF input-power of BC-BC cascode for varying bias voltage.                                                                                                                                                                                 | 28 |

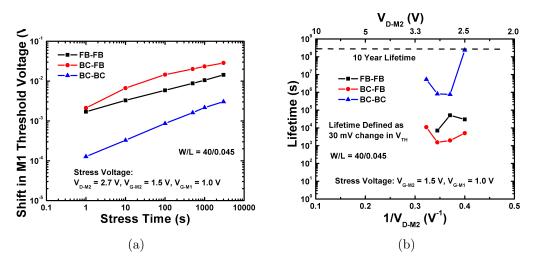

| 21 | (a) Shift in threshold voltage as a function of stress time of the three cascodes. (b) Lifetime (in seconds) as a function of the inverse of drain voltage of the cascodes                                                                                                                                                                                                                                                                                 | 28 |

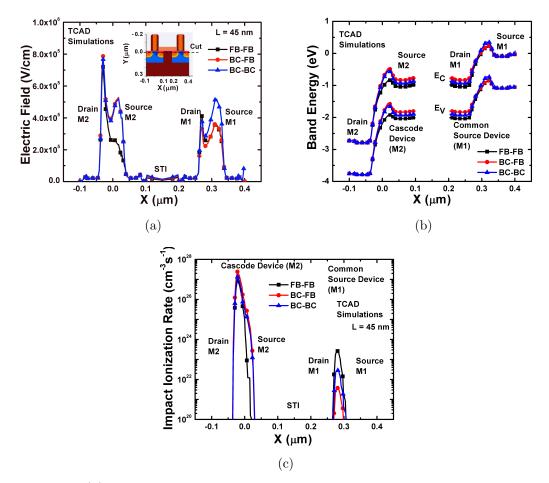

| 22 | (a) Electric field in the channel region of a FB-FB, BC-FB and BC-BC cascode at constant gate and drain voltage. (b) Conduction band energy in the channel region of a FB-FB, BC-FB, and BC-BC cascode at constant gate and drain voltage. (c) Avalanche generation in the channel region of a FB-FB, BC-FB and BC-BC cascode at constant gate and drain voltage ( $V_{D-M2} = 2.7 \text{ V}$ , $V_{G-M2} = 1.5 \text{ V}$ , $V_{G-M1} = 1.0 \text{ V}$ ). | 29 |

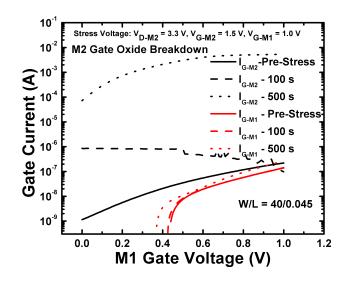

| 23 | Gate current as a function of the common-source device gate voltage<br>for varying stress conditions of the BC-FB cascode (Stress voltage:<br>$V_{D-M2} = 3.3 \text{ V}, V_{G-M2} = 1.5 \text{ V}, V_{G-M1} = 1.0 \text{ V}).$                                                                                                                                                                                                                             | 30 |

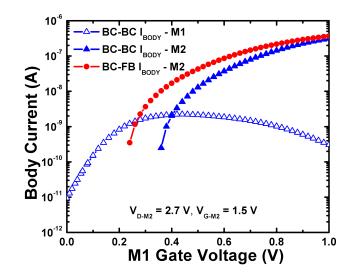

| 24 | TCAD simulated body current as a function of M1 gate voltage of the BC-BC and BC-FB cascode                                                                                                                                                                                                                                                                                                                                                                | 31 |

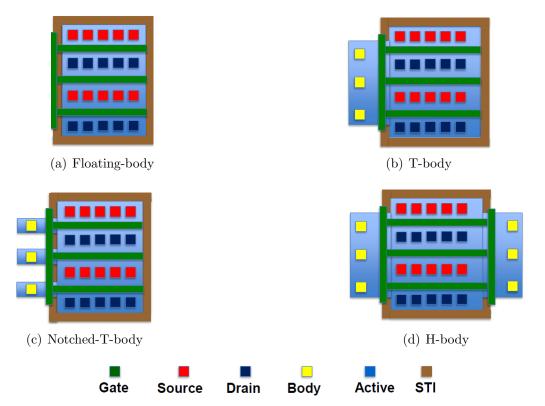

| 25 | Schematic layout of (a) Floating-body, (b) T-body, (c) Notched-T-body, and (d) H-body device.                                                                                                                                                                                                                                                                                                                                                              | 34 |

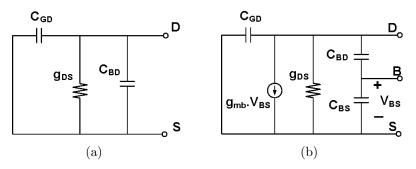

| 26 | Small-signal equivalent circuit of (a) BC and (b) FB device. $\ldots$ .                                                                                                                                                                     | 34 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

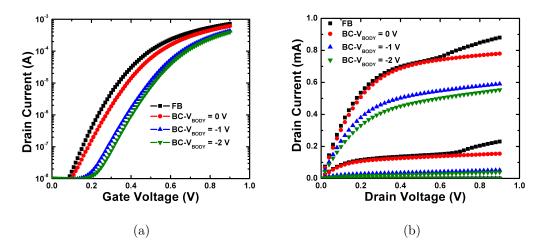

| 27 | (a) Drain current as a function of gate voltage of FB and BC device for varying body bias. (b) Drain current as a function of drain voltage of FB and BC device for varying body bias (Data on 180-nm CMOS-on-SOI technology (IBM 7RFSOI)). | 36 |

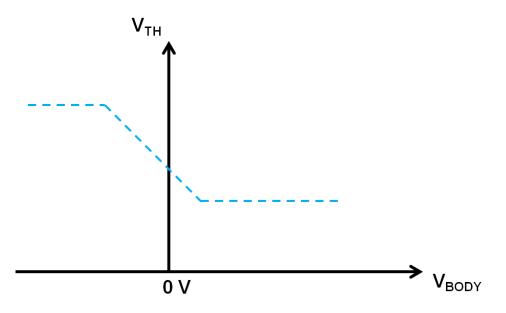

| 28 | Effect of body bias on a SOI MOSFET threshold voltage                                                                                                                                                                                       | 36 |

| 29 | Effect of body bias on a nFET hot-carrier reliability [50]                                                                                                                                                                                  | 37 |

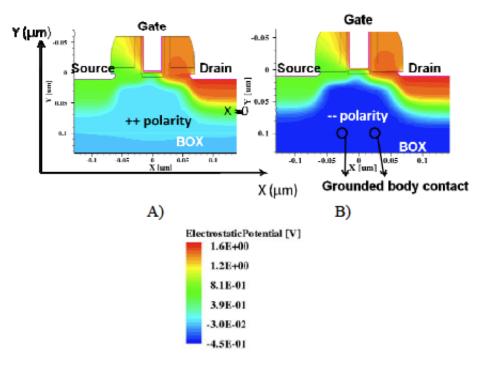

| 30 | Electrostatic potential of (a) FB and (b) BC device                                                                                                                                                                                         | 38 |

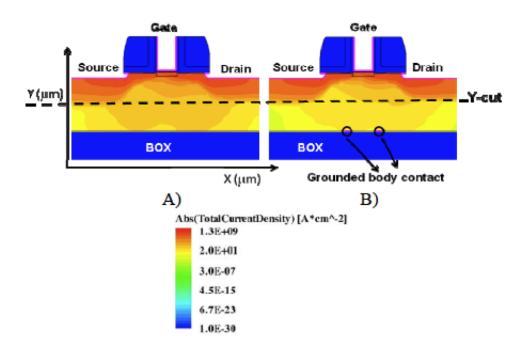

| 31 | Current density in the body-region of (a) FB and (b) BC device                                                                                                                                                                              | 38 |

| 32 | (a) Comparison of current density of FB and BC device in the body region. (b) Simulated $I_{DS} - V_{GS}$ characteristics of FB and BC device.                                                                                              | 39 |

| 33 | ARACOR X-ray radiation source.                                                                                                                                                                                                              | 40 |

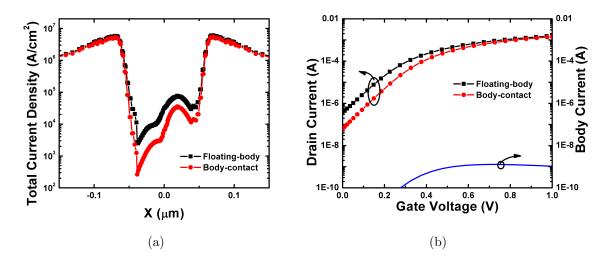

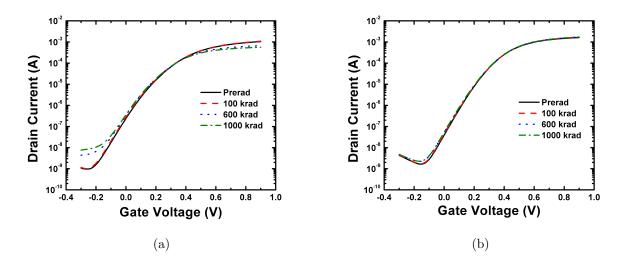

| 34 | (a) Drain current as a function of gate voltage of FB device for varying ionizing dose. (b) Drain current as a function of gate voltage of BC device for varying ionizing dose                                                              | 41 |

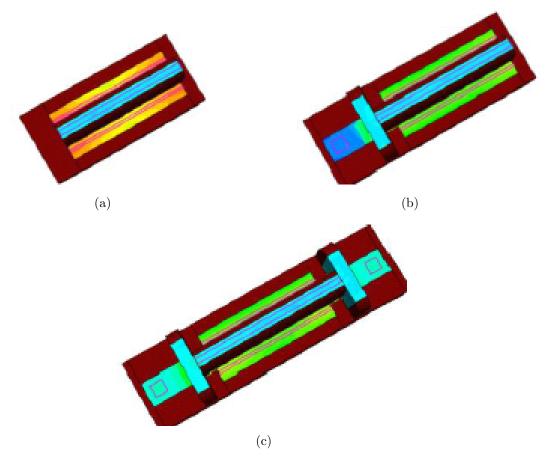

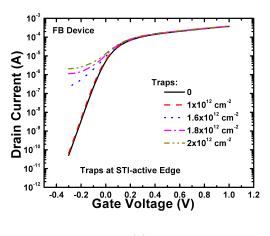

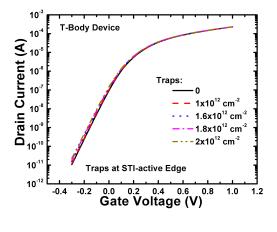

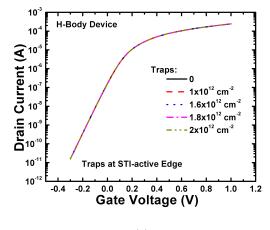

| 35 | 3D TCAD simulated electron current density for (a) FB device, (b) T-body device, and (c) H-body device.                                                                                                                                     | 41 |

| 36 | TCAD simulated drain current as a function of gate voltage of (a) FB device, (b) T-body device, and (c) H-body device for varying trap concentrations at the active-STI edge                                                                | 42 |

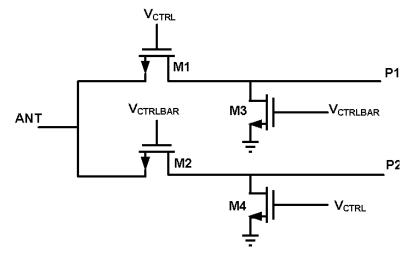

| 37 | Schematic of a SPDT switch.                                                                                                                                                                                                                 | 43 |

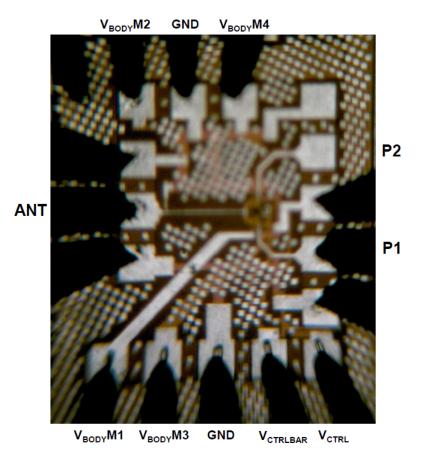

| 38 | Die photograph of the SPDT switch.                                                                                                                                                                                                          | 43 |

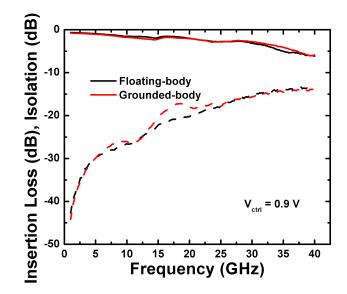

| 39 | Insertion loss and isolation as a function of frequency of a FB and BC switch with grounded body.                                                                                                                                           | 44 |

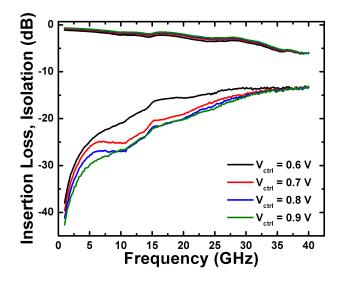

| 40 | Effect of gate bias on switch performance.                                                                                                                                                                                                  | 44 |

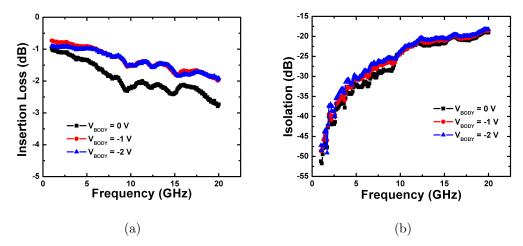

| 41 | (a) Effect of negative body bias on IL. (b) Effect of negative body bias on isolation.                                                                                                                                                      | 46 |

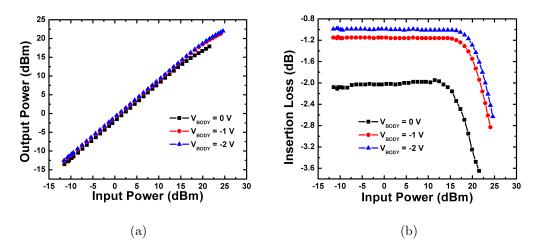

| 42 | (a) Output power as a function of input power of the switch for varying body bias. (b) Insertion loss as a function of input power of the switch for varying body bias.                                                                     | 46 |

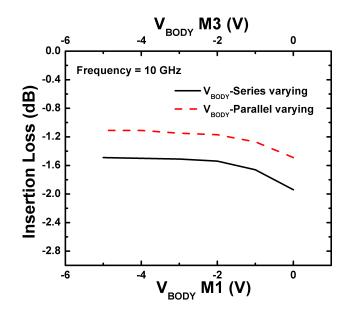

| 43 | Effect of body bias of series and shunt nFETs on switch performance.                                                                                                                                                                        | 47 |

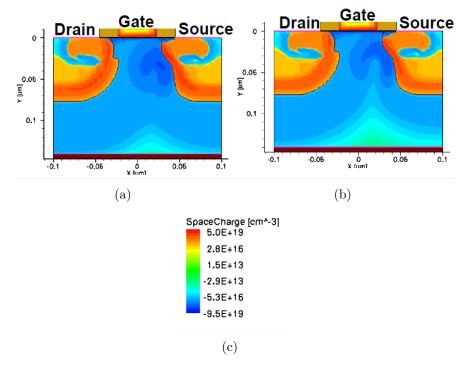

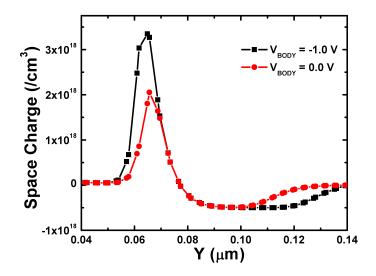

| 44 | (a) Space charge contour diagram of a nFET for $V_G = 1.0$ V, $V_D = 1.0$ V, $V_S = 0.0$ V, and $V_{BODY} = -1.0$ V. (b) Space charge contour diagram for a nFET of $V_G = 1.0$ V, $V_D = 1.0$ V, $V_S = 0.0$ V, and $V_{BODY} = 0.0$ V.    | 48 |

| 45 | Space charge at the source-body junction of the nFETs for negative and zero body bias.                                                                                                                                                      | 49 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

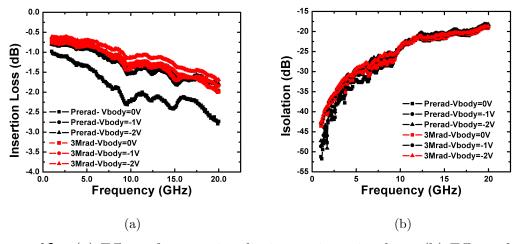

| 46 | (a) Effect of proton irradiation on insertion loss. (b) Effect of proton irradiation on isolation.                                                                                                                                          | 49 |

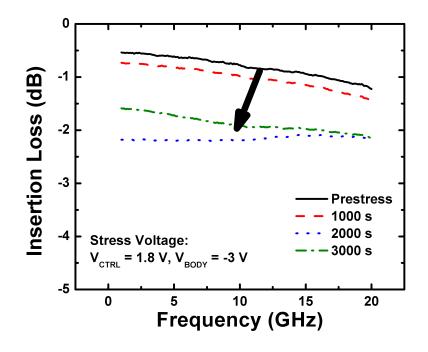

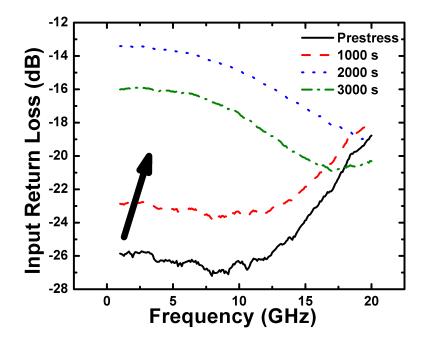

| 47 | (a) Effect of gate and body stress on insertion loss. (b) Effect of gate and body stress on input return loss (S11)                                                                                                                         | 50 |

| 48 | (a) Electric field in the channel region for varying body bias. (b) Impact ionization in the body region for varying body bias. (c) Electric field in the gate oxide region for varying body bias                                           | 51 |

| 49 | (a) TCAD simulated drain current and body current as a function of gate voltage for a 2 $\mu m$ channel length nFET. (b) TCAD simulated drain current and body current as a function of gate voltage for a 45-nm channel length nFET.       | 55 |

| 50 | (a) TCAD simulated impact ionization in the channel region for a 2 $\mu m$ channel length nFET. (b) TCAD simulated impact ionization in the channel region for a 45-nm channel length nFET                                                  | 56 |

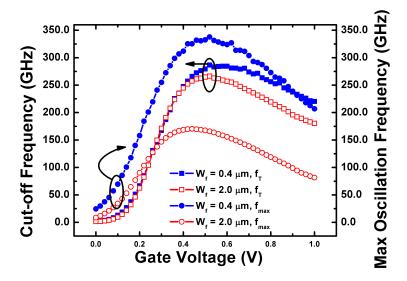

| 51 | Maximum oscillation frequency $(f_{MAX})$ and cut-off frequency $(f_T)$ as a function of gate voltage of the devices with varying finger width                                                                                              | 57 |

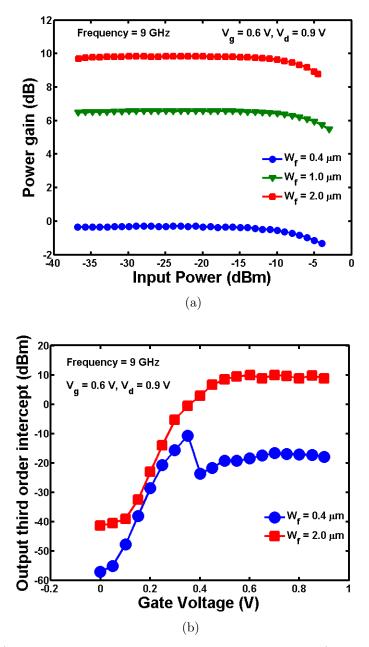

| 52 | (a) Power-gain as a function of input RF power (frequency = 9 GHz) of<br>the devices with varying finger width. (b) Output-third-order-intercept<br>point (OIP3) as a function of gate voltage of the devices with varying<br>finger width. | 59 |

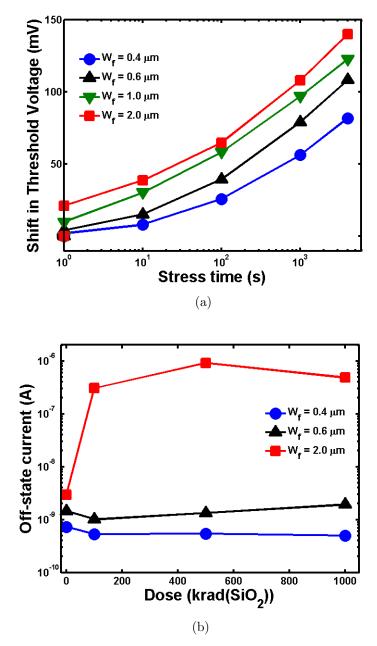

| 53 | (a) Shift in threshold voltage as a function of stress time of the nFETs with varying finger width. (b) Total-dose irradiation induced increase in off-state current of the nFETs with varying finger width                                 | 61 |

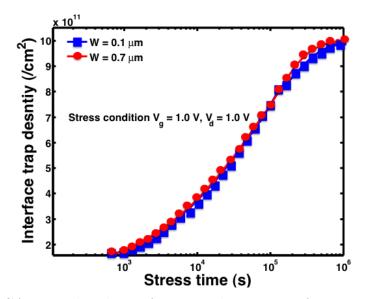

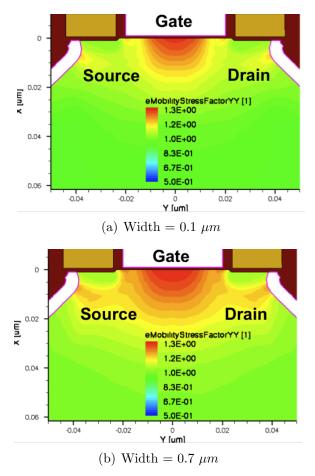

| 54 | TCAD simulated interface trap density as a function of stress time for device of width 0.1 $\mu m$ and 0.7 $\mu m$                                                                                                                          | 62 |

| 55 | TCAD simulated electron mobility enhancement factor along the channel direction for device of width (a) 0.1 $\mu m$ and (b) 0.7 $\mu m$                                                                                                     | 62 |

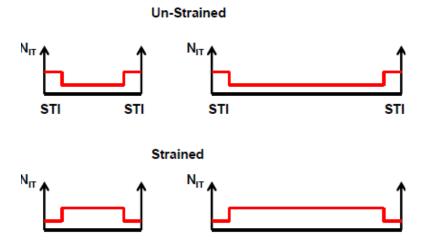

| 56 | Schematic diagram of enhanced trap formation along the STI edge for<br>un-strained MOSFET, and trap formation in the middle of channel for<br>strained MOSFET.                                                                              | 63 |

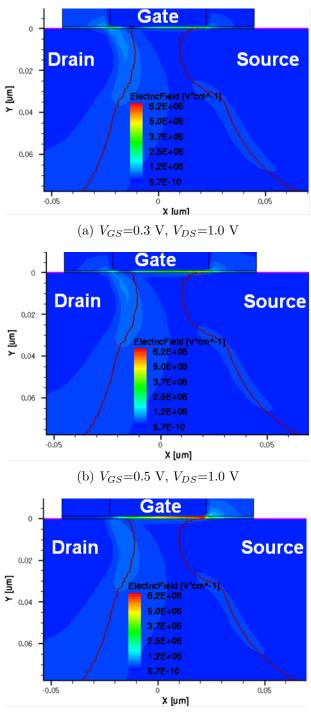

| 57 | TCAD simulated electric field lines of a nFET with varying gate voltage.                                                                                                                                                                    | 65 |

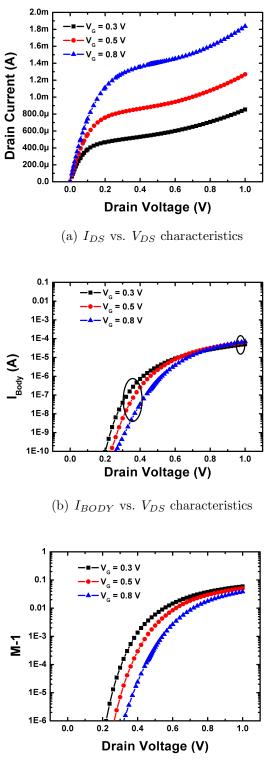

| 58 | TCAD simulated $I_{DS}$ vs. $V_{DS}$ , $I_{BODY}$ vs. $V_{DS}$ , $M - 1$ vs. $V_{DS}$ characteristics of a nFET with varying gate voltage.                                                                                                  | 66 |

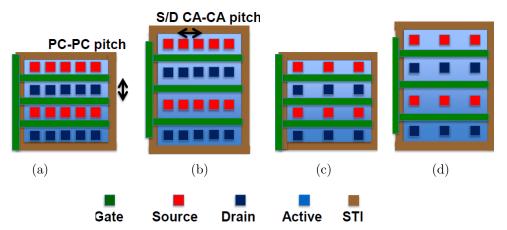

| 59 | Layout of the floating-body devices. Device with (a) tight gate-finger<br>to gate-finger and tight source/drain (S/D) metal contact spacing, (b)<br>loose gate-finger to gate-finger and tight S/D metal contact spacing,<br>(c) tight gate-finger to gate-finger and loose S/D metal contact spacing,<br>and (d) loose gate-finger to gate-finger and loose S/D metal contact<br>spacing. | 69 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 60 | (a) Cut-off frequency $(f_T)$ as a function of gate voltage of the devices<br>with varying contact spacing. (b) Maximum oscillation frequency<br>$(f_{MAX})$ as a function of gate voltage of the devices with varying contact<br>spacing.                                                                                                                                                 | 71 |

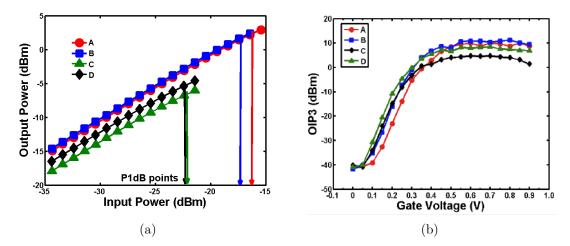

| 61 | (a) Output-power as a function of input-power of the nFETs with varying contact spacing. (b) Output-third-order-intercept point (OIP3) of nFETs with varying contact spacing.                                                                                                                                                                                                              | 72 |

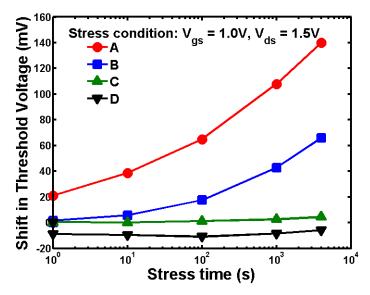

| 62 | Threshold voltage shift of nFETs with the same dimensions (L = 45 nm, $W_f = 2 \ \mu m$ ), but varying contact spacing                                                                                                                                                                                                                                                                     | 73 |

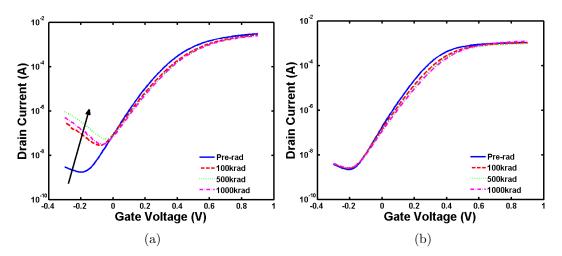

| 63 | (a) Transfer characteristics of device A with tight S/D contact and gate-finger to gate-finger spacing. (b) Transfer characteristics of device C with loose S/D contact and gate-finger to gate-finger spacing                                                                                                                                                                             | 73 |

| 64 | Off-state drain current as a function of total irradiation dose of the four devices with varying contact spacing.                                                                                                                                                                                                                                                                          | 74 |

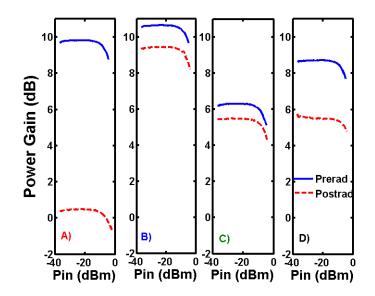

| 65 | Power-gain as a function of input-power of the devices with varying contact spacing (pre- and post-irradiation)                                                                                                                                                                                                                                                                            | 74 |

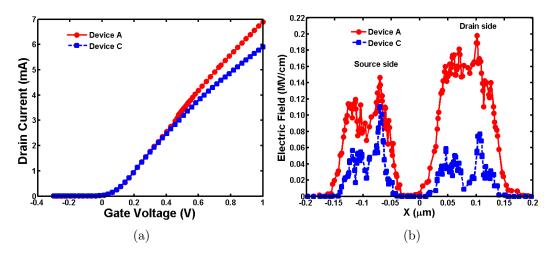

| 66 | (a) TCAD simulated $I_{DS}$ - $V_{GS}$ characteristics of the devices with varying contact spacing. (b) Simulated electric-field along the channel region of the devices with varying contact spacing                                                                                                                                                                                      | 75 |

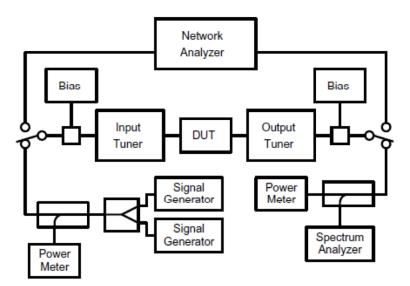

| 67 | Block diagram of the load-pull measurement setup used for RF measurements                                                                                                                                                                                                                                                                                                                  | 76 |

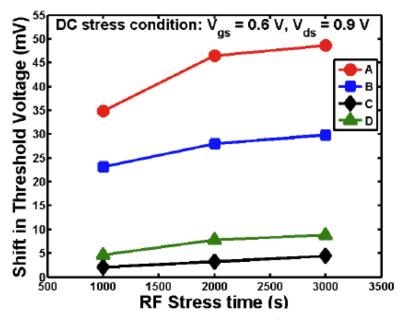

| 68 | Shift in threshold voltage with RF stress (at $V_{GS} = 0.6$ V, $V_{DS} = 0.9$ V) of nFETs with loose and tight S/D contact spacing (Frequency = 9 GHz, $P_{in} = 0$ dBm).                                                                                                                                                                                                                 | 76 |

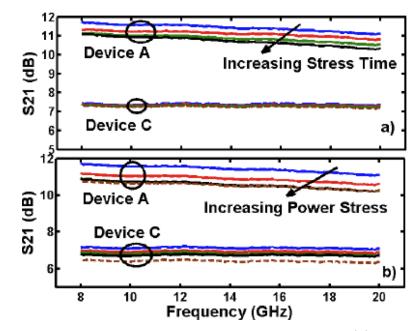

| 69 | Comparison of S21 degradation with increasing (a) RF stress time for 1000 s, 2000 s, and 3000 s stress (for constant power = 0 dBm) and (b) input RF power of $+5$ , $+6$ , $+7$ dBm (for constant stress time = 100 s) of nFETs (at peak $f_T$ bias).                                                                                                                                     | 78 |

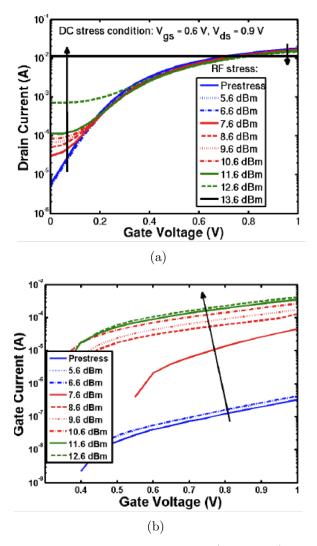

| 70 | (a) Transfer characteristics of nFET (device C) with varying RF power stress ( $V_{GS} = 0.6 \text{ V}, V_{DS} = 0.9 \text{ V}$ ). Stressed for 100 s at each power step (frequency = 9 GHz). (b) Gate current characteristics of nFET (device C) with varying RF power stress ( $V_{GS} = 0.6 \text{ V}, V_{DS} = 0.9 \text{ V}$ )                                                        | 80 |

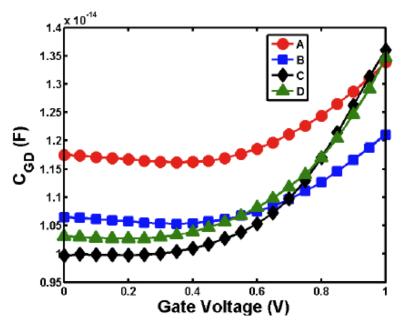

| 71 | Gate-to-drain capacitance $(C_{GD})$ as a function of gate voltage of nFETs with varying contact spacing.                                                                                                                                                                                                                                                                                                                                                                                                                                         | 81 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

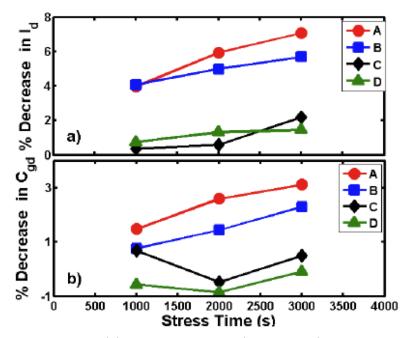

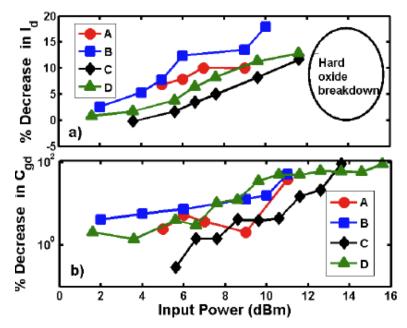

| 72 | Comparison of (a) $I_{DS}$ degradation (percentage) as a function of RF stress time (at peak $f_T$ bias) (b) $C_{GD}$ degradation (percentage) as a function of RF stress time of nFETs (at peak $f_T$ bias)                                                                                                                                                                                                                                                                                                                                      | 81 |

| 73 | Comparison of (a) $I_{DS}$ degradation (percentage) as a function of RF input-power (b) $C_{GD}$ degradation (percentage) as a function of RF input-power of nFETs (at peak $f_T$ bias).                                                                                                                                                                                                                                                                                                                                                          | 82 |

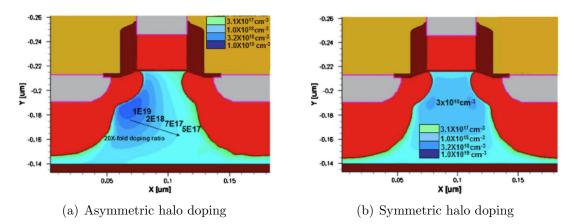

| 74 | (a) TCAD simulations showing the doping concentration for the asymmetric device. Asymmetric devices have a large lateral gradient doping profile with a source-side halo pocket of $1 \times 10^{19} cm^{-3}$ concentration and a low-doped drain channel doping of $5 \times 10^{17} cm^{-3}$ (a change of 20-fold). (b) TCAD simulations showing the active doping concentration for the symmetric control device. The symmetric control devices have a uniform profile with a channel doping concentration of $3 \times 10^{18} cm^{-3}$ [25]. | 83 |

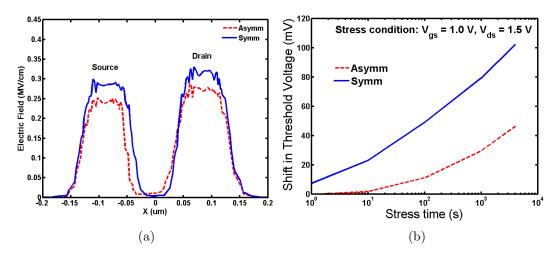

| 75 | (a) Electric-field in the channel region of asymmetric and symmetric halo doping nFETs. (b) Threshold voltage shifts of asymmetric and symmetric halo doping nFETs with the same dimensions (L = 45 nm, $W_f = 2 \ \mu m$ ).                                                                                                                                                                                                                                                                                                                      | 83 |

| 76 | Total-dose irradiation induced increase in off-state current of nFETs with asymmetric halo doping (L = 45 nm, $W_f = 2 \ \mu m$ )                                                                                                                                                                                                                                                                                                                                                                                                                 | 84 |

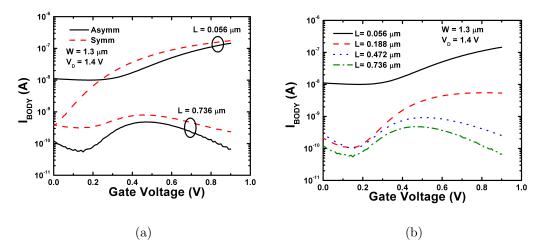

| 77 | (a) Measured body current as a function of gate voltage of nFETs with asymmetric halo doping and symmetric halo doping. (b) Measured body current as a function of gate voltage of nFETs with asymmetric halo doping for varying channel length                                                                                                                                                                                                                                                                                                   | 85 |

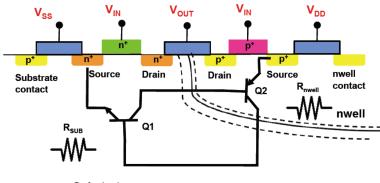

| 78 | Schematic of the parasitic transistors present in a CMOS inverter circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90 |

| 79 | Latchup process flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90 |

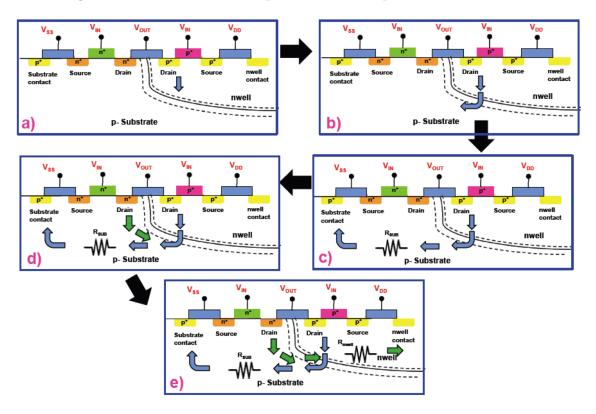

| 80 | SEM image of a metal line damaged from the large current generated<br>by a latchup event [74]                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 91 |

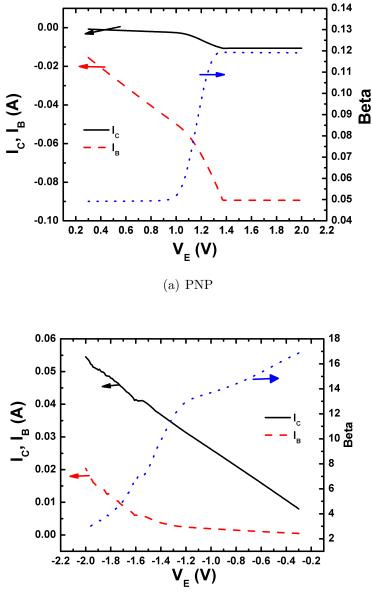

| 81 | Gummel characteristics of (a) parasitic PNP and (b) parasitic NPN transistor present in a p-n-p-n doping structure.                                                                                                                                                                                                                                                                                                                                                                                                                               | 92 |

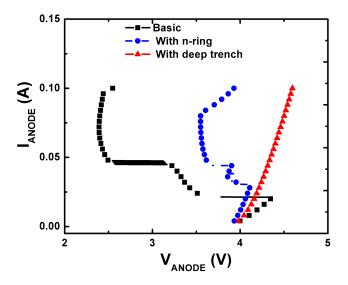

| 82 | Latchup characteristics of a p-n-p-n structure without any protection (Basic), with a N-ring (NS), and with a deep-trench (DT).                                                                                                                                                                                                                                                                                                                                                                                                                   | 93 |

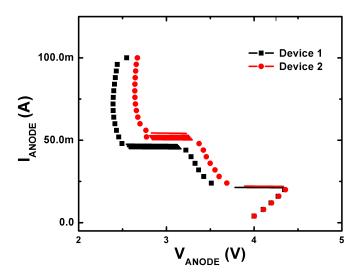

| 83 | Latchup characteristics of a p-n-p-n structure without any protection (Basic) and with variation in anode-to-cathode spacing. Device 2 has a larger anode-to-cathode spacing than device 1                                                                                                                                                                                                                                                                                                                                                        | 94 |

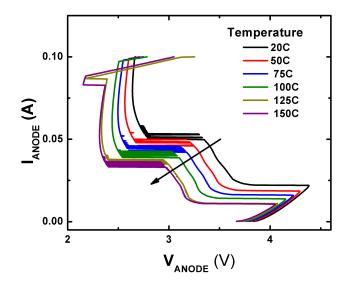

| 84 | Effect of temperature on the latchup characteristics of a basic p-n-p-n structure.                                                                                                                                        | 95  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

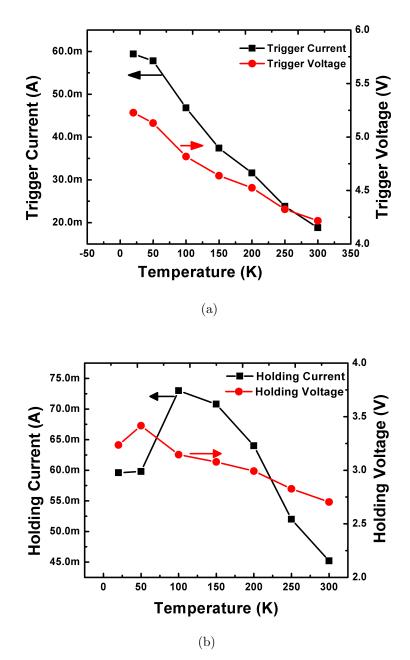

| 85 | (a) Trigger-current and trigger-voltage of a basic p-n-p-n structure as a function of temperature. (b) Holding-current and holding-voltage of a basic p-n-p-n structure as a function of temperature.                     | 96  |

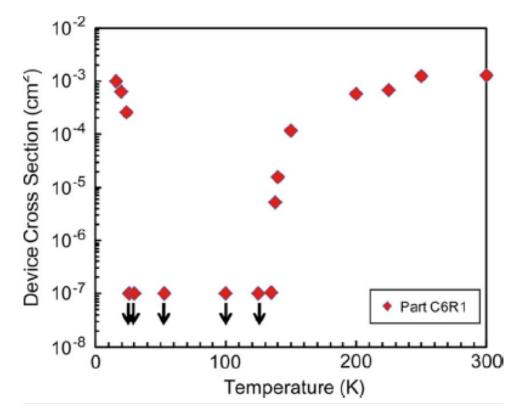

| 86 | Device cross sections for hard SEL events versus temperature. All data was measured at 60° incidence using 15 MeV/u Kr with $LET_{eff} = 64.4$ and $R_p = 43$ . The downward arrows indicate limiting cross sections [5]. | 97  |

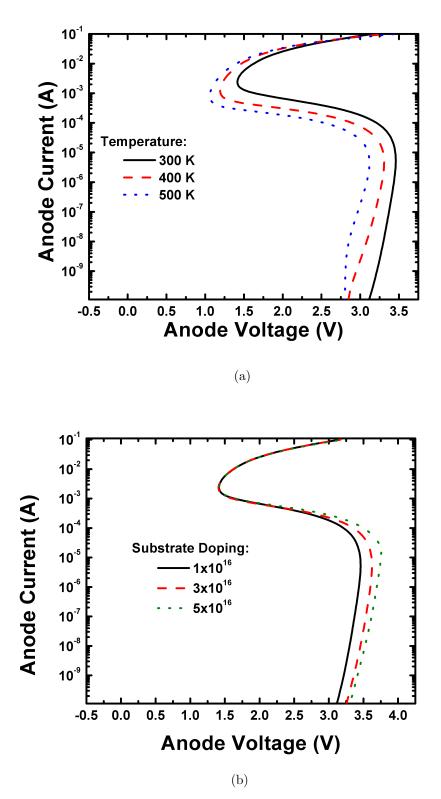

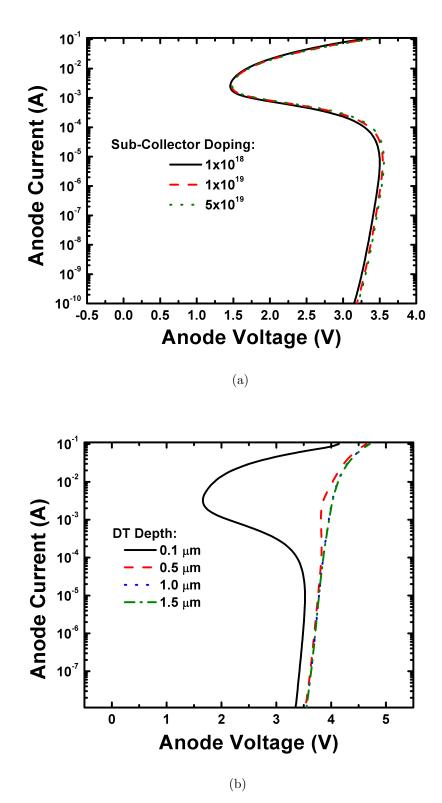

| 87 | Anode current as a function of anode voltage for varying (a) temperature and (b) substrate doping.                                                                                                                        | 99  |

| 88 | Anode current as a function of anode voltage for varying (a) sub-collector doping and (b) deep trench (DT) depth.                                                                                                         | 100 |

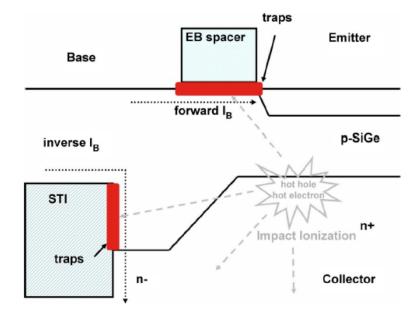

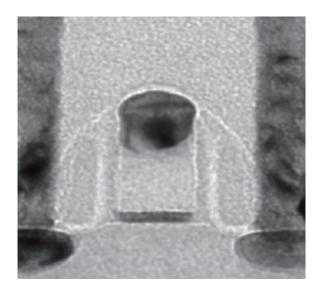

| 89 | Cross section of a SiGe HBT showing the interface trap formation at<br>the EB-spacer and STI interface with silicon during a mixed-mode<br>stress condition [78]                                                          | 103 |

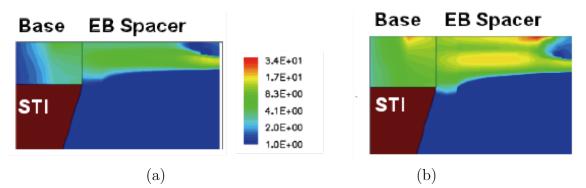

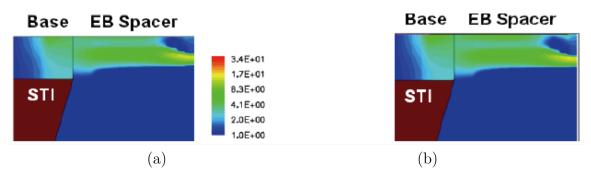

| 90 | Majority-carrier current density (a) before stress (b) after stress, for traps only at the EB-spacer.                                                                                                                     | 106 |

| 91 | Majority-carrier current density (a) before stress (b) after stress, for traps only at the STI edge                                                                                                                       | 106 |

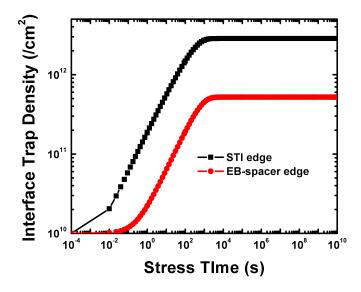

| 92 | Interface trap density as a function of stress time for STI and EB-spacer oxides                                                                                                                                          | 107 |

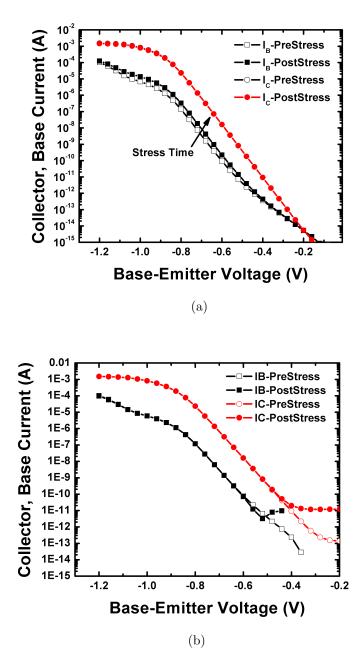

| 93 | (a) Collector- and base- current as a function of base-emitter voltage for traps at EB-spacer oxides. (b) Collector- and base- current as a function of base-emitter voltage for traps at STI oxides                      | 108 |

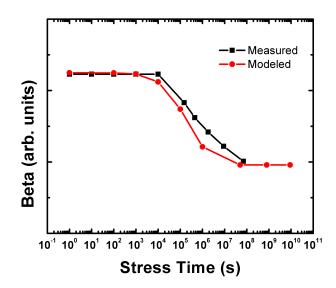

| 94 | Measured and modeled DC current gain (Beta) as a function of stress time                                                                                                                                                  | 109 |

| 95 | TEM cross-section of a 32-nm CMOS device (after [86])                                                                                                                                                                     | 112 |

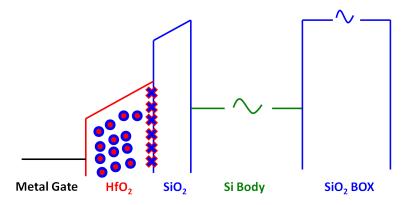

| 96 | Schematic energy band diagram of the gate-stack of a 32-nm SOI CMOS device.                                                                                                                                               | 112 |

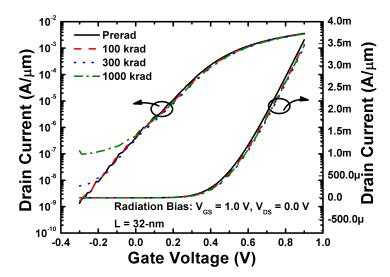

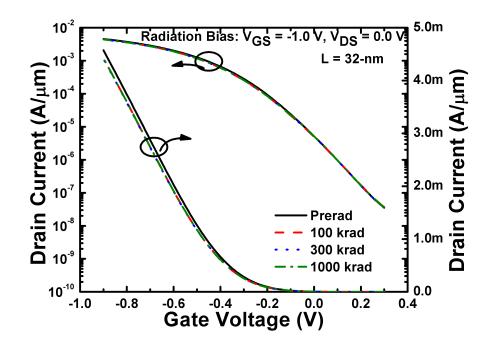

| 97 | Transfer characteristics of the nFET as a function of radiation dose (L = $32 \text{ nm}$ , W = $0.325 \mu m$ )                                                                                                           | 113 |

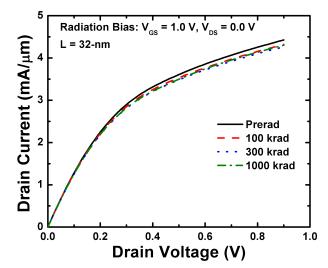

| 98 | Output characteristics of the nFET as a function of radiation dose (L = $32 \text{ nm}$ , W = $0.325 \mu m$ )                                                                                                             | 113 |

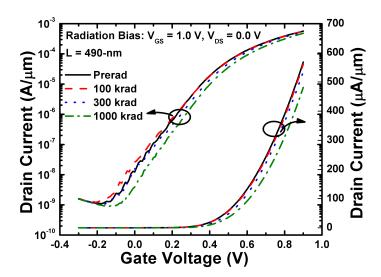

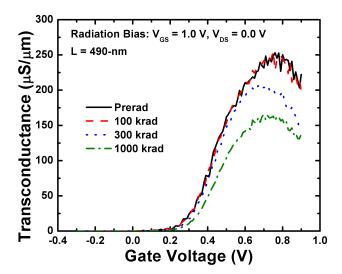

| 99 | Transfer characteristics of the nFET as a function of radiation dose (L = 490 nm, W = 0.325 $\mu m$ ).                                                                                                                    | 115 |

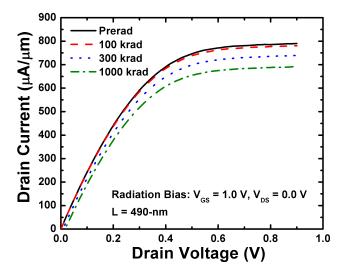

| 100 | Output characteristics of the nFET as a function of radiation dose (L = 490 nm, W = 0.325 $\mu m$ ).                                                                                                                                                      | 115   |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 101 | Transconductance characteristics of the nFET as a function of radiation dose (L = 490 nm, W = 0.325 $\mu m$ )                                                                                                                                             | 116   |

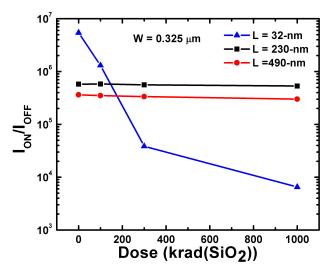

| 102 | On-Off current ratio of the nFETs with varying channel length as a function of radiation dose.                                                                                                                                                            | 116   |

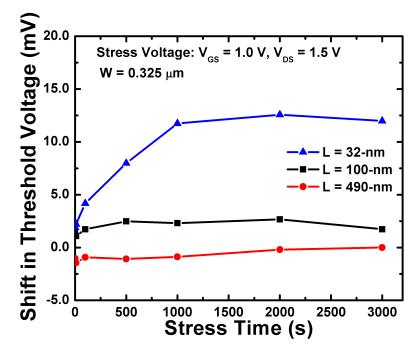

| 103 | Hot-carrier degradation induced shift in threshold voltage as a function of stress time for transistors of different channel length in the 32-nm technology.                                                                                              | 117   |

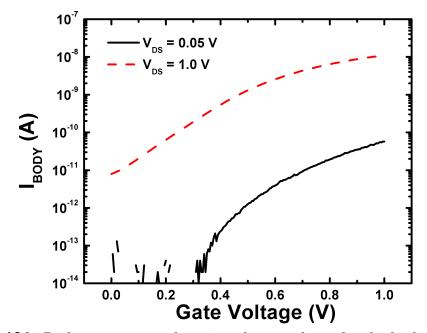

| 104 | Body current as a function of gate voltage for the body-contact device with varying drain voltage.                                                                                                                                                        | 117   |

| 105 | Transfer characteristics of the pFET as a function of radiation dose (L= 32 nm, W = 0.425 $\mu m$ )                                                                                                                                                       | 118   |

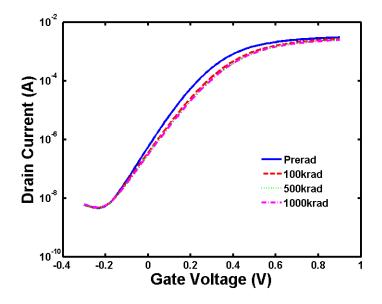

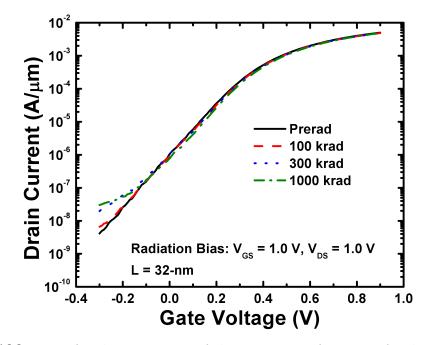

| 106 | Transfer characteristics of the nFET as a function of radiation dose (L= 32 nm, W = 0.325 $\mu m$ )                                                                                                                                                       | 118   |

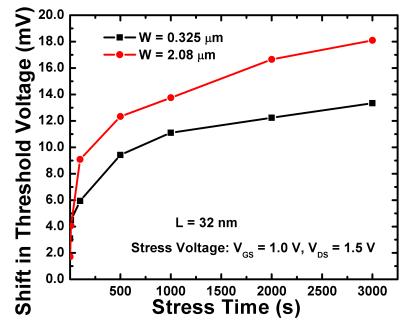

| 107 | Shift in threshold voltage as a function of hot-carrier stress time for the nFETs with varying device width                                                                                                                                               | 119   |

| 108 | Shift in threshold voltage as a function of hot-carrier stress time for the floating-body (FB) and body-contacted (BC) nFETs                                                                                                                              | 119   |

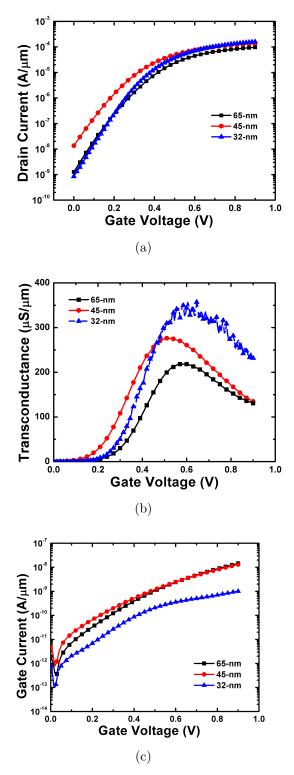

| 109 | Measured (a) drain current as a function of gate voltage, (b) transcon-<br>ductance as a function of gate voltage, and (c) gate current as a function<br>of gate voltage for the smallest channel length devices from 65-, 45-<br>and 32- nm technologies | 122   |

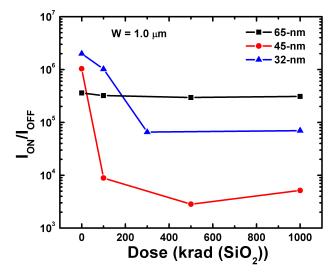

| 110 | On-Off current ratio as a function of radiation dose for the three technology nFETs                                                                                                                                                                       | 123   |

| 111 | Shift in threshold voltage as a function of hot-carrier stress time for the three technology nFETs                                                                                                                                                        | 123   |

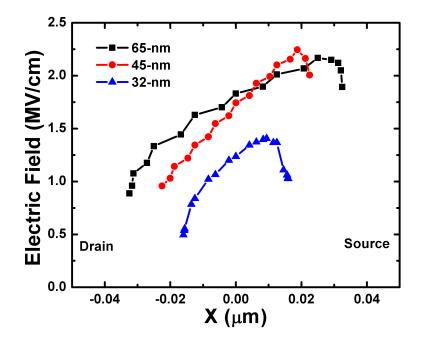

| 112 | Electric field in the gate oxide for the three technology nFETs                                                                                                                                                                                           | 124   |

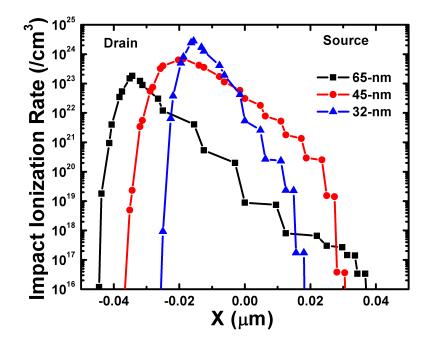

| 113 | Impact ionization in the channel region for the three technology nFETs                                                                                                                                                                                    | . 125 |

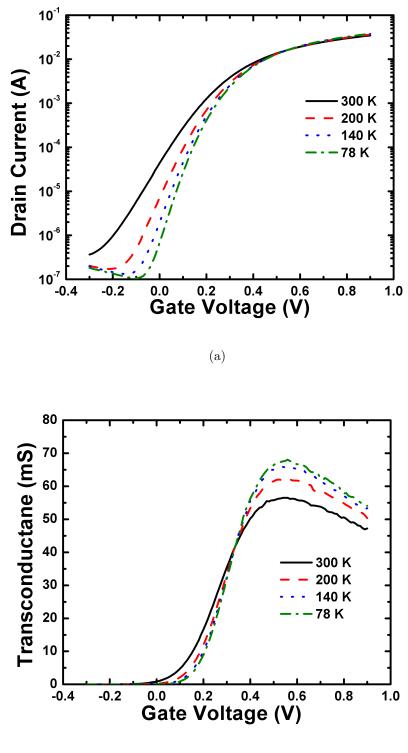

| 114 | (a) Drain current as a function of gate voltage of a 45-nm floating-body<br>SOI CMOS device for varying temperature. (b) Transconductance as a<br>function of gate voltage of a 45-nm floating-body SOI CMOS device<br>for varying temperature            | 128   |

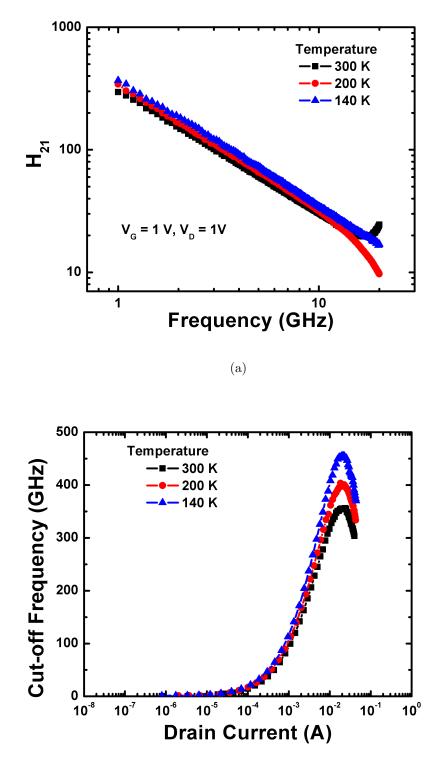

| 115 | (a) AC Current gain (H21) as a function of frequency of a 45-nm floating-<br>body SOI CMOS device at 300 K and 80 K. (b) Cut-off frequency as a<br>function of gate voltage of a 45-nm floating-body SOI CMOS device at<br>300 K and 80 K.                                                                 | 129 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

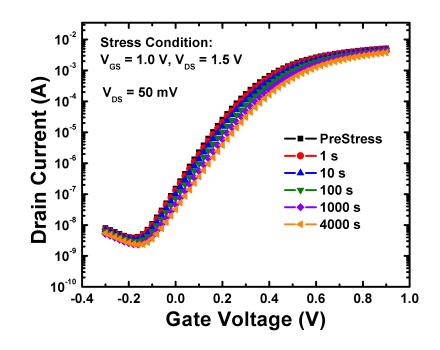

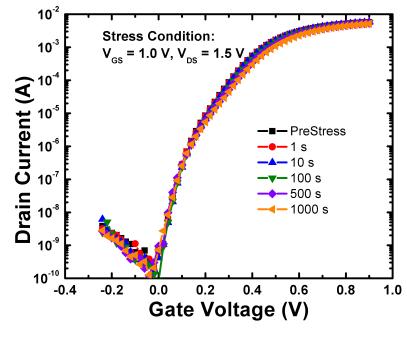

| 116 | (a) Transfer characteristics of a 45-nm floating-body SOI CMOS device<br>for increasing stress time (at $V_{GS}=1.0$ V and $V_{DS}=1.5$ V) at 300 K. (b)<br>Transfer characteristics of a 45-nm floating-body SOI CMOS device for<br>increasing stress time (at $V_{GS}=1.0$ V and $V_{DS}=1.5$ V) at 80 K | 130 |

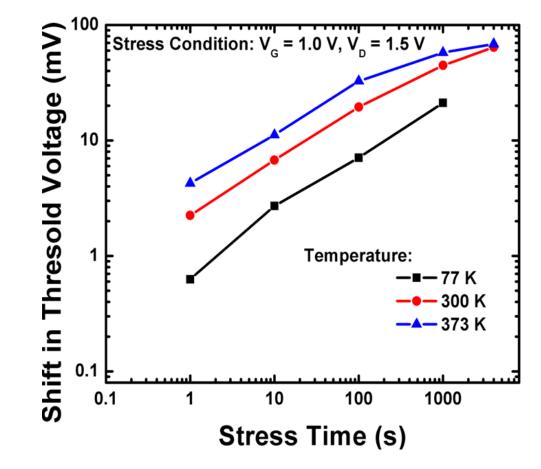

| 117 | Shift in threshold voltage as a function of stress time of a 45-nm floating-body SOI nFET for varying temperature                                                                                                                                                                                          | 131 |

| 118 | Different phenomenon studied in this dissertation in sub-100 nm CMOS-<br>on-SOI technologies, and their impact on performance and reliability<br>of MOSFETs                                                                                                                                                | 134 |

## SUMMARY

The objective of this research is to develop an understanding of the tradeoffs between performance and reliability in sub 100-nm silicon-on-insulator (SOI) CMOS technologies. Such trade-offs can be used to demonstrate high performance reliable circuits in scaled technologies. Several CMOS reliability concerns such as hot-carrier stress, ionizing irradiation damage, RF stress, temperature effects, and single-event effects are studied. These reliability mechanisms can cause temporary or permanent damage to the semiconductor device and to the circuits using them. Several improvements are made to the device layout and process to achieve optimum performance. Parasitics are shown to play a dominant role in the performance and reliability of sub 100-nm devices. Various techniques are suggested to reduce these parasitics, such as the use of the following: a) optimum device-width, b) optimum gate-finger to gate-finger spacing, c) optimum source/drain metal contact spacing, and d) floating-body/body-contact. The major contributions from this research are summarized as follows:

Role of floating-body effects on the performance and reliability of sub 100-nm CMOS-on-SOI technologies is investigated for the first time [1], [2]. It is demonstrated through experimental data and TCAD simulations that floating-body devices have improved RF performance but degraded reliability compared to body-contacted devices.

Floating-body effects in a cascode core is studied. Cascode cores are demonstrated to achieve much larger reliability lifetimes than a single device. A variety of cascode topologies are studied to achieve the trade-offs between performance and reliability for high-power applications [2].

3) The use of body-contact to modulate the performance of devices and single-poledouble-throw (SPDT) switches is studied. The SPDT switch performance is shown to improve with a negative body-bias.

4) The impact of device width on the RF performance and reliability is studied. Larger width devices are shown to have greater degradation, posing challenging questions for RF design in strained-Si technologies [3].

5) A novel study showing the effect of source/drain metal contact spacing and gatefinger to gate-finger spacing on the device RF performance is carried out. Further, the impact of above on the hot-carrier, RF stress, and total-dose irradiation tolerance is studied [3], [4].

6) Latchup phenomenon in CMOS is shown to be possible at cryogenic temperatures (below 50 K), and its consequences are discussed [5].

7) A time-dependent device degradation model has been developed in technology computer aided design (TCAD) to model reliability in CMOS and SiGe devices.

8) The total-dose irradiation tolerance and hot-carrier reliability of 32-nm CMOSon-SOI technology is reported for the first time. The impact of  $HfO_2$  based gate dielectric on the performance and reliability is studied [6].

9) The impact of technology scaling from 65-nm to 32-nm on the performance and reliability of CMOS technologies is studied [6].

10) Cryogenic performance and reliability of 45-nm nFETs is investigated. The RF performance improves significantly at 77 K. The hot-carrier device reliability is shown to improve at low temperatures in short-channel CMOS technologies.

## CHAPTER I

## INTRODUCTION

## 1.1 Origin and History of the Problem

CMOS-based radio-frequency (RF) and analog systems have made rapid inroads into the analog/wireless market in the last decade [7]-[9]. The digital-driven CMOS scaling into the sub 100-nm range has produced transistors with competitive RF performance characteristics ( $f_T$ ,  $f_{MAX}$ , linearity, power-gain, noise, etc.)(see Figure 1) [10]. Today, a lot of the CMOS-based commercial analog/RF circuits and systems are based on the 180-nm or 130-nm technologies. This is because of better device models, tolerable process-variation, and lower cost of these matured technologies. However, many digital/memory products have come out in the market with short-channel CMOS technologies. For example, Apple iPad 2 and iPhone 4S use 45-nm CMOS A5 microprocessor [11]. Intel is building microprocessors at 22-nm technology node with three-dimensional transistors [12]. Figure 2 shows the advantages of scaling in digital circuits with decreasing SRAM cell area and increasing SRAM bit density. A smaller form-factor of the integrated-circuit and improved functionality can be achieved at highly scaled technology nodes.

Clearly, deep sub-micron CMOS technologies are essential for building mixed-signal systems. However, using these short-channel technologies in analog/RF circuits is a challenge because of several reasons. With such scaling, the short-channel effects can degrade circuit performance. Silicon-on-insulator (SOI) technology is widely adopted to help mitigate these short-channel effects [13]-[14]. Decreasing device dimensions at similar power supply levels has resulted in transistors with increasing intrinsic electric-fields and hence increasing reliability concerns. In general, there is expected to

**Figure 1:** Cut-off frequency  $(f_T)$  as a function of drain current for the nFETs from different sub 100-nm RF-CMOS technologies [10].

**Figure 2:** SRAM bit cell area and bit density as a function of CMOS technology node [10].

be some degradation in device parameters under extreme operating conditions, such as large voltage swings, large RF stress, etc. [15]-[17]. This can lead to degradation in circuit and system-level performance [18]-[19]. In sub 100-nm CMOS technologies, the device parasitics have a large impact on the performance and reliability of the device itself and to the circuits using them. Thus the knowledge of the trade-offs between performance and reliability are essential for the design of high performance and reliable circuits, and will be the focus of this work. Ideally, such trade-offs should be included in the transistor compact models for designers to simulate circuit reliability at design stage. However, building such models can be a challenge because of their high cost and complexity. Thus, the onus is upon the sub 100-nm CMOS circuit designers to understand and apply these trade-offs to achieve the design specifications, and at the same time, meet the ten-year product lifetime requirement [20]. Scaling, for enhanced performance and cost reduction reasons, has pushed existing CMOS materials much closer to their intrinsic reliability limits. Future robust designs will require a strong team effort whereby the design engineer must clearly understand the process variability and its impact on reliability. This strong team effort, between design and process, will become critically important as the industry is seeking to replace the very materials that has made the industry so successful: Si substrates,  $SiO_2$ gate-dielectric, Aluminum-based metallization and  $SiO_2$  interconnect-dielectrics [21]. These increasing number of variables in process technology has resulted in increasing design rules with technology scaling (Figure 3).

**Figure 3:** Operation count and the design rule count of a single integrated circuit as a function of technology scaling [20].

## 1.2 Sub 100-nm CMOS Technologies

Until the 130-nm technology node standard CMOS scaling rules had been followed [22]. However, from the 90-nm technology node, it was realized that scaling alone cannot meet the technology performance requirements, and novel ideas like strained-silicon, high-k dielectrics, and SOI have been implemented.

### 1.2.1 Strained-Silicon CMOS

Strain (deformation of a material as a result of applied stress) in the Si crystal lattice improves the carrier mobility, resulting in improved device performance [23]. Stress can be introduced with the formation of the silicon-nitride (SiN) cap over the polysilicon gate. Depending on how the SiN is deposited, this stress may be either tensile or compressive. Silicon germanium (SiGe) can be introduced into the source/drain for PMOS to create compressive stress in the channel region. The germanium atom is larger than the silicon atom, and when it replaces a silicon atom, the crystal lattice is strained. For a device mobility improvement, this strain must be present in the silicon where the FET channel is formed. The modifications to a MOSFET structure over four technology generations from 130-nm to 32-nm are shown in Figure 4. The major changes to a MOSFET structure have been the addition of strain-enhancing layers on top of the gate electrode (for NMOS), SiGe source/drain (for PMOS), and the replacement of  $SiO_2$  gate-dielectric with high-k gate-dielectrics (for both NMOS and PMOS).

## 1.2.2 Silicon-on-Insulator Technology

A thin-film silicon-on-insulator (SOI) technology is advantageous because of a number of factors. An SOI technology provides a simple device isolation. SOI MOSFETs have charge coupling between the front and back gates [24]. The performance advantage of SOI over bulk Si is caused by the elimination of area junction capacitance, the lack of a reverse body-effect in stacked circuits, and because the SOI body is slightly

**Figure 4:** Evolution of CMOS transistor architecture in the last decade, from a nonstrained oxide/poly gate structure to a high-k/metal-gate strained-silicon transistor at the 32-nm node [10].

forward-biased under most operating conditions. No p-n-p-n path exists in a SOI structure and hence latchup is eliminated. With SOI, the floating-body voltage is a function of applied source/drain (S/D) voltages and prior operation. This can be used to reduce the switching time, and the voltage drop across pass gate and source follower circuits. The reduction of the S/D capacitance improves the technologies power performance. SOI technologies eliminate the risk caused by single-event effects (SEE). The coupling between digital and analog circuits in a SOI platform is naturally eliminated. The technologies used in this work (IBM 65-nm, 45-nm, and 32-nm SOI) have partially-depleted FETs [25]. In the partially-depleted devices, the source/drain doping does not extend all the way to the BOX layer permitting varying threshold voltage. Another feature of SOI MOSFETs is that the local substrate ('body') of the device floats electrically, and therefore, the substrate-source bias voltage  $(V_{BS})$ is not fixed. As  $V_{BS}$  changes, the device threshold voltage  $(V_{TH})$  will change. This instability in  $V_{TH}$  is what has made SOI device design quite challenging. There are some drawbacks in partially-depleted devices, namely, History- and Kink- effects that need to be considered. History-effect causes a delay variation in circuits as a result of dynamic switching conditions ensuing from previously applied voltages [13]. These delay variations can be quite large and some application may not be tolerant of them. Body-contacted FETs can be used to minimize this effect in SOI. Silicon-on-insulator (SOI) technology is widely adopted to mitigate drain-induced-barrier-lowering (DIBL) and to suppress fringing fields and charge sharing effects that have become dominant in short-channel CMOS technologies [13]-[14]. SOI technology has been used in 65-nm, 45-nm, and 32-nm CMOS technologies [26], [27]. SOI also offers additional design advantages over traditional bulk CMOS technologies. These advantages include a significant reduction in cross-talk between on-chip RF and digital circuitry, and the ability to integrate high quality, passive elements on-chip (thanks to larger substrate resistivity).

Therefore, SOI technology has an advantage in performance over bulk technologies (at an added cost of course!). However, the different reliability mechanisms of SOI technologies are still an active area of research.

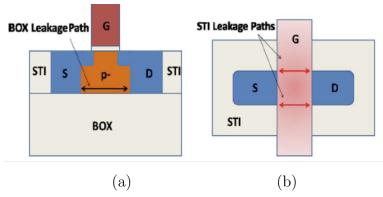

#### 1.2.3 Digital-CMOS vs. RF-CMOS

Digital technologies are optimized for digital circuits and RF technologies are optimized for analog/RF circuits. Most of the digital CMOS circuits require narrow width devices (W < ~ 1  $\mu$ m), whereas RF-CMOS circuits require much larger width devices (W ~ 100  $\mu$ m). Large width is required in RF devices to get sufficient current and gain from the device. Because of the large widths, the devices are laid-out in multiple gate-finger configuration (see Figure 5).

The gate resistance of a MOSFET is given by (Eqn. 1):

$$R_g = \frac{R_{poly}W_F}{3n^2L},\tag{1}$$

where  $R_{poly}$  is the poly-silicon gate sheet resistance,  $W_F$  is the gate-finger width, n is the number of gate contacts, and L is the channel length. Therefore,  $W_F$  is made smaller, and n is made larger to minimize  $R_g$ . A smaller  $R_g$  results in smaller noise. Device width has a significant effect on the performance and reliability of a CMOS

**Figure 5:** Top-view layout comparison of (a) single-finger digital nFET and (b) multi-finger RF nFET.

device (as will be shown later). Thus, a digital-CMOS device behaves very different from a RF-CMOS device. The side-view layout of FETs connected in a multi-finger configuration is shown in Figure 6.

Figure 6: Side-view layout of a multi-finger RF nFET.

## 1.2.4 BEOL in Short-Channel CMOS Technologies

Back-End-of-Line (BEOL) in semiconductor technology refers to the transmission lines and passives (inductors, capacitors, resistors, and transformers). In a bulk CMOS technology, the silicon wafer doping is relatively high to prevent latchup. A high wafer-doping results in poor quality of transmission lines and passives on silicon. With technology scaling the BEOL has also scaled down (Figure 7).

The metal line thicknesses and the spacing between two metal layers have decreased.

0.13 um 6 layers B2 nm 8 layers

**Figure 7:** SEM images of 130-nm six layer metal stack vs. 32-nm eight layer metal stack [10].

This has resulted in further lower quality factors of transmission lines and passives. SOI technologies have improved passive quality factors because of larger resistivity of the substrate. BEOL metal layers can affect a transistor performance though parasitics.

## 1.3 Reliability Mechanisms in a CMOS Technology

The following are the major reliability concerns for any CMOS technology:

## 1.3.1 Hot-Carrier Effects

Hot-carrier effects are caused by the high electric-field induced impact-ionization in a semiconductor. The high electric-field creates highly energetic carriers ('hot' electrons/holes) that can create defects at the interface of two different materials (e.g. at the semiconductor-oxide interface in a MOSFET) [28], [29]. These defects at the material interface trap electrons/holes and result in shift in device parameters, such as threshold voltage, transconductance, off-state and on-state current, output resistance, etc. Both bulk and SOI processes are prone to this degradation mechanism. For long-channel length MOSFETs, the worst hot-carrier stress condition is at  $V_{GS} = \sim V_{DD}/2$  (peak substrate-current gate bias). However, this classical prediction does not work for short-channel MOSFETs [30].

## 1.3.2 Negative/Positive Bias Temperature Instability (NBTI/PBTI)

NBTI/PBTI is a physical phenomenon that occurs when pFETs/nFETs are operated at high temperatures. NBTI/PBTI testing of a pFET/nFET is done at a constant negative/positive bias applied to the gate electrode at high temperatures, with source, drain, and substrate grounded. When the MOSFET operates at high temperatures, a reaction-diffusion process causes the diffusion of hydrogen species from the semiconductor-oxide interface, creating interface traps [31], [32]. These interface traps can cause a shift in device threshold voltage, transconductance, etc. Both bulk and SOI processes are prone to this degradation mechanism.

### 1.3.3 Dielectric Breakdown

State-of-the-art short-channel length MOSFETs have gate-dielectrics as thin as  $\sim$  1-nm. However, the supply voltages have not scaled down at the same rate as the gate-oxide thickness. Thus large electric-fields exist across the thin gate-oxide. This large electric-field can cause carriers to tunnel across the oxide. These energetic carriers can create damage paths through the gate-oxide and can eventually cause large leakage currents to flow. Such a situation is called a dielectric breakdown [33]. Once the dielectric breaks down the transistor is rendered useless and cannot be used for switching or amplification applications anymore. Both bulk and SOI MOSFETs are sensitive to this degradation mechanism.

### 1.3.4 Large RF Stress Effects in CMOS

Large input RF stress can cause significant damage in BiCMOS technologies [34]. RF signal superimposed on a DC bias can cause voltage swings across a device, which

are beyond the safe-operating area of the device. This can cause the creation of traps in the gate-oxide and/or gate-oxide dielectric breakdown. Creation of interface traps at the silicon to gate-oxide interface causes decrease in carrier mobility and hence decrease in on-state current, transconductance, small-signal gain, power-gain, etc. Dielectric breakdown can result in catastrophic degradation of device parameters, rendering a device useless.

## 1.3.5 Latchup

Latchup can be caused in a semiconductor when there is a p-n-p-n doping path. Such a doping path exists in various circuits, e.g. a CMOS inverter having a pMOSFET and nMOSFET [35], [5]. Such a p-n-p-n doping path results in the existence of parasitic PNP and NPN bipolar transistors connected in a positive feedback loop. Once the gain of this parasitic feedback loop becomes larger than one ( $\beta_{PNP} \beta_{NPN} > 1$ ), a negative differential resistance action happens (current increases even at lower voltages) and results in excessive current through the p-n junctions, which can break them down. Latchup can also cause electro-migration and gate-oxide breakdown. Latchup is a significant concern in bulk technologies. Guard-ring structures are added in bulk technologies to prevent latchup. Latchup is automatically avoided in a SOI structure because of no p-n-p-n doping paths.

## 1.3.6 Ionizing Radiation Damage

Ionizing radiation effects are a concern in MOSFETs operating in space environments or in terrestrial applications with high radiation dose (e.g. nuclear reactors or medical facilities). Ionizing radiation creates electron-hole pairs in a semiconductor or oxide. The electron-hole pairs can re-combine quickly in a semiconductor. However, holes get trapped in the oxides because of their lower mobility than electrons. The holes can be trapped in gate-oxide bulk-traps, gate-oxide interface traps, and/or isolation oxide (field oxide or shallow trench oxides) traps [36]-[38] (Figure 8). These hole traps can cause shift in MOSFET parameters, such as threshold voltage, transconductance, off-state current, etc. SOI technologies are more prone to ionizing radiation effects because of the presence of buried oxide, which also traps the radiation generated holes and causes MOSFET parameter shifts (Figure 9).

**Figure 8:** Schematic representing the fundamental radiation induced electron-hole pair generation with bulk hole trapping and movement of the charge centroid to the interface under bias [38].

#### **1.3.7** Single-Event Effects (SEE)

SEE are caused in space environments where particles such as heavy ions (oxygen, helium, etc.) can strike a semiconductor material. These ion strikes create electronhole pairs in semiconductors that are collected at one of the transistor terminals. Such a collection of carriers causes current spikes at transistor terminal, which can corrupt the digital circuit operation state. Single-event effects have become a significant concern for short-channel length MOSFETs as a single ion strike can cause current spikes in multiple devices [39], [40]. Heavy ion strikes can also cause single-event-gaterupture (SEGR), single-event-latchup (SEL). SOI technologies are immune to SEE to a first-order.

**Figure 9:** Possible radiation-induced leakage paths along the (a) surface of buried-oxide (BOX) and (b) STI sidewalls.

## 1.3.8 Low- or High- Temperature Effects

Temperature plays a major role in the operation of semiconductor devices. Devices are designed such that they can operate across a wide temperature range. Carrier mobility in a semiconductor increases at low temperatures and decreases at high temperatures. The carrier recombination-generation is also affected by temperature, which affects the off-state current of MOSFETs. Threshold voltage of nMOSFETs increases at low temperatures and decreases at high temperatures behave in a similar way across temperature to a first-order [41]-[43].

#### 1.3.9 Electro-Migration

Electro-migration is the opening of metal lines on an integrated circuit as a result of the material voids created by high currents flowing through them. The thickness of the metal lines and of the vias should be chosen carefully considering the current flowing through those lines. Electro-migration can be an issue in both bulk and SOI technologies [44].

#### 1.3.10 Electro-Static Discharge (ESD)

ESD is a serious concern for integrated circuits. Spurious ESD pulses like those arising from handling of packaged devices can damage the devices, and can cause manufacturing yield loss and reliability failures. The scaling trend towards thinner gate-oxides aggravates this problem. ESD can cause large current pulses (of the order of amperes) to flow through the miniature MOSFETs, thereby damaging the gate-oxides. ESD protection circuits are commonly used to prevent such large currents from flowing into the input MOSFET gate [45]. Both bulk and SOI processes are susceptible to ESD failure.

#### 1.3.11 Antenna Effects

Process plasma charging during fabrication processes and the resulting gate-oxide damage is a major reliability concern for sub 100-nm CMOS technologies. During plasma processing, current passes through the thin gate-oxide as if it was under high electric field stress. The large metal lines present on the wafer act as antennas and the plasma charge moves from antenna to antenna destroying the thin gate-oxides of the MOSFETs connected to those antennas [46]. Foundries normally supply antenna rules, which are rules that must be obeyed to avoid this problem. Antenna rules are normally expressed as the allowable ratio of metal area to gate area. There is one such ratio for each interconnect layer. Antenna diodes are connected in parallel to the susceptible MOSFET gate to prevent gate-oxide damage. Both bulk and SOI processes are susceptible to antenna effects.

For a partially-depleted SOI device, alongside the above mentioned reliability concerns, the floating-body effect poses major challenge for large-scale design. The kink-effect and the history-effect resulting from floating-body device is a major problem [13], [47]. In a SOI technology, both floating-body and body-contacted MOSFET options are available. A body-contacted device allows a contact to the MOSFET body, which can be grounded or biased to a specific value. In this work, the results are presented for 65-nm, 45-nm, and 32-nm RF-CMOS on SOI technology, however, these results are valid for any short-channel SOI technology. Several trade-offs exist between performance and reliability mechanisms in these sub 100-nm CMOS technologies, and will be the focus of this work (Figure 10).

**Figure 10:** Trade-offs between performance and reliability in sub 100-nm CMOS technologies.

## 1.4 Organization and Contributions of the Dissertation

The objective of this research is to enhance the understanding of different reliability mechanisms in CMOS devices and circuits, and to understand the trade-offs between performance and reliability of sub 100-nm CMOS technologies. In this direction, several reliability-performance trade-offs studies have been carried out. Such trade-offs are used to demonstrate high performance reliable circuits. This research has leveraged access to the IBM 180-nm (7RFSOI), 65-nm (11soi), 45-nm (12soi), and 32-nm (32soi) RF-CMOS platforms as well as multiple generations of commercially available SiGe BiCMOS technologies.