## High-performance and electrically stable C60 organic field-effect transistors

X.-H. Zhang, B. Domercq, and B. Kippelen

Citation: Appl. Phys. Lett. 91, 092114 (2007); doi: 10.1063/1.2778472

View online: http://dx.doi.org/10.1063/1.2778472

View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v91/i9

Published by the American Institute of Physics.

## Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/

Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded

Information for Authors: http://apl.aip.org/authors

## **ADVERTISEMENT**

## High-performance and electrically stable C<sub>60</sub> organic field-effect transistors

X.-H. Zhang, B. Domercq, and B. Kippelen<sup>a)</sup>

Center for Organic Photonics and Electronics (COPE), School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, Georgia 30332

(Received 26 July 2007; accepted 9 August 2007; published online 27 August 2007)

The authors report on high-performance  $C_{60}$  organic field-effect transistors fabricated by physical vapor deposition. Electron mobility ranging from 2.7 to 5.0 cm<sup>2</sup>/V s was achieved when treating the gate dielectric with divinyltetramethyldisiloxane bis(benzocyclobutene) and depositing  $C_{60}$  at room temperature. The transistors combine threshold voltages near zero, low subthreshold slopes (<0.7 V/decade), on/off current ratios larger than  $10^6$ , excellent reproducibility, and good electrical stability under prolonged continuous dc bias stress. © 2007 American Institute of Physics. [DOI: 10.1063/1.2778472]

Thin-film field-effect transistors fabricated from organic semiconductors that can be processed onto various substrates at low temperature are of great interest. To enable the design of complementary circuits and take advantage of their intrinsic features such as low power consumption, n-channel and p-channel organic transistors with comparable performance are desirable. To date, more interest was given to the fabrication of p-channel transistors from hole transport organic materials, while electron transport organic semiconductors were given less attention. 1-4 Among electron transport organic semiconductors, fullerenes hold great promise for high-mobility *n*-channel organic field-effect transistors (OFETs). Since the first report by Haddon et al. in 1995, improvements in the processing of C<sub>60</sub> have led to the demonstration of the highest electron mobility of 6 cm<sup>2</sup>/V s by Anthopoulos et al.<sup>2</sup> in C<sub>60</sub> films deposited by hot wall epitaxy at an elevated temperature of 250 °C. By modifying the properties of the C<sub>60</sub>/SiO<sub>2</sub> interface using pentacene, Itaka et al. obtained an electron mobility of 4.9 cm<sup>2</sup>/V s in devices processed at 50 °C and tested in high vacuum, and the devices exhibited an ambipolar property due to the presence of the pentacene wetting layer. Hence, it is highly desirable to achieve high-performance n-channel OFETs with large electron mobility, low threshold voltage, low subthreshold slope, and large on/off current ratio, and that can be processed at room temperature using standard physical vapor deposition. Furthermore, the transistors should show good stability when subjected to multiple testing cycles and under continuous electrical bias.

Here, we report on high-performance  $C_{60}$ -based OFET devices that were fabricated by standard physical vapor deposition at room temperature. Devices with various geometries were fabricated and tested in nitrogen at ambient pressure. These devices exhibit high electron field-effect mobility values that range from 2.7 to 5.0 cm²/V s, depending on the device geometry. In addition to high-mobility values, these devices simultaneously exhibit threshold voltages near zero ( $|V_T| < 1$  V), low subthreshold slopes (< 0.7 V/decade), and on/off current ratios larger than  $10^6$ . By modifying the surface at the gate oxide with different organic dielectric materials, devices with excellent reproducibility and good electrical stability under multiple test cycles and continuous

electrical stress could be demonstrated. The best combination of high-performance and good electrical stability could be achieved by using divinyltetramethyldisiloxane bis(benzocyclobutene)<sup>7</sup> (BCB) at the semiconductor/gate dielectric interface.

Transistors were fabricated on heavily *n*-doped silicon substrates ( $n^+$ -Si, as the gate electrode) with 200-nm-thick thermally grown SiO<sub>2</sub> as the gate dielectric ( $\varepsilon_r$ =3.9). To better control the interfacial properties at the dielectric and C<sub>60</sub> interface, the SiO<sub>2</sub> dielectric surface was passivated with different thin buffer layers of polymers or with a self-assembled monolayer (SAM). Three hydroxyl-free polymers: BCB (Cyclotene<sup>TM</sup>, Dow Chemicals), polystyrene (PS), and poly(methyl methacrylate) (PMMA) were used to coat the SiO<sub>2</sub> surface. The thin films from diluted Cyclotene<sup>TM</sup> BCB were cross-linked at 250 °C on a hot plate for 1 h in a N<sub>2</sub>-filled glovebox. PS or PMMA films were spin coated from a 4 mg/ml solution in toluene and annealed at 130 °C on a hot plate for 1 h. Octadecyltrichlorosilane (OTS) SAM with a long alkyl chain, known as a good tunnel barrier to silanol groups on SiO2 surface, was formed by soaking the substrates in a 5 mM toluene solution of OTS for 15 h in a dry N<sub>2</sub>-filled glovebox right after the substrates were oxygenplasma treated for 2 min. The thickness of the OTS layer was 2.25 nm, as measured by ellipsometry. The root-meansquare (rms) surface roughness of both polymer-coated and OTS-treated 200-nm-thick SiO<sub>2</sub> was below 5 Å, as measured by atomic force microscopy (AFM). The capacitance density  $C_{\rm ox}$  (nF/cm<sup>2</sup>) was measured from parallel-plate capacitors with 12 varying contact areas. The buffer layer on SiO<sub>2</sub> refrom 16.6 to 16.2 nF/cm<sup>2</sup> with OTS, duced  $C_{\text{ox}}$ with BCB, 15.3 nF/cm<sup>2</sup> with PS, and 15.8 nF/cm<sup>2</sup> with PMMA. The results on rms and  $C_{ox}$  are listed in Table I and will be used to calculated OFET electrical parameters.

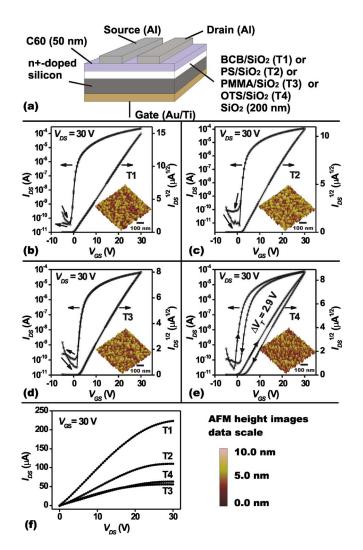

OFETs were fabricated with a top-contact geometry, as shown in Fig. 1(a). For convenience, the transistors with BCB, PS, PMMA, and OTS as a buffer layer are referred to as devices T1, T2, T3, and T4, respectively. All transistors, for which data are reported here, underwent the same processing, measurement, and analysis steps. The devices were completed by evaporating a 50-nm-thick film of purified C<sub>60</sub> at room temperature followed by the shadow mask deposition of the patterned 150-nm-thick Al as top source/drain electrodes. The electrical measurements were performed in a

a) Author to whom correspondence should be addressed; electronic mail: kippelen@ece.gatech.edu

TABLE I. Summary of the electrical parameters for  $C_{60}$  transistors T1, T2, T3, and T4. rms, root-mean-square roughness (of the gate dielectrics),  $C_{\rm ox}$ , capacitance density;  $\mu$ , field-effect mobility;  $V_T$ , threshold voltage;  $V_{\rm TO}$ , turn-on voltage;  $S_{\rm ox}$ , subthreshold slope,  $I_{\rm on/off}$ , on/off current ratio. T1: BCB/SiO<sub>2</sub>/ $n^+$ -Si; T2: PS/SiO<sub>2</sub>/ $n^+$ -Si; T3: PMMA/SiO<sub>2</sub>/ $n^+$ -Si; T4: OTS/SiO<sub>2</sub>/ $n^+$ -Si.

|    | rms<br>(Å) | $C_{\rm ox}$ (nF/cm <sup>2</sup> ) | $\mu$ (cm <sup>2</sup> /V s) | $V_{\mathrm{TO}} \ \mathrm{(V)}$ | $V_T$ (V)      | S<br>(V/decade) | $I_{ m on/off}$   |

|----|------------|------------------------------------|------------------------------|----------------------------------|----------------|-----------------|-------------------|

| T1 | 3.2        | 15.5                               | $3.1 \pm 0.2$                | $-1.5 \pm 0.3$                   | $-0.1 \pm 0.4$ | $0.5 \pm 0.1$   | $1 \times 10^7$   |

| T2 | 2.9        | 15.3                               | $2.1 \pm 0.1$                | $-0.1 \pm 1.4$                   | $1.2 \pm 1.3$  | $0.5 \pm 0.2$   | $6 \times 10^{6}$ |

| T3 | 3.1        | 15.8                               | $1.1 \pm 0.1$                | $1.4 \pm 0.3$                    | $2.1 \pm 0.4$  | $0.4 \pm 0.0$   | $6 \times 10^{6}$ |

| T4 | 4.1        | 16.6                               | $1.2 \pm 0.1$                | $-0.8 \pm 0.3$                   | $1.8 \pm 0.6$  | $0.6 \pm 0.1$   | $2 \times 10^6$   |

$N_2$ -filled glove box ( $O_2$ ,  $H_2O$  < 0.1 ppm) at normal pressure (1 atm) in the dark using an Agilent E5272A source/monitor unit.

To explore the influence of the different dielectrics on device performance, the electrical characteristics of transistors T1, T2, T3, and T4 with the same channel length L = 100  $\mu$ m and the same channel width W=1000  $\mu$ m are compared in Figs. 1 and 2. Figures 1(b)–1(e) show the representative transfer characteristics ( $I_{DS}$  vs  $V_{GS}$  plotted on a semi-logarithmic scale and  $\sqrt{I_{DS}}$  vs  $V_{GS}$ , at  $V_{DS}$ =30 V) for

FIG. 1. (Color online) (a) Diagram of the OFET device geometries for transistors T1–T4. [(b)–(e)] Transfer characteristics at  $V_{DS}$ =30 V for both forward and reverse gate bias scans with corresponding AFM height images of C<sub>60</sub> films (insets) for transistors T1–T4, respectively. (f) Output characteristics at  $V_{GS}$ =30 V for all four types of transistors.

both forward and reverse gate bias scans. Figure 1(f) compares the representative output characteristics ( $I_{DS}$  vs  $V_{DS}$ ) of all four types of transistors at  $V_{GS}$ =30 V. Field-effect mobilities  $\mu$  and threshold voltages  $V_T$  were calculated in the saturation regime defined by standard metal-oxidesemiconductor field-effect transistor models by fitting the  $\sqrt{I_{DS}}$  vs  $V_{GS}$  data to the square law. Also extracted from the transfer characteristics are turn-on voltage  $(V_{TO})$  and on/off current ratio  $(I_{\text{on/off}})$ . For each type of transistors, four devices with identical geometry were measured to obtain the mean value with its standard deviation (SD). The extracted electrical parameters ( $\mu$ ,  $V_{TO}$ ,  $V_T$ , S, and  $I_{on/off}$ ) (calculated from forward bias scans) are summarized and compared in Table I, along with rms and  $C_{ox}$  previously obtained. As seen from AFM height images in the insets of Figs. 1(b)-1(e),  $C_{60}$ films generally exhibit similar morphology and microstructure with small grains, regardless of the dielectric surface modification. This structure is characteristic to that observed previously in C<sub>60</sub> films deposited at low temperature.<sup>8,9</sup> Even with small grains in C<sub>60</sub> films, all transistors presented a mobility  $\mu$  higher than 1 cm<sup>2</sup>/V s, a threshold voltage  $V_T$ less than 2.5 V, a subthreshold slope S steeper than 1 V/decade, and  $I_{\text{on/off}}$  ratios larger than 10<sup>6</sup>. Note that among them, T1 (BCB) showed the highest mobility of  $3.1 \pm 0.2 \text{ cm}^2/\text{V s}$ .

Also shown in Figs. 1(b)-1(e) is the influence of the surface dielectric properties on the hysteresis observed sometimes in the transfer characteristics. Here, the threshold voltage shift  $\Delta V_T = \Delta V_T^R$  (reverse scan)  $-\Delta V_T^F$  (forward scan) was used as a metric to quantify the hysteresis and bias stress effects. A value of  $\Delta V_T$ =2.9 V due to hysteresis was observed in T4 with an OTS SAM, as shown in Fig. 1(e). However, the hysteresis behavior was strongly suppressed in transistors T1, T2, and T3 where the SiO<sub>2</sub> surface was passivated with hydroxyl-free polymers such as BCB, PS, or

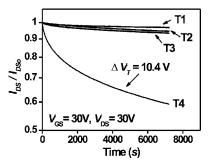

FIG. 2. Time-dependent decay of  $I_{DS}$  of  $C_{60}$  OFETs for transistors T1–T4 with different buffer layers under continuous dc voltage biases of  $V_{GS}$  =  $V_{DS}$ =30 V for 2 h.

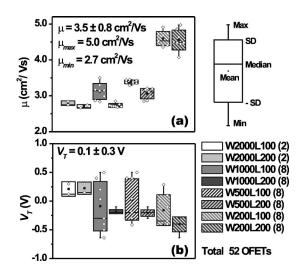

FIG. 3. Statistical analysis of the electrical characteristics: (a) mobility and (b) threshold voltage of 52  $\rm C_{60}$  OFETs obtained from two substrates fabricated within the same batch.

PMMA. The same trend was also found when conducting dc bias stress tests. No degradation was observed in transistors other than T4 (OTS) when the devices were repeatedly stressed by measuring transfer characteristics in the saturation regime 100 times with a 2 s waiting time between scans. Figure 2 shows the time-dependent decay of  $I_{DS}$  of  $C_{60}$ OFETs with different buffer layers under continuous dc voltage biases of  $V_{GS} = V_{DS} = 30 \text{ V}$  for 2 h. The C<sub>60</sub> OFETs with polymers as a buffer dielectric (T1, T2, and T3) show negligible degradation with 3.1%, 5.4%, and 6.6% decrease in  $I_{DS}$ , respectively. In contrast, T4 (OTS) devices show a steep decay with a 40% decrease in  $I_{DS}$  and a large  $V_T$  shift of 10.6 V. Hydroxyl-free polymers used with C<sub>60</sub> as gate dielectrics are shown to significantly improve the device stability. These observations are in agreement with the findings of Chua et al. 4 that hydroxyl groups (e.g., silanol) can lead to the electrochemical trapping of electrons that in turn can induce a gradual change in gate threshold over time when the transistor is under continuous bias. The electrical instability observed from T4 transistors treated with OTS confirms that surface silanol groups cannot be fully passivated by siloxane-based SAMs, <sup>10</sup> as previously shown by Chua *et al.* <sup>4</sup> in n-channel transistors fabricated from various conjugated polymers.

In view of the best combination of performance and stability obtained in T1 devices, a set of 52 OFETs devices with channel width ranging from 200 to 2000  $\mu$ m and channel length of 100 or 200  $\mu$ m was fabricated on two separate substrates that were processed identically within the same batch. The distribution and uniformity of device parameters  $(\mu, V_T)$  measured in the 52 devices are shown in Fig. 3 in the form of box plots. The on/off current ratios for the 52 devices range from  $10^6$  to  $10^8$  where the resolution of the off current  $(10^{-11} \text{ A})$  is a limiting factor. As shown in Fig. 3(a),

the mobility values measured in the 52 devices range from a minimum value of  $2.7 \text{ cm}^2/\text{V}$  s to a maximum value of  $5.0 \text{ cm}^2/\text{V}$  s with a mean value of  $3.5 \text{ cm}^2/\text{V}$  s and a SD of  $0.8 \text{ cm}^2/\text{V}$  s. Devices with the lowest W/L ratio ( $W=L=200 \mu\text{m}$ ) showed the highest mobility where geometry effects such as fringing currents may lead to larger effective field-effect mobilities. All the devices have a  $V_T$  near zero  $[0.1\pm0.3 \text{ V}$  see Fig. 3(b)] and a subthreshold slope S smaller than 1 ( $0.5\pm0.1 \text{ V/decade}$ ).

In conclusion, we have demonstrated electrically stable, high-performance top-contact C<sub>60</sub>-based *n*-channel OFETs in which BCB was inserted at the semiconductor gate dielectric interface. Studies of electrical degradation under dc bias stress performed on devices with different gate dielectric materials have shown that hydroxyl-free polymers such as BCB, PS, and PMMA can lead to devices with superior lifetime in which interface charge trapping effects are minimized. Current devices were fabricated using standard physical vapor deposition with substrates held at room temperature during the C<sub>60</sub> deposition demonstrating ease of processing over large area. Testing was performed in inert atmosphere at normal pressure. Future work will focus on passivating these transistors using atomic layer deposition which provides good encapsulation, as demonstrated recently with pentacene/C<sub>60</sub> solar cells.

This material is based upon work supported in part by the STC Program of the National Science Foundation under Agreement No. DMR-0120967 and by the Office of Naval Research. This work was performed in part at the Microelectronics Research Center at Georgia Institute of Technology, a member of the National Nanotechnology Infrastructure Network, which is supported by NSF (Grant No. ECS-03-35765).

<sup>1</sup>R. J. Chesterfield, J. C. McKeen, C. R. Newman, P. C. Ewbank, D. A. Da Silva Filho, J.-L. Bredas, L. L. Miller, K. R. Mann, and C. D. Frisbie, J. Phys. Chem. B **108**, 19281 (2004).

<sup>2</sup>T. D. Anthopoulos, B. Singh, N. Marjanovic, N. S. Sariciftci, A. Montaigne Ramil, H. Sitter, M. Cölle, and D. M. de Leeuw, Appl. Phys. Lett. 89, 213504 (2006).

<sup>3</sup>M.-H. Yoon, C. Kim, A. Facchetti, and T. J. Marks, J. Am. Chem. Soc. **128**, 12851 (2006).

<sup>4</sup>L.-L. Chua, J. Zaumseil, J.-F. Chang, E. C. W. Ou, P. K. H. Ho, H. Sirringhaus, and R. H. Friend, Nature (London) **434**, 194 (2005).

<sup>5</sup>R. C. Haddon, A. S. Perel, R. C. Morris, T. T. M. Palstra, A. F. Hebard, and R. M. Fleming, Appl. Phys. Lett. 67, 121 (1995).

<sup>6</sup>K. Itaka, M. Yamashiro, J. Yamaguchi, M. Haemori, S. Yaginuma, Y. Matsumoto, M. Kondo, and H. Koinuma, Adv. Mater. (Weinheim, Ger.) 18, 1713 (2006).

<sup>7</sup>L.-L. Chua, P. K. H. Ho, H. Sirringhaus, and R. H. Friend, Appl. Phys. Lett. **84**, 3400 (2004).

<sup>8</sup>S. Kobayashi, T. Takenobu, S. Mori, A. Fujiwara, and Y. Iwasa, Appl. Phys. Lett. **82**, 4581 (2003).

<sup>9</sup>M. A. Ramil, T. B. Singh, N. T. Haber, N. Marjanovic, S. Guenes, A. Andreev, G. J. Matt, R. Resel, H. Sitter, and S. Sariciftci, J. Cryst. Growth 288, 123 (2006).

<sup>10</sup>D. L. Angst and G. W. Simmons, Langmuir 7, 2236 (1991).

<sup>11</sup>W. J. Potscavage, S. Yoo, B. Domercq, and B. Kippelen, Appl. Phys. Lett. 90, 253511 (2007).