# FLOATING-GATE-PROGRAMMABLE AND RECONFIGURABLE, DIGITAL AND MIXED-SIGNAL SYSTEMS

A Thesis Presented to The Academic Faculty

By

Richard B. Wunderlich

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

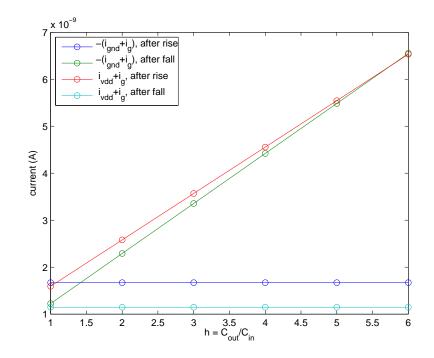

> School of Electrical and Computer Engineering Georgia Institute of Technology May 2014

Copyright © 2014 by Richard B. Wunderlich

### CONTENTS

| CHAPTE                                           | <b>R 1 OVERVIEW</b>                                                                                                                                                                                                                                                             |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CHAPTE</b><br>2.1<br>2.2                      | <b>R 2 BACKGROUND</b> 2         SRAM Based Switches       2         Floating-Gate Based Switches       6                                                                                                                                                                        |

| <b>CHAPTE</b><br>3.1<br>3.2<br>3.3               | <b>R 3</b> CAPACITIVELY COUPLED FLOATING GATE DIGITAL CIRCUITS10CCFG CMOS13Simulation14Measurement18                                                                                                                                                                            |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7    | <b>R 4 LOGICAL POWER</b> 20Introduction20Logical Power24Parameter Estimation274.3.1 Logical Effort284.3.2 Logical Power32Parameter Extraction34Statistical Path Analysis42Hand Optimization of Inverter Chain43Conclusion48                                                     |

| CHAPTE<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | <b>R 5 MEASURING SHORT-CIRCUIT POWER</b> 50Components of Power50Measuring Active Power51Voltage Overshoot and Miller Effect53Measuring Short-Circuit Power60Measuring Dynamic Power68Measuring Static Power72                                                                   |

| СНАРТЕ                                           |                                                                                                                                                                                                                                                                                 |

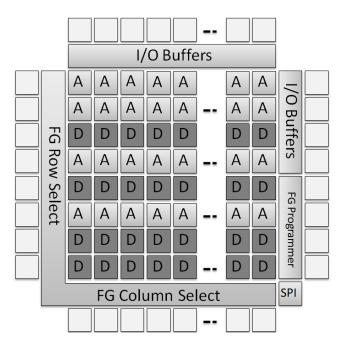

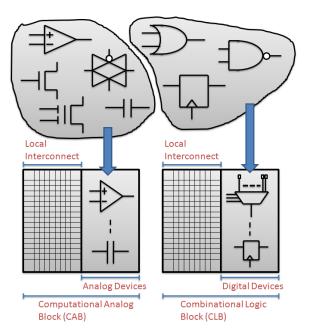

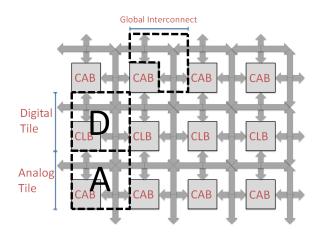

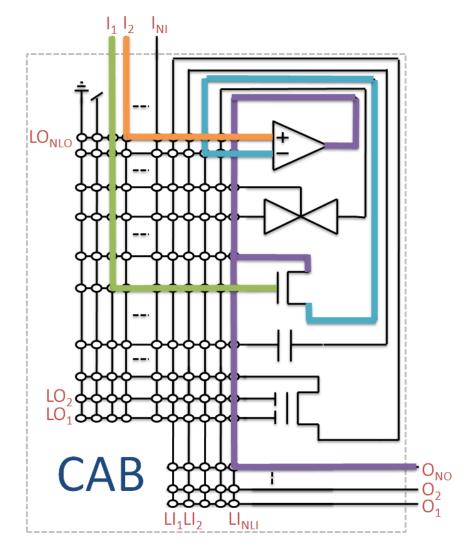

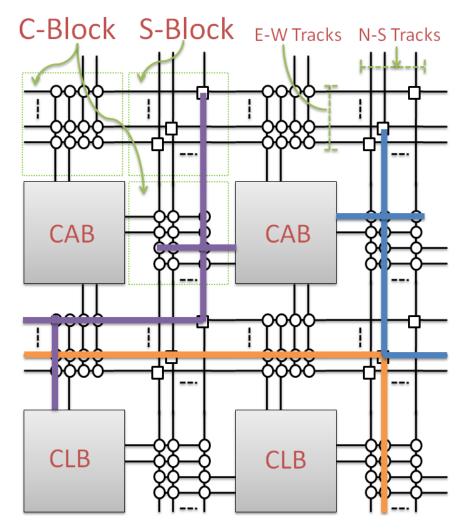

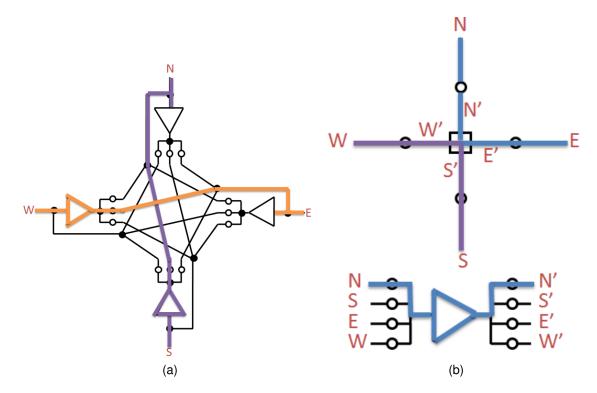

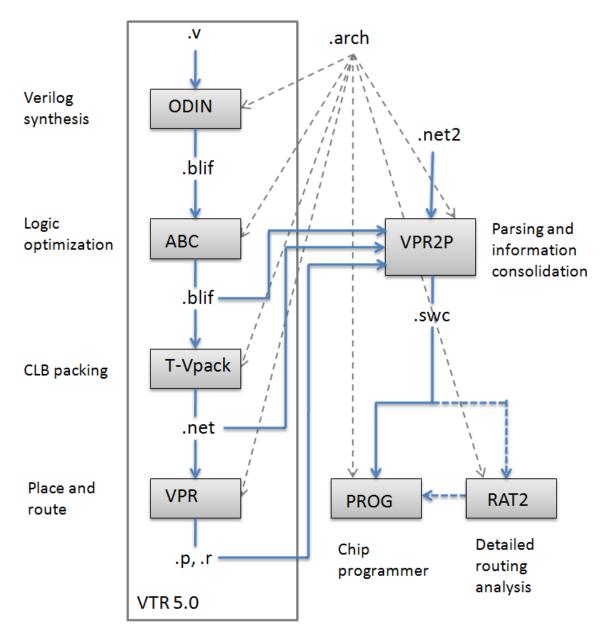

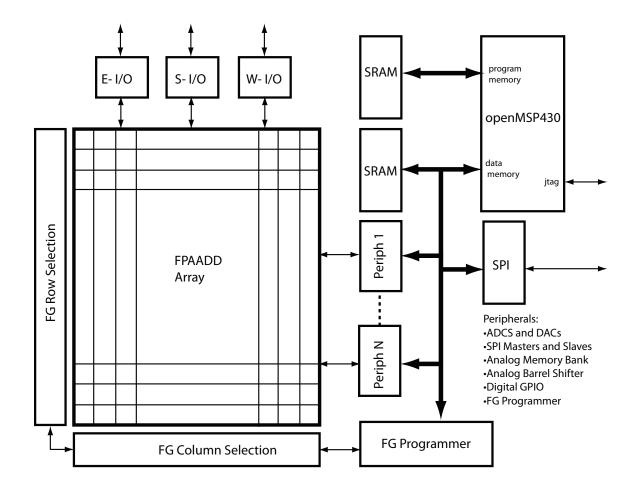

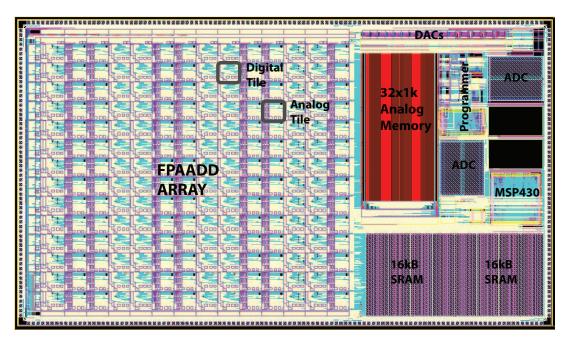

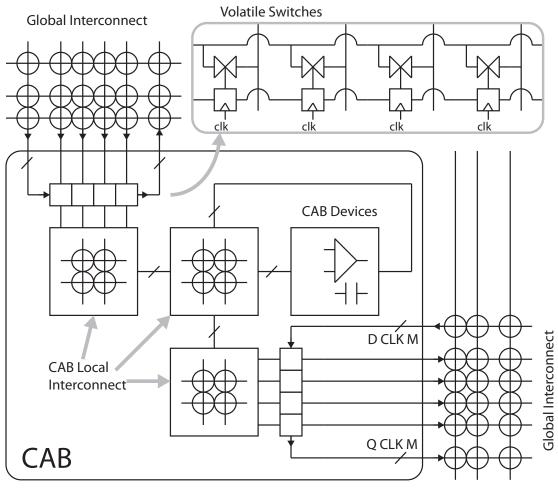

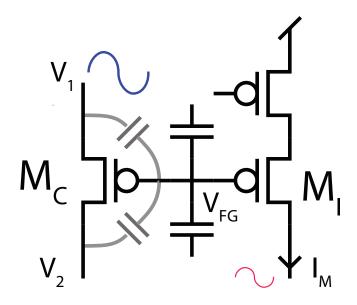

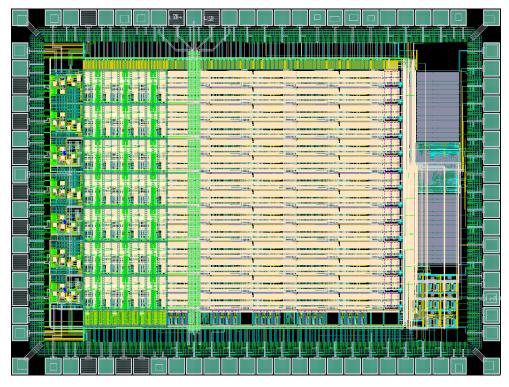

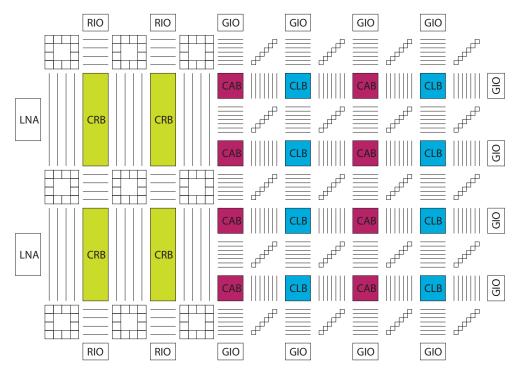

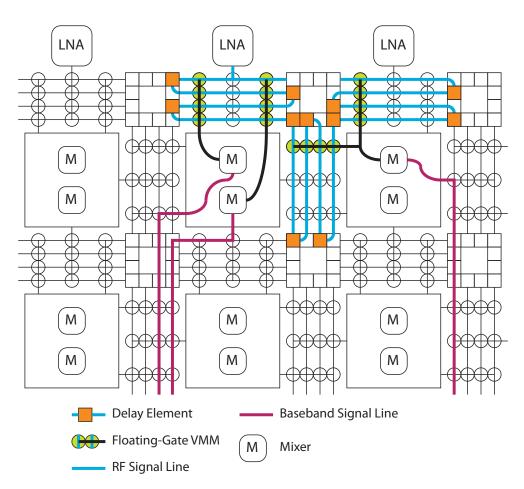

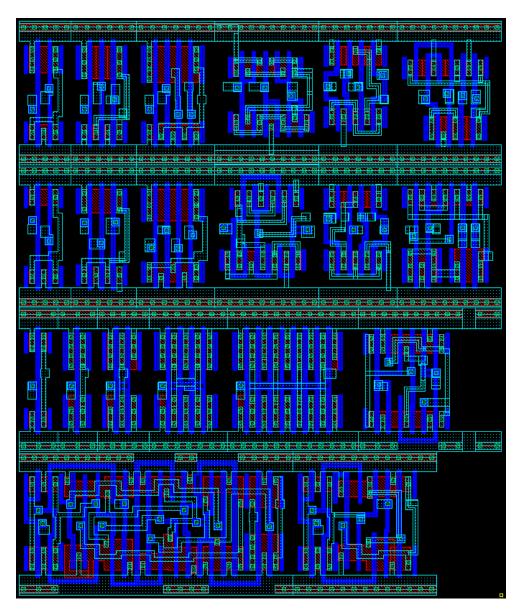

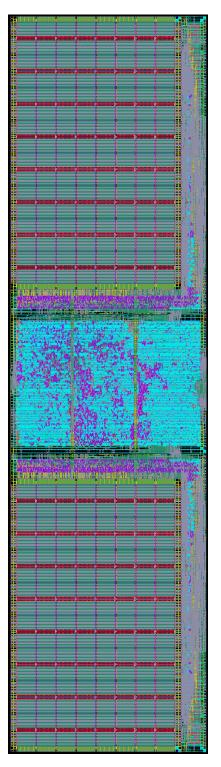

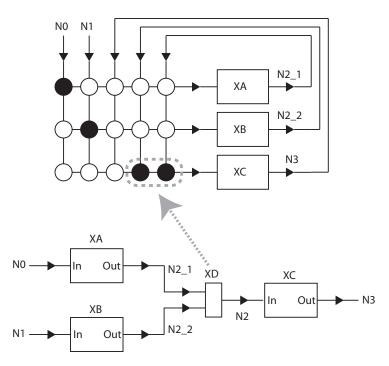

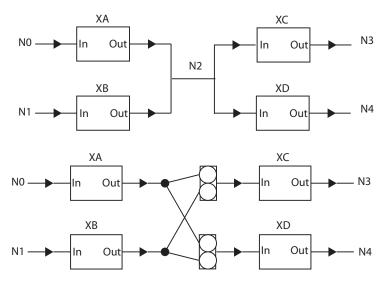

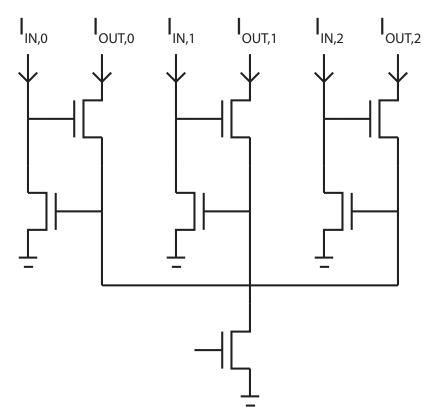

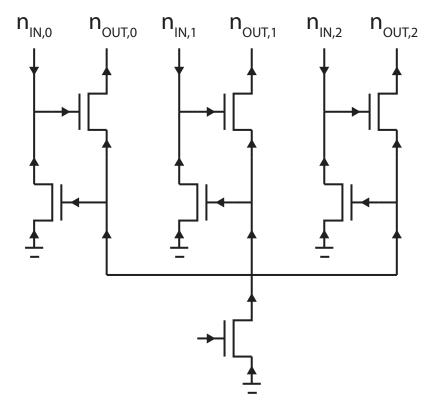

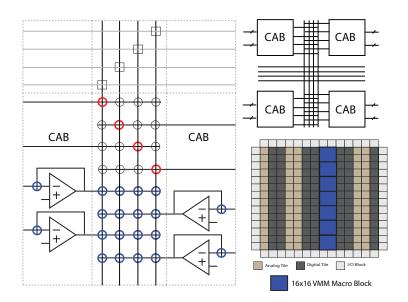

| 6.1<br>6.2<br>6.3                                | SIGNAL ARRAY78Introduction78FPAADD Architecture816.2.1 Floating-Gate Switch856.2.2 Combinational Logic Block876.2.3 Computational Analog Block876.2.4 Global Interconnect926.2.5 Interconnect Comparison93CAD Software956.3.1 Verilog To Routing966.3.2 Routing on the FPAADD98 |

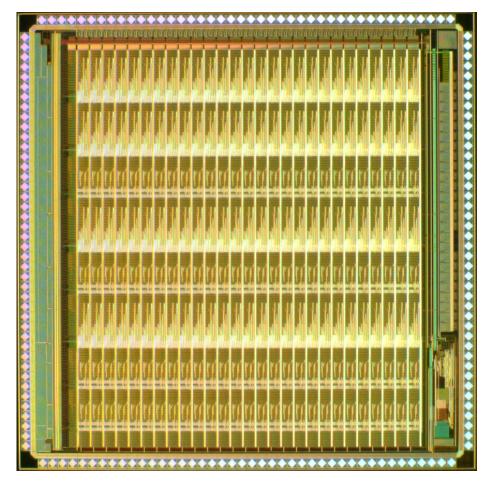

| 6.4<br>6.5<br>6.6 | System Verification                      | <br> | <br><br> | 102<br>102<br>103 |

|-------------------|------------------------------------------|------|----------|-------------------|

|                   |                                          |      |          |                   |

| CHAPTE            |                                          |      |          |                   |

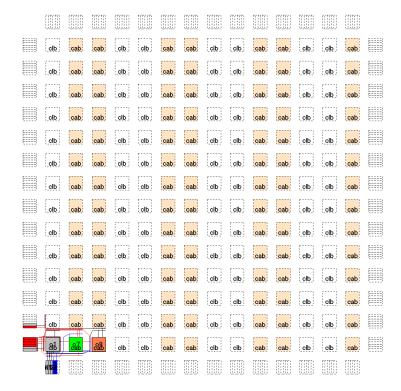

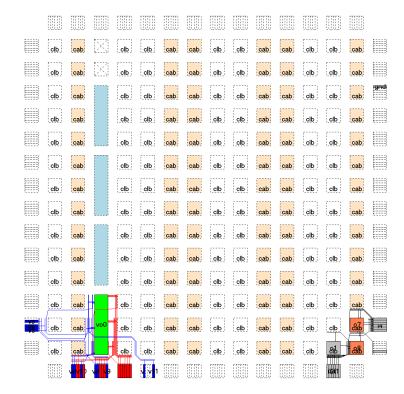

| 7.1               | RASP3.0 Architecture Family              |      |          |                   |

| 7.2               | The RASP3.0 and RASP3.0a                 |      |          |                   |

| 7.3               | Direct and Indirect Switch Programming   |      |          |                   |

| 7.4               | Volatile Switches as CAB Components      |      |          |                   |

| 7.5               | Floating-Gate Based Analog JTAG          |      |          |                   |

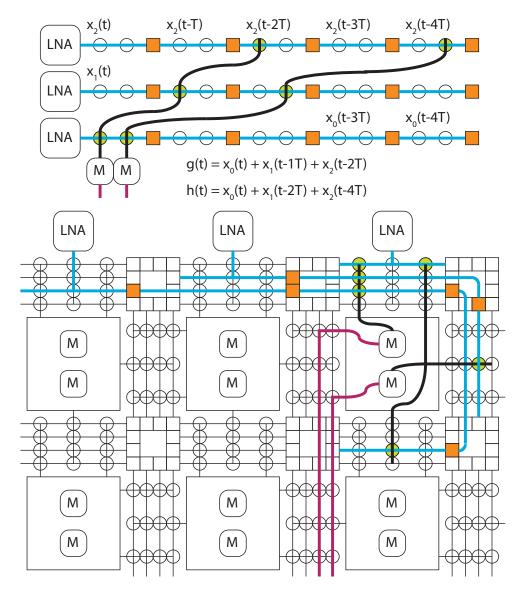

| 7.6               | The RASP3.0rf                            |      |          |                   |

| 7.7               | Reconfigurable Delay Lines               |      |          |                   |

| 7.8               | Custom Processor and Memory              |      |          |                   |

| 7.9               | Floating-Gate Scaling to 40nm            |      |          |                   |

|                   |                                          |      |          |                   |

| 7.11              | RASP 3.0 CAD Tools                       |      |          |                   |

|                   | 7.11.1 VPR                               |      |          |                   |

|                   | 7.11.2 VMM Synthesis and Fan-In Elements |      |          |                   |

| 7 10              | 7.11.3 VMM with WTA circuit example      |      |          |                   |

| 1.12              | 2 VMM Synthesis and Macroblocks          | • •  | • •      | 143               |

| CHAPTE            | ER 8 CONCLUSION                          |      |          | 148               |

| APPEND            | DIX A LOGICAL POWER EXTRACTION SOFTWARE  |      |          | 157               |

| A.1               | Characterization Circuit                 |      |          | 157               |

| A.2               | Installation and Setup                   |      |          | 157               |

| A.3               | Simple Example                           |      |          |                   |

| A.4               | Modifying Default Parameters             |      |          | 160               |

| A.5               | Sweeps                                   |      |          | 161               |

| A.6               | 2D Sweep Example: r, VDD                 |      |          | 162               |

| A.7               | 1D Sweep Example: r                      |      |          | 163               |

| A.8               | Generating Netlists                      |      |          | 164               |

|                   |                                          |      |          |                   |

## CHAPTER 1 OVERVIEW

This body of work as a whole has the theme of using floating-gates and reconfigurable systems to explore and implement non-traditional computing solutions for difficult problems. Various computational methodologies are used simultaneously to solve problems by mapping pieces of them to the appropriate type of computer. There does not exist a systematic approach to simultaneously apply analog, digital, and neuromorphic techniques for solving general problems. Typically this is a very difficult task, one that few attempt to undertake. However, when done right, solutions can be found with orders-of-magnitude improvement over existing solutions restricted to using only one type computational domain. To that end, I have helped build large and complex recon-figurable systems (and associated software tools for helping to utilize these systems) capable of implementing solutions to problems in all three of these domains simulta-neously. These systems are used to explore and implement cross domain solutions to difficult problems.

The earlier work was involved with simply applying floating-gate technology to improving the building blocks of digital systems. Through that early work a new logic family built from floating-gate transistors was discovered, a Logical Effort compatable power analysis technique was developed, and a low power floating-gate based FPGA was implemented. This work was then merged with existing research in the group involving solving problems using reconfigurable analog and neuromorphic techniques. Thus my work converged on the mentioned systems that allow one to solve problems using techniques from all three domains: analog, neuromorphic, and digital.

# CHAPTER 2 BACKGROUND

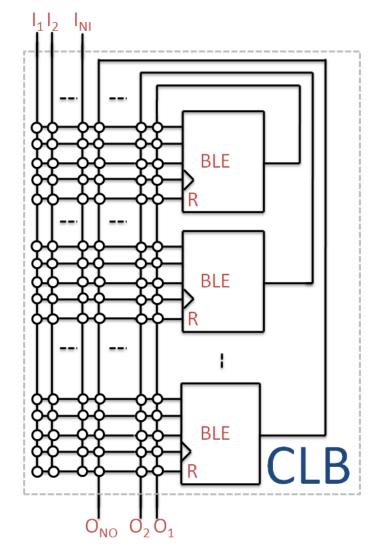

Since we are trying to solve a wide variety of computational problems, we will be implementing systems that are, to a certain degree, general purpose. The approach we will undertake is largely one of reconfigurable systems. Low level computational elements (digital or analog devices) are placed in a sea of flexible wiring. High level functionality is produced by building large circuits out of these devices by using the flexible wiring (interconnect) to reconfigure the devices into a new topology. Switches are the smallest elements of the interconnect, and provide the utility of being able to either connect two nets together, or not, decided by the state of some memory element assigned to that switch.

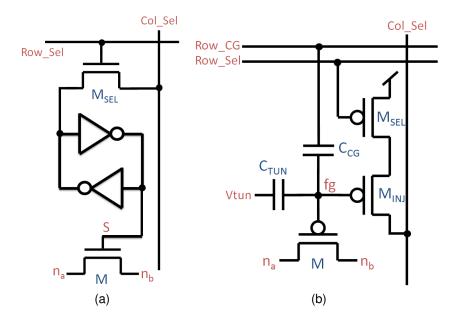

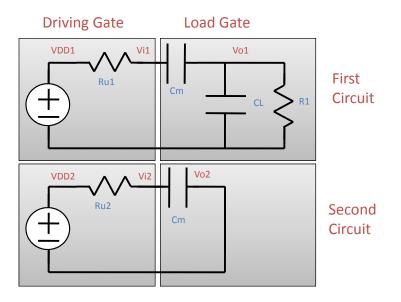

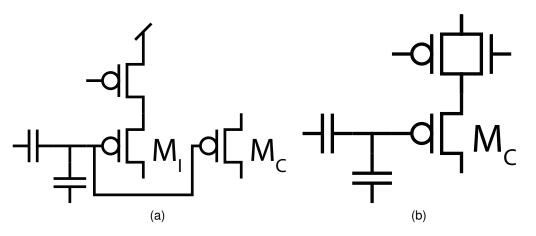

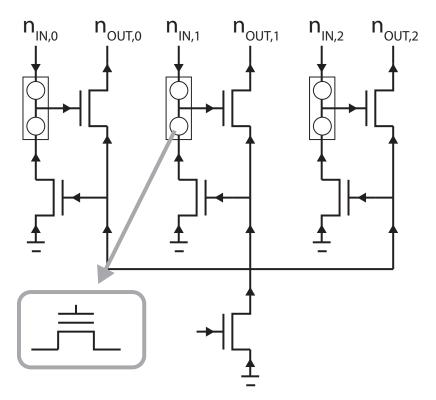

In the majority of modern FPGAs, this is implemented by a single nFET (or sometimes a transmission gate) whose gate is driven by SRAM. Our reconfigurable systems, however, use floating-gate transistors as both the switch and the storage device. Figure 1 shows examples of SRAM based and floating-gate based switches.

#### 2.1 SRAM Based Switches

One way to increase the efficiency of an SRAM based switch is to utilize a single nFET, instead of a transmission gate (a pFET and nFET in parallel). This reduces parasitic capacitance at the cost of conductance, but the net effect is usually a faster switch. This circuit, when both the SRAM and logic are on the same voltage, only passes up to about a threshold voltage less than the rail for a logic high output. This reduces headroom and noise margin and significantly increases the leakage power in gates driven by this lower logic level.

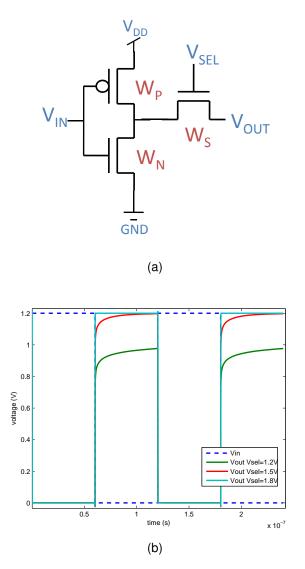

Consider the tristate inverter of Figure 2a. Its function is to invert the input signal when  $V_{SEL}$  is high, connecting the output through a low impedance path to either the

2

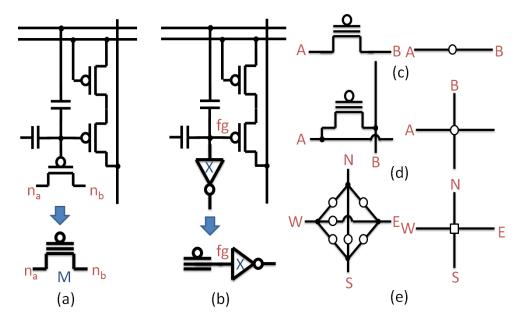

Figure 1. a) Switch element *M* is an nFET with SRAM based state storage as is typical of modern FPGAs. *M*'s state is set by turning on  $M_{SEL}$  and driving *ColSel* high or low. b) Switch element *M* is a pFET whose gate has no DC paths under run-time bias, and whose state is stored as charge trapped on the fg node. Negative charge is added through  $M_{INJ}$  by channel hot electron injection or removed through  $C_{TUN}$  by Fowler-Nordheim tunneling

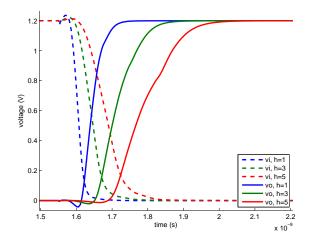

$V_{DD}$  or GND, and to disconnect the output from any rail voltage when  $V_{SEL}$  is low. A transient simulation of input and output voltage for this device can be seen in Figure 2b for various values of  $V_{SEL}$ . An idiosyncratic output is observed for when the gate tries to pull the output high. This is the well known threshold drop behavior of nFETs attempting to pass logic level high signals.

This response is due to the output of the gate being the source terminal of the passfet nFET. Assuming that the output is initially low, and that the input makes a transition from high to low, the tristate's pull-up network turns on and starts to pull the output high. However, as the output voltage starts to rise, the source voltage of the nFET starts to increase and eventually causes the passfet to enter subthreshold, where conduction is significantly weaker. The EKV model predicts this to be when

$$\kappa (V_G - V_{T0}) - V_S < 0, \tag{1}$$

Figure 2. Transient input and output voltages for a tristate inverter with  $V_{SEL} = 1.2V$ , 1.5V, and 1.8V for an arbitrary load.  $V_{DD}$  was 1.2V and the threshold voltage for this process is about 0.4V.

where  $\kappa$  is the capacitive coupling ratio of the gate voltage,  $V_G$ , into the surface potential of the channel, and all voltages are referenced to the bulk. In this case,  $V_G = V_{SEL}$  and  $V_S = V_{OUT}$ , such that the maximum voltage the output can go to before the onset of subthreshold is

$$V_{out} = \kappa (V_{SEL} - V_{T0}) \tag{2}$$

To keep the passfet above threshold during the entire transition,  $V_{SEL}$  must be biased higher than  $V_{DD}$ :

$$V_{SEL} = \frac{V_{DD}}{\kappa} + V_{T0} \tag{3}$$

Figure 2b shows that for  $V_{SEL} = V_{DD}$  the output quickly reaches to about a threshold drop down from  $V_{DD}$  before the passfet leaves above threshold and then starts to slowly conduct up towards  $V_{DD}$  in subthreshold. Larger values of  $V_{SEL}$  cause the passfet to stay in above threshold longer, and for  $V_{SEL} = 1.8V$  the passfet is in above threshold the entire time and the output voltage quickly converges on  $V_{DD}$ .

If the delay of the gate is measured as the 50% rail-to-rail propagation delay, then the time scale of this figure is too large to see any speed differences, as for all values of  $V_{SEL}$  in this figure, the onset of subthreshold is after the output goes to  $V_{DD}/2$ .

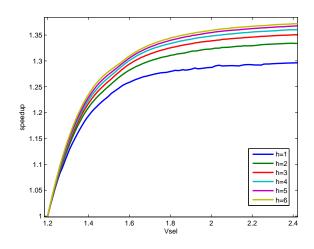

Figure 3 shows the average propagation delay speedup of a tristate inverter in a chain of tristate inverters versus  $V_{SEL}$  for various h, where each stage  $h_i = h$ , for various h. Here h stands for the *Logical Effort* term, *electrical effort*, which is closely related to fanout and load capacitance, and is defined as the ratio of load capacitance seen by the driving gate to the driving gate's input capacitance,  $h = C_{out}/C_{in}$ .

Note that speedup increases monotonically with  $V_{SEL}$  and h, which makes sense, as the smaller the load capacitance, the more delay is dominated by the gate's own parasitic capacitances which are not discharged by the passfet. For this particular process and gate topology, simulation shows speedups in excess of 30% when  $V_{SEL}$  >

Figure 3. Average propagation delay speedup of a tristate inverter in a chain of tristate inverters versus  $V_{SEL}$  for various *h*. Where each stage of the chain has the same *h*.

$V_{DD} + V_{T0}.$

SRAM can achieve these results by running the SRAM rail voltage at a higher voltage than the rest of the logic in the chip. But this comes at a cost of an increase in leakage current in the SRAM. Floating gates, however, can do this without increasing memory stand-by power, while also simultaneously reducing all stand-by power from off switches.

### 2.2 Floating-Gate Based Switches

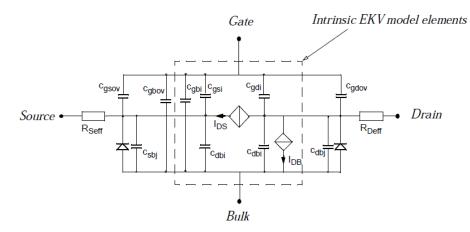

Floating-gate transistors are normal MOSFET devices where the gate is completely insulated by silicon-dioxide. This means that all terminals capacitively couple onto the gate, and the device's effective threshold is modified by charge trapped on the gate. The modeling of the behavior of this device can be achieved by substituting for the gate voltage the following in any MOSFET current equation

$$V_{fg} = \frac{1}{c_{tot}} (Q_{fg} + \sum v_i c_i)$$

(4)

where  $c_{tot}$  is the total capacitance at the floating-gate,  $c_i$  and  $v_i$  are the capacitance coupling into the floating-gate and the voltage at the  $i^{th}$  node of the device. Q is the net total charge on the floating gate that is modified (or programmed) to set the state of the device.

Since the gate has no DC path to ground, the charge Q is trapped and remains on the floating-gate during normal circuit operation. However, for the floating-gate to implement the state storage of the switches, this charge has to be modifiable in a selective manner.

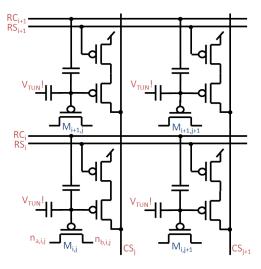

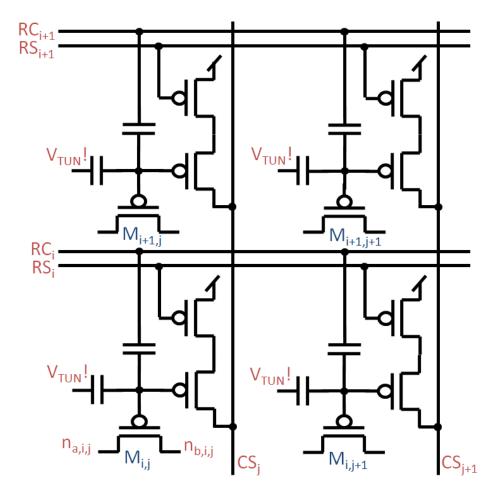

Figure 4 shows an array of floating-gates. All floating-gates are erased by applying a very large voltage to the global signal  $V_{TUN}$ ! which enables electrons to flow off of the floating-gate nodes into the  $V_{TUN}$ ! net by Fowler-Nordheim tunneling. This makes all floating-gates very positive in potential, and effectively turns off all floating-gate pFETs. To selectively turn on a pFET floating-gate, electrons are injected onto the floating-gate by way of impact based channel hot electron injection through  $M_{inj}$  (Figures 1b and 4) [1]. If  $A_{VDD}$  is set to a high enough voltage to allow for injection, the  $i^{th}$  floating-gate is injected by setting RS<sub>i</sub> low and CS<sub>j</sub> low. Injection takes place in regions where the electric field is strong enough to heat a significant portion of the minority carriers in the pFET channel to energies high enough to conduct in the silicon-dioxide, and the field in the oxide is such that those carriers are attracted to the floating-gate. The highest electric fields are achieved by operating the device in subthreshold, where almost all of the source to drain voltage is dropped in a very short region near the drain, and setting the source to drain voltage as high as possible. In this case, the probability of injection of each carrier is maximized, but when this is maximized the amount of available carriers tends to be very low. Because of this, injection rate is maximized somewhere near the onset of above threshold, and tends to be very poor in regions of high above threshold (lots of carriers, not very high fields) and deep subthreshold (very high fields, but not many carriers) [1]. In order to bias the device in regions conducive to

Figure 4. Programming is achieved by globally removing charge from the floating-gate nodes through  $C_{TUN}$  via Fowler-Nordheim tunneling, and then selectively adding charge through  $M_{i,j}$  with impact carrier hot channel electron injection. Injection of charge per row is controlled by the selection lines  $CS_i$ , and per column by the drain lines  $CS_j$ .

injection, and further optimize the dynamic range of programmability, there is a control gate on each floating-gate that is controllable during injection.

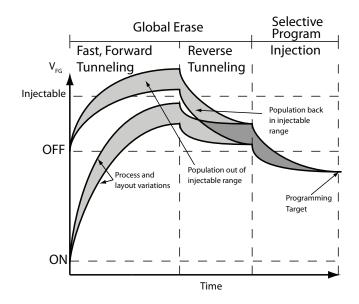

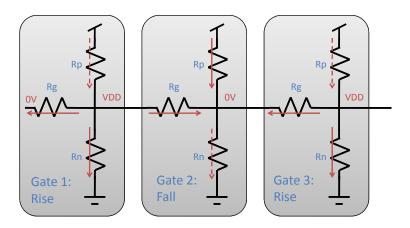

Figure 5 shows the floating gate erase and program method. The erase comprises a forward tunneling operation that removes electrons from all floating gates in the system. Due to different starting conditions, and different tunneling rates, floating-gates end up at different states at the end of the tunneling. The different starting conditions are due to previously programmed state, or floating-gate drift due to multiple erase exposures. The rates are largely layout dependent, but are also significantly impacted by process variations across the chip.

In general, tunneling slower( ie. at a lower voltage) for longer periods of time, can bring the entire population of floating-gates to the same average. But this can take an unreasonable amount of time. Therefore, an aggressive forward tunneling operation takes place that pushes the worst case floating-gates into the accepted off range. But also happens to push some of the floating-gates into such an off state that they can not be programmed with injection (injection being proportional to current). A reverse tunneling pulse is used to bring the populations back together. Then individual floating

Figure 5. The floating-gate programming procedure uses a global erase comprising a forward and reverse tunneling phase, and then individual floating-gates are selectively programmed using hot electron injection.

gates are programmed selectively using hot electron injection.

Well designed floating-gates and programming techniques are able to produce runtime voltage ranges on the floating gates (this range is fundamentally limited by tunneling) that are higher and lower than the supply nets. This makes a switch with a much higher  $I_{on}/I_{off}$  value than an SRAM based switch would be able to achieve. And since accurate programming algorithms exist that can precisely set the charge on floating gate, a continuous spectrum of currents between the on and off state can be achieved. This property makes the floating-gate transistor useful as an explicit circuit element to modify the behavior of analog and digital circuits, or can be used to perform meaningful computation with interconnect devices.

#### **CHAPTER 3**

### CAPACITIVELY COUPLED FLOATING GATE DIGITAL CIRCUITS

In synchronous digital design the delay of the critical path is used to set the clock frequency in order to guarantee that the propagation delays of all paths will satisfy the setup and hold times of the latches used to synchronize the data. In the classical CMOS design space, the choices allowed on these paths include gate mapping and transistor sizing. While a larger, more parallelized gate architecture with transistors sized through methods like Logical Effort are able to sacrifice area and power in order to further enhance the performance of the critical path, a smaller, less complicated architecture with minimally sized transistors can be used on non-critical paths, sacrificing speed for area and power. The synchronization, however, still becomes a necessity as given by these quantized design options, and the intrinsic process variability of fabrication, it becomes nigh impossible to equate the propagation delays of all paths. All paths will end up with a varying amount of slack Figure 6. Giving the designers more options to allow them to optimize out the slack, as well as to further control the power, area, and delays can pave the way for a better design and has been the topic of much research, giving rise to commercially implemented techniques such as: Dynamic Voltage Scaling (DVS), and variable threshold transistors [2].

While lowering the clock frequency of a chip at run time can certainly reduce the average power consumed by the chip, it hurts average MIPS/Watt performance giving rise to an increase in energy used per computation. This is because it increases the amount of slack in every path on the chip, and while the dynamic energy consumed per computation may stay the same, an increase in time is spent dissipating static power. In order to decrease the energy consumed per computation, techniques like DVS scale the rail voltage of the chip with the frequency to reduce the slack.

Figure 6. Various cominational logic paths. The maximum delay worst case delay path sets the clock period, and all other paths operate with timing slack.

Changing the rail voltage has a many fold effect on a digital circuit's operation. Increasing VDD increases the amount of charge that has to be moved onto a gate in order to fully charge it up which linearly increases dynamic energy per switch, and because the driving gate's ability to source current increases polynomially with VDD, a net decrease in switching time results. An increase in VDD, while usually not significantly increasing subthreshold leakage currents, increase the voltage drop over which the leakage currents pass and therefore linearly increases static power dissipation.

Adjusting the threshold voltages of the transistors that make up the gates gives rise to a new design trade-off. Increasing the threshold of a device exponentially decreases the subthreshold leakage currents but polynomially decreases the driving current when the devices are supposed to be on. Adjusting the threshold allows the designer to trade off static power dissipation and speed and can be done at fabrication time by changing the doping profiles or the oxide thicknesses.

An important consequence here is that given a particular path architecture and a

target path delay, there is a two dimensional design space for  $V_{DD}$  and  $V_T$  in which a subset of points exist that will produce the target frequency, and within this space dynamic and static power dissipation are traded off, and that there exists a particular VDD and  $V_T$  for that path that globally minimized total power [3].

There exist significant barriers to picking the optimal  $V_T$  for all paths. While the threshold voltages can be adjusted rather harmlessly by changing the doping profiles, the select ability of this offset is coarse-grained in that doping profiles are applied to either the entire chip or very large portions. Changing the doping can also produce adverse effects on carrier mobility within the devices, hindering speed even further. Threshold adjustments in the form of varying oxide thicknesses can be applied very selectively to individual paths but the choice of thickness is usually process limited to only a couple. Varying  $V_T$  in these manners are static at run time and allow for no run time trade off of energy per cycle and cycle time.

Having varying VDDs for spatially local paths becomes logistically implausible. For every new VDD desired a new rail routing network needs to be introduced and a new power source needs to be fabricated. This aside, two adjacent paths with varying VDD will either be forced to have separate wells for their pFETS or suffer significant well leakage between the rails. Another barrier is that paths with different VDDs produce different logic levels, and upon mixing these signals it may be necessary to introduce logic level shifters. This is why in VDS VDD is often varied globally across the entire chip, or at best variable VDDs exist on the chip but in very coarse grained regions to minimize the area penalties. To further limit the choices of DVS, there exists maximum and minimum values for acceptable CMOS operation for VDD [2]. Significant problems arise when VDD approaches the reverse bias breakdown voltage of the PN diode junctions or within twice the threshold voltage of the devices.

We present a capacitively-coupled, floating-gate based digital CMOS logic family (CCFG CMOS) that allows a designer to trade-off dynamic power versus delay, and

12

static power versus delay, without the limitations of DVS.

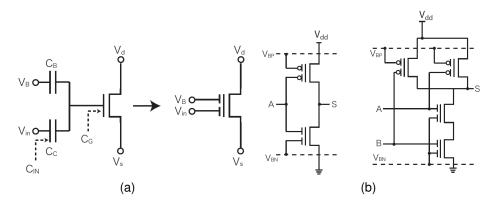

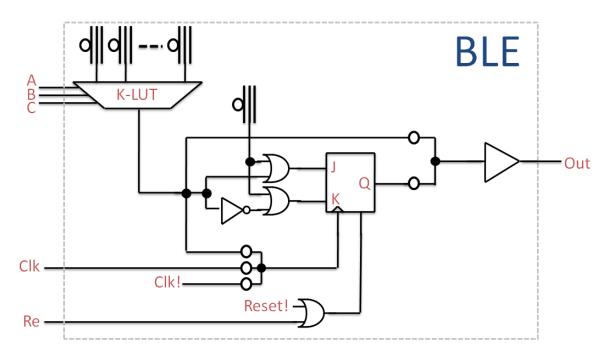

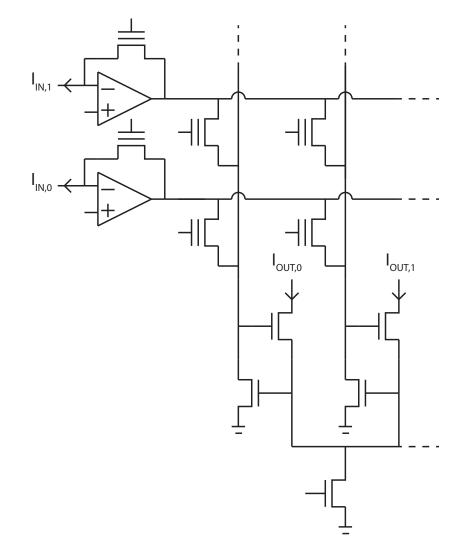

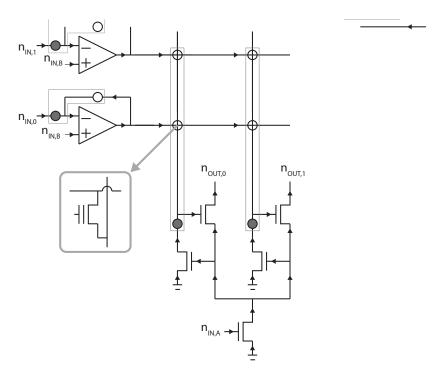

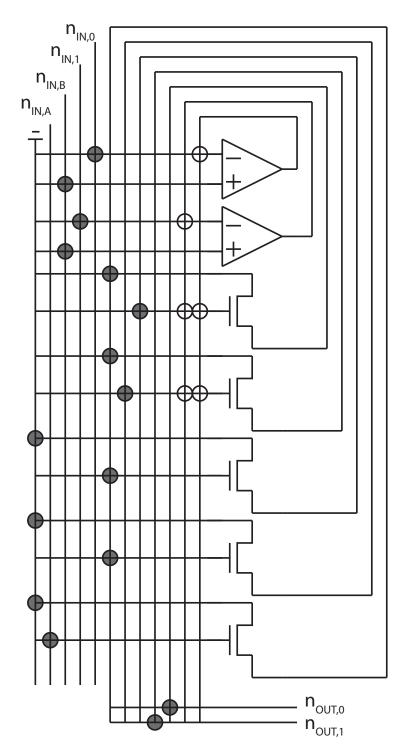

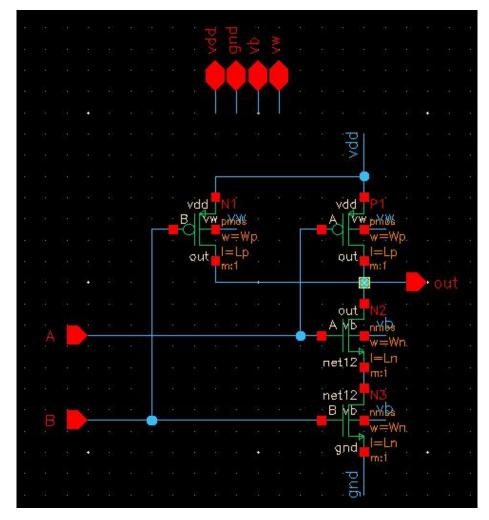

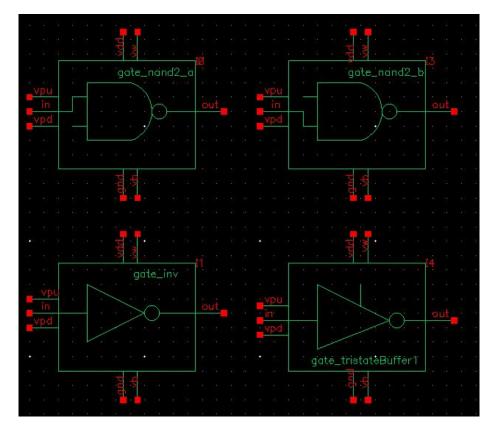

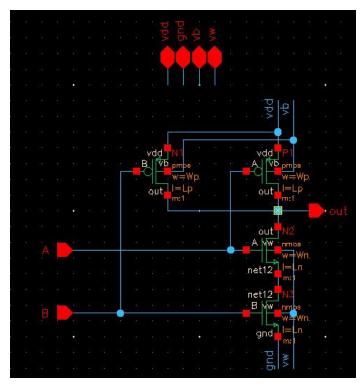

### 3.1 CCFG CMOS

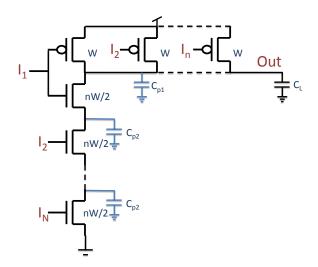

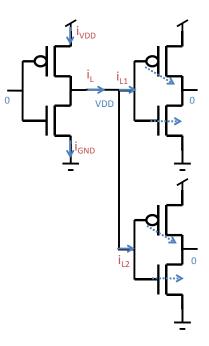

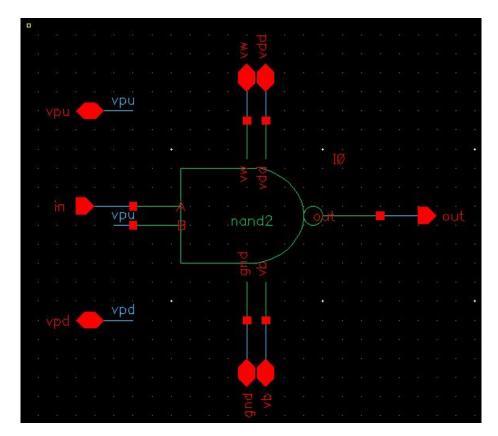

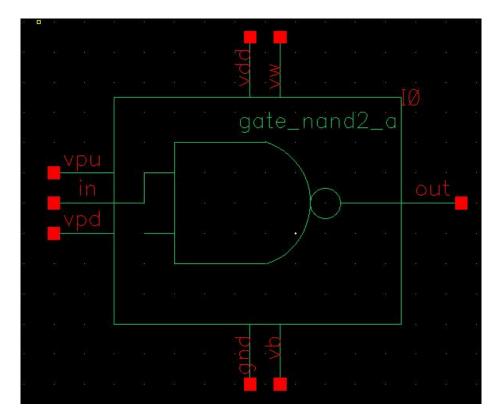

As can be seen in Fig. 7, there are two capacitively coupled inputs to the floating-gate of the transistor. The input labeled  $V_{IN}$ , coupled through  $C_C$ , serves as the regular transistor gate input used in CMOS devices, while the other input, labeled  $V_B$  and coupled through  $C_B$ , is used as a bias voltage for the transistor. The pull-up and pull-down networks of CMOS logic gates can be built using floating-gate nFETs and floating-gate pFETs as per normal CMOS design using the  $V_{IN}$  inputs as the regular gate inputs. The bias inputs of each floating-gate nFET are tied together to form the nFET bias net,  $V_{BN}$ , while the bias inputs of the pull-up network are assembled to form  $V_{BP}$ . An inverter and a two-input NAND gate made by this arrangement are shown in Figure. 7.

The capacitance  $C_{IN}$ , seen by the regular input, becomes the parallel combination of  $C_C$  and the rest of the capacitance seen at the floating gate node including  $C_B$  and the capacitance looking into the gate  $C_G$ . The smaller  $C_C$ , the smaller the input capacitance, and the less charge that has to be moved in order to charge up the node. This in turn linearly decreases the amount of energy consumed per switch with decrease in input capacitance. The caveat here is that the contribution of  $V_{IN}$  to the floating gate voltage is then proportional to the capacitive divider of  $C_C$  and the total capacitance seen at the floating gate,  $C_{total}$ , so while the driven gate requires less charge per switch, the strength of the driving gate at supplied current decreases polynomially with decrease in the amount coupled. This gives rise to a fabrication time trade off of dynamic power dissipation and speed.

The bias voltage gets coupled into the floating-gate much in the same way as the input voltage but through  $C_B$ . However, this voltage remains static during normal operation of the gate and after charging up once serves to simply couple an extra bias voltage into the floating-gate to effectively adjust the the threshold of the device. By

increasing the  $V_{BN}$  voltage a polynomial increase in driving current results which increases speed, but an exponential increase in subthreshold current occurs increasing static power dissipation. This allows a run-time adjustment of speed and static power dissipation.

Dynamic power dissipation can be optimized on a per path basis using CCFG CMOS by choosing the capacitive dividers at fabrication time without any of the penalties associated with trying to apply multiple VDDs to spatially local paths, or without having to mix and convert different logic level signals.

Threshold adjustments of floating-gate CMOS inverters have been explored in the past by [4] and [5] by moving charge on to and off of the floating-gate through hotelectron injection / Fowler-Nordheim tunneling and UV light conductances respectively. In this scheme static power dissipation can be adjusted on a per path basis using CCFG CMOS and tying all of the nFET biases together and all of the pFET biases together within the path and applying bias voltages accordingly. This incurs a similar, but not nearly as large, problem as having multiple VDDs in that the finer grain the solution the more voltage sources are required. The benefit with CCFG CMOS is that the voltage sources are not constrained locally by well leakage, and simply act as references drawing little to no measurable power and can be routed therefore on a minimally invasive network.

### 3.2 Simulation

The design space for a few simple paths were explored using SPICE. The paths were variations on inverter chains. All of the inverts involved were minimum sized, the paths contained a varying number of stages, and simulations were carried out for standard

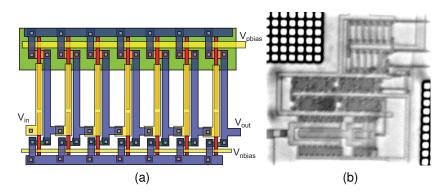

Figure 7. Multiple floating-gate transistor and its abbreviated drawing. One can see how the devices come together to create complex CCFG CMOS gates with local, shared biases.

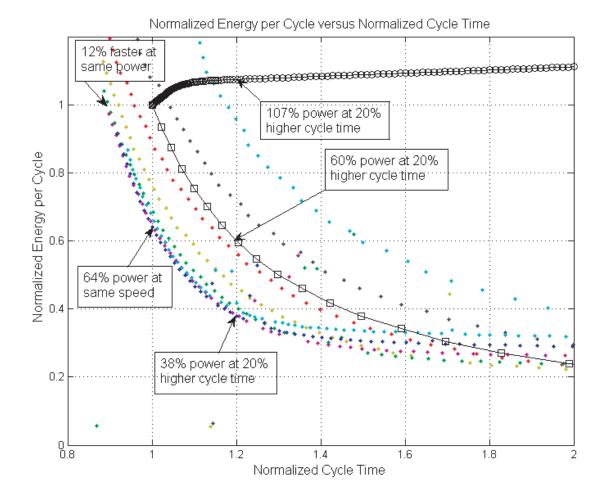

Figure 8. Normalized energy per cycle versus normalized cycle time for various six stage inverter chains simulated with SPICE3F5 using the BSIM3.3 models provided by MOSIS for the TSMC 0.35u process: standard CMOS implementation shown in dense black circles, standard CMOS using DVS shown in sparse black squares, and CCFG CMOS implementations of varying capacitor sizes shown in colors

15

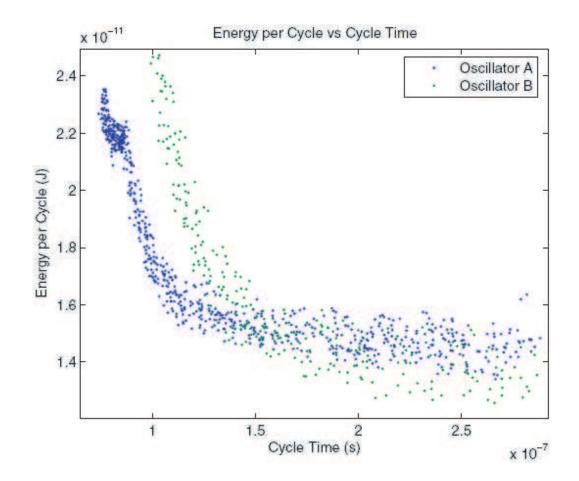

Figure 9. Energy versus cycle time plot for a CCFG CMOS inverter chain that was fabricated in a 0.35*um* process. The two different curves were for two different values of input capacitance for the CCFG inverters, and moving along each curve was done by varying the bias voltages on the coupling lines.

Figure 10. a) Partial layout of the fabricated CCFG CMOS inverter chain. Using a two poly process the common poly1 gate is split and overlapped with a strip of poly2 which becomes the new gate input. The top and the bottom portions of the original poly1 strip are crossed with a horizontal strip of poly2 which spans all of the gates in a path to comprise the bias lines. b)Partial die photograph of the test chip, a CCFG CMOS ring oscillator is in the top right.

CMOS structures with and with out DVS, and CCFG CMOS structures (Figure. 7) of varying capacitive dividers and bias voltages.

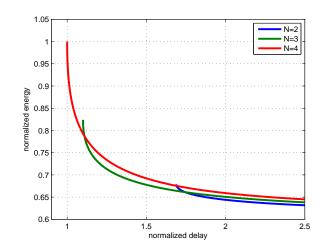

The results for a particular path architecture of six minimum sized inverters in a 0.35*um* (the same process chosen for verification through fabrication) digital process can be seen in Fig. 8. This figure shows energy consumed per cycle (EPC) for various path implementations normalized by the EPC of the standard CMOS implementation running as fast as it can versus the cycle time normalized by the delay of the standard CMOS path.

The densely populated line of black circles represents the standard CMOS case. The data ready was taken at 50% of the rail to rail voltage, and as can be seen the EPC increases rapidly until it settles in a rather linear slope representing only further static power dissipation as the path waits the amount of slack time before switching again. The path populated with sparse black squares represents the same standard CMOS implementation with DVS, which does rather better when slack is introduced. Under a 20% increase in cycle time the standard CMOS case consumes 7% more power and the DVS case consumes 40% less power. In practice, these gains will vary with circuit topology.

Each colored curve represents a CCFG CMOS implementation with different capacitor sizes for  $C_C$  with  $C_B = C_C/10$ , moving curves from left to right represents a decrease in  $C_C$ , while moving along the an individual curve from left to right represents a decrease in bias voltage  $V_{BN}$  with  $V_{BN} = -V_{BP}$ . As can be seen, for the same EPC, a CCFG CMOS implementation can operate 12% faster, or at the same speed a reduction in EPC of 36\% can be achieved. In this case, the CCFG CMOS path really shines when a 20\% increase in slack is introduced, where a 62% reduction in EPC is observed.

#### 3.3 Measurement

A chip was designed to help validate the results of simulation, as well as to further explore the area ramifications of designing with CCFG CMOS. A double-poly process was chosen because it allowed for a very tight layout. A partial layout involving a chain of inverters is shown in Fig. 10a, when layout is done in this manner a minimal amount of area penalty is incurred in implementing low capacitively coupled CCFG CMOS, however, in designing for very fast structures that require higher capacitive coupling of the inputs a larger area penalty will be incurred. CCFG CMOS oscillators were also fabricated using MOSFET capacitors to explore the layout consequences in the absense of a double poly process. Using MOSFETs certainly increases the area overhead but still works. To chips were also also erased by exposure to ultraviolet light to normalize any change that may have accumulated on the floating-gates during fabrication.

In order to get accurate speed measurements the inverter chains were implemented as 13 stage ring oscillators (12 CCFG CMOS inverters and one CCFG CMOS NAND gate) whose output was divided down many times to a reasonable speed to get off chip. A partial photo including a ring oscillator and instrumentation circuitry is shown

18

in Fig. 10b. A few EPC versus cycle time sweeps are shown for two different CCFG CMOS ring oscillators built using double-poly capacitors in Fig. 9. The power dissipation was higher than expected for all floating-gate implementations due to fabrication errors which have been fixed in a new version of the chip that is in fabrication, but the functionality of CCFG CMOS and the trends for the trade offs as expected from theory and simulation are clearly shown.

## CHAPTER 4 LOGICAL POWER

In this chapter, we propose a method to predict power that is compatible with Logical Effort (LE) that we call Logical Power (LP). Logical Power is designed for the characterization of digital CMOS logic gates at the level of hand analysis in order to predict delay and energy consumption. The models for delay and energy presented are naive, first-order, linear predictors that take into account load capacitance while ignoring input slew rate, but are shown to be quite accurate. LE has previously been shown, and LP will be shown, to be greater than 90% accurate versus SPICE simulation for a wide variety of cases. An approximate analytical solution to the optimal inverter chain sizing for minimized energy under constrained non-minimum delay is proposed and shown to be within 2% of optimal when compared to the exact numerical solutions to the LE and LP equations.

#### 4.1 Introduction

*Logical Effort* [6] is a model for unitless approximations for normalized path propagation delay, *d*, for an *N* deep logic chain with last stage load capacitance,  $c_{N+1} = c_L$ , as

$$d = \sum_{i=1}^{N} f_i + p_i = \sum_{i=1}^{N} g_i h_i + p_i = \sum_{i=1}^{N} g_i \frac{b_i c_{i+1}}{c_i} + p_i,$$

(5)

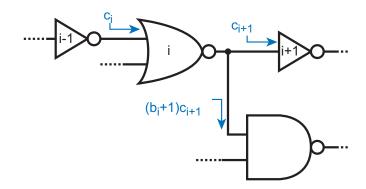

where  $f_i$  is the *effort delay* of the *i*<sup>th</sup> stage in the path associated with the gate driving its load, which is proportional to the ratio of the load capacitance to the input capacitance (called the *electrical effort*) of the driving gate by the gate dependent scalar,  $g_i$ , called the gate's *logical effort*. The *parasitic delay*,  $p_i$ , is the load and gate size independent delay associated with the gate driving its own internal parasitic capacitances. The capacitance coefficient  $c_i$  is the input capacitance to the *i*<sup>th</sup> stage, with  $b_ic_{i+1}$  (see Figure 11) being the total load capacitance seen by the *i*-th stage, and represents the effective

Figure 11. An arbitrary logic path is illustrated. The  $i^{th}$  stage is a two-input nor gate with output load capacitance equal to  $b_i c_{i+1}$ , the load capacitance of the previous stage is equal to the input capacitance of the  $i^{th}$  stage,  $c_i$ .

sizing of the gate- double the size of a gate, double the input capacitance. Absolute path delay is given by  $d_{abs} = \tau d$  where  $\tau$  is the absolute *effort delay* of a minimum sized reference inverter driving a minimum sized reference inverter that sets  $g_{inv} \equiv 1$ .

For the purpose of *Logical Effort* and this chapter, a gate is defined as any digital CMOS configuration of a pull-up network of pFETs and complementary pull-down network of nFETs with a single output and one or many inputs applied only to the MOS-FET gate terminals, where the ratio of any two transistor sizes is fixed. It is important to emphasize that the parameters  $g_i$  and  $p_i$  are simply then gate dependent and are independent of the gate's particular sizing.

The LE formulation of delay is simple. It treats MOSFET capacitances as constant, pull-up and pull-down networks as either open circuits or effective resistancs, and ignores input slew rate. However, it remarkably and consistantly is able to predict the delay of arbitrary logic paths in modern processes to within 10% error, and usually with much higher accuracy. In general, the parameters *logical effort* and *parasitic delay* will be different for a falling and rising transition, as well as being input-gate dependent. One can obtain decent results with average parameters, or can use specific parameters for transition and input.

The real power of LE is that it solves the sizing problem of gates in a path in order to

minimize delay. When the first stage gate is set to be constant and the load capacitance also to be a constant, there then exist N-1 degrees of freedom for sizing choices for the path. There is an exact set of gate sizings that minimizes Equation 5 and the solution is obtained when the *effort delay* of all stages are made equal. This happens when

$$\hat{f} = g_i \frac{b_i c_{i+1}}{c_i} = \left(\prod_{i=1}^N g_i b_i h_i\right)^{\frac{1}{N}} = (GBH)^{(1/N)} = F^{(1/N)},$$

(6)

where  $G = \prod_{i=1}^{N} g_i$ ,  $B = \prod_{i=1}^{N} b_i$ , and  $H = \prod_{i=1}^{N} h_i = \prod_{i=1}^{N} C_{i+1}/C_i = C_{L/C_1}$ . The path effort, *F*, is then independent of the gate sizing choices, and minimum delay is immediately obtained as

$$d_{\min} = NF^{(1/N)} + P \tag{7}$$

where  $P = \sum_{i=1}^{N} p_i$ . Predicting delay and gate sizing for speed is what *Logical Effort* does well, but what LE does not do is identify the energy ramifications of any particular set of gate sizings. The sizing for minimum delay has only one solution, but what about sizing for a target non-minimum delay that minimizes energy? In [7], for instance, *Logical Effort* is applied to various high valency adders, which provides a fast and efficient means of evaluating the delay trade-offs of the different architectures, but provides no insight into the energy trade-offs.

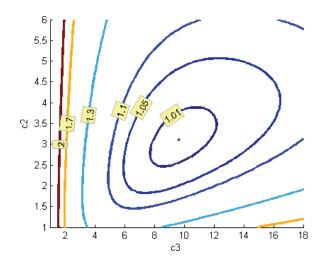

Figure 12 shows constant delay contours using text-book values for the *Logical Effort* parameters for the sizings of the second and third stages for a three-stage logic path of inverters with fixed load and first stage input capacitance as predicted by Equation 5. *Logical Effort* predicts the minimum delay by Equation 7 obtained with the sizings by Equation 6 and this is the point at the center of the graph. For any delay greater than the minimum delay, there are contours of values able to obtain that delay. These contours are of increasing delay as they move outward from that minimum delay point. Delay for each contour is labeled normalized by the minimum delay sizing.

If a path had a timing delay requirement of 5% higher than the minimum delay it

Figure 12. Constant delay contours for  $C_2$  and  $C_3$  of an arbitrary three-stage logic path of inverters with fixed load and first stage capacitance, F = 30. The contours are labeled in normalized delay to that of the minimum delay, with the optimal minimal delay sizing shown as the point in the center.

could obtain, then any point on the 1.05 contour shown would suffice. Moving to the top right in the graph corresponds to greater total capacitance, so perhaps a good choice on the constant delay contour would be the one towards the bottom left as this would trend to a smaller design and less dynamic energy. But to figure out exactly which point minimizes energy, the method of *Logical Effort* needs a compatible energy prediction methodology.

The method of *Logical Effort* is explained in detail in [8]. We show its validity in modern processes as well as go into further detail how to extract its parameters. In [9] *Logical Effort* is applied to cyclic asynchronous control paths, and a similar method for analyzing power is introduced that considers only active power as a result of the dominant parasitic and gate capacitances as a function of sizing, but provides no method for accounting for *static power*, the active power due to intermediate node capacitances, and limits its scope to only scenarios in which the delay of all stages are the same. In [10] the energy-delay trade-offs of sizing individual transistors are explored using the same linear models as in [9], but only heuristics are suggested for the solving the

optimization problem.

This section served as a crash-course in *Logical Effort*, and explained the motivation for *Logical Power*. The rest of this chapter is organized as follows. Section 4.2 derives *Logical Power* as a method to predict path energy as a linear function of the sizing choices of gates in the path. Section 4.4 investigates the validity of the linear predictors of *Logical Effort* and *Logical Power* with a SPICE simulation based methodology, and a means of extracting the gate dependent parameters of the two methods. Section 4.3 details the pencil and paper method of estimating the parameters of *Logical Effort* and addresses the problems of using a similar method for estimating the paremters of *Logical Power*. Section 4.5 provides a statistical analysis of the two methods' abilities to predict power when compared to detailed SPICE simulations of randomly generated logic paths. Section 4.6 applies both methods to the optimization problem of sizing an inverter chain for the minimization of energy under delay constraints and proposes an approximate but analytical solution to the exact sizings required to do so.

#### 4.2 Logical Power

Logical Power is a linear predictor for power designed to be compatibile with Logical Effort- that is, its degrees of freedom are the same and limited to gate sizings. Energy is predicted on a per gate basis, using only these variables, and two new gate-dependent paramters, *active internal* and *static internal*.

The per-cycle energy consumption of the  $i^{th}$  gate is split into its *active* and *static* components as

$$E_i = E_{act,i} + E_{stat,i}$$

The *active energy* is then expressed as the sum of the *dynamic* and *short circuit* energy as

$$E_{act,i} = E_{dyn,i} + E_{sc,i}$$

$$= V_{dd}^2 [c_{out,i} + c_{p,i}] + E_{sc,i}$$

with the first term simply being load capacitances as seen from the gate output of the gate, the second term being internal capacitances, and *short-circuit energy* making up the third term. We define a new parameter,  $a_i$ , to predict the internal active energy of a gate, the amount of dynamic energy consumed by internal capacitances plus the short circuit energy of the gate, which we will refer to as the *active internal* coefficient, defined as

$$a_{i}c_{i} = c_{p,i} + \frac{1}{V_{dd}}Q_{s.c.,i}.$$

(8)

If the right hand side of the above equation scales linearly with input capacitance, we can write the *active energy* as

$$E_{act,i} = V_{dd}^2 [b_i c_{i+1} + a_i c_i],$$

which is a reasonable approximation, as both internal capacitance and short-circuit current should double when a gate's width is doubled when all other factors are held equal (input and output slew rate, for instance). In [11], the authors show that when the input and output slew rates of a gate are the same that *short-circuit power* is a constant scalar multiple of its *dynamic power*, which makes it reasonable to lump the two together using the same coefficient accounting for both, the accuracy of such an approximation relying on circuits to not vary too far from the equal stage delay points.

The static energy is then

$$E_{stat,i} = V_{dd}I_{stat,i}T$$

where  $I_{stat,i}$  is the static current dissipated by the gate and T is the time the gate is static state, which will be assumed to be the cycle time. We define a unitless time constant,  $d_s$ , as

$$d_s = \frac{\tau_s}{\tau} = \frac{V_{dd}C_{inv}}{I_{s,inv}\tau}$$

The process dependent variable,  $\tau_s$ , and its normalized value,  $d_s$ , can be interpreted as the amount of time a minimum sized reference inverter needs to remain in static operation to have its *static energy* equal to its *active energy*. We define a new coefficient to predict *static energy* as a function of input capacitance as

$$s_i = \frac{c_{inv}}{I_{s,inv}} \frac{d}{dc_i} I_{s,i}$$

where  $c_i$  is the gate's input capacitance that varies with its size, and  $c_{inv}$  is the input capacitance for the reference inverter gate.

If the static current scales linearly with input capacitance, we can then represent the *static energy* of the  $i^{th}$  gate as

$$E_{stat,i} = V_{dd}^2 \frac{d}{d_s} s_i c_i$$

where *d* is time normalized per-cycle that the gate remains static, and  $s_i$  is a scaling factor comparing the gate's leakage current divided by input capacitance to that of a reference inverter, and will be called the *static internal* coefficient that takes into account only leakage currents sourced by the gate, not that are dissipated in the gate. That is, for gate's with non-trivial ammounts of gate leakage current, some of the leakage power dissipated in a gate could have been sourced by a previous gate, and we do not want to double count this.

As a matter of convenience, we will use e, which has units of capacitance; consequently, absolute energy is then obtained by multiplying by  $V_{dd}^2$ :

$$E = V_{dd}^2 e$$

The amount of energy dissipated by the *i*<sup>th</sup> stage is then

$$e_i = b_i c_{i+1} + a_i c_i + \frac{d}{d_s} s_i c_i$$

And the contribution of energy dissipation by the entire path due to the size of the  $i^{th}$  stage is then

$$e = (b_{i-1} + a_i + \frac{d}{d_s} s_i)c_i$$

(9)

The total path energy per cycle then becomes

$$e_{path} = c_L + \sum_{i=1}^{N} (b_{i-1} + a_i + \frac{d}{d_s} s_i) c_i$$

(10)

where  $b_0 = 0$  to remove the input capacitance of the first stage out of the energy calculation. The total path energy equation assumes that every gate makes a transition during every cycle. In general, this is not the case, and for completeness a per gate activity factor,  $\alpha_i$ , can be added to all terms associated with *active power*, resulting in

$$e_{path} = \alpha_N c_L + \sum_{i=1}^{N} (\alpha_{i-1} b_{i-1} + \alpha_i a_i + \frac{d}{d_s} s_i) c_i.$$

(11)

#### 4.3 Parameter Estimation

In order to apply these methods, the gate dependent parameters of *Logical Effort* and *Logical Power* must be determined for the logic paths. These parameters are either extracted through simulation (Section 4.4), experimentation, or through topological analysis with simple circuit principles. While simulation and experimentation certainly produce the most accurate parameters, hand analysis methods allow for an intuitive

understanding of how different gate topologies will affect the various parameters. Extracting parameters for *Logical Power* is the topic of this section, and we start from the approximations used in *Logical Effort*.

#### 4.3.1 Logical Effort

For a simple inverter, the pull-up network is a single pFET and the pull-down network a single nFET. The pull-up and pull-down networks source current as functions of their gates,  $v_{in}$ , and drains,  $v_{out}$ . If the input slew rate is ignored and approximated as constant with respect to time, and it is assumed that for rising output transitions the pull-up network does not fight the pull-down network, and vice versa, then the delay of a pullup transition (the time for the output to rise from  $V_{out} = V_1$  to  $V_{out} = V_2$ ) of a gate driving a fixed load can be approximated as

$$\Delta t = C_L \int_{V_1}^{V_2} \frac{1}{I_{pu}(V_o, V_i)} dV_o = C_L R_{pu}$$

where regardless of the shape of  $I_{pu}$  so long as the choices of  $V_1$  and  $V_2$  remain fixed, the value of the integral, the effective resistance over the pull-up transition  $R_{pu}$ , remains valid for varying load capacitances. This approximation is scaled to more complicated pull-up and pull-down networks by ignoring the intermediate node capacitances leaving only the dominant pole of the Elmore delay model caused by the output parasitic and load capacitances. In this approximation, series transistors are treated as a single transistor of length equal to the addition of both original transistor lengths, and parallel combinations leading to an increased effective width.

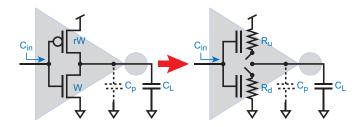

We define a reference inverter in Figure 13, with approximations for the scaling of effective pull-up,  $R_u$ , pull-down,  $R_d$ , resistances, gate input capacitance,  $C_{in}$ , and output parasitic capacitance,  $C_p$  with width are as follows:

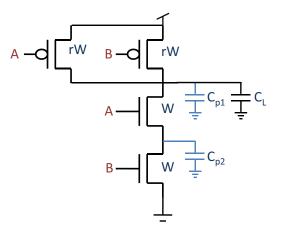

$$R_u = \frac{R_p W_{min}}{W_P} = \frac{R_p W_{min}}{rW}$$

Figure 13. An inverter with pFET width *r* times that of the nFET showing input, output load, and parasitic capacitances is transformed into the pull-up and pull-down networks are replaced with their effective resistances.

$$R_d = \frac{R_n W_{min}}{W_N} = \frac{R_n W_{min}}{W}$$

$$C_{in} = \frac{C_{fet}}{W_{min}}(1+r)W$$

$$C_p = \frac{xC_{fet}}{W_{min}}(1+r)W$$

where  $R_P$  and  $R_N$  are the effective resistances of a minimum sized pFET and nFET respectively, and  $C_{fet}$  is the input capacitance of a minimum sized pFET or nFET (assumed to be relatively equal for both), and x is some scalar relating parasitic capacitance to gate capacitance.

Propagation delay is then modeled as some effect pull-op or pull-down resistance multiplied by the the total capacitance seen at the outout (load capacitance plus internal capacitance), so the pull-down propagation time is given by

$$d_d = R_d(C_p + C_{out})$$

=  $\frac{R_n W_{min}}{W} [\frac{x C_{fet}}{W_{min}} (1 + r) W + C_{out}]$

=  $\frac{R_n W_{min}}{W} C_{out} + x R_n C_{fet} (1 + r)$

The first term is the part of the delay that scales with output capacitance and inversely with gate width, and the second term is independent of both capacitance and gate size. Transforming this equation into the form of Logical Effort results in

$$d_d = \tau(g_{inv}\frac{C_{out}}{C_{in}} + p_{inv})$$

Comparing these two equations, it becomes clear that the first term is the *electrical effort* and the second term the *parasitic delay*. Equating these terms results in

$$\tau g_{inv} \frac{C_{out}}{C_{in}} = \frac{R_n W_{min}}{W} C_{out}$$

$$= R_n C_{fet} (1+r) \frac{C_{out}}{C_{in}}$$

where  $g_{inv} \equiv 1$  and  $\tau = R_n C_{fet}(1 + r)$ .

We define the *logical effort* of a reference inverter to be equal to one. The *Logical Effort* of any other gate is then approximated as the ratio of its driving strength multiplied by its input capacitance and the driving strength and input capacitance of the reference inverter:

$$g = \frac{RC_{in}}{R_{inv}C_{inv}}$$

(12)

The *parasitic delay* of the reference inverter is

$$p_{inv} = \frac{xR_nC_{fet}(1+r)}{\tau} = x \simeq 1$$

where in most processes *x* is nearly one.

In practice, it is difficult to size for equal rise and fall times, and generally impossible to do so for all possible values of *h*. In general, when the rising and falling *logical efforts*,  $g_r$  and  $g_f$ , are equal, the rising and falling *parasitic delays*,  $p_r$  and  $p_f$ , are not. However, for pedagogical reasons we will assume that a reference inverter is sized for equal rise and fall times and that this leads to r = 2.

Applying the model to an n-input NAND gate (Figure 14) and sizing for equal rise and fall times results in

Figure 14. n-input NAND gate sized for equal rise and fall times.

$$R_u = \frac{2R_n}{W/W_{min}},$$

$$R_d = \frac{nR_n}{(n/2)(W/W_{min})},$$

$$C_{in} = (\frac{n}{2} + 1)C_{fet}\frac{W}{W_{min}},$$

and

$$g = \frac{2R_n(n/2+1)C_{fet}}{R_n 3C_{fet}} = \frac{n+2}{3}$$

In order to estimate simple parasitic delay, we continue with our approximation of ignoring internal parasitic capacitances and consider only those parasitic capacitances at the output that results in

$$\tau p = \frac{2R_n}{W/W_{min}} \frac{(n+n/2)C_{fet}}{W_{min}/W}$$

$$= n3R_nC_{fet}$$

$$= n\tau$$

which is the same result as obtained through the simplest reasonable *parasitic delay* approximation method: for na n-input gate, p = n.

#### 4.3.2 Logical Power

In order to approximate the *active internal* coefficients, we need to get estimates of the parasitic capacitance for the gates. One way to do this is to re-extract from *parasitic delay:*

$$p = \frac{R_d C_p}{\tau}$$

Solving for  $C_p$  and equating to Equation 8 and dropping the *short circuit* term we find that

$$ac_{in} = C_p = \frac{p\tau}{R_d}$$

Solving for *a* and using the normalized equation for the *logical effort* parameter, Equation 12, we arrive at the very simple equation

$$a = \frac{p}{g} \tag{13}$$

When ignoring *short-circuit* power and miscellaneous intermediate parasitic capacitances, the above relationship provides a very simple approximation for our *active internal* coefficient *a* using only *Logical Effort* parameters.

Referencing Figure 15, it can be seen that for a switching A-input, that the intermediate parasitic capacitance,  $C_{p2}$ , remains discharged and should therefore negligibly contribute to active power dissipation, and Equation 13 represents an approximation for the A-input. However, when switching B-input, the intermediate capacitance is charged and discharged. Because in the delay approximation, delay is increased polynomially with the distance a capacitance is from the source of the signal, ignoring intermediate capacitances was justified because a differential amount of capacitance

Figure 15. A two-input nand gate showing load capacitance,  $C_L$ , and various internal parasitic capacitances,  $C_{p1}$  and  $C_{p2}$ .

contributed less to delay the farther away it was from the end of the path of signal propagation. The energy consumed due to intermediate capacitances does not follow this trend, a differential amount of capacitance added anywhere will eventually get charged or discharged by the same amount regardless of location in the signal path and thus contributes equally to energy. Ignoring these intermediate nodes is not a good approximation in the energy case.

Instead of deriving *active internal* parameters from *Logical Effort* parameters, one could always be more thorough and re-extract these from the gate topology and include the internal parasitics. For the B-input of our 2-input NANDE gate this becomes

$$a_{nand2,b} = \frac{5}{2}$$

For an n-input NAND gate and an n-input NOR gate of equal rise and fall time with the assumed above parameters and a switching input of distance y in the transistor stack from the output (y = 1 for the closest input to the output), these become:

$$a_{nand} = \frac{2n(y-1) + 3n}{2+n}$$

(14)

and

$$a_{nor} = \frac{4n(y-1) + 3n}{2n+1} \tag{15}$$

Unfortunately, there do not seem to be any estimation techniques of comparable simplicity for getting the *static internal* coefficients that are appropriate over varying technology nodes. This is due to different mechanisms of leakage being dominant in different processes, and will be explained in further detail in the following section.

#### 4.4 Parameter Extraction

To extract the *Logical Power* and *Logical Effort* parameters, we need to be able to accurately measure the components of power and delay for a given logic gate versus its load capacitance. To do so, we employ the same characterization structure used to extract the parameters for LE.

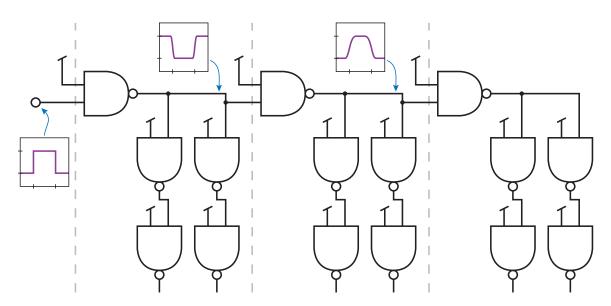

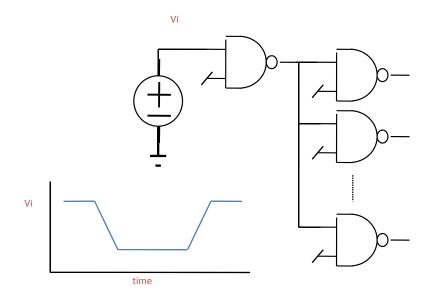

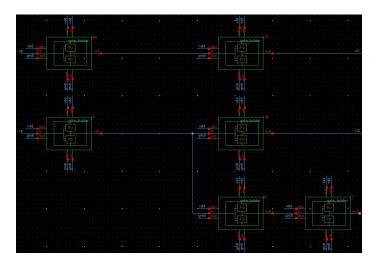

Figure 16 shows the circuit used for gate characterization. It is simply the circuit suggested in chapter 5 of [8]. The circuit comprises multiple chains of gates, where each gate is the same gate to be characterized. The chains are five stages deep. In any chain each stage is subjected to the same *electrical effort* with varying *electrical efforts* between chains by increasing the number of branches at each stage.

A pulse is applied to the first stage and performance is measured on the third stage, the first two stages used to shape the input pulse to something reasonable. Integer values of *electrical effort* are achieved by loading a gate with multiples of itself, each load being loaded to reduce Miller capacitance effects on delay.

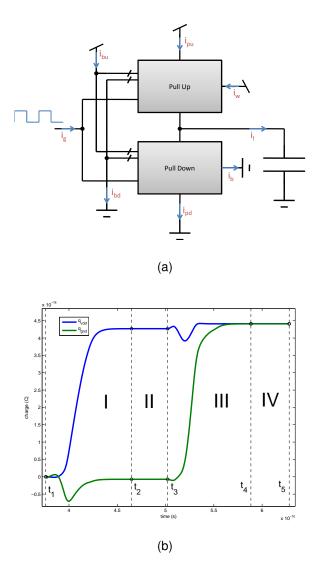

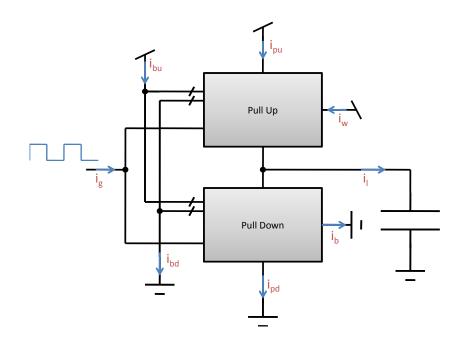

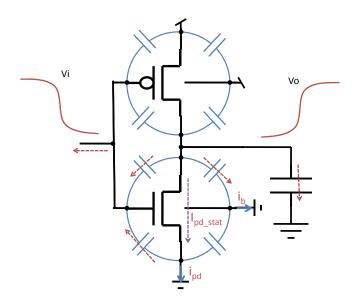

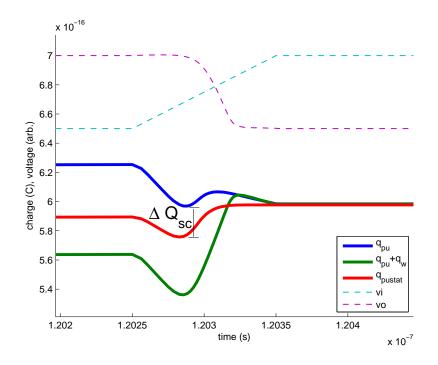

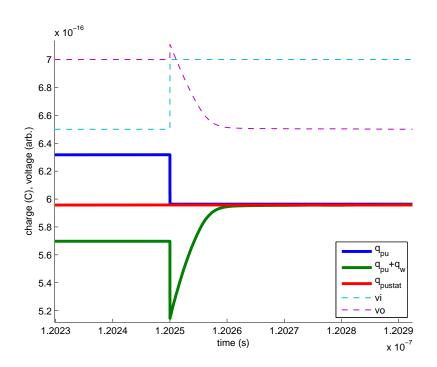

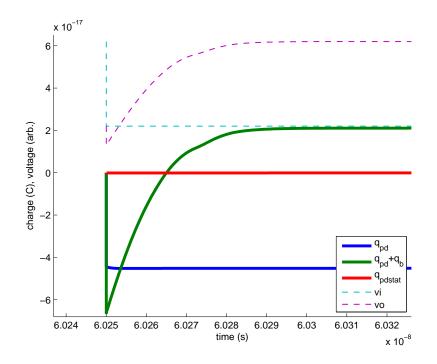

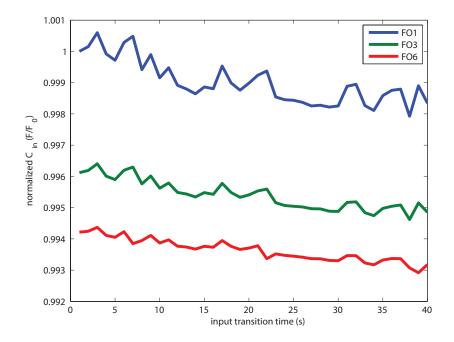

The parameters need to be extracted for each gate in order to use LP. In order to extract the parameters of *Logical Power*, we need a method to accurately measure the components of power for a given gate. To do so, we observe various currents associated with a gate, illustrated in Figure 27:  $I_{pd}$  the current entering the channels of the nFETs of the pull-down network connection to *GND*,  $I_b$  the current entering the

Figure 16. Three stages of the characterization circuit used for parameter extraction.

bulks of these devices,  $I_{pu}$  the current entering the channels of the pFETs in the pull-up network from  $V_{dd}$ ,  $I_w$  the currents entering the wells of these devices,  $I_g$  the current entering the gates of the transitioning input,  $I_{bu}$  the current entering the gates of the non-transitioning inputs that are held high,  $I_{bd}$  the currents entering the gates of the non-transitioning inputs that are held low, and  $I_L$  the current entering the output of the gate. All currents are referenced as positive going into the gate, such that the sum of all of the above currents equals zero. The total currents coming out of the *GND* and *VDD* supplies is then:

$$I_{GND} = I_b + I_{pd} + I_{bd}$$

and

$$I_{VDD} = I_w + I_{pu} + I_{bu}$$

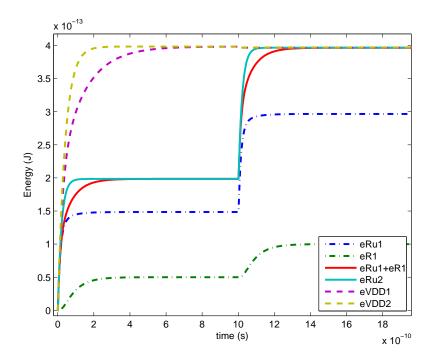

The integrals of current are used to evaluate energy as

$$E = Vq = V \int idt \tag{16}$$

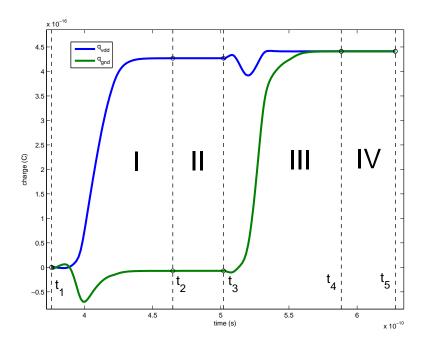

Figure 17. A) an arbitrary CMOS logic gate with pull up and pull down networks and corresponding currents, b) Integrals of current through the *VDD* and *GND* supply nets.

where the integral is taken over a time period that returns the gate to its starting state. This ensures that all flux that enters through the positive terminal of the voltage leaves through the negative terminal with no net flux accumulating in the circuit. That is, that all charge entering the circuit through  $V_{dd}$  leaves through *GND*. All power measurements are done through explicit integration of saved values of currents post simulation, as opposed to using power-meter subcircuits like the one proposed in [12] and used in [13].

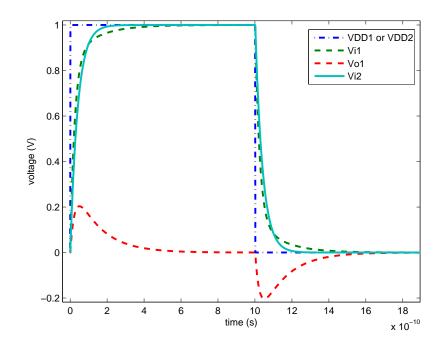

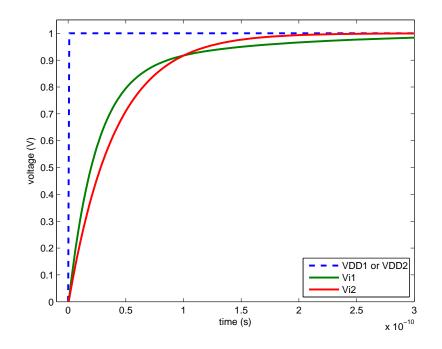

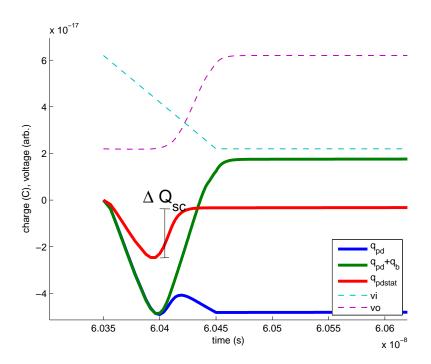

Integrals of  $I_{VDD}$  and  $-I_{GND}$  for a rising then falling transition for an arbitrary inverter in Figure 28. In this plot there are four distinct regions of interest. In Region I there is a significant amount of charge leaving through  $V_{DD}$  corresponding to a rising transition at the output of the gate. This current goes to charging capacitances and thus does not immediately show up through GND network of the gate. Region II is after the rising transition has settled and the gate has entered a static region, with Region III being the falling transition and Region IV the post falling static mode. One can see that after the gate has been restored to its original state does all charge that has entered the circuit leave the circuit.

Active energy is then extracted by integrating this current (either  $i_{vdd}$  or  $i_{gnd}$ , both being equivalent) over Region I and Region III

$$E_{act} = V_{dd} \left[ \int_{t_1}^{t_2} i_{vdd} dt + \int_{t_3}^{t_4} i_{vdd} dt \right]$$

(17)

Effective input capacitance,  $c_{in}$ , is measured as

$$C_{in} = \frac{1}{V_{DD}} \int_{t_1}^{t_2} i_g dt$$

(18)

Assuming that after a rise transition that there is negligible voltage drop across the pull-up network, not all current coming out of  $V_{dd}$  gets dissipated in the target gate as

some of this current leaves into the MOSFET gates of the load where it is then dissipated in the load gates. In order to avoid over-counting we need to consider only the leakage currents in the target gate that have an appreciable voltage drop in that gate. To do so, we measure different currents after different transitions. These transitions for a rise and fall respectively are

$$P_{stat,rise} = V_{DD}(-i_{pd} - i_b - i_g + i_{bu} - i_{bd})$$

and

$$P_{stat,fall} = V_{dd}(i_{pu} + i_w + i_g + i_{bu} - i_{bd})$$

with  $P_{stat}$  being the average of the two.

Figure 18 shows the input voltage and output voltage of a two-input NAND gate (switching the A-input) using the characterization circuit for various *electrical efforts*. The input slew rate changes as all stages in the characterization circuit have the same *electrical effort*. This choice tends to make *Logical Effort* more accurate in the cases where all stages have similar slew rates which is certainly the case for circuits optimized for maximum speed.

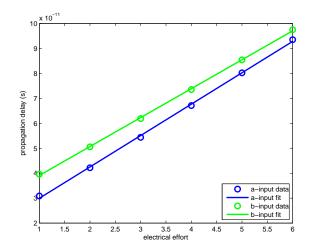

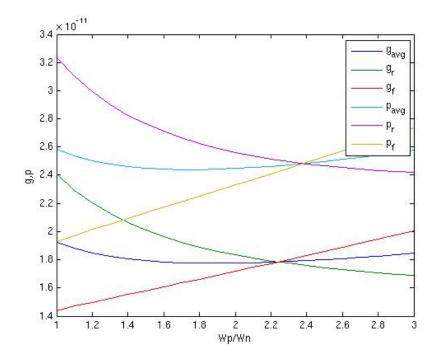

Rising and falling propagation delays are shown in Figure 19, which shows the linear behavior of propagation delay in this range of *electrical efforts*. From this rising, falling, and average *logical efforts* are extracted as

$$g = \frac{1}{\tau} \frac{d}{dh} d_{abs}$$

where  $\tau$  is obtained from a reference inverter where  $g \equiv 1$ . The parasitic delay is

$$p = \frac{d_{abs}|_{h=0}}{\tau}$$

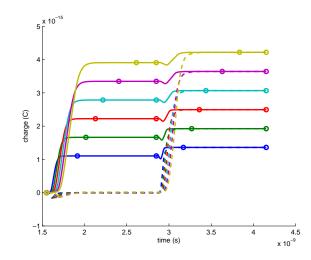

The total charge dissipated in the characterized gate flowing out of the  $V_{dd}$  and

Figure 18. Input and output voltages versus time for input-a of a 2-input NAND gate for various h for a rising output transition.

Figure 19. Average propagation delays versus *h* for for switching either input of a NAND2 gate.

Figure 20. Integrals of  $i_{vdd}$  (solid lines) and  $i_{gnd}$  (dashed lines) versus time for various h for a 2-input NAND gate.

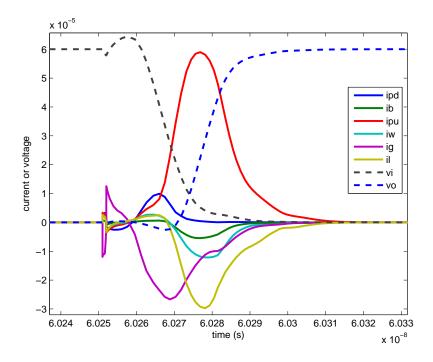

*GND* networks per time is shown in Figure 20 for various *electrical efforts*. The active energy parameter is then extracted from the active energy versus electrical effort plot by the following relationship:

$$a = \frac{E_{act}|_{h=0}}{V_{dd}^2 C_{in}}$$

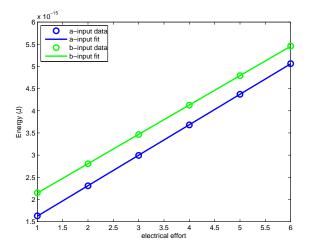

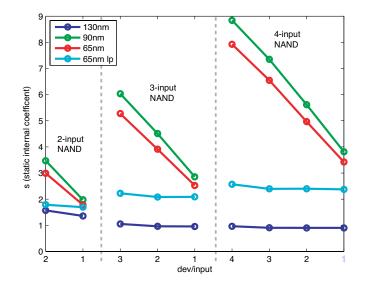

The static current dissipation is dependent on the input vector to any complex gate. The static internal coefficient for each input for multiple gates is shown in Figure 22 as extracted from the following relationship:

$$s_i = \frac{c_{in,inv}}{P_{stat,inv}} \frac{d}{dc_{in,i}} P_{stat,i}$$

This figure shows that the relationship of of how the static internal coefficient changes with input number is very process dependent. The big difference here is that in the 130*nm* and 65*nm* LP models used, gate current is insignificant and not modeled. Because of this, simple relationships can be made for estimating how static internal coefficients will change with gate topology, however, these relationships are going to change depending on the presence of significant gate current or not.

Figure 21. Active Energy versus *h* for switching either input of a NAND2 gate. Since the B-input is farther away from the output, it has to charge and discharge extra parasitic capacitance for this transition.

Figure 22. Leakage current for a 2-input, 3-input, and 4-input nand gate after a rise or fall transition. The x-axis corresponds to different sized nand gates and different inputs within the nand gates, from left to right: y=2 down to 1 for a 2-nand, y=3 down to 1 3-nand, y=4 down to 1 4-nand.

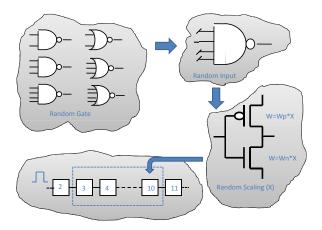

Figure 23. Randomly generated test circuit. A pool of 2 to 4 input NANDs and NORs and inverters of random sizes (1 to 8x) are chosen to comprise the 12 stage circuit. Propagation delay and energy consumption of the 3rd to 10th stage are measured in simulation and predicted with LE and LP.

### 4.5 Statistical Path Analysis

The accuracy of the *logical power* method was verified through a test circuit of random gate types. The test circuit was a 12 stage logic path composed of two to four input NANDs and NORs as well as inverters all scaled to random sizes between 1 and 8x minimum size, as illustrated in Figure 23. This structure of test circuit was chosen because each gate has an activity factor of  $\alpha_i = 1$ . The most trivial of circuits have this property, and the individual activity factors are dependent on circuit topology and input vector. This circuit was chosen to evaluate the effectiveness of *logical power* in the limit of perfect knowledge of activity factor, as the method itself is independent of whatever system one uses to predict an activity factor.

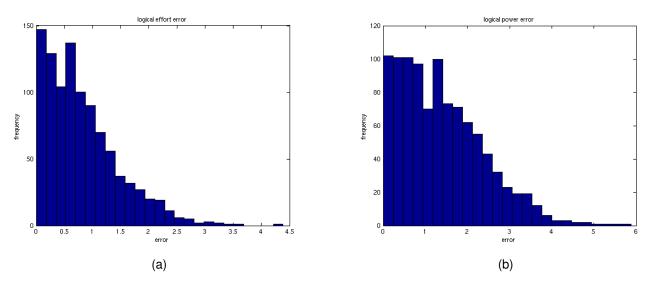

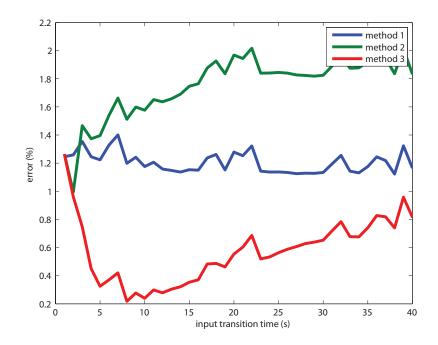

Propagation delay and total power was measured from the 3rd through the 10th stage, as well as predicted by LP and LE and the results were compared. Out of 1000 randomly generated circuits, LE had an average error of 0.8% while *logical power* an error of 1.6% with a worst case of 5%. Histograms of these data are shown in Figures 24b and 24a.

Figure 24. a) LE Error mean 0.8%, b) Logical Power error mean 1.6%

|         | 0              |               |            |            |

|---------|----------------|---------------|------------|------------|

| Tech    | Mean Error (%) | Max Error (%) | Active (%) | Static (%) |

| 130nm   | 0.7            | 4.5           | 99         | 1          |

| 90nm    | 5.3            | 10.2          | 84         | 16         |

| 65nm LP | 10.4           | 18.4          | 99         | 1          |

| 65nm SF | 6.0            | 9.5           | 77         | 23         |

Table 1. Statistical results for Logical Power

Table 1 shows this same experiment for various processes from 65nm to 130nm as well as a breakdown for each process what percent of total power was *active power*. The best result was a 0.7% mean error from the 130nm process and the worst was a 10% mean error from the 65nm low power process.

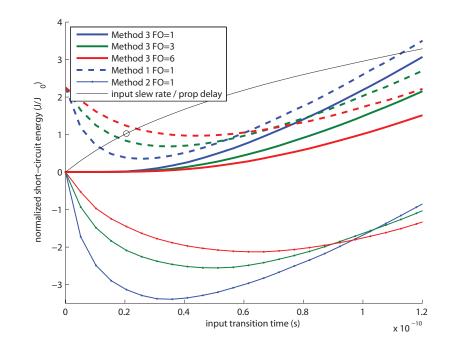

# 4.6 Hand Optimization of Inverter Chain

Unfortunately, there appears to be no analytical solution to the non-linear programming problem for gate sizings to minimize energy as specified by the *Logical Power* Equation 11 under the constraint of meeting a target delay specified by the *Logical Effort* Equation 5. These equations can be solved numerically by a method that will be referred

to as the optimal sizing method. In this section, we present an approximation to this solution for the optimization of inverter chains.

Consider an inverter chain of depth *N* with input driving capacitance  $c_1 = c_{inv}$  and load  $c_{N+1} = xc_{inv}$ , in order to calcualte the Pareto points in the energy delay space, we start with the *LE* optimized delay as the minimum delay, maximum energy point (any solution with higher energy than this would use different sizings, and thus be slower), and then increase this delay with a method that decreases energy. We choose to increase the delay of the final stage by decreasing its input capacitance, while keeping all intermediate stage delays the same, which we refer to as the constant intermediate delay method. This method fixes *electrical effort* (through subseqent decreases in their input capacitances in order to maintain constant *electrical effort*) up until the first stage, where delay must decrease.

To gain insight into this method, consider the differential amount of gate stage energy saved when that stage's delay is increased by decreasing its input capacitance, which is given by

$$\frac{dE_i}{df_i} = -(b_{i+1} + a_i)g_ic_{i+1}f_i^{-2}$$

(19)

This is obtained by plugging the equation for *effort delay* into Equation 9, which describes energy consumed by the entire path due to the *i*<sup>th</sup> stage's input capacitance. Only *effort delay* is considered as parasitic delay remains invariant under sizing choices. This equation assumes that *static power* is negligible, which is true only for  $d \ll d_s$ .

It is clear that if a differential amount of delay is to be introduced to any one stage, that for for the case of an optimally sized inverter chain with monotonically increasing stage capacitances (always true for H > 1) that the greatest amount of energy savings per incremental delay is obtained when this delay is introduced into the last stage. Keeping in mind that we desire to introduce delay only to the  $N^{th}$  stage, but a decrease in  $C_N$  will lead to a decrease in  $h_{N-1}$  which in order to return  $f_i = \hat{f}$ ,  $c_{N-1}$  will also have to decrease. Which in order to keep  $f_2$  through  $f_{N-1}$  all equal to  $\hat{f}$ , all intermediate stages will have to have their input capacitances reduced leading to even further energy savings. While this method does not exactly minimize energy as a function of delay, it does come very close and has an analytical solution for the required stage sizings.

Starting with the sizings necessary for minimum delay, we obtain an optimal stage *effort delay* of  $\hat{f}$ , such that all stage efforts  $f_i = \hat{f}$ :

$$f_i = \hat{f} = g_i \frac{b_i c_{i+1}}{c_i}$$

and

$$d_{min} = N\hat{f} + P$$

We then increase the delay of the last stage by decreasing  $C_N$  from its optimal, while all middle stages are sized such that their *effort delays* remain unchanged, this is propagated back to the initial stage whose delay must naturally increase a big as  $c_2$ decreases without  $c_1$  decreasing:

$$d = g_1 b_1 \frac{c_2}{c_1} + (N - 2)\hat{f} + g_N b_N \frac{c_L}{c_N} + P$$

(20)

Which considering the target application of an inverter chain, this reduces to

$$d = \frac{c_2}{c_{inv}} + (N-2)x^{\frac{1}{N}} + \frac{xc_{inv}}{c_N} + N$$

(21)

$c_2$  and  $c_N$  are not independent, but are related through recursive application of Equation 6 to the intermediate stages:

$$c_N = c_2 \frac{\hat{f}^{N-2}}{\prod_{i=2}^N g_i b_i}$$

Which for an inverter chain reduces to, keeping in mind that  $\hat{f}$  simplifies to  $x^{1/N}$  and that all parameters like *logical effort* and *branching effort* are one in this case,

$$c_N = c_2 x^{1 - \frac{2}{N}}$$

Plugging this into Equation 21 and applying the quadratic formula,  $c_2$  can be solved for for any desired delay as:

$$c_2 = \frac{c_{inv}}{2} \left\{ d - N - (N - 2)x^{\frac{1}{N}} \right\}$$

(22)

$$\pm \sqrt{[(N-2)x^{\frac{1}{N}} - d + N]^2 - 4x^{\frac{2}{N}}}$$

(23)

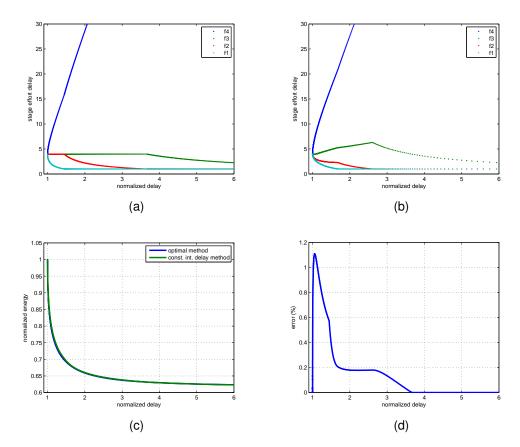

This method is applied to a four stage buffer chain of inverters driving a fixed load with fixed 1st stage size. Figure 25a shows stage *effort delays* versus target delay for sizings picked by Equation 22, the constant intermediate stage delay method. The middle stages stay at a fixed *effort delay* of  $\hat{f}$  until sizings hit minimum sized. Figure 25b shows the same buf for sizings picked by the optimal sizing method. Figure 25c shows the energy versus delay curves of the two different methods. Each point on the curve represents a different cycle energy and cycle delay time obtained different gate sizings. The constant intermediate delay method comes very close to the performance obtained by the optimal method, the error in energy between the two methods is shown in Figure 25d, and in this scenario it is shown that it produces energies around 1% of optimal. The difference is due to the incremental savings in capacitance when delay is allowed to increase. Since energy savings decrease with  $1/f^2$ , the optimal method distributes marginal portions of the increase in delay to many stages and is able to save a little more energy than the constant intermediate delay method.

The optimal sizing method is applied to various stage length inverter chains driving a fixed load with F = 250, and the energy delay curves are shown in Figure 26. Stage lengths of 2, 3 and 4 are shown. For this particular *path effort* an appropriately sized N = 4 chain minimizes delay, with more or less stages leading to an increase in minimum obtainable speed. Interestingly at speeds less than minimum, depending

Figure 25. Stage *effort delays* of a four stage inverter chain (F = 250) versus target delay. a) Sizings picked via Equation 22. The middle stages stay at fixed *effort delay* of  $\hat{f}$  until sizings hit minimum sized. b) Sizings picked by numerically solving Equation 5 and Equation 11 c) the energy-delay curves obtained by both methods, and d) the error in the approximation method (a) from ideal (b).

Figure 26. Energy-delay points obtained by different gate stage sizing choices of various inverter chains of different depths driving a fixed load with path effort F=250. All points shown are pareto-points in the sizing space in terms of energy and delay for their respective chains. N=4 produces the fasted possible speed for this particular path effort, but at speeds less than minimum, depending on the actual target delay, energy is minimized by choosing not only the right sizing options but the right number of stages. In particular, there are some scenarios in which a higher number of stages can minimize energy for a target delay obtainable with less stages.

on the actual target delay, energy is minimized by choosing not only the right sizing options but the right number of stages. In particular, there are some scenarios in which a higher number of stages can minimize energy for a target delay obtainable with fewer stages.

# 4.7 Conclusion

The method of *Logical Effort* is extended to allow for energy delay tradeoffs by *Logical Power*. This new method requires two new gate dependent parameters, *active internal* and *static internal*, and uses gate sizing as the only variable, ignoring all sorts of higher order effects including input slew rate, and is intended for hand analysis for gate circuit topologies and logic paths. Nevertheless, it is hown to be accurate to within 10% error when compared to detailed SPICE simulations across many technologies, and is usually much more accurate than that.

A hand analysis method for approximating one of the new parameters, *active internal*, is presented using many of the same approximations that *Logical Effort* uses to estimate its gate dependent parameters. This method ends up being about as accurate as approximation methods for estimating *logical effort* and is significantly better than those used to approximate *parasitic delay*. Approximating the *static internal* coefficient is difficult as different leakage mechanisms dominate in different technologies.

A method is suggested that approximates the optimal sizing problem for minimizing energy under constrained delay. This method solves analytically for the stage sizes and produces energy delay tradeoffs within 1.2% of optimal in the test case it was applied to.

#### **CHAPTER 5**

#### **MEASURING SHORT-CIRCUIT POWER**

In this chapter, A new method for accurately measuring short-circuit power dissipation of simulated CMOS digital gates is presented. Previous methods have had difficulty in differentiating between dynamic and short-circuit currents in the "turning off" network during an active transition. This new method naturally converges on zero short-circuit energy for infinitely fast switching inputs and outputs and never produces negative answers for short-circuit energy- things previous methods have had difficulty with.

#### 5.1 Components of Power

Power dissipated in a logic gate is a complicated function of the gate's implementation and its environment. The logic family, transistor topology, transistor sizings, and rail voltages that all define a gate are only part of the picture. The load that the gate drives, and transient inputs all factor into the power a gate will dissipate over time.

The power dissipated by the gate can be broken down into three well defined components: *dynamic power, static power,* and *short-circuit power.* Dynamic power is simply defined as the amount of power consumed by charging and discharging capacitances seen by the logic gate and can be expressed as:

$$P_{dyn} = \alpha f V_{dd}^2 C_{tot} \tag{24}$$

Where  $\alpha$  is the activity-factor defining the fraction of the cycles that the logic gate makes an output transition, *f* the cycle frequency,  $V_{dd}$  the rail-to-rail voltage, and  $C_{tot}$  the total amount of capacitance seen by the driving gate.

Whereas *dynamic power* is dissipated during an output transition, *static power* is the power consumed when the gate is not making a transition and is a simple function of the static current draw  $I_{stat}$ :

$$P_{stat} = V_{dd} I_{stat} \tag{25}$$

The last portion of power, *short-circuit* power, is defined as the portion of power consumed during an output transition that did not go to charging capacitances. This portion of power is quite difficult to express compactly, and for even the most trivial of logic gates, an inverter, has no closed-form analytical solution. Most approximations are extremely cumbersome. *Short-circuit power*, is a function of input slew rate, output slew rate, and gate topology.

#### 5.2 Measuring Active Power

In order to extract the parameters of *Logical Power*, we need a method to accurately measure the components of power for a given gate. To do so we observe various currents associated with a gate, illustrated in figure 27:

$$I_{GND} = I_b + I_{pd} + I_{bd} \tag{26}$$

and

$$I_{VDD} = I_w + I_{pu} + I_{bu} \tag{27}$$

where  $I_{GND}$  is the total amount of current supplied by the GND rail, whose components are  $I_b$ ,  $I_{pd}$ ,  $I_{bd}$  being the currents leaving the bulk, pull down network, and any logic level zero bias applied to the circuit respectively.  $I_{VDD}$  being the  $V_{dd}$  rail equivalent.

The integrals of current are used to evaluate energy in:

$$E = Vq = V \int idt \tag{28}$$

where the integral is taken over a time period that returns the gate to its starting state. This ensures that all flux that enters through the positive terminal of the voltage leaves

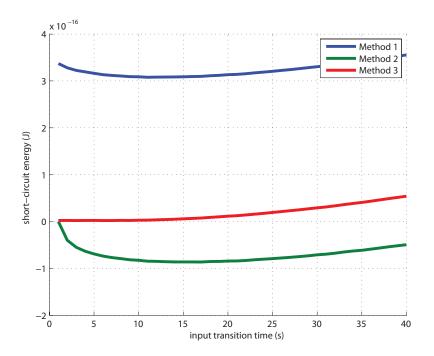

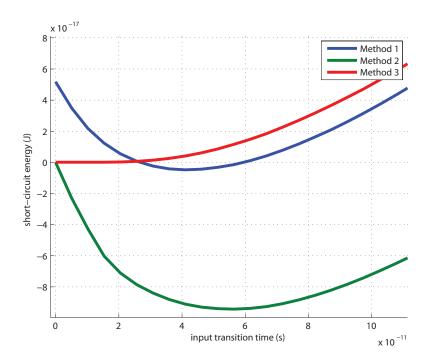

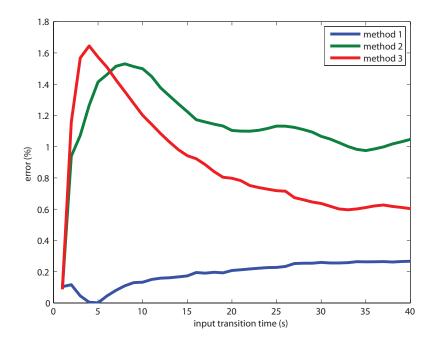

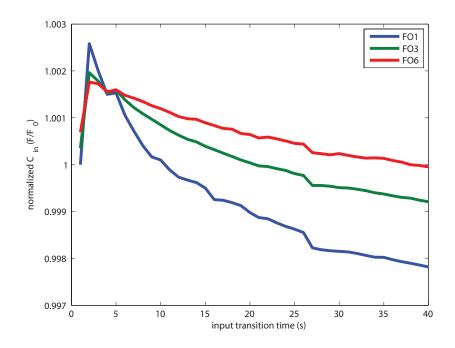

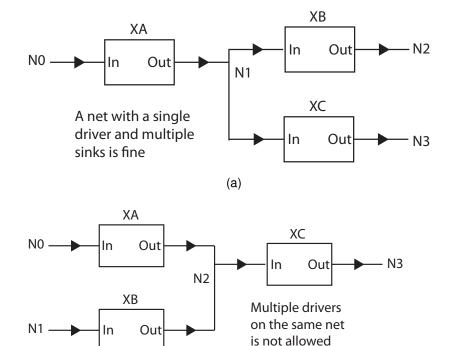

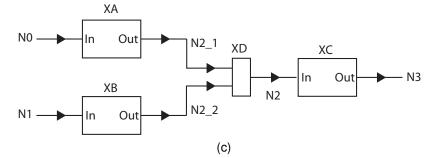

Figure 27. An arbitrary CMOS logic gate with pull up and pull down networks and corresponding currents.