# INTEGRATED FRONT-END ANALOG CIRCUITS FOR MEMS SENSORS IN ULTRASOUND IMAGING AND OPTICAL GRATING BASED MICROPHONE

A Dissertation Presented to The Academic Faculty

By

Muhammad Shakeel Qureshi

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology August 2009

Copyright © 2009 by Muhammad Shakeel Qureshi

# INTEGRATED FRONT-END ANALOG CIRCUITS FOR MEMS SENSORS IN ULTRASOUND IMAGING AND OPTICAL GRATING BASED MICROPHONE

Approved by:

Dr. Paul E. Hasler, Advisor Professor, School of ECE Georgia Institute of Technology Atlanta, GA

Dr. Farrokh Ayazi Professor, School of ECE Georgia Institute of Technology Atlanta, GA

Dr. David V. Anderson Professor, School of ECE Georgia Institute of Technology Atlanta, GA Dr. F. L. Degertekin, Advisor Professor, School of ME Georgia Institute of Technology Atlanta, GA

Dr. Oliver Brand Professor, School of ECE Georgia Institute of Technology Atlanta, GA

Dr. Peter Hesketh Professor, School of ME Georgia Institute of Technology Atlanta, GA

Date Approved: April 2009

# **DEDICATION**

To my loving family ...

## ACKNOWLEDGMENTS

First of all, I am thankful to God for giving me the strength to pursue graduate school and survive Georgia Tech's rigorous academic program. I like to express my sincere gratitude to everyone who supported and helped me during this long journey. Without them, I would not have made it this far. I have been very fortunate to work with Dr. Levent Degertekin and Dr. Paul Hasler, both as my co-advisors. I appreciate the time and effort they have put into my thesis work along with my committee members, Dr. Farrokh Ayazi, Dr. Oliver Brand, Dr. David Anderson and Dr. Peter Hesketh. Their dedication to students is inspiring, and I am proud to be a branch on the Degertekin and Hasler family tree.

I give special thanks to professor Alvin Connelly who brought me to Georgia Tech as a Texas Instrument Fellow. I still remember the very first conversation I had with him over phone when I was deciding which school should I pick for graduate studies. Thanks to Dr. Connelly, I have never regretted my decision of coming to Georgia Tech Analog Circuit's program.

I had the great fortune to work on my Master's degree with Dr. Phil Allen. He has been a great source of inspiration to me. He helped me try different areas of research and get my hands dirty with a wide range of topics. He really prepared me for the graduate research that I was about to embark on during my years as a PhD student. Since his retirement, I have always missed his presence.

I believe that for every student in higher education, there is a key person who set's student's future path. In my case, Dr. Jeff Jessing has that distinction. During my undergraduate studies, I had the pleasure to take micro-electronics classes taught by him at Texas A and M University. With his dedication to teaching, he was able to implant the desire in me for taking the non-traditional path in Analog Circuits, in those days when digital was the buzz word. During my graduate days at Georgia Tech, I had the opportunity to work in three research groups. I started as a rookie in Analog Circuits and Signal Processing group. I am thankful to all the colleagues who sparked my interest to stick around for a PhD. My research involved collaboration between MEMS group MiST in Mechanical Engineering and circuit's group CADSP in Electrical Engineering. Through these collaborations, I gained a lot of knowledge that was simply now possible without them. I am in particularly thankful to Dr. Wook Lee, Dr. Neal Hall, Caesar Garcia and Baris Bicen for collaboration on hearing aid project. I was very fortunate to work with Arindam Basu and Dr. Sheng-Yu Peng on the circuits side of things. They had the major contribution to my research work. For the MEMS side, I like to thank Jaime Zahorian and Dr. Rasim Guldiken for spending countless hours in the cleanroom for fabricating CMUT on CMOS.

I am grateful to Texas Instruments for awarding me Master's Analog Fellowship at Georgia Tech. Ron Cox at Texas Instruments was instrumental in introducing me to Georgia Tech's Analog program. Special thanks to Dr. John Bordelon who kept things smooth with my collaborators at Texas Instruments.

To my friends, I thank you for your understanding and support throughout my PhD. My friends from Dhahran, College Station, Atlanta and the Bay Area, have been a key contributor to my studies through out these long years. I thank my officemates for having all sort of discussions that had no direct contribution to the research work, but made the days bearable for so many years. They made my stay pleasant while at school.

Finally to my loving family who has always been there for me regardless what ever path I have taken in life. You all have been asking me "how much longer?" for so many years and now I have an answer. I am grateful to my mother(late) and father for their investment and belief in me. They have supported me through out my studies. I can not imagine to be standing where I am right now, without their support and prayers. I have been fortunate to spend so many holidays with my sister and brother-inlaw in Washington DC. They truly made DC, a home in US for me. There are no words that can express my feelings and

appreciation for them. Last but not least, to my wife Sehar who has been an equal partner in this journey. Your love inspired me through these years. For even my dreams were not as breathtaking as this life came to be with you. Thank you.

# TABLE OF CONTENTS

| ACKNO   | WLEDGMENTS                                                   | iv  |

|---------|--------------------------------------------------------------|-----|

| LIST OF | TABLES                                                       | ix  |

| LIST OF | FIGURES                                                      | X   |

| SUMMA   | <b>RY</b>                                                    | xiv |

| CHAPT   | ER 1 ANALOG INTERFACE FOR MEMS SENSORS                       | 1   |

| 1.1     | Capacitive Micromachined Ultrasound Transducers              | 2   |

|         | 1.1.1 Intra-vascular Ultrasound Imaging                      | 2   |

|         | 1.1.2 Capacitive Micromachined Ultrasound Transducer         | 3   |

|         | 1.1.3 Challenges in Capacitive Sensing and IVUS imaging      | 3   |

| 1.2     | Diffraction Grating Optical Microphone                       | 5   |

| 1.3     | Low Power and Low Voltage Design                             | 6   |

|         | 1.3.1 Total Harmonic Distortion (THD)                        | 7   |

|         | 1.3.2 Rail-to-rail Input Stages                              | 8   |

|         | 1.3.3 Tobi Element                                           | 11  |

| CHAPT   | ER 2 CHARGE AMPLIFIER FOR CAPACITIVE SENSING                 | 13  |

| 2.1     | Analysis of Capacitive Sensing Charge Amplifier              | 13  |

| 2.2     | Charge Amplifier with Charge Adaptation Feedback             | 14  |

|         | 2.2.1 Design Procedure                                       | 16  |

|         | 2.2.2 Setup And Measurement Results                          | 17  |

|         | 2.2.3 Pulse-Echo Experiment and Results                      | 19  |

|         | 2.2.4 Comparison                                             | 21  |

| 2.3     | CMOS-FIRST MEMS Integration for CMUTs                        | 23  |

|         | 2.3.1 Pulse Echo Results                                     | 26  |

| CHAPT   | ER 3 ANALOG FRONT-END FOR BIOMIMETIC MICROPHONE .            | 28  |

| 3.1     | Diffraction Based Optical Detection Method                   | 29  |

| 3.2     | Integration of Optical Displacement Detection and Challenges | 31  |

| 3.3     | Optical MEMS Microphone Receiver Architecture                | 32  |

| 3.4     | VCSEL Driver in Standard CMOS                                | 33  |

|         | 3.4.1 VCSEL Driver Design                                    | 34  |

|         | 3.4.2 VCSEL Driver Measurements                              | 35  |

|         | 3.4.3 Experimental Data and Discussion                       | 36  |

| 3.5     | CMOS PN Junction Photodiode                                  | 37  |

| 3.6     | On-chip CMOS Filter                                          | 46  |

|         | 3.6.1 Band Pass CMOS Filter                                  | 47  |

|         | 3.6.2 Low Pass CMOS Filter                                   | 51  |

| 3.7     | AM Demodulators                                              | 51  |

|        | 3.7.1 Synchronous Detector                           |

|--------|------------------------------------------------------|

|        | 3.7.2 Track and Hold without Bandpass                |

|        | 3.7.3 Track and Hold with Bandpass                   |

|        | 3.7.4 Envelope Detector                              |

|        | 3.7.5 Envelope detector without bandpass             |

|        | 3.7.6 Envelope detector with bandpass                |

|        | 3.7.7 Continuous Mode VCSEL Receiver                 |

| 3.8    | Receiver comparison                                  |

| ~~~    |                                                      |

| СНАРТІ |                                                      |

| 4.1    | Sigma-Delta Analog-to-Digital Converter              |

|        | 4.1.1 First Order 1-bit Sigma-Delta                  |

|        | 4.1.2 Higher Order 1-bit Sigma-Delta                 |

| 4.2    | Measurements                                         |

| 4.3    | Comparison                                           |

| СНАРТІ | ER 5 CONCLUSION                                      |

| 5.1    | Main Contributions                                   |

| 5.2    | Future Directions       92                           |

| 5.2    |                                                      |

| APPEND | DIX A LIST OF ICS FOR CMOS-FIRST CMUT INTEGRATION 94 |

| APPEND | DIX B LIST OF ICS FOR OPTICAL GRATING MICROPHONE 93  |

| REFERE | ENCES                                                |

| алта   |                                                      |

# LIST OF TABLES

| Table 2.1 | Performance Comparison                                   | 21 |

|-----------|----------------------------------------------------------|----|

| Table 2.2 | Typical CMUT Parameters for CMUT on CMOS approach        | 25 |

| Table 3.1 | Specifications for Lasermate VCSEL (VCC-85A1G-IS)        | 36 |

| Table 3.2 | Specifications for Photodiode Amplifier (Thorlab PDA36A) | 36 |

| Table 3.3 | VCSEL current consumption with varying duty cycle        | 36 |

| Table 3.4 | Photodiode Parameters and Measurement Results            | 42 |

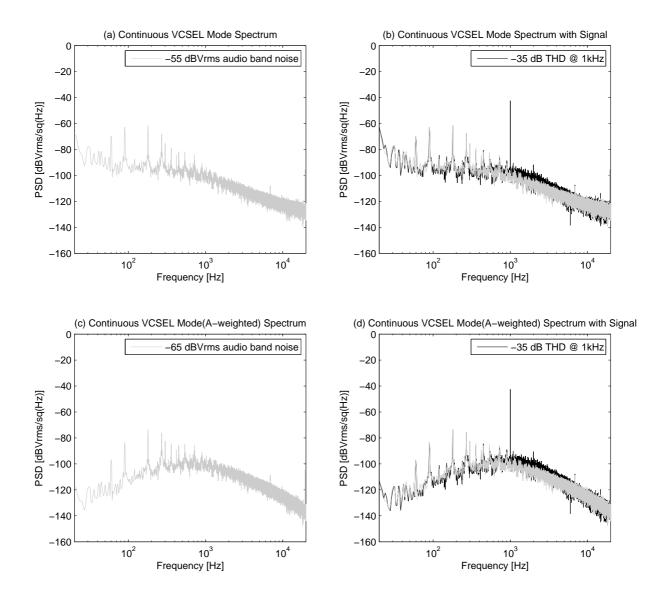

| Table 3.5 | Measurement results of continuous mode VCSEL receiver    | 77 |

| Table 3.6 | Receiver Comparison                                      | 80 |

| Table 3.7 | Total Harmonic Distortion @ 1kHz 100mV input             | 81 |

| Table 3.8 | Analog Receiver Comparison                               | 81 |

| Table 4.1 | Digital Hearing Aid Comparison                           | 89 |

# LIST OF FIGURES

| Figure 1.1  | 1 Cross sectional view of Capacitive Micromachined Ultrasound Trans<br>ducer (CMUT).                                                 |    |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| Figure 1.2  | Schematic diagram of the IVUS catheter with integrated front-end electronics.                                                        | 4  |  |  |

| Figure 1.3  | Schematic diagram of a micromachined acoustic sensor with a built in phase-sensitive diffraction grating for displacement detection. | 5  |  |  |

| Figure 1.4  | Diffraction efficiencies of the zero, first, and third orders                                                                        | 6  |  |  |

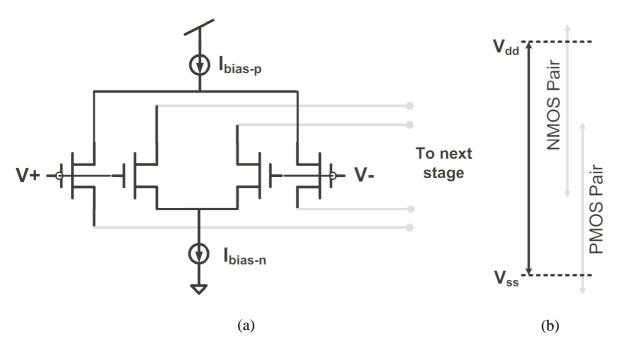

| Figure 1.5  | Rail-to-rail input stage.                                                                                                            | 9  |  |  |

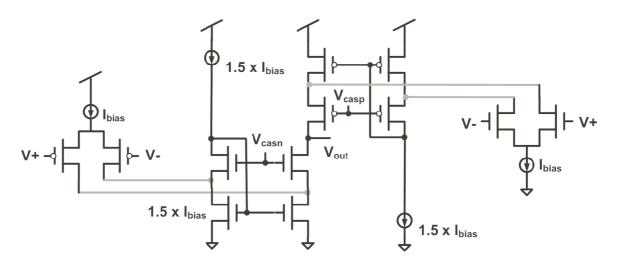

| Figure 1.6  | Complementary input rail-to-rail folded cascode amplifier                                                                            | 10 |  |  |

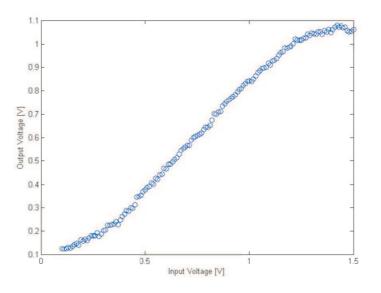

| Figure 1.7  | ICMR measurement for rail-to-rail input.                                                                                             | 10 |  |  |

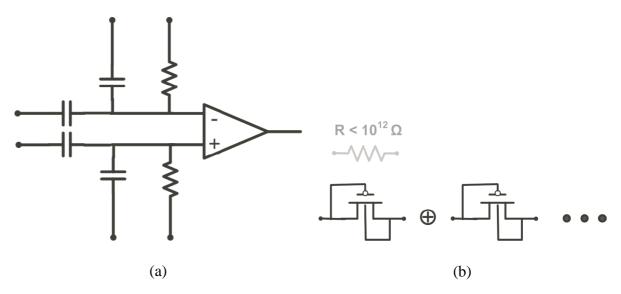

| Figure 1.8  | Wide Linear Range Technique.                                                                                                         | 11 |  |  |

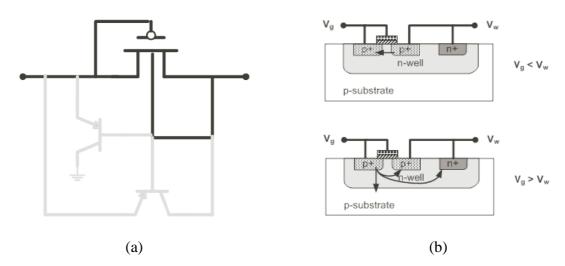

| Figure 1.9  | Tobi element with cross-sectional view.                                                                                              | 11 |  |  |

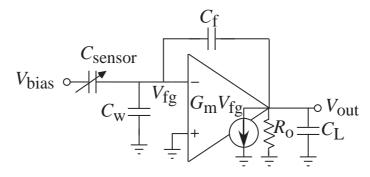

| Figure 2.1  | Schematics of the small-signal model of capacitive sensing charge amplifier.                                                         | 14 |  |  |

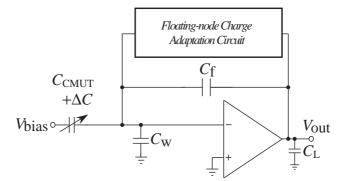

| Figure 2.2  | Illustration of a charge amplifier and a floating-gate based charge adap-<br>tation circuit for capacitive sensing.                  | 14 |  |  |

| Figure 2.3  | Small-signal model of a charge amplifier with charge adaptation feed-<br>back and its frequency response.                            | 15 |  |  |

| Figure 2.4  | Conventional approaches to CMUT sensing                                                                                              | 16 |  |  |

| Figure 2.5  | Setup of capacitive sensing measurement using a capacitive feedback charge amplifier.                                                | 18 |  |  |

| Figure 2.6  | Measured spectrum from a capacitive sensing charge amplifier                                                                         | 18 |  |  |

| Figure 2.7  | Photographs of the setup for the testing of CMUT sensing                                                                             | 19 |  |  |

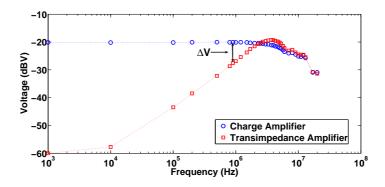

| Figure 2.8  | Frequency response of a charge amplifier with <i>pmos</i> feedback                                                                   | 20 |  |  |

| Figure 2.9  | Measured pulse-echo response from a charge amplifier                                                                                 | 20 |  |  |

| Figure 2.10 | Previous approaches to capacitive sensing.                                                                                           | 22 |  |  |

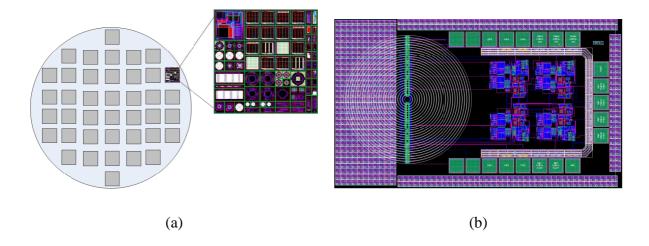

| Figure 2.11 | Reticle on TSMC 0.35um process with example of annular array CMUT electronics layout.                                                | 23 |  |  |

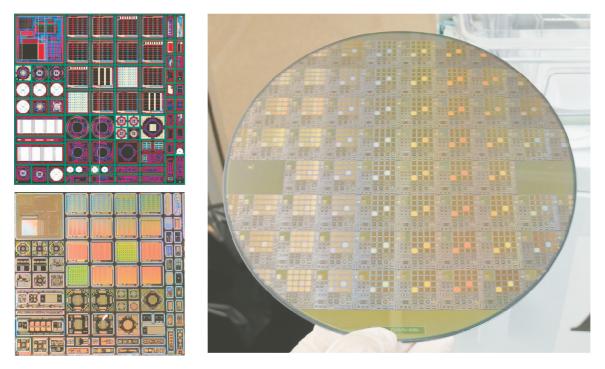

| Figure 2.12 | Wafer 0.35um TSMC 8" inch                                                                | 25 |  |  |  |  |

|-------------|------------------------------------------------------------------------------------------|----|--|--|--|--|

| Figure 2.13 | CMUT on CMOS and pulse echo plot.                                                        | 26 |  |  |  |  |

| Figure 3.1  | Design of biomimetic gradient microphone                                                 | 28 |  |  |  |  |

| Figure 3.2  | Fabricated chip with directionality plots.                                               | 29 |  |  |  |  |

| Figure 3.3  | Operating principle of the diffraction based optical displacement de-<br>tection scheme. |    |  |  |  |  |

| Figure 3.4  | System level block diagram for the Optical MEMS hearing aid                              | 32 |  |  |  |  |

| Figure 3.5  | VCSEL driver schematic.                                                                  | 34 |  |  |  |  |

| Figure 3.6  | VCSEL driver layout.                                                                     | 35 |  |  |  |  |

| Figure 3.7  | VCSEL driver measurement setup                                                           | 35 |  |  |  |  |

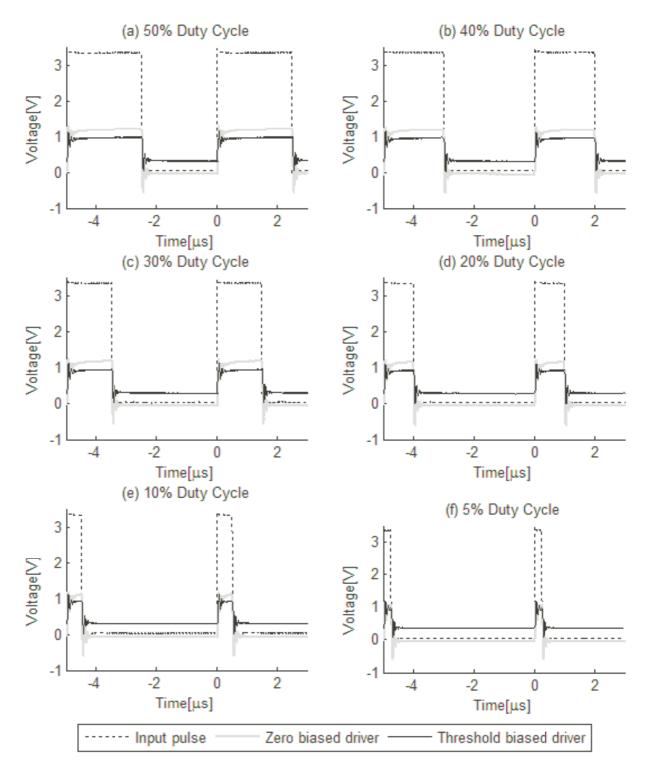

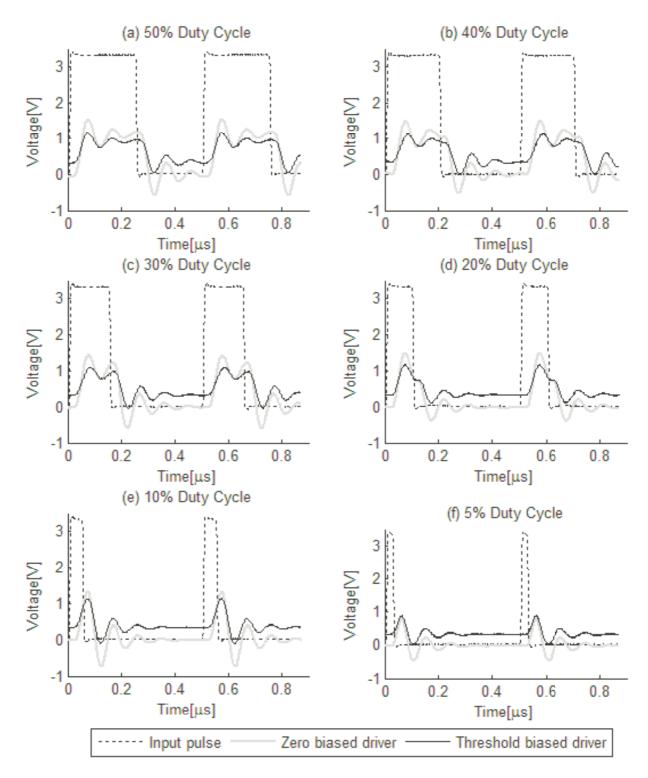

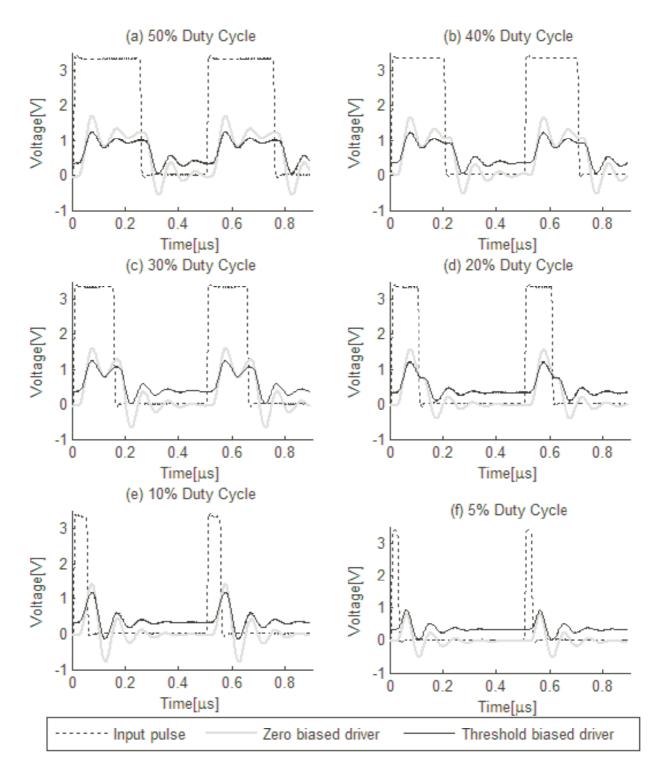

| Figure 3.8  | Output pulses with MOSFET only VCSEL driver at 200kHz                                    | 38 |  |  |  |  |

| Figure 3.9  | Output pulses with inverter VCSEL driver at 200kHz                                       | 39 |  |  |  |  |

| Figure 3.10 | Output pulses with MOSFET only VCSEL driver at 2MHz                                      | 40 |  |  |  |  |

| Figure 3.11 | Output pulses with inverter VCSEL driver at 2MHz                                         | 41 |  |  |  |  |

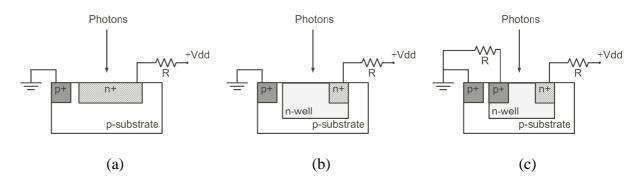

| Figure 3.12 | Photodiode in standard CMOS process                                                      | 43 |  |  |  |  |

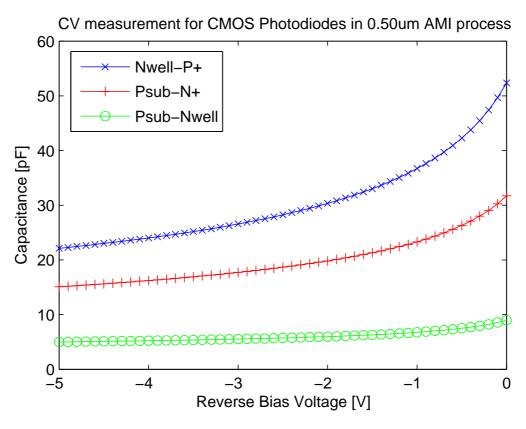

| Figure 3.13 | CV measurement plot for photodiodes in 0.5um AMI CMOS process                            | 44 |  |  |  |  |

| Figure 3.14 | IV measurement plot for photodiodes in 0.5um AMI CMOS process                            | 45 |  |  |  |  |

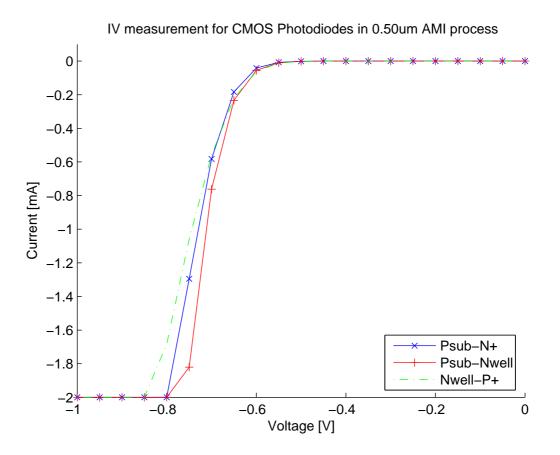

| Figure 3.15 | Setup for photodiode responsivity measurements and Chip micropho-<br>tograph.            | 45 |  |  |  |  |

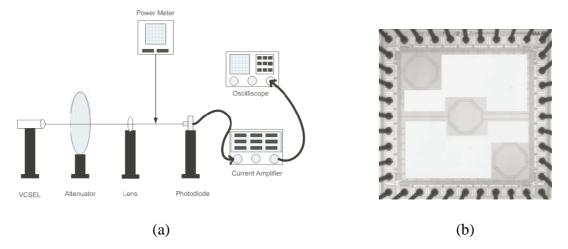

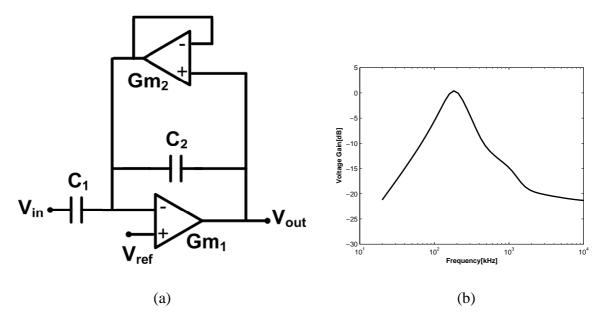

| Figure 3.16 | Band pass filter with independent controls on high and low corners                       | 47 |  |  |  |  |

| Figure 3.17 | Schematic of the capacitively coupled current conveyor (C4)                              | 49 |  |  |  |  |

| Figure 3.18 | AC measurement of band pass filter                                                       | 50 |  |  |  |  |

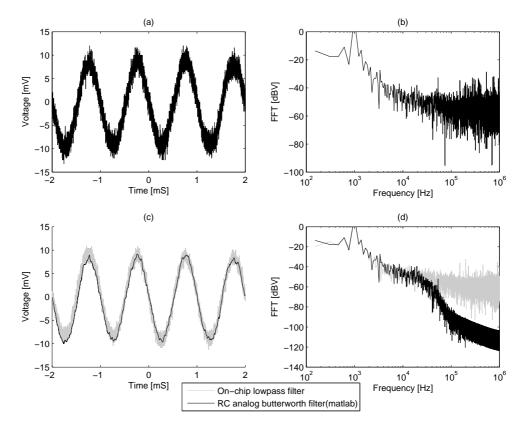

| Figure 3.19 | Low pass filter for audio band.                                                          | 51 |  |  |  |  |

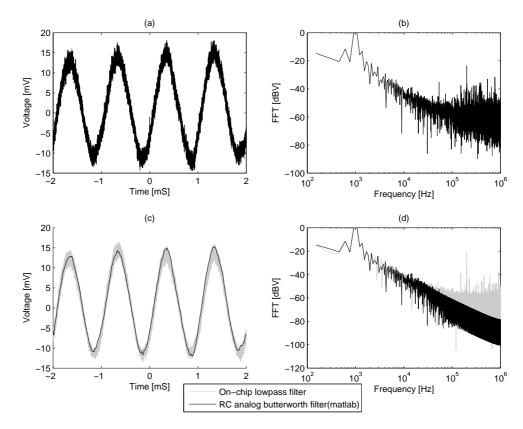

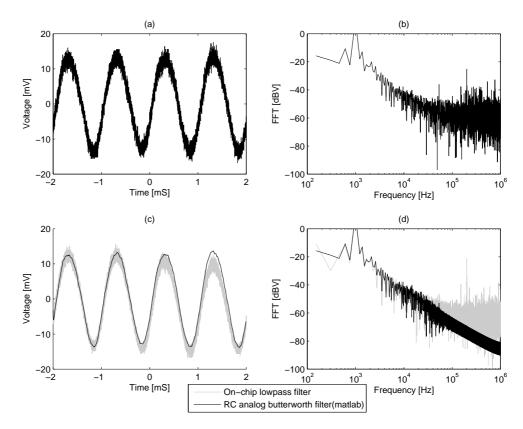

| Figure 3.20 | AC measurement of low pass filter                                                        | 52 |  |  |  |  |

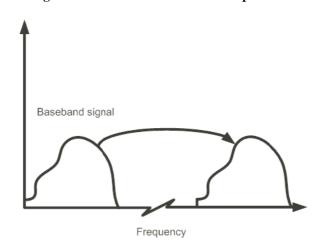

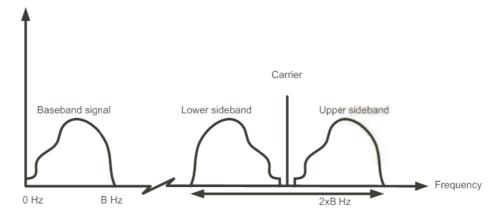

| Figure 3.21 | Frequency shifting.                                                                      | 52 |  |  |  |  |

| Figure 3.22 | Frequency shifting with AM modulation                                                    | 53 |  |  |  |  |

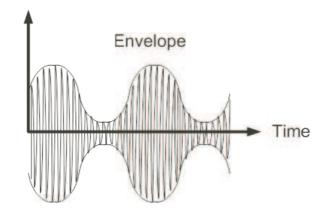

| Figure 3.23 | AM modulated envelope.                                                                   | 53 |  |  |  |  |

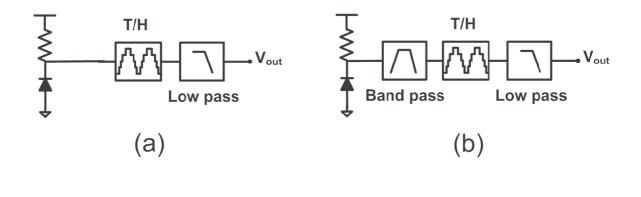

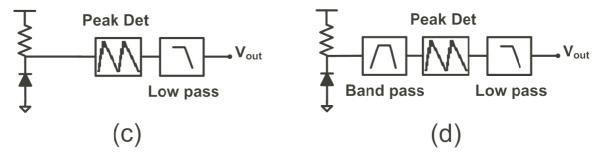

| Figure 3.24 | Different approaches for Am-demodulation.                                                | 54 |

|-------------|------------------------------------------------------------------------------------------|----|

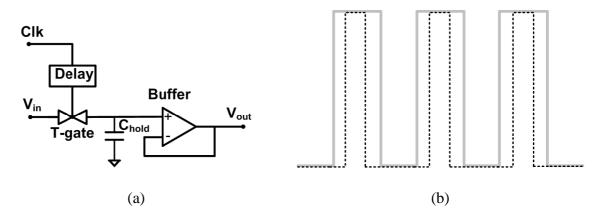

| Figure 3.25 | Synchronous detector for AM modulated signal and the clock signal used for demodulation. | 54 |

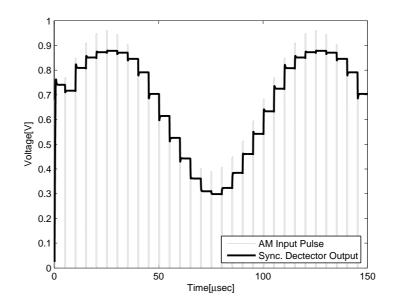

| Figure 3.26 | Synchronous detector output for AM modulated input pulse                                 | 55 |

| Figure 3.27 | Track and hold receiver without bandpass filter.                                         | 56 |

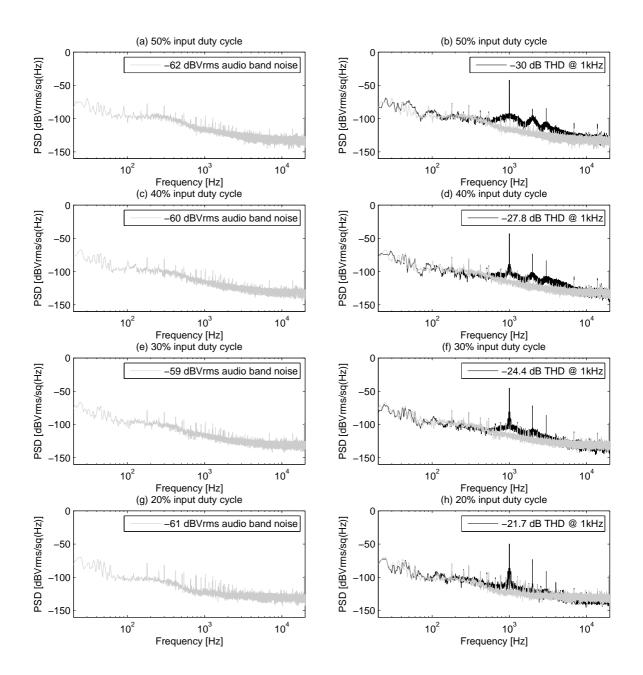

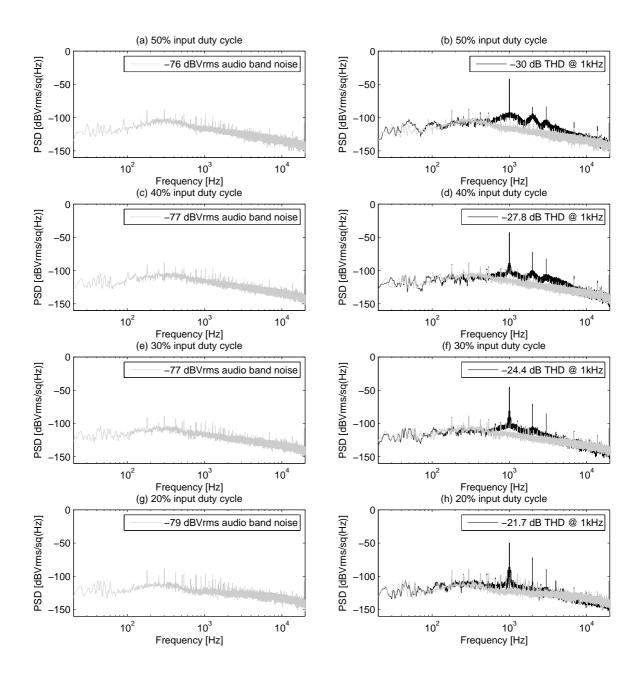

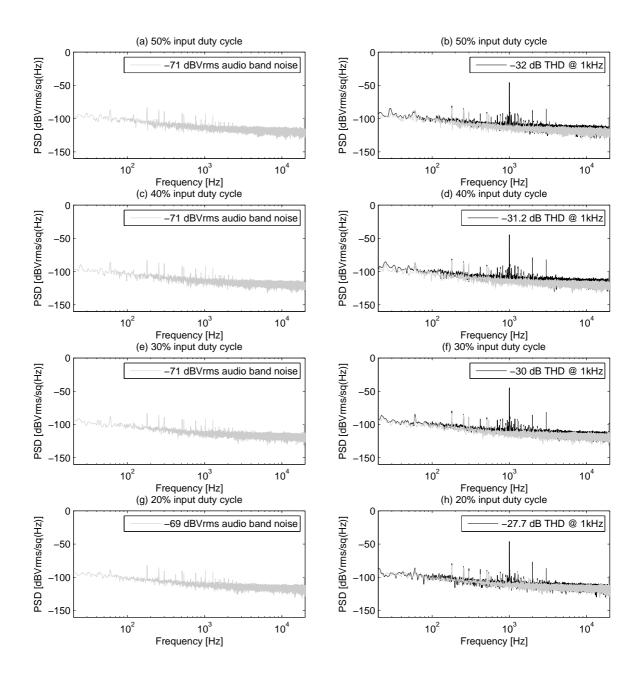

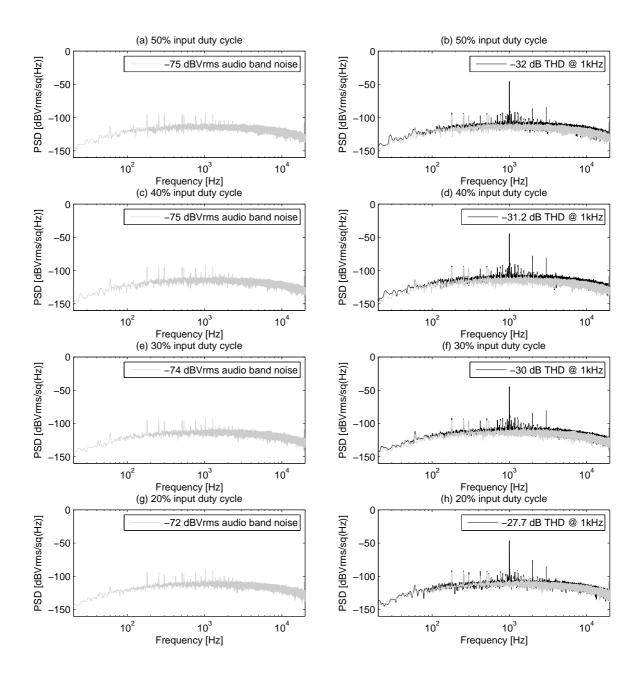

| Figure 3.28 | Track and hold receiver noise without bandpass filter                                    | 57 |

| Figure 3.29 | Track and hold receiver A-weighted noise without bandpass filter                         | 58 |

| Figure 3.30 | Track and hold receiver output without bandpass filter                                   | 60 |

| Figure 3.31 | Track and hold receiver with bandpass filter.                                            | 60 |

| Figure 3.32 | Track and hold receiver noise with bandpass filter.                                      | 61 |

| Figure 3.33 | Track and hold receiver A-weighted noise with bandpass filter                            | 62 |

| Figure 3.34 | Track and hold receiver output with bandpass filter.                                     | 63 |

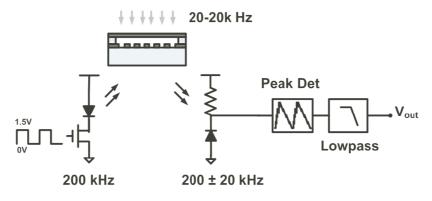

| Figure 3.35 | Envelope detector for AM modulated signal                                                | 65 |

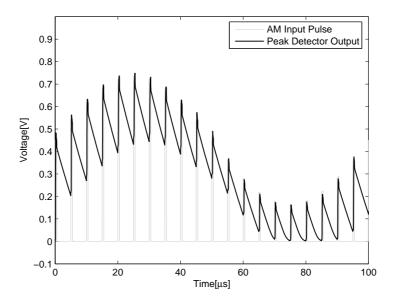

| Figure 3.36 | Peak detector output for AM modulated input pulse                                        | 65 |

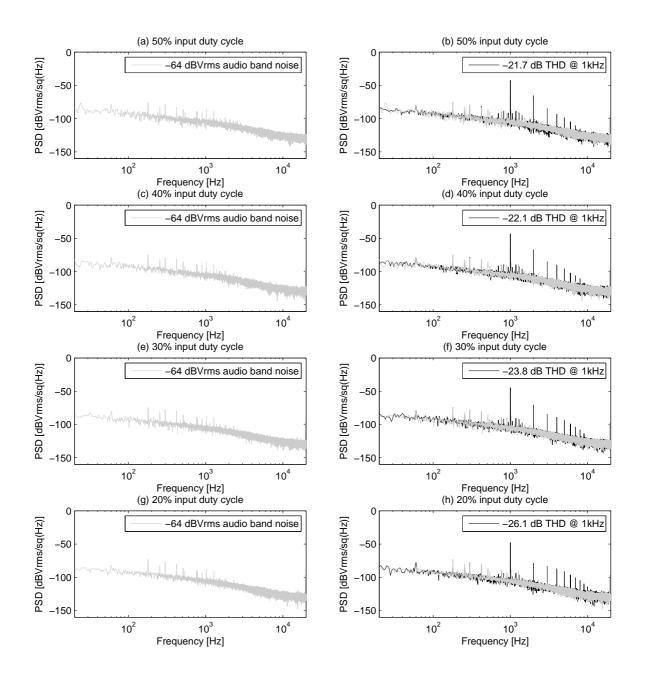

| Figure 3.37 | Peak detector receiver without bandpass filter.                                          | 67 |

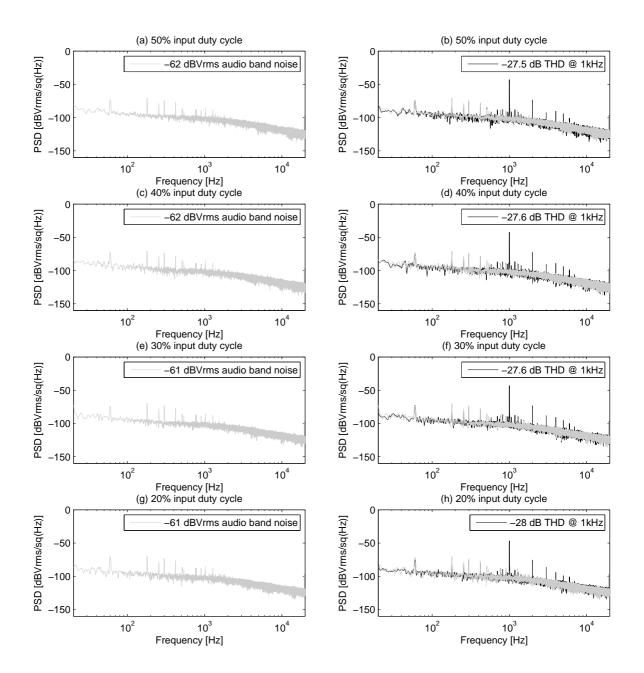

| Figure 3.38 | Peak detector receiver noise without bandpass filter                                     | 68 |

| Figure 3.39 | Peak detector receiver A-weighted noise without bandpass filter                          | 69 |

| Figure 3.40 | Peak detector receiver output without bandpass filter                                    | 70 |

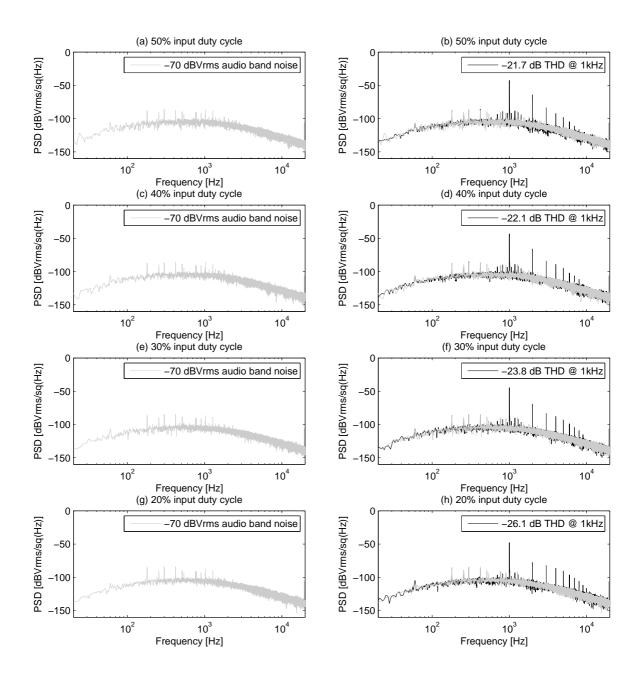

| Figure 3.41 | Peak detector receiver with bandpass filter.                                             | 71 |

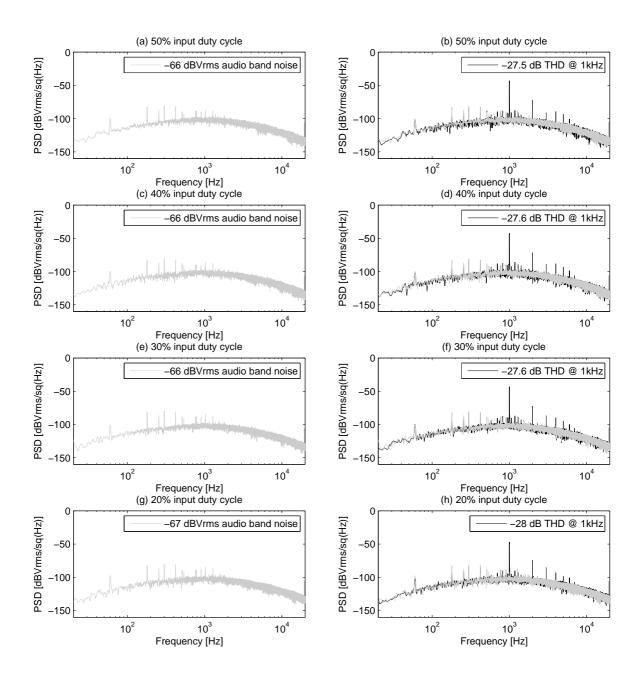

| Figure 3.42 | Peak detector receiver noise with bandpass filter                                        | 72 |

| Figure 3.43 | Peak detector receiver A-weighted noise with bandpass filter                             | 73 |

| Figure 3.44 | Peak detector receiver output with bandpass filter.                                      | 74 |

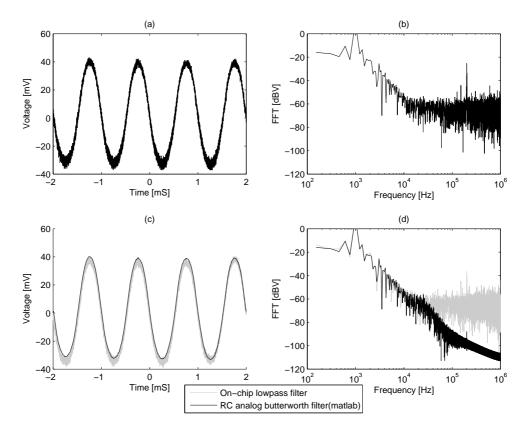

| Figure 3.45 | Receiver with continuous mode VCSEL input.                                               | 75 |

| Figure 3.46 | Continuous mode receiver noise.                                                          | 76 |

| Figure 3.47 | Continuous VCSEL mode receiver output.                                                   | 77 |

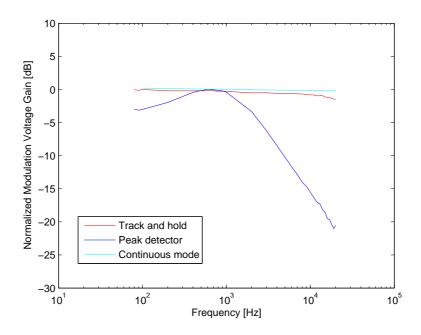

| Figure 3.48 | AC response of demodulators                                                              | 78 |

| Figure 3.49 | Noise reduction with bandpass filter.                                                    | 79 |

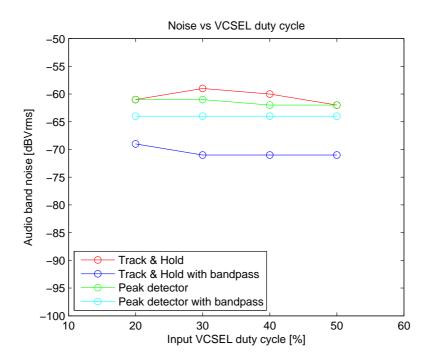

| Figure 3.50 | SNR and VCSEL current consumption with input duty cycle                                                                                                                                                    |    |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

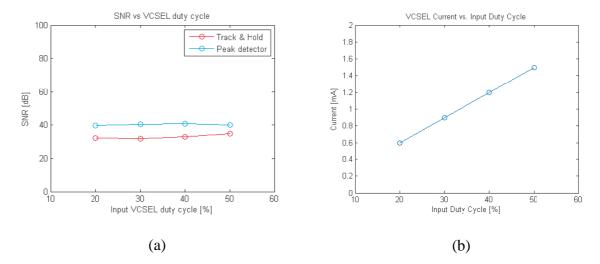

| Figure 3.51 | Continuous time CMOS chip                                                                                                                                                                                  | 82 |  |  |

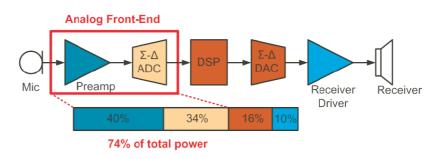

| Figure 4.1  | Power breakdown of an hearing aid                                                                                                                                                                          | 83 |  |  |

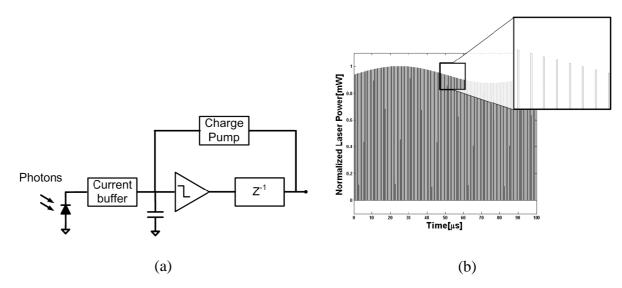

| Figure 4.2  | System level integration of photodiode with current input sigma-delta and input PWM signal.                                                                                                                | 84 |  |  |

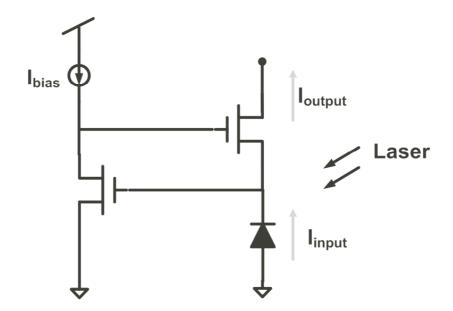

| Figure 4.3  | Input current buffer.                                                                                                                                                                                      | 85 |  |  |

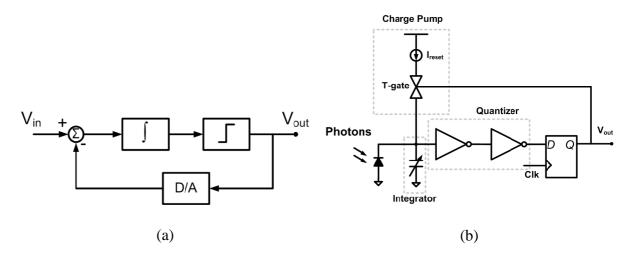

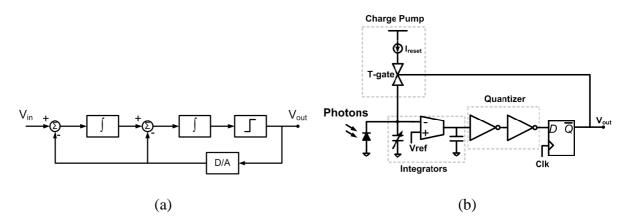

| Figure 4.4  | System and circuit level architecture of 1-bit first order sigma-delta ADC                                                                                                                                 | 85 |  |  |

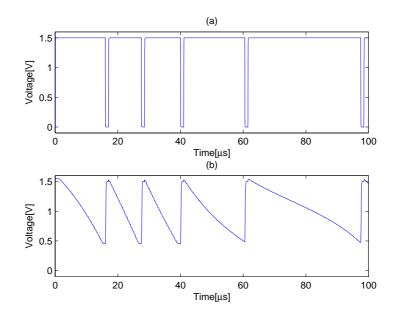

| Figure 4.5  | Bit stream from 1-bit first order sigma-delta in response to PWM si-<br>nusoidal signal Integrating voltage for 1-bit first order sigma-delta and<br>Integrating voltage for 1-bit first order sigma-delta | 86 |  |  |

| Figure 4.6  | System and circuit level architecture of 1-bit second order sigma-delta ADC                                                                                                                                | 86 |  |  |

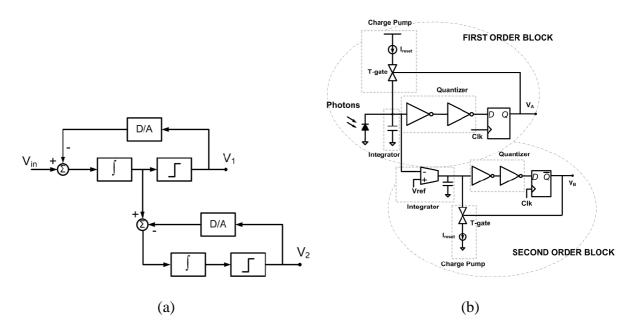

| Figure 4.7  | System and circuit level architecture of 1-bit incremental sigma-delta ADC                                                                                                                                 | 87 |  |  |

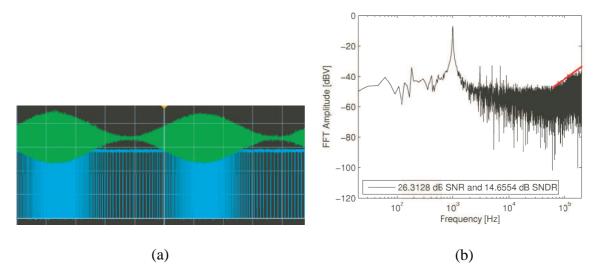

| Figure 4.8  | Output from first order sigma delta.                                                                                                                                                                       | 88 |  |  |

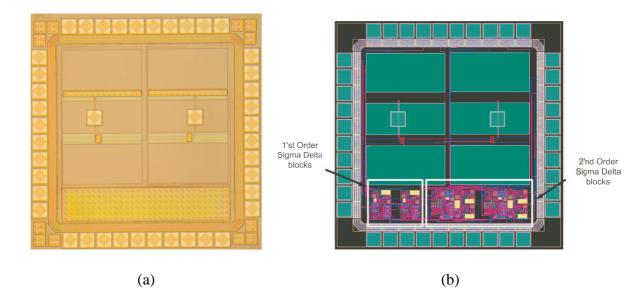

| Figure 4.9  | Sigma Delta Chips.                                                                                                                                                                                         | 90 |  |  |

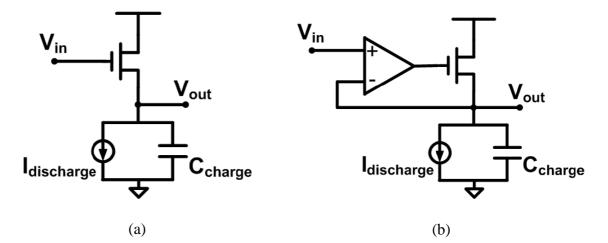

| Figure 5.1  | Simplified input current buffer.                                                                                                                                                                           | 93 |  |  |

#### SUMMARY

The objective of this research is to develop and design front-end analog circuits for Capacitive Micromachined Ultrasound Transducers (CMUTs) and optical grating MEMS microphone. This work is motivated by the fact that with micro-scaling, MEMS sense capacitance gets smaller in a CMUT array element for intravascular ultrasound imaging, which has dimensions of 70um x 70um and sub pico-farad capacitance. Smaller sensors lead to a lower active-to-parasitic ratio and thus, degrads sensitivity. Area and power requirements are also very stringent, such as the case of intravascular catheter implementations with CMOS-First CMUT fabrication approach. In this implementation, capacitive feedback charge amplifier is an alternative approach to resistive feedback amplifiers. Capacitive feedback charge amplifier provides high sensitivity, small area, low distortion and saving power. This approach of charge amplifiers is also suitable in capacitive microphones where it provides low power and high sensitivity. Another approach to overcome capacitive detection challenges is to implement optical detection. In the case of biomimetic microphone structure, optical detection overcomes capacitive detections thermal noise issues. Also with micro-scaling, optical detection overcomes the increased parasitics without any sensitivity degradation, unlike capacitive detection. For hearing aids, along with sensitivity, battery life is another challenge. We propose the use of 1-bit front-end sigma-delta ADC for overall improved hearing aid power efficiency. Front-end interface based on envelope detection and synchronous detection schemes have also been designed. These interface circuits consume currents in micro-ampere range from a 1.5V battery. Circuit techniques are used for maximizing linear range and signal handling with low supplies. The entire front end signal processing with Vertical Cavity Surface Emitting Laser (VCSEL) drivers, photodiodes, filters and detectors is implemented on a single chip in 0.35um CMOS process.

### **CHAPTER 1**

# ANALOG INTERFACE FOR MEMS SENSORS

Microelectromechanical system (MEMS)-based sensors gather information from the environment through measuring mechanical, thermal, biological, chemical, optical, and magnetic phenomena. The electronics then process the signal information derived from the sensors in the presence of parasitics and noise. Because MEMS devices are manufactured using batch fabrication techniques similar to those used for integrated circuits, unprecedented levels of functionality, reliability, and sophistication can be placed on a small silicon chip at a relatively low cost [1]. Interface electronics becomes challenging with the miniaturization of sensors in the presence of parasitics and reduced sense capacitance. The first part of this research focuses on an alternative approach of using capacitive feedback charge amplifiers to a resistive feedback charge amplifier for addressing these issues. The second part covers interface electronics for optical detection, which is another approach to capacitive detection as used in hearing aid microphones with strict power and supply limitations.

MEMS have the capabilities to manipulate and process signals from the physical world. The micro-scale size of these device increases the relative parasitics with respect to the sense capacitance. In order to mitigate the parasitics and increase the sensitivity of the signal of interest, we make use of a capacitive feedback charge amplifier with pseudo-MOS resistors for stabilizing the DC input node voltage. This capacitive detection technique is used with capacitive micromachined ultrasound transducers (CMUT) for intra-vascular imaging and also with capacitive MEMS microphones. With post-processed CMUTs on a CMOS wafer, we have designed an integrated chip solution for an ultrasound signal transceiver.

However, capacitive detection is not the only approach for sensing MEMS. Optics is

now also becoming feasible for sensing MEMS with the reduction in size of the vertical cavity surface emitting laser (VCSEL). Optical detection is very powerful for highresolution interferometric displacement sensing. The parasitics and thermal noise of MEMS sense capacitance can also be solved with the use of optics. This approach gives added benefit as the shot noise limit can be reached [2]. In a miniature sized packaging, diffractionbased MEMS membranes can be integrated with VCSEL to form a highly sensitive microphone for hearing aid applications. We have investigated and designed various circuits for a low-power, low-voltage electronic interface with the optical MEMS sensor in microphone applications. These interface electronics consume micro-amperes of current from a 1.5V battery. Furthermore, a 1-bit ADC is also proposed for the front-end interface for optical detection in order to maximize the power efficiency in hearing aid applications.

## **1.1 Capacitive Micromachined Ultrasound Transducers**

MEMS are embedded systems that involve one or more micromachined components or structures. They enable higher level functions, though their utility may be limited. For example, a micromachined pressure sensor in one's hand is useless, but, under the hood, it controls the fuel-air mixture of the car engine. These sensors often integrate several functions together into one package for greater utility (e.g., merging an acceleration sensor with electronic circuits for self-diagnostics). Additionally, the cost benefits of MEMS can come either directly through low unit pricing or indirectly by cutting service and maintenance costs [3]. This section will cover capacitive micromachined ultrasound transducers (CMUT) for intra-vascular imaging.

#### 1.1.1 Intra-vascular Ultrasound Imaging

Intravascular ultrasound (IVUS) is a medical imaging technique that uses a catheter with a built-in ultrasound probe. This makes use of ultrasound to see the inside of the blood vessels. It gives a cross sectional view of the inner wall of blood vessels. IVUS is primarily used in coronary arteries to examine the amount of plaque buildup along the inner

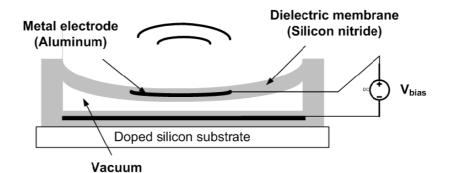

Figure 1.1. Cross sectional view of the Capacitive Micromachined Ultrasound Transducer (CMUT). In transmit mode, the electrodes are actuated with AC signal on a high voltage DC bias. While in receive mode a DC bias is applied on the electrodes and the CMUT is connected with the receive electronics.

walls. Visualizing plaque is the most valuable use of IVUS, since plaque cannot be seen by angiography.

## 1.1.2 Capacitive Micromachined Ultrasound Transducer

Piezoelectric transducers have long dominated ultrasonic transducer technology; however, CMUTs have recently emerged as an alternative technology, offering advantages such as wide bandwidth, ease of fabricating large arrays, and potential for integration with electronics [4].

CMUTs are essentially capacitors with one moveable electrode. Actuation occurs according to Coulombs Law, as shown in Fig. 1.1. The force of attraction generated between two oppositely charged electrodes causes the moveable electrode to deflect. If an alternating voltage is applied to the device, the moveable electrode begins to vibrate, thus generating ultrasound. If CMUTs are used as receivers, then changes in pressure, such as those from an ultrasonic wave, cause the moveable electrode to deflect, hence producing a measurable change in capacitance.

#### 1.1.3 Challenges in Capacitive Sensing and IVUS imaging

Capacitive transduction is one of the more important and widely used techniques in MEMS, such as in CMUTs. In a typical two-chip hybrid approach there is current leakage along with parasitics to ground. This parasitic capacitance along with the static capacitance of

Figure 1.2. Schematic diagram of the IVUS catheter employing the forward-looking annular-ring CMUT array with integrated front-end electronics.

the sensor can be much larger than the capacitance variations to be sensed. This creates many challenges for high sensitivity, high dynamic range detection. In addition, power consumption is also a critical issue in applications like MEMS hearing aids and CMUT-based IVUS imaging.

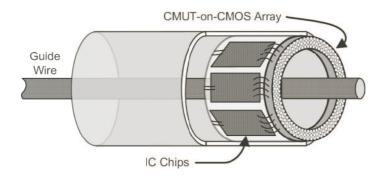

In intra-vascular ultrasound applications, the piezoelectric transducer technology has prevented effective implementation of systems with diameters below 1 mm. On the other hand, the latest advancements in CMUT technology enable the construction of forward-looking (FL) annular-ring transducer arrays that can be placed in front of the catheter [5]. Because of the small size of each CMUT element in an FL-IVUS array, which is on the order of  $100 \,\mu$ m and is much smaller than that in a non-invasive 1-D CMUT array, the parasitic capacitances introduced by the electrical interconnects can easily overwhelm the device capacitance and impair the achievable signal-to-noise (SNR) ratio. Either integrating the CMUT array with electronics on the die level or building the CMUT array directly on CMOS elements, as illustrated in Fig. 1.2, can avoid the performance degradation caused by the cable losses. Since the probe is located inside the patient's body, power dissipation is another major concern. Because IVUS imaging requires a high resolution and because the imaging depth for vessels is relatively shallow, the transducers usually operate at a high frequency; therefore, low-power electronics are very critical.

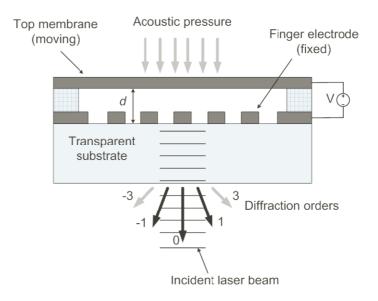

Figure 1.3. Schematic diagram of a micromachined acoustic sensor with a built in phase-sensitive diffraction grating for displacement detection.

# **1.2 Diffraction Grating Optical Microphone**

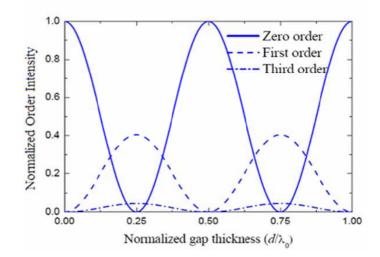

A simple schematic of the diffraction-based optical displacement detection scheme is illustrated in Fig. 1.3. It consists of a transparent substrate with an optically reflective diffraction grating fixed to the surface. The grating consists of alternating regions of reflective fingers. An optical reflector, whose displacement is to be monitored, is placed behind the substrate. A highly compliant membrane is made part of a phase-sensitive diffraction grating, and the deflection resulting from external acoustic pressure alters the intensities of the diffracted orders, which are monitored with photodiodes [6]. Figure 1.4 illustrates the diffractions orders on the intensity plot [2].

This highly sensitive optical displacement detection method implemented in a small volume and with reduced power consumption has the potential to compete with commonly used capacitance-based methods in micromechanical sensor systems [2]. The traditional capacitive acoustic sensors do not scale down favorably. In other words, reducing the membrane size decreases the ratio of the active capacitance to the parasitic capacitance, thereby requiring a gain in mechanical compliance, which in turn necessitates the use of very thin, low-stress membranes, that are difficult to reproduce in a repeatable manner [1].

Figure 1.4. Diffraction efficiencies of the zero, first, and third orders.

Reducing the membrane gap to increase the active capacitance can increase the stiffness of the trapped air and reduce the electrical sensitivity by limiting the sustainable electric field [7, 8]. To address these problems, optical techniques are used with diffraction gratings as a method to measure displacement from acoustic pressure in microphones. This hybrid integrated system can be implemented in acoustic-sensor applications using both continuous wave and pulse VCSEL to show reduced power consumption.

#### **1.3** Low Power and Low Voltage Design

There are limitations of integrated circuits when faced with the requirements of low power. Low-noise amplifiers are critical in applications where a large dynamic range is needed. We can express dynamic range as signal-to-noise ratio (SNR). As the standard CMOS technology continues to improve, the power supplies are decreasing and even going below 1 Volts. This reduction comes from the fact that processes are designed for speed and this indirectly affects the breakdown voltages hence the maximum power supply voltages.

Along with noise, we must also take into account the linearity of the amplifiers. If the amplifier is nonlinear, then a pure sinusoidal input signal will create harmonics. Now if the total harmonic distortion (THD) is more than the noise, then in this case, the non-linearity

becomes the limiting factor. It is common to use the notation of signal-to-noise plus distortion (SNDR). This includes noise and the distortion in dynamic range specifications.

When considering low noise design, we start with the single MOS transistor. The equivalent input mean square voltage noise is given by:

$$v_{\rm n}^2 = \frac{8kT}{3g_m} + \frac{K}{WLC_{\rm ox}f} \tag{1.1}$$

The first part of the equation is the thermal noise and the second part is the flicker noise where k is the Boltzman's constant, T is temperature,  $g_m$  is the small signal transconductance, K is the flicker noise, W is the width of the transistor, L is the length of the transistor, f is the frequency in Hertz and  $C_{ox}$  is the gate oxide capacitance per unit area [9].

In many respects, the thermal noise of a MOSFET device is equivalent to the thermal noise of a BJT. Unfortunately, the 1/f noise is much larger. We note that minimizing the thermal noise of an amplifier is reasonably straightforward. From the first term in (1.1), we see that we want the small-signal transconductance  $g_m$  to be large to minimize the equivalent input-mean-square noise voltage. This can be done by large dc currents or large W/L ratios. For the 1/f noise, there are at least three approaches to minimizing the 1/f noise of CMOS amplifiers. The first is to minimize the noise contribution of the MOSFETs through circuit topology and transistor selection (NMOS vs. PMOS), dc currents, and W/L ratios. The second is to replace the MOSFETs by BJTs to avoid the 1/f noise.

#### **1.3.1** Total Harmonic Distortion (THD)

If a sinusoidal signal is applied to a linear time-invariant system, it is well known that the output will also be a sinusoidal waveform at the same frequency, but possibly with different magnitude and phase values. However, if the same input is applied to a nonlinear system, the output signal will have frequency components at harmonics of the input waveform, including the fundamental harmonic. For example, if a 1 MHz sinusoidal input signal

is used, the output signal will have power at the fundamental, 1 MHz, as well as at the harmonic frequencies, 2 MHz, 3 MHz, 4 MHz, and so on. The total harmonic distortion (THD) of a signal is defined to be the ratio of the total power of the second and higher harmonics components to the power of the fundamental for that signal. In units of dB, THD is found using the following relation:

$$THD = 10\log(\frac{V_{h2}^2 + V_{h3}^2 + V_{h4}^2 + \cdots}{V_f^2})$$

(1.2)

where  $V_f$  is the amplitude of the fundamental and  $V_{hi}$  is the amplitude of the i'th harmmonic component. Sometimes THD is presented as percentage value. In this case,

$$THD = \frac{\sqrt{V_{h2}^2 + V_{h3}^2 + V_{h4}^2 + \cdots}}{V_{f}} \times 100$$

(1.3)

It should be noted that the THD value is always a function of the amplitude of the input signal, and thus the corresponding signal amplitude must also be reported. Typically first 5 harmonics are used for THD calculations as the higher components falls off very quickly.

#### 1.3.2 Rail-to-rail Input Stages

A very well-known approach for implementing an input stage with a rail-to-rail common mode input range is to place an N-type and P-type differential pair in parallel[10], as shown in Fig. 1.5(a). In this circuit the bias currents are generated by transistors. In each case of the differential pair, the biasing transistor's drain to source voltage should be able to support the current it provides. For the N-type differential pair, this determines the lower boundary of operation range of the N-type metal-oxide-semiconductor (NMOS) differential pair. The upper boundary is determined by the supply voltage and the fact that the gate voltage of a transistor may exceed the drain voltage by only a threshold voltage before it brings the transistor out of saturation. Therefore, the N-type differential pair can operate from a certain common-mode input voltage above the negative supply rail up to a certain

Figure 1.5. (a)Rail-to-rail differential input pair (b)Voltage range of operation

common-mode input voltage above the positive supply rail as indicated in Fig. 1.5(b). For the PMOS differential pair the opposite is true. Thus applying the two complementary input pairs in parallel results in an input stage which has a common-mode input range that can even exceed the supply rails., provided that adequate circuitry is available for combining the output signals of the individual differential pairs.

Three different operation areas can be distinguished:

- The common-mode input voltage is near the negative supply rail; signal transfer will take place only by the P-type differential pair.

- The common-mode input voltage is in a region somewhere in the middle between the supply voltages; both the NMOS and the PMOS differential pairs will be active.

- The common-mode input voltage is near the positive supply rail; signal transfer will take place only by the N-type differential pair.

It is clear that without precautions the transconductance  $g_{\rm m}$  of the combination strongly

Figure 1.6. Complementary input rail-to-rail folded cascode amplifier.

Figure 1.7. ICMR measurement for rail-to-rail input.

depends on the common-mode input level because only in a region somewhere in the middle of the supply voltages will both differential pairs be active. A nonconstant (i.e. a common-mode input voltage dependent) transconductance  $g_m$  is undesirable, because a variation in  $g_m$  causes a variation in the unity-gain bandwidth of the amplifier and prevents an optimal frequency compensation. This reduces the feasible unity-gain bandwidth of the compensated amplifier. Furthermore, a common-mode input voltage dependent transconductance causes extra distortion.

The ICMR measurement is shown in Fig. 1.7. We seep the input common mode of a

Figure 1.8. (a)Capacitive division. (b) Tobi element for on-chip high resistance element.

Figure 1.9. (a) Tobi element with resulting bipolar transistors. (b) Cross-sectional view of Tobi element.

buffer configuration from 0 to 1.5Volts. Notice that the wide rail-to-rail behavior. In case of a single PMOS or NMOS input, the response would be reduced by the turn-on voltage of the differential pair.

## 1.3.3 Tobi Element

For increasing signal linearity by attenuating input signal with capacitive division[11] is one interesting approach as shown in Fig. 1.8(a), but this comes with the challenges of biasing the floating node. Here we go over a very simple element that exactly performs that. Figure Fig. 1.8(b) shows an adaptive element with a sinh-like I-V characteristic. It has a very nonlinear resistor-like characteristics. It is commonly called "tobi element" (after Tobi Delbruck)[12]. It consists of a diode-connected well transistor in one direction and a parasitic vertical bipolar transistor in the other as shown in Figure 1.9. It essentially has two modes of operations, namely bipolar and MOS mode. The mode of conduction when the well voltage is higher than the gate voltage: The structure acts as a diode-connected MOS transistor. The opposite case: The p+/n junction is forward-biased, and the device as a whole acts as a bipolar transistor with two collectors. It can also be looked at like to diodes in parallel with opposite polarity. The current increases exponentially with voltage with either sign of voltage, and there is an extremely high resistance region around the origin. Tobi element now can be used in conjunction with capacitive division in amplifiers. As our microphone is low power and low voltage batttey system, we will make use of linearity maximizing approachs through out receiver electronics.

## **CHAPTER 2**

# **CHARGE AMPLIFIER FOR CAPACITIVE SENSING**

Capacitive detection is a common, and most important method used in microelectromechanical systems, such as in CMUTs. The flexibility of digital data processing systems has sparked significant research efforts to develop new algorithms to reconstruct, enhance, and analyze ultrasound images. However, the ability and usefulness of these algorithms depend on the quality (e.g., SNR, bandwidth, and dynamic range) of the original echo signal, making the transducer and associated front-end electronics the most critical components of ultrasound imaging systems. In this section, we propose a capacitive feedback charge amplifier for front-end analog processing of CMUT sensors.

## 2.1 Analysis of Capacitive Sensing Charge Amplifier

Fig. 2.1 shows the small-signal model of the capacitive sensing charge amplifier. In this amplifier, the input capacitance, the explicitly drawn capacitance, and all the parasitic capacitances from the floating node to ground are all included in  $C_w$ . The amplifier is modeled as a first-order system in the following analysis [13].

The transfer function and SNR expression are summarized below:

#### Transfer function:

$$\frac{V_{\text{out}}(s)}{C_{\text{sensor}}(s)} = -\frac{V_{\text{bias}}}{C_{\text{f}}} \cdot \frac{1 - sC_{\text{f}}/G_{\text{m}}}{1 + sC_{\text{eff}}/G_{\text{m}}},$$

(2.1)

where  $C_{\text{eff}} = \left(C_{\text{o}}C_{\text{T}} - C_{\text{f}}^2\right)/C_{\text{f}}$ ,  $C_{\text{o}} = C_{\text{L}} + C_{\text{f}}$ , and  $C_{\text{T}} = C_{\text{sensor}} + C_{\text{w}} + C_{\text{f}}$ . *SNR*:

$$SNR \ge C_{\text{eff}} \cdot \frac{2\kappa\Delta V_{\text{lin,max}}^2}{nqU_{\text{T}}},$$

(2.2)

where  $\kappa$  is the subthreshold slope coefficient of transistors, *n* is the effective number of noisy transistors, *q* is the charge of an electron,  $U_{\rm T}$  is the thermal voltage, and  $\Delta V_{\rm lin,max}$  is the maximum input linear range of the differential pair. From (2.1), the circuit can achieve

Figure 2.1. Schematics of the small-signal model of capacitive sensing charge amplifier.

Figure 2.2. A new approach to sensing capacitance change by using a charge amplifier and a floatinggate based charge adaptation circuit.

high sensitivity by choosing a large  $V_{\text{bias}}$  and a small  $C_{\text{f}}$ . From (2.2), a larger  $G_{\text{m}}$  can improve the linearity and the SNR.

# 2.2 Charge Amplifier with Charge Adaptation Feedback

Fig. 2.2 shows the basic topology of capacitive feedback charge amplifier. The charge adaptation circuit can be modeled by a small feedback conductance,  $g_f$ , as shown in Fig. 2.3(a). The transfer function of the sensing circuit can be expressed as:

$$\frac{V_{\text{out}}(s)}{C_{\text{CMUT}}(s)} = \frac{V_{\text{bias}}}{g_{\text{f}}} \cdot \frac{s(s\frac{C_{\text{f}}}{G_{\text{m}}} - 1)}{s^2 \frac{C_{\text{T}}C_{\text{o}} - C_{\text{f}}^2}{G_{\text{m}}g_{\text{f}}} + s\left[\frac{C_{\text{f}} + C_{\text{T}}/A}{g_{\text{f}}} + \frac{C_{\text{T}} + C_{\text{o}} - 2C_{\text{f}}}{G_{\text{m}}}\right] + 1},$$

(2.3)

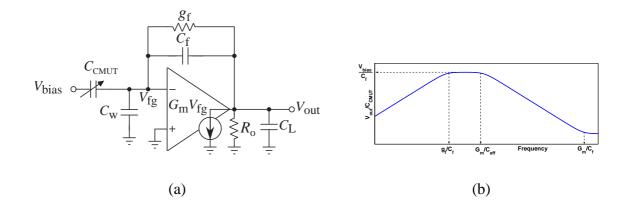

where A is the amplifier gain. As shown in Fig. 2.3(b), the adaptation scheme creates an extra zero at the origin and an extra low-frequency pole around  $g_f/C_f$ , assuming A is large enough. If the transistors are in subthreshold region, we can derive the minimum detectable

Figure 2.3. (a) The small signal model of a charge amplifier with charge adaptation circuit, which is modeled by a feedback conductance. (b) Simulated frequency response of the circuit shown in (a).

capacitance as:

$$\Delta C_{\min,CA} = \frac{1}{V_{\text{bias}}} \cdot \sqrt{\frac{nqU_{\text{T}}C_{\text{T}}C_{\text{f}}}{2\kappa C_{\text{o}}}}.$$

(2.4)

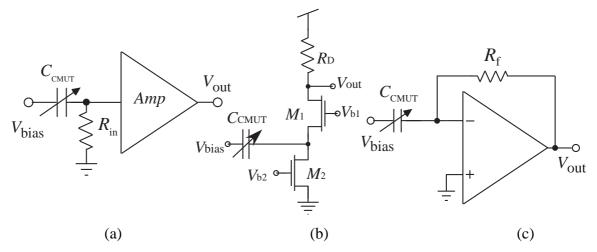

Conventionally, CMUT signals are converted from capacitive currents into voltages by using either resistive terminations followed by amplifiers, common-gate amplifiers, or resistive feedback TIAs as shown in Fig. 2.4 [4]. The first approach suffers from the direct trade-off between bandwidth and input-referred current noise because they both are proportional to  $1/R_{in}$ . In the common-gate topology, although the noise can be minimized by maximizing the load resistance and the overdrive voltage of  $M_2$  without affecting the bandwidth, it incurs a reduction in the output voltage headroom. In the last case, because the feedback resistance does not limit the voltage headroom and because the input capacitance can be reduced by the amplifier gain by the "shunt-shunt" feedback, TIA topology is widely used in capacitive sensing applications. However, when the operating frequency is high, the bandwidth can be limited by the parasitic feedback capacitance.

It is interesting to note that Fig. 2.3(a) can also be viewed as a small signal model of a TIA with a parasitic feedback capacitance. The expression of (2.3) can be rearranged to

Figure 2.4. (a) Schematic of a resistive termination followed by an amplifier stage. (b) Schematic of a common-gate amplifier. (c) Schematic of a resistive feedback transimpedance amplifier.

describe the transfer function of the TIA as:

$$\frac{V_{\text{out}}(s)}{I_{\text{CMUT}}(s)} = \frac{V_{\text{out}}(s)}{sV_{\text{bias}}C_{\text{CMUT}}(s)} = \frac{1}{g_{\text{f}}} \cdot \frac{s\frac{C_{\text{f}}}{G_{\text{m}}} - 1}{s^2\frac{C_{\text{T}}C_{\text{o}} - C_{\text{f}}^2}{G_{\text{m}}g_{\text{f}}} + s\left[\frac{C_{\text{f}} + C_{\text{T}}/A}{g_{\text{f}}} + \frac{C_{\text{T}} + C_{\text{o}} - 2C_{\text{f}}}{G_{\text{m}}}\right] + 1}.$$

(2.5)

The minimum detectable capacitance of the TIA can be derived as:

$$\Delta C_{\min,\text{TIA}} = \frac{g_{\text{f}}}{\omega_0 V_{\text{bias}}} \cdot \sqrt{\frac{nqU_{\text{T}}C_{\text{T}}}{2\kappa C_{\text{f}}C_{\text{o}}}},$$

(2.6)

where  $\omega_0$  is the operating frequency.

Although the topologies of a TIA and a charge amplifier are the same, their design philosophies are different. In a typical TIA design, the operating frequency should be lower than the first pole, which corresponds to the ascendent region in Fig. 2.3(b). The sensitivity-bandwidth trade-off of a TIA is obvious from (2.5) and (2.6). Increasing the bandwidth by increasing  $g_f$  decreases sensitivity. On the other hand, using a charge amplifier to sense the CMUT signals can avoid all the dilemmas mentioned before. The sensitivity can be improved by choosing large values of  $V_{\text{bias}}$  and  $C_L$  and a small value of  $C_f$ . The bandwidth, corresponding to the second pole, can be extended by using a larger value of  $G_m$ .

#### 2.2.1 Design Procedure

With given specifications of minimum detectable capacitance ( $\Delta C_{\min}$ ), bandwidth ( $\omega_{3dB}$ ), and SNR, the goal is to optimize the current consumption ( $I_b$ ), feedback capacitance ( $C_f$ ), and load capacitance  $(C_{\rm L})$ . We assume that the known variables include the total capacitance seen from the floating node  $(C_{\rm T} \approx C_{\rm sensor} + C_{\rm w})$ , the bias voltage of the sensing capacitor  $(V_{\rm bias})$ , and the maximum input linear voltage of the transconductance amplifier  $(\Delta V_{\rm lin,max})$ . We also assume that the maximum output linear range is not limited by the supply rails but only affected by the nonlinearity of the OTA.

The design procedure starts from the sensitivity expression:

$$\Delta C_{\min}^2 = \frac{nqU_{\rm T}}{2\kappa V_{\rm bias}^2} \cdot \frac{C_{\rm T}C_{\rm f}}{C_{\rm o}},\tag{2.7}$$

where  $\Delta C_{\min}$  is the minimum detectable capacitance. From (2.7) we can have:

$$\frac{C_{\rm f}}{C_{\rm L}} \le \frac{\Delta C_{\rm min}^2}{C_{\rm T}} \cdot \frac{2\kappa V_{\rm bias}^2}{nqU_{\rm T}}.$$

(2.8)

Since only the ratio of  $C_{\rm f}$  to  $C_{\rm L}$  matters, these two capacitances can be chosen from reasonable and practical values.

The next step is to determine the current consumption for a given  $C_f/C_o$  ratio. Assuming that an OTA is biased in subthreshold region, the required current is estimated as:

$$I_{\rm b} \ge \omega_{3dB} \cdot \frac{2U_{\rm T}}{\kappa} \cdot \frac{C_{\rm o}C_{\rm T}}{C_{\rm f}}$$

(2.9)

$$I_{\rm b} \ge \sqrt{SNR} \cdot \frac{2nqU_{\rm T}^3 \omega^2}{\kappa^3 \Delta V_{\rm lin,max}^2} \frac{C_{\rm o} C_{\rm T}}{C_{\rm f}}.$$

(2.10)

The current consumption is usually determined by (2.9).

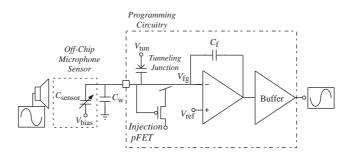

#### 2.2.2 Setup And Measurement Results

A version of the capacitive sensing circuit is fabricated in a  $0.5 \,\mu$ m double-poly CMOS process and is tested with a MEMS microphone sensor. The setup diagram is shown in Fig. 2.5. A tunneling junction and an indirect injection transistor are integrated on chip as floating-node charge adaptation circuitry. To measure the characteristics without any auto-zeroing scheme, the charge adaptation circuitry is disabled by shorting the tunneling and the drain voltages to  $V_{DD}$  supply. The floating-node voltage settles slowly to an equilibrium

Figure 2.5. Setup of capacitive sensing measurement using a capacitive feedback charge amplifier.

Figure 2.6. (a) The measured output signal and noise spectrums. A card type speaker is used as the 1K Hz acoustic signal source and a MEMS microphone is interfaced with the circuit. (b) Measured output signal and noise spectrums when the circuit is interfaced with a linear 2 pF capacitor.

value and the non-inverting terminal voltage can be adjusted so that the output is at the mid-rail.

The spectrum of a 1kHz 1Vrms output waveform with -37dB total harmonic distortion is shown in Fig. 2.6(a). The distortion may come from the cascoded output stage, the amplifier offset, and the nonlinearity of the speaker and the MEMS sensor. In the same plot, we also show the noise spectrum of the capacitive sensing circuit without the MEMS sensor. The calculated total noise power of the circuit in the audio band (i.e. 20Hz to 20kHz with uniform weighting) is  $115 \,\mu V_{rms}$ . The SNR of our circuit can be as high as 78.8dB. The minimum detectable capacitance variance in the audio band is 28 aF. The capacitance sensitivity is  $0.2 \,aF/\sqrt{Hz}$  and the minimum detectable displacement is  $7 \times 10^{-4} \text{\AA}/\sqrt{Hz}$ .

To get rid of the nonlinearity from the speaker and the MEMS sensor, the sensor is

Figure 2.7. (a) Photograph of a chip wire-bonded to an IVUS annular-ring CMUT array. (b) Photograph of a Petri dish placed on top of a DIP40 package. The circuit and the transducers are immersed in a vegetable oil bath during the measurement.

replaced by a 2 pF linear capacitor. A sinusoidal voltage is applied directly to the linear capacitor. When the output signal is 1V peak-to-peak, -60 dB total harmonic distortion is measured as shown in Fig. 2.6(b). The even order harmonic may be due to the offset of the OTA instead of the nonlinearity of the transconductance. Noise spectrum with power consumptions of  $1 \mu W$ ,  $0.23 \mu W$ , and  $0.13 \mu W$  are also shown in Fig. 2.6(b). The extracted total output thermal noise over the entire bandwidth is about  $575 \mu V_{rms}$ , which is slightly higher than the estimated value of  $370 \mu V_{rms}$ .

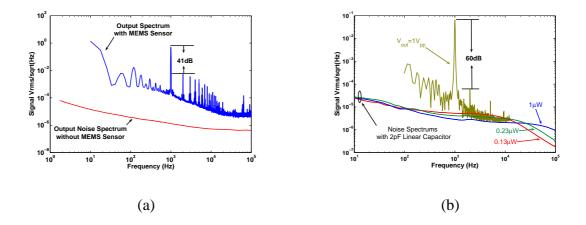

#### 2.2.3 Pulse-Echo Experiment and Results

A version of the charge amplifier that uses a *p*MOS transistor as the charge adaptation feedback is fabricated. As shown in Fig. 2.7(a), the chip with electronics is wire-bonded to a annular-ring IVUS CMUT array [14]. The size of each element is  $70 \,\mu\text{m} \times 70 \,\mu\text{m}$ , giving rise to a measured capacitance of 2 pF, including the parasitic capacitance. A Petri dish with an opening at the bottom is glued on top of the package by epoxy. During measurement, transducers and the circuit are immersed in a vegetable oil bath, as shown in Fig. 2.7(b).

By applying different bias voltage to the feedback transistor, the same circuit can be configured as a TIA or as a charge amplifier. Because the charge effect due to the capacitance change is equivalent to that due to the voltage change, the frequency response of the circuit can be performed by applying an AC signal at one of the CMUT terminals. The

Figure 2.8. Frequency response of a charge amplifier with *pmos* feedback. The input voltage is applied to one of the CMUT terminals. The gate voltage of the transistor can be biased by different voltage to configure the receiver amplifier as a charge amplifier or a TIA. As the operating frequency is below the second pole, the charge amplifier approach can generate larger output magnitude than the TIA approach given the same voltage (or capacitance) variation.

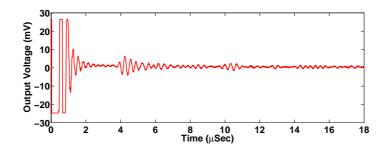

Figure 2.9. Measured pulse-echo response from a charge amplifier. The acoustic source is transmitted from one CMUT device biased by 70V with 20Vpp pulse and the receiver element is bias at 50V. Both devices are immersed in oil. The distance of these two elements is about 3mm. The measured SNR is 16.65dB.

results are shown in Fig. 2.8. As one can see, as long as the operating frequency is less than the second pole, a charge amplifier can obtain a larger output magnitude than the TIA.

The pulse-echo experiment is performed by using one CMUT device as a transmitter and the other element bonded to the circuit as a receiver. The transmitting element is stimulated by a 20V-peak pulse. The receiving device is biased by a 50V DC voltage and the feedback capacitance is extracted as 200 fF. The distance between these two devices is about 6mm corresponding to a pulse-echo distance from a planar target 3mm away. The recorded waveform, shown in Fig. 2.9, indicates a center frequency of 3MHz, which is mainly limited by the amplifier bandwidth. The measured output noise floor is  $2.5 \text{mV}_{rms}$

#### Table 2.1. Performance Comparison

| Lit.                 | [17]         | [19]         | [20]         | [21]                              | [22]              | [23]              | This work |

|----------------------|--------------|--------------|--------------|-----------------------------------|-------------------|-------------------|-----------|

| Approach             | Fig. 2.10(b) | Fig. 2.10(b) | Fig. 2.10(e) | Fig. 2.10(d)                      | Fig. 2.10(h)      | Fig. 2.10(f)      | Fig. 2.5  |

| Diff. Cap.           | Yes          | Yes          | No           | No                                | No                | No                | No        |

| BW (Hz)              | 2K           | 100          | 15K          | 10K                               | 10K               | 10K               | 20K       |

| Noise floor          | 1.12 aF      | 3.75 aF      | 27 dB SPL    | $4.8\mu\mathrm{V}_{\mathrm{rms}}$ | 25 dB SPL         | $30 \mu V_{rms}$  | 28 aF     |

| V <sub>out,max</sub> | 0.13V        | -            | 0.2V         | 0.51V                             | 0.5V              | 0.2V              | 1V        |

| THD                  | -60 dB       | -            | -20 dB       | -40 dB                            | -                 | -50 dB            | -60 dB    |

| SNR (dB)             | 77           | -            | 93           | 80                                | 95                | 54                | ≥ 78      |

| Power                | 30 mW        | 20 mW        | 150 µW       | 96 µW                             | $60\mu\mathrm{W}$ | $24\mu\mathrm{W}$ | 3.3 µW    |

and the measured SNR from the first received acoustic signal is 16.65dB. The power consumption of the charge amplifier is only  $122 \,\mu$ W.

#### 2.2.4 Comparison

One early approach to detecting capacitance change is to use switched-capacitor (SC) circuits containing a charge amplifier, as shown in Fig. 2.10(a). Switches reset the charge on the connecting node. Correlated double sampling (CDS)[15] techniques are also commonly used[16] to reduce low-frequency noise and DC offset. Issues like noise-folding, clock feed-through, and charge sharing need to be taken care of. For applications which require very high sensitivity, lock-in capacitive sensing is one of the most popular techniques[17– 19], as shown in Fig. 2.10(b). Because of the modulation scheme, the circuit consumes lots of power, usually in the milli-watt range, and is very complicated. In either SC or lock-in approaches, circuits process the entire charge on the sensing capacitor, instead of only the portion caused by the minute capacitance change. To cancel the effect of large static capacitance, differential capacitor structures are used; otherwise the output dynamic range will be very limited.

For capacitive microphone MEMS sensors, where the differential capacitor structures are not available, traditional approaches usually convert the capacitive current, instead of

Figure 2.10. Previous approaches to capacitive sensing: (a) Switched-capacitor approach. (b) Lock-in approach. (c) A self-biased JFET source follower as a microphone interface circuit. (d) The current through JFET is sensed and amplified to improve PSRR. (e) to (h) Diodes or linearized OTA are used as a large resistor and the voltage is directly amplified or buffered and then amplified.

Figure 2.11. (a)Reticle on TSMC 0.35um wafer. (b)Layout of annular array CMUT interface electronics.

the charge, into voltage which will be amplified in the following stages. Because of its high input impedance, a self-biased JFET source follower, as shown in Fig. 2.10(c), is the most commonly used interface circuit for electret condenser microphones (ECMs). However, JFET is not compatible to CMOS process and the source follower has poor power supply rejection ratio (PSRR). In [21], the current through the JFET is sensed and amplified to improve the PSRR as shown in Fig. 2.10(d). Another approache uses diodes[20, 22] or a unity-gain feedback OTA[23] as a large resistor to convert current to voltage. The resulting voltages can be amplified directly or can be buffered and amplified by the next stage, as shown in Fig. 2.10. These approaches usually have much less power consumption compared with SC and lock-in techniques. However, the linearity is usually poor. In this work, we can achieve ultra-low power consumption and very large output dynamic range with high linearity. The comparison results are shown in Table 2.1.

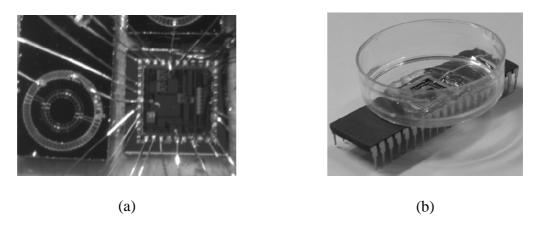

# 2.3 CMOS-FIRST MEMS Integration for CMUTs

Advancements in the processing and integration of MEMS with CMOS open doors to highly integrated sensors with front-end processing. Figure 2.11(a) shows the reticle submitted to TSMC 0.35 *um* fab. Figure **??**(b) shows an example of a layout for an annular array CMUT. The two-chip hybrid approach used until now adds the unwanted parasitics. CMOS-FIRST MEMS integration for CMUTs provides a good solution with reduced parasitics and a one-chip solution. Electronics for three different types of CMUTs with different bandwidths and geomeries are being fabricated on the CMOS wafer (listed in Appendix A). Each chip has digital controls for the selection of different CMUT elements. The core amplifiers are a high input swing folded-cascode topology with a high-speed output buffer. These designs will provide experimental verification of a high-sensitivity CMUT interface along with a good comparison of the traditional transimpedance amplifier approach vs charge amplifier with capacitive feedback and peudo-MOS floating-node stabilization.

To meet the demands of medical ultrasound imaging using high density arrays with CMUT technology, specialized integrated circuits should be custom designed. Because the parasitic interconnect capacitance is a significant factor degrading the SNR, monolithic integration emerges as a viable option. Silicon-based CMUTs enable different array structures and are especially suitable for various levels of electronics integration. Integrated electronics reduces cable count, mitigates parasitic effects and lowers overall cost, and hence is a key factor for successful implementation of catheter-based imaging arrays.

Single-chip or hybrid electronics integration is required for arrays with small element size. Hybrid integration of CMUT array and CMOS electronics through flip-chip bonding is demonstrated in [Wygant (2005)].1]. Single-chip integration of CMOS and CMUT devices includes interleaved CMOS-MEMS integration, where CMUTs are fabricated as an intermediate step in CMOS process flow [2Eccardt (1996), Chen (2008)3], and CMOS before MEMS approaches, where CMUTs are fabricated on CMOS electronics [4, 5].

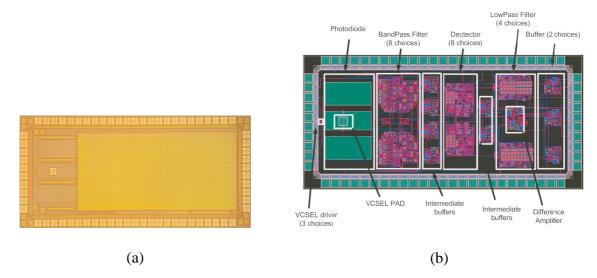

Here we present CMOS design aspects for CMUT-on-CMOS integration. We designed and fabricated 8"wafer using the TSMC 0.35um two-polysilicon four-metal CMOS process. Each wafer contains many chips of size 2 cm 2cm (reticle) containing many smaller IC cells (Fig. 1). We optimized integrated cells with significant design effort to meet the

Figure 2.12. Reticle layout and microphotograph (left) and TSMC 0.35um 8" wafer (right).

| CMUT PARAMETERS |                 |                   |                   |  |  |  |

|-----------------|-----------------|-------------------|-------------------|--|--|--|

|                 | Dual Ring Array | Annular Array     | Linear ICE Array  |  |  |  |

| # of Elements   | 32Rx-24Tx       | 8Rx               | 64Rx              |  |  |  |

|                 | 64Rx-48Tx       | 16Rx              |                   |  |  |  |

| Operation Freq  | 15–25 MHz       | 10–50 MHz         | 3–13 <i>MHz</i>   |  |  |  |

| Element Area    | 70 µm×70 µm     | $100000  \mu m^2$ | $172000  \mu m^2$ |  |  |  |

| $R_{CMUT}$      | $1M\Omega$      | $53k\Omega$       | 31.25 <i>k</i> Ω  |  |  |  |

| $C_{CMUT}$      | 145 fF          | 3 pF              | 5.1 pF            |  |  |  |

Table 2.2. Typical CMUT Parameters for CMUT on CMOS approach

specifications for three different arrays designed for IVUS and ICE applications. The number of receive and transmit elements, operation bandwidth and calculated device capacitances of CMUT arrays used in these applications are presented in Table 1. In this paper we focus our discussion to one particular integrated cell to explain the design process.

Our previous dual-ring imaging study [6] included a 32 RX - 24 TX element CMUT array and 4 IC chips surrounding the array, along with a glass layer to help routing. CMUT

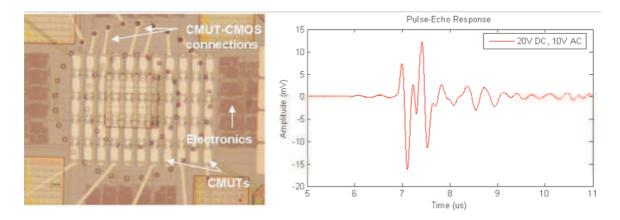

Figure 2.13. CMUT built on CMOS wafer (left) and the received pulse echo data (right).

arrays and IC chips were placed on glass interface chip which was then placed on a 64 pin chip carrier for testing. Such configuration requires more than 100 wirebonds for connections which is quite prone to errors. Hence, CMUT-on-CMOS approach is a remedy for that as it eliminates all those wirebonds. We designed and fabricated an IC chip for monolithic implementation of forward-looking IVUS imaging employing a dual-ring array. A micrograph of this IC is shown in Fig. 2.13. The chip has a die-size of 2 mm 2 mm. It includes all the components of the imaging device, such as transmitters, receivers and control logic. It was optimized to interface a dual-ring array with 32 receive and 24 transmit elements. The chip includes 4 sets of pulser arrays, each containing 6 pulsers. Those pulser arrays are connected to 24 CMUT Tx element connections. There are 4 sets of receiver arrays. Each receiver array includes 8 transimpedance amplifiers, one 81 multiplexer and a buffer to drive cable and pad capacitances. Chip has total of 4 parallel outputs having one from each set of receiver arrays. Digital control block is designed to synchronize transmit and receive element operations in the dual-ring array. It includes an 8 bit counter that generates control bits for pulser and receiver arrays.

#### 2.3.1 Pulse Echo Results

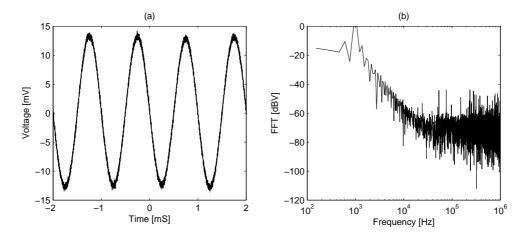

For initial testing, we performed pulse-echo measurements with a CMUT array on an IC consisting of transimpedance amplifiers, multiplexers and buffers to drive 50 and 12 pico

farad cables. The CMUT test array consists of 5 RX and 6 TX elements fabricated on top of this particular cell Fig. 2.13. The electronics shows no degradation after CMUT fabrication. With transimpedance gain of 500 kohm and 3-MHz bandwidth, an echo signal of 28-dB SNR is obtained without any averaging, applying 20-V bias and an external 10-Vpp pulse in a 5-mm deep oil bath. Although used CMUT device is designed for higher frequency operation this test is limited by the low TIA bandwidth that stems from an issue with the fabricated on-chip resistors. We resolved this resistor problem in the new set of wafers and expect to demonstrate higher bandwidth operation.

### **CHAPTER 3**

# ANALOG FRONT-END FOR BIOMIMETIC MICROPHONE

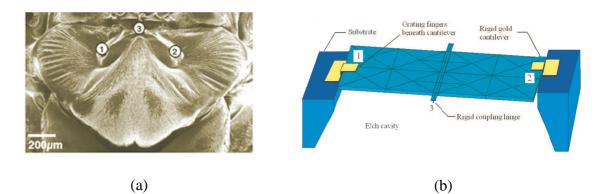

The biomimetic microphone is inspired by the directional acoustic sensing capabilities of a small fly called Ormia ochracea [24]. This fly has an ability to locate the mating singing of crickets in order to lay its eggs on these hosts. When the distance between the ears (1mm apart) of this fly is taken into consideration, the ability of locating sound within 2 degree accuracy is quite challenging. That shows that this fly is able to detect very small pressure differences between the two inlet ports of its ear. The intertympanal membrane of this fly is pivoted from the center by a hinge that couples the two side of the membrane. This ear structure and the design of a diaphragm model that is inspired by this structure can be seen from Fig. 3.1. The coupling effect of the two side of the diaphragm allows this fly to locate the sound without any other information [25].

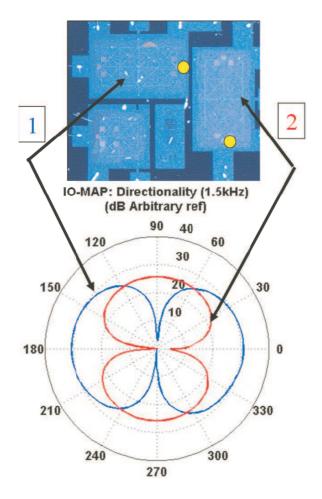

Fabricated biomimetic gradient microphone chip can be seen in Fig. 3.2. One chip contains two gradient and one omnidirectional microphone diaphragms whose measured directivity patterns are also plotted in Fig. 3.2. The chip is fabricated using silicon micro-machining technology. The differential diaphragm of this microphone structure is made of polysilicon and 1mmx2mm in dimensions. The diaphragm is hinged at the center which allows this structure to do 'teeter-tooter' type motion. The gratings and reflective gold

Figure 3.1. (a)Ormia ochracea's ear. (b)Design of biomimetic gradient microphone.

Figure 3.2. Fabricated chip with directionality plots.

backplates are located on each side of the membrane which allows us to use diffraction based optical detection method with these microphone structures [26].

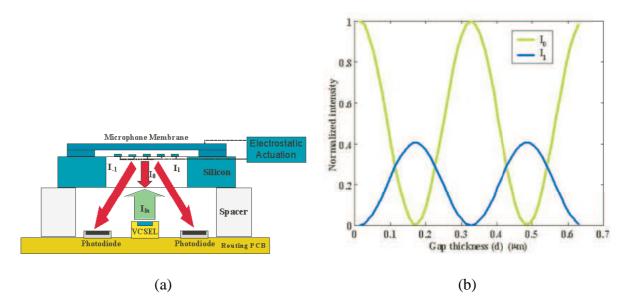

# 3.1 Diffraction Based Optical Detection Method

The basic operating principle of the diffraction based optical displacement detection scheme is shown in Fig. 3.3(a). In this configuration, the top electrode is the microphone diaphragm which serves as a backplate and the bottom electrode is the diffraction grating fabricated on the silicon substrate. Both these electrodes are electrically conductive and optically reflective. The silicon substrate is etched from the backside so that there is an optical path to reach the reflective diffraction grating. In this configuration the diffraction grating is fixed to the substrate and the microphone diaphragm is moving with the incoming sound wave.

However, moving grating with fixed reflective backplate is also an acceptable design. The overall system forms a phase sensitive diffraction grating [27]. A coherent light source illuminates on the back side of the microphone diaphragm through the diffraction fingers. Some of the light is reflected from the diffraction gratings and some reflected from the microphone diaphragm. The reflected light beam returns as a zero order and the diffracted beam causes higher orders. These orders whose intensities are modulated by the movement of the diaphragm by the sound pressure are captured by photodetectors. Using scalar diffraction theory, the beam intensity of the zero and first diffraction orders can be calculated. These first and zero order intensities vs. the gap height can be seen from Fig. 3.3(b) for 650nm optical wavelength. It is clear from this figure that when the gap thickness is a multiple of  $\lambda/2$ , the zero order intensity is a maximum and the diffraction grating acts as a mirror. When the gap thickness is an odd multiple of  $\lambda/4$ , the first order intensity becomes a maximum. To get the highest sensitivity of the diffracted orders, the gap height should be an odd multiple of  $\lambda/8$  where the slope of the intensity curve is a maximum. At this maximum sensitivity point, which is the inflection point, this curve is linear. Any factor that causes the shift of the operating point from the maximum sensitivity point results in nonlinearity

There are many different advantages of this optical detection method when it is integrated with a microphone. In this method, sensitivity does not depend on acoustic frequency, the device capacitance or the device size. Because of the fact that the same sensitivity can be achieved with large membrane and grating distance, the gap can be fabricated large enough to reduce the squeeze film damping effect of the air in the gap. Also, different and novel backplate designs are possible to implement since the capacitance of the device is not too critical. The laser intensity noise can be reduced by using the differential detection (first and zero order). With the differential detection, shot noise limits can be achieved ideally [28]. Integration can be made easier with the fabrication of photodetectors with the integrated amplifiers on a silicon wafer that can be integrated with the microphone

Figure 3.3. (a)Operating principle of the diffraction based optical displacement detection scheme. (b)First and zero order intensities vs. gap thickness curve.

structure. This method also makes the array applications more feasible. The last important advantage of this method is that the electrical port of the microphone is left open. With this port, electrostatic actuation is possible which can be used for tuning the membrane position to get highest sensitivity, tuning the dynamic response of the microphone and applying the force feedback operation to alter the device dynamics in a desired manner.

## **3.2** Integration of Optical Displacement Detection and Challenges

The highly sensitive optical displacement detection methods implemented in a small volume and with reduced power consumption have the potential to compete with commonly used capacitance-based methods in micromechanical sensor systems. The traditional capacitive acoustic sensors do not scale down favorably. In other words, reducing the membrane size decreases the ratio of the active capacitance to the parasitic capacitance, thereby requiring a gain in mechanical compliance, which in turn necessitates the use of very thin, low-stress membranes, that are difficult to reproduce in a repeatable manner. Reducing the membrane gap to increase the active capacitance can increase the stiffness of the trapped air and reduce the electrical sensitivity by limiting the sustainable electric field. To address

#### **Acoustic Pressure**

Figure 3.4. System level block diagram for the Optical MEMS hearing aid.

these problems, optical techniques are used with diffraction gratings as a method to measure displacement from acoustic pressure in microphones. This hybrid integrated system can be implemented in acoustic-sensor applications using both continuous wave and pulse VCSEL to show reduced power consumption.

Optical methods have advantages in small displacement sensing applications primarily because the sensitivity is independent of device capacitance. Optical fiber based sensors have been commonly used for optical detection, but integration of optical fibers with micromachined structures in small volume is quite challenging, and these sensing methods are susceptible to external mechanical noise sources. Recently, diffraction based methods have emerged for compact integration of optical interferometric methods with micromachined structures. Furthermore, VCSELs enables further integration possibilities due to various favorable properties, such as the small chip dimension, out of plane light emission, and low power consumption [2].

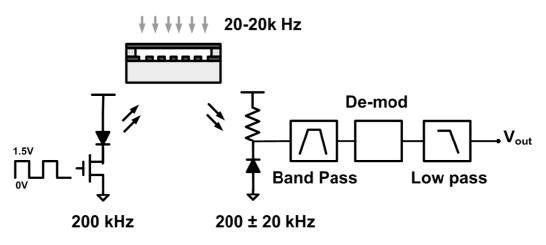

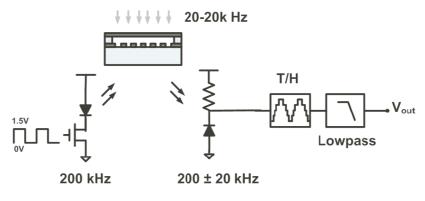

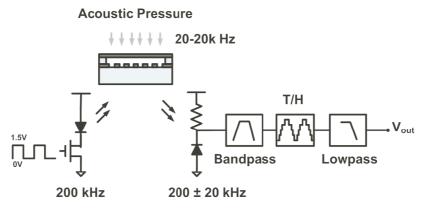

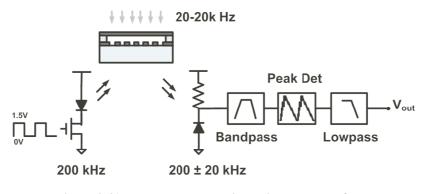

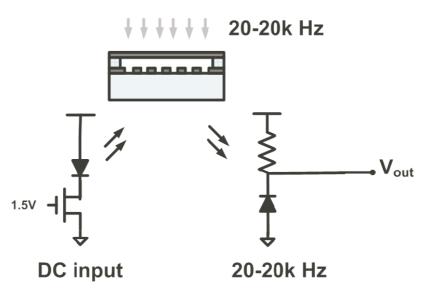

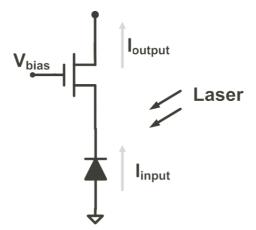

## 3.3 Optical MEMS Microphone Receiver Architecture

Fig. 3.4 shows the receiver system level electronics interface for the Optical MEMS hearing aid sensor. A VCSEL is used to generate the incident optical pulse on to the MEMS sensor. The duty cycle of the VCSEL is minimized to keep the power down on the transmit end. A simple CMOS switch is used to pulse VCSEL current, which turns the VCSEL on and off with 200kHz input carrier pulse. This incident pulse is modulated with the acoustic pressure in the audio band.

On the receive end of the modulated light, a photodiode is used along with a passive on-chip resistor to do front-end detection. The signal is first cleaned with a bandpass filter centered at 200kHz to remove low frequency content along with undesirable 1/f noise. Then the signal is feed into a demodulator to extract our signal of interest in the 20kHz audio band. Finally, the signal is further cleaned with a low pass filter at 20KHz to remove ripples and high frequency contents.

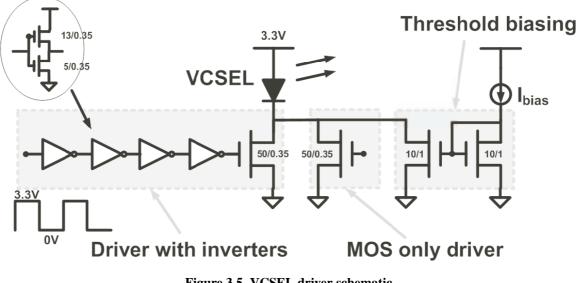

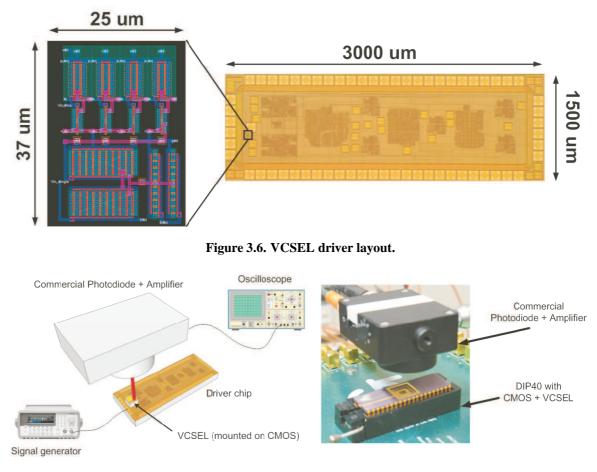

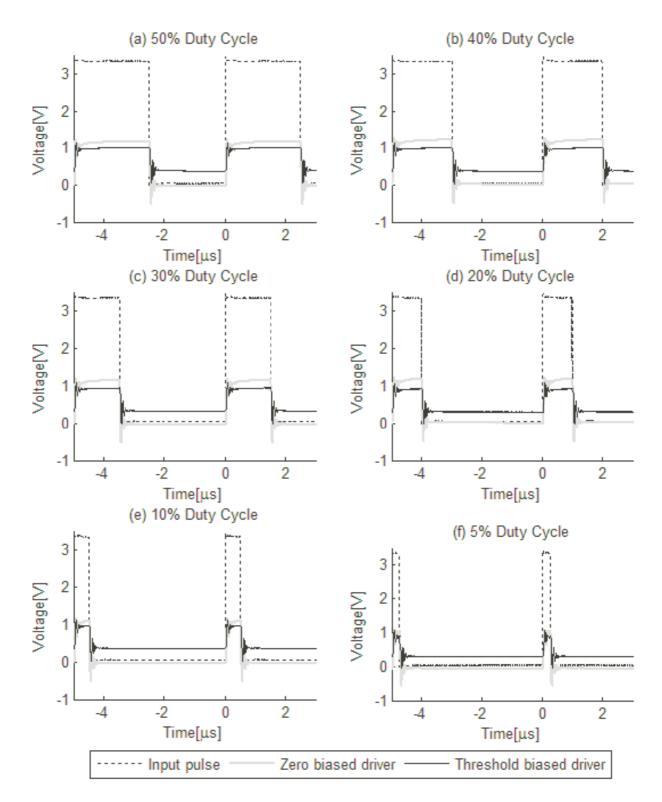

## 3.4 VCSEL Driver in Standard CMOS

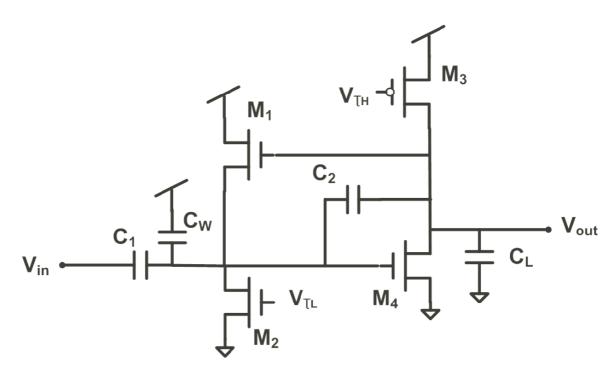

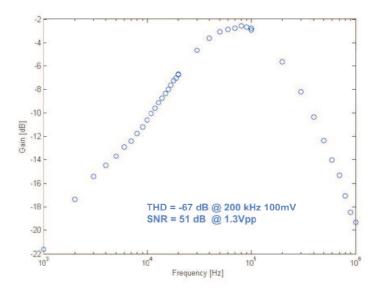

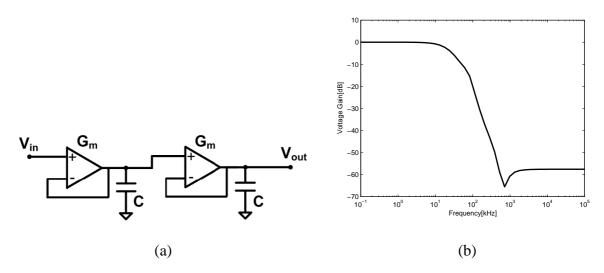

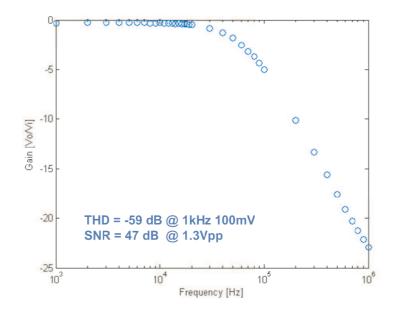

Power consumption is one of the major design constraints for the microphone. The electronics are designed in weak inversion to consume minimum currents with audio frequency bandwidth requirements. The whole receive chain for the continuous time case, can operate for less than 50uA of current from 1.5V battery supply. This leaves us with the power drain at the transmitter side. VCSEL is the most power hungry block in the whole system. One of the main push to use pulsed approach is to cut down average current levels in VCSEL. The reduction in the duty cycle of the pulse can even reduce the average easily less that 1mA.