# EFFICIENT PROGRAMMING OF MASSIVE-MEMORY MACHINES

A Dissertation Presented to The Academic Faculty

by

Alexander M. Merritt

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Computer Science

Georgia Institute of Technology December 2017

Copyright © 2017 by Alexander M. Merritt

# EFFICIENT PROGRAMMING OF MASSIVE-MEMORY MACHINES

Approved by:

Professor Ada Gavrilovska, Committee Chair School of Computer Science *Georgia Institute of Technology*

Professor Karsten Schwan, Advisor School of Computer Science *Georgia Institute of Technology*

Professor Taesoo Kim School of Computer Science Georgia Institute of Technology Professor Umakishore Ramachandran School of Computer Science Georgia Institute of Technology

Professor Moinuddin K. Qureshi School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Dejan S. Milojicic Hewlett Packard Labs *Hewlett Packard Enterprise*

Date Approved: July 28, 2017

To my wife, who does everything with me.

# PREFACE

The latest git version identifier used for the Nibble source code in this dissertation is dd1adf23d9dbc3c64174668512dff7a79f8dc4d5 on July 14, 2017.

## ACKNOWLEDGEMENTS

The work in this dissertation was supported by Karsten Schwan and Ada Gavrilovska, both of my advisors whom I would like to thank, for pushing me and always being available for sharing their guidance.

Many students of our lab shared their time, feedback, and coffee breaks with me, all of which served valuable moments of my life during my PhD at the university. Vishakha Gupta-Cledat was my senior mentor during my early years; Naila Farooqui is a valuable friend, who studied for the qualifier exam with me; Sudarsun Kannan, Jeff Young, Jai Dayal, Hrishikesh Amur, Vishal Gupta, Mukil Kesavan, Priyanka Tembey, Min Lee gave me their time during many random moments; many other colleagues I shared my time with I would like to thank for various aspects. Susie McClain was (and is) utmost supportive in assisting with all aspects surrounding the lab and support for the students (e.g. when needing more paper for printing, or to subsequently shred it).

Many courses were valuable in fostering my knowledge of Computer Science and surrounding disciplines. I particularly enjoyed courses with Moin Qureshi, Nick Feamster, Hyesoon Kim, and opportunities to both be a teaching assistant for and independently teach the undergraduate course CS 3210 Design of Operating Systems (together with Jai Dayal) supported by Matt Wolf and Karsten Schwan. An independent study with Sudhakar Yalamanchili gave me the opportunity to work together with Jeff Young on an alternative aspect of cluster computing.

I would like to specially thank Dejan Milojicic for having a multi-faceted role in my PhD – as a mentor, committee advisor, colleague, and supporter – without whom I would not have learned as much as I know now. He facilitated the effort during one summer to work closely with two colleagues – and now friends – Gerd Zellweger and Izzat El Hajj, all of whom I valued working with very much.

The Graduate Student Counsel provided me with much-needed funding many times to visit conferences throughout the years. H. Venkateswaran I would like to thank for his oft-sought advice.

Not least, I wish to thank each of my PhD committee members – Dejan, Taesoo, Moin, Ada, and Kishore – for their time and feedback to review my work, early drafts of papers, and advice.

# TABLE OF CONTENTS

| DE  | DICA  | TION                                                                 | iii |

|-----|-------|----------------------------------------------------------------------|-----|

| PR  | EFAC  | Е                                                                    | iv  |

| AC  | KNO   | WLEDGEMENTS                                                          | v   |

| LIS | ST OF | TABLES                                                               | ix  |

| LIS | ST OF | FIGURES                                                              | x   |

|     | MMA   |                                                                      | xiv |

| I   | INT   | RODUCTION                                                            | 1   |

| 1   |       |                                                                      |     |

|     | 1.1   | Thesis Statement                                                     | 4   |

|     | 1.2   | Contributions                                                        | 5   |

| Π   | BAC   | CKGROUND AND MOTIVATION                                              | 6   |

|     | 2.1   | The Advent of Large Memory Multi-core Machines                       | 6   |

|     | 2.2   | Software Challenges in Programming Large Systems                     | 12  |

|     |       | 2.2.1 Key-Value Stores for Managing Large Datasets                   | 12  |

|     |       | 2.2.2 Virtual Memory Interfaces in the Operating System are Limiting | 16  |

|     |       | 2.2.3 Summary                                                        | 19  |

| III | SCA   | ALABLE MEMORY EFFICIENT KEY-VALUE STORES                             | 20  |

|     | 3.1   | Background and Motivation                                            | 20  |

|     | 3.2   | Scaling Log-Structured Systems                                       | 22  |

|     |       | 3.2.1 The Index - Enabling Concurrent Operations                     | 22  |

|     |       | 3.2.2 Supporting Scalable Asynchronous Compaction                    | 23  |

|     |       | 3.2.3 Prioritizing High, Sustained Write Throughputs                 | 24  |

| IV  | NIB   | BLE - A CONCURRENT LOG-STRUCTURED KEY-VALUE STORE                    | 26  |

|     | 4.1   | System Overview                                                      | 26  |

|     | 4.2   | Overview - Index, Objects, and Segments.                             | 26  |

|     | 4.3   | Optimistic Concurrency - The Index                                   | 28  |

|     | 4.4   | Multi-Head Log Allocation                                            | 29  |

|     | 4.5   | Distributed Hardware Epochs For Coordination                         | 33  |

|                      | 4.6                                                                                                                                                                           | Hardware Assumptions                                                                                             | 35                                                                       |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| $\mathbf{V}$         | NIB                                                                                                                                                                           | BLE - EVALUATION                                                                                                 | 36                                                                       |

|                      | 5.1                                                                                                                                                                           | Breakdown of Components                                                                                          | 39                                                                       |

|                      | 5.2                                                                                                                                                                           | Memory Overhead                                                                                                  | 41                                                                       |

|                      | 5.3                                                                                                                                                                           | Dynamic Workloads — Postmark                                                                                     | 42                                                                       |

|                      | 5.4                                                                                                                                                                           | Data-Serving Workloads — YCSB                                                                                    | 45                                                                       |

| VI                   | AN                                                                                                                                                                            | ANALYSIS OF COMPACTION                                                                                           | 49                                                                       |

|                      | 6.1                                                                                                                                                                           | Breakdown of Compaction                                                                                          | 49                                                                       |

|                      | 6.2                                                                                                                                                                           | Relaxing the nature of the log-structured design                                                                 | 53                                                                       |

|                      | 6.3                                                                                                                                                                           | Evaluation – Nibble-2                                                                                            | 60                                                                       |

|                      | 6.4                                                                                                                                                                           | Summary                                                                                                          | 63                                                                       |

| VII                  | SYS                                                                                                                                                                           | TEMS CHALLENGES WITH IN-MEMORY COMPUTING                                                                         | 65                                                                       |

|                      | 7.1                                                                                                                                                                           | Memory Sizes > Address Bits                                                                                      | 65                                                                       |

|                      | 7.2                                                                                                                                                                           | Limited control over in-memory data organization                                                                 | 71                                                                       |

|                      | 7.3                                                                                                                                                                           | Summary                                                                                                          | 77                                                                       |

| <b>*</b> 7 <b>**</b> | LADI                                                                                                                                                                          | DRESS SPACES - NEW ABSTRACTIONS FOR MEMORY                                                                       | 79                                                                       |

| VII                  | ΙΑΡΙ                                                                                                                                                                          | <b>TRESS STACES - NEW ADSTRACTIONS FOR MEMORI</b>                                                                | 19                                                                       |

| VП                   | 8.1                                                                                                                                                                           | SpaceJMP - an Operating System Model                                                                             | 80                                                                       |

| VII                  |                                                                                                                                                                               |                                                                                                                  |                                                                          |

| VII<br>IX            | 8.1<br>8.2                                                                                                                                                                    | SpaceJMP - an Operating System Model                                                                             | 80                                                                       |

|                      | 8.1<br>8.2<br>SPA                                                                                                                                                             | SpaceJMP - an Operating System Model                                                                             | 80<br>87                                                                 |

| IX                   | 8.1<br>8.2<br>SPA<br>EVA                                                                                                                                                      | SpaceJMP - an Operating System Model          Summary          CEJMP - REFERENCE IMPLEMENTATION IN DRAGONFLY BSD | 80<br>87<br><b>88</b>                                                    |

| IX                   | <ul> <li>8.1</li> <li>8.2</li> <li>SPA</li> <li>EVA</li> <li>10.1</li> </ul>                                                                                                  | SpaceJMP - an Operating System Model                                                                             | 80<br>87<br>88<br>94                                                     |

| IX                   | <ul> <li>8.1</li> <li>8.2</li> <li>SPA</li> <li>EVA</li> <li>10.1</li> <li>10.2</li> </ul>                                                                                    | SpaceJMP - an Operating System Model                                                                             | 80<br>87<br><b>88</b><br><b>94</b><br>94                                 |

| IX                   | <ul> <li>8.1</li> <li>8.2</li> <li>SPA</li> <li>EVA</li> <li>10.1</li> <li>10.2</li> <li>10.3</li> </ul>                                                                      | SpaceJMP - an Operating System Model                                                                             | 80<br>87<br><b>88</b><br>94<br>94                                        |

| IX                   | <ul> <li>8.1</li> <li>8.2</li> <li>SPA</li> <li>EVA</li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> </ul>                                                        | SpaceJMP - an Operating System Model                                                                             | 80<br>87<br><b>88</b><br>94<br>94<br>96<br>98                            |

| IX                   | <ul> <li>8.1</li> <li>8.2</li> <li>SPA</li> <li>EVA</li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> </ul>                                          | SpaceJMP - an Operating System Model                                                                             | 80<br>87<br><b>88</b><br>94<br>94<br>96<br>98<br>99                      |

| IX<br>X              | <ul> <li>8.1</li> <li>8.2</li> <li>SPA</li> <li>EVA</li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li>REI</li> </ul>                             | SpaceJMP - an Operating System Model                                                                             | 80<br>87<br><b>88</b><br>94<br>96<br>98<br>99<br>99                      |

| IX<br>X              | <ul> <li>8.1</li> <li>8.2</li> <li>SPA</li> <li>EVA</li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li>REI</li> <li>11.1</li> </ul>               | SpaceJMP - an Operating System Model                                                                             | 80<br>87<br><b>88</b><br>94<br>96<br>98<br>99<br>99<br>99                |

| IX<br>X              | <ul> <li>8.1</li> <li>8.2</li> <li>SPA</li> <li>EVA</li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li>REI</li> <li>11.1</li> <li>11.2</li> </ul> | SpaceJMP - an Operating System Model                                                                             | 80<br>87<br><b>88</b><br>94<br>96<br>98<br>99<br>99<br><b>101</b><br>101 |

| 11.5 Garbage collection systems           | 05  |

|-------------------------------------------|-----|

| 11.6 Operating Systems and Address Spaces | .06 |

| 11.7 Hardware Address Space Support       | .09 |

| XII CONCLUSION                            | 111 |

| 12.1 Extensions and Opportunities         | 12  |

| 12.1.1 Load-Balancing in Nibble           | 12  |

| 12.1.2 Index Optimizations in Nibble      | 13  |

| 12.1.3 Hybrid DRAM + NVM Machines         | 14  |

| 12.1.4 Hardware Extensions                | 15  |

| 12.1.5 Miscellaneous                      | .16 |

| 12.2 Closing Remarks                      | 16  |

| REFERENCES                                | 18  |

# LIST OF TABLES

| 1 | Example single-system large-memory machines. Total Memory bandwidth is a sum of bandwidth to local memory across sockets. *64 TiB is a limit of the CPU, not the platform, able to address only $2^{46}$ bytes of physical memory. | 7  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | Example large-memory networked machines. "The Machine" is a datacenter system, and Summit an HPC machine.                                                                                                                          | 7  |

| 3 | Summary of compared systems.                                                                                                                                                                                                       | 37 |

| 4 | Summary of workloads                                                                                                                                                                                                               | 37 |

| 5 | Large-memory platforms used in this study.                                                                                                                                                                                         | 94 |

| 6 | Breakdown of <i>context switching</i> . Measurements on M2 in cycles. Numbers in <b>bold</b> are with the use of CPU cache TLB tagging                                                                                             | 94 |

# LIST OF FIGURES

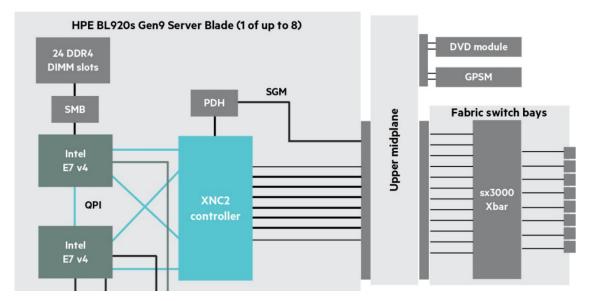

| 1  | HPE Superdome X system design – a custom controller connects to each processor via QPI channels, establishing a large load/store domain to all of memory. Reproduced from [9].                                                                                                                                                                                                                                                                  | 9  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

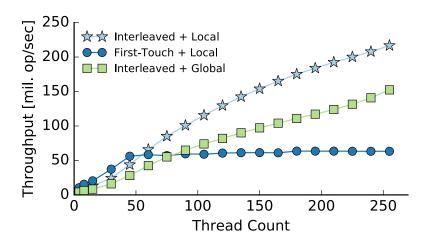

| 2  | Figure showing the effect of data placement within a 16-socket machine on the performance of a concurrent implementation of a hash table (Cuckoo)                                                                                                                                                                                                                                                                                               | 10 |

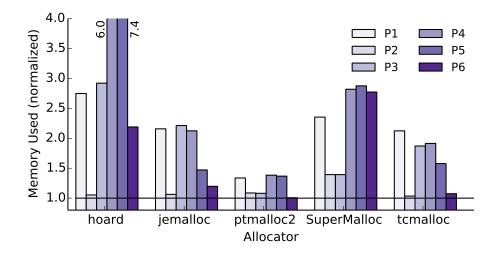

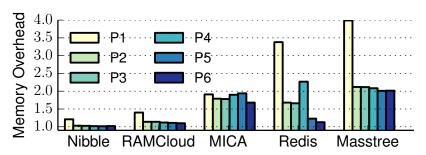

| 3  | Figure showing a measure of memory bloat in common general-purpose heap alloca-<br>tors. P1-P6 are object sizes. P1-P6 are explained in Figure 14b                                                                                                                                                                                                                                                                                              | 13 |

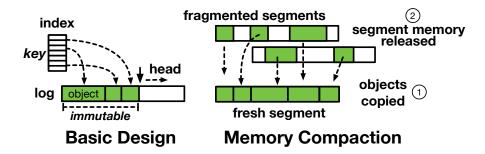

| 4  | Figure illustrating a high-level view of log-structured allocation.                                                                                                                                                                                                                                                                                                                                                                             | 14 |

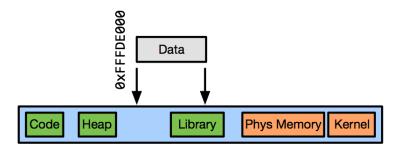

| 5  | Data region cannot be mapped into the current address space because of a conflict with an existing library mapping.                                                                                                                                                                                                                                                                                                                             | 17 |

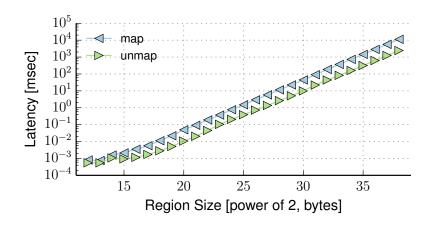

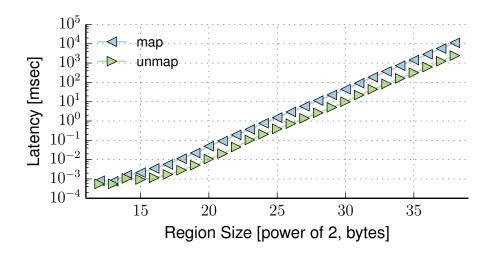

| 6  | Cost of mapping virtual memory using 4 KiB page sizes to preallocated physical memory. Costs are directly a result of page table modifications.                                                                                                                                                                                                                                                                                                 | 18 |

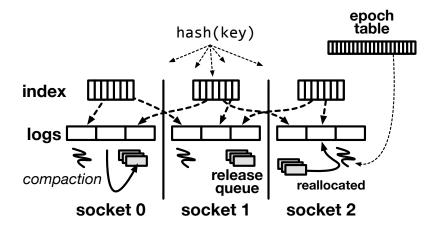

| 7  | High-level design of Nibble. A global index is partitioned across sockets, pointing to objects anywhere within the system. Logs, segments, and compaction activities are isolated to the cores and memory within each socket.                                                                                                                                                                                                                   | 27 |

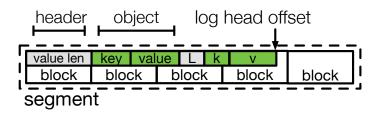

| 8  | A segment – a container of blocks holding objects.                                                                                                                                                                                                                                                                                                                                                                                              | 27 |

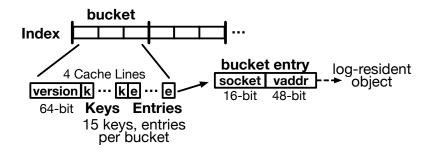

| 9  | The hash table with optimistic concurrency. Buckets are in-lined and entries searched for via linear probing. Nibble allocates 15 entries and one version counter per bucket. Update operations will atomically increment the version to an odd value, blocking new traversals into the bucket, and forcing in-progress reads to restart. Once complete, the version is bumped again, allowing read operations to scan the bucket concurrently. | 28 |

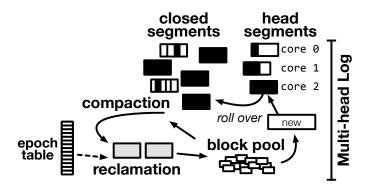

| 10 | Decomposition of one multi-head log in Nibble                                                                                                                                                                                                                                                                                                                                                                                                   | 29 |

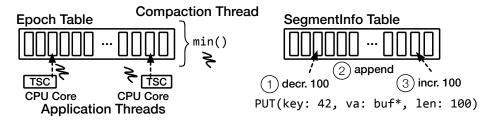

| 11 | Illustration of synchronization between application threads recording their current epochs, and compaction threads determining minimum epoch for recycling segment memory (left), and updating the live bytes information for segments (right).                                                                                                                                                                                                 | 33 |

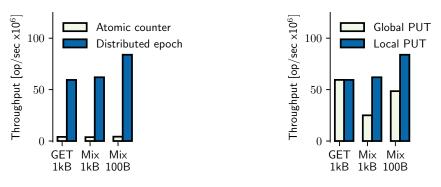

| 12 | Performance breakdown of various designs in Nibble: uniform YCSB 240 threads (Mix is a 50:50 ratio of PUT and GET).                                                                                                                                                                                                                                                                                                                             | 39 |

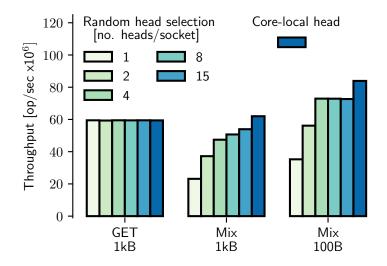

| 13 | Performance breakdown of use of multiple log heads in Nibble: uniform YCSB 240 threads (Mix is a 50:50 ratio of PUT and GET). With PUT to local memory, more heads provide the greatest initial performance gains. Selecting the core-specific head, we avoid further contention, gaining an additional 15%.                                                                                                                                    | 40 |

| 14 | Measured memory overhead (bloat)                                                                                                                                                                                                                                                                                                                                                                                                                | 41 |

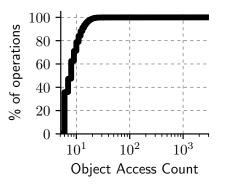

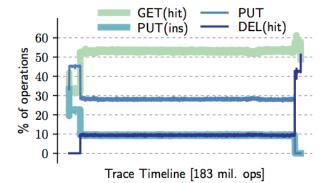

| 15 | Characteristics of our trace captured from Postmark. Overall, the workload presents a dynamic behavior: most objects are accessed infrequently, yet a consistently high churn in objects is present. 20% of all operations will add or remove objects, putting                                                                                                                                                                                  | 10 |

|    | stress on each system's object allocator logic.                                                                                                                                                                                                                                                                                                                                                                                                 | 43 |

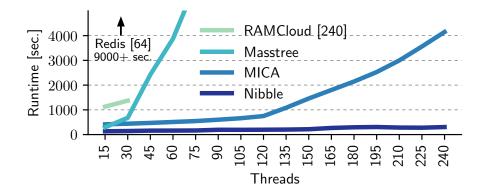

| 16 | Weak scaling of our Postmark trace, measured in time- to-completion, at a consistent 17% memory utilization: as each thread executes the entire trace on a private working set, we increase available memory as appropriate (except for Masstree). Nibble completes the trace within a few minutes, whereas the other systems require upwards of an hour or more with more threads. RAMCloud was able to run with only 2% utilization until system memory was insufficient. | 44 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

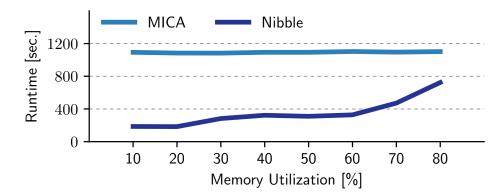

| 17 | From Figure 16 we measure time-to-completion for Nibble and MICA at 135 threads, and progressively decrease available memory. At 65% utilization, Nibble's runtime doubles due to compaction costs. MICA seems unaffected, however any such effect is masked by contention on its per-core heap allocators.                                                                                                                                                                 | 44 |

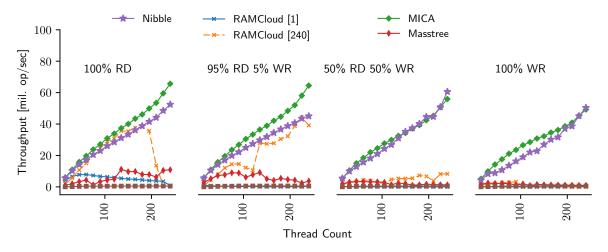

| 18 | Uniform YCSB throughput measurements on 1 TiB of data – ca. 230 1 KiB objects.<br>"95% RD 5% WR" is a workload with GET composing 95% of all operations and<br>5% with PUT. No configuration uses DEL. Approximately 8 TiB of storage capacity<br>was provided to ensure a low utilization rate of ca. 12%.                                                                                                                                                                 | 45 |

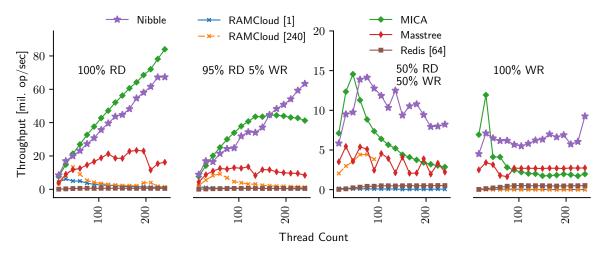

| 19 | Zipfian YCSB throughput measurements on 1 TiB of data – ca. 230 1 KiB objects.<br>"95% RD 5% WR" is a workload with GET composing 95% of all operations and<br>5% with PUT. No configuration uses DEL. Approximately 8 TiB of storage capacity<br>was provided to ensure a low utilization rate of ca. 12%.                                                                                                                                                                 | 46 |

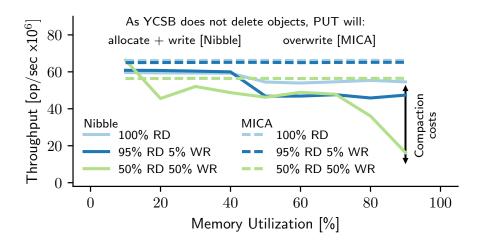

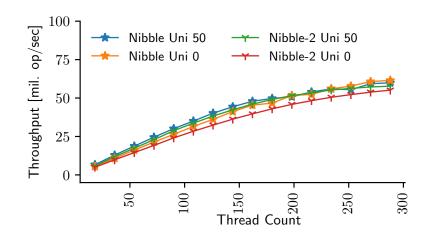

| 20 | Throughput of MICA and Nibble driven with YCSB (uniform) using all 240 cores, steadily increasing the capacity used                                                                                                                                                                                                                                                                                                                                                         | 47 |

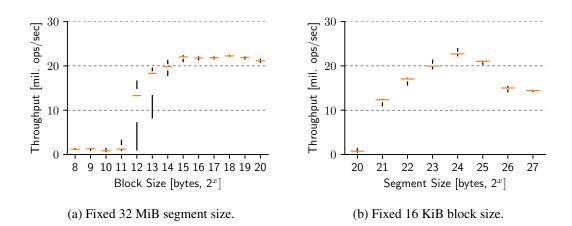

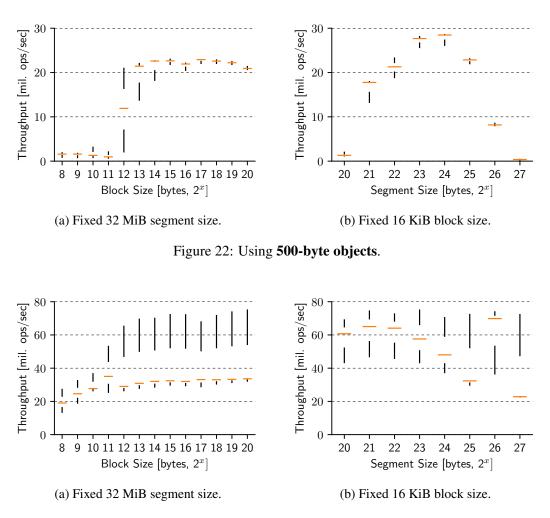

| 21 | Effect of varying the block and segment size in Nibble on the throughput, executing YCSB (uniform) with <b>1-KiB objects</b> on smaug-3. 224 client threads in total, with 8 compaction threads per socket, on 1 TiB of data at 90% fill capacity (1.1 TiB total memory allocated to Nibble). Three runs executed, showing the median, and standard deviation.                                                                                                              | 51 |

| 22 | Using <b>500-byte objects</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51 |

| 23 | Using <b>64-byte objects</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51 |

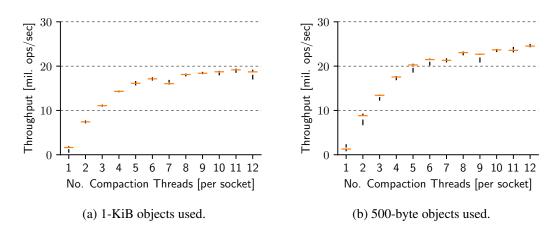

| 24 | Effect of varying the number of compaction threads in Nibble (per socket) on the throughput, executing YCSB (uniform) on smaug-3. 224 client threads in total, on 1 TiB of data at 90% fill capacity (1.1 TiB total memory allocated to Nibble). Three runs executed, showing the mean, and standard deviation.                                                                                                                                                             | 52 |

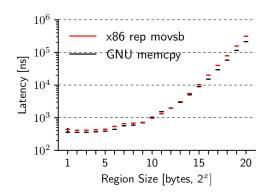

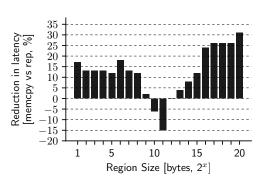

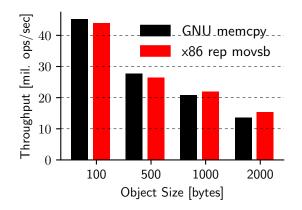

| 25 | Latency of memory copy mechanism as the size of the copy region varies. Source and destination locations are in local memory only.                                                                                                                                                                                                                                                                                                                                          | 54 |

| 26 | Performance as a function of memory copy mechanism. Client threads copying in/out objects use the x86 rep movsb mechanism; only the compaction's use of memory movement was modified. Shown are four object sizes, executed with 224 client threads at 90% capacity utilization, running YCSB uniform.                                                                                                                                                                      | 54 |

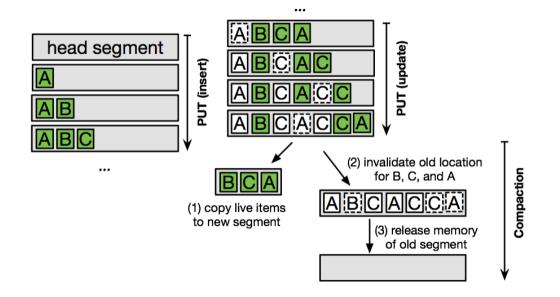

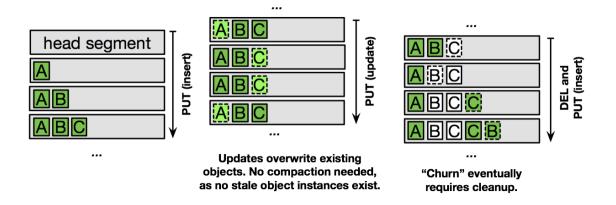

| 27 | Operations that update existing objects by appending new instances to the log heads create unnecessary work for compaction to perform: object versioning occurs, and is unused in Nibble. Dashed box outlines indicate values that are made stale due to an update.                                                                                                                                                                                                         | 55 |

|    | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 28 | By allowing update operations, such as used by PUT, to overwrite existing object locations (subject to constraints such as the new size is $\leq$ existing allocation size) we can avoid creating unnecessary cleanup work for compaction threads. Light-green boxes indicate objects overwritten with new data (operation sequence is identical to the prior figure). When new objects are inserted (their keys do not exist in the index) do we perform a bump allocation in the log head, and append the item. Only when such operations — insertion and deletion — occur frequently, will compaction be necessary. <i>Workloads that never insert or delete objects (e.g., after loading the initial working set) will not incur overheads due to compaction</i> . | 57 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

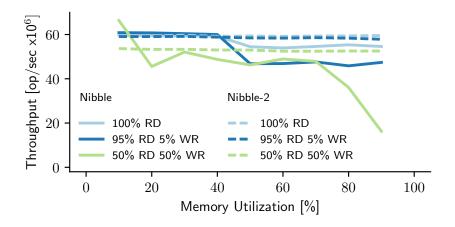

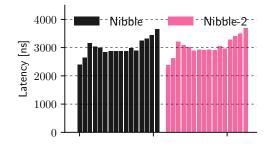

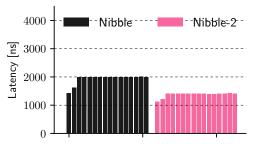

| 29 | Throughput comparison of Nibble and Nibble-2 on YCSB (uniform) with 240 threads on the HPE Superdome X (smaug-1). As the amount of available memory decreases, compaction costs draw performance down in Nibble. The dip at 50% is due to compaction threads triggered into polling in attempts to reduce fragmentation. Nibble-2 experiences zero compaction, as all PUT operations overwrite existing objects. YCSB does not delete or insert objects.                                                                                                                                                                                                                                                                                                               | 61 |

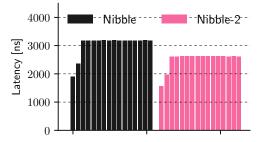

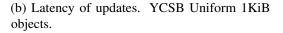

| 30 | Comparison of Nibble and Nibble-2 for YCSB Uniform distribution accesses of 1<br>KiB objects. '50' means 50:50 ratio between PUT (update) and GET; '0' means<br>a pure-PUT (update) workload configuration. Nibble-2 shows a slight drop in<br>throughput for the pure-PUT workload, as it breaks the "local-write global-read"<br>policy, updating objects wherever they happen to reside in memory; Nibble always<br>updates by append to local memory.                                                                                                                                                                                                                                                                                                              | 62 |

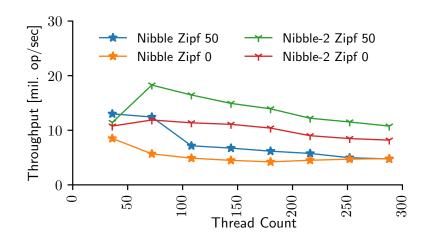

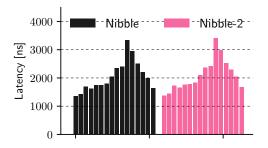

| 31 | Comparison of Nibble and Nibble-2 for YCSB Zipfian distribution accesses of 1<br>KiB objects. '50' means 50:50 ratio between PUT (update) and GET; '0' means a<br>pure-PUT (update) workload configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62 |

| 32 | Latency for PUT between Nibble and Nibble-2 for a single thread running without contention at low utilization. Insert behavior for PUT shows no difference in performance, as both systems behave the same (append). Update for Nibble-2 shows roughly a 15% reduction in latency for a PUT of 1-KiB objects to local memory.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63 |

| 33 | Latency for PUT between Nibble and Nibble-2 for a single thread running without contention at low utilization. Insert behavior for PUT shows no difference in performance, as both systems behave the same (append). Update for Nibble-2 shows roughly a 25% reduction in latency for a PUT of 64-byte objects to local memory.                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63 |

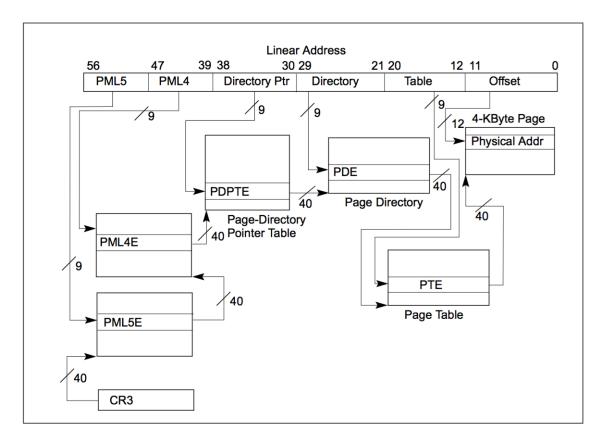

| 34 | Linear-address translation using 5-level paging. From Intel's white paper 5-Level Paging and 5-Level EPT, document number 335252-002, revision 1.1 [12].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66 |

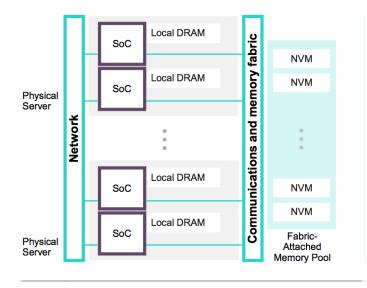

| 35 | Diagram of The Machine as a memory-centric system, reproduced from [99]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68 |

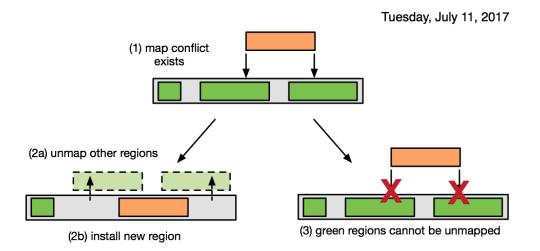

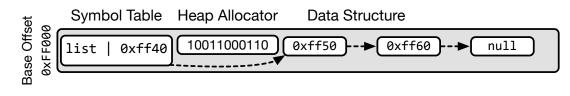

| 36 | Figure illustrating how to access an alternate memory region in (1) that either (a) does not fit, or (b) conflicts with one or more existing regions (e.g., if the new region requires a specific base virtual address). (2a)-(2b) illustrate unmapping the conflicting regions; (3) if they cannot be unmapped (e.g., the application may have stored references into such regions, which we cannot track), then the new region cannot be mapped at the required location (e.g., otherwise pointers must be swizzled).                                                                                                                                                                                                                                                | 72 |

| 37 | Cost of creating a mapping in a page table with 4-KiB pages, as a function of the size of the region. Measured on Linux.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74 |

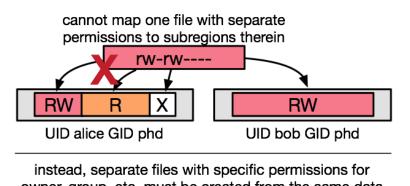

| 38 | Figure illustrating how sharing in-memory data among multiple processes with varying access rights to disjoint subsets of the data. An individual file is insufficient to express relationships such as these, and programmers must use system administration access policies on multiple files to accurately express and enforce them                                                                                                                                                                                                                                                                      | 76 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

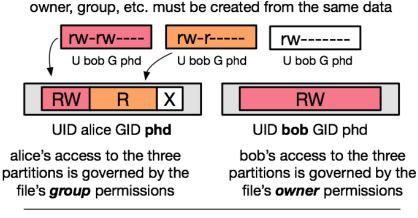

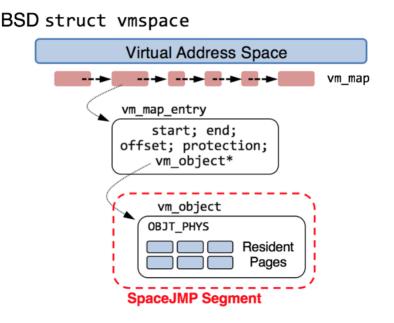

| 39 | Example segment. Segments are a contiguous region of virtual memory, composed of physical memory pages, with a base address and a length. The segment shown contains a symbol table and heap allocator context that a process may use to create and manipulate memory-resident data structures, e.g. a linked list.                                                                                                                                                                                                                                                                                         | 81 |

| 40 | API in SpaceJMP for managing address spaces and memory segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 81 |

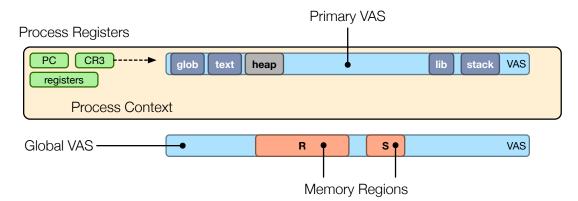

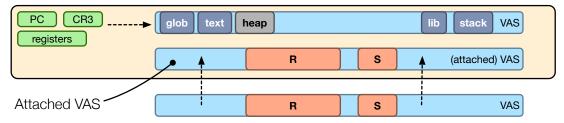

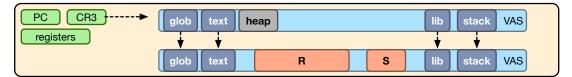

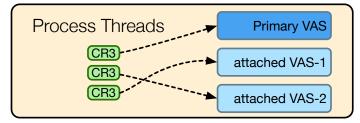

| 41 | Examples of virtual address space types and their uses by a process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83 |

| 42 | Process Alice creating a memory segment with shared data for other processes to attach to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 86 |

| 43 | Process Bob attaching to the "shared" named address space and accessing the com-<br>mon data within.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86 |

| 44 | Illustration of a virtual address space in DragonFly BSD, VM objects. The imple-<br>mentation of a segment and address space in SpaceJMP are simply wrappers around<br>each                                                                                                                                                                                                                                                                                                                                                                                                                                 | 89 |

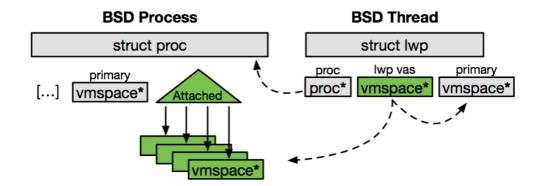

| 45 | Figure illustrating modifications made to the BSD process and thread structures.<br>Green shapes are additions. A process maintains a set of references to attached<br>address spaces, and each thread an additional reference to its active address space, if<br>not currently in the primary.                                                                                                                                                                                                                                                                                                             | 90 |

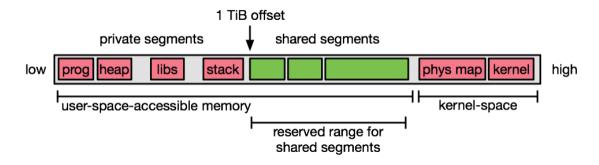

| 46 | Diagram to show the private, shared, reserved segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 90 |

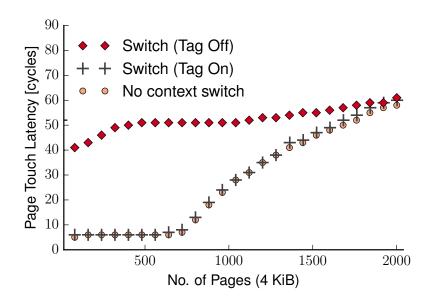

| 47 | Latency to access one cache line within a random page between context switches – simply modifying the base address of the active translation page table in the processor, held in CR3. When CR3 is modified, the CPU will automatically (for x86-based processors) flush the TLB. With a small number of pages, the translation state will fit within the TLB, illustrating the direct impact of flushing the TLB on memory load latencies. As the working set size increases, we see the effect of the TLB capacity to translate for a random-access workload, where tagging exhibits diminished benefits. | 95 |

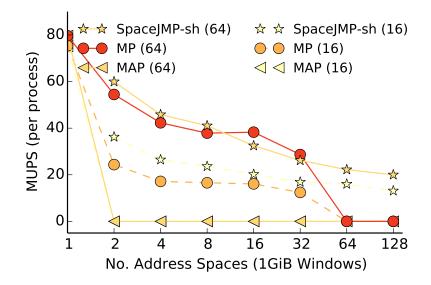

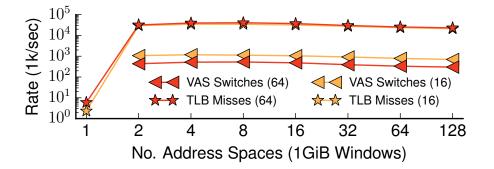

| 48 | Comparison of three designs to program large memories with GUPs M3. Update set sizes 16 and 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 96 |

| 49 | Rate of VAS switching and TLB misses for GUPS executed with SpaceJMP, averaged across 16 iterations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97 |

### SUMMARY

New and emerging memory technologies combined with enormous growths in data collection and mining within industry are giving rise to servers with massive pools of main memory — terabytes of memory, disaggregated bandwidth across tens of sockets, and hundreds of cores. But, these systems are proving difficult to program efficiently, posing scalability challenges for all layers in the software stack, specifically in managing in-memory data sets. Larger and longer-lived data sets managed by key-value stores require minimizing over- commitments of memory, but current designs trade off performance scalability and memory bloat. Furthermore, opaque operating system abstractions like virtual memory and ill-matched, non-portable interfaces used to manipulate them make the expression of semantic relationships between applications and their data difficult: sharing in-memory data sets requires careful control over internal address mappings, but mmap, ASLR, and friends remove this control.

To explore and address these challenges, this dissertation is composed of two pieces: (1) We introduce and compare a new design for key-value stores, a multi-head log-structured allocator whose design makes explicit use of a machine's configuration to support linear scalability of common readand write-heavy access patterns. Our implementation of this design, called Nibble, is written in 4k lines of Rust. (2) Going beyond key-value stores, the second part of this dissertation introduces new general support within the operating system enabling applications to more explicitly manage and share pointer-based in-memory data: we introduce explicit control over address space allocation and layout by promoting address spaces as an explicit abstraction. Processes may associate with multiple address spaces, and threads may arbitrarily switch between them to access infinite data set sizes without encountering typical bottlenecks from legacy mmap interfaces. Our implementation of this design is in DragonFly BSD.

#### **CHAPTER I**

### **INTRODUCTION**

Within the last decade, application data sets have grown to enormous sizes [35, 52, 70, 173] frequently exceeding the capacities of main-memory machines [83]. Numerous software systems, such as key-value stores [123, 115, 72, 152, 27, 143], databases [92, 120], file systems [165, 63], and operating systems [163, 96, 14], have thus introduced clever designs that balance the performance of main memory with the capacity provided via cheaper persistent storage, such as disks and SSDs [137].

In response to the continued growth of application data sets, and the demand for faster access to such data [134, 62, 143, 100, 86] computer manufacturers have introduced very large multi-socket machines with (now) terabytes of byte-addressable main memory. Keeping entire working sets in main memory provides fast access to data sets — at DRAM latencies, 100-400 nanoseconds for one cache line — even under random-access patterns; a design property that proves extremely advantageous for web applications [86], databases [101, 70], etc. In many domains, low latency is vital for revenue and customer retention [154, 86]. As analytics applications increasingly demand real-time or near real-time processing of large data sets, a new class of in-memory big data systems (e.g., key-value/object stores, in-memory databases and in-memory analytics engines) has arisen to store and process data in memory. The demand for in-memory processing of large data sets and advances in hardware such as newer more dense memory technologies [137] accelerate the emergence of large-memory systems with a large number of cores [8, 82, 7, 6, 11, 20]. Compared to distributed systems to scale computation, large single machines prove to be more effective, for example in graph computations [173, 121], where individual large data sets are accessed in parallel (or if it cannot be independently partitioned). Designs of software systems executing on such machines have increasingly incorporated concurrent algorithms and data structures [44, 116, 125, 68, 37] to achieve the multi-core performance available on such hardware.

Key-value stores are important in building large-scale applications, mapping arbitrary keys to locations in memory that hold objects (structureless, opaque memory blobs). Ignoring a machine's

underlying topology, a key-value store may initialize all memory on a single socket; when supporting many threads, performance often plateaus due to insufficient inter-socket link bandwidth [95, 108]. And, common synchronization primitives, such as those which rely on atomic compare-and-swap to guard shared resources, quickly become bottlenecks [126, 127, 129, 59], using only a fraction of the total compute resources within such machines. Alternative methods for handling such scale, such as concurrent methods [162, 91, 84, 60], are necessary.

A further consideration within such data management layers concerns the effectiveness of memory allocation to ensure the use of available capacity is efficient — as low a ratio of used memory to allocated memory as possible. Just as in file systems or other persistent storage where data sets live for extended periods [106], fragmentation becomes a concern for main-memory data storage, as well [170, 151]. Often, key-value stores incorporate common general-purpose heap allocators or techniques derived from their designs [42, 152, 72, 123], given their excellent SMP scalability. As applications' use of the heap can often be described as regular – reusing a small number of specific object sizes, derived from structs or other memory objects [42] – the management, then, of *arbitrary data* leads to situations of high fragmentation. Such fragmentation, or "bloat", can result in as high as twice or three times as much memory used for a given data set [151], making very little of the immense capacity of large-memory machines available. Situations like these result in degenerate behaviors, where software swaps to storage mediums, or arbitrary failures.

As very large memory SMP machines are characterized by designs that resemble distributed systems where resources are disaggregated and have non-uniform characteristics [141, 108], the design of the machine more directly impacts higher-level software performance; having the operating system present resources entirely transparent presents limits in how far software systems can scale or program their data. Specifically, building large applications or runtimes that take advantage of long-lived, complex data sets is met by a lack of control from the operating system to manage these data sets, such as interfaces for virtual memory management [65, 138], or physical memory management [105] (memory interfaces in the operating system are the most heavily used, according to a recent survey of POSIX [30]). Data often takes on two forms: the in-memory representation, and the persistent (or on-disk) format, with additional code developed to convert between the two (e.g., Protobuf [16]). Given the size and complexity, it becomes increasingly beneficial to maintain

the in-memory representation, as serialization to and from alternative mediums can increasingly become costly [71] – a burden on recovery, maintenance, and persistence. This burden is directly imposed on software by the virtual memory interface presented by operating systems. The fact it remains a transparent "resource", and hides knowledge of where and how physical memory is provided to software presents a "death by a thousand cuts" that makes designs and performance of software managing large data sets impractical. For example, page faulting, page migration, and the translation granularities make it challenging for user-level software to determine how much or where their physical memory is located — information important for ensuring performance and scalability on large machines.

With a memory-centric focus on the design of applications [69, 46], where data is maintained as their in-memory representation, the sharing of large data sets becomes a burden without an effective means of controlling its access. For example, rebuilding an index from its persistent format takes time, but more demanding is the lack of control over how user-level software can set up access to such data: as virtual-to- physical memory translation is required, it remains a challenge with current low-level APIs to ensure that a specific range of addresses can be made available to map in a data set [46, 65]; if address ranges are unavailable, costly swizzling techniques, for example, must be used before such information can be used [168]. Libraries, heap regions, devices memory, etc. all require modifying the address space, where their base offsets are determined by disjoint subsystems within the kernel — address space layout randomization ("ASLR"), device drivers, and the state of the memory map at any point in time — making it difficult or impossible for user- level software to acquire address ranges necessary for accessing large data sets. This problem becomes exacerbated with increasing physical memory sizes, exceeding the translation mechanisms' capacity within commodity processors [77]. x86 processors use radix trees to implement virtual memory, and with four layers, can translate a maximum of 248 bytes (256 terabytes) of memory; individual machines today already have 2<sup>46</sup> bytes of physical DRAM (e.g., SGI UltraViolet machines) – the maximum addressable by current commodity processors. Data center machines based on disaggregated memory designs, such as HPE's "The Machine", will easily exceed this threshold.

Given the scope of this area of research, this dissertation specifically aims to address the following questions concerning the design and implementation of scalability bottlenecks within user-level and

system software on very large-memory SMP machines:

- What key-value store designs exist today, and how is their performance impacted by such machines? How well do they handle operation sequences that may lead to fragmented memory, thus consuming most of a machine's capacity?

- Log-structured systems, as used in key-value stores, allow for 'cleaning' memory to reclaim unused memory holes; are such designs amenable to scaling, and how do they compare to existing alternatives? What are the main overheads and challenges, and how can we overcome them?

- A disadvantage of log-structured systems is the need to "compact" memory. What can we do to reduce this overhead?

- What motivates the need for improving memory interfaces within operating systems today, and are challenges motivating this need specific only to such large machines?

- What does the future of these machines look like, and how relevant are the insights in this dissertation to them?

In exploring these questions, this dissertation discusses the design and evaluation of two systems: (1) a user-level, scalable, log-based key-value store, and (2) an alternative approach to memory management within an operating system where virtual memory is managed with explicit address space abstractions, as would be files.

## 1.1 Thesis Statement

Very-large-memory machines pose many challenges for runtime systems and system software to make the underlying platform scale and capacity available to applications: concurrent access and terabytesize data sets become fragmented over time, and mechanisms for organizing memory access, such as memory allocation techniques underlying key-value stores or abstractions presented by operating systems, result in designs that do not scale to many cores, support high levels of concurrency, or make addressing enormous sizes of physical memory both cumbersome and inefficient. The thesis of this dissertation is: To reduce memory bloat and attain high scalability on massive-memory SMP machines, user-level data management tools, such as key-value stores, must incorporate use of multi-head log allocation, concurrent indexes, and scalable synchronization for memory reclamation, and be built on top of operating systems that expose explicit abstractions for managing and switching between large virtual address spaces.

### 1.2 Contributions

The specific contributions made in this dissertation are as follows:

- 1. Characterization of challenges on large-memory extreme-SMP machines for key-value stores: limitations, programmability, scalability, and efficiency of current methods; and challenges of operating systems for supporting applications in general which work with large, rich in-memory data. Chapters 2, 3, 7.

- 2. Design of a scalable log-structured key-value store using concurrent data structures, state partitioning, use of scalable hardware primitives, called *Nibble*. Chapter 4.

- A view into design parameters that influence efficiency of compaction in Nibble, and a design adaptation of Nibble meant to reduce compaction work itself via a relaxation of strict logbased behavior, *overwriting* objects on updates, instead of appending them, called *Nibble-2*. Chapter 6.

- 4. The design of a new operating system memory subsystem exposing virtual address spaces as a model for supporting memory-centric computing, where processes may allocate, compose, and arbitrarily switch between address spaces, called *SpaceJMP*. Chapter 8.

- Implementation and empirical evaluation of Nibble and Nibble-2 in Rust on an HPE Superdome X machine with 240 CPU cores on terabyte-sized data sets, compared with alternative state-ofthe-art scalable key-value stores. Chapters 4, 5, 6.

- 6. Implementation and empirical evaluation of SpaceJMP in DragonFly BSD on a half-terabyte parallel machine, and demonstration of its use for scalable micro-benchmarks. Chapters 9, 10.

- 7. Public release of source code for Nibble.

#### **CHAPTER II**

## **BACKGROUND AND MOTIVATION**

This chapter provides background and context of the topic of this dissertation, as well as to give definition to the types of machines evaluated.

### 2.1 The Advent of Large Memory Multi-core Machines

Beyond the evolution into multi-core processors from the prior decade, a large growth in data collected by corporations of their customers, financial transactions, and social behavior online together with very tight budgets on processing or analyzing such data has led to machines with enormous memory sizes and parallelism. Different from other high-performance machinery – specialized for high-performance computing on custom chips and networks, such as China's Sunway [22], IBM's Sequoia [19], and Fujitsu's Kcomputer [17] – many more machines today are built from (mostly or entirely) commodity equipment and run standard operating systems, such as HPE's Superdome X [82, 8], or SGI's UltraViolet products [20] Their cost and familiarity enables a large community to take advantage of their capabilities for database processing, analytics of customer purchases and preferences, as well as leveraging the availability of large pools of memory for quickly serving information backing major websites. Often, the argument made in favor of such machines is the extremely close proximity of enormous single data sets to a large pool of computing elements, simplifying programming designs by avoiding networking layers and communication protocols.

It becomes important to understand how to achieve high performance on larger machines, and avoid pitfalls when programming for smaller-scale machines. Typical data centers deploy the most cost-effective machine configurations, with dual-socket multi-core processors, at the scale of thousands of such machines connected over TCP/IP. While software executing on these machines increasingly benefit from parallelism — around 12-24 processing cores — solutions for leveraging many cores by individual applications or runtimes face bottlenecks on terabyte-class machines where many tens to hudreds of processor cores are available [43, 133]. This quantity of hardware parallelism arises not just from an increasing core count on processors – a trend which is not halting, as lower

| Table 1: Example single-system large-memory machines. Total Memory bandwidth is a sum of           |

|----------------------------------------------------------------------------------------------------|

| bandwidth to local memory across sockets. *64 TiB is a limit of the CPU, not the platform, able to |

| address only $2^{46}$ bytes of physical memory.                                                    |

| Machine           | Sockets | Cores | Memory Size | Total Memory BW |

|-------------------|---------|-------|-------------|-----------------|

| SGI UV 3000       | 256     | 4096  | 64 TiB*     | 1 TiBps         |

| SGI UV 300        | 64      | 1536  | 64 TiB*     | -               |

| HPE Superdome X   | 16      | 384   | 48 TiB      | 1 TiBps         |

| Dell R930         | 4       | 96    | 12 TiB      | 240 GiBps       |

| Cavium Thunder X2 | 2       | 96    | 1 TiB       | -               |

Table 2: Example large-memory networked machines. "The Machine" is a datacenter system, and Summit an HPC machine.

|                   | Per Node |          |         | System-wide |            |  |

|-------------------|----------|----------|---------|-------------|------------|--|

| Machine           | CPU      | DRAM     | NVM     | Memory Size | Network    |  |

| HPE "The Machine" | ARM      | 512 GiB+ | 2-4 TiB | 1 PiB+      | Gen-Z      |  |

| <b>IBM Summit</b> | POWER9   | 512 GiB+ | 800 GiB | 2.6 PiB     | InfiniBand |  |

power processors such as ARM-based CPUs are also entering the mainstream server market – but also due to the greater quantity of processing sockets deployed in these machine configurations. Current SGI UV machines, for example, are able to scale up to 256 Intel Xeon processor sockets [20].

We noticed that certain design techniques leveraging simple synchronization primitives, while sufficiently scalable on such smaller machines, quickly became sources of contention once thread counts increased further. In the work within this dissertation, we observed that spin locks, or use of atomic instructions to modify counters, for example, are simply insufficient to guard shared resources when scheduling highly parallel applications. These primitives are often found lurking within the depths of various software libraries that provide concurrent services; one must use more scalable primitives that one might otherwise have considered overkill, or which have higher per-operation latencies (e.g., MCS locks [129]). Two specific examples we stumbled upon in the implementation of our key- value store – Nibble – were in Rust [135] libraries specifically developed for multi-threaded software:

• The crate Crossbeam [136], containing data structures for concurrent programming. The use of epochs is implemented to allow for asynchronous deallocation of memory (i.e., mark a time stamp on the object, and later check for a quiescent period after which to release it). Data structures such as a multi- consumer multi-producer lock-free Michael-Scott queue [132]

use this mechanism. The problem therein is that the epoch mechanism within the library is shared among all instances of queues used in software, even among disjoint sets of threads working on independent queues. The epoch itself is an atomic counter: each time the memory backing an object removed from a queue is released, the counter is incremented. Obviously with increasing numbers of threads, this method quickly becomes a bottleneck, unbeknown to the programmer, when seemingly no threads are actually sharing any data.

• Use of reader-writer locks (either part of std::sync, or in the crate parking\_lot, the latter being used in Nibble). While more trivial of an example (and perhaps not specifically a result of using Rust), reader-writer locks are used in scenarios where the programmer assumes some resource is more frequently accessed by many readers and at most one or few mutators. When a mutator wishes to lock the resource, it must (a) prevent new readers from entering and (b) not itself use the resource until all existing readers or a mutator have relinquished it. To accomplish the latter, an atomic reference counter is used to keep track of in-progress readers. Unfortunately, it is this mechanism in reader-writer locks which limits scalability: with increasing numbers of readers — even with no mutator attempts — read access is bottlenecked, as all threads entering must lock the shared cache line and either increment or decrement the counter, a cost that is greater across large off-chip network distances.

Our experiences from situations like the above have guided us to look for solutions where we minimize the need to actually synchronize operations unless it becomes absolutely necessary. Nibble uses a scalable implementation of an epoch we designed specifically for high-concurrency execution, and optimistic concurrency control within its index (both discussed in more detail in later chapters).

Just as in distributed systems where individual machines can become overloaded due to high request rates across its network, so can individual sockets within these machines. Off-chip network bandwidth is not increasing with time as the amount of hardware parallelism available (Table 1), leading to a growing gap in performance per thread to arbitrary memory. Understanding this is important, as simple workloads that have skewed characteristics, such as in key-value stores, can quickly create bottlenecks. Thus, where data is allocated to — which specific socket memory — can have a large impact on performance. Unlike prior work which uncovered discrepancies in bandwidths

Figure 1: HPE Superdome X system design – a custom controller connects to each processor via QPI channels, establishing a large load/store domain to all of memory. Reproduced from [9].

and even directionality of such bandwidth between sockets on 8-socket AMD machines [108], machines like shown in Figure 1 aim to provide as uniform of memory bandwidth to remote memories across all sockets. While this helps avoid needing solutions in prior work to match application bandwidths to placement across each socket, large machines like these have much more hardware parallelism. What does this imply? Highly multi-threaded software can easily become bottlenecked by saturating a socket's off-chip bandwidth.

We illustrate this problem with a concurrent hash table [111], varying how many threads perform lookups on the data, shown in Figure 2. Allocating physical memory pages backing the hash table to (a) one socket (blue circles), (b) evenly across all sockets with lookups by threads to key only found in local memory (light-blue star), and (c) the same but lookups performed randomly across the entire memory (green square). If we look closely at the behavior under 50 threads, we see all three methods scale well; with all data on a single socket, performance is highest. More threads shows no increase in performance when memory is placed on one socket – we saturated its cross-chip network. Such large machines are expected to be nearly or fully utilized, thus the discrepancies seen at 150+ cores becomes most important.

Thus, a challenge in managing memory requires understanding data placement, as well as data access, and ensuring the aggregate bandwidth available across all memories is balanced to ensure

Figure 2: Figure showing the effect of data placement within a 16-socket machine on the performance of a concurrent implementation of a hash table (Cuckoo).

achieving high overall bandwidth to large in-memory data sets.

Looking at absolute performance in terms of the latency of individual operations on large machines, another characteristic which must be considered is the much larger overall cache line access latencies. On smaller 2-socket systems and a randomized access pattern, 50% of operations will access remote memory, but on larger machines, depending on how numerous their socket configurations are, will see nearly all accesses be to remote memories. For the system evaluated in this dissertation, there are 16 sockets, leading to  $\frac{15}{16}$  or 94% of all operations which touch remote memory. A tool developed as part of this dissertation measures the individual unloaded cache line latency. On a 2-socket machine, remote memory accesses average around 180 nanosecond, and on an HPE Superdome X they average 320 nanoseconds – a 70% increase in latency.

Placement of memory thus must be carefully balanced with scaling operations.

Aside from available hardware parallelism, another aspect concerns the scope of memory sizes, and the capabilities of the processors and operating systems to effectively make this memory accessible to software. We will see an enormous growth in the capacities of memory systems in the future, not only in part due to alternative memory technologies such as NVM, Memristor, 3D XPoint, STT-RAM, etc. but also due to new processor connectivity networks, such as Gen-Z [5]. The latter, Gen-Z, is a memory fabric network technology touted to enable connecting many machines together with custom network processors that connect general CPUs to a unified remote memory.

Effectively, one can create enormous load-store domains, much larger than what current commodity processors are capable of addressing. Today's Intel and AMD processors, although "64-bit enabled", allow for 52 bits of memory addressing in their specifications. Actual implementations (processors purchasable today) are often limited to 46 bits of physical addressing and 48 bits of virtual memory. Such limits are imposed by the implementation of the virtual memory within the hardware, in the form of virtual-to-physical page translations: a fixed 512-child radix tree four levels deep provides translation to, 9 bits (= 512 entries)  $\cdot$  4 levels + 12 (bits in lowest entry, a 4 KiB page) = 48 bits of translation, or 256 TiB of memory. Without the ability to address large regions of memory, or where fragmentation of the address space itself prevents mapping in large regions, applications and system software must resort to frequent modifications of their page tables, which as we will see in later chapters, is an ill-performing workaround.

As of this writing, Intel has updated their processor manuals to include a 5th level in their virtual memory page tables. While there is precedence to do so (earlier 32-bit systems had introduced PAE to increase the address range by a few bits, to use more than 4 GiB of system memory), each additional level in the page table impacts overall performance, as an additional memory fetch is required in translation, as well as increases pressure within translation buffers to cache translations for application, buffers that are already limited in capacity.

**Summary.** Terabyte- and future petabyte-scale machines present different performance and programming characteristics to applications and system software that are not as visible in typical data center servers: memory sizes are larger, and so are the processor configurations. Total system memory bandwidth is available across a greater number of discrete processor sockets where bottlenecks may easily appear without careful placement of data, and memory access latencies are much higher to accommodate ever-increasing memory capacities. The latter encourages system software to take advantage of more scalable methods for designing concurrent mechanisms.