#### MACHINE LEARNING IN PHYSICAL DESIGN FOR 2D AND 3D INTEGRATED CIRCUITS

A Dissertation Presented to The Academic Faculty

By

Yi-Chen Lu

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

Georgia Institute of Technology

May 2023

© Yi-Chen Lu 2023

#### MACHINE LEARNING IN PHYSICAL DESIGN FOR 2D AND 3D INTEGRATED CIRCUITS

Thesis committee:

Dr. Sung Kyu Lim Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Saibal Mukhopadhyay Electrical and Computer Engineering Georgia Institute of Technology

Dr. Shimeng Yu Electrical and Computer Engineering Georgia Institute of Technology Dr. Yingyan (Celine) Lin College of Computing *Georgia Institute of Technology*

Dr. Siddhartha Nath Research and Development Intel Corporation

Date approved: February 24, 2023

It is not intellect that tells so much as character; not brains so much as heart; not genius so much as self-control, patience, and discipline, regulated by judgement.

Ernest Hemingway

To my parents Leng-Chien Tsao and Ching-Chung Lu, my brother Tang-Chen Lu, my wife Jae Youn Kim, and my daughter Hannah Lu.

#### ACKNOWLEDGMENTS

First and foremost, I would like to show my sincere appreciation to my advisor, Dr. Sung Kyu Lim, for his invaluable guidance, support, and encouragement throughout my Ph.D. journey. His unwavering work attitude has inspired me to devote my heart into research, and his liberal approach in pursing knowledge has given wings to my creativity, turning imagination into practice. I would also like to express my heartfelt gratitude to my proposal and dissertation committee members – Dr. Madhavan Swaminathan and Dr. Saibal Mukhopadhyay for their great advice during the proposal exam, and Dr. Shimeng Yu, Dr. Yingyan (Celine) Lin, and Dr. Siddhartha Nath for spending their valuable time and effort in serving in my dissertation committee.

I am deeply grateful to the guidance from numerous industrial members during my internships in Ph.D. study: Kambiz Samadi, Sorin Dobre in Qualcomm; Siddhartha Nath, Vishal Khandelwal, Wei-Ting (Jonas) Chan, Deyuan Guo, Sudipto Kundo in Synopsys; Tian Yang, Haoxing Ren in Nvidia. They provide me the technical resources and insightful discussions that are significantly helpful to my research. Also, my genuine thanks to my past and current colleagues at GTCAD: Dr. Bon Woong Ku, Dr. Kyungwook Chang, Dr. Sai Pentapati, Dr. Anthony Agnesina, Dr. Jinwoo Kim, Da Eun Shim, Jeehyun Lee, Lingjun Zhu, Gauthaman Murali, Chengjia Shao, Pruek Vanna-Iampikul, Hao-Hsiang (Thomas) Hsiao, Yen-Hsiang (Robert) Huang, Dongwon Jang, Ray Anderson, Sandra Shaji, Nesara Bethur, Aditya Iyer, for their great help and exciting collaboration.

I want to show my deepest gratitude to my parents Leng-Chien Tsao and Ching-Chung Lu, and my brother Tang-Chen Lu. Their unconditional love and support is the unshakable foundation of my ability to pursue my dream. Without them, I wouldn't have gone this far.

Lastly, I am particularly indebted to my wife Jae Youn Kim, and my daughter Hannah Lu, for their tremendous love and forever encouragement that give me the greatest strength to conquer any challenge that may arise in the road ahead.

## TABLE OF CONTENTS

| Acknow    | ledgme          | ents                                                                                     |

|-----------|-----------------|------------------------------------------------------------------------------------------|

| List of 7 | <b>Fables</b> . | xv                                                                                       |

| List of I | ligures         | xix                                                                                      |

| Summa     | ry              | <b></b> xxvii                                                                            |

| Chapter   | r 1: Int        | roduction                                                                                |

| 1.1       | Tacklin         | ng Physical Design (PD) with Machine Learning (ML)                                       |

|           | 1.1.1           | Graph Neural Networks for Netlist Encoding 2                                             |

|           | 1.1.2           | ML for Quality-of-Results (QoR) Prediction                                               |

|           | 1.1.3           | From QoR Prediction to Optimization                                                      |

| 1.2       | Contri          | bution and Organization                                                                  |

| Chapter   |                 | Iachine Learning Powered Tier Partitioning Framework for Mono-         ic 3D ICs       9 |

| 2.1       | Backg           | round and Motivation                                                                     |

|           | 2.1.1           | Monolithic 3D (M3D) ICs                                                                  |

|           | 2.1.2           | Limitations of Current Tier Partitioning Methods in M3D Flows 9                          |

|           | 2.1.3           | Different Styles of M3D Flows: Partitioning-First and Partitioning-<br>Last              |

|        | 2.1.4  | Heterogeneous 3D ICs Design Flow                                                  | 14 |

|--------|--------|-----------------------------------------------------------------------------------|----|

| 2.2    | TP-GN  | NN Algorithms                                                                     | 14 |

|        | 2.2.1  | Overview                                                                          | 14 |

|        | 2.2.2  | Hierarchy-Aware Edge Contraction                                                  | 16 |

|        | 2.2.3  | GNN as Feature Aggregator                                                         | 17 |

|        | 2.2.4  | Unsupervised GNN Learning                                                         | 19 |

|        | 2.2.5  | GNN Training Methodology                                                          | 20 |

|        | 2.2.6  | Weighted K-means Clustering                                                       | 21 |

|        | 2.2.7  | Post-partitioning Optimization                                                    | 22 |

|        | 2.2.8  | Implementation Details                                                            | 23 |

| 2.3    | Experi | mental Results                                                                    | 23 |

|        | 2.3.1  | GNN-related Results                                                               | 24 |

|        | 2.3.2  | Maximum Performance Comparison                                                    | 25 |

|        | 2.3.3  | Iso-Performance Comparison                                                        | 27 |

|        | 2.3.4  | Sweeping Experiments on Contracting Edges                                         | 29 |

|        | 2.3.5  | Results on Heterogeneous 3D ICs                                                   | 29 |

| 2.4    | Discus | ssion                                                                             | 32 |

|        | 2.4.1  | Why Does GNN Work Better?                                                         | 32 |

|        | 2.4.2  | MIV Impact                                                                        | 33 |

|        | 2.4.3  | Timing Impact on Crossing Tiers                                                   | 33 |

| 2.5    | Conclu | usion                                                                             | 34 |

| Chapte |        | SI Placement Optimization via PPA-Directed Self-Supervised Deep<br>aph Clustering | 35 |

|        |        |                                                                                   |    |

| 3.1    | Backg  | round and Motivation                                                                                | 35 |

|--------|--------|-----------------------------------------------------------------------------------------------------|----|

|        | 3.1.1  | Related Works: ML in VLSI Placement                                                                 | 35 |

|        | 3.1.2  | Our Goal: PPA-Directed Placement Optimization                                                       | 37 |

| 3.2    | Frame  | work Overview                                                                                       | 39 |

| 3.3    | Algori | thms                                                                                                | 41 |

|        | 3.3.1  | Netlist Transformation                                                                              | 41 |

|        | 3.3.2  | Node-Level Feature Collection                                                                       | 41 |

|        | 3.3.3  | Node Representation Learning                                                                        | 44 |

|        | 3.3.4  | PPA-Directed Deep Graph Clustering                                                                  | 45 |

|        | 3.3.5  | End-to-End Unsupervised Training                                                                    | 50 |

|        | 3.3.6  | Integration with Commercial EDA Tools                                                               | 52 |

|        | 3.3.7  | Integration with DREAMPlace [24]                                                                    | 52 |

|        | 3.3.8  | Integration with Prediction Models                                                                  | 53 |

| 3.4    | Experi | mental Results                                                                                      | 54 |

|        | 3.4.1  | Optimization Results on Industrial Flows                                                            | 56 |

|        | 3.4.2  | Optimization Results on DREAMPlace                                                                  | 58 |

|        | 3.4.3  | Comparisons with Single-Way Clustering [7]                                                          | 59 |

|        | 3.4.4  | Optimization Results with Timing Prediction Models                                                  | 60 |

|        | 3.4.5  | Why Does PPA-GNN Work?                                                                              | 61 |

| 3.5    | Conclu | usion                                                                                               | 62 |

| Charte | - 1. D | idaing Open Source and Commercial Discours wing Commercian                                          |    |

| Chapte |        | idging Open-Source and Commercial Placers using Generative versarial Networks and Transfer Learning | 64 |

| 4.1    | Backg  | round and Motivation                                                                                | 64 |

| 4.2    | Related Work |                                                                                   |    |

|--------|--------------|-----------------------------------------------------------------------------------|----|

| 4.3    | Overvi       | ew and Motivation                                                                 | 68 |

|        | 4.3.1        | Database Construction                                                             | 70 |

| 4.4    | DREA         | M-GAN Algorithms                                                                  | 71 |

|        | 4.4.1        | GNN-based Discriminator                                                           | 71 |

|        | 4.4.2        | Soft-Bin: Differentiable 2D Bin-Density Map Transformation                        | 73 |

|        | 4.4.3        | CNN-Based Discriminator                                                           | 75 |

|        | 4.4.4        | Putting All Together: End-to-End DREAM-GAN Training                               | 76 |

| 4.5    | Experi       | mental Results                                                                    | 77 |

|        | 4.5.1        | Single-Design Optimization Results                                                | 80 |

|        | 4.5.2        | Transfer Learning on Unseen Designs                                               | 80 |

|        | 4.5.3        | Discussion of Optimization Results                                                | 81 |

| 4.6    | Conclu       | sion                                                                              | 82 |

| Chapte |              | N-CTS: A Generative Adversarial Framework for Clock Tree diction and Optimization | 83 |

| 5.1    | Backgr       | ound and Motivation                                                               | 83 |

| 5.2    | Design       | ing Experiments                                                                   | 84 |

|        | 5.2.1        | Database Analysis                                                                 | 84 |

|        | 5.2.2        | Database Construction                                                             | 85 |

| 5.3    | Overvi       | ew of GAN-CTS                                                                     | 88 |

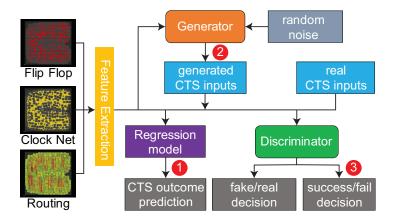

| 5.4    | GAN-0        | CTS Algorithms                                                                    | 90 |

|        | 5.4.1        | Placement Image Feature Extraction                                                | 91 |

|        | 5.4.2        | CTS Outcomes Prediction                                                           | 93 |

|        | 5.4.3  | Interpreting Prediction Results                                                     |

|--------|--------|-------------------------------------------------------------------------------------|

|        | 5.4.4  | CTS Optimization                                                                    |

|        | 5.4.5  | Success vs. Failure Classification                                                  |

|        | 5.4.6  | Training Methodology                                                                |

| 5.5    | Experi | imental Results                                                                     |

|        | 5.5.1  | CTS Prediction and Interpretation Results                                           |

|        | 5.5.2  | CTS Optimization Results                                                            |

|        | 5.5.3  | Success vs. Failure Classification Results                                          |

| 5.6    | Discus | ssion                                                                               |

|        | 5.6.1  | Non-triviality of the CTS Modeling Problem                                          |

|        | 5.6.2  | Train/Test Splitting of Benchmarks                                                  |

|        | 5.6.3  | Discussion of Prediction Results                                                    |

|        | 5.6.4  | Discussion of Optimization Results                                                  |

| 5.7    | Conclu | usion                                                                               |

| Chapte |        | -Sizer: VLSI Gate Sizing for Timing Optimization using Deep<br>inforcement Learning |

| 6.1    | Backg  | round and Motivation                                                                |

| 6.2    | Reinfo | prcement Learning Formulation                                                       |

|        | 6.2.1  | Gate Sizing as a Control Problem                                                    |

|        | 6.2.2  | Our Key Concept: Local-Graph Approximation                                          |

|        | 6.2.3  | Graph Representation Learning                                                       |

| 6.3    | RL-Si  | zer Algorithms                                                                      |

|        | 6.3.1  | Overview                                                                            |

|        | 6.3.2  | Instance Selection                                                                                          |

|--------|--------|-------------------------------------------------------------------------------------------------------------|

|        | 6.3.3  | Encoding RL State using GNNs                                                                                |

|        | 6.3.4  | Policy and Value Networks                                                                                   |

|        | 6.3.5  | Implementation Details: Challenges of ML in EDA                                                             |

| 6.4    | Experi | imental Results                                                                                             |

|        | 6.4.1  | Optimization Results                                                                                        |

|        | 6.4.2  | Discussion of Optimization Results                                                                          |

| 6.5    | Conclu | usion                                                                                                       |

| Chapte |        | -CCD: Concurrent Clock and Data Optimization using Attention-<br>sed Self-Supervised Reinforcement Learning |

| 7.1    | Backg  | round and Motivation                                                                                        |

| 7.2    | Relate | d Works                                                                                                     |

|        | 7.2.1  | Predictive Useful Skew                                                                                      |

|        | 7.2.2  | Learning-Driven Timing Prediction                                                                           |

|        | 7.2.3  | RL in EDA: Going Beyond Commercial Tool Quality                                                             |

| 7.3    | RL-CO  | CD Algorithms                                                                                               |

|        | 7.3.1  | Overview and Reinforcement Learning Formulation                                                             |

|        | 7.3.2  | Detailed Architecture                                                                                       |

|        | 7.3.3  | Fan-in Cone Overlap Masking and the Rationale Behind 143                                                    |

|        | 7.3.4  | Training Methodology                                                                                        |

| 7.4    | Experi | imental Results                                                                                             |

|        | 7.4.1  | Single-Design Optimization Results                                                                          |

|        | 7.4.2  | Transfer Learning on Unseen Designs                                                                         |

|        | 7.4.3  | Discussion: Why Does RL-CCD Work?                                                         |

|--------|--------|-------------------------------------------------------------------------------------------|

| 7.5    | Conclu | usion                                                                                     |

| Chapte |        | CO-GNN: Signoff Power Prediction using Graph Neural Networks<br>Th Subgraph Approximation |

| 8.1    | Backg  | round and Motivation                                                                      |

| 8.2    | Relate | d Works                                                                                   |

| 8.3    | Design | ning of Experiments                                                                       |

| 8.4    | Overv  | iew of ECO-GNN Framework                                                                  |

|        | 8.4.1  | Our Objectives: Regression and Classification                                             |

| 8.5    | Design | n of Experiments                                                                          |

|        | 8.5.1  | Problem Formulation                                                                       |

|        | 8.5.2  | Initial Node Features                                                                     |

| 8.6    | ECO-0  | GNN Algorithm                                                                             |

|        | 8.6.1  | Overview of the Algorithm                                                                 |

|        | 8.6.2  | GNN: Feature Aggregator                                                                   |

|        | 8.6.3  | Loss Function                                                                             |

|        | 8.6.4  | Training Methodology                                                                      |

|        | 8.6.5  | Complexity Analysis                                                                       |

|        | 8.6.6  | Handling Unseen Designs                                                                   |

|        | 8.6.7  | A Regression Perspective: Subgraph Approximation for Fast Power<br>Prediction             |

|        | 8.6.8  | Assisting $V_{th}$ -Assignment with Subgraph Approximation 170                            |

| 8.7    | Explai | ning Prediction Results                                                                   |

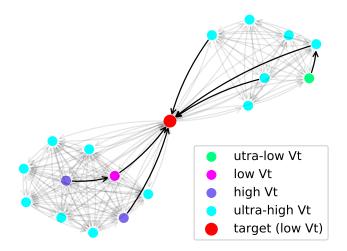

|         | 8.7.1  | Inner Workings of GNN Predictions                                                       |

|---------|--------|-----------------------------------------------------------------------------------------|

| 8.8     | Experi | mental Results                                                                          |

|         | 8.8.1  | Benchmarks Details and Timing Corners                                                   |

|         | 8.8.2  | Subgraph Approximation Results                                                          |

|         | 8.8.3  | Prediction results of $V_{th}$ -Assignment with Subgraph Approximation 175              |

|         | 8.8.4  | Discussion of Subgraph Approximation                                                    |

|         | 8.8.5  | Optimization Results on Unseen Designs                                                  |

|         | 8.8.6  | Discussion of Optimization Results                                                      |

|         | 8.8.7  | GNN Explanation                                                                         |

|         | 8.8.8  | Why Does ECO-GNN Work?                                                                  |

|         | 8.8.9  | Related Works on Improving Chip Design Turnaround Time 183                              |

| 8.9     | Conclu | usion                                                                                   |

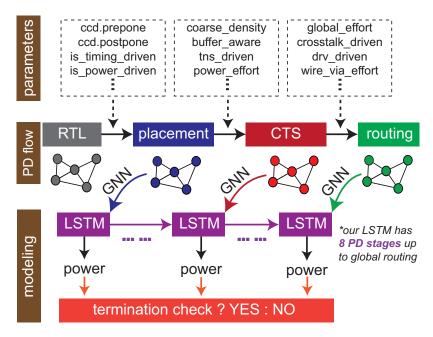

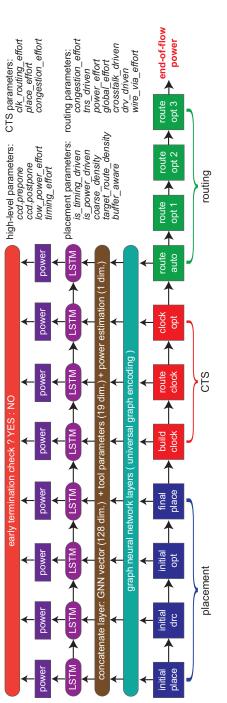

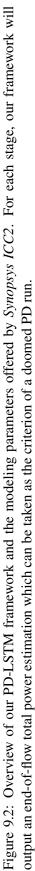

| Chapter |        | omed Run Prediction in Physical Design by Exploiting Sequen-<br>Flow and Graph Learning |

| 9.1     | Backg  | round and Motivation                                                                    |

| 9.2     | Overv  | iew: PD Flow Modeling                                                                   |

| 9.3     | Design | n of Experiments                                                                        |

|         | 9.3.1  | Database Construction                                                                   |

|         | 9.3.2  | Database Analysis                                                                       |

| 9.4     | PD-LS  | TM Algorithms                                                                           |

|         | 9.4.1  | Initial Node Features for Graph Learning                                                |

|         | 9.4.2  | Graph Embedding                                                                         |

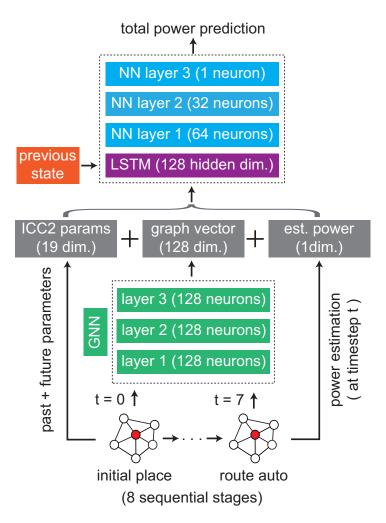

|         | 9.4.3  | PD Sequential Modeling using LSTM                                                       |

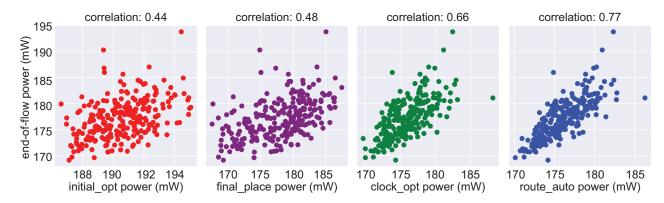

| 9.5      | Experimental Results                                                                                           |

|----------|----------------------------------------------------------------------------------------------------------------|

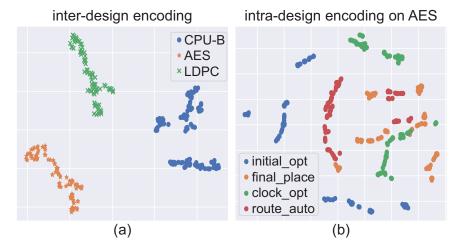

|          | 9.5.1 GNN Netlist Encoding Results                                                                             |

|          | 9.5.2 Sequential Learning Results                                                                              |

| 9.6      | Conclusion                                                                                                     |

| Chapter  | • <b>10:Conclusion</b>                                                                                         |

| 10.1     | A Machine Learning Powered Tier Partitioning Framework for Monolithic<br>3D ICs                                |

| 10.2     | VLSI Placement Optimization via PPA-Directed Self-Supervised Deep Graph<br>Clustering                          |

| 10.3     | Bridging Open-Source and Commercial Placers using Generative Adver-<br>sarial Networks and Transfer Learning   |

| 10.4     | GAN-CTS: A Generative Adversarial Framework for Clock Tree Predic-<br>tion and Optimization                    |

| 10.5     | RL-Sizer: VLSI Gate Sizing for Timing Optimization using Deep Rein-<br>forcement Learning                      |

| 10.6     | RL-CCD: Concurrent Clock and Data Optimization using Attention-Based<br>Self-Supervised Reinforcement Learning |

| 10.7     | ECO-GNN: Signoff Power Prediction using Graph Neural Networks with<br>Subgraph Approximation                   |

| 10.8     | Doomed Run Prediction in Physical Design by Exploiting Sequential Flow<br>and Graph Learning                   |

| 10.9     | Concluding Remarks                                                                                             |

| Referen  | <b>ces</b>                                                                                                     |

| Publicat | tions                                                                                                          |

| Vita     |                                                                                                                |

## LIST OF TABLES

| 2.1 | Initial node features for partitioning last design flows in edge-contracted graph $G'$ . Note that a node may represent multiple cells in the design                                                                                                                                      | 17 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Performance, area, and energy comparison of Shrunk-2D (S2D) [31] and TP-GNN flows on RISC-V-based designs using F2F stacking. $\Delta$ denotes the percentage difference between TP-GNN and S2D                                                                                           | 25 |

| 2.3 | Partitioning-first iso-performance comparison of Snap-3D [33] and TP-GNN flows. $\Delta_{Snap}$ denotes the percentage difference between TP-GNN and the Snap-3D flow. We report the time spend on tier partitioning in minutes.                                                          | 26 |

| 2.4 | Partitioning-last iso-performance comparison of True3D (T3D) [46], Shrunk-2D (S2D), Compact-2D (C2D), and TP-GNN flows. $\Delta_S$ and $\Delta_C$ respectively denotes the percentage difference between TP-GNN vs. S2D and C2D. We report the time spend on tier partitioning in minutes | 30 |

| 2.5 | Iso-Performance comparison on a heterogeneous 3D design of a commer-<br>cial CPU design implemented by Pin3D [36]. TP-GNN <sub>opt</sub> denotes the post-<br>partitioning optimization (Algorithm 4) is enabled                                                                          | 31 |

| 2.6 | Sweeping experiments on running hierarchy-aware edge contraction algo-<br>rithm (Algorithm 1) multiple times.                                                                                                                                                                             | 31 |

| 2.7 | Timing impact between 3D (cross-tier) and 2D (same-tier) nets on ECG benchmark. The unit for net length is $\mu m$ , and the unit for delay is $ps. \ldots$                                                                                                                               | 33 |

| 3.1 | Our initial node features for deep graph clustering. <i>M</i> denotes the number of memory macros                                                                                                                                                                                         | 43 |

| 3.2 | Our three academic benchmarks and their attributes under a foundry $28nm$ technology (attributes of six commercial benchmarks are described in section 7.4 due to proprietary.)                                                                                                           | 54 |

| 3.3 | Detailed PPA comparison between the default tool flow and the enhanced<br>flow. We normalize wirelength and power values due to proprietary issues.<br>All designs have ultra-high frequency targets. (since block6 does not have a<br>complete SAIF file for power simulation, we neglect the power comparison.)                                                                                                     | 55  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.4 | Optimization results analysis using proposed PPA losses. Colored entries denote better evaluations.                                                                                                                                                                                                                                                                                                                   | 56  |

| 3.5 | DREAMPlace [24] integration results on block1. "DREAM" denotes the DREAMPlace default placement.                                                                                                                                                                                                                                                                                                                      | 59  |

| 3.6 | Comparison between proposed PPA-directed clustering framework and a single-way clustering work [7]. The number of clusters $ C _{[23]}$ used for previous work is obtained from the sweeping experiments they proposed                                                                                                                                                                                                | 59  |

| 4.1 | Parameters we leverage for database generation                                                                                                                                                                                                                                                                                                                                                                        | 71  |

| 4.2 | Single-design optimization results. DREAM-GAN optimizes the same de-<br>sign as in the database.                                                                                                                                                                                                                                                                                                                      | 78  |

| 4.3 | Transfer Learning results on unseen designs. Middle column: single-design optimization as Table 4.2. Right-most column: optimization using database built by 5 other designs (the target design at each row remains totally unseen).                                                                                                                                                                                  | 79  |

| 5.1 | Our benchmarks and their attributes in TSMC 28nm                                                                                                                                                                                                                                                                                                                                                                      | 85  |

| 5.2 | Modeling parameters we use and their values                                                                                                                                                                                                                                                                                                                                                                           | 86  |

| 5.3 | Clock trees with different input slew constraints for Nova benchmark                                                                                                                                                                                                                                                                                                                                                  | 87  |

| 5.4 | CTS outcomes prediction results of three regression approaches. MAPE denotes mean absolute percentage error (%), MAXE denotes max. absolute percentage error (%), and CC denotes correlation coefficient. Note the the validations are performed on <i>unseen netlists</i>                                                                                                                                            | 104 |

| 5.5 | Achieved clock metrics comparison between commercial auto-setting (auto),<br>Bayesian optimization (bayes), and GAN-CTS. The method "GAN-CTS +<br>bayes" denotes using the generator suggested CTS parameter sets as the ini-<br>tial solutions of Bayesisan optimization along with the sequential domain<br>reduction technique [98]. Note that the four benchmarks are <i>unseen</i> during<br>the training phase. | 109 |

| 5.6 | GAN-CTS suggested and commercial auto-setting's CTS input parameters (refer to Table 5.5). Note that the commercial clock router has the same auto-setting values for different designs. The capacitance constraints in the auto-setting scenario are varied from net to net, which are subject to the max capacitance constraint of the driving pins                                                                                              |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.7 | Confusion matrix of success vs. failure classification in LEON benchmark.<br>Failure means worse than auto-setting                                                                                                                                                                                                                                                                                                                                 |

| 6.1 | Initial node features for GNN encoding                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.2 | Dimension of RL-Sizer layers                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.3 | Our commercial benchmarks and their attributes                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.4 | TNS optimization results comparison between RL-Sizer and Synopsys ICC2. The unit for timing is $ns$ , and the unit for power is $mW$ . WNS denotes worst negative slack; TNS denotes total negative slack, and #vio. EPs denotes the number of violating endpoints. The runtime for the commercial tool and RL-Sizer is measured on the same machine without GPU support. 129                                                                      |

| 7.1 | Initial node features for EP-GNN endpoint encoding. Note that the first attribute "RL masked" will be updated in each RL training iteration based on the selection of new endpoint and overlapping calculation                                                                                                                                                                                                                                     |

| 7.2 | Optimization results comparison between RL-CCD and the native imple-<br>mentation of an industry-leading commercial tool. RL-CCD is trained to<br>minimize design TNS by selectively prioritizing critical endpoints. The<br>unit for timing is $ns$ and for power is $mW$ . Runtime is normalized by de-<br>fault tool flow. Note that we use the same seed across all experiments to<br>completely remove non-deterministic run-to-run variation |

| 8.1 | 20 initial node features used in our GNN. We obtain them using an initial PPA analysis                                                                                                                                                                                                                                                                                                                                                             |

| 8.2 | Dimension of matrices used in our work (see Figure Figure 8.3). $v$ denotes the number of gates in the circuit                                                                                                                                                                                                                                                                                                                                     |

| 8.3 | Our benchmarks and their attributes in <i>TSMC 28nm</i> . MPL denotes the maximum path length of timing paths, SR denotes the spectral radius of the adjacency matrix, and RCC denotes the Rich Club Coefficient $(10^{-4})$ 173                                                                                                                                                                                                                   |

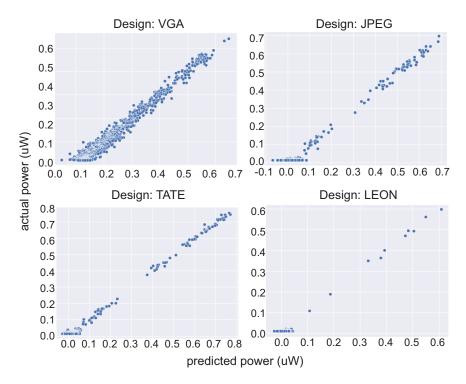

| 8.4 | Subgraph approximation prediction results on unseen benchmarks. CC denotes the Pearson correlation coefficient and is calculated against the <i>ICC2</i> optimization results                                                                                                                                                                                                                                                                                |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.5 | Confusion matrix comparison of $V_{th}$ -assignment with and without subgraph<br>approximation on the VGA benchmark. Each count represents an instance<br>whose slack value is greater than $200ps$ before the PrimeTime ECO opti-<br>mization                                                                                                                                                                                                               |

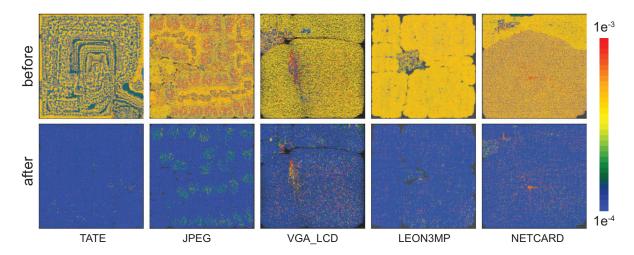

| 8.6 | $V_{th}$ re-assignment impact on power, timing, and runtime between ECO-<br>GNN and <i>Synopsys PrimeTime</i> . Selected designs are <i>unseen</i> during train-<br>ing. Note that both leakage and total power reduce from $V_{th}$ re-assignment,<br>because our initial designs before ECO optimization are using ultra-low<br>$V_{th}$ only as suggested in [43]. Timing also improves because of the gate<br>capacitance reduction from higher $V_{th}$ |

| 8.7 | Sweeping experiments on maximum number of aggregation level $(K)$ of GNN. The entry represents the F1 score of the classification results 179                                                                                                                                                                                                                                                                                                                |

| 9.1 | Initial node features defined for each design instance                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9.2 | Our benchmarks and their attributes in TSMC 28nm                                                                                                                                                                                                                                                                                                                                                                                                             |

| 9.3 | PD-LSTM end-of-flow prediction results on "unseen" designs. CC denotes<br>the Pearson correlation coefficient. NRMSE denotes the accuracy of our<br>model. All metrics are computed against end-of-flow total power values 198                                                                                                                                                                                                                               |

## LIST OF FIGURES

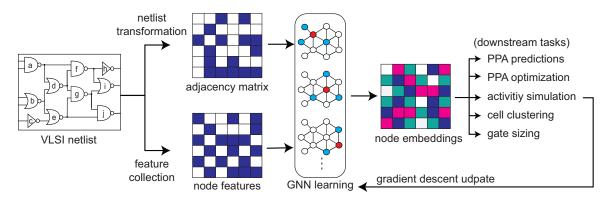

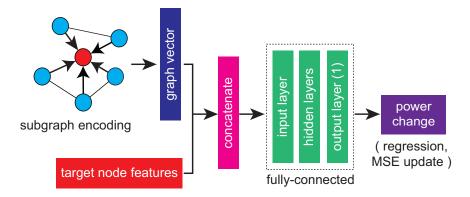

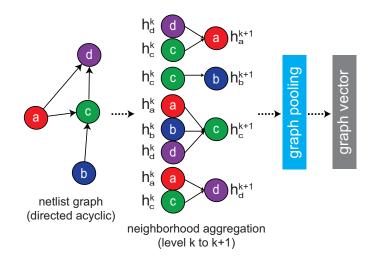

| 1.1 | A common GNN modeling architecture in PD                                                                                                                                                                                                                                                                                                                            | 2            |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

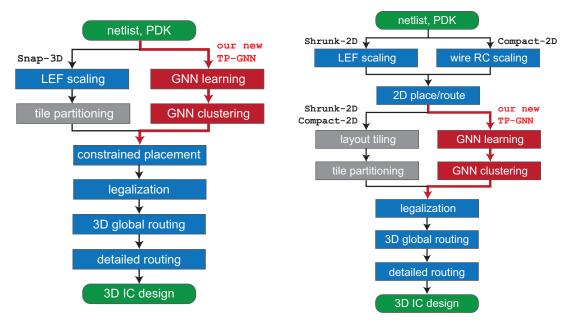

| 2.1 | Partitioning-first M3D design flow.                                                                                                                                                                                                                                                                                                                                 | 11           |

| 2.2 | Partitioning-last M3D design flow.                                                                                                                                                                                                                                                                                                                                  | 11           |

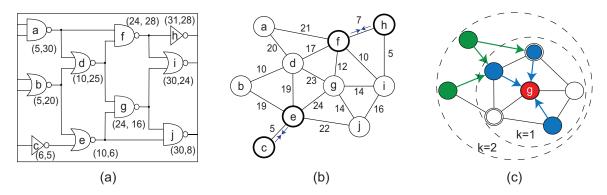

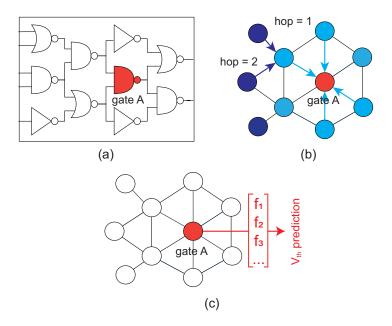

| 2.3 | TP-GNN visualization. (a) Input netlist with two design hierarchies: $\{a, b, d, f, and \{c, e, g, i, j\}$ . Numbers represent cell locations. (b) Hierarchy-aware edge contractions on the transformed clique-based graph. Edge weights represent the Manhattan distance. (c) For target node $g$ , sampling and aggregating features from its $k$ -hop neighbors. | , <i>h</i> } |

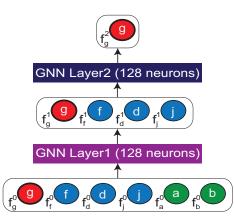

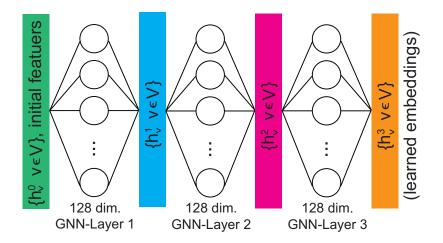

| 2.4 | Graph learning for target node $g$ . Following from Figure 8.1(c) we demonstrate the detailed learning process, where $\{f^0\}$ represent the initial features and $f_g^2$ represents the learned representations.                                                                                                                                                  | 15           |

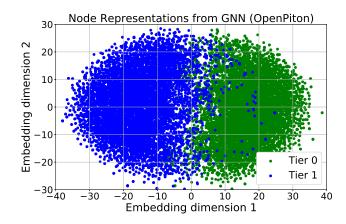

| 2.5 | t-SNE visualizations of the learned node representations from GNN. Each dot represents a cell in the design and is colored by its final tier assignment from Algorithm 3                                                                                                                                                                                            | 24           |

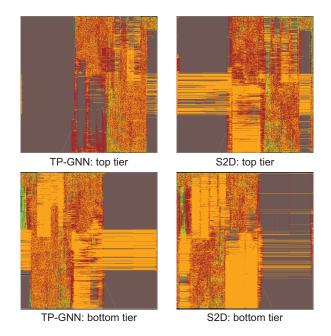

| 2.6 | GDS layouts of OpenPiton [41] using TP-GNN vs. Shrunk-2D [31] flow.<br>TP-GNN flow achieves 7.7% better wirelength.                                                                                                                                                                                                                                                 | 27           |

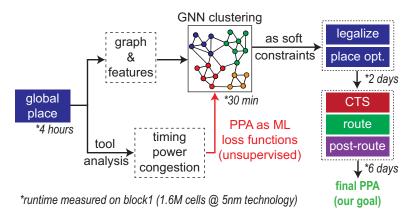

| 3.1 | Our PPA-directed placement optimization framework in an industrial PD flow.                                                                                                                                                                                                                                                                                         | 36           |

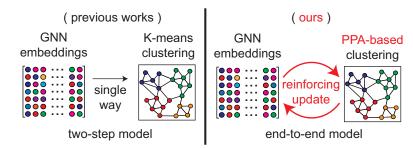

| 3.2 | Difference between prior works [6, 7] and ours. Our framework is end-to-<br>end differentiable and directly optimizes PPA metrics as ML loss functions.                                                                                                                                                                                                             | 36           |

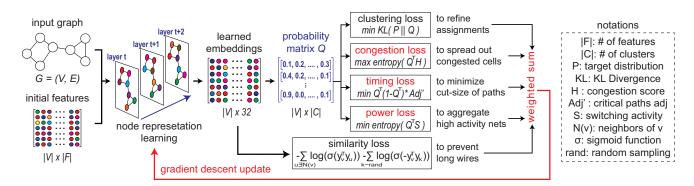

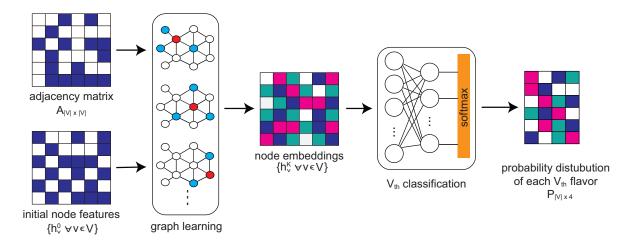

| 3.3  | Our PPA-directed unsupervised deep graph clustering framework. Given<br>a netlist graph, initial node features, and PPA tool analysis (congestion,<br>timing, power), our framework is trained to optimize PPA metrics as ML<br>loss functions by jointly improving the node embeddings and the clustering<br>assignments in an end-to-end manner.                          | 37 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

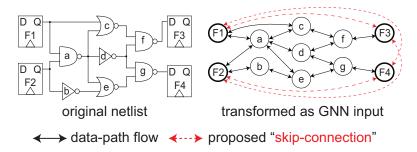

| 3.4  | Proposed netlist transformation that honors timing propagation. "Skip-<br>connections" link start points and end points of timing paths during GNN<br>message passing.                                                                                                                                                                                                      | 40 |

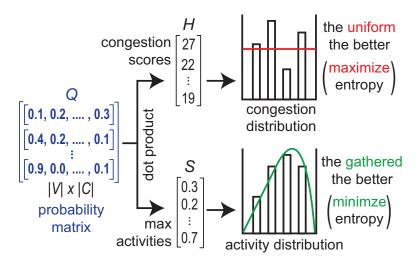

| 3.5  | Illustration of congestion loss and power loss formulations that rely on en-<br>tropy maximization and minimization. Note that both distributions are nor-<br>malized as probabilities.                                                                                                                                                                                     | 47 |

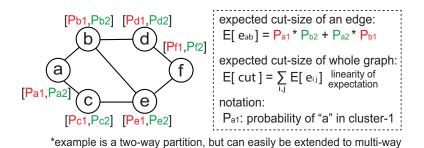

| 3.6  | Illustration of "cut-size" loss formulation.                                                                                                                                                                                                                                                                                                                                | 49 |

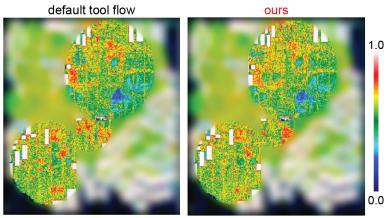

| 3.7  | Unsupervised PPA-directed clustering results on block1 at a commercial $5nm$ technology. The figure is intentionally blurred due to proprietary                                                                                                                                                                                                                             | 54 |

| 3.8  | Impact on congestion after placement. Our optimization technique reduces the worst congestion by <b>60.9%</b> . The worst congestion is defined by the commercial tool to be the largest contiguous overflowing area                                                                                                                                                        | 56 |

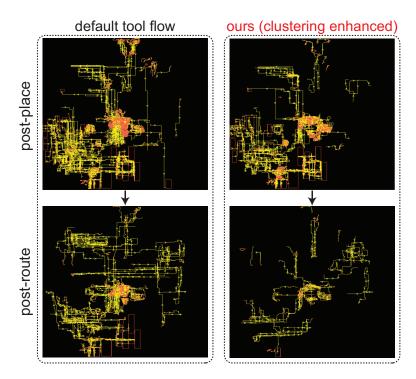

| 3.9  | Illustration of PPA-GNN impact on timing critical paths from post-place to post-route. Critical wires are in yellow and cells are in red.                                                                                                                                                                                                                                   | 57 |

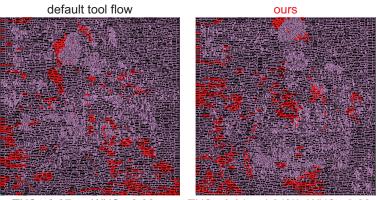

| 3.10 | Illustration of attraction impact on timing violating cells with the DMA benchmark. The left figure shows the distribution of the cells whose output pins have negative slack values in the default tool flow (i.e., without attraction). The right figure shows that with the clustering constraints generated by PPA-GNN, the initially violating cells aggregate closer. | 60 |

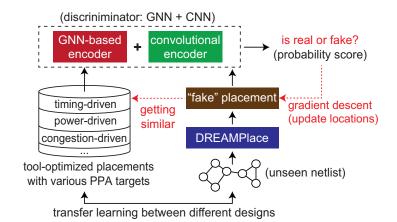

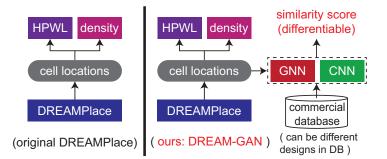

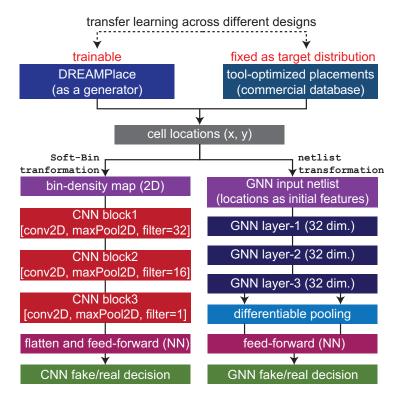

| 4.1  | High-level overview of DREAM-GAN that performs placement optimiza-<br>tion using generative adversarial learning. Note that DREAM-GAN facili-<br>tates transfer learning between different designs.                                                                                                                                                                         | 65 |

| 4.2  | Difference in objectives between DREAMPlace [lin2019dreamplace] and DREAM-GAN at each placement iteration. The cell locations generated from DREAMPlace are encouraged to follow the ones in commercial database.                                                                                                                                                           | 65 |

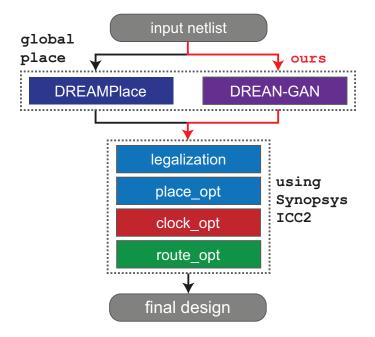

| 4.3  | Illustration of integrating open-source placers into an industrial design flow using Synopsys ICC2, where the global placement stage is replaced with proceeding stages remain the same.                                                                                                                                                                                    | 67 |

|      |                                                                                                                                                                                                                                                                                                                                                                             |    |

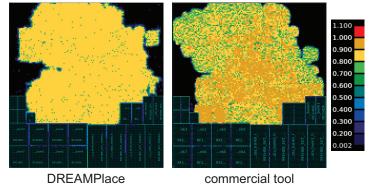

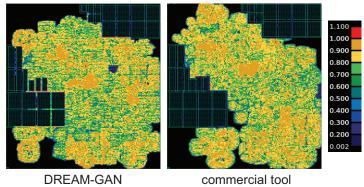

| 4.4 | Comparison of cell density maps between DREAMPlace and Synopsys ICC2 under the same global placement density target. It is observed that the commercial tool has extra intelligence on where to locally aggregate or spread out cells in order to optimize crucial PPA metrics while satisfying the global density constraints.                                                                                                                                                                                                                                                                                                        | 68 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

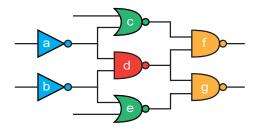

| 4.5 | Illustration of GNN netlist transformation and graph pooling. First, fol-<br>lowing from [8], we perform timing-aware netlist transformation by only<br>taking timing arcs as GNN message passing edges. Then, we perform at-<br>tention graph pooling to construct the final graph-level vector that charac-<br>terizes the input placement. Note that the poolings are differentiable (i.e,<br>learnable), meaning that the clustering results (e.g., $\{a, c, e\}$ is now a clus-<br>ter) will change across training iterations. The obtained graph-level vector<br>is fed to downstream networks to quantify placement similarity | 70 |

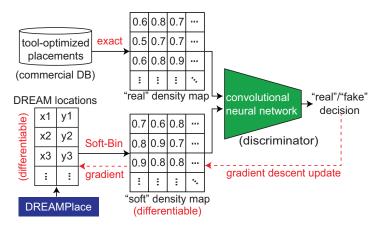

| 4.6 | Generative adversarial learning conducted by CNNs using the proposed<br>Soft-Bin density map transformation technique. The goal of DREAMPlace<br>is to generate the placements that have similar bin-density maps as the ones<br>in the commercial database                                                                                                                                                                                                                                                                                                                                                                            | 75 |

| 4.7 | Detailed architecture of DREAM-GAN that leverages CNN-based and GNN-<br>based discriminators to quantify placement similarity between different<br>placement sources.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76 |

| 4.8 | Density map comparison between the proposed DREAM-GAN and Synopsys ICC2 on the CPU-2 benchmark.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80 |

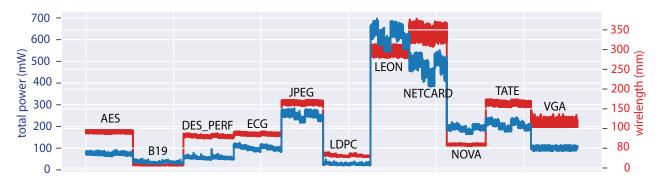

| 5.1 | Total power (mW) and wirelength (mm) distributions among 115.5k full-<br>chip designs of all 11 benchmarks in our database                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 85 |

| 5.2 | A high-level view of this work and the three objectives we have achieved.<br>The first objective is to predict the CTS outcomes in high precision. The<br>second objective is to recommend designers good CTS input settings. The<br>third objective is to determine whether the input settings outperform com-<br>mercial tool's auto-setting.                                                                                                                                                                                                                                                                                        | 89 |

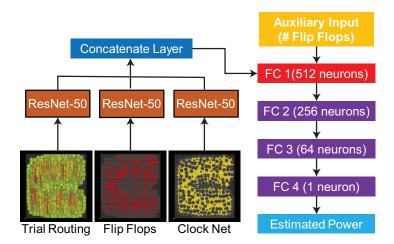

| 5.3 | Our image feature extraction flow. The extracted features are colored in red. Note that each raw image vector extracted from ResNet-50 has 1024 dimensions. The concatenate layer thereby forms a vector in 3072 dimensions. Finally, with an auxiliary input that denotes the number of flip flops, the input of the self-devised FC layers are in 3073 dimensions                                                                                                                                                                                                                                                                    | 91 |

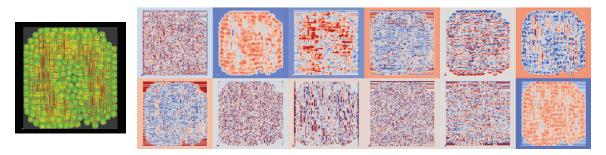

| 5.4  | Visualization of trial routing image in 12 different convolutional filters of ResNet-50 [85], where the usage of metal layers is well captured across different filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

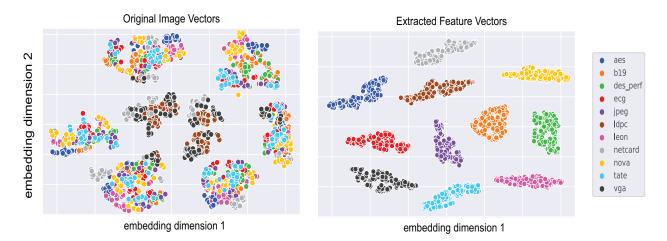

| 5.5  | t-SNE visualizations of the original placement image vectors and the ex-<br>tracted feature vectors from our transfer learning flow, where the extracted<br>features successfully characterize different designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

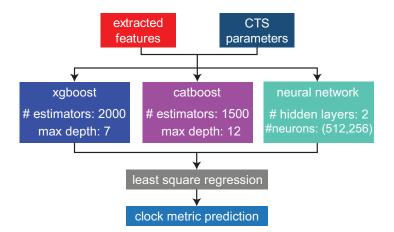

| 5.6  | Visualization of single metal-model, which is stacked by three base models through weighted least square regression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

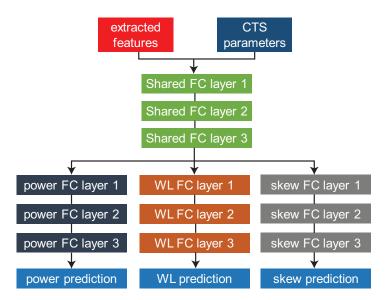

| 5.7  | Our proposed multi-objective regression model. The detailed architectures are as follows. The shared FC layers colored in green have number of neurons equal to 512, 256, and 128 in sequential, where each dedicated FC layer group has number of neurons equal to 64, 32, 1 from input to output. 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

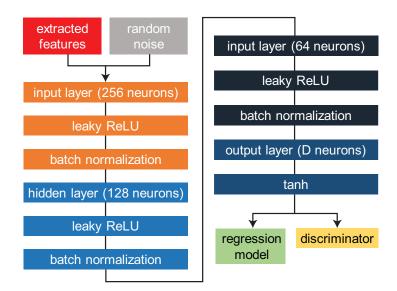

| 5.8  | Detailed structure of our GAN generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

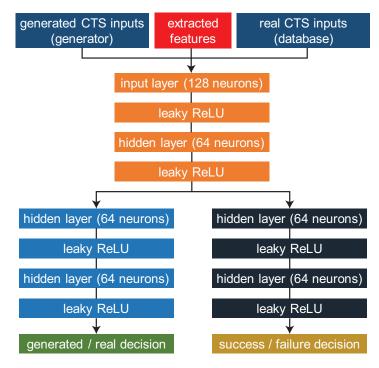

| 5.9  | Detailed structure of our GAN discriminator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

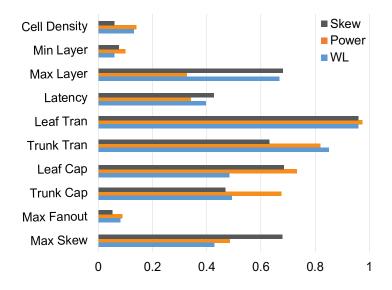

| 5.10 | Relative importance of CTS input parameters on skew, power, and wire-<br>length for JPEG benchmark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

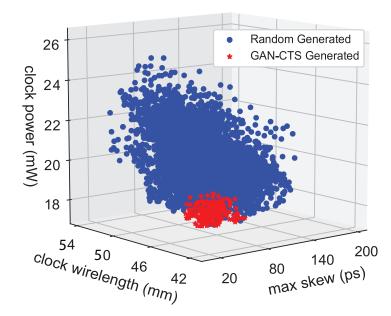

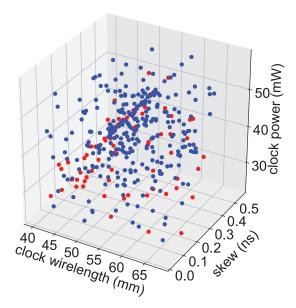

| 5.11 | Distributions of random generated vs. GAN-CTS generated clock trees on the ECG benchmark. The commercial auto-setting achieved a clock tree with values of $23.56mW$ in clock power, $49.69mm$ in clock wirelength, and $16ps$ in skew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

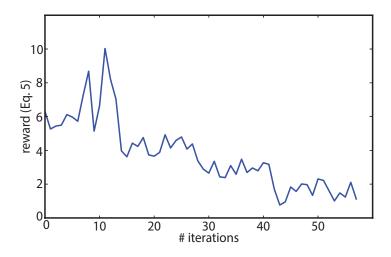

| 5.12 | Bayesian optimization on VGA benchmark (starting from random sampled CTS parameter sets). Reward $r$ is defined in Equation Equation 5.5 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

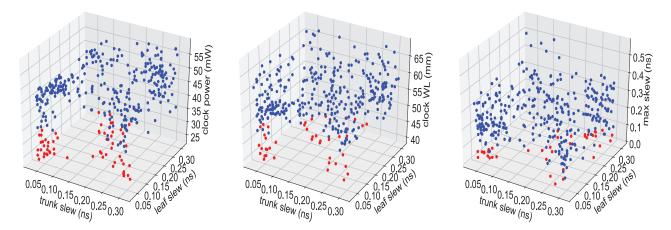

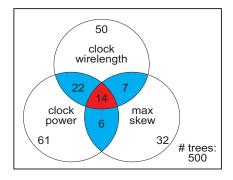

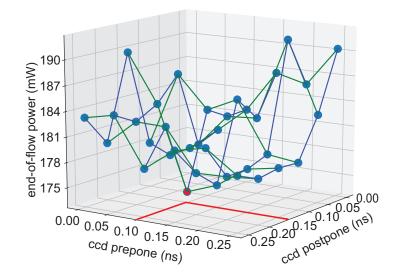

| 5.13 | VGA slew sweeping experiments. Out of the 10 CTS input parameters as shown in Table 9.1, we sweep around the leaf and trunk target slew values while fixing others as auto-set and generate 500 clock trees in total. For each CTS metrics (i.e., clock power, clock wirelength, and maximum achieved skew), we plot the scatter distribution of the 500 clock trees denoted in blue and red dots, where red dots denote the ones whose underlying CTS metric are better than the auto-generated clock tree from the commercial tool. In summary, compared with the auto-generated clock tree, there are 61 (out of 500) trees whose clock power are better, 50 whose clock wirelength are better, and 32 whose achieved skew values are better, where the corresponding Venn diagram is shown in Figure 5.14 |

| 5 | 5.14 | Venn diagram of the VGA slew sweeping experiment (Figure 5.13). Note that a number on a colored region denotes the number of trees fall into that region, where a number on an uncolored region denotes the number of trees in the shape boundary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 | 5.15 | CTS metric distribution of the VGA slew experiment (Figure 13). The red dots denote the clock trees that are achieved with both trunk slew and leaf slew targets smaller than $0.1ns.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

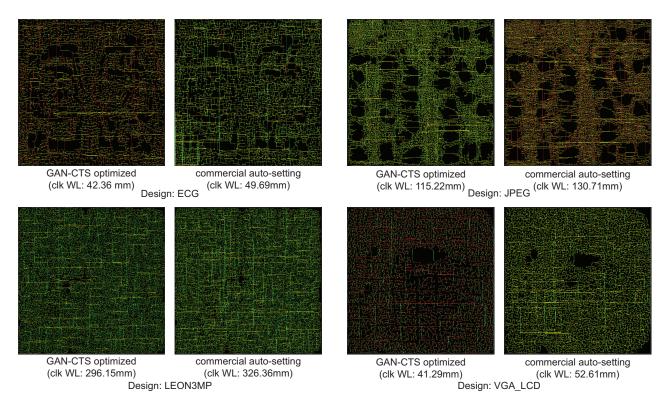

| 5 | 5.16 | Clock tree layout comparison of four validation benchmarks. GAN-CTS optimized clock trees have observant clock wirelength saving. The detailed comparisons are reported in Table 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

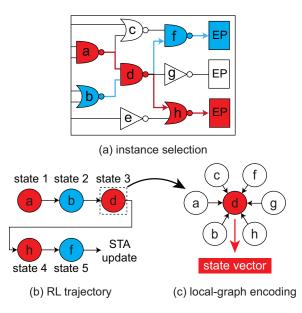

| e | 5.1  | Illustration of our RL gate sizing process. (a) Input netlist with 3 end points (EPs). First, we identify the worst critical path in the design (red), and then for each endpoint, we identify the most negative slack path (e.g. blue) overlapping with the design critical path. Finally, instances on these paths (the design critical path and the other paths overlapped with it) are selected for one sizing iteration. (b) Sort the selected instances in topological order, and determine their final gate sizes sequentially by considering each of them as an <i>RL state</i> . STA is performed after all selected instances are assigned new sizes. (c) Example of local-graph encoding using GNNs on gate "d". The encoded state vector is taken as the input of the RL agent to determine the action (new gate type). |

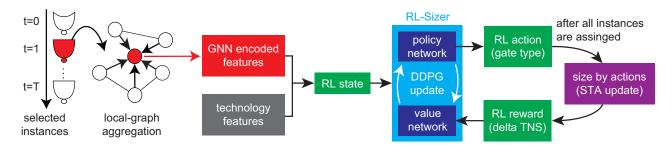

| 6 | 5.2  | Overview of our RL-Sizer framework. Given the selected instances from Algorithm Algorithm 9, for each instance (e.g. red), we take its encoded local-graph features along with the technology information as the <i>RL state</i> $s_t$ , and leverage RL-Sizer to determine the <i>RL action</i> $a_t$ assigned. An STA update is performed when all selected instances are assigned new gate sizes. Finally, we take the "local-graph TNS change" as the <i>RL reward</i> of each action taken. Rewards across time steps (instances) are leveraged to update RL-Sizer through the DDPG algorithm [25]                                                                                                                                                                                                                             |

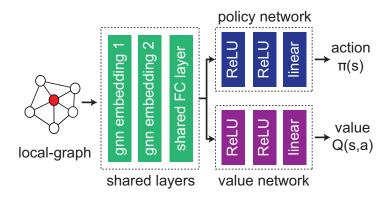

| 6 | 5.3  | Our RL agent architecture that consists of value and policy networks. Table Table 6.2 provides the dimension information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

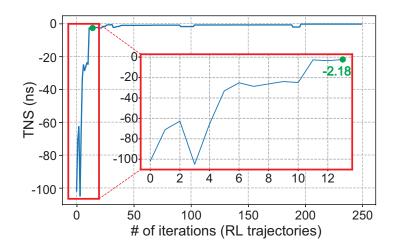

| 6 | 5.4  | RL-Sizer sizing iterations on block2 (5nm). It takes 250 iterations (about 14 hours) to improve TNS from -101.82 to -0.81 (ns). However, the TNS quickly converges in the first 13 iterations (less than 3 hours)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

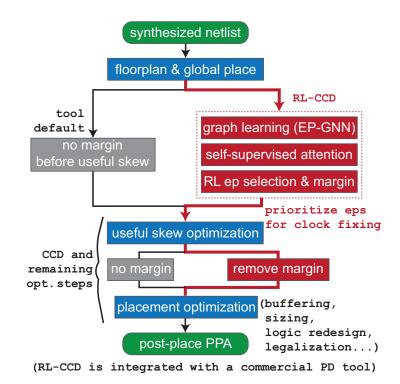

| 7 | 7.1  | Default tool flow vs. our RL-enhanced flow that performs endpoint priori-<br>tization using graph learning and self-supervised attention [111] 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

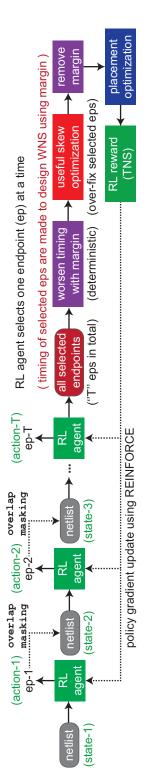

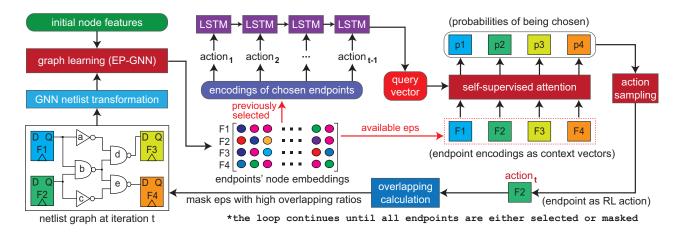

| 7.2 | High-level overview of our framework. At each RL time step (training iteration), our agent selects one endpoint at a time and mask out other end-                                                                                                                                                                                                                                                                                                           |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | points based on overlapping calculation. The selection process completes                                                                                                                                                                                                                                                                                                                                                                                    |     |

|     | when all violating endpoints are either masked or selected. Then, with the                                                                                                                                                                                                                                                                                                                                                                                  |     |

|     | RL-selected endpoints, we apply margin to worsen their timing to design<br>Worst Negative Slack (WNS) prior to the useful skew optimization so that                                                                                                                                                                                                                                                                                                         |     |

|     | they can be "over-fixed" by clock arrival adjustments. The applied margins are removed before entering the remaining placement optimization steps, which involves optimization techniques such as buffering, sizing, logic restructuring, legalization etc. Finally, the achieved TNS value is taken as the <i>RL reward</i> of the current <i>trajectory</i> to update framework parameters using a policy gradient-based algorithm named REINFORCE [112]. | 135 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 100 |

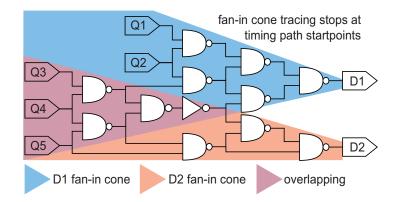

| 7.3 | Illustration of endpoint fan-in cone overlapping. Note that the fan-in cone tracing of an endpoint stops at its previous startpoints. The overlapping ratio is calculated as dividing the number of overlapped cells by the total number of fan-in cone cells.                                                                                                                                                                                              | 137 |