## Design of High-Speed SiGe HBT Circuits for Wideband Transceivers

A Dissertation Presented to The Academic Faculty

by

Yuan Lu

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology May 2007

## Design of High-Speed SiGe HBT Circuits for Wideband Transceivers

Approved by:

Dr. John D. Cressler, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Ioannis Papapolymerou School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Joy Laskar School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Linda Milor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Haomin Zhou School of Mathematics *Georgia Institute of Technology*

Date Approved: December 15, 2006

To my beloved family

### ACKNOWLEDGEMENTS

I would like to to thank my advisor, Professor John Cressler, for the opportunities, guidance, encouragement, and support he has given me throughout the past five years. Not only is he the finest teacher and researcher I have ever met, he is also a friend who is always ready to listen and help.

I would like to thank Professor Joy Laskar, Professor John Papapolymerou, Professor Linda Milor, and Professor Haomin Zhou, who served as my committee members, for all their valuable comments and corrections. I would also like to thank Professor Glenn Smith for serving as a member of my proposal review committee.

I would like to thank my colleagues in the SiGe Research Group: Dr. Ramkumar Krithivasan, Dr. Wei-Min Lance Kuo, Mr. Xiangtao Li, Mr. Joel Andrews, Dr. Jon Comeau, Dr. Enhai Zhao, Dr. Chendong Zhu, Mr. Akil Sutton, Mr. Curtis Grens, Mr. Marco Bellini, Ms. Laleh Najafizadeh, Mr. Aravind Appaswamy, Mr. Jiahui Yuan, Mr. Tushar Thrivikraman, Mr. Tom Cheng, Mr. Steven Finn, Mr. Ryan Diestelhorst, Mr. Kurt Moen, Mr. Nand Jha, Mr. Prabir Saha, Mr. Anuj Madan, Mr. Mustayeen Nayeem, Mr. Adnan Ahmed, Mr. Mustansir Pratapgarhwala, Ms. Becca Haugerud, Ms. Ragad Al-Huq, Mr. Ming Teng Han, Mr. Man-Chun Lam, Mr. Gustavo Espinel, Dr. Zhenrong Jin, Dr. Qingqing Liang, Dr. Tianbing Chen, Dr. Zhiyun Luo, Dr. Shiming Zhang, Dr. Gang Zhang, Dr. Jarle Johansen, Dr. Jongsoo Lee, Dr. Seung-Yun Lee, Dr. Gnana Prakash, Dr. Bongim Jun, and Mr. Jose-Luis Olvera-Cervantes; as well as colleagues in the Microwave Applications Group: Dr. Bhaskar Banerjee, Dr. Sunitha Venkataraman, and Dr. Sebastien Nuttinck, for your significant contributions.

I would like to thank Dr. Hans Gustat and Dr. Bernd Heinemann at Innovations for High Performance Microelectronics for their cooperation.

I am grateful to my friends Chuanquan Liu, Jiancheng Meng, Dr. Shengyuan Li, Min Chen, and Chenfei Li, for their encouragement. My family has always given me strong support and encouragement in my studies and in other aspects of my life. I would like to thank and express my deepest love to everyone in my family from the bottom of my heart.

# **TABLE OF CONTENTS**

| DE  | DICA | <b>ΓΙΟΝ</b>                                 | iii  |

|-----|------|---------------------------------------------|------|

| AC  | KNOV | VLEDGEMENTS                                 | iv   |

| LIS | T OF | TABLES                                      | viii |

| LIS | T OF | FIGURES                                     | ix   |

| SUN | MMA  | RY                                          | xiii |

| I   | INT  | RODUCTION                                   | 1    |

|     | 1.1  | Applications of UWB Transceivers            | 1    |

|     | 1.2  | Motivations For Developing UWB Transceivers | 3    |

|     | 1.3  | Design Challenges of UWB transceivers       | 6    |

|     | 1.4  | SiGe HBT / BiCMOS Technology                | 9    |

|     | 1.5  | Organization of Dissertation                | 10   |

| II  | UWI  | B LOW NOISE AMPLIFIER                       | 14   |

|     | 2.1  | Introduction                                | 14   |

|     | 2.2  | Noise Factor of a Linear Two-Port Network   | 16   |

|     | 2.3  | BJT Noise Model                             | 18   |

|     | 2.4  | Narrow Band LNA                             | 20   |

|     | 2.5  | Resistive Feedback LNA                      | 23   |

|     | 2.6  | UWB LNA 1                                   | 24   |

|     | 2.7  | Measurement Results of LNA 1                | 29   |

|     | 2.8  | UWB LNA 2 and 3                             | 31   |

|     | 2.9  | Measurement Results of UWB LNA 2            | 33   |

|     | 2.10 | Measurement Results of UWB LNA 3            | 36   |

|     | 2.11 | Summary                                     | 42   |

| III | TRA  | CK-AND-HOLD AMPLIFIER                       | 44   |

|     | 3.1  | Introduction                                | 44   |

|     | 3.2  | Volrenkamp THA                              | 46   |

|                   | 3.3 | Fiocchi THA                                          | 48 |  |  |

|-------------------|-----|------------------------------------------------------|----|--|--|

|                   | 3.4 | Improved Fiocchi THA                                 | 49 |  |  |

|                   | 3.5 | Measurement Results                                  | 53 |  |  |

|                   | 3.6 | Summary                                              | 58 |  |  |

| IV                | TRA | NSCONDUCTANCE-C LOW-PASS FILTER                      | 59 |  |  |

|                   | 4.1 | Introduction                                         | 59 |  |  |

|                   | 4.2 | C-SiGe HBT Process Technology                        | 60 |  |  |

|                   | 4.3 | Transconductor Design                                | 63 |  |  |

|                   |     | 4.3.1 Differential Pair                              | 63 |  |  |

|                   |     | 4.3.2 Schmoock Transconductor                        | 65 |  |  |

|                   |     | 4.3.3 Voorman Transconductor                         | 67 |  |  |

|                   | 4.4 | Gyrator Design                                       | 69 |  |  |

|                   | 4.5 | Filter Design                                        | 70 |  |  |

|                   | 4.6 | Measurement Results                                  | 72 |  |  |

|                   | 4.7 | Summary                                              | 75 |  |  |

| V                 | RAI | DIATION RESPONSE OF THE THIRD GENERATION SIGE HBTS . | 76 |  |  |

|                   | 5.1 | Introduction                                         | 76 |  |  |

|                   | 5.2 | Experiment                                           | 78 |  |  |

|                   | 5.3 | <i>dc</i> Results                                    | 79 |  |  |

|                   | 5.4 | ac Results                                           | 82 |  |  |

|                   | 5.5 | Summary                                              | 88 |  |  |

| VI                | CON | NCLUSION AND FUTURE WORK                             | 89 |  |  |

| <b>REFERENCES</b> |     |                                                      |    |  |  |

| VIT               | A.  |                                                      | 99 |  |  |

## LIST OF TABLES

| 1  | Key Specifications of Wireless Technologies (after[6])                  | 2  |

|----|-------------------------------------------------------------------------|----|

| 2  | Military and Commercial Applications of UWB Technology (after [13]).    | 3  |

| 3  | Key Specifications of SiGe BiCMOS Technologies Used in this Research    | 10 |

| 4  | Summary of the SiGe UWB LNA 1 Characteristics                           | 32 |

| 5  | Summary of the SiGe UWB LNA 2 Characteristics                           | 36 |

| 6  | Summary of the SiGe UWB LNA 3 Characteristics                           | 41 |

| 7  | Comparison with Published Si/SiGe UWB LNAs                              | 43 |

| 8  | Summary of the SiGe THA Characteristics.                                | 58 |

| 9  | Comparison with Published Si/SiGe High-Speed Track-and-Hold Amplifiers. | 58 |

| 10 | Key Parameters of the C-SiGe Technology.                                | 60 |

| 11 | Comparison with Published High-Frequency Active Low-Pass Filters        | 75 |

# LIST OF FIGURES

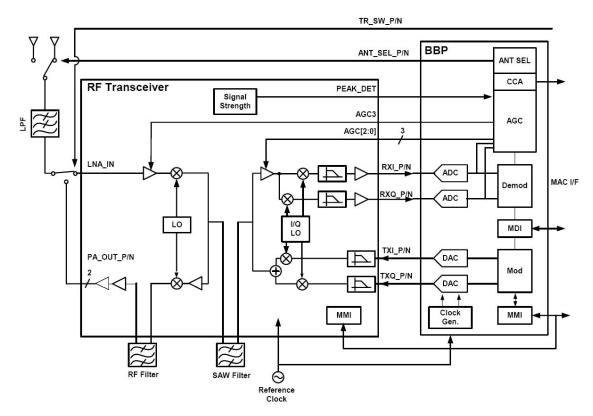

| 1  | Block diagram of a super-heterodyne transceiver for IEEE 802.11b (after [14]).                       | 4  |

|----|------------------------------------------------------------------------------------------------------|----|

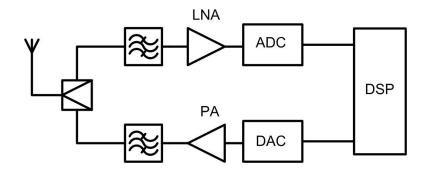

| 2  | Block diagram of the impulse-radio transceiver (after [18])                                          | 6  |

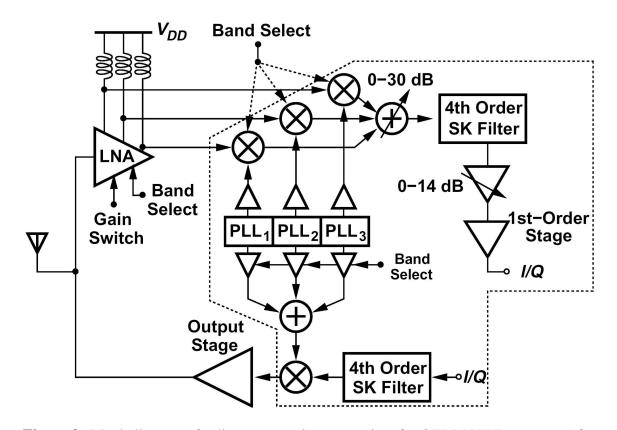

| 3  | Block diagram of a direct conversion transceiver for OFDM UWB systems (after [21]).                  | 7  |

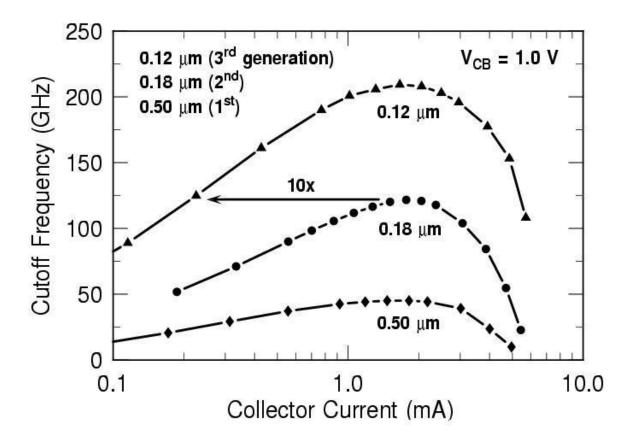

| 4  | Measured $f_T$ as a function of bias current for three SiGe technology generations.                  | 11 |

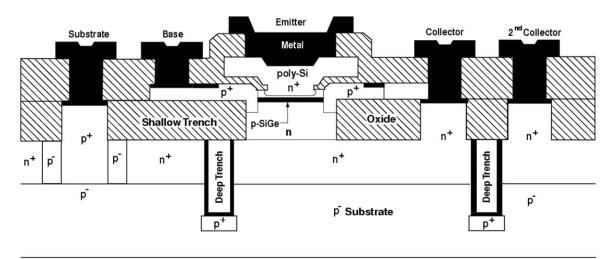

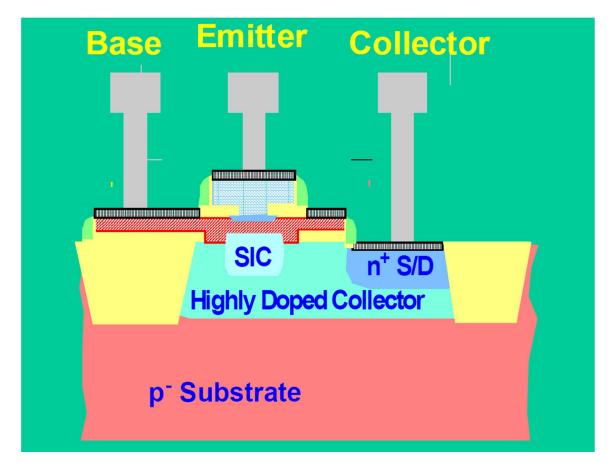

| 5  | Schematic cross-section of the 7HP SiGe HBT.                                                         | 15 |

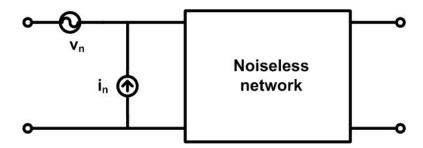

| 6  | Two-port network with input-referred noise voltage source and current source.                        | 16 |

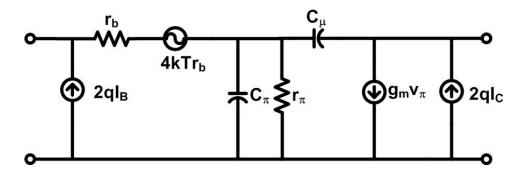

| 7  | Noise model of the bipolar transistor                                                                | 18 |

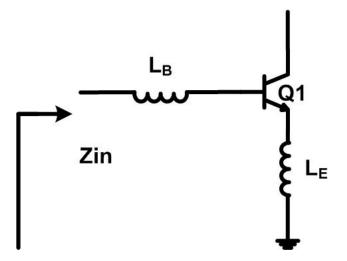

| 8  | Common emitter amplifier with emitter and base inductors                                             | 21 |

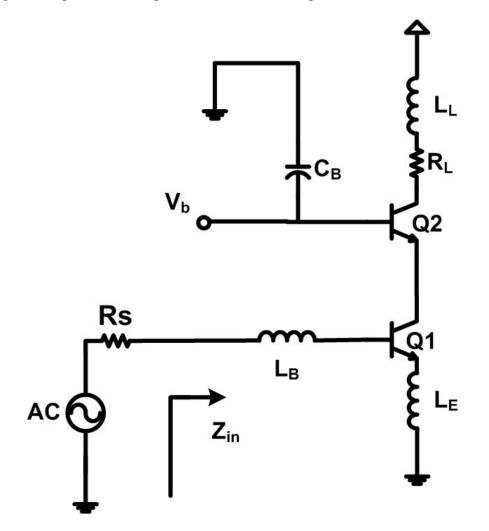

| 9  | Schematic of the cascode LNA with inductive degeneration.                                            | 22 |

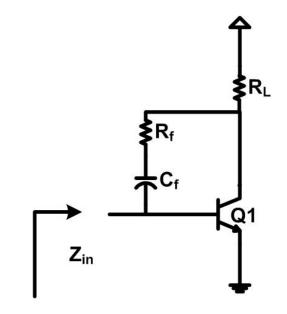

| 10 | Schematic of the LNA with shunt-shunt feedback.                                                      | 23 |

| 11 | Schematic of the LNA with shunt-shunt feedback and emitter follower                                  | 24 |

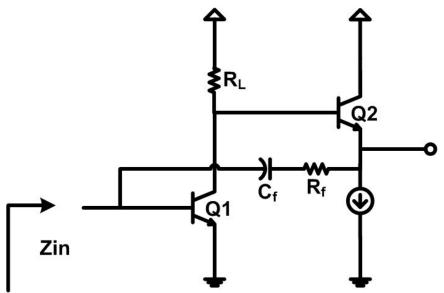

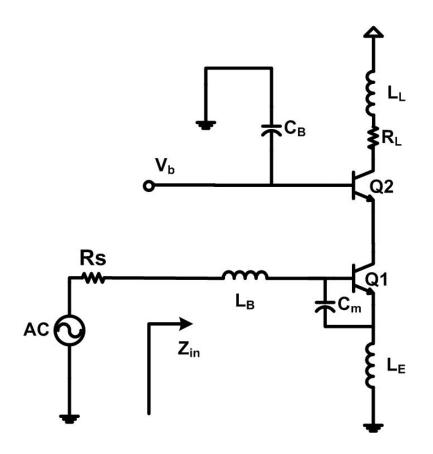

| 12 | Schematic of the broadband LNA with weak resistive feedback                                          | 25 |

| 13 | Schematic of the broadband LNA with shunt base-emitter capacitor                                     | 27 |

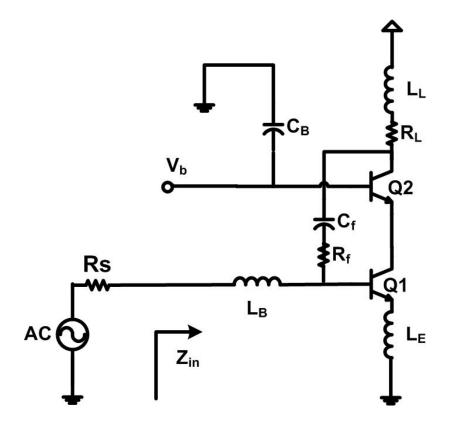

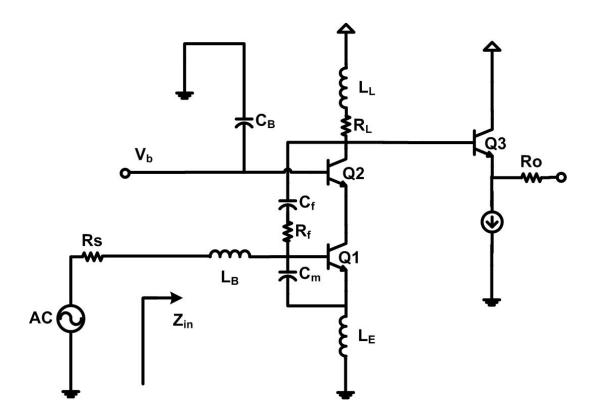

| 14 | Schematic of the present SiGe UWB LNA with weak resistive feedback and shunt base-emitter capacitor. | 28 |

| 15 | Die micrograph of the SiGe UWB LNA 1                                                                 | 29 |

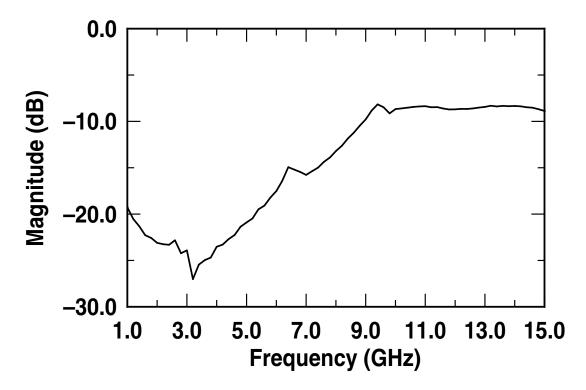

| 16 | Measured S-parameters of the SiGe UWB LNA 1                                                          | 30 |

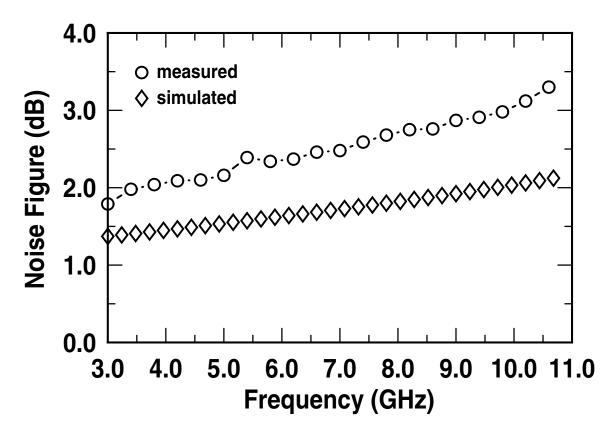

| 17 | Measured and simulated noise figure of the SiGe UWB LNA 1                                            | 31 |

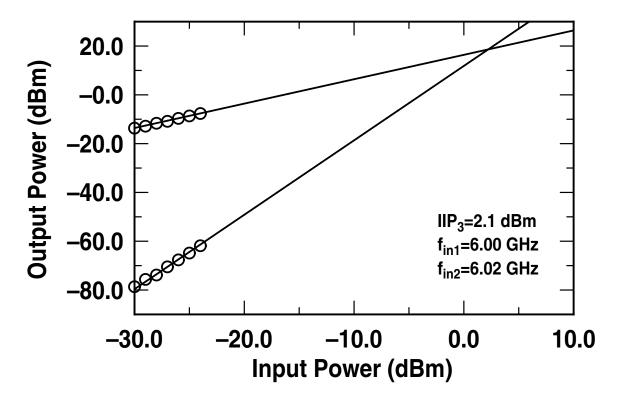

| 18 | Measured IIP3 of the SiGe UWB LNA 1                                                                  | 32 |

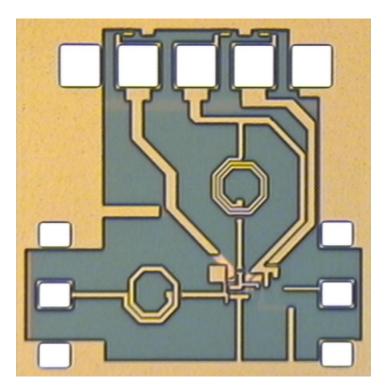

| 19 | Die micrograph of the SiGe UWB LNA 2                                                                 | 33 |

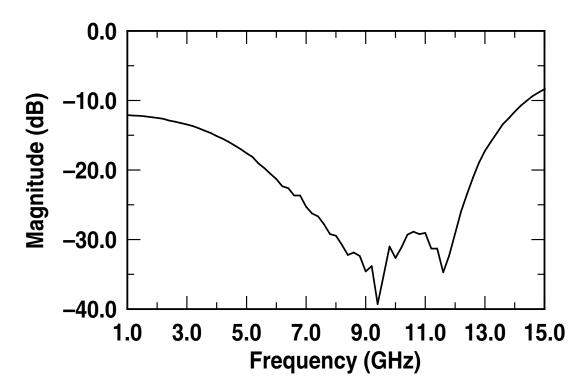

| 20 | Measured $S_{11}$ of the SiGe UWB LNA 2                                                              | 34 |

| 21 | Measured $S_{22}$ of the SiGe UWB LNA 2                                                              | 34 |

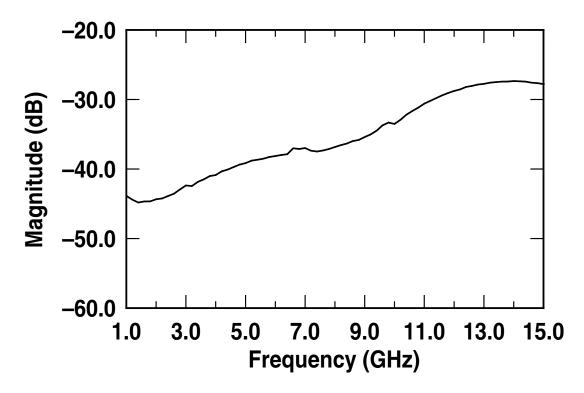

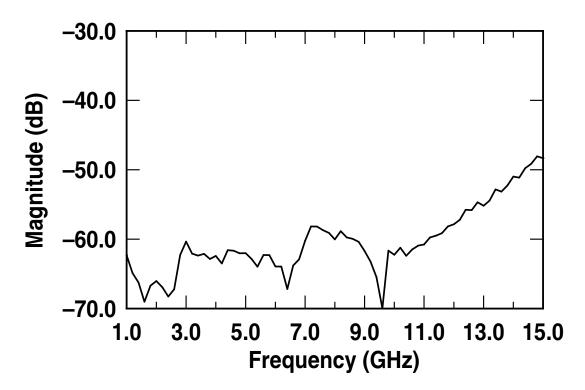

| 22 | Measured $S_{12}$ of the SiGe UWB LNA 2                                                              | 35 |

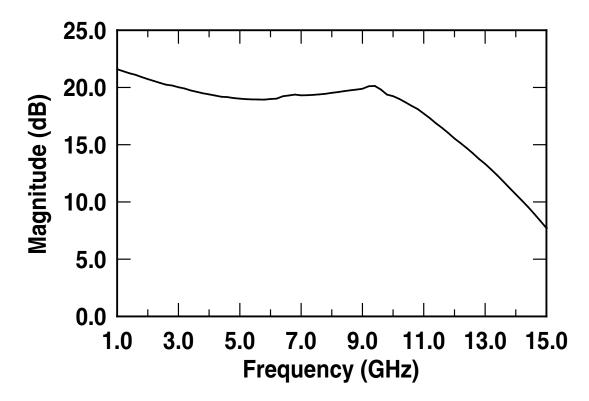

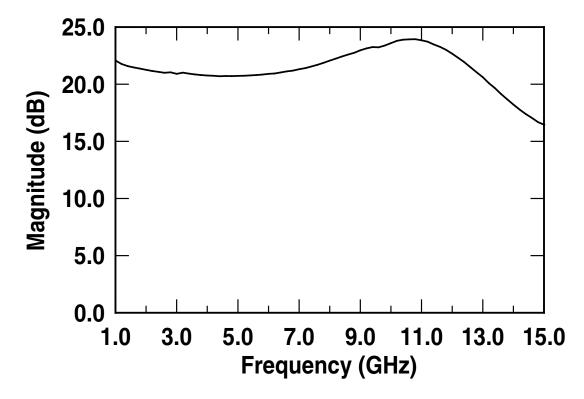

| 23 | Measured $S_{21}$ of the SiGe UWB LNA 2                                                              | 36 |

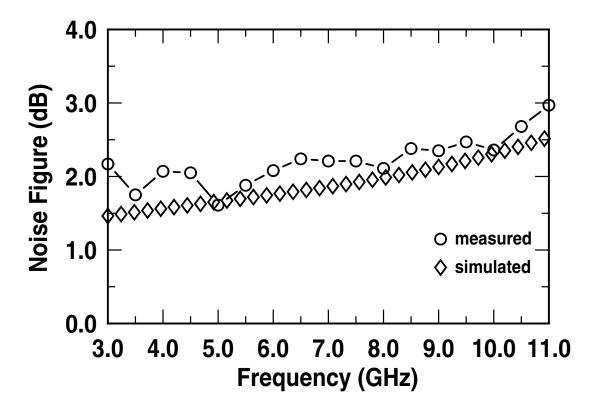

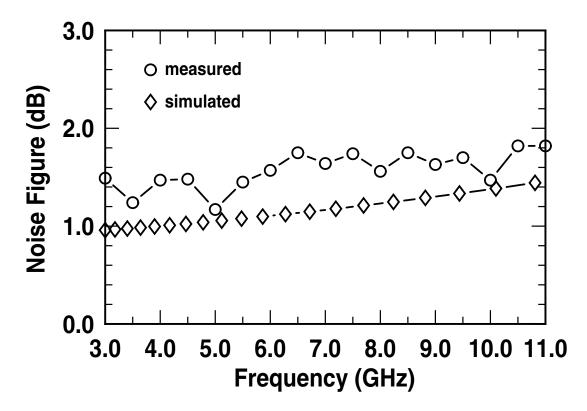

| 24 | Measured and simulated noise figure of the SiGe UWB LNA 2                                            | 37 |

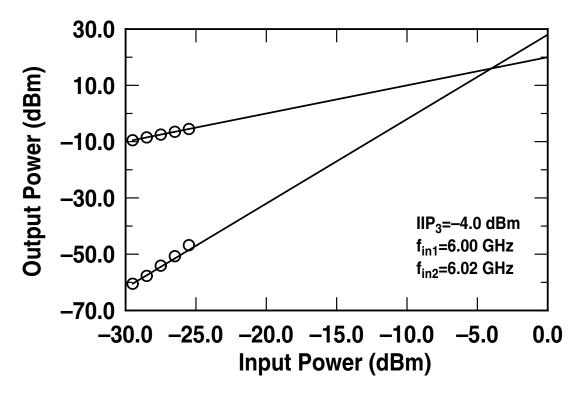

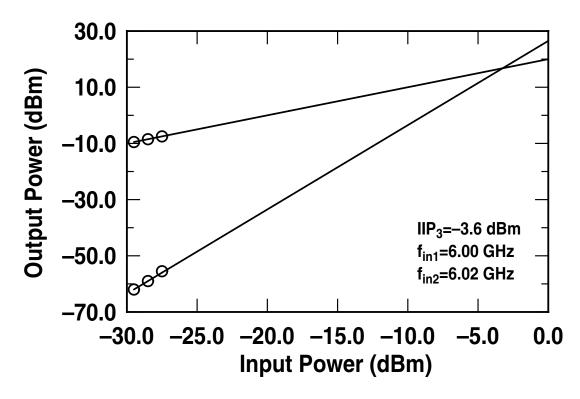

| 25 | Measured IIP3 of the SiGe UWB LNA 2                                                  | 38 |

|----|--------------------------------------------------------------------------------------|----|

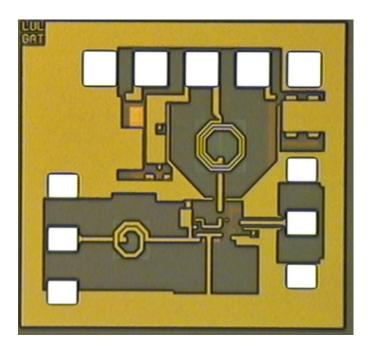

| 26 | Die micrograph of the SiGe UWB LNA 3                                                 | 38 |

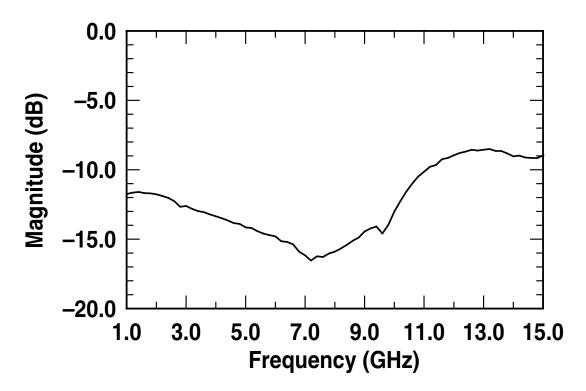

| 27 | Measured $S_{11}$ of the SiGe UWB LNA 3                                              | 39 |

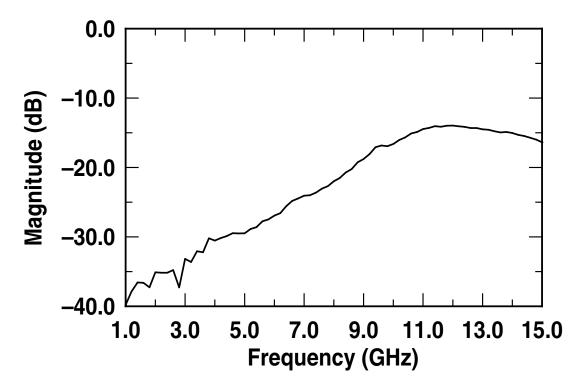

| 28 | Measured $S_{22}$ of the SiGe UWB LNA 3                                              | 39 |

| 29 | Measured $S_{12}$ of the SiGe UWB LNA 3                                              | 40 |

| 30 | Measured $S_{21}$ of the SiGe UWB LNA 3                                              | 40 |

| 31 | Measured and simulated noise figure of the SiGe UWB LNA 3                            | 41 |

| 32 | Measured IIP3 of the SiGe UWB LNA 3                                                  | 42 |

| 33 | Schematic cross-section of the 200 GHz <i>npn</i> SiGe HBT                           | 45 |

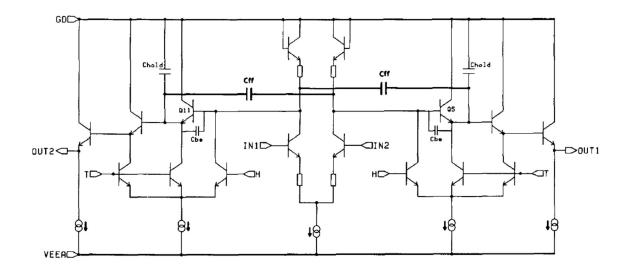

| 34 | Schematic of the Vorenkamp THA (after [65]).                                         | 47 |

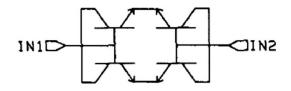

| 35 | Schematics of the feed-forward capacitor $C_{FF}$ (after [65])                       | 48 |

| 36 | Schematics of the Fiocchi THA (after [66])                                           | 49 |

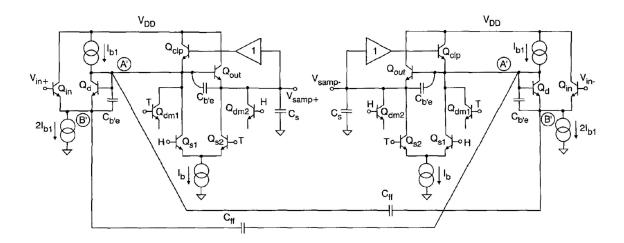

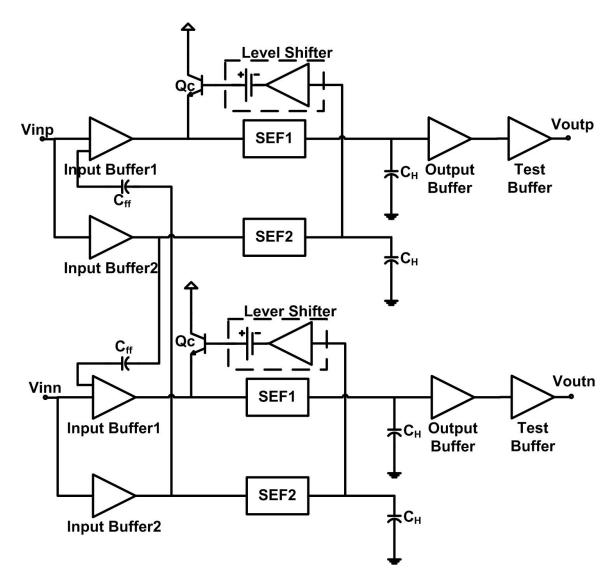

| 37 | Block diagram of the 8-b 12-GSample/sec THA.                                         | 50 |

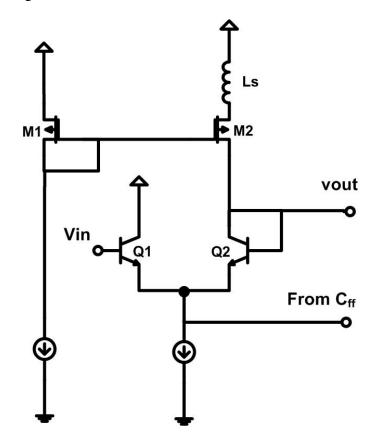

| 38 | Schematic of the proposed high-performance input buffer                              | 51 |

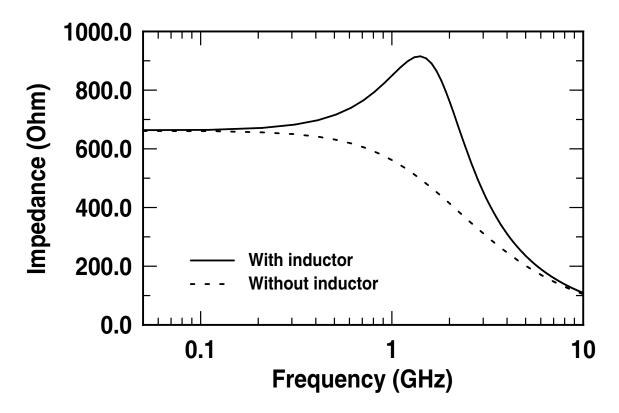

| 39 | Calculated output impedance of the input buffer as a function of frequency.          | 52 |

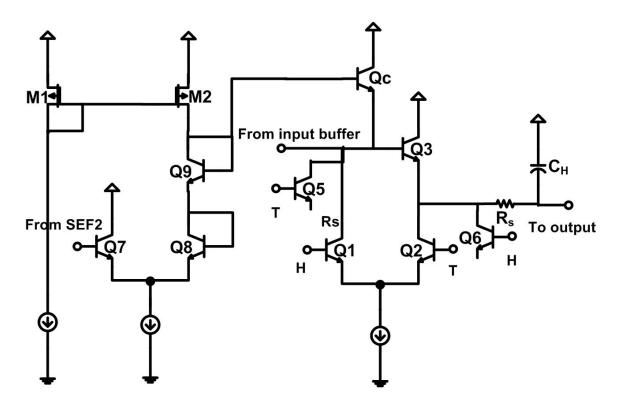

| 40 | Schematic of the switched-emitter-follower and the level shifter                     | 53 |

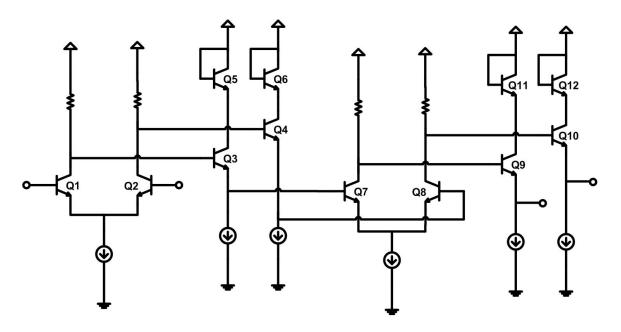

| 41 | Schematic of the clock buffer                                                        | 53 |

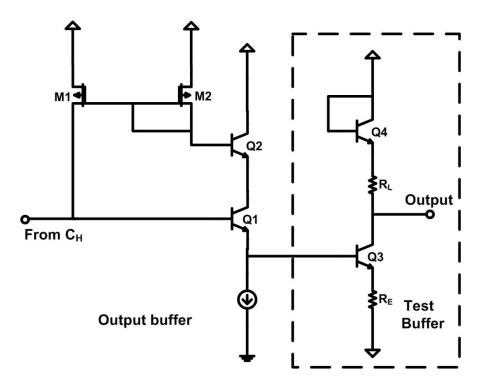

| 42 | Schematic of the output buffer and 50 $\Omega$ test buffer                           | 54 |

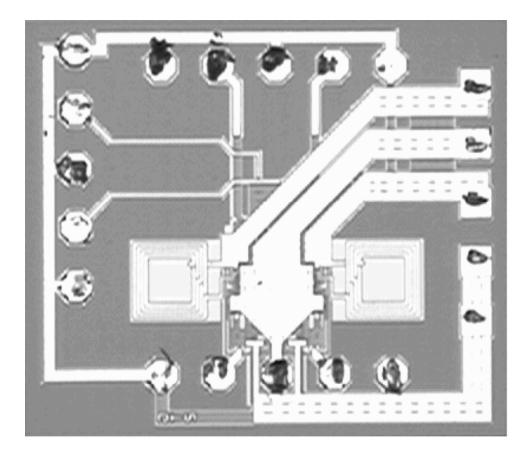

| 43 | Chip micrograph of the 8-b 12-GSample/s SiGe THA.                                    | 55 |

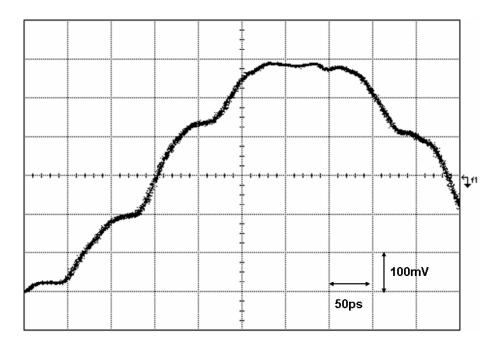

| 44 | Measured output waveform at 12-GSample/sec with a 1.5 GHz input fre-<br>quency.      | 56 |

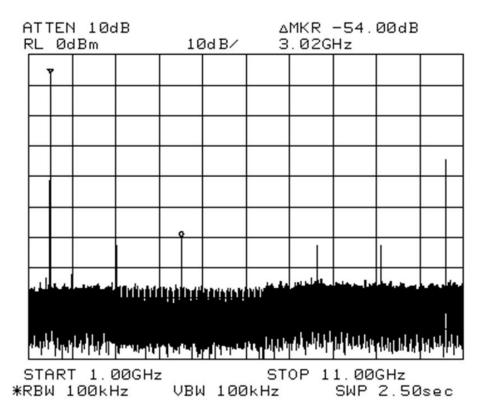

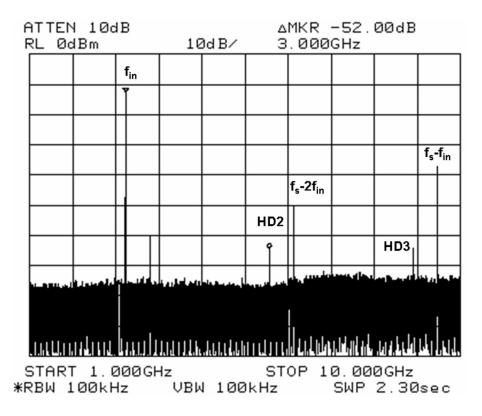

| 45 | Measured output spectrum with 12.5-GSample/sec and a 1.5 GHz input frequency.        | 56 |

| 46 | Measured output spectrum with 12.5-GSample/sec and a 3.0 GHz input frequency.        | 57 |

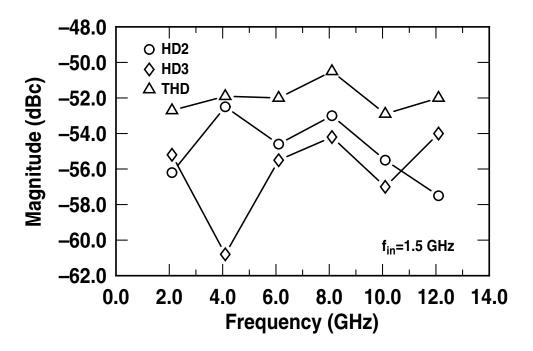

| 47 | Output harmonic distortion as a function of sampling frequency                       | 57 |

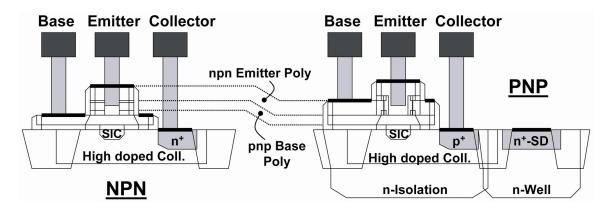

| 48 | Schematic cross-section of the <i>npn</i> and <i>pnp</i> SiGe HBTs                   | 60 |

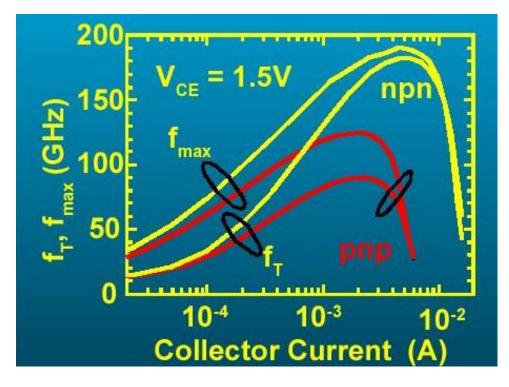

| 49 | $f_T$ and $f_{max}$ vs. collector current of the <i>npn</i> and <i>pnp</i> SiGe HBTs | 61 |

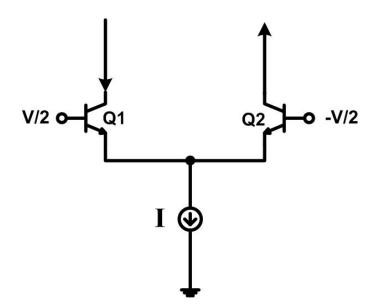

| 50 | Schematic of the differential pair                                                   | 62 |

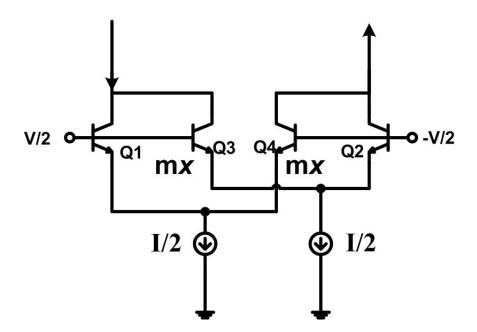

| 51 | Schematic of the Schmoock transconductor.                                            | 63 |

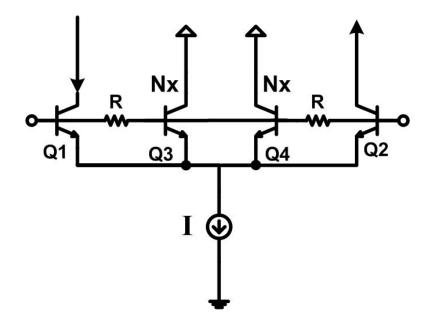

| 52 | Schematic of the Voorman transconductor.                                                                                                                     | 63 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

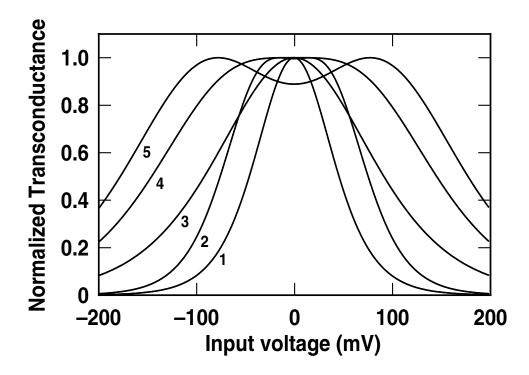

| 53 | Theoretical normalized transconductance $(g_m/g_{m,max})$ as a function of the input voltage.                                                                | 64 |

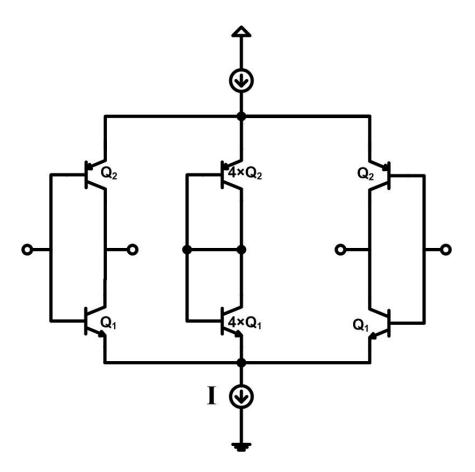

| 54 | Schematic of the complementary Voorman transconductor used here                                                                                              | 65 |

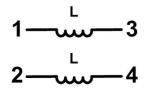

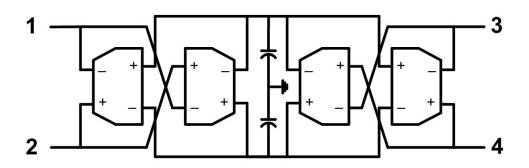

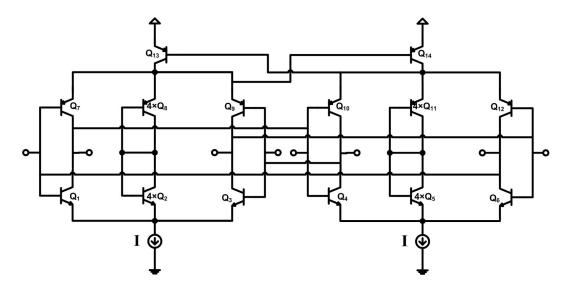

| 55 | Schematic of the differential tunable inductor (gyrator)                                                                                                     | 70 |

| 56 | Schematic of the gyrator with common-mode feedback                                                                                                           | 70 |

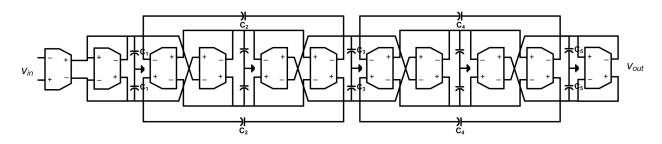

| 57 | Block diagram of the fifth-order low-pass filter.                                                                                                            | 71 |

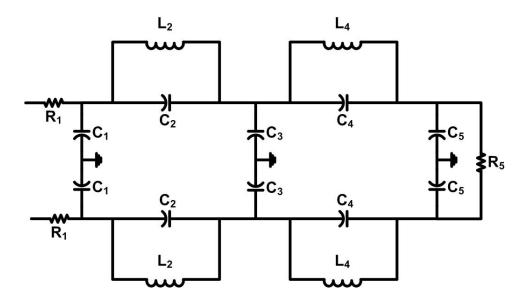

| 58 | Equivalent <i>RLC</i> circuit of the fifth-order low-pass filter                                                                                             | 71 |

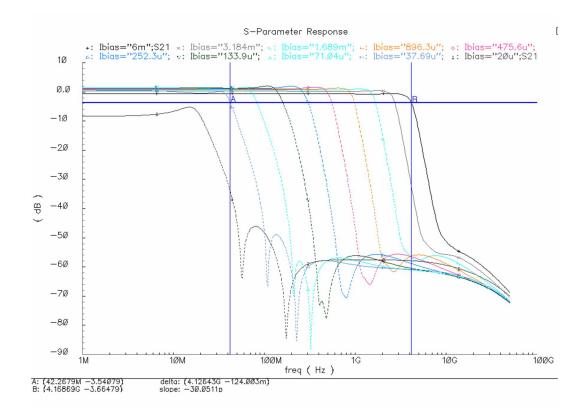

| 59 | Simulated $S_{21}$ of the C-SiGe $g_m$ -C filter over its tuning range                                                                                       | 72 |

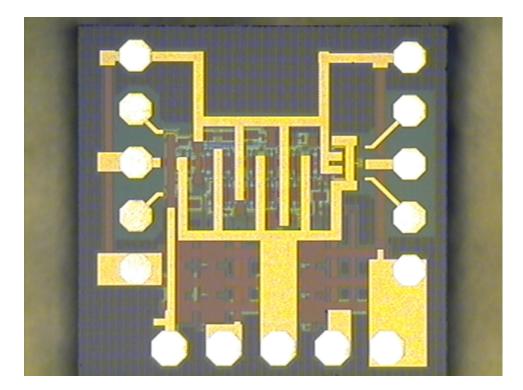

| 60 | Die micrograph of the C-SiGe $g_m$ -C filter                                                                                                                 | 73 |

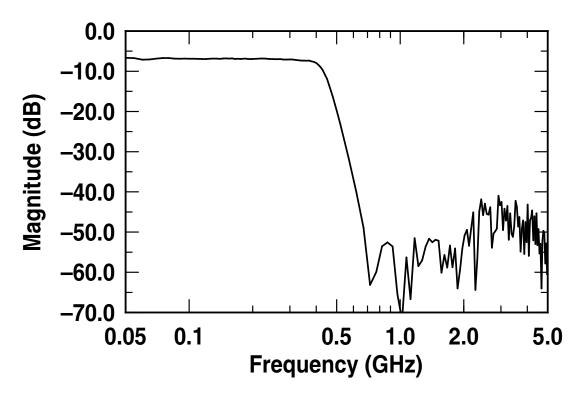

| 61 | Measured $S_{21}$ of the C-SiGe $g_m$ -C filter                                                                                                              | 74 |

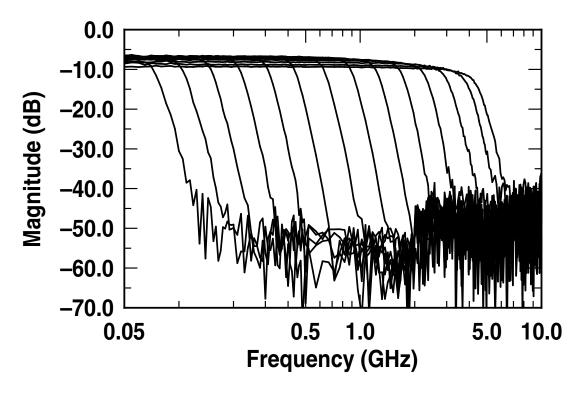

| 62 | Measured $S_{21}$ of the C-SiGe $g_m$ -C filter over its tuning range                                                                                        | 74 |

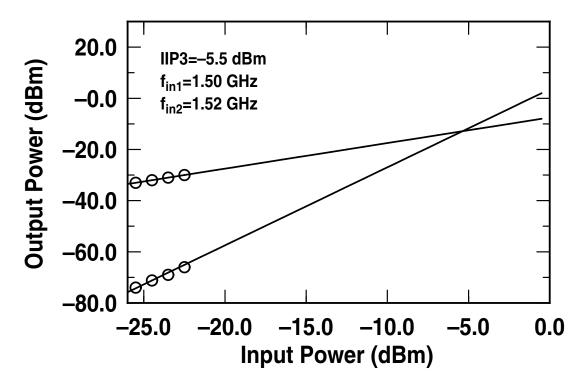

| 63 | Measured IIP3 of the C-SiGe $g_m$ -C filter                                                                                                                  | 75 |

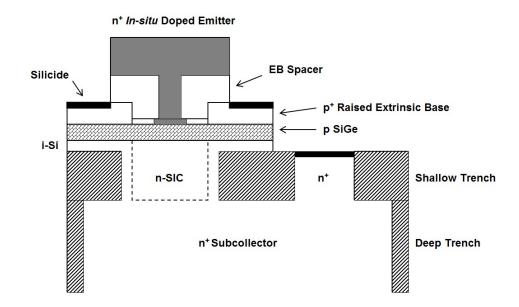

| 64 | Schematic cross-section of the 185 GHz SiGe HBT                                                                                                              | 77 |

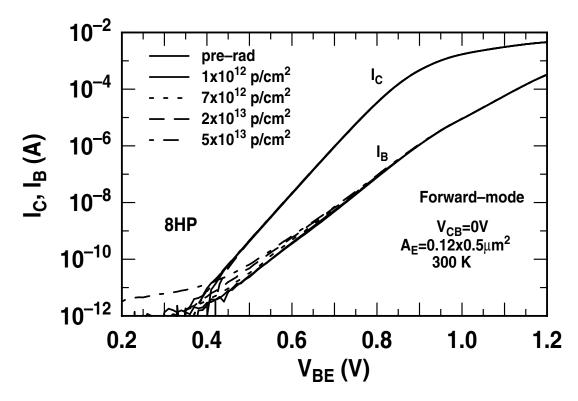

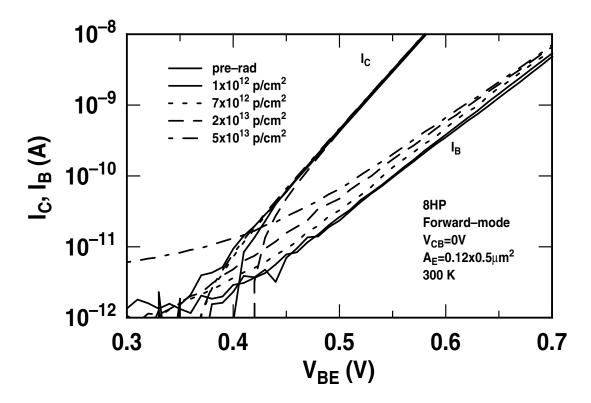

| 65 | Forward-mode Gummel characteristics of the 8HP SiGe HBT                                                                                                      | 79 |

| 66 | Forward-mode Gummel characteristics(Vbe=0.3-0.7V) of the 8HP SiGe HBT                                                                                        | 80 |

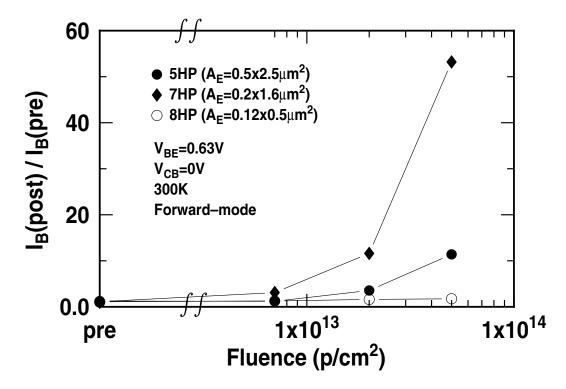

| 67 | Comparison of the normalized base current in <i>forward</i> -mode as a function of proton fluence for the 5HP, 7HP, and 8HP SiGe HBT technology generations. | 81 |

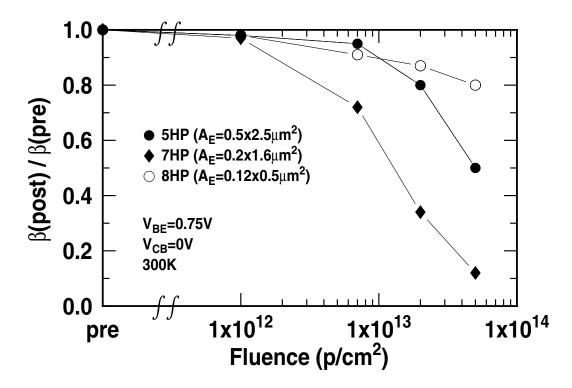

| 68 | Comparison of the normalized current gain as a function of proton fluence for the 5HP, 7HP, and 8HP SiGe HBT technology generations                          | 82 |

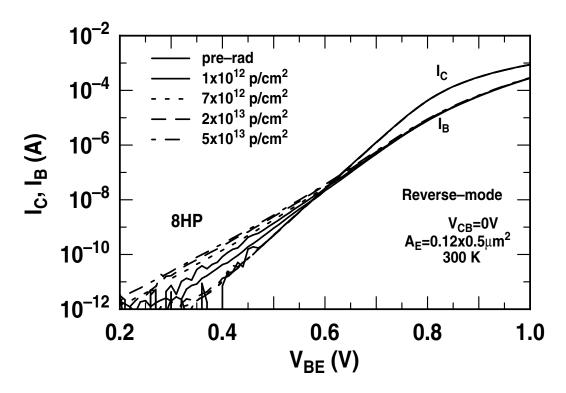

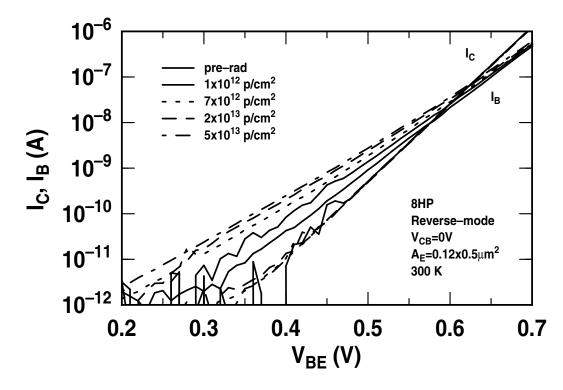

| 69 | Inverse-mode Gummel characteristics of the 8HP SiGe HBT                                                                                                      | 83 |

| 70 | Inverse-mode Gummel characteristics (Vbe=0.3-0.7V) of the 8HP SiGe HBT                                                                                       | 83 |

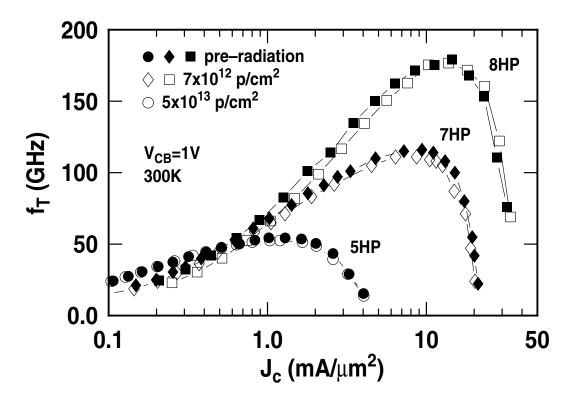

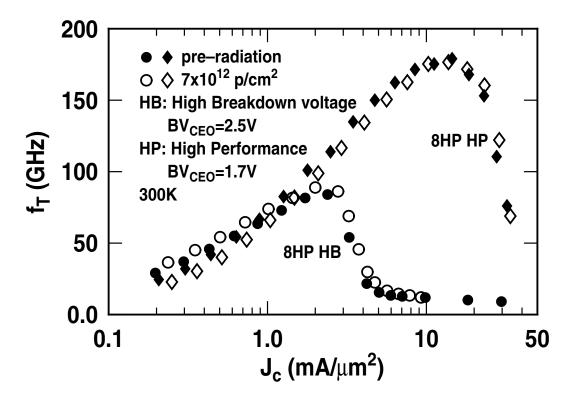

| 71 | Pre-radiation and post-radiation cut-off frequency versus collector current density for 8HP, 7HP, and 5HP SiGe HBTs.                                         | 84 |

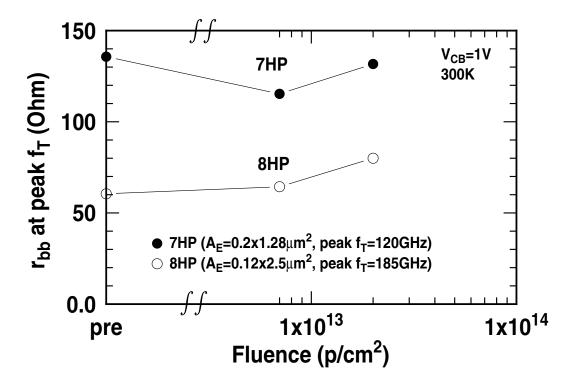

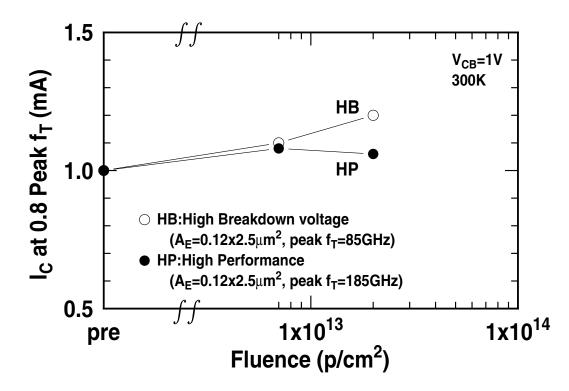

| 72 | Dynamic base resistance dependence on proton fluence                                                                                                         | 85 |

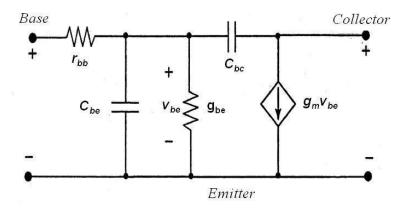

| 73 | Small signal model for SiGe HBTs.                                                                                                                            | 85 |

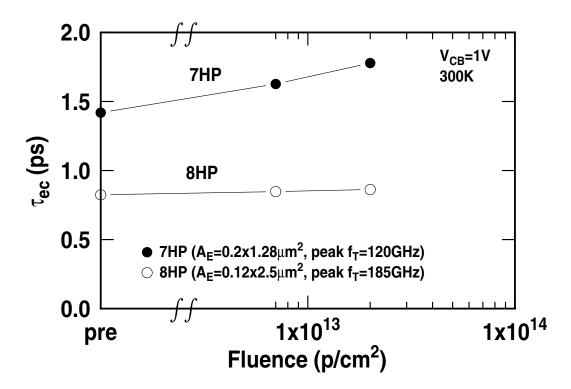

| 74 | Extrapolated transit time dependence on proton fluence                                                                                                       | 86 |

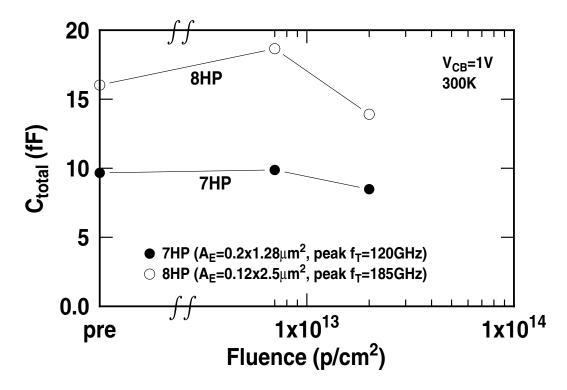

| 75 | Total depletion capacitance dependence on proton fluence                                                                                                     | 86 |

| 76 | Pre- and post-radiation cut-off frequency versus collector current density for both high breakdown and low breakdown 8HP SiGe HBTs | 87 |

|----|------------------------------------------------------------------------------------------------------------------------------------|----|

| 77 | Normalized collector current roll-off point for both high breakdown and low breakdown 8HP SiGe HBTs                                | 88 |

#### SUMMARY

The objective of this work was to design high-speed circuits using silicon-germanium (SiGe) heterojunction bipolar transistors (HBTs) and complementary SiGe (C-SiGe) HBTs, as well as silicon (Si) complementary metal oxide semiconductor (CMOS) devices, for next-generation ultra-wideband (UWB) transceivers. The demand for wideband circuits is driven by many newly introduced military and commercial applications, such as shortrange high data rate communication systems, precision geolocation systems, intrusion detection radar, and software-defined radios. The advantages of using UWB systems over conventional narrowband transceivers include their lower power requirements, higher data rate, more efficient spectrum usage, precise positioning capability, lower complexity, and lower cost. The various components in a UWB system design include UWB communication channel and architecture design, UWB antenna design, and UWB transceiver integrated circuit (IC) implementation. The two major components in a UWB transceiver IC are the radio frequency (RF) circuit and the analog-to-digital converter (ADC). In this proposal, circuit-level solutions to improve the speed and performance of critical building blocks in both the RF front-end and the ADC are presented. Device-related issues affecting SiGe HBTs for potential applications in UWB systems intended for use in extreme environments will also be investigated.

Details of this dissertation can be found in the following refereed publications:

- The design of 3-10 GHz UWB low noise amplifiers (LNAs) in both 120 GHz and 200 GHz SiGe HBT technologies (Chapter II, also published as [59]).

- The design of an 8-bit 12 GSample/sec SiGe BiCMOS track-and-hold amplifier (THA) in 200 GHz SiGe HBT technology (Chapter III, also published as [72]).

- The design of a 70 MHz 4.1 GHz fifth-order elliptic g<sub>m</sub>-C low-pass filter in C-SiGe HBT technology (Chapter IV, also published as [79]).

An investigation of proton radiation effects in third-generation SiGe HBTs (Chapter V, also published as [84]).

## **CHAPTER I**

#### INTRODUCTION

## 1.1 Applications of UWB Transceivers

UWB communications systems are generally characterized in terms of their impulse response in the time domain, in contrast to the frequency domain analysis used in the characterization of their narrowband counterparts [1]. The concept of UWB was pioneered by Ross in 1963 [2]. Since then, UWB has inspired decades of innovations in theory and implementation, and numerous military and commercial applications have emerged that demonstrate the feasibly and viability of UWB technology.

Among all the applications of UWB technologies, the newly introduced commercial UWB communication technology is currently drawing the greatest attention as it exhibits the greatest potential for implementation in next generation wireless communication systems. In 2002, the Federal Communication Commission (FCC) approved UWB for use in commercial communication and imaging systems [3]. UWB systems are now permitted to operate in the 3.1–10.6 GHz range with a minimum signal bandwidth of 500 MHz and maximum power spectral density of -41.3 dBm/MHz [3]. Even though the UWB standard (IEEE 802.15.3a) for wireless personal area network (WPAN) communications has not yet been finalized [4], [5], it is envisioned that these systems will be capable of transmitting extremely high data rates (up to 500 Mb/s) at much lower digital power (less than 1 mW) [6] than the Wi-Fi technology (IEEE 802.11b) currently used for wireless local-area networks (WLAN), which typically delivers a 11 Mb/s data rate with a transmitted power of 200 mW. As a result, not only will UWB technology greatly improve the performance of wireless computer networks, but it will also revolutionize home multimedia by connecting virtually all home electronics such as the computer, camcoder, digital camera, and

high-definition TV with wireless UWB devices [6], [7]. In other words, UWB devices are expected to replace every data cable with a high-speed wireless connection [6].

| Technology   | Data Rate | Output Power | Range | Frequency    |

|--------------|-----------|--------------|-------|--------------|

|              | (Mb/s)    | (mW)         | (m)   |              |

| IrDA         | 4         | 100 mW/sr    | 1-2   | Infrared     |

| Bluetooth    | 1-2       | 100          | 100   | 2.4 GHz      |

| IEEE 802.11a | 54        | 40-800       | 20    | 5 GHz        |

| IEEE 802.11b | 11        | 200          | 100   | 2.4 GHz      |

| IEEE 802.11g | 54        | 65           | 50    | 2.4 GHz      |

| UWB          | 100-500   | 1            | 10    | 3.1-10.6 GHz |

**Table 1:** Key Specifications of Wireless Technologies (after[6]).

An interesting imaging applications of UWB technology is portable intrusion detection radar, or wall-penetrating radar. With this radar, military targets inside a building can be detected and precisely located through walls [8]. Even though some conventional radars, for example the L-band synthetic aperture radar (SAR), can "see through" the wall, several disadvantages, including its large size, heavy weight, high cost, low resolution, high power consumption, and high RF power (unsafe), make it impossible to deploy them widely as portable intrusion-detection radars [8]. However, with the development of UWB technology and the improvement in the performance of digital signal processing (DSP) circuits, low-power and high-resolution portable radars have become possible [8]. Several prototypes of the intrusion-detection radar have been developed in industrial research labs for defence and security applications based on this technology [9], [10].

Another application of UWB technology is in automobile collision-avoidance radar. In 2002, the FCC also approved a second 7 GHz UWB band, 22-29 GHz, for vehicular radar systems [3]. The wide bandwidth of the UWB vehicular radar makes it possible to precisely measure the movement of objects, and thus avoid collisions by triggering safety devices [11]. Even though 77/79 GHz frequencies are considered by the Conference of European Posts and Telegraphs (CEPT) to be a better band for automotive radars, the technology

required to develop a radar working at such high frequencies is still neither mature nor cost effective [11], [12]. consequently, 22-29 GHz radars (24 GHz narrowband radars and 24 GHz UWB radars) are expected to become the preferred solution for low-cost automobile radar in the the next few years [11].

Other applications of UWB technology include radio frequency identification (RFID), precision geolocation systems, surveillance systems, and military short-pulse communication systems [13].

**Table 2:** Military and Commercial Applications of UWB Technology (after [13]).

| Military/Government                        | Commercial                          |

|--------------------------------------------|-------------------------------------|

|                                            |                                     |

| Tactical Handheld and Network LPI/D Radios | High-Speed LAN/WANs                 |

| Non-LOS LPI/D Groundwave Communications    | Industrial RF Monitoring Systems    |

| LPI/D Altimeter/Obstacle Avoidance Radar   | <b>Collision Avoidance Sensors</b>  |

| Tags (RFID)                                | Tags (RFID)                         |

| Intrusion Detection Radars                 | Intrusion Detection Radars          |

| Precision Geolocation Systems              | Precision Geolocation Systems       |

| Unmanned Aerial Vehicles (UAV)             | Altimeter/Obstacle Avoidance Radars |

| Unmanned Ground Vehicles (UGV) Datalinks   | Medical Imaging Systems             |

| LPI/D Wireless Intercom Systems            |                                     |

#### 1.2 Motivations For Developing UWB Transceivers

A typical a narrowband transceiver, in this case a super-heterodyne transceiver for 802.11b (Wi-Fi), is shown in Fig. 1 [14]. The super-heterodyne architecture, which was invented by E.H. Armstrong in 1918, is one of the oldest transceiver architectures, and is still the most widely used architecture in wireless communication systems. The benefits of super-heterodyne transceivers include their easy implementation and reliable operation. A quick glance at Fig. 1 shows that the system is fairly complicated, however, consisting of many RF components and involving several frequency up- and down-conversions. As a result, large power consumption, large chip area, and high cost are involved. In addition,

it takes a long time to design and debug a complicated system such as this, and once it is designed for a particular frequency and standard, the system cannot be reconfigured for operation at another frequency. Another important issue is that for some narrowband communication systems, such as super-heterodyne transceivers, off-chip high-Q channelselection or image-rejection filters are required [15]. These filters, for example surface acoustic wave (SAW) filters, are kept off-chip in order to meet the high-Q and high linearity requirements. Off-chip components make the super-heterodyne architecture less favorable in terms of cost reduction and system-on-a-chip integration.

Figure 1: Block diagram of a super-heterodyne transceiver for IEEE 802.11b (after [14]).

According to Shannon's channel capacity theorem [16], channel capacity C is given by

$$C = B\log_2(1 + \frac{S}{N}) \tag{1}$$

where B is the bandwidth, S is the total signal power, and N is the total noise power. It is clear that the channel capacity (data rate) increases linearly with the bandwidth and logarithmically (and hence weakly) with the signal-to-noise ratio (SNR). Thus, the large bandwidth of a UWB system not only helps achieve high data rates, but also allows operation at a significantly lower signal power than narrowband systems, with only a minor effect on channel capacity [17]. Figure 2 shows an ideal UWB transceiver architecture used in an impulse-radio transceiver [18]. Many components, including frequency synthesizers, down-conversion mixers, up-conversion mixers, image-rejection filters, and channel-selection filters, that are used in narrowband transceivers can be eliminated from a UWB transceiver [18]. Signal processing tasks such as modulation, demodulation, channel selection, and filtering that were previously performed by the RF and analog circuits in narrowband transceivers can now be executed in the digital domain by the baseband digital signal processing (DSP) circuits [18]. Many advantages can be achieved by using fewer RF circuits, including reduction in the hardware, power, cost, and number of design cycles, as well as high integration and more flexibility [18]. Also, the low RF signal power of the UWB system further reduces the transceiver's power consumption [1]. The ability of a UWB communication system using modulated short pulses to operate without a carrier signal allows a very efficient use of the signal spectrum [1], [6]. The PSD of UWB systems is so low (lower than -41.3 dBm/MHz) that it does not cause any interference with existing narrowband communication systems in the same frequency band. For instance, a 802.11.a (5 GHz) system would not be affected at all by UWB signals [19]. The large bandwidth of UWB technology can also be exploited by designing UWB radar systems to achieve higher resolution (as resolution is inversely proportional to the signal bandwidth) than that possible using narrowband radar operating in the same frequency band [11].

The direct implementation of the impulse-radio architecture shown in Fig. 2 for the entire 3.1–10.6 GHz band is very difficult, mainly because of the unavailability of ultrahigh-speed ADCs. To relax the requirement on ADC operating speed, a less aggressive version of the UWB system, namely a direct conversion UWB system utilizing orthogonal frequency-division multiplexing (OFDM), has been proposed [20], [21]. The OFDM

Figure 2: Block diagram of the impulse-radio transceiver (after [18]).

architecture evenly divides the entire UWB band into many sub-bands, each of which has a bandwidth of 528 MHz. An example of a direct conversion UWB transceivers is shown in Fig. 3 [21], which includes a frequency down-conversion stage for digitizing the lowfrequency sub-band signals. However, in contrast to the original architecture shown in Fig. 2, this approach requires the addition of several mixers and frequency synthesizers, inevitably increasing the system complexity and power consumption.

### 1.3 Design Challenges of UWB transceivers

From a signal and system perspective, UWB systems, especially the 3.1-10.6 GHz systems, are a relatively new technology, and standards for these systems have not yet been finalized, and the communication channels fully understood. Interference from the high-power signals generated by narrowband communication systems in the UWB band may cause UWB radio equipment to function improperly [19]. In addition, the design of efficient, wideband matched antennas for UWB systems is challenging, and a wideband antenna needs a constant group delay in order to operate reliably [19].

The two major components in UWB transceivers that pose significant challenges for the integrated circuit (IC) designers are the RF front-end block and analog-to-digital converter (ADC). In the RF front-end block, LNA is one of the more critical circuits, as it forms the first stage of the receiver. It has to not only provide wideband impedance matching to the antenna or external filters, but also achieve low noise, high and constant gain, and high

**Figure 3:** Block diagram of a direct conversion transceiver for OFDM UWB systems (after [21]).

linearity over the entire UWB frequency range [22]-[24]. Conventional narrowband LNAs are composed of a cascode amplifier with inductive degeneration and base inductance and are not adequate to simultaneously achieve all the requirements for a UWB receiver. Other LNA topologies, such as the distributed amplifier and common base amplifier, suffer from high noise figures. Feedback, on the other hand, is a powerful technique that can be used to improve both impedance matching and linearity. However, it also decreases the gain, increases the noise figure, and could lead to stability issues.

Achieving high linearity in UWB LNAs is of paramount importance. As discussed earlier, strong interference from existing narrowband communication systems, whose signal power density could be 1000 times higher than that of the UWB signals, may cause serious problems if the LNA linearity is too low given that only limited filtering can be achieved in a practical system [19]. The power consumption of UWB LNAs tends to be higher than that of narrowband LNAs in the same band because of their more stringent requirements, such as higher gain, wider bandwidth, low noise, and higher linearity, and thus does not favor low-power operation [19].

In RF receivers, in order to relax the dynamic range requirement of the baseband ADCs, analog signals are generally amplified by variable gain amplifiers (VGAs) before being fed to the ADCs. However, because of the extremely large bandwidth of UWB signals, the design of the VGA becomes challenging at high frequencies [24]. In addition, OFDM systems need a 14-band (3.1–10.6 GHz) frequency synthesizer, which can switch rapidly between frequency bands, with less than 9.5 ns switching time available. The conventional closed loop approach using a single phase lock loop (PLL) is not able to meet these stringent settling time and tuning range requirements [24]-[26].

The overall performance of the UWB system (Fig. 2) depends heavily on the performance of the ADC, which needs sufficient sampling rate, bandwidth, and resolution. For instance, according to Nyquist-Shannon sampling theorem, to be able to directly sample the 3–10 GHz UWB signals, the sampling rate must be at least twice the highest signal frequency, or 20 Gsample/s, in order to avoid aliasing [27], and the bandwidth of the ADC must be greater than 10 GHz. Only a few high-speed ADCs can work well at full Nyquist speed, i.e., with a sampling rate two times that of the input frequency, but in practice, an ADC's sampling rate should be at least four times the highest signal frequency for reliable digitization. Therefore, to directly digitize the entire 3-10 GHz UWB band, a 40 Gsample/s ADC with at least 10 GHz bandwidth is required. Unfortunately, the difficulties associated with designing such a high-speed ADC, even for low resolution, are so formidable that a direct implementation of Fig. 2 for the entire 3-10 GHz band (not to mention for 22-29 GHz band) is widely considered impossible in CMOS and not power efficient in other technologies [31]. Some of the world's fastest ADCs reported in [28]-[30] operate at the limits of the technologies they are realized in and all have very high power consumptions of several watts. For the less aggressive version of UWB systems, namely the direct conversion

architecture, the sampling rate of the ADC must still be faster than 528 Msample/s in order to sample a 528 MHz sub-band, which remains a serious challenge for low-power UWB systems.

The receiver path in Fig. 2 is also often referred to as software-defined-radio (SDR), a concept for a far more powerful radio system that can theoretically receive and demodulate any signal falling within the receiver bandwidth, irrespective of whether it is a narrowband or wideband signal. SDR has even more stringent requirements for the ADC. Besides a high speed, the ADC now also needs a higher dynamic range or higher resolution than that needed in a standard UWB system in order to capture some weak narrowband RF signals in the presence of undesired strong in-band signals [31]. Thus, it is clear that the ADC plays an extremely important role in UWB system design. In fact, not only will the UWB system benefit from an improved ADC, but a faster ADC will also be useful in conventional narrowband systems, thus permitting the ADC to be pushed closer to the antenna, and reducing power and hardware requirements. Many high-end measurement instruments, for example ultra-wideband digital oscilloscopes, also require high-sampling rate, high-resolution ADCs.

## 1.4 SiGe HBT / BiCMOS Technology

Bandgap-engineered SiGe HBTs are of increasing interest for wireless communication IC applications [32] because of their remarkable transistor-level performance combined with their ability to simultaneously maintain strict compatibility with conventional low-cost, high-integration, and high-volume Si CMOS manufacturing [33]. SiGe HBT technologies with 50 GHz (first-generation) [34] and 120 GHz (second-generation) [35] peak cutoff frequency are currently in commercial production worldwide from multiple sources, and are being deployed in both the commercial and defense sectors.

The recent announcement of a third-generation SiGe HBT technology with 200 GHz peak cutoff frequency [36]-[37], and a fourth-generation SiGe HBT technology with over

300 GHz peak cutoff frequency [38]-[39], along with the complementary (*npn* and *pnp*) SiGe HBTs with peak  $f_T$  values above 180 GHz and 80 GHz, respectively [40], has pushed the upper bound on the speeds achievable in these devices considerably higher than previously believed possible, thus vastly increasing the application options for SiGe HBT technology to encompass a wide variety of analog and RF through millimeter-wave systems [41].

While it might be argued that a peak cutoff frequency in excess of 200 GHz is not needed to support most IC applications, which are currently clustered in the 1-40 GHz range, such extreme levels of performance create a much broader circuit design space, where, for instance, a designer has the option to trade frequency response for dramatic reductions in power consumption (10x reduction in bias current in the third-generation devices over second-generation technology for similar operating speeds), as indicated in Fig. 4. Third-generation SiGe HBTs are in fact quite competitive now with the best-of-breed commercial InP HBTs, and out-perform these devices when thermal effects are also considered [33].

| SiGe Technology        | 7HP [35] | 8HP [36] | sg25c [37] | sg25h2 [40] |

|------------------------|----------|----------|------------|-------------|

| Company                | IBM      | IBM      | IHP        | IHP         |

| HBT                    | npn      | npn      | npn        | npn/pnp     |

| $f_T$ (GHz)            | 120      | 200      | 190        | 170/90      |

| $f_{max}$ (GHz)        | 100      | 280      | 190        | 170/120     |

| $BV_{CEO}$ (V)         | 1.8      | 1.7      | 1.7        | 1.9/3.1     |

| $W_{E,eff}$ ( $\mu$ m) | 0.18     | 0.13     | 0.25       | 0.25/0.25   |

| CMOS $L_g$ ( $\mu$ m)  | 0.14     | 0.092    | 0.25       | 0.25        |

| CMOS Supply (V)        | 1.8      | 1.3      | 2.5        | 2.5         |

**Table 3:** Key Specifications of SiGe BiCMOS Technologies Used in this Research.

### 1.5 Organization of Dissertation

Chapter II (also published in [59]) presents the design and implementation of SiGe LNAs for use in UWB systems. The use of a shunt base-emitter capacitor and weak shunt

Figure 4: Measured  $f_T$  as a function of bias current for three SiGe technology generations.

resistive feedback in a cascode amplifier with inductive degeneration significantly improves the input bandwidth of the LNA, and simultaneously allows a very low noise figure to be achieved. LNA 1 and 2 were fabricated using a commercially-available 0.18  $\mu$ m 120 GHz SiGe HBT BiCMOS process technology. LNA 1 occupies an area of 0.80 × 0.90 mm<sup>2</sup>, exhibits a noise figure (NF) of 1.8–3.1 dB, and attains a maximum gain of 20.3 dB across 3.0–10.0 GHz. LNA 2 occupies an area of 0.94 × 0.96 mm<sup>2</sup>, exhibits an NF of 1.61–2.38 dB, and attains a maximum gain of 20.6 dB across 3.0–10.0 GHz. Both LNAs operate off a 3.3 V supply with a total power consumption of 26 mW. LNA 3 was fabricated in a 0.13  $\mu$ m 200 GHz SiGe HBT BiCMOS process technology. It occupies an area of 0.86 × 0.95 mm<sup>2</sup>, exhibits an NF of 1.17–1.75 dB (simulated), and attains a maximum gain of 23.3 dB across 3.0–10.0 GHz. LNA 3 operates off a 3.3 V supply with a total power consumption of 32 mW. Chapter III (also published in [72]) presents the design and implementation of an ultrahigh-speed SiGe BiCMOS track-and-hold amplifier (THA) for use in high-speed analogto-digital converters. The use of a degeneration inductor in the input buffer was found to significantly improve the performance of the THA. The THA was fabricated using a commercially-available 0.25  $\mu$ m 200 GHz SiGe HBT BiCMOS process technology. The circuit occupies an area of 1.0×1.2 mm<sup>2</sup>, and exhibits -49.5 dBc of total harmonic distortion (THD) when operated at a sampling frequency of 12.5 GHz with an input frequency of 3.0 GHz. Operating from a 3.5 V supply, the total power consumption is 0.7 W.

Chapter IV (also published in [79]) presents the first demonstration of a continuoustime, fifth-order, elliptic,  $g_m$ -C low-pass active filter in 0.25  $\mu$ m complementary (npn + pnp) silicon-germanium (C-SiGe) HBT technology. This C-SiGe technology features npnSiGe HBTs with peak  $f_T$  and  $f_{max}$  of 170 GHz and 170 GHz, respectively, as well as pnpSiGe HBTs having  $f_T$  and  $f_{max}$  of 90 GHz and 120 GHz, respectively. This C-SiGe active filter was implemented with Voorman transconductors [73] to fully exploit the complementary high-speed npn and pnp SiGe HBTs. The circuit occupies an area of 0.90 × 0.91 mm<sup>2</sup>, and exhibits a filter cut-off frequency of 4.1 GHz. This C-SiGe  $g_m$ -C filter achieves a record continuous tuning range between 70 MHz and 4.1 GHz, attains an output noise power spectrum density (PSD) of -143 dBm/Hz, and operates off a 3.5 V supply, with a total power consumption of 100 mW at the maximum bandwidth of 4.1 GHz.

Chapter V (also published in [84]) presents results for the impact of proton irradiation on the *dc* and *ac* characteristics of third-generation, 0.12  $\mu$ m 185 GHz SiGe HBTs. Comparisons with prior technology generations are used to assess how the structural changes needed to enhance performance between second- and third-generation technology affect the observed proton response. The results demonstrate that SiGe HBT technologies can successfully maintain their Mrad-level total dose hardness without intentional hardening, even when vertically-scaled in order to achieve unprecedented levels of transistor performance.

Chapter VI concludes the dissertation with a discussion of possible future research

directions.

## **CHAPTER II**

## **UWB LOW NOISE AMPLIFIER**

#### 2.1 Introduction

The low-noise amplifier (LNA) is a critical building block in UWB radios and is one of the most difficult components to realize because it must simultaneously achieve both broad impedance matching and low noise performance.

Distributed amplifiers can achieve the widest bandwidth, but their noise figures (NF) are typically very high [42]-[44]. The same problem exists in common-base input LNAs [45] and conventional shunt resistive feedback LNAs [46], [47]. Cascode LNAs with inductive degeneration, on the other hand, achieve the lowest noise figure compared to other architectures. However, they can only be matched to 50  $\Omega$  over a narrowband [50]-[52]. In previous research, an on-chip LC-ladder filter has been employed at the input of the LNA to broaden the bandwidth [22], [23]. However, this technique has several disadvantages, including enlarged chip size, increased circuit complexity, and enhanced noise figure, mainly due to the extra noise contributed by the lossy inductors present in the LC-filter network. Another way to broaden the bandwidth of a reactively matched LNA is to use weak resistive feedback between the input and the output [53]. In this case, however, matching the input to 50  $\Omega$  over the entire 3-10 GHz bandwidth is still a serious challenge.

The UWB LNA designs reported in the present work are implemented in IBM's secondgeneration (7HP) and third-generation (8HP) SiGe HBT BiCMOS technologies. 7HP is a commercially available SiGe technology platform featuring 180 nm lithography, 120/100 GHz ( $f_T / f_{max}$ ), and 1.8 V  $BV_{CEO}$ , and is integrated with aggressively scaled 0.11  $\mu$ m  $L_{eff}$ , 1.8 V Si CMOS. This SiGe technology features shallow- and deep-trench isolation, along with a thermodynamically stable, 25% peak Ge content, graded UHV/CVD epitaxial SiGe base [35]. Figure 5 shows the cross-section of the 7HP SiGe HBT.

8HP features 130 nm lithography, 200/280 GHz ( $f_T / f_{max}$ ), and 1.7 V  $BV_{CEO}$ , and is provided with 0.09  $\mu$ m  $L_{eff}$ , 1.3 V Si CMOS. 8HP technology employs a novel, reduced thermal cycle, "raised extrinsic base" structure, and utilizes conventional deep and shallow trench isolation, an *in-situ* doped polysilicon emitter, and an unconditionally stable, 25% peak Ge, C-doped, graded UHV/CVD epitaxial SiGe base [36].

Both technologies come with a full suite of passive elements and seven levels of metallization.

In this chapter, the design and demonstration of LNAs for use in UWB systems is presented. Section 2.2 and Section 2.3 review noise theory and BJT noise model, respectively. Section 2.4, and Section 2.5 review the narrow band LNA and the resistive feedback LNA, respectively. Details of LNA 1 are described in Section 2.6. Measurement results of LNA1 are presented in Section 2.7. Details of LNA 2 and LNA 3 are described in Section 2.8. Measurement results of LNA 2 and LNA 3 are presented in Section 2.9 and Section 2.10, respectively. This work is also published as [59].

Figure 5: Schematic cross-section of the 7HP SiGe HBT.

## 2.2 Noise Factor of a Linear Two-Port Network

A noisy amplifier can be modeled as a noiseless amplifier with a noise voltage source  $(v_n)$  and a noise current source  $(i_n)$  at the input [48], as shown in Fig. 6. The noise factor is given as [48]

Figure 6: Two-port network with input-referred noise voltage source and current source.

$$F = 1 + \frac{(i_n + v_n Y_s)(i_n^* + v_n^* Y_s^*)}{i_{ns}^2}$$

(2)

$$= 1 + \frac{i_n^2 + 2\Re(i_n v_n^* Y_s^*) + v_n^2 Y_s^2}{i_{ns}^2},$$

(3)

where  $Y_s$  is the source admittance made out of a real part of  $G_s$  and an imaginary part of  $B_s$ [48]

$$Y_s = G_s + jB_s, \tag{4}$$

$i_{ns}^2$  is the mean-square value of the source noise current and is given by [48]

$$i_{ns}^2 = 4kTG_s,\tag{5}$$

where k is the Boltzmann constant and T the absolute temperature. The correlation admittance  $Y_c$  is defined as [48]

$$Y_{c} = \frac{v_{n}i_{n}^{*}}{v_{n}^{2}} = G_{c} + jB_{c}.$$

(6)

The noise resistance  $R_n$  and conductance  $G_n$  can be defined as [48]

$$R_n = \frac{v_n^2}{4kT},\tag{7}$$

$$G_n = \frac{i_n^2}{4kT}.$$

(8)

The noise factor can be written as [48]

$$F = 1 + \frac{i_n^2 + 2v_n^2 \Re(Y_c Y_s^*) + v_n^2 Y_s^2}{i_{ns}^2}$$

(9)

$$= 1 + \frac{G_n + 2R_n \Re(Y_c Y_s^*) + R_n Y_s^2}{G_s}.$$

(10)

The minimum noise factor is achieved when the following conditions are satisfied [48]:

$$\frac{\partial F}{\partial G_s} = 0, \tag{11}$$

$$\frac{\partial F}{\partial B_s} = 0, \tag{12}$$

solving for optimum source admittance  $Y_{s,opt}$  and impedance  $Z_{s,opt}$  [48]

$$B_{s,opt} = -B_c, \tag{13}$$

$$G_{s,opt} = \sqrt{\frac{G_n}{R_n} - B_c^2},\tag{14}$$

$$Y_{s,opt} = G_{s,opt} + jB_{s,opt}, \tag{15}$$

$$Z_{s,opt} = R_{s,opt} + jX_{s,opt} = 1/Y_{s,opt},$$

(16)

$$R_{s,opt} = \frac{G_{s,opt}}{G_{s,opt}^2 + B_{s,opt}^2},\tag{17}$$

$$X_{s,opt} = -\frac{B_{s,opt}}{G_{s,opt}^2 + B_{s,opt}^2}.$$

(18)

Thus, the minimum noise factor is [48]

$$F_{min} = 1 + 2R_n(G_c + G_{s,opt}).$$

(19)

The noise factor can be re-written as [48]

$$F = F_{mim} + \frac{R_n}{G_s} [(G_s - G_{s,opt})^2 + (B_s - B_{s,opt})^2].$$

(20)

## 2.3 BJT Noise Model

The noise model for the bipolar transistor is shown in Fig. 7 [33]. The mean-square values of input-referred noise voltage and current of the bipolar transistor are [33]

Figure 7: Noise model of the bipolar transistor.

$$v_n^2 = \frac{2qI_C}{g_m^2} + 4kTr_b,$$

(21)

$$i_n^2 = 2qI_B + \frac{2qI_C Y_{in}^2}{g_m^2},$$

(22)

where  $2qI_B$  and  $2qI_C$  are the base and collector shot noise, respectively;  $4kTr_b$  is the thermal noise because of the base resistance;  $Y_{in}$ , the input admittance of the transistor, is given as [33]

$$Y_{in} = \frac{1}{r_{\pi}} + j\omega C_{\pi}.$$

(23)

Thus,  $R_n$ ,  $G_n$ ,  $Y_c$ ,  $G_c$  and  $B_c$  can be calculated as [33]

$$R_n = \frac{v_n^2}{4kT} \tag{24}$$

$$=\frac{\frac{2q_{L}c}{g_{m}^{2}}+4kTr_{b}}{4kT}$$

(25)

$$= \frac{1}{2g_m} + r_b, \tag{26}$$

$$G_n = \frac{i_n^2}{4kT} \tag{27}$$

$$= \frac{2qI_B + \frac{2qI_C Y_{ln}^2}{g_m^2}}{4kT}$$

(28)

$$= \frac{g_m}{2} \left(\frac{1}{\beta} + \frac{1}{\beta^2} + \frac{\omega^2 C_{\pi}^2}{g_m^2}\right), \tag{29}$$

$$Y_c = \frac{v_n i_n^*}{v_n^2} \tag{30}$$

$$= \frac{\frac{2qI_{C}}{g_{m}^{2}}(\frac{1}{r_{\pi}} + j\omega C_{\pi})}{\frac{2qI_{C}}{g_{m}^{2}} + 4kTr_{b}}$$

(31)

$$= \frac{\frac{1}{\beta} + j\frac{\omega C_{\pi}}{g_m}}{\frac{1}{g_m^2} + 2r_b},$$

(32)

$$G_c = \frac{1}{\beta} \frac{1}{\frac{1}{g_m} + 2r_b},$$

(33)

$$B_c = \frac{\frac{\omega C_\pi}{g_m}}{\frac{1}{g_m} + 2r_b}.$$

(34)

$G_{s,opt}, B_{s,opt}, R_{s,opt}, X_{s,opt}$ , and  $F_{min}$  can also be calculated [33]

$$G_{s,opt} = \sqrt{\frac{G_n}{R_n} - B_c^2}$$

(35)

$$= \sqrt{\frac{\frac{g_m}{2}(\frac{1}{\beta} + \frac{1}{\beta^2} + \frac{\omega^2 C_{\pi}^2}{g_m^2})}{\frac{1}{2g_m} + r_b}} - (\frac{\frac{\omega C_{\pi}}{g_m}}{(\frac{1}{g_m} + 2r_b)^2})^2,$$

(36)

$$B_{s,opt} = -B_c = -\frac{\frac{\omega C_\pi}{g_m}}{\frac{1}{g_m} + 2r_b},$$

(37)

$$R_{s,opt} = \frac{G_{s,opt}}{G_{s,opt}^2 + B_{s,opt}^2}$$

(38)

$$=\frac{\sqrt{\frac{\frac{g_m}{2}(\frac{1}{\beta}+\frac{1}{\beta^2}+\frac{\omega^2 C_{\pi}^2}{g_m^2})}{\frac{1}{2g_m}+r_b}-(\frac{\omega C_{\pi}}{\frac{g_m}{\frac{1}{g_m}+2r_b}})^2}{\frac{\frac{g_m}{2}(\frac{1}{\beta}+\frac{1}{\beta^2}+\frac{\omega^2 C_{\pi}^2}{g_m^2})}{\frac{1}{2g_m}+r_b}},$$

(39)

$$X_{s,opt} = -\frac{B_{s,opt}}{G_{s,opt}^2 + B_{s,opt}^2}$$

(40)

$$=\frac{\frac{\frac{\frac{\omega c_{m}}{g_{m}}}{\frac{1}{g_{m}}+2r_{b}}}{\frac{\frac{g_{m}}{2}(\frac{1}{\beta}+\frac{1}{\beta^{2}}+\frac{\omega^{2}C_{\pi}^{2}}{g_{m}^{2}})}{\frac{1}{2g_{m}}+r_{b}}},$$

(41)

$$F_{min} = 1 + 2R_n(G_c + G_{s,opt})$$

(42)

$$= 1 + 2\left(\frac{1}{2g_m} + r_b\right)\left[\frac{1}{\beta}\frac{1}{\frac{1}{g_m} + 2r_b} + \sqrt{\frac{\frac{g_m}{2}\left(\frac{1}{\beta} + \frac{1}{\beta^2} + \frac{\omega^2 C_{\pi}^2}{g_m^2}\right)}{\frac{1}{2g_m} + r_b} - \left(\frac{\frac{\omega C_{\pi}}{g_m}}{\frac{1}{g_m} + 2r_b}\right)^2\right].$$

(43)

By scaling the device size and adding reactive components, noise matching can be achieved [33]

$$Z_{s,opt} = R_{s,opt} + jX_{s,opt} = Z_s.$$

$$\tag{44}$$

The design of LNA with simultaneous impedance and noise matching will be discussed in the next section [51].

#### 2.4 Narrow Band LNA

From the previous section, for a given collector current density, the minimum noise factor can be achieved if

$$Z_s = Z_{s,opt}.$$

(45)

In most RF systems,  $Z_s=50 \Omega$ . Thus, in order to achieve noise matching and power matching, both input impedance and optimum noise source impedance should be 50 $\Omega$ . In [51], an elegant solution that achieves simultaneous impedance and noise matching has been given. An optimum current density, which gives the lowest minimum noise figure can first be chosen based on the device minimum noise figure vs. the current density curve [51], which is available from the device model for a given process technology. By changing the emitter length of the device,  $R_{s,opt}$  of 50  $\Omega$  can be realized, thus also determining the device size

Figure 8: Common emitter amplifier with emitter and base inductors.

and bias current [51]. Then a degeneration inductance  $(L_E)$  and a base inductance  $(L_B)$  can be added (Fig. 8) [51].

The impedance looking into the input of LNA is given by [51]

$$Z_{in} = j\omega(L_E + L_B) + \frac{1}{j\omega C_\pi} + \frac{g_m}{C_\pi} L_E, \qquad (46)$$

where  $L_E$  is the emitter degeneration inductance,  $L_B$  is the base series inductance,  $C_{\pi}$  is the base-emitter capacitance of  $Q_1$ , and  $g_m$  is the transconductance. The real part of the input impedance is equal to 50 $\Omega$  [51]

$$\frac{g_m}{C_\pi} L_E = 50\Omega,\tag{47}$$

solving for  $L_E$  [51]

$$L_E = \frac{C_\pi 50\Omega}{g_m}.\tag{48}$$

The value of  $L_B$  is chosen so that the circuit resonances at the center frequency  $\omega$  [51]. The imaginary part of the input impedance is equal to 0 [51]

$$j\omega(L_E + L_B) + \frac{1}{j\omega C_\pi} = 0, \tag{49}$$

solving for  $L_B$  [51]

$$L_B = \frac{1}{\omega^2 C_\pi} - L_E. \tag{50}$$

Simultaneous impedance and noise matching has now been achieved [51]. This technique can be directly appled into cascode topology, as shown in Fig. 9. The cascode LNA has been widely used because of its higher gain, better isolation, and with only slightly higher noise figure compared to a simple common-emitter amplifier. However, this method only

Figure 9: Schematic of the cascode LNA with inductive degeneration.

takes into account the noise and impedance matching. Other important specifications of the LNA, especially its linearity, power consumption and bandwidth also need to be addressed in order to suit different applications. For UWB applications, special techniques need to be adopted to widen the input bandwidth.

# 2.5 Resistive Feedback LNA

Adding a shunt 50  $\Omega$  resistor at the input is the simplest way to achieve wideband impedance matching to 50  $\Omega$ . However, the 3 dB noise figure increasement added by this resistor is unacceptable for LNA in most applications [49]. Shunt-shunt feedback (Fig. 10) is generally preferred as it combines wideband impedance matching with a reasonably low noise figure [49].

Figure 10: Schematic of the LNA with shunt-shunt feedback.

$$a = \frac{v_o}{i_i} = -g_m \frac{R_f R_\pi}{R_f + R_\pi} \frac{R_f R_L}{R_f + R_L},$$

(51)

$$f = \frac{v_o}{i_i} = -\frac{1}{R_f}.$$

(52)

The loop gain (T) is

$$T = af = g_m \frac{R_\pi}{R_f + R_\pi} \frac{R_f R_L}{R_f + R_L},$$

(53)

$$A_{\nu} = \frac{v_o}{v_i} = -g_m \frac{R_f R_{\pi}}{R_f + R_{\pi}}.$$

(54)

The input impedance of the basic amplifier is

$$Z_{ia} = \frac{R_f R_\pi}{R_f + R_\pi},\tag{55}$$

Taking into account feedback, the input impedance becomes [49]

$$Z_{in} = \frac{Z_{ia}}{1+T} = \frac{\frac{R_f R_\pi}{R_f + R_\pi}}{1 + g_m \frac{R_\pi}{R_f + R_\pi} \frac{R_f R_L}{R_f + R_\pi}},$$

(56)

assuming T >> 1

$$Z_{in} = \frac{Z_{ia}}{1+T} \approx \frac{R_f + R_L}{g_m R_L}.$$

(57)

An emitter follower buffer can also be added to to the feedback loop, as shown in Fig. 11 [49]. The input impedance of the amplifier becomes [49]

Figure 11: Schematic of the LNA with shunt-shunt feedback and emitter follower.

#### 2.6 UWB LNA 1

A conventional narrow-band cascode LNA with inductive degeneration is shown in Fig. 9. The expression for its input bandwidth as a function of the quality factor  $(Q_{in})$  of

the input network is [25]

$$BW_{in} = \frac{\omega_0}{Q_{in}},\tag{59}$$

where  $\omega_0$ , the center frequency, is given by

$$\omega_0 = \frac{1}{\sqrt{C_\pi (L_B + L_E)}},\tag{60}$$

and  $Q_{in}$  is given by [25]

$$Q_{in} = \frac{\sqrt{\frac{(L_B + L_E)}{C_{\pi}}}}{\frac{g_m L_E}{C_{\pi}} + R_s} = \frac{1}{C_{\pi} \omega_0 (\frac{g_m L_E}{C_{\pi}} + R_s)},$$

(61)

where  $R_S$  is the source resistance.

Figure 12: Schematic of the broadband LNA with weak resistive feedback.

Typically, in a cascode LNA,  $Q_{in}$  is high and the bandwidth is very narrow [25]. To

broaden the bandwidth, a large resistor  $(R_f)$  is added between the base of the input transistor and the cascode output (Fig. 12).  $Q_{in}$  then becomes [53]

$$Q_{in} \approx \frac{1}{C_{\pi}\omega_0(\frac{g_m L_E}{C_{\pi}} + R_s + \frac{(\omega_0 L_B)^2}{R_f})}.$$

(62)

Observe that this is not a conventional resistive feedback LNA because the resistor does not directly provide the 50  $\Omega$  impedance match. Instead, it uses a much larger resistor that broadens the input bandwidth of the LNA by decreasing the  $Q_{in}$  of the network, while causing only a marginal degradation in the noise performance [53]. However, the bandwidth covering the 3-5 GHz range obtained in [53] is still insufficient to cover the 3-10 GHz range required for UWB applications.

Assuming  $\omega_0$  and  $R_s$  are fixed in the input impedance expression for the original input network (61), the parameters that can be tweaked to obtain the desired wideband response are  $L_E$ ,  $g_m$ , and  $C_\pi$ .  $L_E$  must be very small in order to achieve high gain and low noise and hence offers little room for adjustment. The effective value of  $C_\pi$  (base-emitter capacitance) can, however, be increased by adding a shunt capacitor  $C_m$  between the base and emitter of the input transistor (Fig. 13).

The effective base-emitter capacitance  $(C_{eff})$  is now given by

$$C_{eff} = C_{\pi} + C_m, \tag{63}$$

This increase in effective base-emitter capacitance causes the  $Q_{in}$  of the input network to decrease. In addition, the transconductance  $(g_m)$  needs to be increased so that  $g_m L_E/C_{eff} + r_b$  is still matched to 50  $\Omega$ .  $Q_{in}$  for this modified network is now given by

$$Q_{in} = \frac{1}{C_{eff}\omega_0(\frac{g_m L_E}{C_{eff}} + R_s)},\tag{64}$$

The expression for  $\omega_0$  can be modified as follows to include  $C_{eff}$ .

$$\omega_0 = \frac{1}{\sqrt{C_{eff}(L_B + L_E)}},\tag{65}$$

Contrary to the initial assumption that  $\omega_0$  is fixed, (65) suggests that  $\omega_0$  decreases as  $C_{eff}$

Figure 13: Schematic of the broadband LNA with shunt base-emitter capacitor.

increases. However, the shift in center frequency caused by the increase in  $C_{eff}$  can be offset by decreasing  $L_B$ . This suggests that the  $L_B$  required is much smaller than that used in a traditional narrow-band LNA. For the present design, an  $L_B$  of 300 pH was chosen compared to a 1 nH or larger  $L_B$  required in a conventional narrow-band LNA. In addition, a smaller  $L_B$  can help reduce the noise figure by introducing a smaller series resistance at the input of the LNA.

It is well known that an increased base-emitter capacitance (decreased  $f_T$ ) degrades the gain and noise figure at high frequencies. However, if the value of this extra capacitance is carefully chosen, the degradation in performance over the frequency band of interest can be minimized.

Similar techniques can be found in [55] and [22]. The LNA presented in [55] achieves multi-band matching centered at frequencies of 2.45 GHz and 5.25 GHz, whereas that

**Figure 14:** Schematic of the present SiGe UWB LNA with weak resistive feedback and shunt base-emitter capacitor.

described in [22], relies primarily on an LC filter at the input to achieve an input match. These designs, however, are not adequate to achieve matching over the entire 3-10 GHz UWB range without a filter.

It is clear from the preceding analysis that the bandwidth of the LNA ( $\propto 1/Q_{in}$ ) is very sensitive to the base-emitter capacitance and the feedback resistance. In contrast, the other electrical parameters such as gain, noise, isolation, input impedance, and linearity are not very sensitive to  $C_m$  and  $R_f$ . Thus, a broadband input match can be achieved by using a very small  $C_m$  and a very large  $R_f$  with only a minimal effect on the other parameters.

The LNA realized in the present work incorporates both a shunt base-emitter capacitance and weak resistive feedback in a cascode architecture with inductive degeneration, as shown in Fig. 14. The load inductor  $L_L$  widens the bandwidth at high frequency by causing inductive peaking, which offsets the gain roll-off introduced by a capacitive load. The output buffer is a simple emitter-follower, providing broadband 50  $\Omega$  match at the output.

Figure 15: Die micrograph of the SiGe UWB LNA 1.

### 2.7 Measurement Results of LNA 1

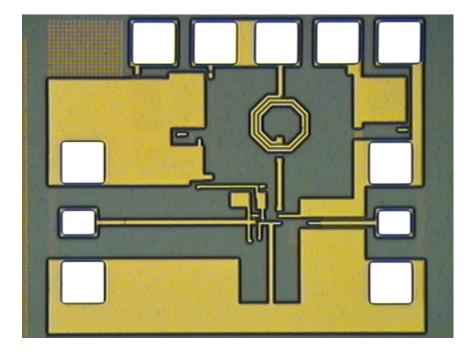

The LNA 1 was implemented in a commercially available 0.18  $\mu$ m 120 GHz SiGe HBT BiCMOS technology [35] and occupies a total area of 0.8×0.9 mm<sup>2</sup>, including the probe pads. The chip micrograph is shown in Fig. 15. The base and emitter inductors ( $L_B$  and  $L_E$ , respectively), both of which are very small, can be best implemented using line inductors, which have higher Q and lower parasitic resistance compared to spiral inductors. The load inductor  $L_L$  is a spiral inductor. The output is connected to the probe pad through a sideshielded 50  $\Omega$  micro-strip transmission line. The LNA was tested on-wafer using 50 GHz probes and cables.

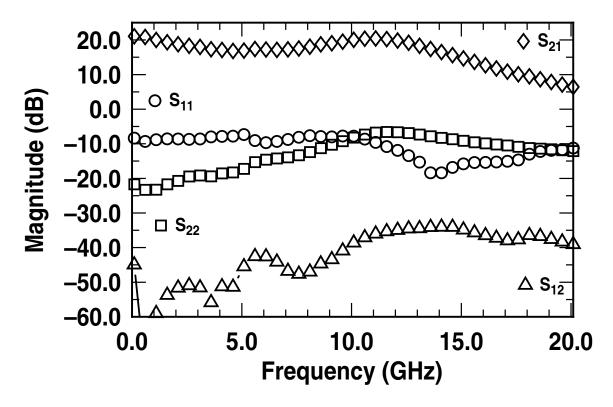

The LNA 1 operates off a 3.3 V power supply and has 7.8 mA of bias current flowing through the core circuit. Figure 16 shows its two-port measured S-parameters from 0.1 GHz to 20 GHz. The measured values  $S_{11}$  and  $S_{22}$  are lower than -7.2 dB across the

Figure 16: Measured S-parameters of the SiGe UWB LNA 1.

frequency band of 3–10 GHz, which is higher than the -12 dB and -16 dB, respectively, predicted by simulations. The  $S_{21}$  displays a maximum gain of 20.3 dB and shows a variation of 3.5 dB over the band of interest. The reverse isolation  $S_{12}$  is lower than -37 dB. Figure 17 shows the measured and simulated noise figures across the frequency range. The measured minimum NF is 1.8 dB at 3.0 GHz compared to 1.38 dB in the simulation. At high frequencies the measured NF reaches as high as 3.1 dB at 10.0 GHz, compared to the 2.03 dB in the simulation. The achieved noise figure is better than that of other UWB LNAs published in the literature and is in fact comparable to a well-designed narrow-band LNA. The key to achieving both low noise and wide bandwidth lies in the simultaneous use of shunt base-emitter capacitance and shunt-resistive feedback in a cascode LNA with inductive degeneration.

Figure 18 shows the linearity data for the LNA 1. The third-order input intercept point (IIP3) is 2.1 dBm for a two-tone input signal containing 6.00 GHz and 6.02 GHz frequency

Figure 17: Measured and simulated noise figure of the SiGe UWB LNA 1.

components, and the 1-dB compression point ( $P_{1dB}$ ) is -12.5 dBm for a 6.0 GHz input signal. The measurement and simulation results of the UWB LNA 1 are summarized in Table 4.

#### 2.8 UWB LNA 2 and 3

The LNA 1 data revealed significant differences between the simulation results and the measured results, with measured results showing worse return losses, lower gain, and a higher noise figure, but better linearity than those simulated. The parasitic inductance at the ground of the degeneration inductor ( $L_E$ ) appears to be responsible these discrepancies. To address this problem, in the LNA 2 and LNA3 design, a better ground was achieved by using all seven metal layers in parallel and as many substrate contacts as possible between the ground pads and the  $L_E$ . Also, the parasitic inductance at the base of the common-base

Figure 18: Measured IIP3 of the SiGe UWB LNA 1.

| Table 4: Summary of the SIGE UWB LINA I Characteristics. |                                 |                                 |  |  |  |  |  |  |  |

|----------------------------------------------------------|---------------------------------|---------------------------------|--|--|--|--|--|--|--|

|                                                          | Measured                        | Simulated                       |  |  |  |  |  |  |  |

| Bandwidth                                                | 0.1-13.6 GHz                    | 0.1-13.7 GHz                    |  |  |  |  |  |  |  |

| $NF_{min}$ - $NF_{max}$                                  | 1.8 - 3.1 dB                    | 1.38 - 2.03 dB                  |  |  |  |  |  |  |  |

| Gain <sub>min</sub> - Gain <sub>max</sub>                | 16.8 - 20.3 dB                  | 19.7 - 21.8 dB                  |  |  |  |  |  |  |  |

| $S_{11}$                                                 | < -7.2 dB                       | < -12.2 dB                      |  |  |  |  |  |  |  |

| $S_{22}$                                                 | < -7.4 dB                       | < -16 dB                        |  |  |  |  |  |  |  |

| $S_{12}$                                                 | < -37 dB                        | < -48.3 dB                      |  |  |  |  |  |  |  |

| IIP3(at 6 GHz)                                           | 2.1 dBm                         | -4 dBm                          |  |  |  |  |  |  |  |

| $P_{1dB}(at \ 6 \ GHz)$                                  | -12.5 dBm                       | -14.6 dBm                       |  |  |  |  |  |  |  |

| Power supply                                             | 3.3 V                           | 3.3 V                           |  |  |  |  |  |  |  |

| Power consumption                                        | 26 mW                           | 26 mW                           |  |  |  |  |  |  |  |

| (without output buffer)                                  |                                 |                                 |  |  |  |  |  |  |  |

| Die size                                                 | $0.80 \times 0.90 \text{ mm}^2$ | $0.80 \times 0.90 \text{ mm}^2$ |  |  |  |  |  |  |  |

Table 4: Summary of the SiGe UWB LNA 1 Characteristics.

transistor (non-ideal ground) may have degraded the S-parameters. A by-pass capacitor was therefore used to achieve a better ground, but the return path to ground may still introduce non-negligible parasitic inductance. Similar methods that incorporated the use of wider and multiple layer of metals have also been used to alleviate this problem. Instead of using a parallel capacitor  $C_M$  between the base and emitter, the new design simply uses a very large transistor size to increase the  $C_{BE}$ . The larger transistor also has a smaller  $r_b$ , and thus a lower noise figure. LNA 2 was implemented in 7HP technology, as with the LNA 1, but LNA 3 was implemented in 8HP technology, which features 130 nm lithography, 200/280 GHz ( $f_T / f_{max}$ ), and 1.7 V  $BV_{CEO}$  [36]. Therefore, a lower noise figure is expected from LNA 3.

Figure 19: Die micrograph of the SiGe UWB LNA 2.

## 2.9 Measurement Results of UWB LNA 2

The chip micrograph of LNA 2 is shown in Fig. 19. This LNA operates off a 3.3 V power supply and has 7.95 mA of bias current flowing through its core circuit.

Figures 20- 23 show the two-port measured S-parameters from 1.0 GHz to 15.0 GHz. The measured  $S_{11}$  and  $S_{22}$  are lower than -13.4 dB and -8.7 dB, respectively, across the

Figure 20: Measured  $S_{11}$  of the SiGe UWB LNA 2.

Figure 21: Measured  $S_{22}$  of the SiGe UWB LNA 2.

Figure 22: Measured  $S_{12}$  of the SiGe UWB LNA 2.

frequency band of 3-10 GHz, compared with the -12.7 dB and -21.9 dB, respectively, predicted by simulations. The  $S_{21}$  displays a maximum gain of 20.0 dB and shows a variation of 1.1 dB over the band of interest. The reverse isolation  $S_{12}$  is lower than -33 dB. Figure 24 shows the measured and simulated noise figures across the frequency range. The measured minimum NF is 1.61 dB, compared to 1.46 dB in the simulation. At high frequencies the measured NF reached as high as 2.38 dB, compared to 2.32 dB in the simulation. The achieved noise figure is better than that of LNA 1 because of the improvements discussed in the previous section.

Figure 25 shows the linearity data for the LNA 2. The third-order input intercept point (IIP3) is -4.0 dBm for a two-tone input signal containing 6.00 GHz and 6.02 GHz frequency components.

**Figure 23:** Measured  $S_{21}$  of the SiGe UWB LNA 2.

| Tuble 5. Summary of the Side 6 will be with 2 characteristics. |                                 |                                 |  |  |  |  |  |  |

|----------------------------------------------------------------|---------------------------------|---------------------------------|--|--|--|--|--|--|

|                                                                | Measured                        | Simulated                       |  |  |  |  |  |  |

| Bandwidth                                                      | 0.1-11.2 GHz                    | 0.1-11.6 GHz                    |  |  |  |  |  |  |

| $NF_{min}$ - $NF_{max}$                                        | 1.61 - 2.38 dB                  | 1.46 - 2.32 dB                  |  |  |  |  |  |  |

| Gain <sub>min</sub> - Gain <sub>max</sub>                      | 18.9 - 20.0 dB                  | 19.0 - 20.6 dB                  |  |  |  |  |  |  |

| $S_{11}$                                                       | < -13.4 dB                      | < -12.7 dB                      |  |  |  |  |  |  |

| $S_{22}$                                                       | < -8.7 dB                       | < -21.9 dB                      |  |  |  |  |  |  |

| $S_{12}$                                                       | < -33 dB                        | < -52.4 dB                      |  |  |  |  |  |  |

| IIP3(at 6 GHz)                                                 | -4 dBm                          | -6.5 dBm                        |  |  |  |  |  |  |

| Power supply                                                   | 3.3 V                           | 3.3 V                           |  |  |  |  |  |  |

| Power consumption                                              | 26.2 mW                         | 26.2 mW                         |  |  |  |  |  |  |

| (without output buffer)                                        |                                 |                                 |  |  |  |  |  |  |

| Die size                                                       | $0.96 \times 0.94 \text{ mm}^2$ | $0.96 \times 0.94 \text{ mm}^2$ |  |  |  |  |  |  |

Table 5: Summary of the SiGe UWB LNA 2 Characteristics.

## 2.10 Measurement Results of UWB LNA 3

The chip micrograph of LNA 3 is shown in Figure 26. This LNA operates off a 3.3 V power supply and has 9.7 mA of bias current flowing through its core circuit.

Figures 27- 30 show the two-port measured S-parameters from 1.0 GHz to 15.0 GHz.

Figure 24: Measured and simulated noise figure of the SiGe UWB LNA 2.

The measured  $S_{11}$  and  $S_{22}$  are lower than -12.6 dB and -16.6 dB, respectively, across the frequency band of 3-10 GHz, compared with the -12.8 dB and -29.2 dB, respectively, predicted by simulations. The  $S_{21}$  displays a maximum gain of 23.6 dB with a variation of 2.9 dB over the band of interest. The reverse isolation  $S_{12}$  is lower than -58 dB. Fig. 31 shows the measured and simulated noise figures across the frequency range. The measured minimum NF is 1.17 dB, compared to 0.96 dB predicted by the simulation. At high frequencies the measured NF reached as high as 1.75 dB, compared to 1.39 dB in the simulation. The achieved noise figure is again better than that of LNA 1 or LNA 2 because of the improvements discussed in the previous section and the more advanced process technology.

Figure 32 shows the linearity data of the LNA 3. The third-order input intercept point (IIP3) is -3.6 dBm for a two-tone input signal containing 6.00 GHz and 6.02 GHz frequency components.

Figure 25: Measured IIP3 of the SiGe UWB LNA 2.

Figure 26: Die micrograph of the SiGe UWB LNA 3.

**Figure 27:** Measured  $S_{11}$  of the SiGe UWB LNA 3.

Figure 28: Measured  $S_{22}$  of the SiGe UWB LNA 3.

Figure 29: Measured  $S_{12}$  of the SiGe UWB LNA 3.

**Figure 30:** Measured  $S_{21}$  of the SiGe UWB LNA 3.

Figure 31: Measured and simulated noise figure of the SiGe UWB LNA 3.

The measurement and simulation results for the UWB LNA 3 are summarized in Table 6.

|                                           | Measured                        | Simulated                       |

|-------------------------------------------|---------------------------------|---------------------------------|

| Bandwidth                                 | 0.1-14.2 GHz                    | 0.1-16.3 GHz                    |

| NF <sub>min</sub> - NF <sub>max</sub>     | 1.17 - 1.75 dB                  | 0.96 - 1.39 dB                  |

| Gain <sub>min</sub> - Gain <sub>max</sub> | 20.7 - 23.6 dB                  | 21.6 - 23.3 dB                  |

| $S_{11}$                                  | < -12.6 dB                      | < -12.8 dB                      |

| $S_{22}$                                  | < -16.6 dB                      | < -29.2 dB                      |

| $S_{12}$                                  | < -58 dB                        | < -51.0 dB                      |

| IIP3(at 6 GHz)                            | -3.6 dBm                        | -7.5 dBm                        |

| Power supply                              | 3.3 V                           | 3.3 V                           |

| Power consumption                         | 32 mW                           | 32 mW                           |

| (without output buffer)                   |                                 |                                 |

| Die size                                  | $0.86 \times 0.95 \text{ mm}^2$ | $0.86 \times 0.95 \text{ mm}^2$ |

Table 6: Summary of the SiGe UWB LNA 3 Characteristics.

Figure 32: Measured IIP3 of the SiGe UWB LNA 3.

Table 7 draws a comparison between the characteristics of the three UWB LNAs reported in this work and those of other published Si/SiGe UWB LNAs. Based on this comparison, the proposed UWB LNAs have the lowest noise figure achieved to date in Si technology.

### 2.11 Summary

High-performance wideband SiGe HBT LNAs for use in UWB systems have been presented here. The use of increased base-emitter capacitance and weak shunt resistive feedback in a cascode amplifier with inductive degeneration significantly improves the bandwidth of the LNA, and simultaneously achieves a very low noise figure. Design strategies for this UWB LNA and comparisons to other topologies have been discussed. The proposed UWB LNAs have the best wideband noise performance of all reported other state-of-the-art UWB LNAs, exhibiting the lowest noise figures across the entire 3-10 GHz bandwidth.

| Table 7: Comparison with Published Si/Si/Ge UWB LNAs. | <i>IIP</i> <sub>3</sub> Power Process | [dBm] [mW] | $0 \qquad 52 \qquad 0.18 \ \mu \mathrm{m}  \mathrm{CMOS}$ | - 52 0.18 $\mu$ m CMOS | 4 5.4 0.35 $\mu m$ CMOS | 2.5   13.2   0.25 $\mu$ m SOI SiGe | -6.7 9 0.18 $\mu$ m CMOS |               |                       | -7.5 9.6 0.18 $\mu$ m SiGe | 12.6 (      |           | 4.5 (     | 12.010.6 10.57 0.18 $\mu$ m CMOS | -8   29.7   0.25 $\mu$ m SiGe | 2.1 <sup>5</sup> 25.7 0.18 $\mu$ m SiGe | $.0^5$   26.2   0.18 $\mu m$ SiGe | $-3.6^5$ 32 0.13 $\mu$ m SiGe |

|-------------------------------------------------------|---------------------------------------|------------|-----------------------------------------------------------|------------------------|-------------------------|------------------------------------|--------------------------|---------------|-----------------------|----------------------------|-------------|-----------|-----------|----------------------------------|-------------------------------|-----------------------------------------|-----------------------------------|-------------------------------|

| ished Si/SiC                                          | -                                     |            | 6 1                                                       |                        | ·                       |                                    |                          |               |                       |                            |             | 5         | 2 7.6-9.1 | -                                |                               |                                         |                                   |                               |