## DEVELOPMENT OF LOW-COST HIGH-EFFICIENCY TUNNEL OXIDE PASSIVATED CONTACT SILICON SOLAR CELLS

A Dissertation Presented to The Academic Faculty

by

Ying-Yuan Huang

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

Georgia Institute of Technology

December 2021

Copyright © 2021 by Ying-Yuan Huang

## DEVELOPMENT OF LOW-COST HIGH-EFFICIENCY TUNNEL OXIDE PASSIVATED CONTACT SILICON SOLAR CELLS

Approved by:

Dr. Ajeet Rohatgi, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Thomas K. Gaylord School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Bernard Kippelen School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Benjamin D.B. Klein School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Juan-Pablo Correa-Baena School of Materials Science and Engineering *Georgia Institute of Technology*

Date Approved: October 29, 2021

This dissertation is dedicated to my wife, my parents, and my daughter for their love, encouragement, support, and patience.

## ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my advisor, Dr. Rohatgi, for his guidance, assistance, and support through the research. I appreciate the tremendous time and effort he has put into my research. I also would like to thank Dr. Thomas K. Gaylord, Dr. Bernard Kippelen, Dr. Benjamin D.B. Klein, and Dr. Juan-Pablo Correa-Baena for serving on my dissertation committee.

I am truly grateful for all the current and former members of University Center of Excellence for Photovoltaics Research and Education (UCEP), including Dr. Young-Woo Ok, Ajay Upadhyaya, Vijay Upadhyaya, Brian Rounsaville, Charles Calloway, Keeya Madani, Wook-Jin Choi, Aditi Jain, Sagnik Dasgupta, Dr. Yuguo Tao, Dr. Eunhwan Cho, Dr. Chia-Wei Chen, Andrew Tam, Francesco Zimbardi, Keith Tate, and Carla East, for their true friendship, generous supports, and great teamwork.

I would like to thank the members in Georgia Tech Institute for Electronics and Nanotechnology (IEN), including Tran-Vinh Nguyen, Andrew Watkins, Dr. Chris Yang, Dr. Hang Chen, Thomas Averette, Dean Sutter, Charlie Suh, and Gary Spinner for their technical supports and valuable discussions. Special thanks to Vinodh Chandrasekaran at First Solar Inc. for discussions on screen-printed metal contacts formation, and Dr. Adam Payne for teaching me LPCVD operation at Suniva Inc.

This research was supported by the U.S. Department of Energy's Office of Energy Efficiency and Renewable Energy (EERE) under Solar Energy Technologies Office (SETO) Agreement Number DE-EE0007554, DE-EE0009350, and DE-EE0008562.

# **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIST OF TABLES vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LIST OF SYMBOLS AND ABBREVIATIONS xvi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CHAPTER 1. INTRODUCTION       1         1.1       Statement of the Problem       1         1.2       Specific Research Objectives       6         1.2.1       Task 1: Development of a Technology Roadmap To 23% Efficiency TOPCon Solar Cells       8         1.2.2       Task 2: Technology Development and Formation of Optimized Ion-Implanted Boron Emitter with Metallized J <sub>0e</sub> of 30 fA/cm <sup>2</sup> 10         1.2.3       Task 3: Development, Optimization and Fabrication of Rear Side N-TOPCon with Metallized J <sub>0b</sub> , of 5 fA/cm <sup>2</sup> 11         1.2.4       Task 4: Fabrication of High-Efficiency (~23%) N-TOPCon Solar Cells by Process Development and Integration of Advanced Technologies       12         1.2.5       Task 5: Modelling and Understanding of > 25% Rear Junction Double-Side Passivated Contact Solar Cells with Selective Area TOPCon on Front       13 |

| CHAPTER 2.BASIC OPERATION OF SILICON SOLAR CELLS AND<br>RECOMBINATION MECHANISMS142.1Basic Operation of a Solar Cell and Structure of an N-TOPCon Cell142.2Recombination Mechanisms in Si Solar Cells182.2.1Radiative Recombination192.2.2Auger Recombination202.2.3Shockley-Read-Hall (SRH) Recombination222.4Surface Recombination242.3The Recombination Current Density Jo272.4Quantum-Mechanical Tunneling30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CHAPTER 3.LITERATURE REVIEW343.1Crystalline Silicon Solar Cells - Current Status and Future Trends343.2Heterojunction with Intrinsic Thin layer (HIT) Solar Cell373.3Tunnel Oxide Passivated Contact (TOPCon) Solar Cell403.4Operating Principle and Fundamental Understanding of Carrier Selective<br>TOPCon Structure for Achieving Excellent Passivation443.5Progress in Industrial Screen-Printed N-TOPCon Cells.46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### CHAPTER 4. TASK 1: DEVELOPMENT OF A TECHNOLOGY ROADMAP TO 23% EFFICIENCY TOPCON SOLAR CELLS 51

| 4.1  | Device Modeling of Si Solar Cells                                                                                                      | 52        |

|------|----------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 4.2  | Development of a Technology Roadmap for > 23% Efficient n-TOPCon Co                                                                    | ells      |

|      |                                                                                                                                        | 54        |

| 4.3  | Modelling and Understanding the Impact of Bulk Lifetime and Resistivity                                                                |           |

|      | the Efficiency of Proposed TOPCon Cell Design                                                                                          | 61        |

| 4.4  | Modeling The Impact of Metallized J <sub>0e</sub> and J <sub>0b</sub> , and Front and Back Conta                                       |           |

| 4 5  | Resistivity on TOPCon Cell Efficiency                                                                                                  | 64        |

| 4.5  | Development of a Grid Design Model and Calculator for Optimizing From<br>and Rear Contact Grid Designs for Bifacial TOPCon Solar Cells | t<br>66   |

| 15   | 1 Series Resistance Calculation                                                                                                        | 68        |

|      | 2 Determination of $J_{SC}$ , $V_{OC}$ , and Efficiency as a Function of Front and Rear Gr                                             |           |

| 1.5. | Design Using the Grid Model                                                                                                            | 74        |

| 4.5. | 3 Determination of FF as a Function of Front and Rear Grid Design Using the                                                            |           |

|      | Grid Model                                                                                                                             | 78        |

| 4.5. | 4 Validation of the Grid Calculator Results with Advanced Quokka 2 Device                                                              |           |

|      | Model                                                                                                                                  | 83        |

| 4.6  | Summary                                                                                                                                | 84        |

| СНАІ | PTER 5. TASK 2: TECHNOLOGY DEVELOPMENT AND FORMATIO                                                                                    | N         |

|      | OF OPTIMIZED ION-IMPLANTED BORON EMITTER WITH                                                                                          | 1         |

|      | METALLIZED $J_{0E}$ OF 30 FA/CM <sup>2</sup>                                                                                           | 87        |

| 5.1  | Fabrication of Passivated and Metallized Ion-Implanted B Emitters and th                                                               | ie        |

|      | Procedure for Determining Corresponding Jopass and Jometal Values                                                                      | <b>89</b> |

| 5.2  | Characterization of Unmetallized Ion-implanted B Emitters as a Function                                                                |           |

|      | Implantation Dose                                                                                                                      | 92        |

| 5.3  | Modeling to Establish a Baseline Metallized J <sub>0e,metal</sub> Value for Implanted B                                                |           |

|      | Emitters Assuming Uniform Metal Contact Interface with Surface                                                                         | 95        |

| 5.4  | Recombination Velocity (SRV) = $10^7$ cm/s<br>Modeling and Quantitative Understanding of the Significant Difference in                 |           |

| 3.7  | Modeling and Quantitative Understanding of the Significant Difference in<br>Measured $J_{0e,metal}$ for Pastes A and B                 | 98        |

| 5.5  |                                                                                                                                        | 105       |

|      |                                                                                                                                        |           |

|      | PTER 6. TASK 3: DEVELOPMENT, OPTIMIZATION AND                                                                                          |           |

|      | FABRICATION OF REAR SIDE N-TOPCON WITH METALLIZED $J_{0B'}$                                                                            | OF        |

|      | 5 FA/CM <sup>2</sup> 106                                                                                                               |           |

| 6.1  | Experimental Development and Characterization of N-TOPCon Using<br>Chemically Grown Tunnel Oxide and LPCVD Polysilicon                 | 107       |

| 61   |                                                                                                                                        | 107       |

|      | <ol> <li>Fabrication of Phosphorous-Doped Poly-Si by Low-Pressure Chemical Vapo</li> </ol>                                             |           |

| 0.11 |                                                                                                                                        | 109       |

| 6.1. | 3 Optimization of Crystallization and Dopant Activation Anneal of Poly-Si Lay                                                          |           |

|      |                                                                                                                                        | 109       |

| 6.1. | 4 Investigation of the Effect of Surface Morphology on Recombination Current                                                           | t         |

|      | 5                                                                                                                                      | 114       |

| 6.1. | 5 Investigation of the Impact of LPCVD Poly-Si Thickness on Recombination                                                              |           |

|      | Current Density $(J_0)$ of the N-TOPCon                                                                                                | 120       |

| 6.1        | .6 Process Development for Large Area Bifacial Screen-Printed Si Solar Cells<br>with Rear Side LPCVD Grown TOPCon and Ion-Implanted Boron Emitter    | 126        |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 6.2        | 1                                                                                                                                                    | 120<br>129 |

| ,          | PTER 7. TASK 4: FABRICATION OF HIGH-EFFICIENCY (~23%) N-<br>TOPCON SOLAR CELLS BY PROCESS DEVELOPMENT AND                                            |            |

|            |                                                                                                                                                      | 131        |

| 7.1        | Fabrication of 239 cm <sup>2</sup> High-Efficiency Screen-Printed Bifacial N-TOPCo<br>Cell with Homogeneous B Emitter                                | n<br>131   |

| 7.2        | Fabrication of 100 cm <sup>2</sup> ~23% N-TOPCon Cells with Homogeneous B Emi                                                                        | -          |

| 7.2        | rabilitation of 100 cm = 25 /0 1(-101 con cens with fromogeneous b Linit                                                                             | 135        |

| 7.3        | Modelling the Impact of Selective Emitter, Improved Contacts and Higher<br>Bulk Lifetime to Estimate the Efficiency Potential of ~23% Single-Side N- |            |

| 7 4        | ð                                                                                                                                                    | 139        |

| 7.4        | Summary                                                                                                                                              | 144        |

|            | PTER 8. TASK 5: MODELLING AND UNDERSTANDING OF > 25%<br>REAR JUNCTION DOUBLE-SIDE PASSIVATED CONTACT SOLAR                                           |            |

|            |                                                                                                                                                      | 146        |

| 8.1        |                                                                                                                                                      | 147        |

| 8.2        | Modeling and Understanding of Proposed Rear Junction Cell Structure of<br>N-Base with Selective Area Front TOPCon                                    | n<br>149   |

| 8.2        | .1 Proposed Structure of Rear Junction Solar Cell with Selective Front TOPCon                                                                        |            |

| 0.2        |                                                                                                                                                      | 149        |

| 8.2        | .2 Optical Simulation of Absorption Loss as a Function of Thickness of Full-As and Selective TOPCon on the Front                                     | rea<br>150 |

| 8.2        | .3 Simulation of Efficiency Potential of Proposed Selective TOPCon Cell Desig                                                                        | gn<br>151  |

| 8.2        | .4 Modelling the Impact of Si Bulk Material Properties on Cell Performance of                                                                        |            |

| 07         | Rear Junction Selective Front TOPCon Cell                                                                                                            | 154        |

| 8.3        | Summary                                                                                                                                              | 157        |

| CHA<br>9.1 | PTER 9. CONCLUSIONS<br>Conclusions                                                                                                                   | 159<br>159 |

|            | ENDIX A INPUT FILES FOR QUOKKA 2 FOR SINGLE-SIDE N-TOPC SOLAR CELL SIMULATION                                                                        | ON<br>163  |

|            | ENDIX B DETAILED PROCESS SEQUENCE FOR SINGLE SIDE N-<br>TOPCON SOLAR CELL FABRICATION                                                                | 170        |

| REFE       | ERENCES                                                                                                                                              | 180        |

| PUBI       | LICATIONS FROM THIS WORK                                                                                                                             | 195        |

# LIST OF TABLES

| Table 1: IV parameters of recent HIT cells from the literature.    38                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2: IV parameters of small area (~4 cm <sup>2</sup> ) R&D TOPCon cells in literature                                                                         |

| Table 3: Literature survey of screen-printed n-TOPCon solar cells on large area n-type Cz wafers.       49                                                        |

| Table 4: Physical models for the device simulations                                                                                                               |

| Table 5: Quokka 2 modeling results and input parameters for the n-PERT and n-TOPCon cells.      58                                                                |

| Table 6: Experimentally measured parameters (yellow-shaded) and calculated parameters (green-shaded) for the analyzed n-TOPCon cell.       73                     |

| Table 7: Analytical expression and calculated values of series resistance components for the n-TOPCon cells                                                       |

| Table 8: J <sub>0</sub> values and contact resistance estimation for different B emitters based on literature and initial measurements.       82                  |

| Table 9: Comparison of the Grid model and Quokka simulation results.       84                                                                                     |

| Table 10: Recipe parameters for phosphorus-doped poly-Si with LPCVD in this work.                                                                                 |

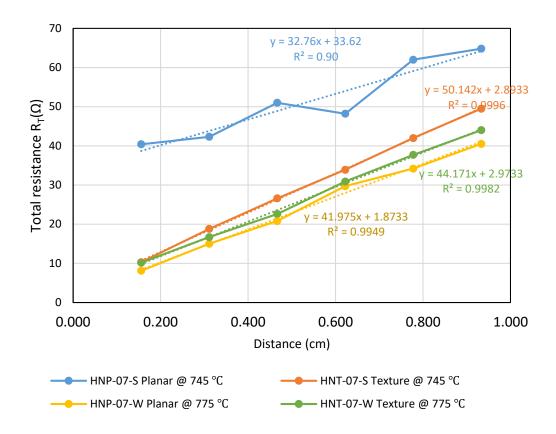

| Table 11: Contact resistivity on n <sup>+</sup> poly-Si as a function of surface morphology and peak firing temperature.         118                              |

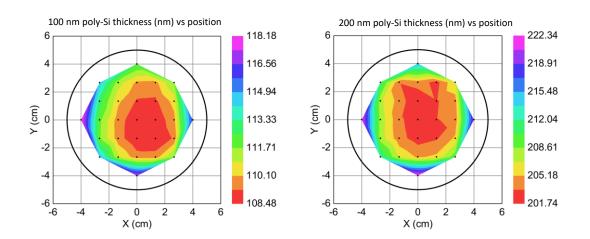

| Table 12: Contact resistivity of different silver paste (fired at 775 °C) on LPCVD poly<br>and the poly sheet resistance with 100 nm and 200 nm thick poly-Si 126 |

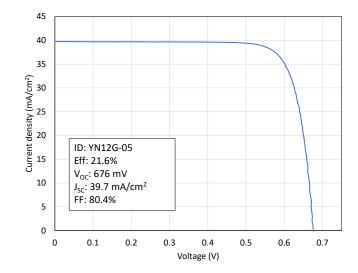

| Table 13: Measured illuminated I-V curve properties of 21.6% screen-printed TOPCon cell.      129                                                                 |

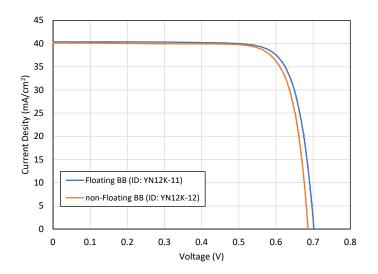

| Table 14: Measured I-V results of screen-printed, large-area n-TOPCon bifacial cells with non-floating and floating busbars.       135                            |

| Table 15: Measured I-V result of 22.6% floating busbar cell with illumination from the rear side.      135                                                        |

| Table 16: Light I-V measurement results of n-TOPCon solar cells with 170 $\Omega/\Box$ and 120 $\Omega/\Box$ implanted B emitters                                 |

|                | taurus Device modeling results and input parameters for the homogeneous 170 $\Omega/\Box$ B emitter and selective B emitter |          |

|----------------|-----------------------------------------------------------------------------------------------------------------------------|----------|

| •              | okka 2 modeling results and input parameters for the roadr                                                                  | 1        |

| Table 19: Deta | ailed parameters for Quokka 2 simulation                                                                                    | 153      |

| Table 20: Para | ameters of n-type poly-Si deposition recipe in Tystar poly                                                                  | tube 174 |

| Table 21: Para | ameters of Despatch belt furnace recipe                                                                                     |          |

# LIST OF FIGURES

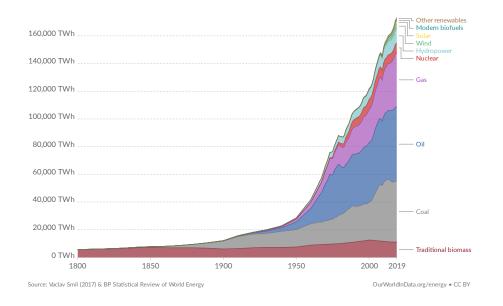

| Figure 1: Global primary energy consumption by source from the year 1800 to 2019<br>(adapted from [3])                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

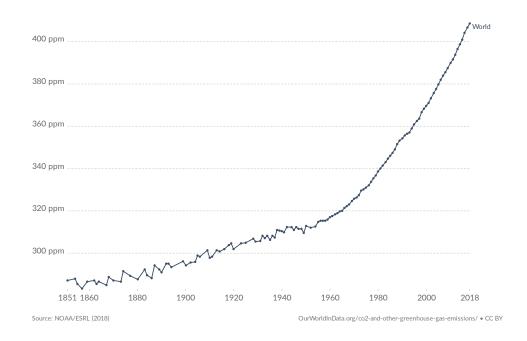

| Figure 2: Global CO <sub>2</sub> atmospheric concentration measured in parts per million (ppm) from the year 1851 to 2018 (adapted from [3])                                                                                                                         |

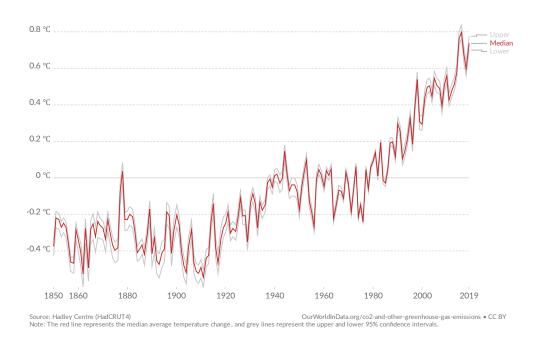

| Figure 3: Global average temperature anomaly relative to the 1961-1990 average temperature from the year 1850 to 2019 (adapted from [3])                                                                                                                             |

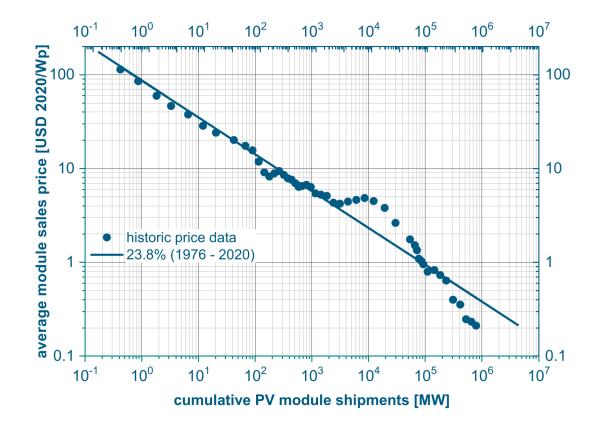

| Figure 4: Learning curve for module price as a function of cumulative shipments (adapted from [4])                                                                                                                                                                   |

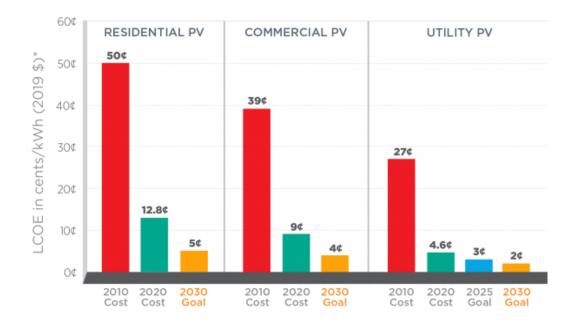

| Figure 5: Photovoltaics LCOE price goals of the US Department of Energy Solar Energy<br>Technologies Office [7]. The LCOE progress and targets are calculated based<br>on average U.S. climate and without the investment tax credit or state/local<br>incentives. 5 |

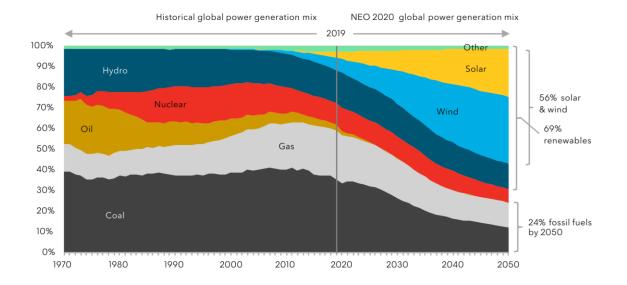

| Figure 6: Global electricity generation mix shift from 1970 to 2050 (Source:<br>BloombergNEF [6])                                                                                                                                                                    |

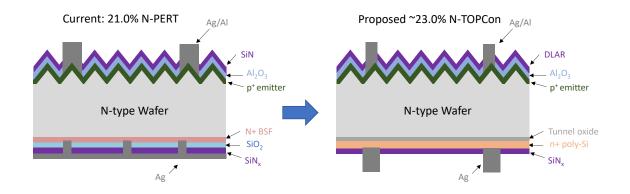

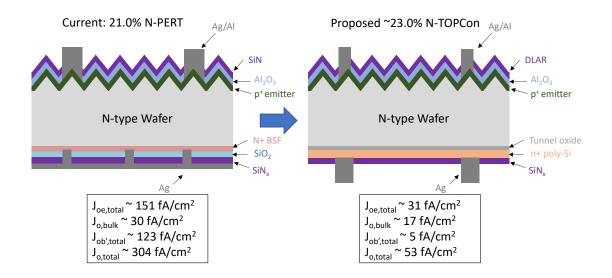

| Figure 7: Current 21% n-PERT cell structure and proposed ~23% n-TOPCon cell structure                                                                                                                                                                                |

| Figure 8: A schematic of a simple solar cell structure                                                                                                                                                                                                               |

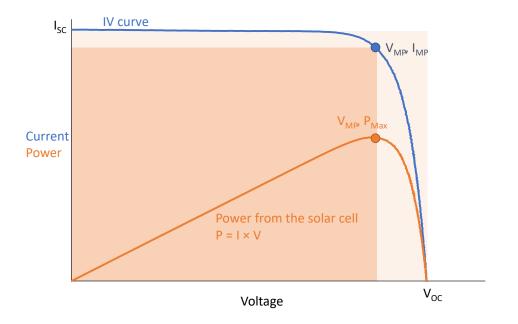

| Figure 9: The current-voltage (IV) and power-voltage curve of a solar cell                                                                                                                                                                                           |

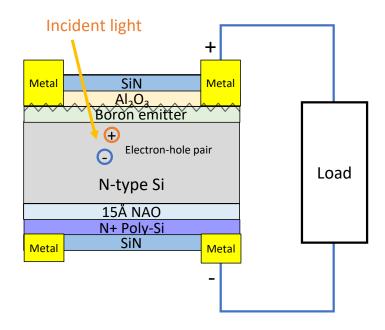

| Figure 10: Structure of the n-type TOPCon Si solar cell with boron-diffused emitter on front and tunnel oxide passivated contacts on the rear                                                                                                                        |

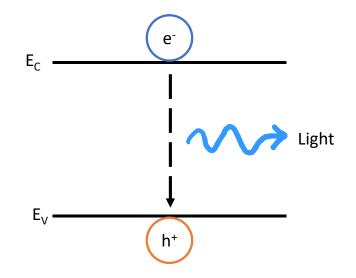

| Figure 11: Schematic representation of radiative recombination                                                                                                                                                                                                       |

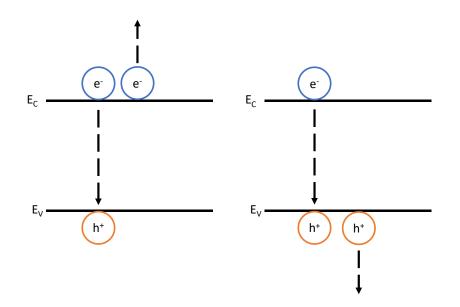

| Figure 12: Schematic representation of Auger recombination, where energy is transferred to an electron (left) or a hole (right)                                                                                                                                      |

| Figure 13: Schematic representation of SRH recombination. The red line in the middle represents a defect level                                                                                                                                                       |

| Figure 14: Schematic representation of surface recombination                                                                                                                                                                                                         |

| Figure 15: Schematic diagram of photoconductance decay lifetime tester used for evaluation of J <sub>0</sub>                                                                                                                                                         |

| $\label{eq:Figure 16:Extraction of recombination current density J_0 and bulk SRH lifetime from the} (1/\tau_{eff}-C_An^2) \ vs \ n \ curve. \qquad 30$                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

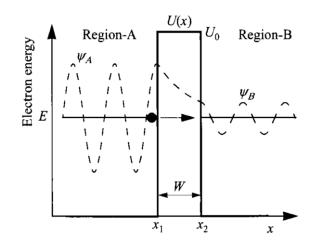

| Figure 17: Wafer functions showing electron tunneling through a rectangular barrier.<br>(Adapted from [24])                                                                                                                                                                                                                                      |

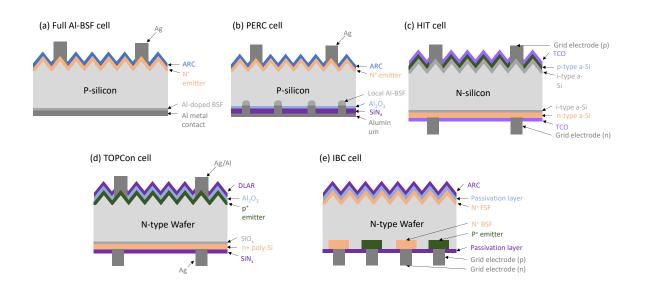

| Figure 18: Schematic diagrams of the main production Si cell technologies: (a) Full<br>aluminum-doped back surface field (Al-BSF) cell, (b) passivated emitter rear<br>cell (PERC), (c) Heterojunction with intrinsic thin layer (HIT) cell, (d) tunnel<br>oxide passivated contact (TOPCon) cell, (e) interdigitated back contact (IBC)<br>cell |

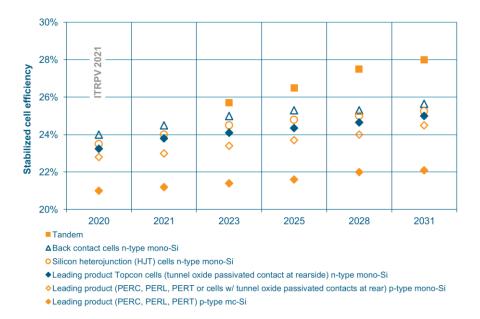

| Figure 19: The expected average stabilized efficiency values of c-Si solar cells in mass production. Adapted from [4]                                                                                                                                                                                                                            |

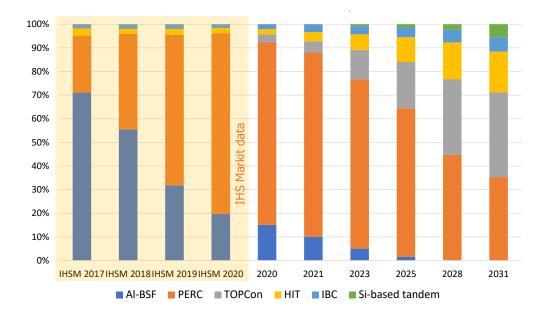

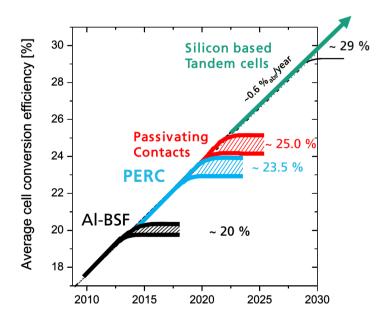

| Figure 20: Trend of market shares for different cell technologies from 2017 to 2031.<br>Replotted from [4, 32-34]                                                                                                                                                                                                                                |

| Figure 21: Potential further technological development in silicon photovoltaics. Adapted from [31]                                                                                                                                                                                                                                               |

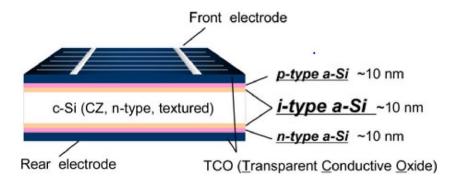

| Figure 22: Structure of a FBC HIT solar cell [35]                                                                                                                                                                                                                                                                                                |

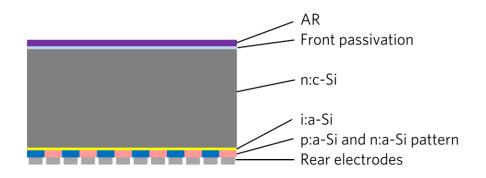

| Figure 23: Structure of an IBC HIT solar cell [36]                                                                                                                                                                                                                                                                                               |

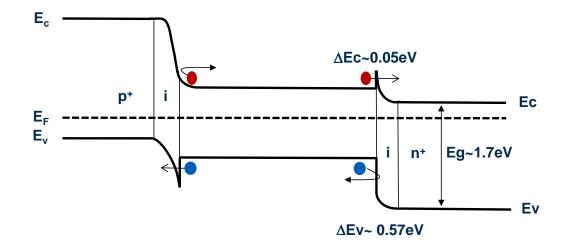

| Figure 24: Schematic band diagram of HIT cell                                                                                                                                                                                                                                                                                                    |

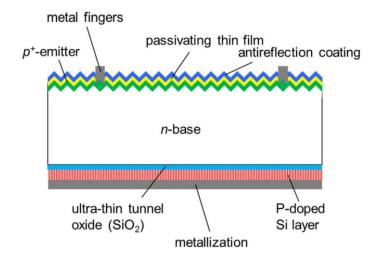

| Figure 25: Structure of a solar cell with the tunnel oxide passivated contact (TOPCon). 41                                                                                                                                                                                                                                                       |

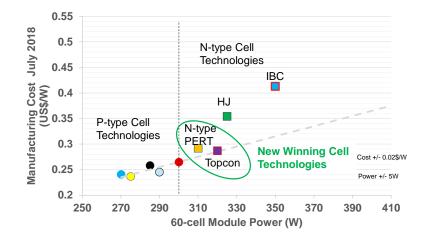

| Figure 26: Manufacturing cost and power output of existing and future commercial p-<br>and n-type PV products. The dashed line is the line of equal LCOE<br>(US\$0.01/10W) (Presented by Pierre Verlinden at 2019 IEEE PVSC)                                                                                                                     |

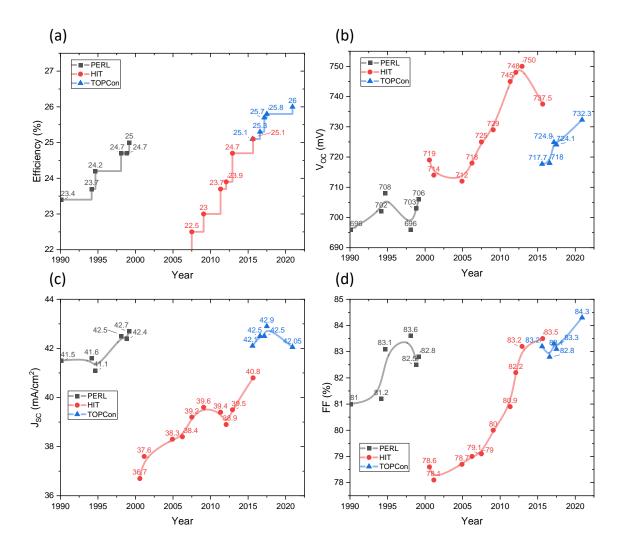

| Figure 27: Efficiency evolution over the past 30 years for different high efficiency cell architectures: PERL, TOPCon and HIT with front and back contacts in small area R&D cells (Replotted from [43])                                                                                                                                         |

| Figure 28: Schematic band diagram of tunnel oxide passivated contact                                                                                                                                                                                                                                                                             |

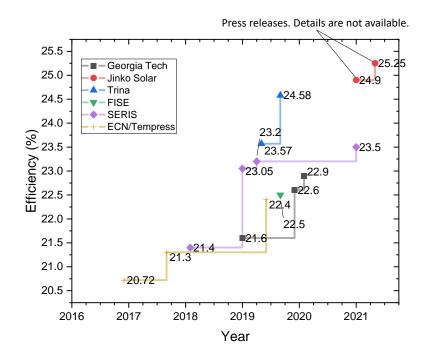

| Figure 29: Evolution of industrial manufacturable n-TOPCon cells from publications, conference, and recent press releases. Detailed information and references are listed in Table 3                                                                                                                                                             |

| Figure 30: Schematic diagram of the starting 21% n-PERT structure and proposed ~23% n-TOPCon structure with recombination current density (J <sub>0</sub> ) targets for different regions                                                                                                                                                        |

| Figure 31 | : Technology roadmap for >23% n-TOPCon cells, starting with our 21% n-<br>PERT cell. Each bar shows $J_0$ contribution from metallized and unmetallized<br>regions on front and back as well as from the base material along with all the<br>key cell parameters and efficiency    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

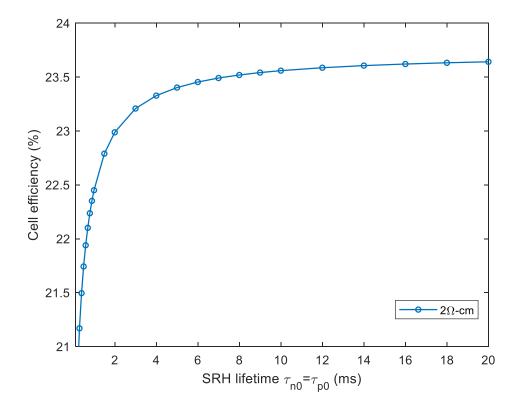

| Figure 32 | : Efficiency vs mid-gap SRH lifetime of n-TOPCon cells with advanced metallization (bar 4 in Figure 31). It shows that 23% efficiency can be achieved with 2 ms lifetime without a selective emitter, and 23.2% efficiency can be achieved with 3 ms lifetime                      |

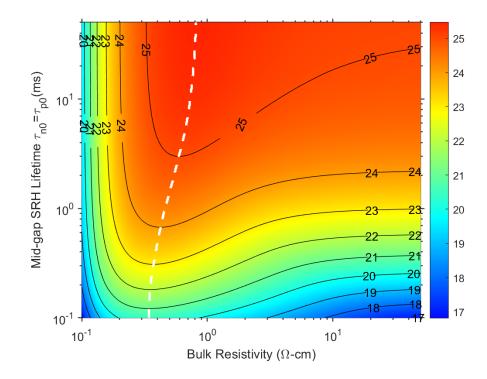

| Figure 33 | : Efficiency contour map of n-TOPCon cells with advanced metallization (bar 4 in Figure 31) as a function of bulk resistivity and mid-gap SRH lifetimes. The white dashed line corresponds to the optimum bulk resistivity that results in maximum efficiency at each SRH lifetime |

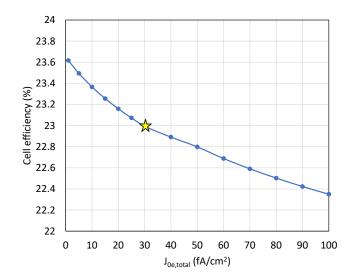

| Figure 34 | : Quokka 2 simulated cell efficiency as a function of $J_{0e,total}$ , assuming 2 ms bulk lifetime (column 5 in Table 5). The star shows the metallized $J_{0e}$ of our 23% cell design                                                                                            |

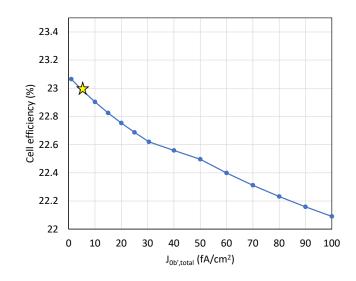

| Figure 35 | : Quokka 2 simulated cell efficiency as a function of $J_{0b',total}$ of the proposed 23% n-TOPCon cell (column 5 in Table 5). The star shows the metallized $J_{0b'}$ of our 23% cell design                                                                                      |

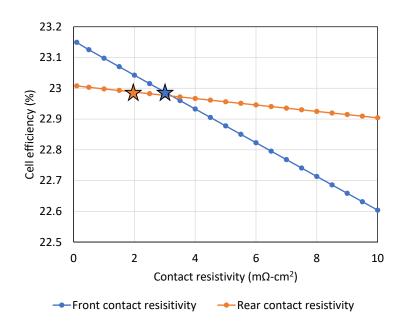

| Figure 36 | : Quokka 2 simulated cell efficiency as a function of front and rear contact resistivities of the proposed 23% n-TOPCon cell (column 5 in Table 5). The stars show the contact resistivity of our 23% cell design                                                                  |

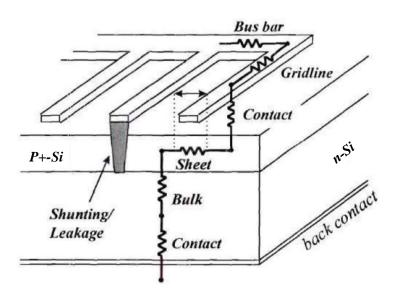

| Figure 37 | : Resistive components in a solar cell                                                                                                                                                                                                                                             |

| Figure 38 | : The trade-off of the grid line design. The arrows in the figure show the trend<br>when the grid metal coverage increases on the front side                                                                                                                                       |

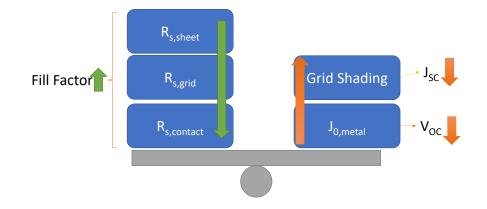

| 0         | : Schematic diagram of a solar cell with five busbars grid pattern. The yellow-<br>colored region represents the unit cell of the series resistance analysis                                                                                                                       |

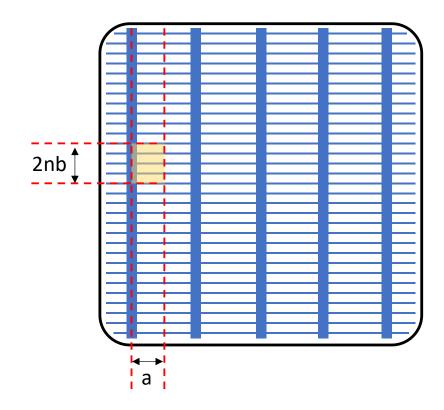

| Figure 40 | : Schematic diagram showing placement of probes in a four-point measurement<br>for determining series resistance components associated with gridline (busbar-<br>to-busbar resistance, BBR), busbar (Busbar), and emitter sheet resistance<br>(Gridline) (adapted from [89])       |

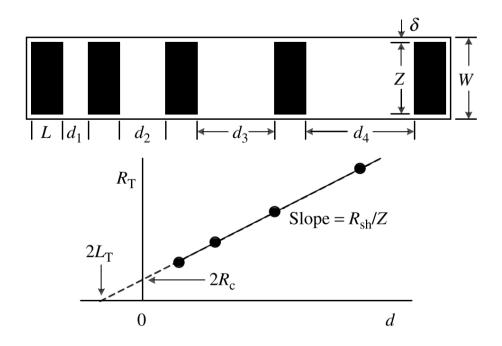

| Figure 41 | : A transfer length method test structure and a plot of total resistance as a function of contact spacing, d. Z is the length of the metal contact, and W is the width of the test sample. The $\delta$ = W-Z should be as small as possible                                       |

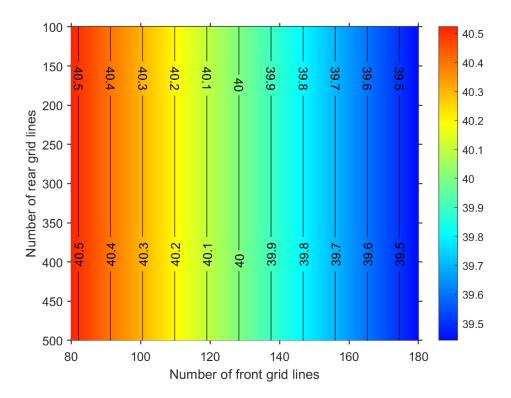

| Figure 42 | : Short-circuit current ( $J_{SC}$ , in mA/cm <sup>2</sup> ) contour as a function of number of front grid lines (x-axis) and rear grid lines (y-axis)                                                                                                                             |

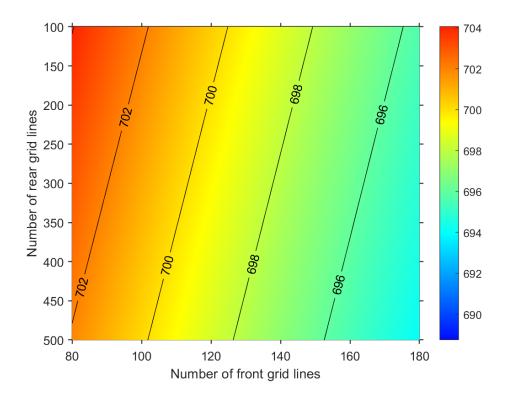

| Figure 43: Open-circuit voltage (V <sub>OC</sub> , in mV) contour as a function of number of front grid lines (x-axis) and rear grid lines (y-axis)                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

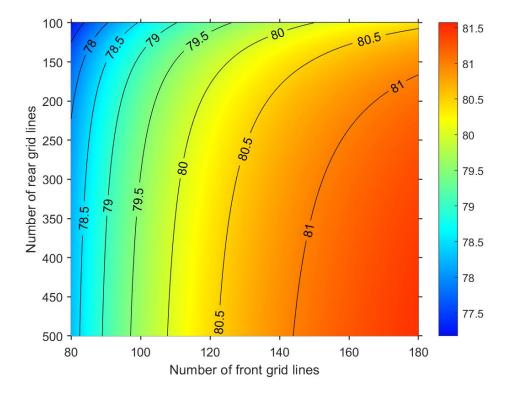

| Figure 44: Fill factor (FF, in %) contour as a function of number of front grid lines (x-<br>axis) and rear grid lines (y-axis)                                                                                                                                                                    |

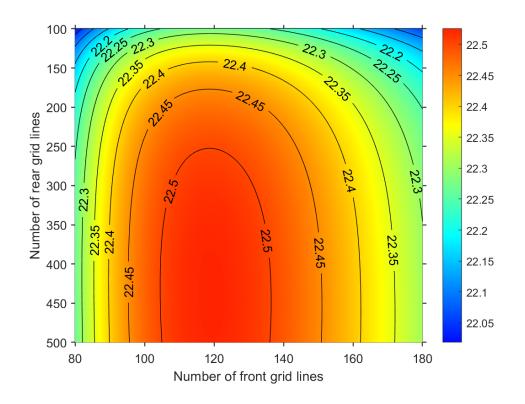

| Figure 45: Cell efficiency (in %) contour as a function of number of front grid lines (x-<br>axis) and rear grid lines (y-axis)                                                                                                                                                                    |

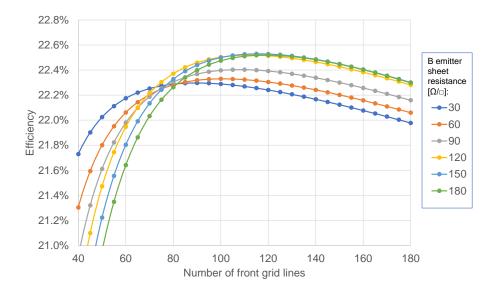

| Figure 46: Simulated cell efficiency from grid calculator as a function of numbers of front fingers for various B emitters fabricated in this research                                                                                                                                             |

| Figure 47: Schematic of symmetric $p^+/n/p^+$ test samples with implanted $p^+$ emitter on both sides and screen-printed Ag/Al paste on one side to investigate the impact of screen-printed metallization on J <sub>0</sub> and extract J <sub>0pass</sub> and J <sub>0metal</sub> components. 92 |

| Figure 48: Boron emitter sheet resistance as a function of boron ion-implantation doses<br>for 10 keV implantation energy and 1050 °C post-implantation anneal                                                                                                                                     |

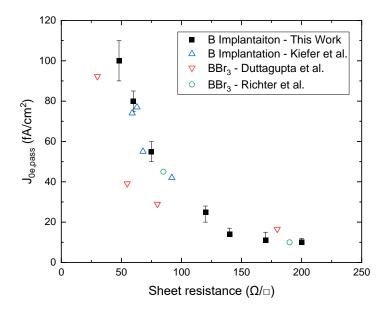

| Figure 49: Experimentally measured J <sub>0e,pass</sub> in this study (solid symbols) and selected literature data (open symbols) [104-106] as a function of boron emitter sheet resistance on textured surface                                                                                    |

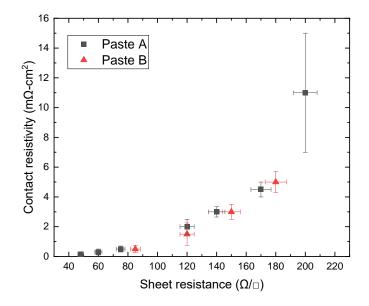

| Figure 50: Measured contact resistivity as a function of boron emitter sheet resistance for paste A and B                                                                                                                                                                                          |

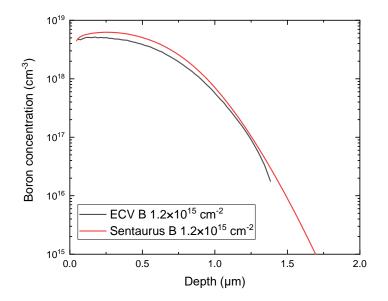

| Figure 51: Comparison between the ECV measurement and the Sentaurus Process simulation for B emitter profile with implanted dose of $1.2 \times 10^{15}$ cm <sup>-2</sup>                                                                                                                          |

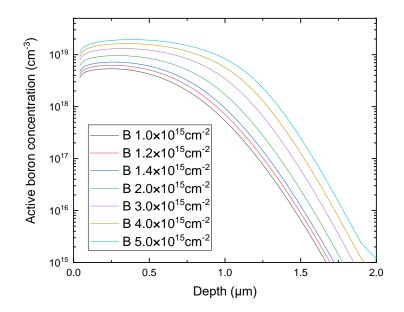

| Figure 52: Simulated boron profiles with different implanted boron doses with Sentaurus<br>Process simulation                                                                                                                                                                                      |

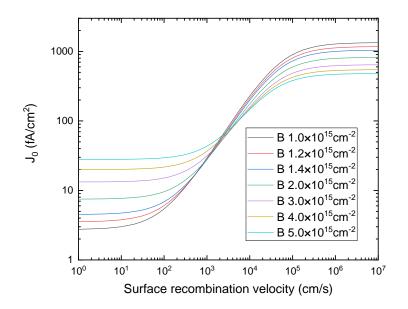

| Figure 53: Sentaurus calculated J <sub>0e</sub> as functions of surface recombination velocity with different boron implant doses                                                                                                                                                                  |

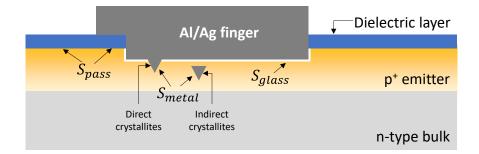

| Figure 54: Schematic diagram of the features of metal-Si contact formation after firing.98                                                                                                                                                                                                         |

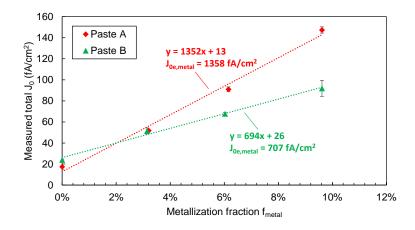

| Figure 55: Plot of measured total $J_0$ as a function of metallization fraction $f_{metal}$ with metal paste A and paste B. $J_{0e,metal}$ is extracted from the slope $(J_{0e,metal} - J_{0e,pass})$ of the fitted line. 100                                                                      |

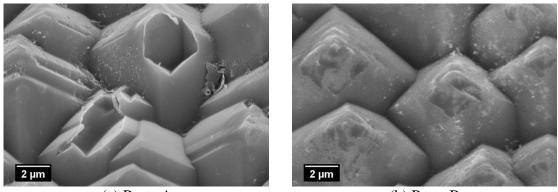

| Figure 56: SEM images of silicon surfaces under metal contacts after removal of the fired screen-printed metal gridline and glass from fired metal gridlines with paste A and paste B                                                                                                              |

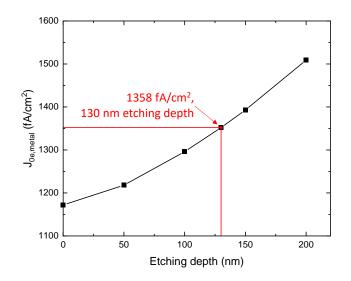

| Figure 57: Simulated paste A $J_{0e,metal}$ with varied metal etching depth for 170 $\Omega/\Box$ B emitter. For a uniform 130 nm surface etching, the simulated $J_{0e,metal}$ matches with the experimentally measured $J_{0e,metal}$ (1358 fA/cm <sup>2</sup> )                                 |

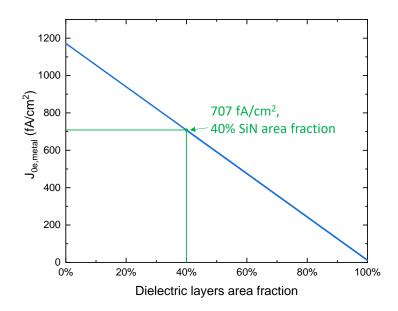

| Figure 58: Simulated paste B $J_{0e,metal}$ with varied dielectric area fraction under the grid for 170 $\Omega/\Box$ B emitter. With 40% unetched dielectric area fraction underneath metal contact, the simulated $J_{0e,metal}$ matches with the measured $J_{0e,metal}$ (707 fA/cm <sup>2</sup> )      |

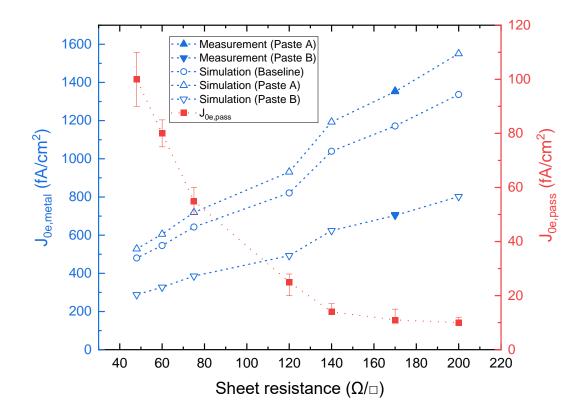

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 59: Measured $J_{0e,metal}$ at 170 $\Omega/\Box$ boron emitter, and simulated $J_{0e,metal}$ for baseline, paste A (assuming emitter etch depth of 130 nm) and paste B (assuming unetched dielectric layers area fraction of 40%) as a function of boron sheet resistance from Sentaurus simulation |

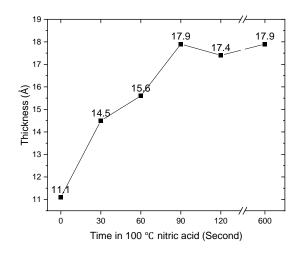

| Figure 60: Oxide thickness as a function of time in 100 °C in nitric acid108                                                                                                                                                                                                                               |

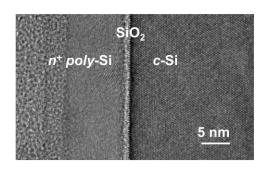

| Figure 61: Transmission electron microscopy image of our tunnel oxide passivated contact structure                                                                                                                                                                                                         |

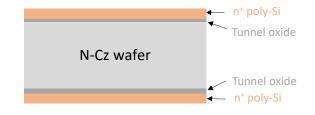

| Figure 62: Symmetric structure to study $J_{0b}$ , and $iV_{OC}$                                                                                                                                                                                                                                           |

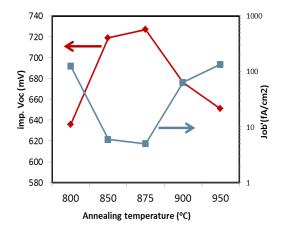

| Figure 63: Implied V <sub>OC</sub> and J <sub>0b</sub> , as a function of annealing temperature of n-TOPCon with NAO grown tunnel oxide and LPCVD poly-Si                                                                                                                                                  |

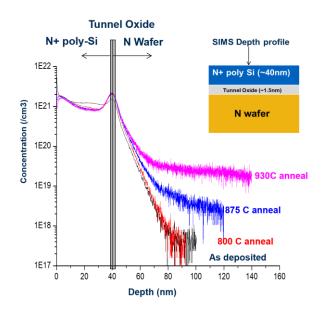

| Figure 64: SIMS measurement of the phosphorous-doped polysilicon after annealing with different temperatures (courtesy of National NanoFab Center, Korea, [126]).                                                                                                                                          |

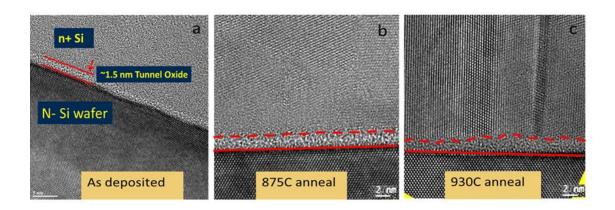

| Figure 65: HREM images of the tunnel oxide interface between n-Si and n <sup>+</sup> poly-Si a) As deposited, b) Annealed at 875°C, c) Annealed at 930°C. (Courtesy of Chonbuk National University, Korea, [126].)                                                                                         |

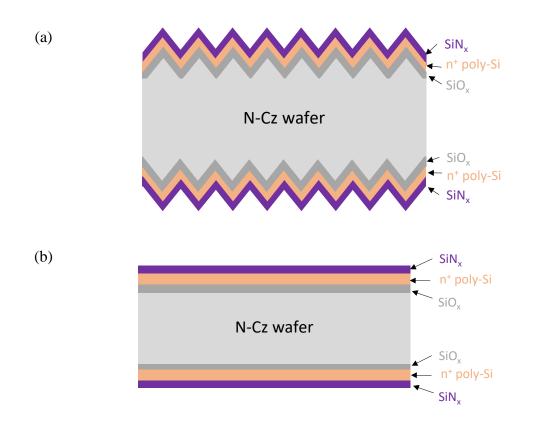

| Figure 66: Schematic structures n-TOPCon symmetric structure with (a) texture surface<br>and (b) planar surface to investigate the impact of surface morphology on<br>passivation quality and metal contact resistivity                                                                                    |

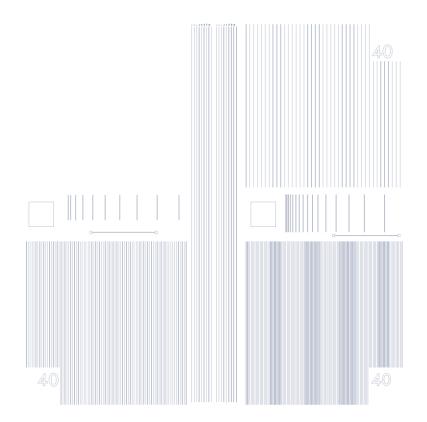

| Figure 67: Test screen with different metal fractions and TLM patterns for metallized J <sub>0</sub> and contact resistance measurements                                                                                                                                                                   |

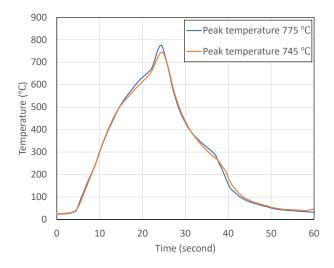

| Figure 68: Measured temperature profile for firing screen-printed metal contacts in a belt furnace at peak temperature $775 \pm 5$ °C and $745 \pm 5$ °C                                                                                                                                                   |

| Figure 69: Plot of total resistance (R <sub>T</sub> ) as a function of contact spacing on planar and textured surfaces, with peak firing temperature at 745 °C and 775 °C 118                                                                                                                              |

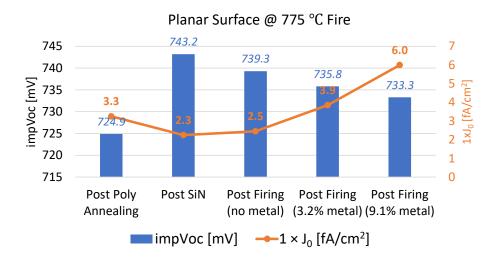

| Figure 70: Metal effect to implied $V_{OC}$ and $1 \times J_0$ value at different process stages on planar surface at 775°C peak firing temperature                                                                                                                                                        |

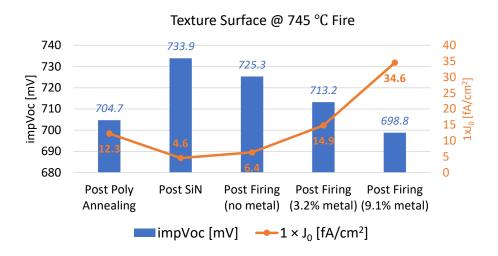

| Figure 71: Metal effect to implied $V_{OC}$ and $1 \times J_0$ value at different process stages on texture surface at 745 °C peak firing temperature                                                                                                                                                      |

| Figure 72: Poly-Si thickness measured with ellipsometer on 4-inch polished monitor wafers                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

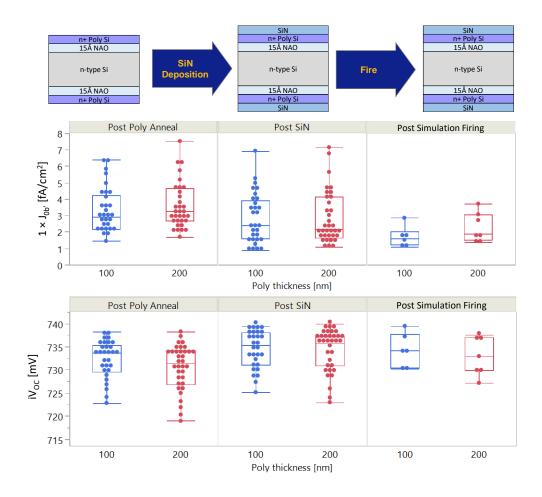

| Figure 73: $J_{0b}$ , and $iV_{OC}$ with different LPCVD poly-Si thicknesses at different stages.<br>Data points are measured with 5 wafers for 100 nm poly, and 6 wafers for 200 nm poly-Si. Each wafer is measured with 5 positions at the post poly anneal stage, and the post SiN stage. For the post simulation firing stage, only the quarters without screen-printed metal are shown (1 point on each wafer) 122 |

| Figure 74: Schematic of n-TOPCon symmetric structure to investigate the impact of screen-printed metallization on J <sub>0</sub>                                                                                                                                                                                                                                                                                        |

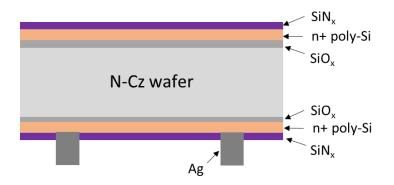

| Figure 75: Full area J <sub>0,poly</sub> with different metal coverage. The left column is for 100nm thick poly-Si, and the right column is for 200 nm thick poly-Si                                                                                                                                                                                                                                                    |

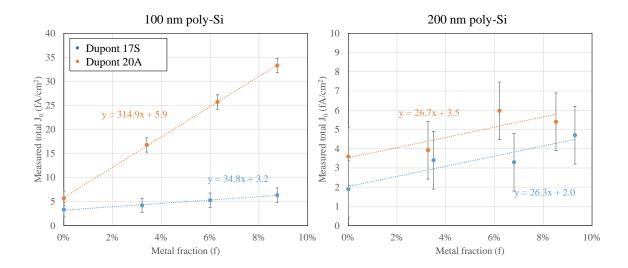

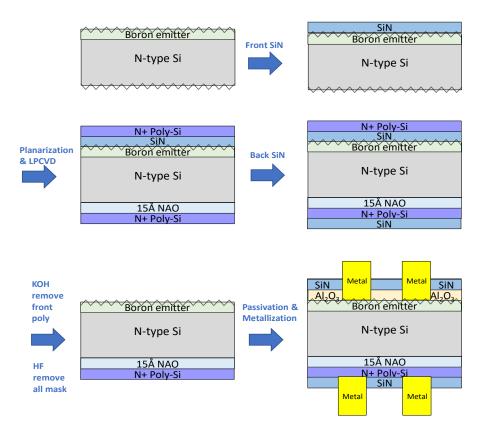

| Figure 76: Schematic diagram of the cell process sequence and structure of the first 21.6% screen-printed TOPCon solar cell fabricated in this study 127                                                                                                                                                                                                                                                                |

| Figure 77: Schematic diagram of LPCVD TOPCon formation and metallization after processing of front B emitter wafer                                                                                                                                                                                                                                                                                                      |

| Figure 78: Measured current-voltage curve of 21.6% the first n-TOPCon cell in this study                                                                                                                                                                                                                                                                                                                                |

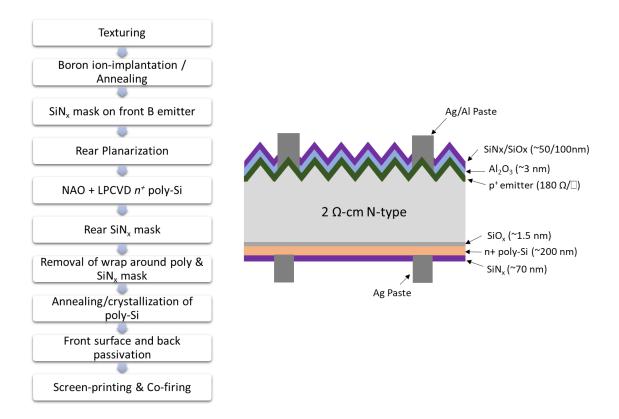

| Figure 79: Process sequence and structure of the screen-printed bifacial N-type Si solar cell with front implanted boron emitter and rear tunnel oxide passivated contact                                                                                                                                                                                                                                               |

| Figure 80: Light I-V curves of screen-printed, large-area n-TOPCon bifacial cells with non-floating and floating busbars                                                                                                                                                                                                                                                                                                |

| Figure 81: EL image of full area 239 cm <sup>2</sup> cell under reverse bias                                                                                                                                                                                                                                                                                                                                            |

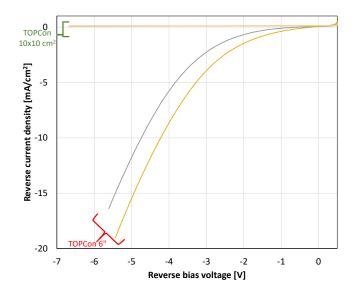

| Figure 82: Comparison of reverse leakage current of laser isolated 100 cm <sup>2</sup> cell and full area 239 cm <sup>2</sup> cell                                                                                                                                                                                                                                                                                      |

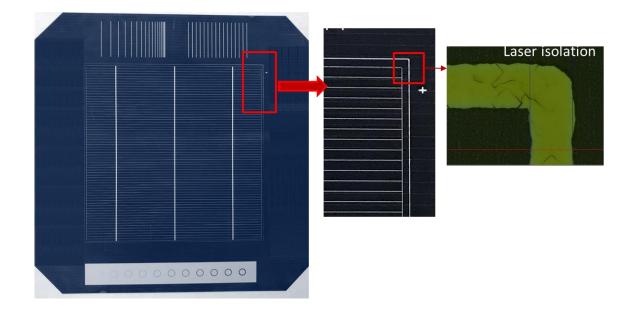

| Figure 83: Cell image of 10×10 cm on 6-inch wafer with laser isolated edge                                                                                                                                                                                                                                                                                                                                              |

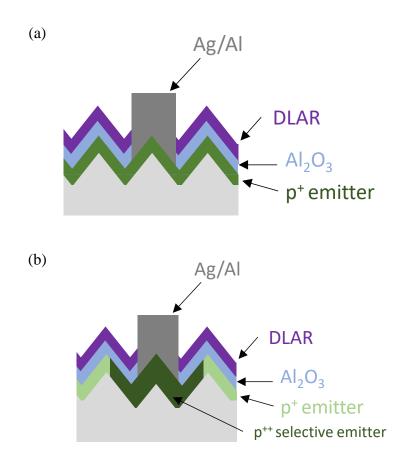

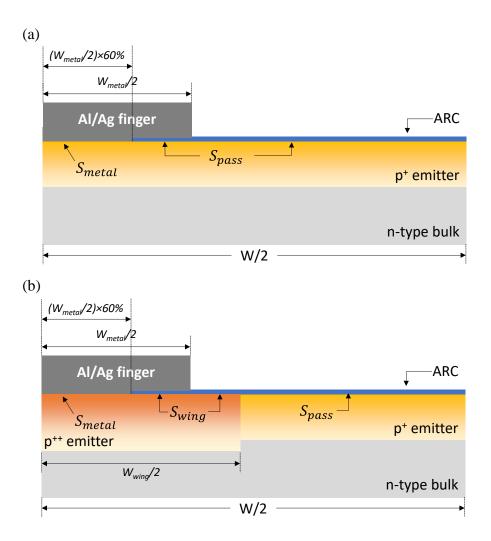

| Figure 84: Schematic diagram of (a) homogeneous emitter and (b) selective emitter 140                                                                                                                                                                                                                                                                                                                                   |

| Figure 85: Unit cells in Sentaurus Device modeling for (a) Homogeneous emitter with paste B (b) Selective B emitter with Paste B                                                                                                                                                                                                                                                                                        |

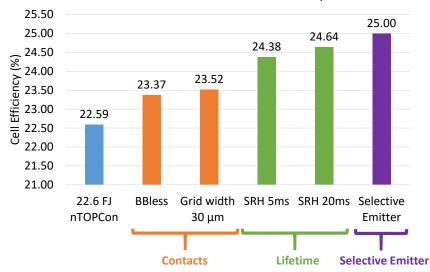

| Figure 86: Roadmap to 25.0% efficiency with single-side TOPCon on rear side 143                                                                                                                                                                                                                                                                                                                                         |

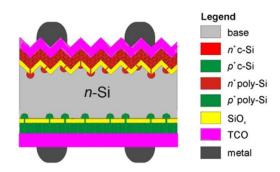

| Figure 87: Schematic drawing of a full-area double-side contacted TOPCon solar cell<br>with TCO and low-temperature Ag screen-print metallization on both sides<br>(adapted from [135])                                                                                                                                                                                                                                 |

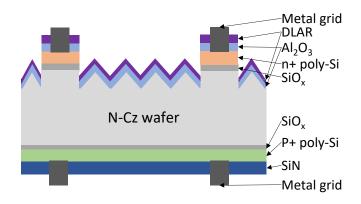

| Figure 88: Schematic diagrams of double-side TOPCon solar cell with selective area<br>TOPCon the front side                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

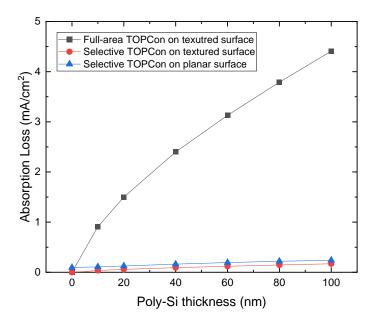

| Figure 89: Simulated absorption loss from the front poly-Si as a function of front poly-Si thickness. Selective poly-Si is simulated by assuming that 3.85% of area is covered by poly-Si and not shaded by metal contacts                                                                    |

| Figure 90: Efficiency contour map as a function of bulk resistivity and mid-gap SRH lifetime for the advanced busbarless selective TOPCon cell. The white dashed line corresponds to the optimum bulk resistivity that results in the highest cell efficiency at a given mid-gap SRH lifetime |

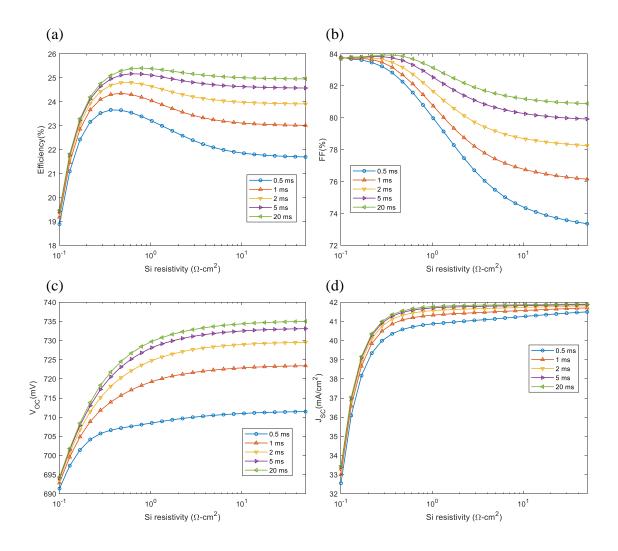

| Figure 91: Efficiency and IV data of the rear-junction advanced busbarless cell in Table I as a function of Si bulk resistivity and SRH lifetime                                                                                                                                              |

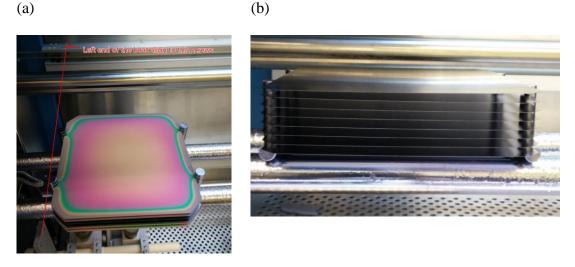

Figure 92: Photo of the quartz boat for poly-Si deposition: (a) top view (b) side view. 175

## LIST OF SYMBOLS AND ABBREVIATIONS

- a-Si Amorphous silicon

- BSF Back surface field

- BSRV Back surface recombination velocity

- CapEx Capital expenditure

- c-Si Crystalline silicon

- Cz Czochralski

- D<sub>it</sub> Interface defect density

- EQE External quantum efficiency

- FBC Front and back contact

- FF Fill factor

- FT Fire through

- FZ Float-zone

- HIT Heterojunction with intrinsic thin layer

- HREM High-resolution transmission electron microscopy

- IBC Interdigitated back contact

- iOx Interface oxide

- IQE Internal quantum efficiency

- ITO Indium-tin oxide

- iVoc Implied open-circuit voltage

- J<sub>0bulk</sub> Bulk recombination current density

- J<sub>0b</sub>, Back surface field recombination current density

- $J_{0b',metal}$   $J_{0b'}$  in the metallized rear surface areas

| т                       | т ·          | .1  | • • 1      |      | C       |       |

|-------------------------|--------------|-----|------------|------|---------|-------|

| J <sub>0b</sub> ', pass | $10b^{1}$ 1n | the | passivated | rear | surface | areas |

| • 00 ,pass              | 000 111      |     | passivatea | rour | Sanace  | aroab |

- J<sub>0e</sub> Emitter recombination current density

- $J_{0e,metal}$  J<sub>0e</sub> in the metallized emitter areas

- $J_{0e,pass}$   $J_{0e}$  in the passivated emitter areas

- J<sub>SC</sub> Short-circuit current density

- LCOE Levelized cost of energy

- LPCVD Low pressure chemical vapor deposition

- NAOS Nitric acid oxidation of silicon

- PDO Plasma deposited oxide

- PECVD Plasma-enhanced chemical vapor deposition

- PERC Passivated emitter rear cell

- PERL Passivated emitter, rear locally-doped

- Poly-Si Polycrystalline silicon

- PV Photovoltaics

- QSSPC Quasi-steady state photoconductance

- RIE Reactive ion etching

- Rs Series resistance

- R<sub>sh</sub> Shunt resistance

- SEM Scanning electron microscope

- SHJ Silicon heterojunction

- SIMS Secondary ion mass spectroscopy

- SiN<sub>x</sub> Silicon nitride

- SiO<sub>2</sub> Silicon oxide

- TCO Transparent conductive oxide

- TEM Transmission electron microscopy

- TLM Transfer length method

- TOPCon Tunnel oxide passivated contact

- Voc Open-circuit voltage

- $\Delta n$  Injection level

- $\tau$  Minority carrier lifetime

- $\tau_{eff}$  Effective minority carrier lifetime

#### SUMMARY

Since the industrial revolution, global energy consumption has been increasing rapidly, fueled by population growth, rising energy demands due to lifestyle modernization and advancements in technology. However, more than 85% of the world energy consumption is currently satisfied by fossil fuels, which has already resulted in a significant increase in carbon dioxide in the atmosphere (from < 300 ppm to > 400 ppm) and ~1 °C rise in global temperature since year 1900. The concerns about the catastrophic effects of global warming have created an urgent need for affordable clean energy technologies like photovoltaics.

Photovoltaics (PV) is one of the most promising options for sustainable and clean energy supply because it can convert virtually unlimited sunlight directly into electricity without any undesirable impact on the environment. However, PV currently accounts for only ~3.3% of the total electricity generation worldwide. Even though the cost of PV modules has decreased by more than a factor of a hundred since 1976, and PV electricity has become quite competitive with fossil fuels in many parts of the world, to make photovoltaic more competitive and widespread, the levelized cost of energy (LCOE, lifetime costs divided by energy production,  $\phi/kWh$ ) must be reduced further. This can be best achieved by increasing the solar cell efficiency while maintaining or reducing the module production cost. Even though some high-cost silicon cell technologies are approaching > 24% efficiency in mass production, more widely used (> 85%) lower-cost solar cells in production are still in the efficiency range of 19-22%. Therefore, the goal of this thesis is to explore a more advanced high-efficiency solar cell structure that can be mass-produced at low cost. The specific objective is to achieve low-cost high-efficiency (> 23%) commercial ready bifacial screen-printed n-type silicon solar cells through a combination of fundamental understanding, modeling and design, technology innovations, and complete cell fabrication. This research involves developing a technology roadmap by device modeling and simulations to achieve > 23% efficiency target followed by development and implementation of required design features such as optimized boron emitter on front and tunnel oxide passivated contact (TOPCon) on the rear side of an n-type silicon wafer, in combination with advanced fine-line screen-printing metallization with floating busbars to attain the efficiency target. Chapter 1 outlines the specific tasks to accomplish this goal along with current status, opportunities and potential growth in photovoltaics.

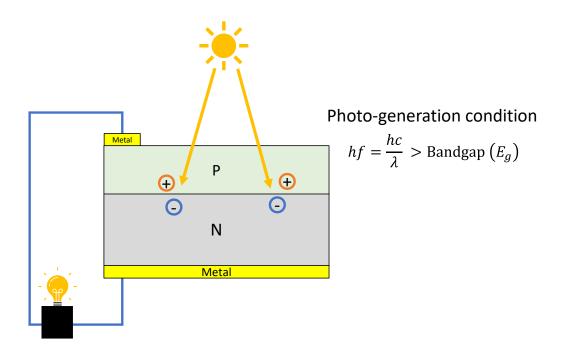

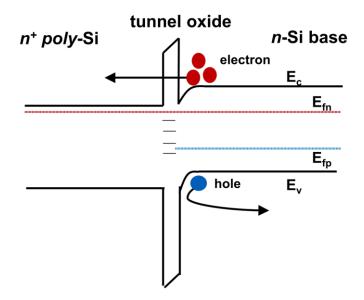

In Chapter 2 of this thesis, the physics and operating principle of silicon solar cells are reviewed along with some key material and device properties that limit its efficiency, including the recombination loss mechanisms, bulk lifetime, recombination current density (J<sub>0</sub>) in each layer of the solar cell, and quantum-mechanical tunneling in TOPCon structure, which provides excellent carrier selectivity by facilitating the transport of majority carriers while blocking the minority carriers to minimize recombination in diffused and metallized regions. Chapter 3 reviews the current status and the future trends in design and fabrication of silicon solar cells, including the literature survey related to carrier-selective passivating contacts.

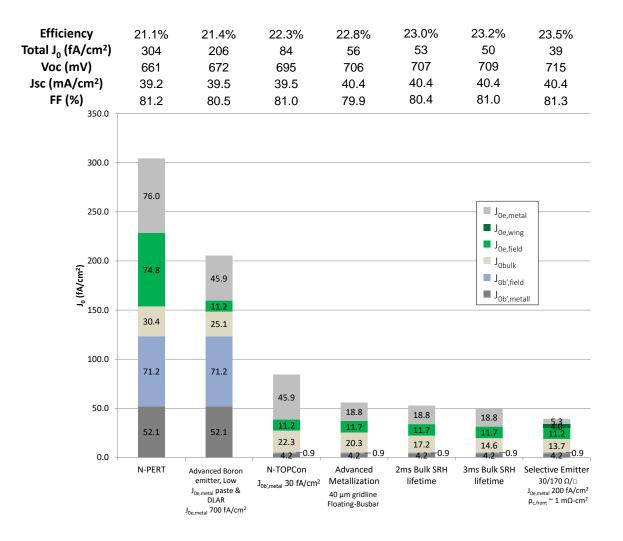

Chapter 4 deals with the development of a technology roadmap to drive the starting efficiency of a traditional 21% n-PERT (P<sup>+</sup>-N-N<sup>+</sup>) cell to 23% by transforming the cell design to n-TOPCon and establishing quantitative requirements for optoelectronic

properties of each layer or region, including B emitter, rear n-TOPCon, n-base Si, screenprinted contacts and anti-reflection coating. Extensive 2D device simulations are performed using Sentaurus and Quokka 2 models to establish a technology roadmap for the  $\geq$  23% efficiency target using practically achievable parameters. Modelling is also used to understand and mitigate the loss mechanisms in the cells fabricated throughout this research by a combination of detailed characterization and simulations. The technology roadmap in this chapter shows how single-side front junction TOPCon cells with 23% efficiency can be achieved through optimization of B emitter, appropriate bulk lifetime and resistivity, screen-printed metallization, and passivating n-TOPCon contacts on the back. The roadmap starts with characterization and modeling of an in-house fabricated 21% n-PERT cell (P<sup>+</sup>-N-N<sup>+</sup>) with a very high total  $J_0$  value of ~315 fA/cm<sup>2</sup> and 55 µm wide screenprinted grid lines. Note that total  $J_0$  is the sum of  $J_0$  contributions from each layer of the cell, including passivated and metallized B and P doped regions on front and back, as well as the  $J_0$  of the bulk wafer. Since high  $J_0$  is the major culprit for efficiency degradation, first an ion-implanted B emitter was designed by modeling, profile engineering and advanced screen-printed metallization that can reduce metallized emitter recombination current density  $J_{0e}$  from ~ 150 fA/cm<sup>2</sup> to ~ 30 fA/cm<sup>2</sup>. Next, it was shown that by replacing full area N<sup>+</sup> back surface field (BSF) in the n-PERT cell with n-TOPCon can lower the metallized rear side recombination current density  $J_{0b}$ , from ~120 fA/cm<sup>2</sup> to < 10 fA/cm<sup>2</sup>. Finally, bulk lifetime and resistivity combinations were established by modelling to minimize bulk recombination and resistive losses, followed by modeling and design of antireflection coating and front and back metal contact grid to minimize reflection and metal-induced recombination. The technology roadmap revealed that the total allowed  $J_0$

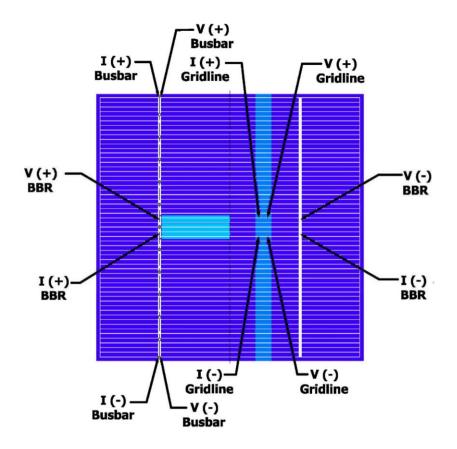

for the 23 % cell efficiency target is only ~50 fA/cm<sup>2</sup>, as opposed to 315 fA/cm<sup>2</sup> in the starting n-PERT cell, which can be achieved with optimized 170  $\Omega/\Box$  homogeneous B emitter with metallized J<sub>0e</sub> of 30 fA/cm<sup>2</sup> in combination with rear n-TOPCon with metallized J<sub>0b</sub> of 5 fA/cm<sup>2</sup> and bulk lifetime of ~2 ms (which corresponds to bulk J<sub>0b</sub> of 17 fA/cm<sup>2</sup>). In addition, grid modelling optimization revealed that we need to reduce metal-Si contact area from 6.6% to ~2.7% and contact shading to ~4.6% on the front side (B emitter) by developing fine-line screen printing (40 µm as opposed to 55 µm wide gridlines) and implementation of five floating busbars as opposed to fire-through busbars with contact resistivity of ~3 m $\Omega$ -cm<sup>2</sup>. Modelling showed that all the above design parameters can produce 23% efficient n-TOPCon cell with V<sub>OC</sub> = 707 mV, Jsc = 40.4 mA/cm<sup>2</sup> and FF = 80.4%.

Besides 2D device modeling in Chapter 4, a grid model calculator is developed in this chapter to rapidly optimize front and back metal grid designs (number, spacing, and width of fingers and busbars) to attain required series and contact resistances based on the doping and sheet resistance of B emitter and n-TOPCon. Our grid model calculator rapidly computes the optical shading, series resistance, and metal-induced recombination losses for different grid designs and also estimates cell V<sub>oC</sub>, J<sub>SC</sub>, FF, and efficiency from these loss mechanisms to establish optimum grid design for the highest cell efficiency. The calculation methodology and the accuracy of our grid model were validated with Quokka 2 model.

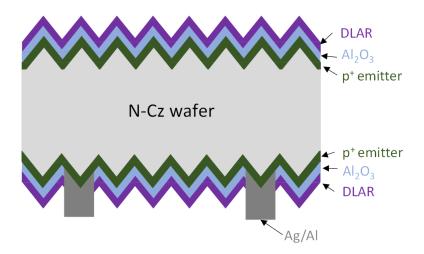

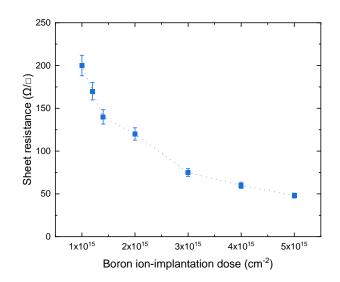

Chapter 5 deals with the experimental development of ion-implanted B emitter by optimization of doping profile, surface concentration, recombination current density, and sheet resistance. Based on the roadmap, target metallized  $J_{0e}$  was 30 fA/cm<sup>2</sup> with contact

resistivity of  $\sim 3 \text{ m}\Omega\text{-cm}^2$ . Ion-implanted emitters on textured Si surfaces were fabricated and characterized in the sheet resistance range of 48-200  $\Omega/\Box$  by tailoring the implantation dose, energy, and annealing conditions. These emitters were passivated with  $Al_2O_3$  and SiN dielectrics prior to contact formation. Nearly record low unmetallized or passivated J<sub>0</sub> values ( $J_{0e,pass} < 15 \text{ fA/cm}^2$ ) were achieved in this study for  $R_{sheet} > 140 \Omega/\Box$ . These emitters were metallized by screen-printing metal grid lines followed by rapid firing through the dielectric stack at ~770 °C. Scanning electron microscope (SEM) study and analysis of the metal/Si contact interfaces revealed that, unlike the evaporated contacts, in screen-printed contacts metal paste chemistry and firing through the dielectric can affect the emitter surface etching as well as the percentage of unetched dielectric islands under the metal contacts. It was found that this can also significantly affect the metallized  $J_0$  value of the emitter, which led to the investigation of metal pastes. Among the various Ag pastes investigated in this study, it was found that, compared to an evaporated contact, a more aggressive Paste A increased the J<sub>0e,metal</sub> by 16% due to 0.13 µm deep etching of the emitter surface. On the other hand, a gentler paste B resulted in 40 % reduction in J<sub>0e,metal</sub> due to the presence of a significant fraction of unetched or undissolved dielectric islands under the metal grid, with no appreciable emitter surface etching. This is beneficial because it is similar to the formation of local contacts through a dielectric instead of traditional full area metal contact under the grid. We were able to achieve unmetallized  $J_{0e}$  of 12 fA/cm<sup>2</sup> and metallized  $J_{0e}$  of 30 fA/cm<sup>2</sup> on 170  $\Omega/\Box$  ion-implanted B emitter with 2.7% metal-Si contact area, 4.5% metal coverage and five floating busbars using paste B. In addition, TLM measurements showed that contact resistivity was 3-5 m $\Omega$ -cm<sup>2</sup>. These parameters are entirely consistent with the requirements of our technology roadmap for 23% cells.

Chapter 6 deals with the development of tunnel oxide passivated contacts (TOPCon) on the back side of solar cells to reduce diffusion and metal-induced recombination in the absorber, which are the two major loss mechanisms in most production cells today. It is important to recognize that in a TOPCon structure, both diffused and metallized regions are physically displaced outside the absorber via a tunnel oxide, and the band bending and barrier heights are such that majority carriers can easily tunnel through the oxide but the minority carriers are blocked. This gives rise to excellent passivation of the Si surface with very low  $J_0$  due to carrier selectivity without compromising contact resistivity. Therefore, in this chapter, an n-TOPCon structure was developed by depositing phosphorus-doped poly-Si layers in a low-pressure chemical vapor deposition (LPCVD) reactor on top of a chemically grown tunnel oxide, followed by a high temperature anneal to crystallize and activate dopants in poly-Si. Due to high temperature (~775 °C) screen-printed fire-thorough contacts used in this research, thick (100-200 nm) poly-Si layers were grown to avoid metal penetration. Since LPCVD grows poly-Si on both sides, a masking process using dielectrics was developed to remove the poly-Si layer from the front side. The effects of screen-printing and firing, different metal pastes, and poly-Si thickness on the surface passivation quality were investigated to minimize the J<sub>0</sub> of the metallized and unmetallized n-TOPCon regions on the rear side. In this study, optimized n-TOPCon was formed by growing a 15 Å thick tunnel oxide in nitric acid at 100 °C on top of the n-Si absorber followed by deposition of 100-200 nm LPCVD  $n^+$  poly-Si at 588 °C, which has a mixture of amorphous and poly-Si phases. Therefore, an anneal was required to crystallize and activate dopants in the poly-Si layer to minimize J<sub>0</sub>. Optimum anneal temperature of 875 °C resulted in excellent  $J_{0,pass}$  of ~2-5 fA/cm<sup>2</sup> which

decreased further to 1-2 fA/cm<sup>2</sup> after 750 Å SiN deposition and simulated contact firing cycle without metal contacts. Next, the impact of Ag metal contacts was investigated after firing the Ag contacts through the SiN coating. This also resulted in a very low metallized  $J_0$  value of ~5 fA/cm<sup>2</sup> with 9% metal coverage on the rear side, supporting very little degradation in  $J_0$  after contact formation. Such low unmetallized and metallized  $J_0$  values are among the best reported for screen-printed contacts and are consistent with the requirements of our technology roadmap for 23% efficiency.

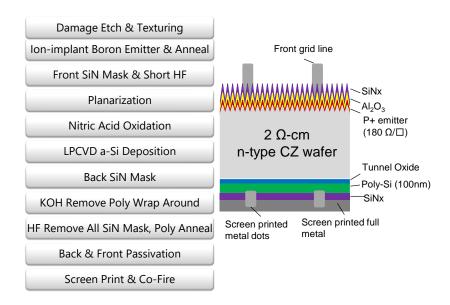

Chapter 7 involves the integration of all the promising advanced technologies developed in the above chapters to demonstrate screen-printed 23% commercial size bifacial silicon solar cells. A complete process sequence developed in this task achieved screen-printed 239 cm<sup>2</sup> n-TOPCon bifacial cells with efficiency of 22.6%. Detailed analysis showed slightly higher ideality or n-factor (~1.1) due to edge leakage effects which lowered the FF and efficiency. To eliminate the edge effects, we fabricated a 10 cm  $\times$  10 cm cell size within the 6-inch pseudo square wafer by laser isolation and modified the grid design with three busbars for the 100 cm<sup>2</sup> cells. This resulted in 22.9% efficiency, entirely consistent with our objective and technology roadmap. Note that the above cells were fabricated with homogeneous B emitters, n-Si wafers with a bulk lifetime of 1-2 ms, and fire-through grid contacts with five busbars because these were the capabilities available in the lab at the time. However, there are recent reports on the availability of better materials and contact schemes like floating multi-busbars or busbarless contacts. Therefore, based on the experimental and theoretical understanding developed in this research, a new technology roadmap was developed that shows that implementation of selective B emitter with busbarless contacts on the front and use of 5-20 ms bulk lifetime Si can push the ~23% efficiency achieved in this research closer to 25%.

In Chapter 8, a next-generation industry-compatible double-side passivated contacts solar cell structure is proposed with TOPCon on both sides. This cell structure is composed of full area p-TOPCon on the rear and selective area n-TOPCon on the front side of an n-type Si wafer. Detailed modeling using practically achievable material and device parameters shows that ~25.4% efficiency is achievable with this design using traditional screen-printing. This is because selective n-TOPCon on the front minimizes parasitic absorption and rear junction design allows the use of thicker poly under the front grid without the need for any diffusion in the field region. The undiffused field region is passivated with Al<sub>2</sub>O<sub>3</sub>/SiN coating to provide a J<sub>0</sub> comparable to TOPCon passivated Si surface without any absorption loss. Modeling reveals that this structure does not require any front diffusion because lateral conduction to the front grid takes place through Si bulk without appreciable resistive or FF loss. Because bulk material properties are very important for such a rear junction device, an efficiency contour map is generated through numerical modeling to show that a given target efficiency can be achieved by several combinations of bulk lifetime and resistivity. However, to achieve the highest efficiency for a fixed bulk lifetime, there is an optimum resistivity. For the proposed design and structure, bulk lifetime needs to be  $\geq$  3ms to achieve > 25% cell efficiency.

In summary, we have developed a cost-effective and manufacturable process sequence to fabricate high-efficiency (~23%) screen-printed n-TOPCon cells on industrialgrade n-type Cz Si wafers using commercial-ready technologies and equipment. This innovative low-cost process sequence features optimized ion-implanted emitter with advanced fine-line screen-printing metallization with five floating busbars, and n-type tunnel oxide passivated contacts fabricated by depositing phosphorus-doped LPCVD poly-Si on top of ~15 Å tunnel oxide grown by nitric acid oxidation. The n-TOPCon cells fabricated with this process achieved 22.6% efficiency on commercial-grade 239 cm<sup>2</sup> Cz silicon wafers and 22.9% efficiency on 100 cm<sup>2</sup> area, compared to 21% industrial n-PERT cell at the start of this research. Based on the fundamental understanding developed in this research, roadmaps for achieving ~25% front-junction single-side n-TOPCon cells and 25.5 % rear-junction double-side selective TOPCon cells are developed in this thesis to provide quantitative guidelines for future research on this topic.

The research in this thesis has resulted in 14 publications in peer-reviewed journals and international refereed conferences. This research was supported by the U.S. Department of Energy's Office of Energy Efficiency and Renewable Energy (EERE) under Solar Energy Technologies Office (SETO) Agreement Number DEEE0007554, DE-EE0009350, and DE-EE0008562.

## CHAPTER 1. INTRODUCTION

#### **1.1** Statement of the Problem

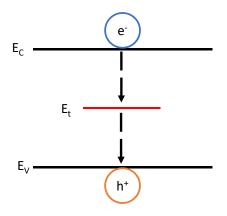

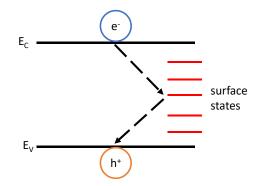

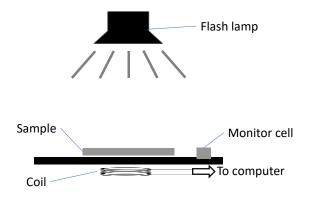

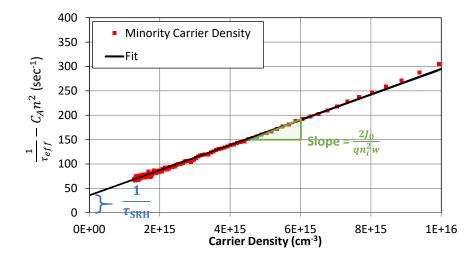

The demand for energy has been increasing rapidly since the industrial revolution in 1900, however, more than 85% of the current world energy consumption is satisfied by fossil fuels, as shown in Figure 1. This is primarily due to low cost, ease of production, and availability of fossil fuels in the past. However, fossil fuels are depleting rapidly and are known to release a significant amount of carbon dioxide (CO<sub>2</sub>) that traps heat in the atmosphere and causes global warming. This has resulted in a sharp increase in atmospheric concentration of CO<sub>2</sub> (> 400ppm) and ~1°C rise in global temperature, as shown in Figures 2 and 3. If the temperature continues to increase at this rate, it could result in catastrophic effects by 2050, including the rise in sea level, drought, floods, storm surges, and species extinction [1, 2], emphasizing the urgent need for developing and using renewable and clean source of energy to slow down the climate change.