# MODELING AND IMPLEMENTATION OF AN INTEGRATED PIXEL PROCESSING TILE FOR FOCAL PLANE SYSTEMS

A Dissertation

Presented to

The Academic Faculty

By

William Hugh Robinson, III

In Partial Fulfillment

Of the Requirements for the Degree

Doctor of Philosophy in Electrical and Computer Engineering

Georgia Institute of Technology

August 2003

Copyright © 2003 by William Hugh Robinson, III

# MODELING AND IMPLEMENTATION OF AN INTEGRATED PIXEL PROCESSING TILE FOR FOCAL PLANE SYSTEMS

Approved by:

Dr. D. Scott Wills, Advisor

Dr Jeffery A. Davis

Dr. Sung Kyu Lim

Date Approved 8-13-3003

Dedicated in loving memory to my great-grandmother, Mrs. Sallie Robinson, who instilled the value of education into her descendants, William Sr., William Jr., and William III.

#### ACKNOWLEDGEMENT

I once wrote "knowledge is the ever-flowing river that quenches the thirst of mankind's inquisitive spirit." At the time, I only referred to academic knowledge in that metaphor. However, I have learned through revelation that God's gift of salvation is the true knowledge that mankind should seek (Eph. 2:8-9). This knowledge is the living water that quenches my inquisitive spirit (John 4:10-14). Therefore, I first acknowledge my Lord and Savior Jesus Christ, who is the author and finisher of my faith (Heb. 12:2). This journey towards a Ph.D. would not have been possible without my Lord's divine providence. Let Your will be done in my life.

As my academic advisor, Dr. D. Scott Wills has directed my development as a scholar and researcher. I am truly grateful for his wisdom, enthusiasm, and support over the years. Our shared passion for education has provided a solid foundation for our friendship. I look forward to a new dynamic in our relationship as I pursue my own academic career.

I would like to thank Dr. Jeffery A. Davis and Dr. Sung Kyu Lim for serving on my dissertation reading committee. I would also like to thank Dr. Gary S. May and Dr. Umakishore Ramachandran for serving on my dissertation defense committee. Their valuable insight has considerably improved the quality of this research.

I would like to thank Dr. Donna C. Llewellyn and Dr. Mark J. T. Smith for their valuable mentorship during my time at Georgia Tech. Each has significantly contributed

towards fostering my career in academia. I am thankful for the professional development you provided.

I have also benefited from a rich research environment during my graduate years at Georgia Tech, thanks to the former and current members of the PICA Research Group. When I first joined, observing other students in the group provided an example of what was required for a Ph.D. I am proud of the tremendous research accomplishments our group has made in computer architecture design. In particular, I would like to acknowledge Dr. Sek M. Chai and Dr. Antonio Gentile for their research and collaboration in the area of focal plane processing. I also thank you for setting a high mark for both presentation skills and PowerPoint creativity.

To my immediate family, my Mom, Mrs. Mae M. Robinson, my Dad, Mr. William H. Robinson, Jr., and my sister, Ms. Elisa C. Robinson, I want to express my sincere gratitude for your loving-kindness. I am truly blessed by your influence in my life. I thank my parents for being outstanding and passionate educators. They instilled within me the desire to pursue this advanced degree. I also thank my sister for the strong friendship we have developed over the years. I look forward to celebrating your educational goals in the near future.

Although I do not have an older brother, I regard my cousin, Mr. Jonathan Lofton, in that capacity. I have always looked to him as a role model to emulate. Because of his achievements, a thirteen-year-old boy sitting in the Alexander Memorial Coliseum was inspired to attend Georgia Tech.

I would like to acknowledge Mr. Gregory E. Triplett for his friendship and research collaboration during our quest for a Ph.D. at Georgia Tech. I never would have

imagined such a fruitful relationship when we first met during freshman week at Florida Agricultural & Mechanical University (FAMU) in 1991. Our talents complement each other, which helps us both to improve.

I also would like to acknowledge Mr. Phillip A. Harp, whose friendship also began at FAMU in 1991. The transition to graduate school at Georgia Tech in 1996 was eased by starting with a close friend. I appreciate your words of encouragement during this journey towards a Ph.D.

I am grateful to the Georgia Tech Black Graduate Students Association (BGSA) for its infrastructure of unity, support, and academic guidance. I am appreciative of all the past and current members who have touched my life. In particular, I acknowledge Mr. Derrick S. Brown for his mentorship when I started graduate school. I have carried his advice until this day, and have done my best to pass along that wisdom to others.

I acknowledge "scholarship, manly deeds, and love for all mankind," which are the three aims of my fraternity, Alpha Phi Alpha Fraternity, Incorporated. This dissertation is a testament to upholding the light.

I would like to thank Rev. Craig L. Oliver, Sr., and the Elizabeth Baptist Church family for providing a spiritual home during my time in Atlanta.

Finally, I want to acknowledge my remaining family and friends too numerous to name for love, support, and prayer. I appreciate you all!

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTiv                                                       |

|-------------------------------------------------------------------------|

| TABLE OF CONTENTSvii                                                    |

| LIST OF TABLESxii                                                       |

| LIST OF FIGURESxiv                                                      |

| LIST OF SYMBOLS OR ABBREVIATIONSxvi                                     |

| SUMMARYxvii                                                             |

| CHAPTER I1                                                              |

| INTRODUCTION1                                                           |

| 1.1 Motivation                                                          |

| 1.1.1 Architecture design                                               |

| 1.1.2 System integration                                                |

| 1.1.3 Resource utilization                                              |

| 1.2 Problem Statement                                                   |

| 1.3 Related work                                                        |

| 1.3.1 Traditional architectures                                         |

| 1.3.2 Focal plane architectures4                                        |

| 1.4 Research approach                                                   |

| 1.4.1 Performance analysis of front-end image processing applications 6 |

| 1.4.2 Efficiency analysis of focal plane architectures                  |

| 1.4.3      | Statistical experimental design for photodetector modeling | 8  |

|------------|------------------------------------------------------------|----|

| 1.5 Con    | ntribution Summary                                         | 9  |

| 1.6 Dis    | sertation Outline                                          | 11 |

| CHAPTER II |                                                            | 13 |

|            | NCE ANALYSIS OF FRONT-END IMAGE PROCESSING                 | 13 |

| Summary .  |                                                            | 13 |

| 2.1 Intr   | oduction                                                   | 14 |

| 2.2 Bac    | ckground                                                   | 17 |

| 2.2.1      | Characterization of the image application suite            | 18 |

| 2.2.2      | Traditional architectural approaches                       | 19 |

| 2.2.3      | Focal plane processing approach                            | 20 |

| 2.3 Apj    | plication suite                                            | 23 |

| 2.3.1      | Median filtering                                           | 24 |

| 2.3.2      | Convolution                                                | 24 |

| 2.3.3      | Morphological processing                                   | 24 |

| 2.3.4      | Discrete Cosine Transform                                  | 25 |

| 2.3.5      | Algorithm implementation                                   | 25 |

| 2.4 Ana    | alysis                                                     | 28 |

| 2.4.1      | Focal Plane Architectural Simulator                        | 28 |

| 2.4.2      | Methodology                                                | 28 |

| 2.4.3      | System performance calculation                             | 30 |

| 2.5 Foo    | al plane processing integration                            | 31 |

| 2.5.1      | Application constraints for hardware implementation        | 31 |

| 2.5.2        | Functional unit usage percentages            | 33 |

|--------------|----------------------------------------------|----|

| 2.6 Pe       | rformance analysis                           | 38 |

| 2.6.1        | Workload characterization                    | 38 |

| 2.6.2        | Comparison with traditional DSP architecture | 40 |

| 2.7 Co       | nclusion                                     | 42 |

| CHAPTER III. |                                              | 44 |

| EFFICIENC    | Y ANALYSIS OF FOCAL PLANE ARCHITECTURES      | 44 |

| Summary      | ······································       | 44 |

| 3.1 Int      | roduction                                    | 45 |

| 3.2 Ba       | ckground                                     | 49 |

| 3.2.1        | Data acquisition                             | 50 |

| 3.2.2        | Analog-to-digital conversion                 | 52 |

| 3.2.3        | Data storage                                 | 53 |

| 3.2.4        | Digital processing                           | 53 |

| 3.3 Ap       | plication suite analysis                     | 55 |

| 3.3.1        | Focal plane architectural simulator          | 55 |

| 3.3.2        | Description of applications                  | 56 |

| 3.3.3        | Application performance                      | 58 |

| 3.3.4        | Application hardware constraints             | 61 |

| 3.4 Pro      | pjected area                                 | 62 |

| 3.4.1        | Component area models                        | 62 |

| 3.4.2        | Processing element area                      | 63 |

| 3.4.3        | Focal plane processor array area             | 68 |

|    | 3.5    | Projected power                                                 | 69 |

|----|--------|-----------------------------------------------------------------|----|

|    | 3.6    | Resource efficiency analysis                                    | 71 |

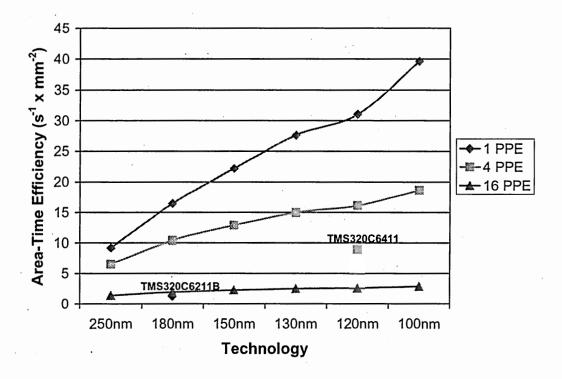

|    | 3.6    | .1 Area-time efficiency                                         | 72 |

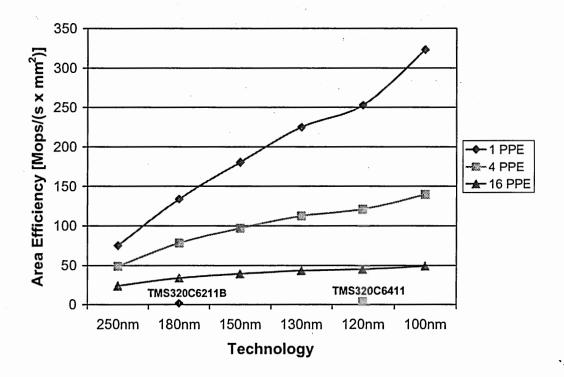

|    | 3.6    | 2 Area efficiency                                               | 73 |

|    | 3.6.   | 3 Energy efficiency                                             | 75 |

|    | 3.7    | Conclusion                                                      | 77 |

| CF | HAPTER | IV                                                              | 79 |

|    |        | TICAL EXPERIMENTAL DESIGN FOR PHOTODETECTOR JING                | 79 |

|    | Summ   | nary                                                            | 79 |

|    | 4.1    | Introduction                                                    | 80 |

|    | 4.2    | Background                                                      | 81 |

|    | 4.2.   | 1 Programmable digital pixel                                    | 82 |

|    | 4.2.   | 2 Data acquisition                                              | 83 |

|    | 4.3    | Model development                                               | 84 |

|    | 4.4    | Analysis                                                        | 87 |

|    | 4.4.   | 1 Photodiode requirements                                       | 88 |

|    | 4.4.   | 2 Diode area versus integration time                            | 88 |

|    | 4.5    | Conclusion                                                      | 91 |

| Cŀ | HAPTER | V                                                               | 93 |

|    | CONCL  | USION AND FUTURE WORK                                           | 93 |

|    | 5.1    | Contributions                                                   | 93 |

|    | 5.2    | Summary of Results                                              | 96 |

|    | 5.2.   | Performance analysis of front-end image processing applications | 96 |

| 5.2.2       | Efficiency analysis of focal plane architectures           | 97  |

|-------------|------------------------------------------------------------|-----|

| 5.2.3       | Statistical experimental design for photodetector modeling | 97  |

| 5.3 Futu    | re Research                                                | 98  |

| APPENDIX A  |                                                            | 100 |

| FOCAL PLA   | NE ARCHITECTURAL SIMULATOR                                 | 100 |

| APPENDIX B  |                                                            | 102 |

| TI DSP ARCI | HITECTURE                                                  | 102 |

| REFERENCES. |                                                            | 105 |

| VITA '      |                                                            | 112 |

# LIST OF TABLES

| Table 1: Selected early image processing applications23                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Table 2: Focal plane processor array characteristics for QCIF resolution31                                                        |

| Table 3: Application constraints for focal plane processor implementation32                                                       |

| Table 4: Application characterization for median filtering using a 10 MHz clock with Quad-CIF resolution39                        |

| Table 5: Application characterization for convolution using a 10 MHz clock with Quad-<br>CIF resolution                           |

| Table 6: Application characterization for inside edge detection using a 10 MHz clock with Quad-CIF resolution40                   |

| Table 7: Application characterization for discrete cosine transform using a 10 MHz clock with Quad-CIF resolution                 |

| Table 8: Execution time for imaging sequence using focal plane architectures41                                                    |

| Table 9: Execution time for imaging sequence using DSP architectures42                                                            |

| Table 10: Increase in sustained throughput using focal plane architecture implementations                                         |

| Table 11: Increase in area efficiency using focal plane architecture implementations 49                                           |

| Table 12: Selected early image processing applications                                                                            |

| Table 13: Total execution time for Quad-CIF focal plane architecture implementations using a 10 MHz clock                         |

| Table 14: Focal plane processor array characteristics for QCIF resolution60                                                       |

| Table 15: Application characterization for focal plane architecture implementations using a 10 MHz clock with Quad-CIF resolution |

| Table 16: Application constraints for focal plane processor implementation                                                        |

| Table 17: Area of a single processing element using 1 PPE            | 65  |

|----------------------------------------------------------------------|-----|

| Table 18: Area of a single processing element using 4 PPE            | 66  |

| Table 19: Area of a single processing element using 16 PPE           | 67  |

| Table 20: Parameter ranges for statistical experimental design       | 85  |

| Table 21: Analysis of variance (ANOVA) for photodiode parameters     | 87  |

| Table 22: SNR requirements for ADC                                   | 88  |

| Table 23: Correlation matrix for photodiode parameters               | 89  |

| Table 24: Candidate photodiode areas for different integration times | 91  |

| Table 25: TI DSP chip specifications                                 | 103 |

| Table 26: C62x <sup>™</sup> DSP Benchmarks for cycle count           | 103 |

| Table 27: C64vTM DSP Renchmarks for cycle count                      | 104 |

# LIST OF FIGURES

| Figure 1: Architectural paradigms for image processing                                            | 15 |

|---------------------------------------------------------------------------------------------------|----|

| Figure 2: Typical image processing sequence (a) processing tasks (b) examples and (amount of data |    |

| Figure 3: Programmable digital pixel                                                              | 22 |

| Figure 4: Spiral communication pattern for applications using 3 x 3 window                        | 26 |

| Figure 5: Forward transform of the all-lifting binDCT-C                                           | 27 |

| Figure 6: Methodology for application characterization                                            | 29 |

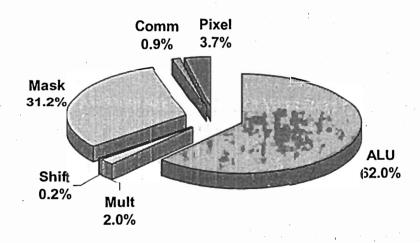

| Figure 7: Utilization of functional units for 3 x 3 window applications using 1 PPE               | 34 |

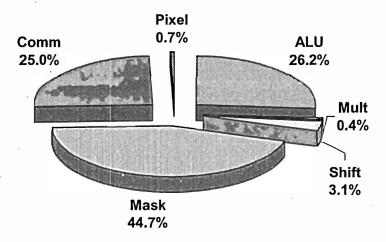

| Figure 8: Utilization of functional units for 3 x 3 window applications using 4 PPE               | 35 |

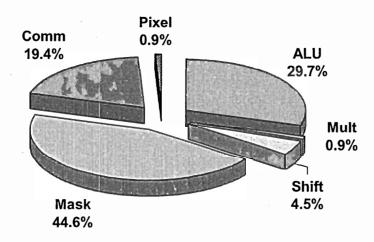

| Figure 9: Utilization of functional units for 3 x 3 window applications using 16 PPE.             | 35 |

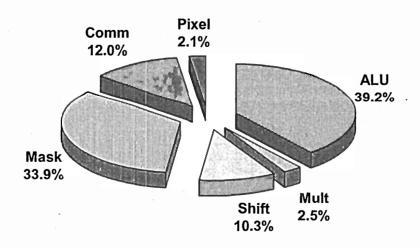

| Figure 10: Utilization of functional units for 8 x 8 window application using 1 PPE               | 36 |

| Figure 11: Utilization of functional units for 8 x 8 window application using 4 PPE               | 37 |

| Figure 12: Utilization of functional units for 8 x 8 window application using 16 PPE.             | 37 |

| Figure 13: Architectural paradigms for image processing                                           | 46 |

| Figure 14: Programmable digital pixel                                                             | 50 |

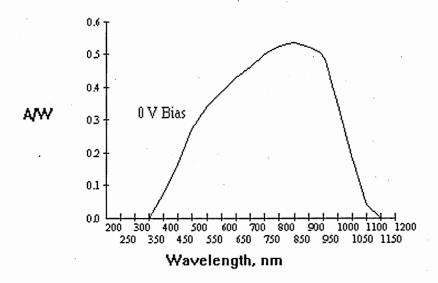

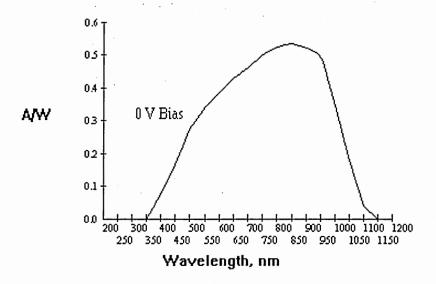

| Figure 15: Spectral response of a typical silicon photodetector                                   | 51 |

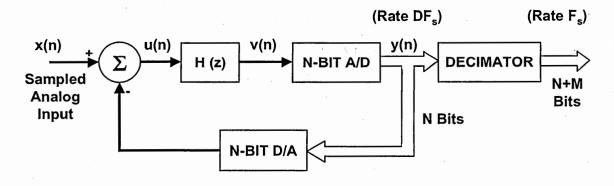

| Figure 16: Generic noise-shaping feedback loop                                                    | 52 |

| Figure 17: Typical image processing sequence (a) processing tasks (b) examples and amount of data |    |

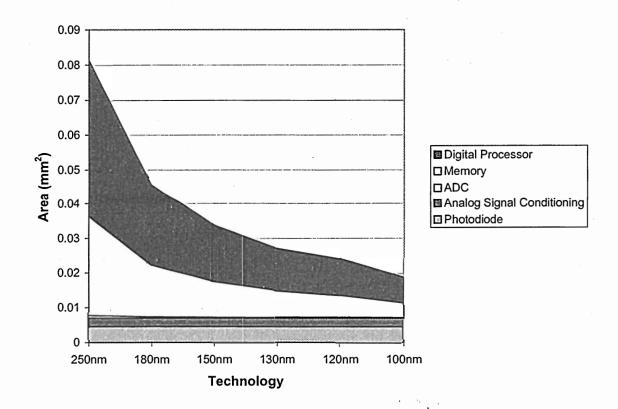

| Figure 18: Component area trend for 1 PPE with decreasing feature size                            | 65 |

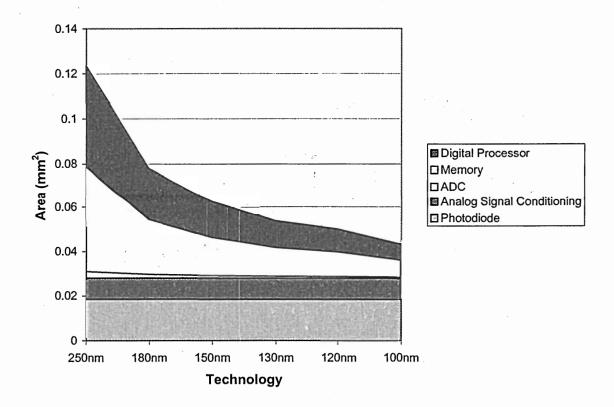

| Figure 19: Component area trend for 4 PPE with decreasing feature size                                 |

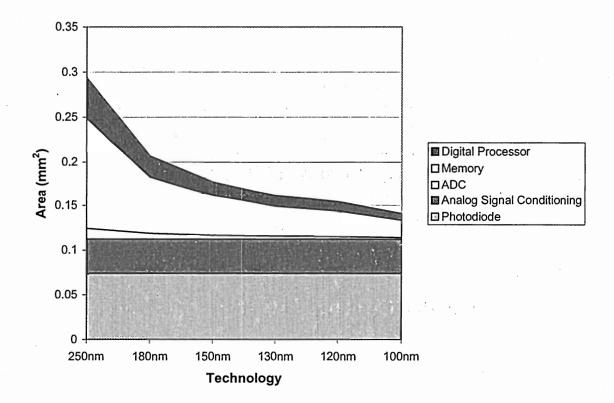

|--------------------------------------------------------------------------------------------------------|

| Figure 20: Component area trend for 16 PPE with decreasing feature size                                |

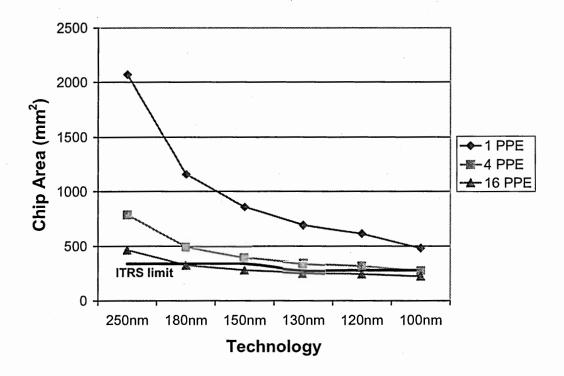

| Figure 21: Projected area for a QCIF processor array implementation                                    |

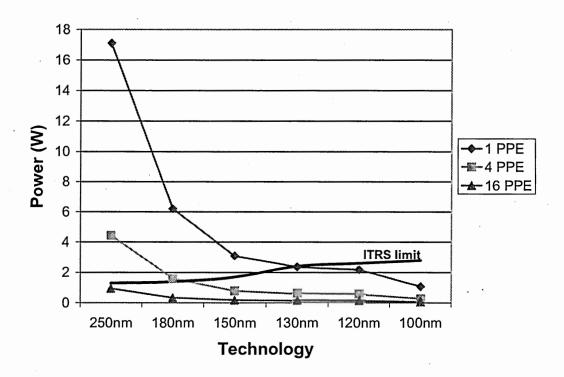

| Figure 22: Projected power for a QCIF processor array implementation using a 10 MHz clock              |

| Figure 23: Comparison of (area • time) <sup>-1</sup> efficiency for image processing architectures .73 |

| Figure 24: Comparison of area efficiency for image processing architectures75                          |

| Figure 25: Comparison of energy efficiency for image processing architectures76                        |

| Figure 26: Programmable digital pixel83                                                                |

| Figure 27: Spectral response of a typical silicon photodetector                                        |

| Figure 28: Photodiode response using area and integration time                                         |

| Figure 29: Tradeoff between area and integration time for different bit precisions90                   |

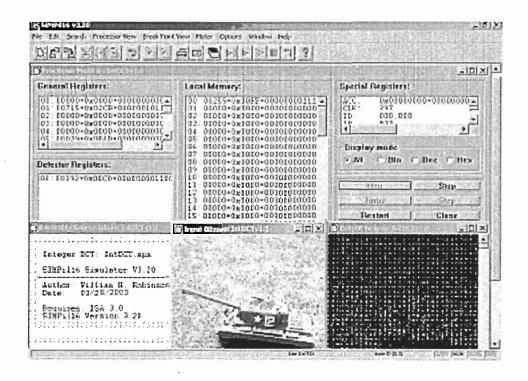

| Figure 30: A screenshot of the SIMPil Simulator during execution of the DCT application                |

## LIST OF SYMBOLS OR ABBREVIATIONS

ADC Analog-to-Digital Conversion

APS Active Pixel Sensor

CMOS Complementary Metal Oxide Semiconductor

DCT Discrete Cosine Transform

DSP Digital Signal Processor

NSIP Near Sensor Image Processing

PDA Portable Data Assistant

PE Processing Element

PPE Pixels per Processing Element

PVLSAR Programmable and Versatile Large Size Artificial Retina

S<sup>3</sup>PE Simple and Smart Sensory Processing Elements

SED Statistical Experimental Design

SIMD Single-Instruction Multiple-Data

SIMPil SIMD Pixel Processor

SNR Signal-to-Noise Ratio

TeSA Technology Scenario Analyzer

TI Texas Instruments

VLSI Very Large Scale Integration

#### **SUMMARY**

Technology improvements to monolithically integrate CMOS sensors, analog-todigital conversion circuitry, and digital processing offer the potential for a highly efficient imaging system for multimedia processing. However, this requires an understanding of the connections among applications, architecture, and technology. This dissertation presents a study of system-level design issues to develop monolithic focal plane architectures. Research contributions include workload characterization of key front-end imaging applications to determine hardware design constraints for the architecture, development of models to predict performance and efficiency of system components (photodetectors, analog-to-digital converters, data storage, and digital processing), and evaluation of design tradeoffs to improve overall system performance. The additional hardware in the focal plane architecture expands application versatility compared to current pixel-level processors. Analysis shows the focal plane architecture can deliver up to 130x the performance of a traditional DSP architecture for key front-end applications. In addition, implementations of the focal plane architecture achieve up to 81x higher area efficiency and up to 11x higher energy efficiency. These benefits are significant because front-end applications can consume over half of the required processing time, allowing that workload to be offloaded to the more efficient focal plane architecture. Further developments in computer architecture, microelectronics, and signal processing will enable low-cost, portable imaging systems.

#### **CHAPTER I**

#### INTRODUCTION

#### 1.1 Motivation

The demand for mobile productivity with image and video applications has sparked the development of highly integrated processing systems. Low-cost, embedded image processing chips appear in numerous portable products, including cellular phones, video and still cameras, and portable data assistants. These systems must deliver high performance with efficient use of resources such as area and energy. The development of these systems can leverage the abundant data parallelism in the application domain as well as improved fabrication techniques for both image sensors and integrated circuits. Key issues for future portable imaging devices include:

- Designing a suitable architecture for an imaging system

- Integrating the system components monolithically

- Utilizing the limited system resources to maintain portability

# 1.1.1 Architecture design

Numerous architectures have been developed for image processing systems using both analog and digital techniques [1-3]. Efficient handling of the two-dimensional image data is a common issue among these designs. Because of the high spatial locality of image processing applications, the Single-Instruction Multiple-Data (SIMD) [4] construct

provides a method to increase performance through data parallelism in both general-purpose processors [5] and fine-grain parallel processing arrays [6, 7]. However, new architectures must account for the increased impact of interconnect as the limiting factor in the design [8].

# 1.1.2 System integration

The monolithic integration of CMOS sensors with additional functionality can provide a system-on-a-chip solution for imaging systems [9]. The recent trend is away from the historical use of analog processing circuitry and towards digital pixels [10]. With smaller technology feature sizes, more digital circuitry can be incorporated at the sensor site for analog-to-digital conversion, data storage, and digital processing. However, technology scaling presents a challenge to CMOS imagers, and enhancements to the standard CMOS process are required to maintain image sensing [11, 12]. These modifications hold the promise to increase CMOS image sensor performance [13].

## 1.1.3 Resource utilization

Higher efficiency ratings (performance per resource) are desired for portable image processing systems because of technology limitations such as interconnect wiring density and heat extraction. Portability limits system resources such as area and power, and overall system performance is affected by design tradeoffs. Silicon area allocation is a significant issue because in single-level VLSI, the photodiode, the analog signal conditioning, the analog-to-digital converter, the memory, and the digital processing core compete for silicon area. Power consumption is also vital because the architecture must

provide a meaningful battery life. Area and energy (power) efficiency are important figures of merit in this design space [14].

# 1.2 Problem Statement

Incorporating analog and digital components to process pixels at the detection site requires an understanding of the connections among applications, architecture, and technology. The imaging application suite is a rich opportunity to design a targeted architecture that leverages the abundant data parallelism. Improvements in technology dramatically impact architecture design and implementation. The challenge is not maximum performance, but sufficiency with minimal resource cost.

## 1.3 Related work

An imaging system includes both data acquisition and data processing. Traditional architectures focus on the data processing functionality. Focal plane architectures integrate data acquisition and data processing functionality to utilize the data parallelism inherent within the image applications.

## 1.3.1 Traditional architectures

The abundant data parallelism inherent in image applications has motivated the development of multimedia extensions for general-purpose processors to improve performance on these applications. Using the Single-Instruction Multiple-Data (SIMD) processing model described by Flynn [4], these extensions supply the processor's functional units with subword data in parallel. General-purpose architectures utilizing

multimedia extensions include Intel's MMX<sup>TM</sup> [15] and SSE<sup>TM</sup> [16], Hewlett-Packard's MAX2<sup>TM</sup> for the PA-RISC<sup>TM</sup> architecture [17], Sun Microsystems' VIS<sup>TM</sup> for the SPARC [18], MIPS's MDMX<sup>TM</sup> [19], the Alpha's MVI<sup>TM</sup> [20], and Motorola's ALTIVEC<sup>TM</sup> for the PowerPC<sup>TM</sup> [21]. Alternatively, digital signal processors (DSPs) such as the TI TMS320C80 or TMS320C6000 families follow a more specialized approach [22]. However, both microprocessors and DSPs require high overhead in both area and power to execute image processing applications. In addition, the most severe limits of these architectures will not be imposed by transistors performing computing functions but by interconnection networks that perform signal communication, clock distribution, and power distribution functions [23].

# 1.3.2 Focal plane architectures

A logical approach for focal plane processing incorporates analog computational ability into the sensor device. Analog design methods, such as the Silicon Retina, have been presented to implement focal plane arrays [24]. This has led to the development of neuromorphic vision sensors for early image processing [25]. However, the advantages of analog techniques, such as low power and small area, break down as CMOS technology scales [26]. In addition, analog architectures are typically non-programmable, requiring multiple designs to implement different functionality.

Several digital architectures, such as the Near Sensor Image Processing (NSIP) [27], the Programmable and Versatile Large Size Artificial Retina (PVLSAR) [28], and the Simple and Smart Sensory Processing Elements (S<sup>3</sup>PE) [29], follow the pixel-level model to perform early image processing in the focal plane. However, these architectures

utilize bit-serial processing techniques with limited memory, which can either restrict processing to binary images or require multiple cycles to perform a single instruction on data words. This may prevent the implementation of some early image processing algorithms.

# 1.4 Research approach

The research presented in this dissertation addresses system-level design issues to monolithically integrate photodetectors, analog-to-digital converters, data storage, and digital processing into focal plane architectures. These components are combined into a single processing element that is tiled to form a SIMD focal plane processor array with nearest-neighbor communication, capable of executing front-end image applications. The outline of the approach is as follows:

- Characterize and evaluate front-end image processing applications

- Develop component models relating performance and resource usage

- Assess technology scaling for focal plane architecture implementation

- Quantify design tradeoffs in focal plane architectures

An important characteristic of the architecture is the processing granularity, also known as the number of pixels per processing element (PPE). Key performance and cost metrics for focal plane architectures include execution time, system throughput, chip area, power consumption, area-time efficiency, area efficiency, and energy efficiency.

The main task for the system level study of integrated focal plane architectures is developing the framework for interrelationships among components. Although design

expertise exists for data acquisition [30], analog-to-digital conversion [31], data storage [32], and digital architecture [33], the impact of design choices on other components is not as clear. Modeling and simulation can project the behavior of focal plane architecture implementations across technology generations.

Results will show the performance and efficiency benefits gained by integrating digital processing with data acquisition and will identify feasible design configurations and technology for implementation.

# 1.4.1 Performance analysis of front-end image processing applications

Pixel-level image processing architectures can leverage the abundant data parallelism to provide high performance embedded systems. However, sufficient hardware complexity and data storage must be available to broaden the suite of image applications.

A focal plane architectural simulator is used to determine performance metrics for convolution, discrete cosine transform (DCT), edge detection, and median filtering. Sustained throughput, measured in billion operations per second, is determined for the target system while varying the number of pixels per processing element (PPE).

The applications also have a direct impact on the physical implementation. The hardware must satisfy both the data storage and the data precision constraints to execute the applications. Also, the hardware must support the required instruction set to execute each application.

Results show the sustained throughput of the focal plane architecture exceeds the reported specification of the TI DSP chips up to 130x for 1 PPE. The execution time is

also reduced. The 1 PPE implementation operating at 10MHz executes an imaging sequence 4x faster than the TI TMS320C6411 chip operating at 300MHz. In addition, execution times from TI DSP benchmarks are dependent on the image size. Therefore they increase with larger resolutions, while the execution time of the focal plane architecture is independent of the image size. This makes the focal plane architecture an excellent candidate for an embedded processor for front-end imaging tasks.

# 1.4.2 Efficiency analysis of focal plane architectures

Future portable imaging products will benefit from the monolithic integration of photodetectors, analog-to-digital converters, digital processing, and data storage. However, the goal is not strictly building the system with the highest performance, but delivering the system with the required performance at the lowest cost.

Software tools provide a means to evaluate potential architectural configurations to determine bounds for system feasibility as well as good candidates for implementation. A focal plane architectural simulator [34] is used to determine performance metrics for median filtering, convolution, and inside edge detection, which corresponds to an imaging sequence of: (1) noise removal, (2) smoothing, and (3) segmentation. Different architecture implementations vary the number of pixels per processing element (PPE). Component area models based upon physical layout are developed to project silicon area for the architecture using different fabrication technologies. A Technology Scenario Analyzer (TeSA) [35] projects power consumption using different fabrication technologies, incorporating parameters from The International Technology Roadmap for Semiconductors [36, 37].

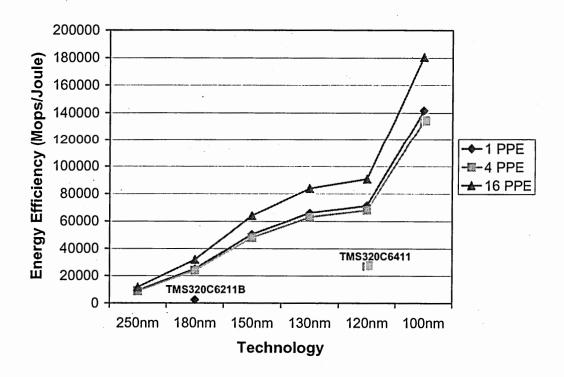

Results show that, despite a significant difference in clock frequency, implementations of the focal plane architecture perform well compared to a traditional DSP architecture while demonstrating higher ratings in area and energy efficiency across fabrication technologies. Performance is increased by 130x when using a focal plane architecture with 1 PPE. In addition, this implementation achieves 81x higher area efficiency and 11x higher energy efficiency when compared to traditional TI DSP chips. However, more aggressive technology shows diminishing returns for area and power usage, indicating that less expensive technologies can be used to implement the system. Because data acquisition and data storage have the highest cost in terms of silicon area, the architecture must address those components to be effective.

# 1.4.3 Statistical experimental design for photodetector modeling

Imaging chips are being developed that convert the image to the digital domain and process the spatially parallel data within the image plane. However, with monolithic integration, the photodetector, the analog-to-digital converter (ADC), the digital processing core, and the memory compete for silicon area. Modeling the integrated optoelectronics can provide insight for design choices.

A regression model was developed from the theoretical physical implementation of a photodiode. Key input parameters selected for designing the photodiode included the area, integration time, acceptor density, donor density, temperature, and reverse bias. A  $2^6$  full-factorial experimental design was used to explore the broad design space.

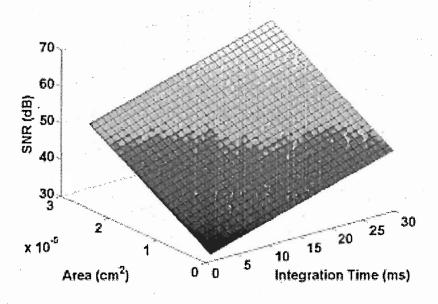

Results show that the regression model accurately depicts the behavior of the SNR response as a function of the input parameters. The two most significant factors,

photodiode area and integration time, provide a helpful design tradeoff in the context of the digital pixel. A 1ms increase in the integration time reduces the photodiode area by  $212\mu\text{m}^2$  while maintaining SNR. This relationship significantly impacts the design of a focal plane processor by trading time for limited silicon resources.

# 1.5 Contribution Summary

The contributions of this dissertation relate to the study of system-level design issues to monolithically integrate photodetectors, analog-to-digital converters, data storage, and digital processing into focal plane architectures. The contributions are outlined in three categories.

# Performance analysis of front-end image processing applications

- Workload characterization of image processing sequence

- Implemented front-end image processing application suite

- Determined data storage requirements to execute applications

- Evaluated functional units for digital pixel

- Key results from analysis

- Determined required number of register to execute selected applications equals

[(2 PPE) + 7] with a 12-bit datapath

- Data parallelism in the selected applications enables utilization exceeding 78%

- Communication cost for nearest-neighbor applications (3 x 3 window) is less than

8% while communication cost for larger windows (8 x 8) exceeds 12%

- 1 PPE implementation operating at 10MHz executes an imaging sequence 4x faster than the TI TMS320C6411 chip operating at 300MHz.

# Efficiency analysis of focal plane architectures

- Evaluation of focal plane architectures with 1 PPE, 4 PPE, and 16 PPE

- Developed component models for area projections

- Developed framework for system analysis of component models

- Projected power consumption for different technology generations

- Evaluated area-time efficiency, area efficiency, and energy efficiency of focal plane architectures

- Key results from analysis

- Sustained throughput is increased up to 130x versus TI Benchmarks using a focal plane architecture

- Focal plane architectures have up to 81x higher area efficiency and up to 11x

higher energy efficiency compared to TI DSP chips

- Area and power constraints for portability are feasible using 180nm fabrication technologies and beyond to implement a focal plane architecture

# Statistical experimental design for photodetector modeling

- Analysis of CMOS photodiode signal-to-noise ratio (SNR)

- Developed photodiode SNR performance model based upon physical implementation

- Performed statistical experimental design to create regression model

- Validated regression model using analysis of variance (ANOVA)

- Key results from analysis

- Regression model reduces complexity for determining photodiode SNR

- Significant parameters, in order of importance, are diode area, integration time, donor density, reverse bias, and then the combination of reverse bias and donor density

- Photodiode area and integration time are the most dominant parameters, with a correlation to SNR of 0.794 and 0.587 respectively

- Each 1ms increase in integration time reduces photodiode area by 212μm² while maintaining constant SNR

## 1.6 Dissertation Outline

Chapter II presents a characterization of the image application suite for focal plane architectures. A background of image processing applications and architectures is presented. The targeted application suite and the evaluation methodology are described. Performance results are provided with a comparison versus TI DSP benchmarks.

Chapter III presents the analysis of efficiency metrics for focal plane architectures. A background of image processing architectures is presented. Performance, area, and power are projected for focal plane architecture implementations. Efficiency comparisons versus TI DSP chips are provided.

Chapter IV presents the statistical experimental design for photodetector modeling to use within a mixed-signal processing element. A background of the digital pixel and image acquisition is presented. The development and validation of the model is

described. The model is analyzed and applied to the design of a photodiode to meet system constraints

Chapter V presents a summary of the dissertation with a list of contributions and key results. Future research directions are also provided.

Appendix A provides a detailed description of the focal plane architectural simulator used to evaluate front-end image applications, including software features and available metrics.

Appendix B provides a detailed description of the TI DSP chips used for comparison, including reported chip specifications and application benchmarks.

#### **CHAPTER II**

# PERFORMANCE ANALYSIS OF FRONT-END IMAGE PROCESSING APPLICATIONS

## **Summary**

Pixel-level image processing architectures can leverage the abundant data parallelism to provide high performance embedded systems. Previous pixel-level focal plane processors were limited to a small set of applications for binary images. However, the addition of sufficient data storage and key functional units, made possible with current technological improvements, expand the application functionality to operate on image formats with higher resolution. This chapter presents performance analysis of an integrated focal plane architecture for common front-end imaging applications. The focal plane architecture combines data acquisition, analog-to-digital conversion, and image processing. Using fine-grain processing of 16 pixels per processing element (PPE) or less, this system achieves performance that exceeds comparable DSP architectures on key front-end imaging applications such as convolution, DCT, edge detection, and median filtering. The 1 PPE implementation operating at 10MHz executes an imaging sequence 4x faster than the TI TMS320C6411 chip operating at 300MHz. These basic tasks can consume over half of the execution time of a typical imaging sequence. That workload can be partitioned to the focal plane architecture, leaving more complex tasks for the DSP.

# 2.1 Introduction

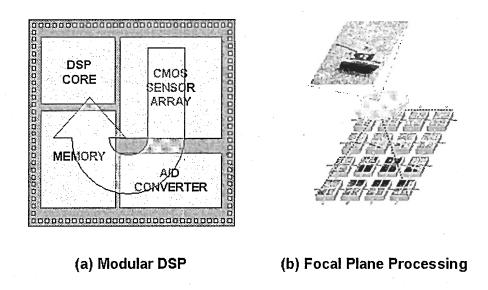

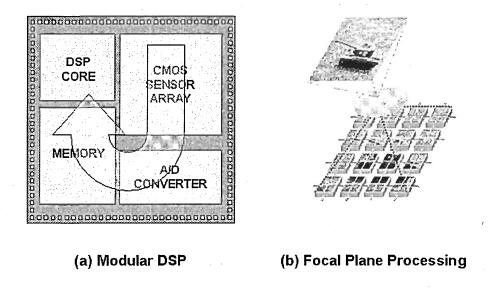

Recent emphasis has been placed upon multimedia processing to create a ubiquitous computing environment. In addition, our mobile society demands this multimedia processing be incorporated in portable devices, sparking the further development of embedded systems for real-time applications. A wide range of products, such as video and still cameras, laptop computers, and portable data assistants (PDAs), deliver multimedia processing by including inexpensive imaging chips. However, this processing creates a challenging design problem [38] and requires a change in paradigm to accommodate processing requirements [39]. Next-generation portable imaging products will benefit from the monolithic integration of photodetectors, analog-to-digital converters, digital processing, and data storage to improve their performance, efficiency, and cost. A typical system-on-a-chip digital signal processing (DSP) architecture, shown in Figure 13(a), assigns an entire image to a single processing core. This architecture is designed to span all stages of image processing. However, the DSP architecture uses a significant amount of processing to perform basic image enhancement and image analysis applications. For example, the digital image signal multiprocessor [40] reports 53% of its execution time for preprocessing and 47% for feature extraction. Preprocessing includes common tasks, such as noise reduction, smoothing, and segmentation, which are characterized by high spatial locality. Processing in the focal plane can more efficiently handle these basic tasks, leaving the more complex applications to the DSP architecture. A focal plane architecture, shown in Figure 13(b), can be built by integrating analog-todigital conversion (ADC) and digital processing at each detector site in the focal plane array.

Figure 1: Architectural paradigms for image processing

Incorporating analog and digital components to process pixels at the detection site create new design challenges [9, 41, 42], including the choice of image tasks to perform on the focal plane. Each application requires various computation, communication, and storage costs when mapped to a focal plane processor. These costs are determined by the image processing granularity, where a finer grain size translates to more pixel values external to the processing element (PE). Also, the hardware design of the processing element directly impacts the image workload. Using simple binary processing elements at each pixel severely limit the scope of the application suite and do not provide the required front-end processing capability. However, supporting an extensive Instruction Set Architecture (ISA) with infrequently used hardware may prove costly in terms of silicon area. Understanding the targeted application suite can aid architectural design choices.

This chapter presents a characterization of the image application suite for use in embedded focal plane processing systems. A Single-Instruction Multiple-Data (SIMD) focal plane architectural simulator provides dynamic workload statistics for the image application suite. A key design parameter is the number of pixels assigned to each processing element. The number of Pixels-per-Processing Element (PPE) is adjusted to determine the effect of processing granularity on the computation, communication, and storage costs for these applications.

The workload for an application suite of median filtering, convolution, inside edge detection, and the discrete cosine transform has been characterized. This application suite requires a 12-bit datapath to retain computational precision. In addition, the application suite requires at least [(2 • PPE) + 7] words of data storage to account for the original image, the final image, and processing overhead. Utilization of processing elements within the focal plane architecture ranges from 78% for the discrete cosine transform to 100% for convolution.

For the sequence of median filtering, convolution, and inside edge detection, the execution time with the focal plane architecture is reduced when compared to the conventional DSP architecture despite a 30x difference in clock frequency (10MHz for focal plane architecture, 300MHz for TMS320C6411 DSP). This benefit is for front-end applications that can consume over half of the processing time of an imaging sequence. For a Quad-CIF resolution, the focal plane architecture requires 52.5µs using 1 PPE and 195.2µs using 4 PPE. The DSP architecture requires 210.9µs. However, the DSP execution time is dependent on the image size and would increase for larger resolutions. The execution time of the focal plane architecture is independent of the image resolution.

Because of its specialized nature, this architecture would not replace a conventional DSP chip but could be used in combination as an embedded preprocessing system to perform early image applications faster and more efficiently. This would enable the DSP chip to focus on subsequent, more complex tasks of the image processing sequence. Future work includes translating the workload statistics into hardware projections using models for the analog and digital components of the pixel. These component models will quantify the silicon area tradeoffs to make the best use of available resources for overall system performance.

The organization of this chapter is as follows. Section 2.2 provides the background for applications and architectures used by image processing systems. Section 2.3 describes the application suite targeted for implementation with a focal plane processor. Section 2.4 describes the technique to characterize image application performance on a focal plane architecture. Section 2.5 presents analysis for integrating image processing in the focal plane. Section 2.6 presents performance results and compares the performance to a traditional DSP architecture. Finally, Section 2.7 concludes the discussion on workload characterization for embedded image processing applications.

# 2.2 Background

An imaging system includes both data acquisition and data processing. Image data enters the system where processing techniques convert the data into a useful format. Processing functions include image enhancement, image analysis, and image transformation. Image enhancement improves the quality of the image data. Image

analysis provides interpretation of image data. Image transformations are conversion operations applied to the image data. Each algorithm within a category requires different computation, communication, and storage costs to process each pixel of data.

Numerous architectures have been developed for image processing systems [2, 3]. Efficient handling of the two-dimensional image data is a common issue among these designs. A natural solution to this issue is to process the spatially parallel data within the image plane [43]. Both analog and digital techniques have been investigated to implement image processing functions. A monolithic system-on-a-chip with pixel-level processing is a potential solution to next-generation portable image products.

This section discusses the image application suite and presents both the traditional architectural approaches used to implement the required functionality as well as the focal plane processing approach. As an alternative, processing images in the focal plane can utilize the data parallelism inherent within the image application domain.

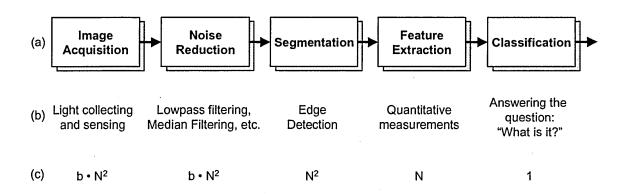

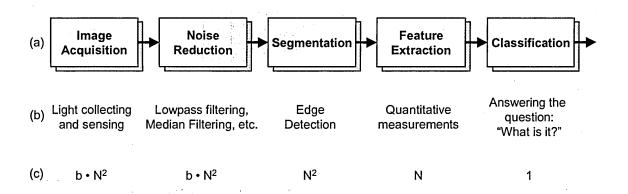

# 2.2.1 Characterization of the image application suite

Image processing applications are categorized into (1) point operations, (2) local operations, and (3) global operations [44]. A point operation such as thresholding occurs at the individual pixel level. A local operation such as smoothing requires knowledge of an individual pixel and its immediate neighbors. A global operation such as histogramming uses all pixel data from the image. These operations form the basis of applications found in imaging systems. To illustrate the processing sequence required for a typical imaging system of  $(N \times N)$  pixels, Figure 17(a) describes the processing tasks, Figure 17(b) gives example applications at each stage, and Figure 17(c) quantifies the

amount of data required for processing [45]. In Figure 17(c), the variable b represents the number of bits per pixel and N represents the image resolution on side for a square image. Point operations are the first stage, and local operations include the first three stages. The fourth and fifth stages are global feature-measuring operations [46]. The first three stages represent a significant proportion of the computational workload. For example, the digital image signal multiprocessor [40] reports 53% of its execution time for preprocessing, which includes tasks from the first three stages such as noise reduction, smoothing, and segmentation.

Figure 2: Typical image processing sequence (a) processing tasks (b) examples and (c) amount of data

# 2.2.2 Traditional architectural approaches

Image applications within the first three stages of the processing sequence exhibit high spatial locality because of the similarity in data volume. The abundant data parallelism inherent in these applications has motivated the development of multimedia extensions for general-purpose processors to improve performance on image applications. Using the Single-Instruction Multiple-Data (SIMD) processing model described by Flynn

[4], these extensions supply the processor's functional units with subword data in parallel. General-purpose architectures utilizing multimedia extensions include Intel's MMX<sup>TM</sup> [15] and SSE<sup>TM</sup> [16], Hewlett-Packard's MAX2<sup>TM</sup> for the PA-RISC<sup>TM</sup> architecture [17], Sun Microsystems' VIS<sup>TM</sup> for the SPARC [18], MIPS's MDMX<sup>TM</sup> [19], the Alpha's MVI<sup>TM</sup> [20], and Motorola's ALTIVEC<sup>TM</sup> for the PowerPC<sup>TM</sup> [21]. Alternatively, digital signal processors (DSPs) such as the TI TMS320C80 or TMS320C6000 families follow a more specialized approach [22]. However, both microprocessors and DSPs lack the computational power required to execute most media applications in real-time. In addition, the most severe limits of these architectures will not be imposed by transistors performing computing functions but by interconnection networks that perform signal communication, clock distribution, and power distribution functions [23]. Processing the image data in the focal plane can potentially address the issues of computational throughput and signal (data) communication.

# 2.2.3 Focal plane processing approach

Data acquisition occurs through an analog process using techniques such as charge-coupled devices (CCD) or active pixel sensors (APS) [47]. A logical approach for focal plane processing incorporates analog computational ability into the sensor device. Analog design methods, such as the Silicon Retina, have been presented to implement focal plane arrays [24]. This has led to the development of neuromorphic vision sensors for early image processing [25]. However, the advantages of analog techniques, such as low power and small area, break down as CMOS technology scales [26]. In addition, analog architectures are typically non-programmable, requiring multiple designs to

implement different functionality. Although analog architectures remain a viable candidate for certain focal plane processing applications, research efforts are also exploring the digital architecture design space. These programmable systems can utilize the advantages of future improvements in device fabrication.

The Single-Instruction Multiple-Data (SIMD) processing model described by Flynn [4] forms the foundation of the data parallel approach to programmable focal plane processing. Early architectures such as the Massively Parallel Processor (MPP) [48] and the Cellular Logic array Image Processor (CLIP) [49] applied this paradigm to the tasks of image processing and pattern recognition. More recently, SIMD architectures like the Connection Machine models CM-1 [50] and CM-2 [51], the MasPar [52] and the GAPP [53] have been successfully used for image processing applications. However, these designs were targeted to a more general set of applications and achieve performance with high cost, poor data bandwidth, and lack of portability. MGAP [54] and ABACUS [7] are examples of fine grain parallel processing architectures that address portability issues. However, the I/O to individual processing elements limits conventional SIMD arrays. To alleviate this problem, processing elements within the SIMD array are mapped directly to subsets of the image detector array. The granularity of data mapping ranges from column-level [42] to pixel-level [7].

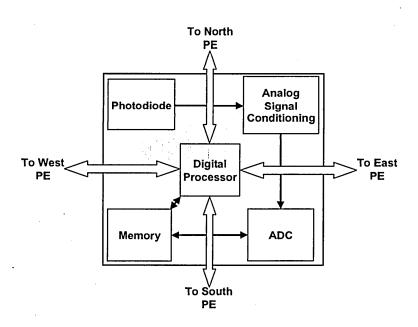

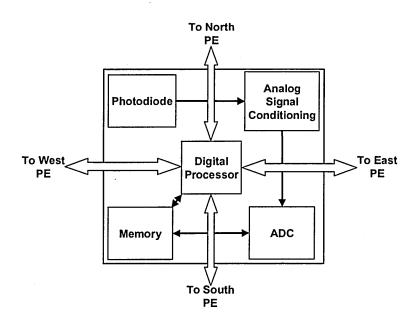

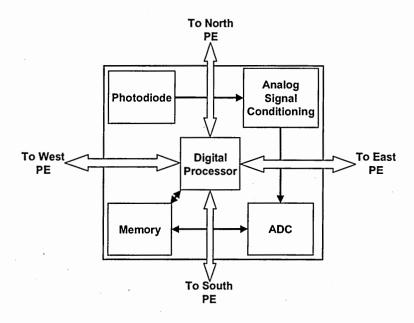

Advances in device fabrication [36] and image sensors [47] enable the development of a system-on-a-chip with pixel-level early image processing. A programmable digital pixel is formed by monolithically incorporating the sensor device, analog-to-digital conversion (ADC) circuitry, digital processing circuitry, and data storage within a processing element (PE). A block diagram of an integrated pixel-

processing tile [26] is shown in Figure 14. This tile element is replicated to form a focal plane array imager with integrated analog-to-digital conversion and SIMD processing. Research at Stanford [55, 56] has demonstrated the feasibility of pixel level ADC. Several architectures, such as the Near Sensor Image Processing (NSIP) [27], the Programmable and Versatile Large Size Artificial Retina (PVLSAR) [28], and the Simple and Smart Sensory Processing Elements (S³PE) [29], follow the pixel-level model to perform early image processing in the focal plane. However, these architectures utilize bit-serial processing techniques with limited memory, which can either restrict processing to binary images or require multiple cycles to perform a single instruction on data words. This may prevent the implementation of some early image processing algorithms. However, the integration of more data storage and functional units at the pixel level enables the versatility to execute a broader set of applications.

Figure 3: Programmable digital pixel

# 2.3 Application suite

The grayscale (8-bit) front-end applications, shown in Table 12, provide workload characteristics for image enhancement, image analysis, and image transformation in order to design the focal plane processor. The enhancement and analysis applications of median filtering, convolution, and morphological processing represent the typical early image processing sequence of: (1) noise removal, (2) smoothing, and (3) segmentation. The discrete cosine transform is a fundamental component of image compression standards such as JPEG. The workload characteristics for these applications are used to make efficient architectural choices for processing in the focal plane. This section briefly discusses each application and the algorithm implementation for a focal plane processor.

Table 1: Selected early image processing applications

| Applications                                   | Description                                                                                                          |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Image Enhancement  Median Filtering            | Removes impulse noise from an image while preserving spatial resolution.                                             |

| Convolution                                    | Performs different filtering operations, such as shadowing, smoothing, and edge-detection.                           |

| Image Analysis  Morphological  Processing      | Performs feature extraction and segmentation of binary or grayscale images such as inside edge detection.            |

| Image Transformation Discrete Cosine Transform | Exploits the spatial redundancy inherent in image data and is a fundamental component of image compression standards |

#### 2.3.1 Median filtering

Median filtering (MED) is useful to remove impulse noise from an image while preserving spatial resolution. The algorithm is a rank-order filter [57] that replaces each pixel in the image with the median value in the window. Generally, a window size is selected to generate a rank-order filter with odd length. A larger window size increases the severity of the median filtering effect [58]. The implemented algorithm performs a 2-D nonseparable rank and selects the median value for a 3 x 3 window.

#### 2.3.2 Convolution

Convolution-based filtering (CONV) has been implemented to perform different filtering operations, such as shadowing, smoothing, and edge detection [58]. The filter mask elements are broadcast one at a time to every processing element. All calculations requiring the mask element are performed before the next element is broadcast. Each PE multiplies the mask element by the corresponding pixel value from the original image and accumulates the result. Values are accumulated in a spiral pattern that places the final result in the center pixel of the filter mask. The implemented algorithm uses a 3 x 3 filter mask for the smoothing operation.

## 2.3.3 Morphological processing

Morphological image processing refers to the study of the topology or structure of objects from their 2D spatial representation [59]. Binary or grayscale images are morphologically transformed by passing a structuring element over the image in a

process similar to convolution. At each pixel position, a specified logical function is performed between the structuring element and the underlying image. For grayscale images, erosion is the minimum pixel value in the structuring element, and dilation is the maximum pixel value in the structuring element [58]. Depending upon the size and content of the structuring element, different effects such as inside edge detection (IED) can be produced from erosion and dilation operations. The implemented algorithm uses a  $3 \times 3$  structuring element to perform the morphological operations.

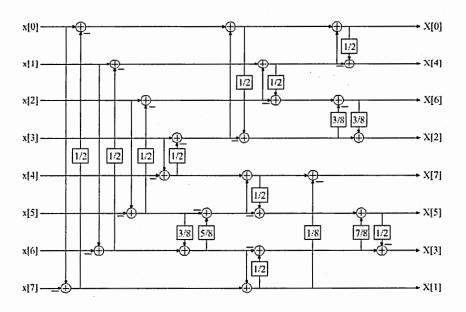

## 2.3.4 Discrete Cosine Transform

The Discrete Cosine Transform (DCT) is a transform based on the cosine kernel with resulting values mapped into the real number domain [58]. The importance of this application is particularly evident in real-time video compression and decompression, where DCT operations account for 25%-50% of CPU time without dedicated hardware support. An 8 x 8 2D-DCT has been implemented using the row-column method, in which a one-dimensional DCT is applied to the rows and then columns. The implemented algorithm maps to an integer architecture using the lifting scheme for a multiplierless transform [60].

#### 2.3.5 Algorithm implementation

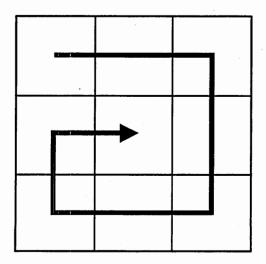

Fine-grain processing with a SIMD focal plane array requires each algorithm to be implemented in a parallel manner. Convolution and inside edge detection both compute a value for a pixel using a 3 x 3 window. A spiral communication pattern was utilized to efficiently implement these algorithms using a single pixel per processing

element (Figure 4). For convolution, the spiral pattern represented the multiply-accumulate chain for computing the center pixel value. Corresponding weights were broadcast for each multiply operation, and the accumulated value was transferred to the next pixel in the spiral. For inside edge detection, the spiral pattern represented the computation of the maximum or minimum value within the window. Each processor compares its pixel value to the transferred pixel value. The minimum is transferred for erosion, or the maximum value is transferred for dilation. For multiple pixels per processing element, the spiral communication was used only for pixels external to the processing element.

Figure 4: Spiral communication pattern for applications using 3 x 3 window

For the 3 x 3 median filtering algorithm, a novel strategy is employed. Instead of a single-pass sorting algorithm for the nine pixel values in the window, the algorithm uses a two-pass sorting routine with seven values. Any group of seven values can be sorted from minimum to maximum. Next, the remaining two values selectively replace

the second and sixth values from the sorted pixels. After the second sorting pass, the median value from the new group of seven is also the median value for the original 3 x 3 window. This implementation requires two fewer registers than the single pass sort at the cost of increased processing time. However, in the focal plane architecture design, data storage is a significant cost, while processing throughput is in abundance due to the inherent data parallelism of the application. This method also provides the minimum and maximum pixel values of the original 3 x 3 window.

The 8 x 8 discrete cosine transform is a challenge for fine-grain processing because most of the data is external to the processing element. However, the SIMD processing array can be mapped to a forward transform structure, like the multiplierless DCT approximation shown in Figure 5 [61]. Processing elements are grouped to form 8 x 8 pixel blocks. The transform is first performed for the rows. The data is then properly reordered before performing the transform on the columns.

Figure 5: Forward transform of the all-lifting binDCT-C

#### 2.4 Analysis

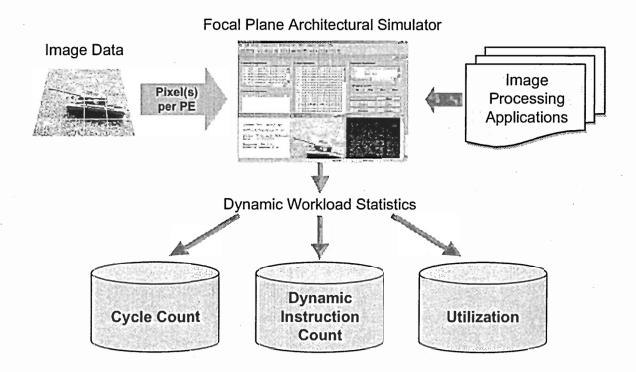

This section describes the technique to characterize image application performance. A focal plane architectural simulator is used to implement the application suite. A methodology is described that provides dynamic workload statistics from each application. The system performance is calculated using these statistics.

#### 2.4.1 Focal Plane Architectural Simulator

Applications for focal plane architectures can be programmed using the SIMD Pixel Processor (SIMPil) Simulator [34]. This software tool is a windows-based instruction level simulator, running on a PC platform. The SIMPil Simulator allows editing, assembling, executing, and debugging parallel image applications in a single integrated workbench. This tool has been used extensively to evaluate focal plane processing of multimedia applications [62]. The current version of the SIMPil Simulator is available on the download page. An extended description of the focal plane architectural simulator can be found in Appendix A.

#### 2.4.2 Methodology

The block diagram in Figure 6 illustrates the methodology for characterizing the image processing application suite. Image data is sampled by the focal plane architectural simulator based upon the preset number of pixels per processing element (PPE). The PPE is set to 1, 4 or 16. In the 4 PPE case, the pixels are arranged in a 2 x 2 pattern. In the 16 PPE case, the pixels are arranged in a 4 x 4 pattern. Each application is then executed to

determine the dynamic workload statistics. Key measurements include the cycle count, the dynamic instruction count, and the utilization. The cycle count is based upon a single instruction issued per cycle. The dynamic instruction count is the total number of parallel instructions issued to the PE array. The utilization is the average number of active processing elements. The dynamic instructions are classified by functional units to determine the relative usage of each unit within the application. The storage requirement is based upon the number of register words and the operand resolution used during execution.

Figure 6: Methodology for application characterization

## 2.4.3 System performance calculation

Performance is calculated for a target system using grayscale (8-bit) Quad-CIF (QCIF = 176 pixels x 144 pixels). The Quad-CIF resolution is one specification of the H.261 and H.263 video codec standards of the International Telecommunications Union (ITU) [63]. Using the simulator for the target system, execution time  $t_{exec}$  is computed as follows:

$$t_{exec} = \frac{C}{f_{ck}}$$

[s]

where C is the cycle count for a given application and  $f_{ck}$  is the clock frequency. The execution time is determined with reference to a 10 MHz target platform This clock frequency addresses both the speed of analog components in each processing element and power density limitations for the high utilization factor of PEs in the array. Using the execution time, the sustained throughput  $Throughput_{sust}$ , measured in billion operations per second, is determined for the target system as follows:

$$Throughput_{sust} = \frac{IC \cdot U \cdot N_{PE}}{t_{exec}} \qquad \left[\frac{Gops}{s}\right]$$

(2)

where IC is number of parallel instructions issued to the PE array during the application (i.e., the dynamic instruction count which includes both computation and communication). The system utilization U is calculated as the average number of active processing elements determined from the simulator's concurrency meter.  $N_{PE}$  is the number of processing elements in the PE array and is determined from the following formula:

$$N_{PE} = \frac{\text{system\_resolution}}{PPE}$$

(3)

where PPE is the number of pixels in each processing element (1, 4, or 16). For PPE > 1, pixels are arranged in a square (i.e. 2 x 2 or 4 x 4). The target system resolution is QCIF (176 x 144 pixels). The values for  $N_{PE}$  are shown in Table 14.

Table 2: Focal plane processor array characteristics for QCIF resolution

| PE Array Dimensions |     | Total |               |

|---------------------|-----|-------|---------------|

| PPE                 | . X | Y     | Number of PEs |

| 1                   | 176 | 144   | 25344         |

| 4                   | 88  | 72    | 6336          |

| 16                  | 44  | 36    | 1584          |

## 2.5 Focal plane processing integration

Processing in the focal plane represents a challenging design problem to integrate the data acquisition circuitry with digital processing functionality. Characterizing the targeted application workload leads to reasonable design choices for register file size, datapath width, and functional units to efficiently utilize silicon area. The hardware must satisfy both the data storage and the data precision constraints to execute the algorithms. Functional unit usage depends upon the neighborhood window size for selected applications (e.g.  $3 \times 3$ ,  $8 \times 8$ ).

## 2.5.1 Application constraints for hardware implementation

Table 16 shows the architectural design parameters for each processing element determined by the application suite. Register requirements are derived from the code for the implemented algorithm and include twice the PPE (to store the input and output

images) plus overhead for intermediate calculations. Datapath requirements are determined from the measured operand resolutions for each instruction during simulation. With an overhead of 2 registers, convolution required the fewest total registers,  $[(2 \cdot PPE) + 2]$ , but the widest datapath (12 bits) to accommodate the successive multiply-accumulates of pixel values with the corresponding 3 x 3 mask values. The discrete cosine transform also required a 12-bit datapath because of its lifting scheme with arithmetic shifts. The other applications only required the original grayscale resolution of 8 bits. Median filtering required  $[(2 \cdot PPE) + 7]$  registers to store and sort the pixels in the 3 x 3 window. A sufficient architecture capable of executing all four applications would require  $[(2 \cdot PPE) + 7]$  registers with a 12-bit datapath. These values are used to select the sizes of both the ALU datapath and the register file in each processing element.

Table 3: Application constraints for focal plane processor implementation

| Application               | Registers required | Datapath<br>required |

|---------------------------|--------------------|----------------------|

| Median Filtering          | (2 • PPE) + 7      | 8 bits               |

| Convolution               | (2 • PPE) + 2      | 12 bits              |

| Inside Edge Detection     | (2 • PPE) + 3      | 8 bits               |

| Discrete Cosine Transform | (2 • PPE) + 5      | 12 bits              |

| Full Application Suite    | (2 • PPE) + 7      | 12 bits              |

The relationship for required registers impacts the feasibility of processing integration in the focal plane. The data storage competes with other components for silicon area within the processing tile (Figure 14). In addition, the PPE should allow grouping into standard 8 x 8 blocks for processing (i.e. PPE =  $2^{2n}$  where n = 0, 1, 2, etc).

For PPE > 16, the data storage requirement becomes a prohibitive cost in terms of silicon area within the pixel tile.

## 2.5.2 Functional unit usage percentages

The usage percentages are key for determining which functional units are costeffective to include in the hardware implementation. The dynamic instruction count for

the applications in Table 12 has been categorized based upon the required functional

units: arithmetic logic unit (ALU), multiplier (MULT), shifter (SHIFT), PE activity

control unit (MASK), communication (COMM), and image loading (PIXEL). The ALU,

MULT, and SHIFT units are responsible for the computation for an application. The

MASK and COMM units are required for synchronization and data distribution among

the processing elements of the SIMD array. The processing granularity (PPE = 1, 4, or

16) combined with the application window size (3 x 3, 8 x 8) affects the distribution of

workload among the functional units.

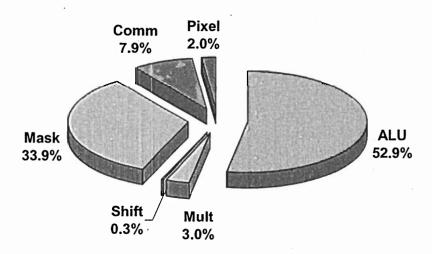

#### 2.5.2.1 Processing for 3 x 3 window

The utilization of the functional units for 1 PPE, 4 PPE, and 16 PPE implementations are shown in Figure 7, Figure 8, and Figure 9 respectively for the applications that use a 3 x 3 window (MED, CONV, IED). As the PPE increases, the communication requirement decreases because more neighborhood image data is already contained within the processing element. However, each processing element is required to compute the final values for multiple pixels, thereby increasing the percentage of ALU

instructions issued. The MASK instructions represent a significant percentage (30% - 35%) to handle the control flow in the SIMD array.

Figure 7: Utilization of functional units for 3 x 3 window applications using 1 PPE

Figure 8: Utilization of functional units for 3 x 3 window applications using 4 PPE

Figure 9: Utilization of functional units for 3 x 3 window applications using 16 PPE

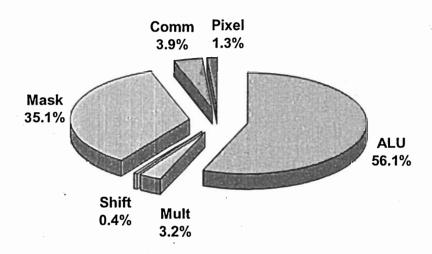

# 2.5.2.2 Processing for 8 x 8 window

Applications that extend beyond neighborhood processing will challenge a fine-grain processing architecture. For an 8 x 8 2-D discrete cosine transform, using 1 PPE represents that extreme case. The MASK and COMM units dominate the execution workload utilization (Figure 10). Because the algorithm operates on a single row in an 8 x 8 block, the MASK unit is utilized often to deactivate and activate PEs in the SIMD array. In addition, data values must be transferred along each row or column to implement the separable transform. The 4 PPE case reduces some of the COMM usage, but has similar MASK proportions as the 1 PPE case (Figure 11). However, the 16 PPE case, which uses a 4 x 4 pattern, maps well to the DCT algorithm in Figure 5. Because the processing occurs mostly in two 4 x 1 blocks, both the COMM and the MASK proportions are reduced (Figure 12).

Figure 10: Utilization of functional units for  $8 \times 8$  window application using 1 PPE

Figure 11: Utilization of functional units for 8 x 8 window application using 4 PPE

Figure 12: Utilization of functional units for 8 x 8 window application using 16 PPE

## 2.6 Performance analysis

Previous pixel-level processing architectures, such as the Programmable and Versatile Large Size Artificial Retina (PVLSAR) [28], and the Simple and Smart Sensory Processing Elements (S³PE) [29], have restricted application suites operating on binary images. However, the focal plane architecture provides a programmable environment that enables high performance on common imaging applications. The workload characterization shows that the number of pixels per processing element impacts the sustained throughput of the architecture. Yet, the architecture exceeds the reported throughput of comparable TI DSP chips. A comparison with TI DSP chips is also presented using the execution time of an imaging sequence.

## 2.6.1 Workload characterization

Using the focal plane architectural simulator, the dynamic workload has been determined for median filtering (Table 15), convolution (Table 5), inside edge detection (Table 6), and the discrete cosine transform (Table 7) for 8-bit Quad-CIF images. The maximum number of PE instructions executed equals ( $IC \cdot N_{PE}$ ). Utilizations above 90% for both convolution and inside edge detection result from local area calculations at each processing pixel. The algorithms for those two applications require little or no deactivation of PE's during processing. In contrast, median filtering and the discrete cosine transform have utilizations of approximately 80%. The median filtering algorithm involves data-dependent sorting. The discrete cosine transform algorithm requires a sequential calculation of butterfly operations within the 8 x 8 block.

The sustained throughput has been calculated using equations (1), (2), and (3) from Section 0. The sustained throughput achieved by the focal plane architecture implementations (1 PPE, 4 PPE, 16 PPE) exceeds the values achieved by a traditional DSP architecture despite a significant difference in clock frequency. For example, the throughput specification of the TI TMS320C6211B DSP chip running at 150 MHz is 1.2 Gops/s, and the throughput specification of the TI TMS320C6411 DSP chip running at 300 MHz is 2.4 Gops/s [22].

Table 4: Application characterization for median filtering using a 10 MHz clock with Quad-CIF resolution

| PPE | Execution Time (μs) | Utilization | Sustained<br>Throughput<br>(Gops/s) |

|-----|---------------------|-------------|-------------------------------------|

| 1   | 38.5                | 81.50%      | 146                                 |

| 4   | 153.1               | 81.47%      | 37                                  |

| 16  | 1353.1              | 86.73%      | 11                                  |

Table 5: Application characterization for convolution using a 10 MHz clock with Quad-CIF resolution

| PPE | Execution Time (µs) | Utilization | Sustained<br>Throughput<br>(Gops/s) |

|-----|---------------------|-------------|-------------------------------------|

| 1   | 5.6                 | 100.00%     | 204                                 |

| 4   | 18.3                | 100.00%     | 50                                  |

| 16  | 82.6                | 100.00%     | 13                                  |

Table 6: Application characterization for inside edge detection using a 10 MHz clock with Quad-CIF resolution

| PPE | Execution Time (μs) | Utilization | Sustained<br>Throughput<br>(Gops/s) |

|-----|---------------------|-------------|-------------------------------------|

| 1   | 8.4                 | 93.26%      | 166                                 |

| 4   | 23.8                | 94.41%      | 42                                  |

| 16  | 97.9                | 94.54%      | 11                                  |

Table 7: Application characterization for discrete cosine transform using a 10 MHz clock with Quad-CIF resolution

| PPE | Execution Time (μs) | Utilization | Sustained<br>Throughput<br>(Gops/s) |

|-----|---------------------|-------------|-------------------------------------|

| 1   | 39.6                | 78.16%      | 198                                 |

| 4   | 72.1                | 78.62%      | 50                                  |

| 16  | 112.1               | 78.59%      | 12                                  |

## 2.6.2 Comparison with traditional DSP architecture