# RELIABLE CLOCK AND POWER DELIVERY NETWORK DESIGN FOR THREE-DIMENSIONAL INTEGRATED CIRCUITS

A Dissertation Presented to The Academic Faculty

by

Xin Zhao

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2012

Copyright  $\bigodot$  Xin Zhao 2012

# RELIABLE CLOCK AND POWER DELIVERY NETWORK DESIGN FOR THREE-DIMENSIONAL INTEGRATED CIRCUITS

Approved by:

Dr. Sung Kyu Lim, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Saibal Mukhopadhyay School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Muhannad Bakir School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Madhavan Swaminathan School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Hyesoon Kim College of Computing Georgia Institute of Technology

Date Approved: October 12, 2012

Dedicated to my beloved family: To my parents, Deshan Zhao and Chunying Liu to my husband, Hongyi Qu and to my son, Kevin Qu for boundless love, support, and encouragement.

## ACKNOWLEDGEMENTS

I would like to express my deepest appreciation to my advisor, Professor Sung Kyu Lim for his guidance, professional advice, and support through my Ph.D. study at Georgia Tech. I would also like to express my sincere thanks to Dr. Michael R. Scheuermann from IBM T. J. Watson Research Center. I am grateful to have had the chance to learn and develop under his expert guidance. I would like to thank Professor Saibal Mukhopadhyay for numerous discussions that provide insights on my research and for serving as my proposal committee and dissertation reading committee. I thank Professor Hsien-Hsin S. Lee for providing indepth discussions on my research and serving as my proposal committee. I am thankful to Professor Muhannad Bakir, Professor Madhavan Swaminathan, and Professor Hyesoon Kim for serving as my dissertation committee and providing useful feedbacks. I am also grateful to Dr. Gabriel H. Loh.

I would like to extend my thanks to the GTCAD members (past and present) for insightful discussions, valuable comments, and friendship: Dr. Michael B. Healy, Mohit Pathak, Dr. Dae Hyun Kim, Dr. Krit Athikulwongse, Young-Joon Lee, Moongon Jung, Taigon Song, Chang Liu, Shreepad Panth, Yang Wan, Steven Zhang, Yarui Peng, Woongrae Kim, and Sandeep Samal. I would also like to thank GREEN, MARS, STING, and Epsilon members for sharing knowledge and collaborations: Dr. Jeremy R. Tolbert and Dr. Dean L. Lewis for practical discussions and close collaboration, Subho Chatterjee, Minki Cho, Amit R. Trivedi, Kwanyeob Chae, Dr. Dong Hyuk Woo, Tzu-Wei Lin, Mohammad M. Hossain, Guanhao Shen, and Jianyong Xie.

I gratefully acknowledge the support of the VLSI design team in IBM. They provided me an internship, which allowed me to broaden my knowledge in reliability issues.

I express my deepest gratitude to my beloved parents Deshan Zhao and Chunying Liu for everything they have provided me. A special word of thanks must go to my husband, Hongyi Qu, for his endless devotion and encouragement.

# TABLE OF CONTENTS

| ACKNO  | OWLEDO   | EMENTS iv                                            |

|--------|----------|------------------------------------------------------|

| LIST O | F TABLI  | ES x                                                 |

| LIST O | F FIGUI  | RES                                                  |

| LIST O | F SYMB   | OLS OR ABBREVIATIONS                                 |

| SUMMA  | ARY      |                                                      |

| СНАРТ  | ER I     | INTRODUCTION AND BACKGROUND                          |

| 1.1    | l Introd | luction                                              |

|        | 1.1.1    | Contributions                                        |

|        | 1.1.2    | Thesis Organization                                  |

| 1.5    | 2 Backg  | ground                                               |

|        | 1.2.1    | Traditional Clock Network Design                     |

|        | 1.2.2    | Clock Network Design in Three-Dimensional ICs        |

|        | 1.2.3    | Reliability Issues in TSVs                           |

|        | 1.2.4    | 3D Power Integrity Analysis for EM Reliability       |

| СНАРТ  | ER II    | LOW-POWER CLOCK NETWORK DESIGN FOR 3D ICS 12         |

| 2.1    | l Prelin | ninaries                                             |

|        | 2.1.1    | Electrical and Physical Model of 3D Clock Network 13 |

|        | 2.1.2    | Problem Formulation                                  |

| 2.2    | 2 3D Cl  | ock Tree Synthesis                                   |

|        | 2.2.1    | Overview                                             |

|        | 2.2.2    | 3D Abstract Tree Generation                          |

|        | 2.2.3    | Slew-Aware Buffering and Embedding                   |

| 2.3    | B Exten  | sion of 3D-MMM Algorithm                             |

| 2.4    | 4 Simul  | ations and Discussions                               |

|        | 2.4.1    | Simulation Settings                                  |

|        | 2.4.2    | Impact of TSV Count and Parasitic Capacitance        |

|        | 2.4.3    | Exhaustive Search Results                            |

|        | 2.4.4    | 3D-MMM-ext Algorithm Results                         |

|     |     | 2.4.5  | Low-Slew 3D Clock Routing                        | 32 |

|-----|-----|--------|--------------------------------------------------|----|

|     | 2.5 | Summ   | nary                                             | 33 |

| СНА | PTE | R III  | CLOCK NETWORK DESIGN FOR PRE-BOND TESTING OF 3D- |    |

|     | STA | CKED   | ICS                                              | 35 |

|     | 3.1 | Proble | em Formulation                                   | 36 |

|     | 3.2 | Pre-B  | ond Testable Clock Routing                       | 36 |

|     |     | 3.2.1  | Overview                                         | 36 |

|     |     | 3.2.2  | TSV-Buffer Insertion                             | 37 |

|     |     | 3.2.3  | Redundant Tree Insertion                         | 40 |

|     |     | 3.2.4  | Putting It Together                              | 41 |

|     |     | 3.2.5  | Multiple-Die Extension                           | 41 |

|     | 3.3 | Buffer | ing for Wirelength and Slew Control              | 43 |

|     | 3.4 | Exper  | imental Results                                  | 45 |

|     |     | 3.4.1  | TSV-Buffer and TG Model Validation               | 46 |

|     |     | 3.4.2  | Sample Trees                                     | 47 |

|     |     | 3.4.3  | Wirelength, Skew, and Power Results              | 48 |

|     |     | 3.4.4  | Comparison with The Single-TSV Approach          | 49 |

|     |     | 3.4.5  | Impact of TSV Bound on Power                     | 51 |

|     |     | 3.4.6  | Impact of CMAX on Power and Slew                 | 52 |

|     |     | 3.4.7  | Trend Study: Impact of TSV Bound and Capacitance | 53 |

|     | 3.5 | Summ   | ary                                              | 55 |

| CHA | PTE | R IV   | THROUGH-SILICON-VIA-INDUCED OBSTACLE-AWARE CLOCK | ζ. |

|     |     |        | THESIS FOR 3D ICS                                | 56 |

|     | 4.1 | TSV (  | Obstacle Analysis                                | 57 |

|     | 4.2 | Prelin | ninaries                                         | 59 |

|     |     | 4.2.1  | Problem Formulation                              | 59 |

|     |     | 4.2.2  | Extension of Merging Segment Concept             | 60 |

|     | 4.3 | Overv  | iew of the algorithm                             | 61 |

|     | 4.4 | Feasib | le Merging Segments                              | 62 |

|     |     | 4.4.1  | Expanded-Obstacle Cutting                        | 62 |

|     |     | 4.4.2  | Nine-Region-Based Cutting                        | 63 |

| 4    | 4.5  | TSV-C   | Obstacle-Aware Detouring                           | 65    |

|------|------|---------|----------------------------------------------------|-------|

|      |      | 4.5.1   | Routing-Obstacle-Aware Detour                      | 65    |

|      |      | 4.5.2   | Placement-Obstacle-Aware Detour                    | 66    |

| 4    | 4.6  | Clock   | TSV Merging                                        | 67    |

| 4    | 4.7  | Experi  | mental results                                     | 68    |

|      |      | 4.7.1   | Simulation Setting                                 | 68    |

|      |      | 4.7.2   | Sample TSV-Aware Clock Topology                    | 68    |

|      |      | 4.7.3   | Impact of TSV-Induced Obstacles                    | 69    |

| 4    | 4.8  | Summ    | ary                                                | 71    |

| CHAP | PTEI | R V     | TSV ARRAY UTILIZATION IN LOW-POWER 3D CLOCK NET-   |       |

| Ţ    | WOI  | RK DE   | SIGN                                               | 72    |

| Ę    | 5.1  | Introd  | uction                                             | 72    |

| Ę    | 5.2  | Clock   | Design Methodology for TSV Arrays                  | 74    |

|      |      | 5.2.1   | Problem Formulation                                | 74    |

|      |      | 5.2.2   | Overview                                           | 74    |

|      |      | 5.2.3   | Our Decision Tree                                  | 75    |

|      |      | 5.2.4   | Power Minimization with Decision Tree              | 77    |

| Ę    | 5.3  | Decisio | on-Tree-based Clock Synthesis Algorithms           | 78    |

|      |      | 5.3.1   | Decision Tree Construction Algorithm               | 78    |

|      |      | 5.3.2   | Clock Tree Construction Algorithm                  | 78    |

|      |      | 5.3.3   | Clock Tree Refinement Algorithm                    | 80    |

|      |      | 5.3.4   | Extensions                                         | 81    |

| Ę    | 5.4  | Experi  | mental Results                                     | 82    |

|      |      | 5.4.1   | Simulation Setting                                 | 82    |

|      |      | 5.4.2   | Comparison with ALG-X                              | 85    |

|      |      | 5.4.3   | Comparison with Related Work                       | 85    |

| Ę    | 5.5  | Summ    | ary                                                | 86    |

| CHAP | PTEI | R VI    | THREE-DIMENSIONAL POWER NETWORK ANALYSIS FOR ELE   | CTRO- |

| 1    | MIG  | RATIC   | N RELIABILITY                                      | 89    |

| (    | 6.1  | Curren  | at Crowding in 3D ICs                              | 90    |

|      |      | 6.1.1   | Current-Density Distribution inside a TSV $\ldots$ | 90    |

|        | 6.1.2  | TSV-Diameter-to-Wire-Thickness Ratio                                                                                          | 1 |

|--------|--------|-------------------------------------------------------------------------------------------------------------------------------|---|

|        | 6.1.3  | Impact of Current Crowding on IR Drop                                                                                         | 2 |

|        | 6.1.4  | Interface of Power Wires and TSVs                                                                                             | 3 |

| 6.2    | TSV (  | Current Crowding Model                                                                                                        | 4 |

|        | 6.2.1  | 3D Resistance Network for TSV Modeling                                                                                        | 5 |

|        | 6.2.2  | Modeling of Transition Region                                                                                                 | 6 |

|        | 6.2.3  | Modeling Accuracy                                                                                                             | 6 |

|        | 6.2.4  | Impact of XY-Mesh Size                                                                                                        | 8 |

| 6.3    | Chip-S | Scale 3D PDN Analysis                                                                                                         | 8 |

|        | 6.3.1  | Chip-Scale PDN Circuit Model                                                                                                  | 8 |

|        | 6.3.2  | Simulation Results                                                                                                            | 9 |

|        | 6.3.3  | Impact of TSV Mesh Size                                                                                                       | 2 |

|        | 6.3.4  | Impact of Power Wire Density                                                                                                  | 3 |

|        | 6.3.5  | Impact of TSV and C4 Count 103                                                                                                | 3 |

|        | 6.3.6  | Impact of TSV Diameter                                                                                                        | 4 |

|        | 6.3.7  | Impact of TSV and C4 Offset 105                                                                                               | 5 |

|        | 6.3.8  | 3D Power Integrity on Large-Scale PDNs 105                                                                                    | 5 |

| 6.4    | Summ   | ary                                                                                                                           | 6 |

| CHAPTE | R VII  | MODELING OF ATOMIC CONCENTRATION AT THE WIRE-                                                                                 |   |

| -      |        | VTERFACE                                                                                                                      | 8 |

| 7.1    | Funda  | mentals $\ldots \ldots 110$ | 0 |

|        | 7.1.1  | Mean Time To Failure                                                                                                          | 0 |

|        | 7.1.2  | Grains and Grain Boundaries                                                                                                   | 0 |

| 7.2    | Model  | ing Approach and Settings                                                                                                     | 2 |

|        | 7.2.1  | Electromigration Equations                                                                                                    | 2 |

|        | 7.2.2  | Atomic Flux and Atomic Flux Divergence                                                                                        | 3 |

|        | 7.2.3  | Effect of Activation Energy and Atomic Concentration 114                                                                      | 4 |

|        | 7.2.4  | Effect of Current                                                                                                             | 4 |

|        | 7.2.5  | Effect of Thermal and Stress                                                                                                  | 5 |

|        | 7.2.6  | Model Settings                                                                                                                | 6 |

| 7.3    | Simula | ation Flow and Assumptions                                                                                                    | 7 |

|         | 7.3.1  | Simulation Flow                            | 7   |

|---------|--------|--------------------------------------------|-----|

|         | 7.3.2  | Assumptions in This Work                   | .8  |

| 7.4     | Invest | igations on TSVs 11                        | .8  |

|         | 7.4.1  | Impact of Current Crowding                 | .8  |

|         | 7.4.2  | Impact of Current Direction and Density 12 | 22  |

|         | 7.4.3  | Impact of Temperature 12                   | 23  |

|         | 7.4.4  | Impact of Grain Size 12                    | 25  |

|         | 7.4.5  | Impact of Activation Energy 12             | 25  |

| 7.5     | Simula | ation of TSV Effective Resistance          | 26  |

|         | 7.5.1  | Resistivity Function                       | 26  |

|         | 7.5.2  | TSV Resistance Evolution                   | 27  |

|         | 7.5.3  | Adding Grains in Wires                     | 27  |

| 7.6     | Summ   | nary                                       | 80  |

| CHAPTE  | R VIII | CONCLUSIONS AND FUTURE WORKS 13            | 31  |

| 8.1     | Conclu | usions                                     | 31  |

| 8.2     | Future | e Works                                    | 3   |

| REFERE  | NCES . |                                            | \$4 |

| PUBLICA | TIONS  | 514                                        | 1   |

| VITA    |        |                                            | 15  |

# LIST OF TABLES

| Table 1  | Comparison of wirelength (um), power (mW), TSV count( $\#$ TSVs), buffer<br>count ( $\#$ Bufs), simulation runtime (s), and skew (ps) between using single<br>TSV and using multiple TSVs (3D-MMM-ext) for the two-die stacks. The<br>TSV capacitance is 15 <i>f</i> F, 50 <i>f</i> F, and 100 <i>f</i> F | 30  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2  | Comparison of wirelength (um), power (mW), TSV count ( $\#$ TSVs), buffer count ( $\#$ Bufs), simulation runtime (s), and skew (ps) between using single TSV and using multiple TSVs (3D-MMM-ext) for the six-die stacks. The TSV capacitance is 15 <i>f</i> F, 50 <i>f</i> F, and 100 <i>f</i> F         | 30  |

| Table 3  | Wirelength, clock power, and skew results for post-bond testable 3D clock trees and pre-bond testable 2D clock trees                                                                                                                                                                                      | 48  |

| Table 4  | Comparison between single-TSV and multi-TSV designs                                                                                                                                                                                                                                                       | 50  |

| Table 5  | Buffer usage between the single- and multi-TSV cases. We report the total number of buffers (#Bufs), TSV-buffers (#TBs), and clock buffers (#CBs). The number of dies is two.                                                                                                                             | 50  |

| Table 6  | Impact of CMAX $(fF)$ on skew $(ps)$ and slew $(ps)$ based on four-die stack of $r_1$ . We compare the single-TSV and the multi-TSV approaches                                                                                                                                                            | 52  |

| Table 7  | Benchmark information. Footprint area is in $\mu m^2$                                                                                                                                                                                                                                                     | 68  |

| Table 8  | Comparison of two 3D clock routing results. The first one avoids TSV obstacles by applying TSV-obstacle-aware routing; and the second one ignores TSV obstacles. We also show % increase of clock power and wirelength of TSV-obstacle-aware routing                                                      | 71  |

| Table 9  | Benchmark designs. Footprint area is in $mm \times mm$                                                                                                                                                                                                                                                    | 83  |

| Table 10 | Comparison between ALG-X and our ALG-D in power (mW) and runtime (s).                                                                                                                                                                                                                                     | 85  |

| Table 11 | Comparison among ALG-F [1], ALG-M, and our ALG-D with no TSV bound and with TSV bound. Detailed results of power (mW), wirelength $(\mu m)$ , TSV count, buffer count, and skew (ps) in no TSV bound designs are shown.                                                                                   | 88  |

| Table 12 | Impact of the TSV diameter on the current crowding. The TSV delivers $100 \text{mA}$ current, and the wire thickness is $2.0 \mu \text{m}$ .                                                                                                                                                              | 92  |

| Table 13 | Impact of current crowding on voltage drop through a TSV. The thickness of power wire varies from $1.0\mu m$ to $3.0\mu m$ .                                                                                                                                                                              | 93  |

| Table 14 | Impact of the XY-mesh size on the current density $(mA/\mu m^2)$ and the voltage drop $(mV)$                                                                                                                                                                                                              | 98  |

| Table 15 | Impact of the TSV mesh size on current density $(mA/\mu m^2)$ and IR drop $(mV)$ . The TSV diameter is 5.0 $\mu$ m. And the power grid is 16×16                                                                                                                                                           | 102 |

| Table 16 | Impact of the power wire density on current density $(mA/\mu m^2)$ and IR drop $(mV)$ . The TSV mesh size is 0.25 $\mu$ m, the TSV diameter is 5.0 $\mu$ m.                                             | 103 |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 17 | Impact of the TSV count on current density $(mA/\mu m^2)$ and IR drop $(mV)$ . The TSV diameter is 5.0 $\mu$ m, and the mesh size is 0.25 $\mu$ m                                                       | 104 |

| Table 18 | Impact of the TSV diameter ( $\mu$ m) on current density ( $mA/\mu m^2$ ) and IR drop ( $mV$ ). The power grid is 4×4, and the mesh size is 0.25 $\mu$ m                                                | 104 |

| Table 19 | Impact of TSV and C4 offset on current density $(mA/\mu m^2)$ and IR drop $(mV)$ through TSVs.                                                                                                          | 106 |

| Table 20 | Power integrity analysis for large-scale 3D PDNs including the footprint $(mm^2)$ , power density $(W/mm^2)$ , current density $(mA/\mu m^2)$ , and IR drop $(mV)$ .                                    | 107 |

| Table 21 | Notations and meanings in EM PDEs                                                                                                                                                                       | 113 |

| Table 22 | Impact of wire thickness on current density inside the TSV $(mA/um^2)$ , atomic concentration $(Atoms/m^3)$ at time=1e7(s), and MTTF (s). Initial concentration is $1.53 \times 10^{28}$ Atoms/ $m^3$ . | 122 |

# LIST OF FIGURES

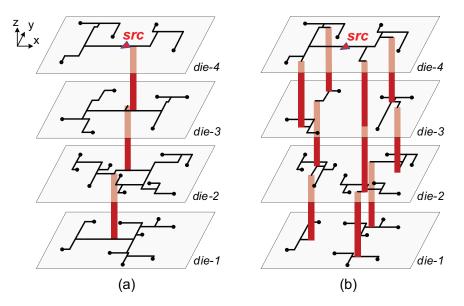

| Figure 1  | Four-die stack 3D clock networks with two different TSV counts. (a) uses single TSV between adjacent dies; (b) uses ten TSVs. The overall wirelength is shorter in (b).                                                                                                                                                                                                                                                                                                                                                                                | 12 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

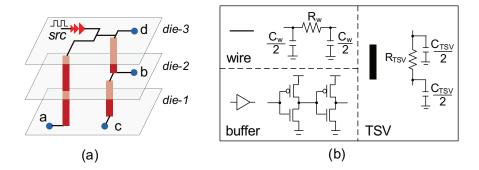

| Figure 2  | A sample clock tree and its electrical model. (a) A sample three-die clock network using four TSVs. The clock source is in die-3. Sink $a$ in die-1 uses two vertically aligned TSVs. And Sink $b$ in die-2 uses one TSV to connect to the clock source. (b) Electrical models of the clock wire segments, TSVs, and buffers/drivers                                                                                                                                                                                                                   | 14 |

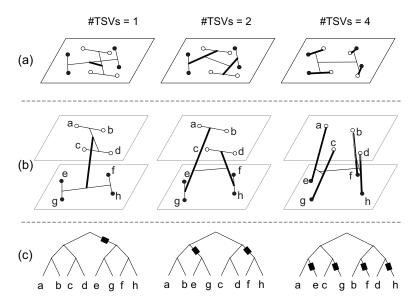

| Figure 3  | The 3D abstract trees generated by the 3D-MMM algorithm under various TSV bounds. (a) 2D view, where thick lines denote TSV connection. (b) 3D view. (c) Binary abstract trees, where the squares denote TSVs                                                                                                                                                                                                                                                                                                                                          | 16 |

| Figure 4  | Pseudo code of the 3D-MMM algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18 |

| Figure 5  | Pseudo code of the Z-cut procedure, which corresponds to Line 6 in the 3D-MMM algorithm in Figure 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19 |

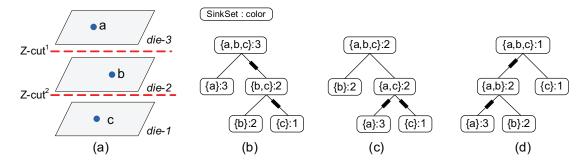

| Figure 6  | Three-colored 3D abstract trees after applying Z-cut twice on the three-<br>die-stacked Sink Set $\{a, b, c\}$ , if the clock source is located in (b) die-3,<br>(c) die-2, and (d) die-1. Each node in the abstract tree contains the<br>corresponding sink set and a color index.                                                                                                                                                                                                                                                                    | 20 |

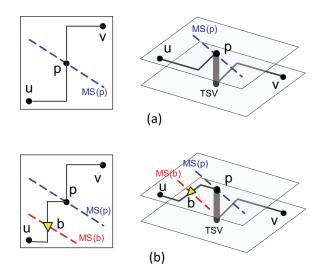

| Figure 7  | Samples of 3D merging segments for (a) an unbuffered tree and (b) a buffered tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21 |

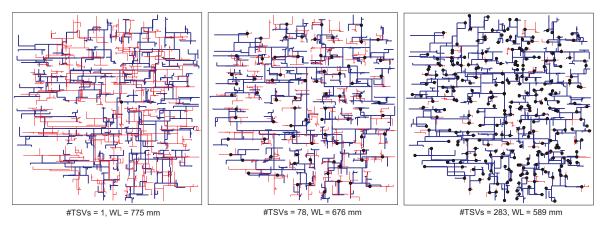

| Figure 8  | 3D clock trees for the two-die stack $r_3$ with varying TSV bounds. The black dots are the TSV location candidates. And the bold and thin lines illustrate the clock nets in die-1 and die-2, respectively                                                                                                                                                                                                                                                                                                                                             | 22 |

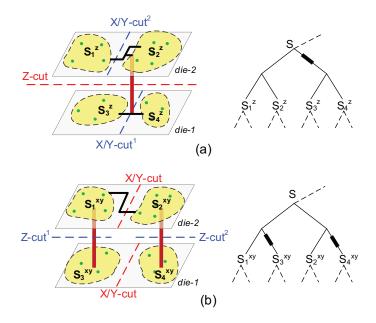

| Figure 9  | The 3D-MMM-ext algorithm performed on a two-die stack with Sink Set $S$ . We show the 3D abstract trees, cut orders, and the subsets from Case-1 and Case-2 style partitions. (a) Case-1, where we apply Z-cut at the current iteration, and then X/Y-cut <sup>1</sup> and X/Y-cut <sup>2</sup> in die-1 and die-2, respectively. (b) Case-2, where we apply X/Y-cut at the current iteration, and then Z-cut <sup>1</sup> and Z-cut <sup>2</sup> . $P_z$ and $P_{xy}$ are the cost of merging $S_i^z$ and $S_i^{xy}$ in (a) and in (b), respectively. | 24 |

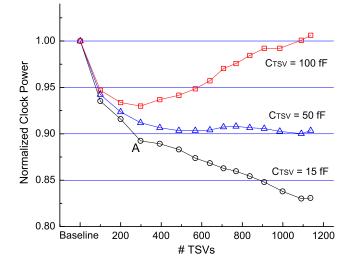

| Figure 10 | Impact of the TSV capacitance and count on clock power for the two-die $r5$ . The TSV capacitance $(C_{\text{TSV}})$ is set to 15 $f$ F, 50 $f$ F, and 100 $f$ F. Our baseline is the clock tree that uses one TSV between adjacent dies. For each $C_{\text{TSV}}$ , we show the 3D-MMM results by sweeping the TSV count. We also highlight the 3D-MMM-ext results for each $C_{\text{TSV}}$ , which are                                                                                                                                             | 07 |

|           | marked as stars near to the trends                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27 |

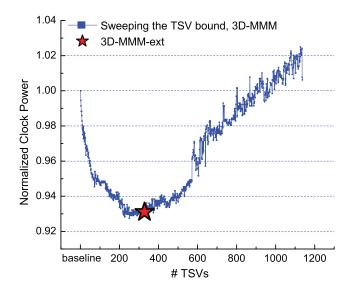

| Figure 11 | Clock power trends for the two-die stack $r_5$ based on the exhaustive search<br>within the TSV count range [1,1137]. The TSV capacitance is 100 <i>f</i> F.<br>We also plot the 3D-MMM-ext algorithm result. The exhaustive search<br>covers 1137 simulations on various clock trees. The runtime for each<br>simulation is around 200 seconds                                                                                                                                                                                    | 29 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

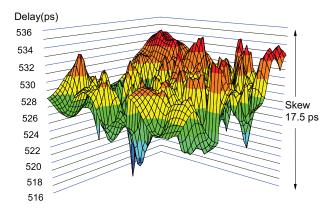

| Figure 12 | Spatial distribution of propagation delay (ps) and clock skew (ps) of the clock source die for the six-die stack $r_5$ . The TSV count is 3497                                                                                                                                                                                                                                                                                                                                                                                     | 31 |

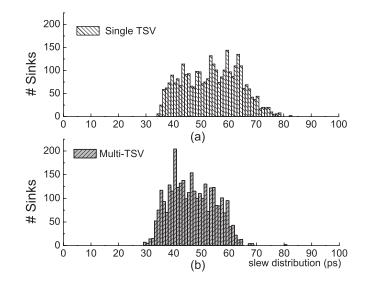

| Figure 13 | Slew distribution of six-die 3D clock network among all sinks. Slew con-<br>straint is set to 10 % of the clock period, and CMAX is 300 $fF$ . (a) Slew<br>distribution in the single-TSV clock tree, (b) in the multiple-TSV clock<br>tree                                                                                                                                                                                                                                                                                        | 32 |

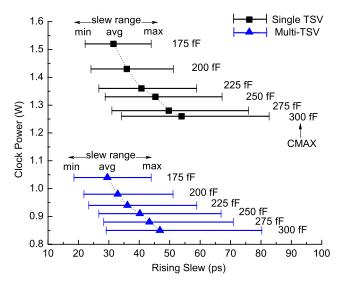

| Figure 14 | Slew variations and power comparisons between single-TSV and multiple-TSV clock trees. CMAX varies from 175 $fF$ to 300 $fF$                                                                                                                                                                                                                                                                                                                                                                                                       | 33 |

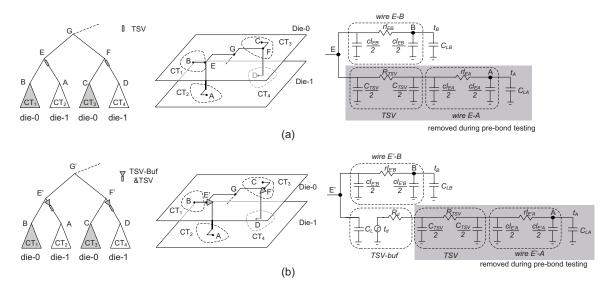

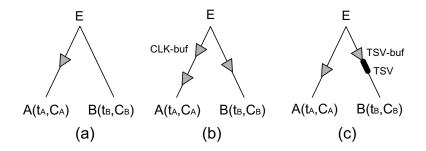

| Figure 15 | (a) A 3D clock tree built with TSVs, where the separation of die-0 and die-1 skews the tree in die-0. (b) A 3D clock tree built with TSV-buffers, where the separation of die does not skew the die-0 tree                                                                                                                                                                                                                                                                                                                         | 38 |

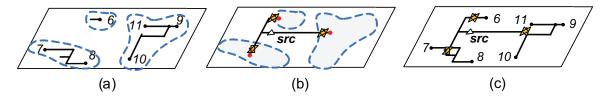

| Figure 16 | The redundant tree insertion in die-1. (a) Extract sinks from subtrees.<br>(b) Generate a redundant tree and insert transmission gates. (c) The<br>final pre-bond testable clock tree in die-1. The extra control signal that<br>connects the transmission gates is not shown here for simplicity                                                                                                                                                                                                                                  | 40 |

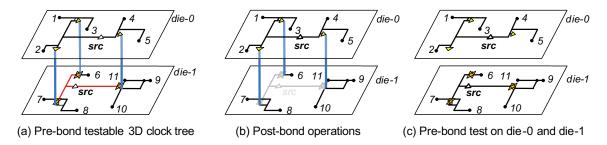

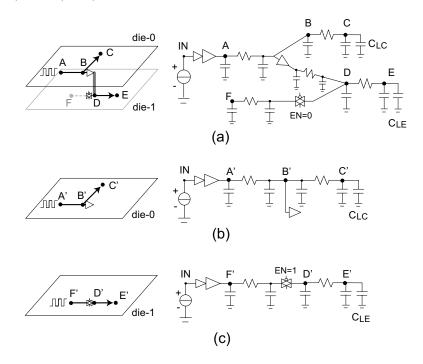

| Figure 17 | Example of the post-bond operations and pre-bond test using our 3D clock tree. (a) A pre-bond testable 3D clock tree; (b) a <i>post-3d</i> in post-bond operation with TGs turned off; (c) <i>pre-die-0</i> and <i>pre-die-1</i> in pre-bond test with TGs turned on                                                                                                                                                                                                                                                               | 41 |

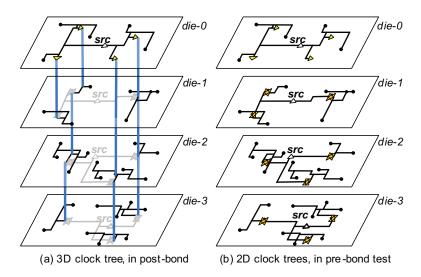

| Figure 18 | An example of a pre-bond testable clock routing in a four-die stack. $\ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42 |

| Figure 19 | Examples of the clock buffer and TSV-buffer insertion. (a) A clock buffer<br>is inserted to balance the delay of the two branches, where $t_A < t_B$ .<br>(b) Multiple clock buffers are inserted if the wires are long and/or the<br>download capacitance is large. (c) A clock buffer is inserted along with a<br>TSV-buffer to balance the delay.                                                                                                                                                                               | 45 |

| Figure 20 | Circuit models for (a) the post-bond 3D clock tree, (b) the pre-bond testable 2D clock tree in die-0, and (c) the pre-bond testable 2D clock tree in die-1                                                                                                                                                                                                                                                                                                                                                                         | 46 |

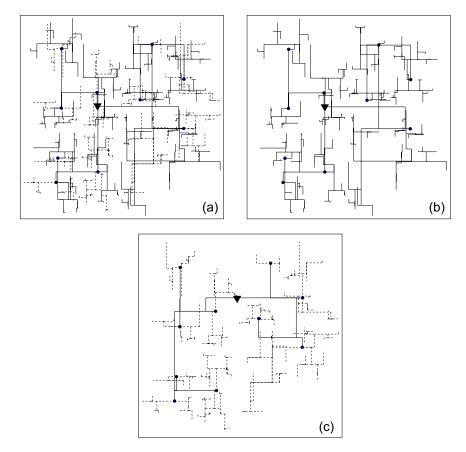

| Figure 21 | The pre-bond testable clock trees for circuit $r1$ in a two-die stack for<br>a TSV bound of 10. The TSVs and the clock sources are represented<br>by black dots and triangles, respectively. (a) The post-bond 3D clock<br>tree, where the solid and dotted lines denote the trees in die-0 and die-1,<br>respectively. (b) The pre-bond testable 2D clock tree for die-0. (c) The<br>pre-bond testable 2D clock tree for die-1, where the redundant tree and<br>the subtrees are drawn in solid and in dotted lines, respectively | 47 |

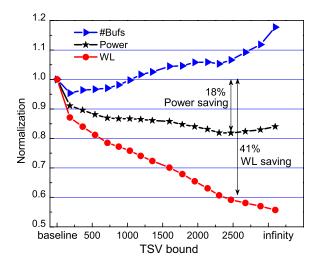

| Figure 22 | Impact of the TSV bound constraint on wirelength, buffer count, and clock power consumption based on the four-die stack of $r_5$ . The baseline is the single-TSV approach.                                                                                                                                                                                | 51 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

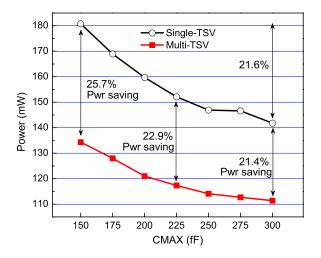

| Figure 23 | Impact of CMAX $(fF)$ on power consumption $(mW)$ based on four-die stack of $r_1$ .                                                                                                                                                                                                                                                                       | 53 |

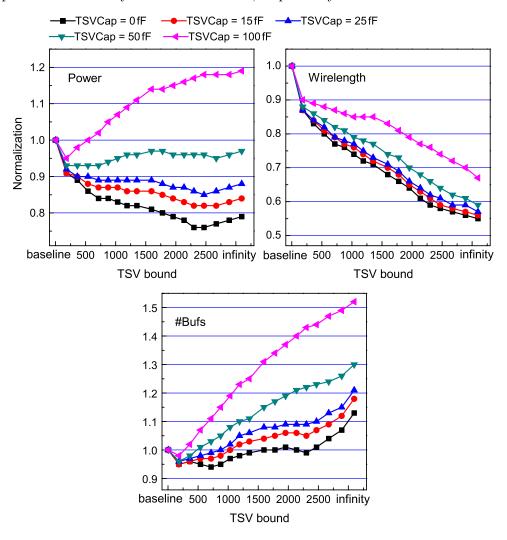

| Figure 24 | Impact of the TSV capacitance and the TSV usage on the clock power consumption, wirelength, and buffer count trends based on the four-die stack of $r_5$ . The baselines are the single-TSV clock tree for each value of the TSV capacitance.                                                                                                              | 54 |

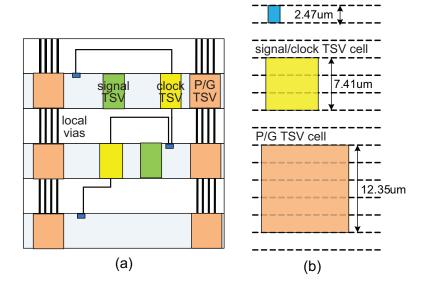

| Figure 25 | Side and top-down view of via-first power/ground (P/G) TSVs, clock TSVs and signal TSVs. (a) P/G TSVs use many local vias in between vertically, (b) size of the TSV cells (= $TSV + keep$ -out-zone) in terms of the standard cell row height (45nm technology)                                                                                           | 56 |

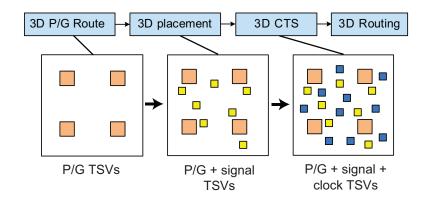

| Figure 26 | Addition of TSVs during 3D IC physical design. Note that $P/G$ and signal TSVs are added before clock routing                                                                                                                                                                                                                                              | 58 |

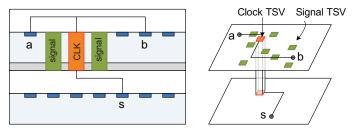

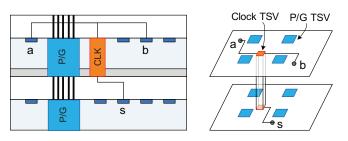

| Figure 27 | TSV-induced obstacles in 3D clock routing for Clock Sinks $a$ , $b$ and $s$ .<br>(a) signal TSVs as placement obstacles, where the clock net is allowed<br>to route over the signal TSVs, (b) P/G TSVs as placement and routing<br>obstacles, where the clock net is not allowed to route over the P/G TSVs.                                               | 59 |

| Figure 28 | TSV-obstacle avoidance in 3D clock routing. TSVs cannot overlap with each other, clock buffers cannot overlap with TSVs, and clock nets cannot route over P/G TSVs                                                                                                                                                                                         | 60 |

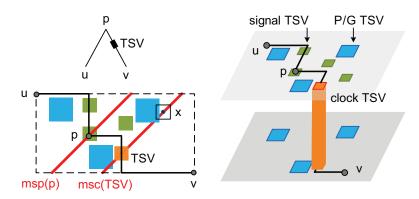

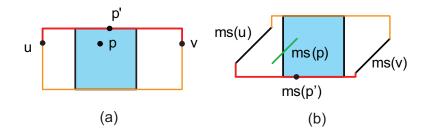

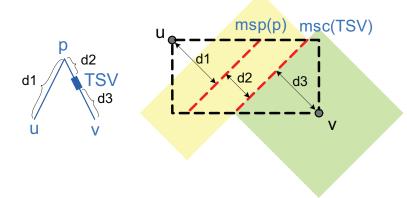

| Figure 29 | Illustration of the extended merging segment concept. When merging<br>Nodes $u$ and $v$ in different dies, $msp(p)$ denotes the merging segment of<br>Node $p$ ; $msc(TSV)$ denotes the center-point locations of the clock TSV.<br>Signal TSVs allow Node $p$ and the clock net to route over it. However,<br>clock TSV $x$ cannot overlap with a P/G TSV | 61 |

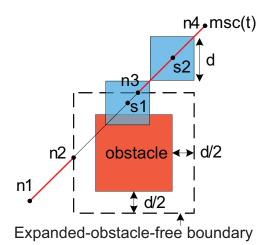

| Figure 30 | Expanded-Obstacle Cutting on a merging segment $msc(t)$ . The expanded-<br>overlap-free boundary determines that Segments $n1-n2$ and $n3-n4$ are the<br>feasible merging segments. A clock TSV with $s1$ as the center will cause<br>an overlap with the obstacle, whereas inserting the TSV with its center<br>on $s2$ is safe.                          | 63 |

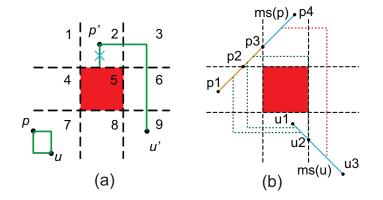

| Figure 31 | Nine-Region-Based Cutting method. (a) Nine regions partitioned by a routing obstacle in red. $p$ to $u$ is HV and VH connectable, and $p'$ to $u'$ is HV only. (b) $(p1, p2)$ and $(p2, p3)$ are the routing-overlap-free merging segment of $ms(p)$ to its child $ms(u)$ , $(p3, p4)$ is not due to the shortest distance constraint.                     | 64 |

| Figure 32 | Detour policy when a routing-obstacle blocks the routing region. (a) merging segment for $u$ and $v$ are points, where the top (= red) detour is chosen over the bottom (= orange), (b) merging segments for $u$ and $v$ are lines, where the bottom (= red) detour is chosen.                                                                             | 65 |

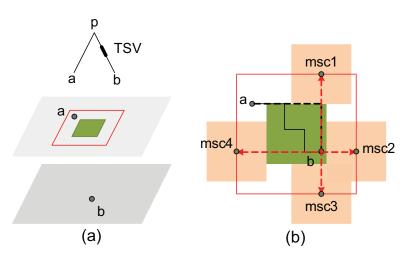

| Figure 33 | Placement-obstacle-aware detour for TSV merging. A signal TSV occu-<br>pies the merging area between Nodes $a$ and $b$ where a TSV is needed. A<br>feasible merging segment for this clock TSV is added on the expanded-<br>overlap-free boundary with the shortest merging distance. $msc1-msc4$<br>show four candidates. We choose $msc2$ due to its shortest distance to $b$ .           | 66 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 34 | Finding the longest feasible merging segment for the clock TSV by sweeping the distance between clock TSV and $ms(v)$ .                                                                                                                                                                                                                                                                     | 67 |

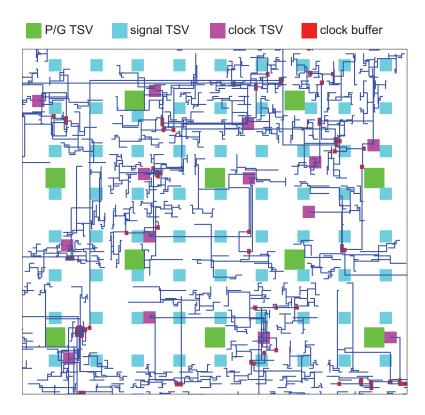

| Figure 35 | A two-die stack clock routing WITHOUT considering TSV obstacles. We show P/G TSVs (green), signal TSVs (blue), clock TSVs (red), clock wires, and clock buffers (red). This tree violates several overlapping constraints, including clock TSVs overlap with other P/G TSVs, signal TSVs, and buffers, and routing over P/G TSVs.                                                           | 69 |

| Figure 36 | A two-die stack clock tree WITH TSV obstacle avoidance for the same circuit as Figure 35. This tree does not contain any illegal overlap. $\ldots$                                                                                                                                                                                                                                          | 70 |

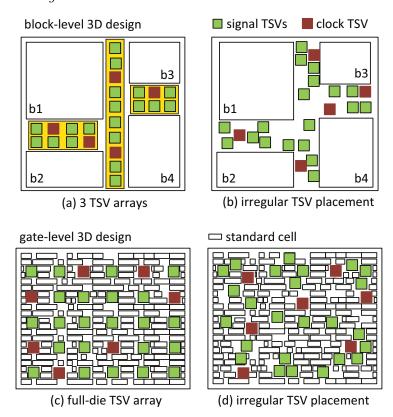

| Figure 37 | TSVs at regular locations (TSV arrays) vs. irregular locations in block-<br>level and gate-level 3D designs                                                                                                                                                                                                                                                                                 | 73 |

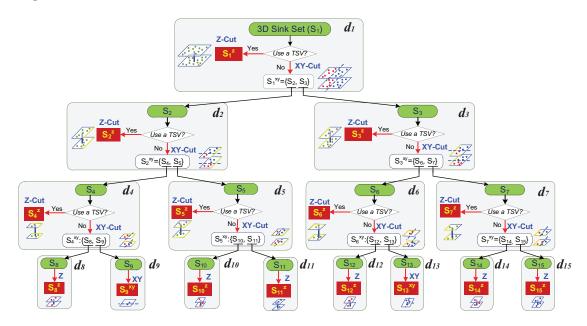

| Figure 38 | Illustration of our decision tree that shows the entire solution space of TSV array usage for low power. Each node (except leaf nodes) can choose between using one TSV (= Z-cut) or multiple TSVs (= XY-cut) in the array. Once the entire decision tree is built, we obtain different 3D clock trees by visiting all possible sink-to-root paths during our clock tree construction step. | 75 |

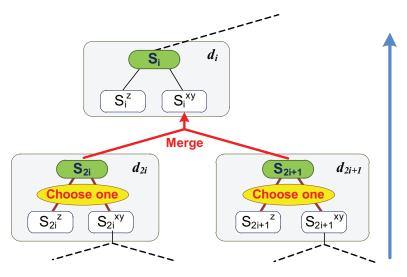

| Figure 39 | Bottom-up merging for node $d_i$ , where we decide (1) clock tree and its power value for $d_i$ for XY-cut (= $S_i^{XY}$ ), and (2) cut orientations for its children $d_{2i}$ and $d_{2i+1}$ .                                                                                                                                                                                             | 79 |

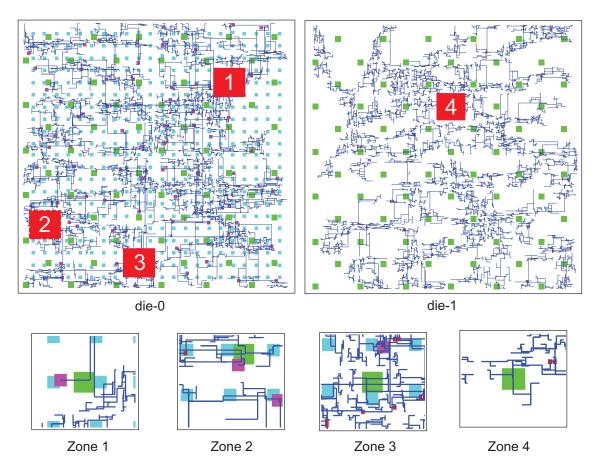

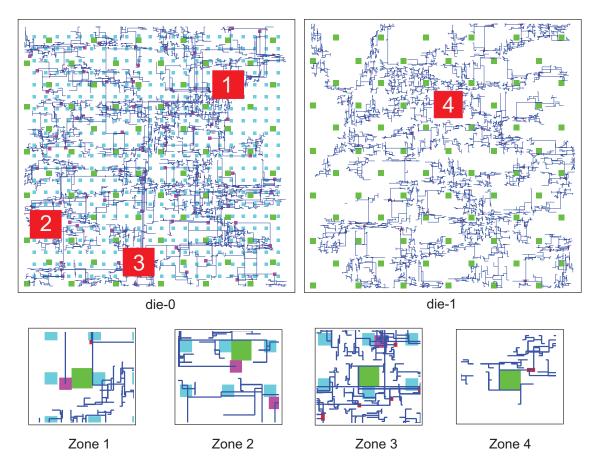

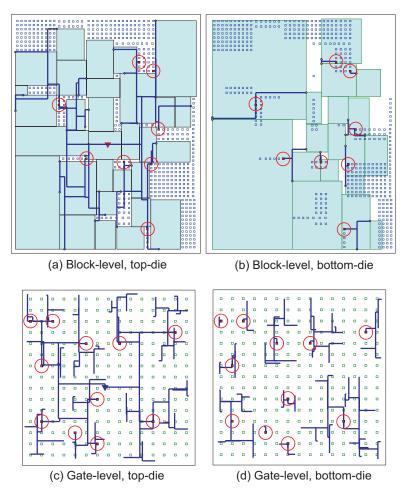

| Figure 40 | Clock trees generated by our ALG-D using TSV arrays. We show 3D clock trees for block-level ckt8 ((a) and (b)) and a gate-level ckt ((c) and (d)) in top- and bottom-die, respectively. TSV arrays are denoted as squares. Clock TSVs are shown in red circles.                                                                                                                             | 84 |

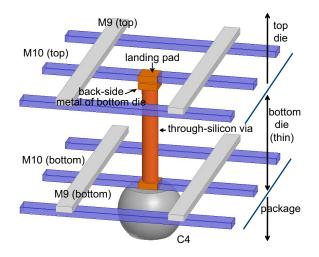

| Figure 41 | 3D connection in a global power-delivery network.                                                                                                                                                                                                                                                                                                                                           | 90 |

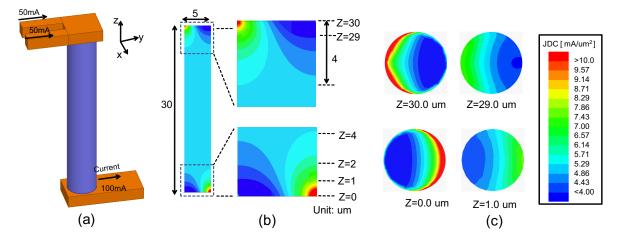

| Figure 42 | Current crowding in the test case of a TSV and power wires (a). The current-density distribution is shown in a ZY plane (b) and in top-down XY planes (c).                                                                                                                                                                                                                                  | 90 |

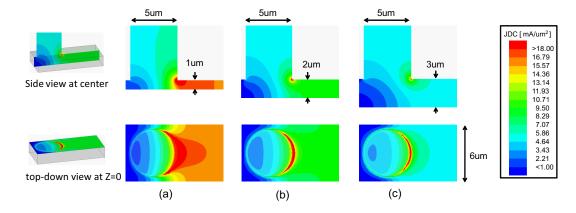

| Figure 43 | The ratio of the TSV diameter to the wire thickness affects the current crowding at the connection corner. The TSV diameter is set to $5.0\mu m$ , and the power thickness is $1.0\mu m$ (a), $2.0\mu m$ (b), and $3.0\mu m$ (c)                                                                                                                                                            | 92 |

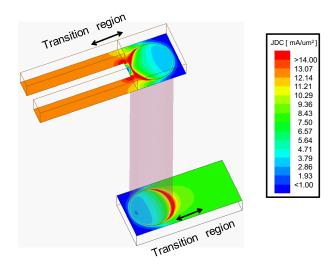

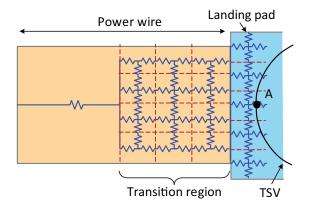

| Figure 44 | Current crowding in the transition region between power wires and TSVs.                                                                                                                                                                                                                                                                                                                     | 93 |

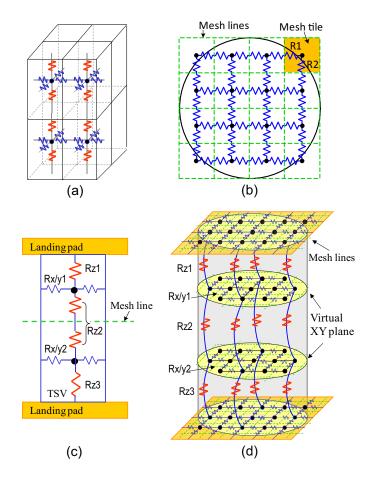

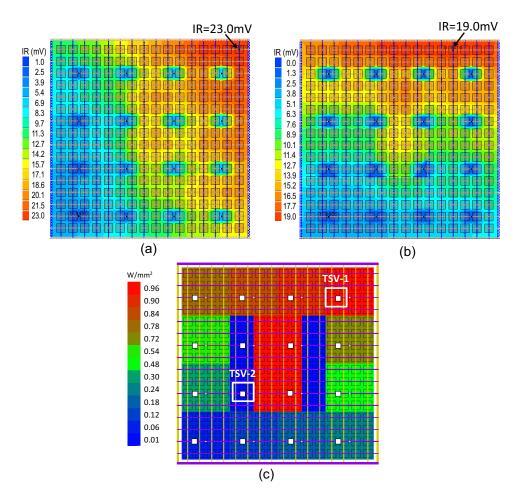

| Figure 45 | The proposed TSV modeling approach. Basic rectangular box after 3D meshing (a); XY-mesh and partially overlapped mesh tiles (b); side view (c); 3D view of the network (d)                                                                                                                                                                                                                  | 94 |

| Figure 46 | Meshing on the transition region.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 96        |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Figure 47 | Current density distributions and the error histogram of ANSYS Q3D and the proposed TSV modeling approach in PSIM at Z=0.1 $\mu$ m. The error in each tile is the absolute difference between Q3D and PSIM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 97        |

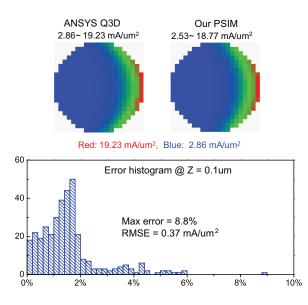

| Figure 48 | A circuit model for a two-die TSV-based PDN using the proposed 3D TSV modeling approach in top-down view (a) and side view (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 99        |

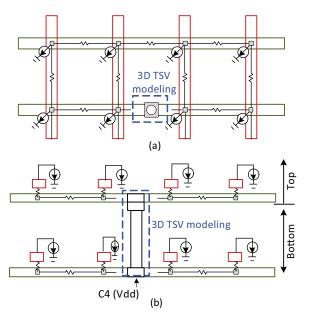

| Figure 49 | The voltage-drop maps in the top die (a) and in the bottom die (b). The power map in the bottom die (c).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 100       |

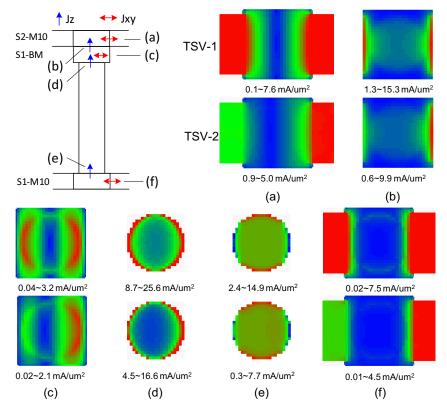

| Figure 50 | Current-density distribution in the XY direction (Jxy) and the Z direction (Jz) of TSV-1 and TSV-2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 101       |

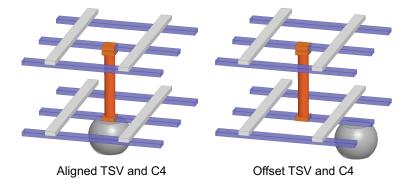

| Figure 51 | Zoom-in for partial PDNs with aligned vs offset TSV and C4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 105       |

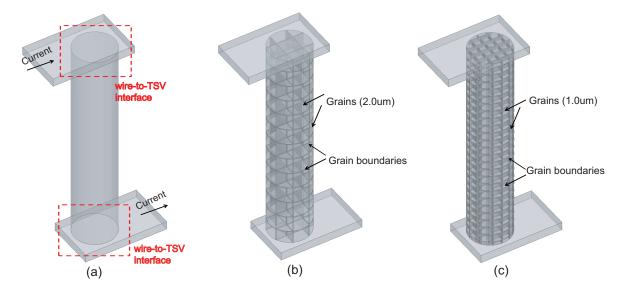

| Figure 52 | A test case to study the EM reliability of wire-to-TSV interface, with no grain structure (a), 2.0 $\mu$ grain size (b), and 1.0 $\mu$ grain size (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 109       |

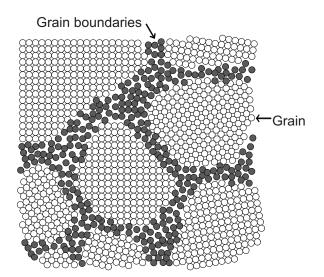

| Figure 53 | Illustrations of grains and grain boundaries in polycrystalline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 111       |

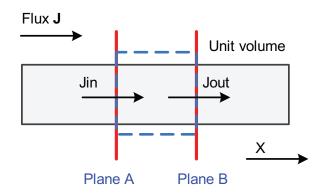

| Figure 54 | Illustration of the atomic flux and divergence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 114       |

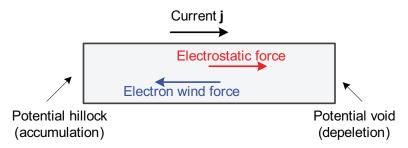

| Figure 55 | The electrostatic force and electron wind force on the atoms, and the weak positions of void and hillock formation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 115       |

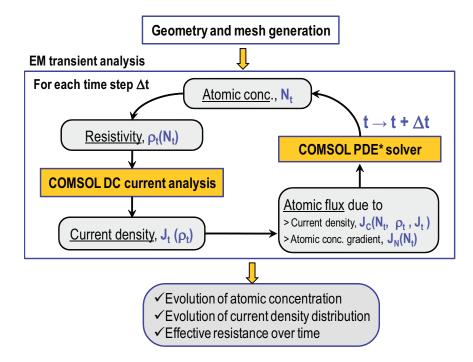

| Figure 56 | Simulation flow using COMSOL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 117       |

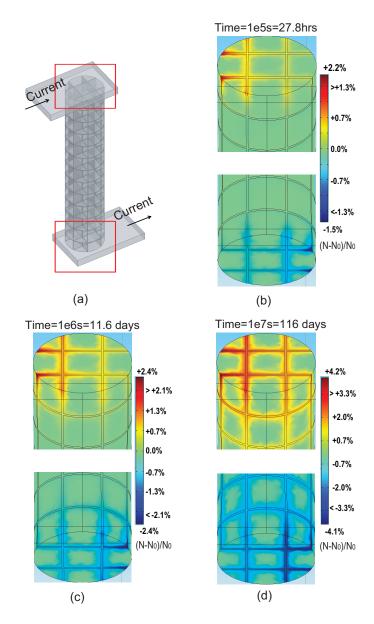

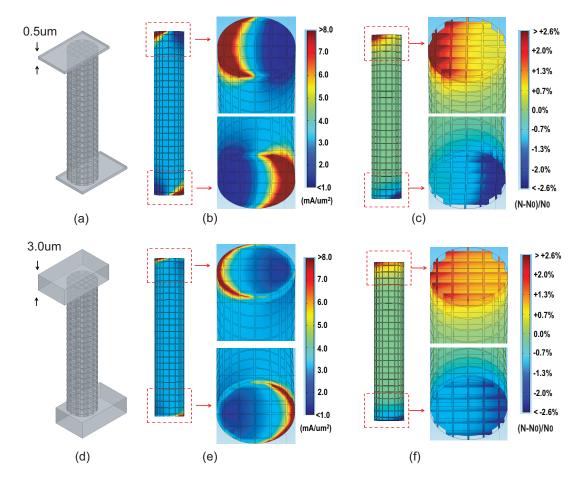

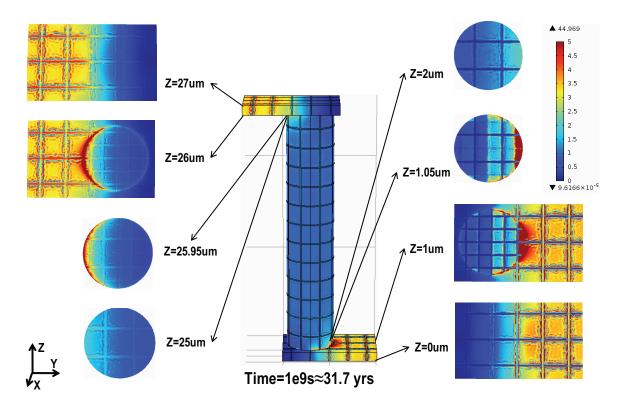

| Figure 57 | Atomic concentration on top and bottom wire-to-TSV interface at time=1et (b), time=1e6s (c), and time=1e7s (c). The color legend displays the percentage difference of atomic concentration normalized to the initial concentration $(N_0=1.53e28 \text{ Atoms/m}^3)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5s<br>119 |

| Figure 58 | Impact of wire thickness on current crowding and atomic concentration at<br>time 1e7s for top and bottom wire-to-TSV interfaces. The wire thickness<br>is 0.5um (a)-(c) and 3.0um (d)-(f). (a) and (d) are 3D views for 0.5um<br>and 3.0um wire thickness. (b) and (e) are current density distributions<br>in side view and in 3D top and bottom wire-to-TSV interfaces for 0.5um<br>and 3.0um wire thickness. (c) and (f) are atomic concentrations in side<br>view and in 3D top and bottom wire-to-TSV interfaces for 0.5um and<br>3.0um wire thickness. The color legend of atomic concentration is the<br>percentage difference normalized to the initial concentration $N_0=1.53e28$<br>atoms/m <sup>3</sup> | 121       |

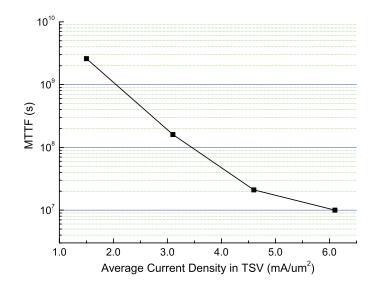

| Figure 59 | MTTF vs. average current density. The average current density increases from $1.5 \text{mA}/\text{um}^2$ to $6 \text{mA}/\text{um}^2$ , T=350K.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 123       |

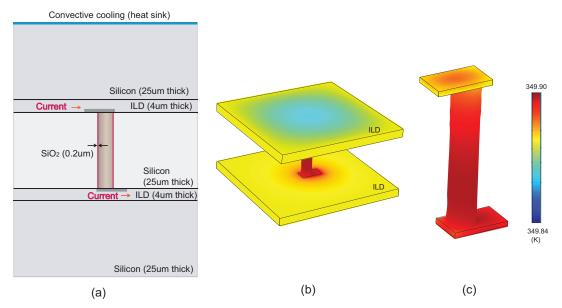

| Figure 60 | Simulation of joule heating for a TSV with 60mA input current. The structure (a) consists of three silicon layers, two ILD layers, a TSV liner $(SiO_2)$ , and a TSV with two landing wires. Heat sink is assigned at the top surface. (b) is the thermal gradient in ILD layers, landing wires, and the TSV. (c) is the thermal gradient inside the TSV which is negligible with a small range of 349.90K to 349.86K                                                                                                                                                                                                                                                                                               | 124       |

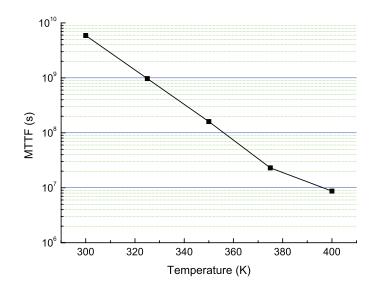

| Figure 61 | MTTF vs. temperature. The temperature is varied from 300K to 400K, and the current density is $3.1 \text{mA}/\text{um}^2$                                                          | 125 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

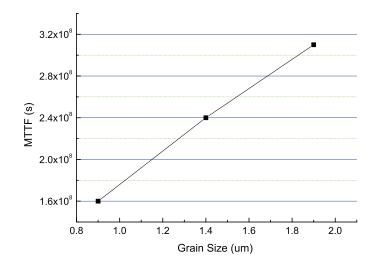

| Figure 62 | MTTF vs. grain size                                                                                                                                                                | 126 |

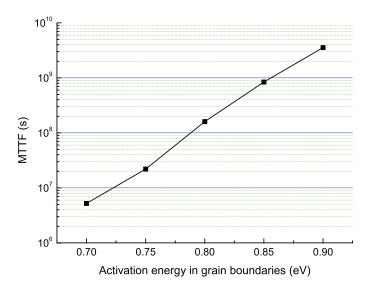

| Figure 63 | MTTF vs. activation energy in grain boundaries. Grain size and grain boundary size is 0.9um and 0.1um.                                                                             | 126 |

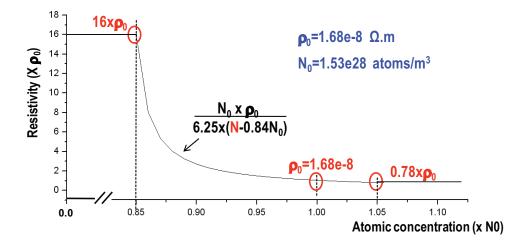

| Figure 64 | The resistivity function vs atomic concentration. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                     | 127 |

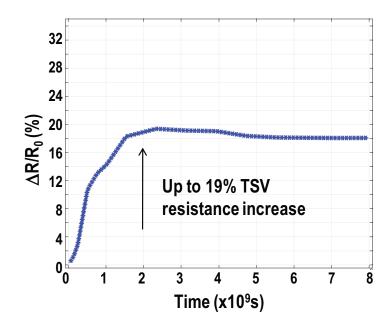

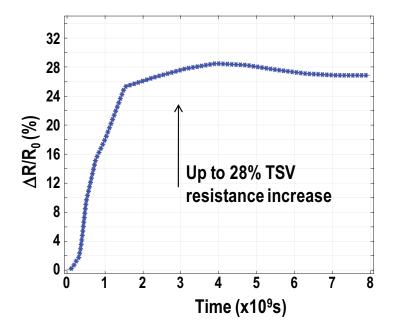

| Figure 65 | The simulation of TSV effective resistance changes over time                                                                                                                       | 128 |

| Figure 66 | Adding grains in the wires. (a) Bamboo wire with no grains. (b) non-<br>bamboo wires with grains.                                                                                  | 128 |

| Figure 67 | The simulated TSV effective resistance evolution when wires have grains.                                                                                                           | 129 |

| Figure 68 | Current density distribution in 3D view and XY planes when wires contain grains. The current density is normalized to the TSV average current density $(5\text{mA}/\text{um}^2)$ . | 130 |

## SUMMARY

The main objective of this thesis is to design reliable clock-distribution networks and power-delivery networks for three-dimensional integrated circuits (3D ICs) using throughsilicon vias (TSVs). This dissertation supports this goal by addressing six research topics. The first four works focus on 3D clock tree synthesis for low power, pre-bond testability, TSV-induced obstacle avoidance, and TSV utilization. The last two works develop modeling approaches for reliability analysis on 3D power-delivery networks.

In the first work, a clock synthesis algorithm is developed for low-power and low-slew 3D clock network design. The impact of various design parameters on clock performance, including the wirelength, clock power, clock slew, and skew, is investigated. These parameters cover the TSV count, TSV parasitics, the maximum loading capacitance of the clock buffers, and the supply voltage.

In the second work, a clock synthesis algorithm is developed to construct 3D clock networks for both pre-bond testability and post-bond operability. Pre-bond testing of 3D stacked ICs involves testing each individual die before bonding. The overall yield of 3D ICs improves with pre-bond testability because manufacturers can avoid stacking defective dies with good ones. Two key techniques including TSV-buffer insertion and redundant tree generation are implemented to minimize clock skew and ensure pre-bond testing. The impact of TSV utilization and TSV parasitics on clock power is also investigated.

In the third work, an obstacle-aware clock tree synthesis method is presented for throughsilicon-via (TSV)-based 3D ICs. A unique aspect of this problem lies in the fact that various types of TSVs become obstacles during 3D clock routing including signal, power/ground, and clock TSVs. These TSVs may occupy silicon area or routing layers. The generated clock tree does not sacrifice wirelength or clock power too much and avoids TSV-induced obstacles.

In the fourth work, a decision-tree-based clock synthesis (DTCS) method is developed for

low-power 3D clock network design, where TSVs form a regular 2D array. This TSV array style is shown to be more manufacturable and practical than layouts with TSVs located at irregular spots. The DTCS method explores the entire solution space for the best TSV array utilization in terms of low power. This method is applied for both gate-level chip-scale 3D clock designs and block-level global clock designs. Close-to-optimal solutions can be found for power efficiency with skew minimization in short runtime.

In the fifth work, current crowding and its impact on 3D power grid integrity is investigated. Due to the geometry of TSVs and connections to the global power grid, significant current crowding can occur. The current density distribution within a TSV and its connections to the global power grid is explored. A simple TSV model is implemented to obtain current density distributions within a TSV and its local environment. These models are checked for accuracy by comparing with identical models simulated using finite element modeling methods. The simple TSV models are integrated with the global power wires for detailed chip-scale power analysis.

In the sixth work, a comprehensive multi-physics modeling approach is developed to analyze electromigration (EM) in TSV-based 3D connections. Since a TSV has regions of high current density, grain boundaries play a significant role in EM dominating atomic transport. The transient analysis is performed on atomic transport including grain and grain boundary structures. The evolution of atomic depletion and accumulation is simulated due to current crowding. And the TSV resistance change is modeled.

## CHAPTER I

## INTRODUCTION AND BACKGROUND

#### 1.1 Introduction

Three-dimensional integrated circuits (3D ICs) have gradually shown promising potentials of low cost, further miniaturization, small area, low power, high bandwidth, and heterogeneous stacking enabled [2–5]. In 3D ICs, the clock distribution network spreads over the entire stack to distribute the clock signal to all the sequential elements. Clock skew, defined as the maximum difference in the clock signal arrival times from the clock source to all sinks, is required to be less than 3% or 4% of the clock period in an aggressive clock network design according to the International Technology Roadmap for Semiconductors (ITRS) projection [6]. Thus, clock skew control, which was well studied in 2D ICs [7], is still a primary objective in the 3D clock network design.

The clock signal in 3D ICs is distributed not only along the X and Y directions, but also along the Z direction using through-silicon vias (TSVs). The clock distribution network drives large capacitive loads and switches at a high frequency, which leads to an increasingly large proportion of the total power dissipated in the clock distribution network. In some applications, the clock network itself is responsible for 25% [8] and even up to 50% [9] of the total chip power consumption. Moreover, because a large clock slew may cause a setup or hold time violation, the clock slew must also be taken into consideration when designing a 3D clock network. Thus, low power, skew, and slew remain important design goals in 3D clock networks.

For a reliable 3D clock network design, several challenging issues should be taken care. First, in-depth investigations on the impact of TSV utilization on clock power and performance is important. This study can help designers understand the policies of robust 3D clock designs and apply efficient techniques accordingly. Second, the pre-bond testing [10], which tests each individual die before bonding, is able to improve the overall yield of 3D ICs by avoiding stacking defective dies with good ones. 3D clock designs should ensure both pre-bond testability and post-bond operability with minimum skew and low power consumption. Third, TSVs may occupy silicon area or routing layers, which are the obstacles during 3D clock routing. 3D clock trees should avoid overlapping with TSV-induced obstacles and should not sacrifice wirelength or clock power too much. Fourth, the TSV array style, where TSVs form a regular 2D array, is shown to be more manufacturable and practical than layouts with TSVs located at irregular spots. The utilization of TSV arrays for 3D clock synthesis significantly affects the clock power. An automatic and efficient approach, which can find an optimum solution of the low-power clock design, is required for TSV array design style.

In addition, electromigration (EM) has been studied for many decades and is still an open issue as an unavoidable source of degradation [11–13]. Voids in the conductive material can grow over time and may result in an open-circuit failure. A few studies have been presented on TSV EM modeling and analysis [14,15]. However, none of them investigated the detailed current distribution inside TSVs and the resulting thermal and stress migrations, where some of the corners may have the large current gradient and suffer EM reliability issues. Furthermore, a comprehensive multi-physics modeling approach is essential for designers to better understand the EM phenomenon and improve the EM lifetime in TSV-based 3D connections.

The reliable power network design is also a critical factor for robust circuit performance. The supply voltage scales slower than the scaling trend of transistors and interconnects. The increased current density and temperature accelerate the transistor and wire degradation, and shorten the lifetime of electronic devices [12]. Therefore, the 3D power integrity analysis for EM reliability is important to reliable 3D integration.

#### 1.1.1 Contributions

The contributions of this thesis are summarized as follows:

• A comprehensive clock synthesis algorithm for 3D ICs: A two-step approach is developed, which includes (1) three-dimensional (3D) abstract tree generation based

on the three-dimensional method of means and medians (3D-MMM) algorithm and (2) buffering and embedding based on the slew-aware deferred-merge buffering and embedding (sDMBE) algorithm. In addition, an extension of the 3D-MMM method (3D-MMM-ext) is implemented to determine the optimal number of TSVs in the 3D clock tree and to minimize the overall power consumption. This 3D-MMM-ext method can find a close-to-optimal design point in the "TSV count vs. power consumption" tradeoff curve very efficiently.

- An in-depth investigation on the impact of TSV utilization on 3D clock performance: For the first time, an extensive investigation on the impact of the TSV count and the TSV parasitics on clock power consumption and performance is presented. Several techniques are introduced to reduce the clock power consumption and clock slew of the 3D clock-distribution network. We analyze how these design factors affect the overall wirelength, clock power, slew, and skew in the clock network designs. Two important observations are made: (1) A 3D clock network that uses multiple TSVs significantly reduces the clock power compared with the single-TSV case; and (2) as the TSV capacitance increases, the power savings of a multiple-TSV clock network decreases.

- The first clock design methodology for pre-bond testing in 3D ICs: For the first time, a 3D clock synthesis methodology and algorithm for pre-bond testing is developed and implemented. Two key techniques including TSV-buffer insertion and redundant tree generation are implemented to minimize clock skew and ensure pre-bond testing. The impact of TSV utilization and TSV parasitics on wirelength and clock power is also investigated. Compared with the single-TSV solution, the proposed method minimizes the overall wirelength, reduces clock power consumption, and provides both pre-bond testability and post-bond operability with minimum skew and constrained slew.

- The first clock synthesis algorithm for TSV-induced obstacle avoidance: For the first time, a comprehensive analysis on TSV-induced obstacles is performed

and a clock routing algorithm for TSV-induced obstacle avoidance is developed and implemented. The traditional concept of merging segment is extended to represent the clock TSV and clock buffer insertion. Two key techniques are developed to determine overlap-free merging segments including Expanded-Obstacle Cutting and Nine-Region-Based Cutting techniques; two detour policies are presented to handle clock routing in heavily crowded regions. This proposed method can generate 3D clock trees that do not sacrifice wirelength or clock power too much and avoid overlapping with TSV-induced obstacles.

- The first clock synthesis algorithm of TSV array utilization for low-power 3D clock design: For the first time, an efficient clock synthesis methodology for TSV array design style is presented. A decision-tree-based clock synthesis (DTCS) method is developed for low-power 3D clock network design, where TSVs from a regular 2D array. The DTCS method explores the entire solution space for the best TSV array utilization in terms of low power. This method is applied for both gate-level chip-scale 3D clock designs and block-level global clock designs. Close-to-optimal solutions can be found for power efficiency with skew minimization in short runtime.

- A detail investigation on current density distribution in the TSV-to-wire interface and a TSV model for chip-scale 3D power integrity analysis: The current density distribution within a TSV and its connections to the global chip power grid is explored, where a significant amount of current crowding is observed. Simple TSV models are implemented to obtain current density distributions within a TSV and its local environment. These models are checked for accuracy by comparing with identical models simulated using finite element modeling methods. This simple TSV models are integrated with the 3D global power-delivery networks for detailed chipscale power analysis.

- The first multi-physics modeling approach for transient analysis on Electromigration in TSV-based 3D connections: For the first time, a multi-physics

modeling approach for electromigration analysis is presented for TSV-based threedimensional connections, where transient analysis is performed on atomic transport and TSV effective resistance including grain and grain boundary structure. The evolution of atomic depletion and accumulation is simulated due to current crowding. The model is validated by exploring the impact of current, temperature, and various grain sizes on the EM reliability. In addition, the TSV effective resistance evolution is modeled. These results and discussions provide guidance for designers to better understand and avoid EM reliability failures in 3D ICs.

#### 1.1.2 Thesis Organization

This dissertation is organized as follows:

- Chapter 1 introduces the thesis of this dissertation, summarizes the contributions, and explains the organization of this dissertation.

- Chapter 2 presents a clock synthesis algorithm for low-power 3D clock network designs and investigates the TSV utilization on clock power reduction.

- Chapter 3 presents a clock synthesis algorithm of 3D clock network design for pre-bond testability.

- Chapter 4 describes an obstacle-aware clock tree synthesis method for TSV-based 3D clock networks.

- Chapter 5 provides a clock synthesis method of TSV-array utilization for low-power 3D clock network design.

- Chapter 6 investigates current crowding in TSV-to-wire interfaces and develops a simple TSV model for chip-scale 3D power-integrity analysis.

- Chapter 7 presents a comprehensive multi-physics modeling approach to analyze electromigration in TSV-based 3D connections.

- Chapter 8 summarizes the research presented in this dissertation and provides concluding remarks.

### 1.2 Background

### 1.2.1 Traditional Clock Network Design

The clock distribution network plays an important role in a synchronous digital system. Clock skew, defined as the maximum difference in the clock signal arrival times, can severely limit the maximum performance of the entire system. The clock skew is required to be less than 3% or 4% of the clock period in an aggressive clock network design according to ITRS projection [6]. The clock distribution network travels the entire chip, drives large capacitive loads, and operates at a high frequency [7,8]. In some applications, the clock network can consume 25% [8] and even up to 50% [9] of the total chip power. In addition, the clock network is sensitive to the thermal gradients, process variations, and systematic variations.

The clock tree construction was first implemented as a H-tree [16, 17]. This symmetric structure significantly reduces clock skew but generates large size of the clock network. Jackson et al. [18] presented robust clock routing techniques for high-performance VLSI circuits. Their algorithm, called the method of means and medians (MMM), generates a clock topology by recursively partitioning the sink set into two subsets and then connecting the centers of these sets. Cong et al. [19] proposed a bottom-up matching approach to construct clock trees and addressed clock skew minimization in the linear delay model. Tsay [20] constructed clock trees with exact zero skew under the Elmore delay model [21]. Chao et al. [22] presented the deferred-merge embedding (DME) algorithm, which achieved shorter wirelength than both the MMM algorithm [18] and the bottom-up matching algorithm [19].

Process variation is a critical aspect of semiconductor fabrication [23]. Several work focused on analyzing the variation impact on clock networks [24–26]. Sauter et al. [24] compared four clock topologies in the presence of die-to-die (D2D) and within-die (WID) process variations, including a H-tree, a clock network with interleaved rings, a trunk tree, and a clock grid. Narasimhan et al. [25] analyzed the process variation impact on a five-stage 2D H-tree in various technology nodes.

Many clock synthesis algorithms have been proposed to improve the variation robustness in a clock network. Early in 1996, Neves and Friedman [27] proposed a clock design methodology to tolerate process parameter variations. Padmanabhan et al. [28] developed a statistical centering-based clock routing technique for the DME algorithm. Lam and Koh [29] integrated the clock scheduling and clock routing to tolerate process variations. Venkataraman et al. [30] addressed the same issue in various stages of the clock synthesis, including skew scheduling, abstract tree generation, and embedding. Rajaram et al. [31] developed a non-tree clock network. They inserted crosslinks in a given clock tree and analyzed the clock skew variation caused by crosslink insertion.

Several studies have been proposed to address low-power clock network design for high-performance and reliable VLSI systems. Dynamic-programming-based buffer insertion mainly focused on wirelength-driven, timing-driven, and maximum-slew-driven designs with power or area minimization [32–37]. Wang et al. [38] formulated the wire and buffer sizing problem as a sequential linear programming problem to minimize clock power under the skew constraint. Guthaus et al. [39] solved the clock tree sizing problem with the consideration of process variations. They minimized the process-variation-aware skew under the given power budget. Cho et al. [40] constructed a clock tree to balance the clock skew under two given static thermal profiles. Chakraborty et al. [41] extended the study [40] by considering the bounded clock skew. Moreover, Yu et al. [42] constructed thermal-aware clock trees by computing many bottom-up merging points based on the thermal sensitivity.

#### 1.2.2 Clock Network Design in Three-Dimensional ICs