# MIXED MATERIAL INTEGRATION FOR HIGH SPEED APPLICATIONS

A Thesis Presented to The Academic Faculty by Nicole Andrea Krishnamurthy

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical Engineering

> Georgia Institute of Technology December 1998

## MIXED MATERIAL INTEGRATION FOR HIGH SPEED

## **APPLICATIONS**

APPROVED: 1 askar, Chairperson Nan M. Jokerst, Chairperson April S. Brown David R. Herting W. Brent Carter

#### DEDICATION

To Tina, a soul taken far too soon from this earth. My heart reaches out to her parents, my aunt and uncle, in their time of sorrow. Tina, since you left this world before you completed yours, this thesis is dedicated to you.

#### Christina Lachenmann 1970 - 1998

#### A CHILD LOANED

"I'll lend you for a little time a child of Mine," He said, "for you to love the while he lives and mourn for when he's dead. It may be six or seven years or twenty-two or three, but will you, till I call him back, take care of him for Me? He'll bring his charms to gladden you, and should his stay be brief, you'll have his lovely memories as solace for your grief."

"I cannot promise he will stay, since all from earth return, but there are lessons taught down here I want this child to learn. I've looked this wide world over in My search for teacher true, and from the throngs that crowd life's lanes I have selected you.

Now will you give him all your love, not think the labor vain, or hate Me when I come to call and take him back again?"

I fancied that I heard them say, "Dear Lord, Thy Will be done. For all the joy the child shall bring, the risk of grief we'll run.

We'll love him while we may, and for the happiness we've known, forever grateful stay.

But should the Angels call for him much sooner than we planned we'll brave the bitter grief that comes and try to understand."

#### DON LARSON 1974

#### ACKNOWLEDGEMENTS

My thanks goes out to all those whose help, support and guidance has given me the strength to complete this chapter in my life. I would also like to thank those who have ever doubted my ability to succeed, for without them I would never have continued to push myself, constantly reaching for higher goals.

There are a few people I would like to thank separately. First, I would like to thank Dr. David R. Hertling, for without his belief in me when I was struggling with the idea of continuing my education, I would never have had the confidence to continue. I would also like to thank my thesis advisors, Dr. Joy Laskar and Dr. Nan Marie Jokerst, for all their guidance and advice. My thanks goes out to the other faculty members on my committee for their time and additional advising: Dr. April Brown, Dr. Ajeet Rohatgi, Dr. David Hertling, and Dr. Brent Carter. Gratitude goes out to Dr. Ray and Marilou Mycko for their continued efforts to make my thesis completion from long distance be as painless as possible.

I would like to thank my family, especially my mother who instilled in me the belief that there was never anything I couldn't achieve. Gratefulness goes to my husband, Dr. Vikram Krishnamurthy, for his never ending patience.

My appreciation goes out to all those who have kept me sane throughout the years, including Suzanne Fike, Carl Chun, Anh-Vu Pham, Georgi Dagnall, Steven Bond,

Dr. Carrie Carter-Coman, Dr. Nada El-Zein, Devi Laskar, and last but not least Dr. Alan Doolittle. Not only did all of you lend a sympathetic ear in times of need, but you also offered your help unselfishly. My evil twin acknowledges my partners in crime, Carl and Devi, for some of the most amusing jokes created for a certain someone's behalf. Dr. Laskar, I promised being the first to graduate, I would be the worst. I think I succeeded.

For all the integral passives work, I need to thank and recognize all of the help, support, and teamwork of the group of people at General Electric's Corporate Research and Development. This DARPA program is headed at the GE CR&D end by Herb Cole. I am indebted to Kevin Durocher and Rich Saia for their processing expertise, Matt Nielsen at RPI for Ta<sub>2</sub>O<sub>5</sub> deposition, and Hemant Kapida for his help on the high frequency layout. Thanks goes to Tim Schaefer at the Mayo Foundation and Dr. Eugene Rymaszewski for advice on the characterization of the passive components.

Finally, I'd like to thank Jim Murphy and Pat Sullivan for the DARPA support of the integral passives work and Gernot Pomrenke at DARPA, Ted Moise, Alan Seabaugh, and Bobby Brar at Raytheon/TI for the support of the thin film resonant tunneling diode work.

### TABLE OF CONTENTS

| DEDICATION                                            | ii       |

|-------------------------------------------------------|----------|

| ACKNOWLEDGEMENTS                                      | iii      |

| TABLE OF CONTENTS                                     | v        |

| LIST OF TABLES                                        | viii     |

| LIST OF FIGURES                                       | ix       |

| SUMMARY                                               | xvi      |

| CHAPTER I: INTRODUCTION                               | 1        |

| CHAPTER II: THIN FILM INP-BASED SEMICONDUCTOR INTE    | GRATION  |

| PROCESS                                               | 8        |

| 2.1 Standard Substrate Removal and Bonding            | 10       |

| 2.2 Modified Substrate Removal and Bonding            | 11       |

| 2.3 Integration Using Transfer Diaphragm              | 13       |

| CHAPTER III: THIN FILM RESONANT TUNNELING DIODES      | 16       |

| 3.1 Growth and Fabrication                            | 19       |

| 3.2 Experimental Results of Thin Film RTDs on Silicon | 20       |

| 3.3 Physics-Based Spice Model and MDS Diode Model     | 22       |

| 3.4 Process Optimization for Circuit Integration      | 32       |

| 3.5 RTD Circuit Integration                           |          |

| CHAPTER IV: TUNNELING HOT ELECTRON TRANSFER AMPL      | IFIERS48 |

| 4.1 Device Structure and Characteristics                                     |

|------------------------------------------------------------------------------|

| 4.2 Comparison of DC and RF Characteristics                                  |

| CHAPTER V: HETEROJUNCTION BIPOLAR TRANSISTORS                                |

| 5.1 InP-Based Single Heterojunction Bipolar Transistor                       |

| 5.2 DC and RF Performance of Thin Film HBTs                                  |

| CHAPTER VI: THIN FILM INTEGRAL PASSIVES                                      |

| 6.1 Testing of Integral Passives71                                           |

| 6.1.1 DC Testing of Thin Film Resistors71                                    |

| 6.1.2 DC and Low Frequency Testing of Thin Film Capacitors                   |

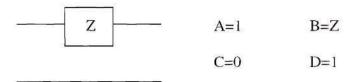

| 6.1.3 Microwave Testing of Integral Passive Components74                     |

| 6.2 Thin Film Ta <sub>2</sub> N Resistors on Flex                            |

| 6.2.1 Design of Thin Film Resistors                                          |

| 6.2.2 Overview of DC testing of Thin Film Ta <sub>2</sub> N Resistors        |

| 6.2.3 One- and Two- Port Resistor Extractions from S-Parameters80            |

| 6.3 Thin Film Inductors91                                                    |

| 6.3.1 Inductance and Parasitic Resistance Extraction from S-Parameters       |

| 6.3.2 Results                                                                |

| 6.4 Thin Film DLC and Ta <sub>2</sub> O <sub>5</sub> Capacitors              |

| 6.4.1 DC and Low Frequency Characterization107                               |

| 6.4.2 High Frequency One and Two Port Extractions of Thin Film Capacitors112 |

| 6.4.3 Results                                                                |

| CHAPTER VII: CONCLUSIONS                    | 124 |

|---------------------------------------------|-----|

| CHAPTER VIII: FUTURE DIRECTIONS             |     |

| 8.1 Thin Film RTDs                          |     |

| 8.2 Thin Film HBTs                          | 128 |

| 8.3 Thin Film Passives                      | 132 |

| APPENDIX A: RTD CIRCUIT INTEGRATION PROCESS | 134 |

| APPENDIX B: S-PARAMETER CONVERSION TABLE    | 141 |

| VITA                                        |     |

## LIST OF TABLES

| Table 3.1 Original and varied parameter values for the resonant tunneling current  |

|------------------------------------------------------------------------------------|

| equation27                                                                         |

| Table 3.2 Statistics of the peak voltage for the negative NDR                      |

| Table 3.3 Statistics of the peak current for the negative NDR                      |

| Table 5.1 Various Si host substrates and dielectric layers to which the HBTs were  |

| bonded62                                                                           |

| Table 6.1 Summary of DC testing of some of the Ta <sub>2</sub> N resistors         |

| Table 6.2 Resistor designs for one sided resistors.    85                          |

| Table 6.3 Percentage off from target value and percent change for the single-sided |

| resistor designs                                                                   |

| Table 6.4 Summary of high frequency response for some inductors with ground plane  |

| over 90 mils away. *** notes these structures were not tested                      |

| Table 6.5 Specifications of inductor designs, predicted and actual inductance      |

| Table 6.6 Different Capacitor sizes for GE designed capacitors                     |

#### LIST OF FIGURES

Figure 2.1 Substrate removal and bonding of RTDs onto silicon host substrates ......10 Figure 2.2 Transfer of thin film devices to host substrate without use of transfer diaphragm. Contacts are made on both sides of the device. The ability to align utilizing Figure 2.3 Substrate removal and bonding using a transfer diaphragm. The transfer diaphragm enables the alignment and bonding of the thin film devices to the host substrate as well as the ability to process both top and bottom of the device. Postprocessing of top contact pads is done after device has been contact bonded to the host Figure 3.1 Conduction band profiles of the RTD under the conditions of zero bias, threshold bias, resonance, and off-resonance. The local Fermi levels in the emitter and collector are  $\mathbf{E}_{\mathbf{F}}^{\mathbf{L}}$  and  $\mathbf{E}_{\mathbf{F}}^{\mathbf{R}}$ , and the energies of the conduction-band edge in the emitter and Figure 3.2 Structure of the high PVR RTD (a) before and (b) after substrate removal and Figure 3.3 SEM of a 64 µm<sup>2</sup> high PVR RTD after substrate removal and bonding......20 Figure 3.4 256  $\mu$ m<sup>2</sup> high PVR RTD before and after substrate removal and bonding.

| Figure 3.5 Four vertically stacked 16 $\mu$ m <sup>2</sup> RTDs before and after substrate removal and |

|--------------------------------------------------------------------------------------------------------|

| bonding                                                                                                |

| Figure 3.6 SPICE Program for Physics-Based DC Curves                                                   |

| Figure 3.7 Variations in DC response of the RTDs due to changes in the parameters in                   |

| the resonant tunneling current equation27                                                              |

| Figure 3.8 A large signal model in MDS for simulation of current-voltage characteristics               |

| of RTD29                                                                                               |

| Figure 3.9 A resistor is added in series with the model for simulation of the voltage shift            |

| which occurred for the thin film RTDs                                                                  |

| Figure 3.10 DC characteristics of low and high series resistance RTDs modeled using                    |

| MDS                                                                                                    |

|                                                                                                        |

| Figure 3.11 On wafer DC characteristics of low current 6 $\mu$ m RTD's with thick                      |

| planarizing nitride                                                                                    |

| Figure 3.12 Low current 6 $\mu$ m RTD's with thick planarizing nitride after substrate                 |

| removal and bonding                                                                                    |

| Figure 3.13 Current-voltage characteristics of on wafer low current 6 $\mu$ m RTD's after              |

| RIE nitride removal                                                                                    |

| Figure 3.14 Low current 6 $\mu$ m RTD's after wet etch of nitride and substrate removal35              |

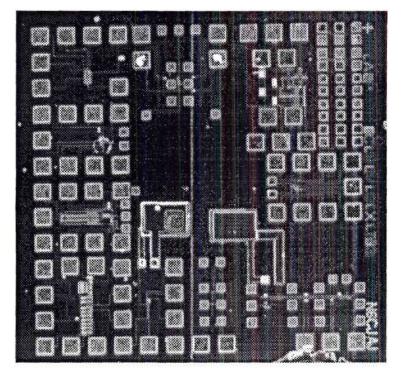

| Figure 3.15 Silicon comparator circuit with integrated InP RTD                                         |

| Figure 3.16 Photograph of RTD with Si comparator circuit                                               |

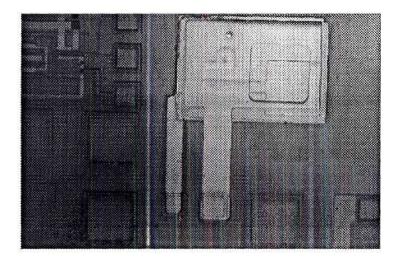

| Figure 3.17 Close-up of RTD integrated with a Si comparator circuit                                         |

|-------------------------------------------------------------------------------------------------------------|

| Figure 3.18 Negative region current-voltage characteristics of RTD after integration                        |

| with comparator circuit                                                                                     |

| Figure 3.19 Modeled current-voltage characteristics of RTD for circuit simulations41                        |

| Figure 3.20 Simulated current-voltage characteristics of comparator circuit without RTD                     |

|                                                                                                             |

| Figure 3.21 Simulated current-voltage characteristics of comparator circuit with RTD .42                    |

| Figure 3.22 Bias conditions for testing of comparator circuit with InP RTD43                                |

| Figure 3.23 Actual current-voltage characteristics of comparator circuit without RTD .44                    |

| Figure 3.24 Actual current-voltage characteristics of comparator circuit with and without                   |

| RTD45                                                                                                       |

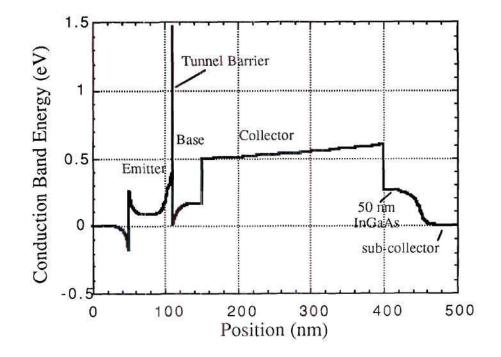

| Figure 4.1 Computed conduction band profile for the Tunneling Hot Electron Transfer                         |

| Amplifier. The emitter thickness has been reduced in the simulation                                         |

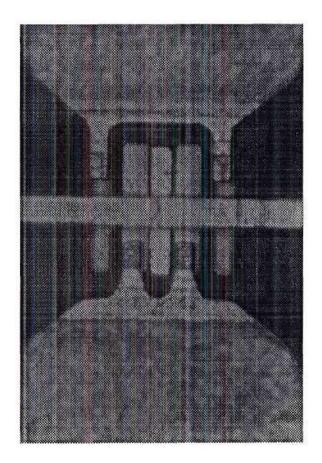

| Figure 4.2 Close-up of thin film, 1.3 $\mu$ m thick THETA device on silicon with 0.5 $\mu$ m of             |

| silicon nitride                                                                                             |

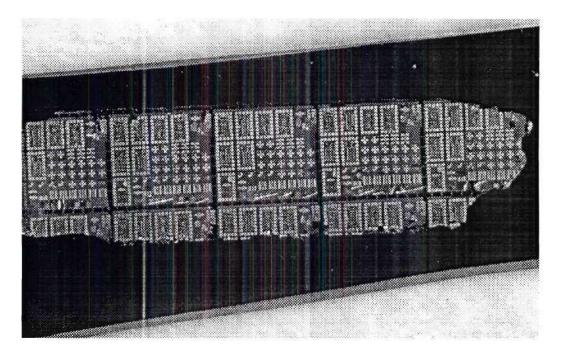

| Figure 4.3 Thin Film THETAs on silicon coated with 5000 Å silicon nitride51                                 |

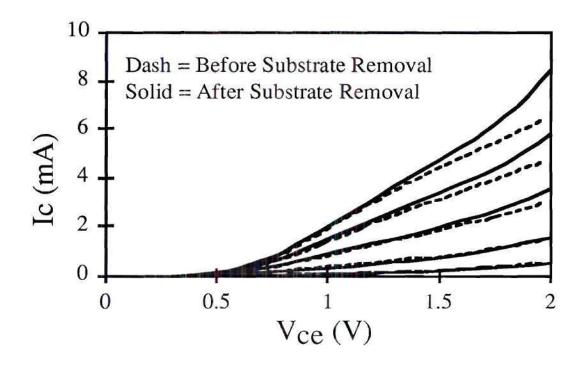

| Figure 4.4 DC characteristics of a THETA before and after substrate removal and                             |

| bonding to silicon coated with 0.5 µm of silicon nitride                                                    |

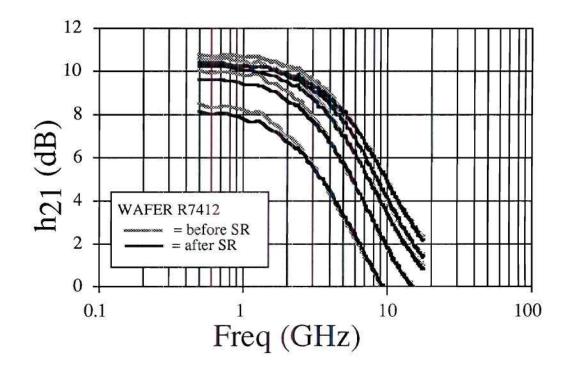

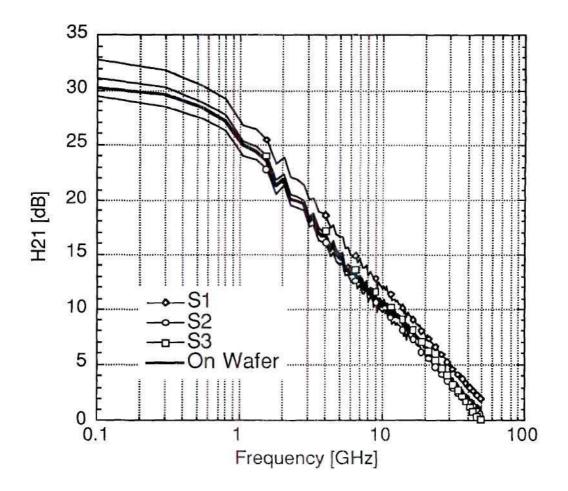

| Figure 4.5 $H_{21}$ of the THETA for $V_{ce}=1.5V$ , $I_{b}$ from 0.5 to 2.5 mA (0.5 mA steps), and $I_{c}$ |

| from 2.8 to 11.5 mA before and after substrate removal and bonding to sapphire. $F_x$                       |

| exceeded 20 GHz for $I_{b}$ >1.5 mA ( $I_{c}$ >6.8 mA). Similar characteristics were observed for           |

|                                                                                                             |

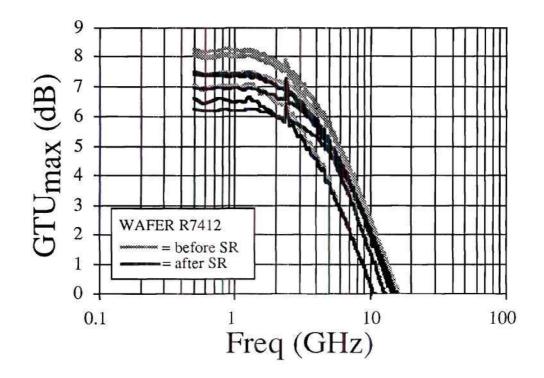

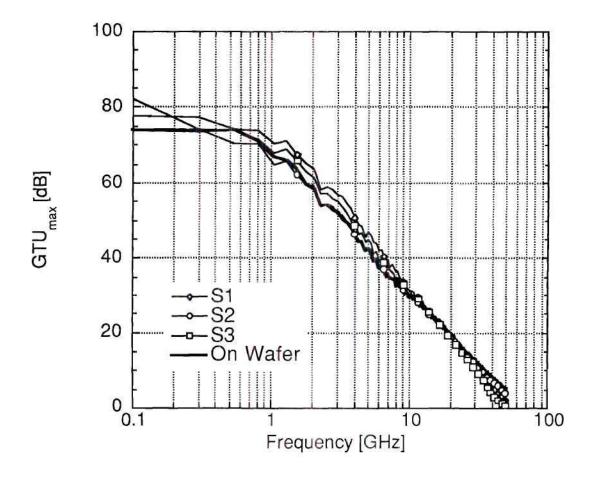

| Figure 4.6 $\text{GTU}_{\text{max}}$ of a THETA for $V_{ce}$ =1.5V, $I_{b}$ from 0.5 to 2.5 mA (0.5 mA steps), and |

|--------------------------------------------------------------------------------------------------------------------|

| $I_{e}$ from 2.8 to 11.5 mA before and after substrate removal and bonding to sapphire. F $_{max}$                 |

| was around 17 GHz for $I_c=11.5$ mA. Similar characteristics were observed for alumina                             |

| and quartz host substrates                                                                                         |

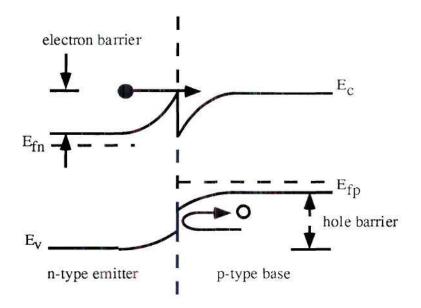

| Figure 5.1 Energy band diagram of the emitter-collector transition region of the HBT. 57                           |

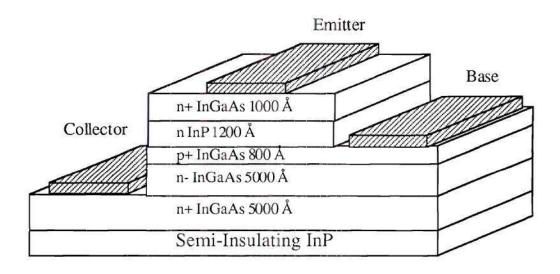

| Figure 5.2 SHBT device structure used in this study                                                                |

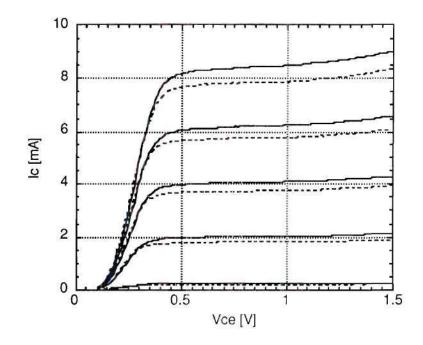

| Figure 5.3 IV characteristics of HBT on-wafer (solid) and bonded to BCB on Si                                      |

| (dashed)60                                                                                                         |

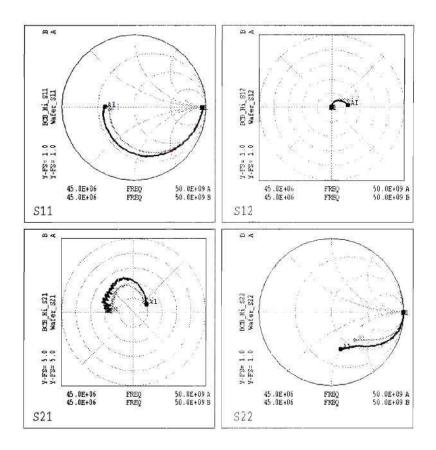

| Figure 5.4 Comparison of S-parameters of HBT on-wafer (dark line) and HBT on BCB                                   |

| insulated Si substrate (gray line)61                                                                               |

| Figure 5.5 H <sub>21</sub> of HBT at Vce=1.5V Ic=2mA on various substrates63                                       |

| Figure 5.6 GTU <sub>max</sub> of HBT at $V_{cc}$ =1.5V and $I_c$ =2mA on various substrates64                      |

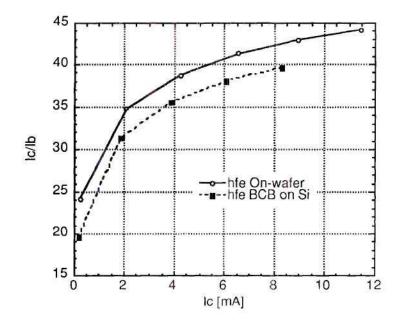

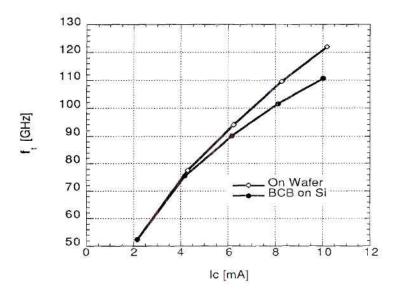

| Figure 5.7 DC $\beta$ vs. collector current plot of HBT before and after bonding to BCB on                         |

| Si65                                                                                                               |

| Figure 5.8 Comparison of HBT cutoff frequency verses $I_e$ before and after integration to                         |

| Si65                                                                                                               |

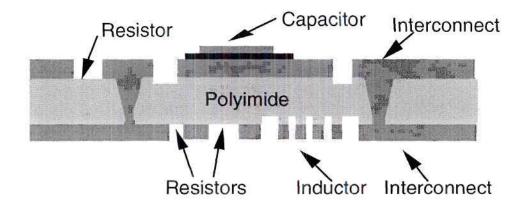

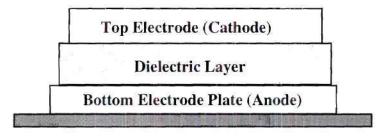

| Figure 6.1 Cross-section of two-sided integrated passives on flex                                                  |

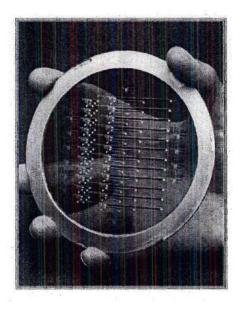

| Figure 6.2 One of the smaller area flex consisting of resistor TEGs supported by a                                 |

| titanium frame                                                                                                     |

| Figure 6.3 Cathode and anode definitions of the thin film capacitor                                                |

|                                                                                                                    |

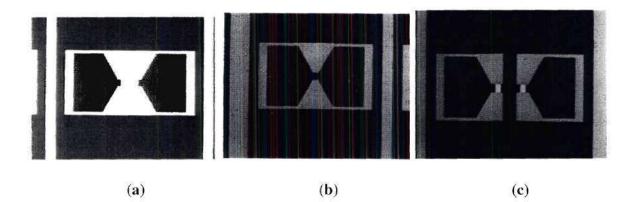

| Figure 6.4 (a) Open, (b) through, and (c) matched load on-wafer LRM calibration                                                                             |                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| designs for de-embedding the resistor launches and transition region from one-side TaN                                                                      |                      |

| resistors7                                                                                                                                                  | 6                    |

| Figure 6.5 Mayo design of two-sided resistors with vias from top ground pads of                                                                             |                      |

| microwave launches thorough the polyimide to the ground plate on the back of the free                                                                       |                      |

| standing flex7                                                                                                                                              | 7                    |

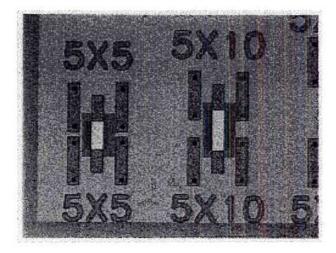

| Figure 6.6 Serpentine and linear resistor designs for the single-sided resistors. To                                                                        |                      |

| evaluate the design limits, length, width, and number of squares were varied7                                                                               | 8                    |

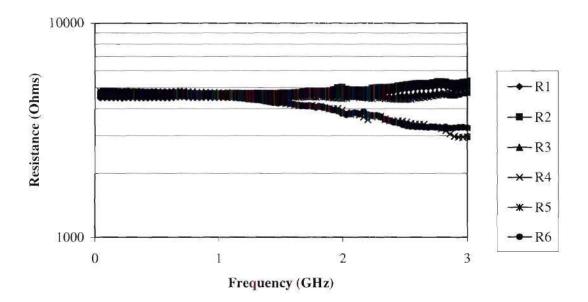

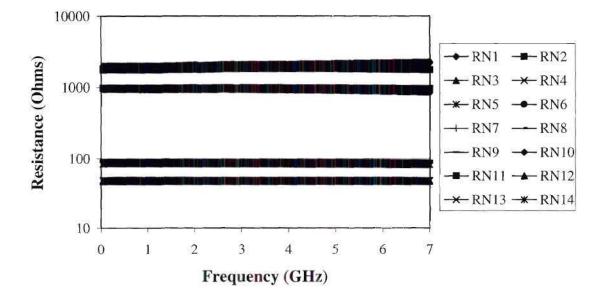

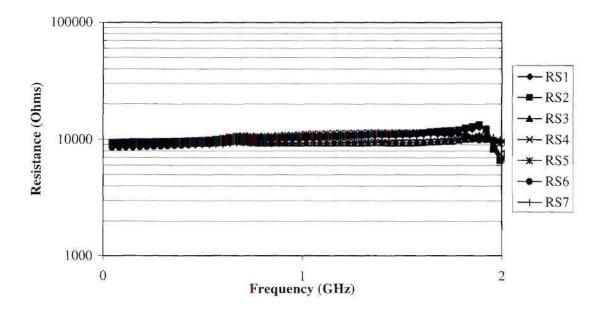

| Figure 6.7 Two-sided resistor design results. Ground plane is on back of 1 mil flex8                                                                        | 3                    |

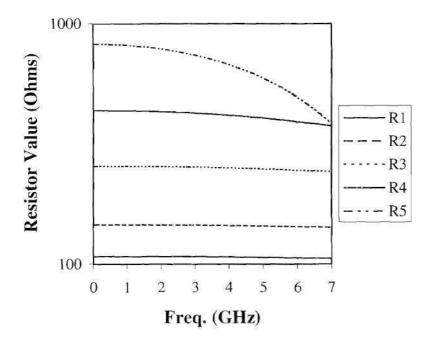

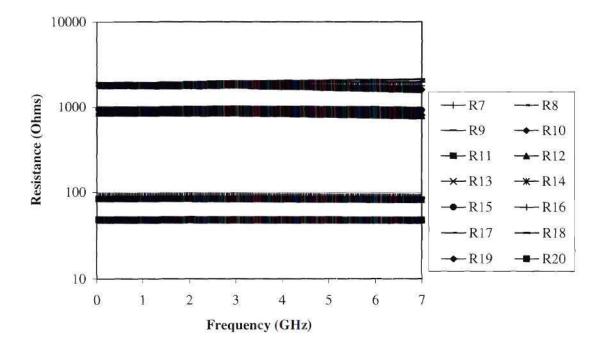

| Figure 6.8 Linear resistors on flex                                                                                                                         | 7                    |

| Figure 6.9 Linear long length resistors on flex. Higher parastics are due to increased                                                                      |                      |

| length of resistors                                                                                                                                         | 8                    |

|                                                                                                                                                             | 0                    |

| Figure 6.10 90 degree turned linear resistors on flex                                                                                                       |                      |

| Figure 6.10 90 degree turned linear resistors on flex                                                                                                       |                      |

|                                                                                                                                                             | 9                    |

| Figure 6.11 Serpentine resistors on flex. Higher parasitics than the linear resistors can                                                                   | 9<br>0               |

| Figure 6.11 Serpentine resistors on flex. Higher parasitics than the linear resistors can be observed partially due to capacitive coupling between lines    | 99<br>90<br>91       |

| Figure 6.11 Serpentine resistors on flex. Higher parasitics than the linear resistors can<br>be observed partially due to capacitive coupling between lines | 99<br>90<br>91       |

| Figure 6.11 Serpentine resistors on flex. Higher parasitics than the linear resistors can<br>be observed partially due to capacitive coupling between lines | 9<br>90<br>91        |

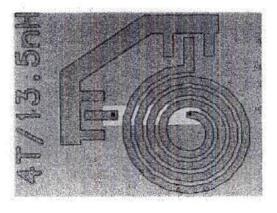

| Figure 6.11 Serpentine resistors on flex. Higher parasitics than the linear resistors can<br>be observed partially due to capacitive coupling between lines | 99<br>90<br>91       |

| Figure 6.11 Serpentine resistors on flex. Higher parasitics than the linear resistors can<br>be observed partially due to capacitive coupling between lines | 90<br>90<br>91<br>96 |

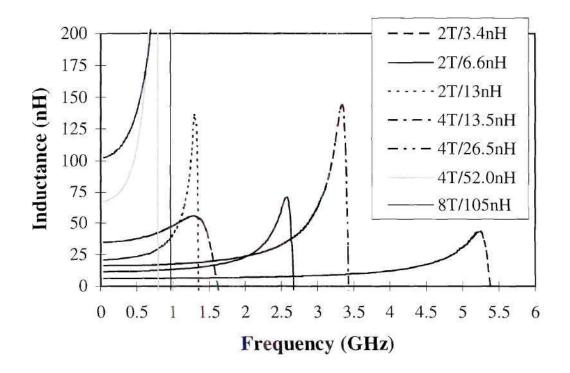

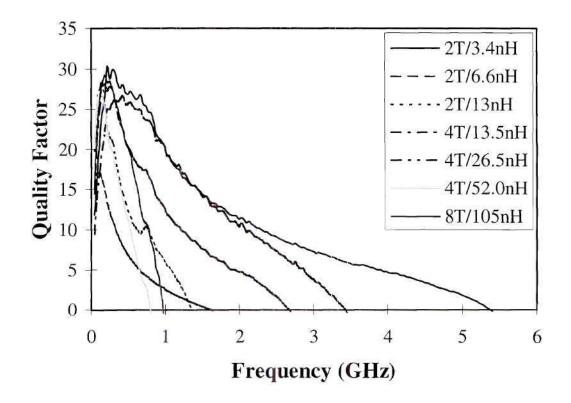

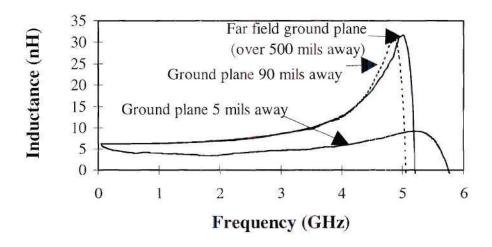

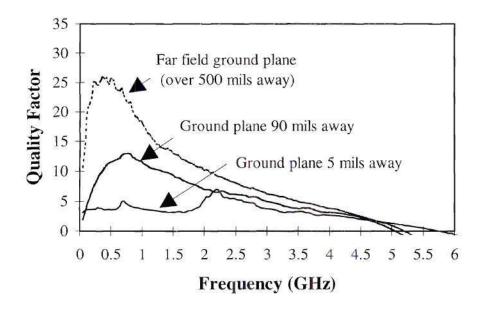

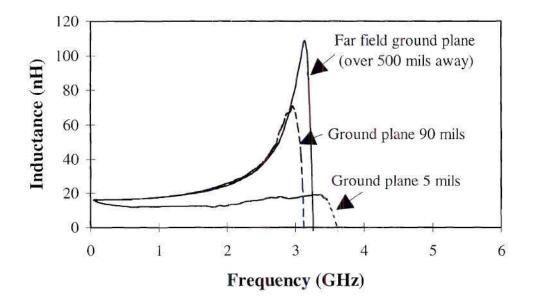

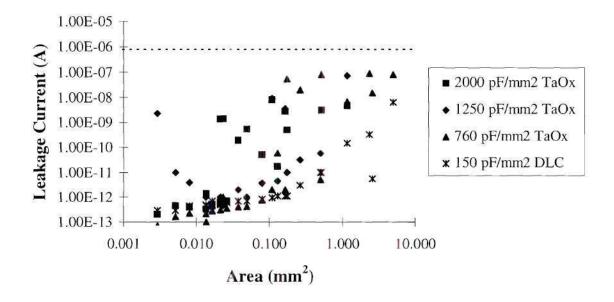

| Figure 6.16 Changes in quality factor vs. frequency for a 3.4 nH inductor as a function                             |

|---------------------------------------------------------------------------------------------------------------------|

| of distance of ground plane101                                                                                      |

| Figure 6.17 Inductance vs. frequency for 13.5 nH inductor with the ground plane                                     |

| distance varied102                                                                                                  |

| Figure 6.18 Changes in quality factor vs. frequency for a 13.5 nH inductor as a function                            |

| of distance of ground plane                                                                                         |

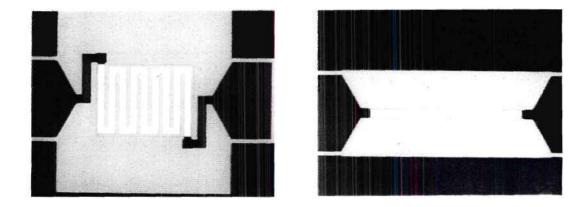

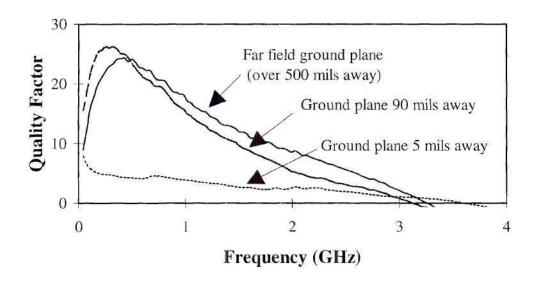

| Figure 6.19 Mayo design of high frequency parallel plate capacitor104                                               |

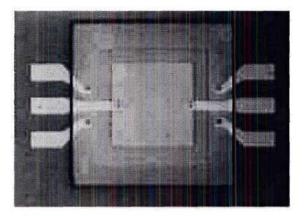

| Figure 6.20 Leakage current at 5 volt bias verses area                                                              |

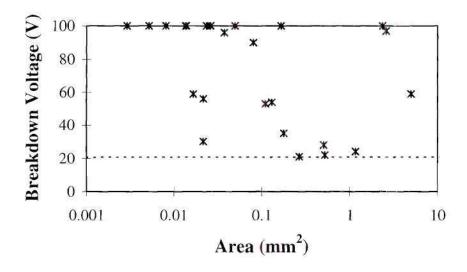

| Figure 6.21 Breakdown voltage verses area for different thicknesses of DLC after top                                |

| passivation. Values at 100 volts did not break down                                                                 |

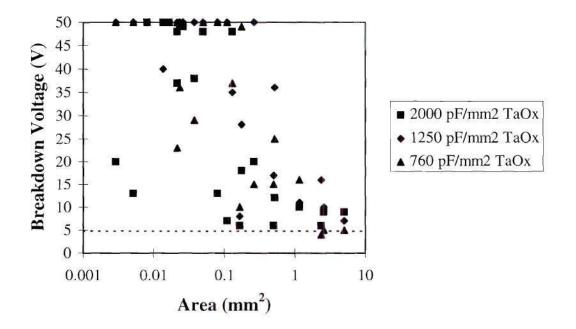

| Figure 6.22 Breakdown voltage verses area for different thicknesses of $Ta_2O_5$ after top                          |

| passivation. Values at 50 volts did not break down                                                                  |

| Figure 6.23 Percentage off target verses capacitance                                                                |

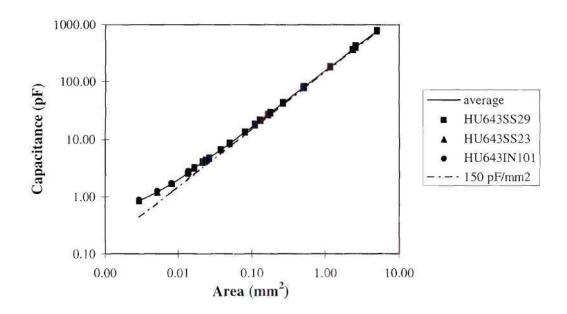

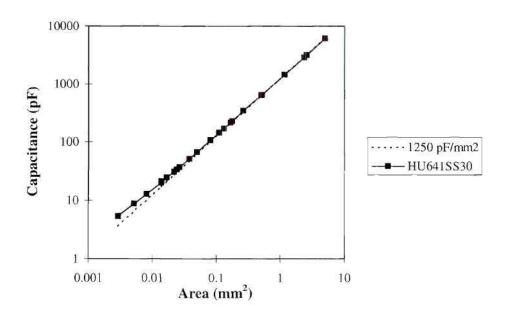

| Figure 6.24 Capacitance verses area for 2kA DLC on flex at 10kHz for parallel plate                                 |

| capacitor design                                                                                                    |

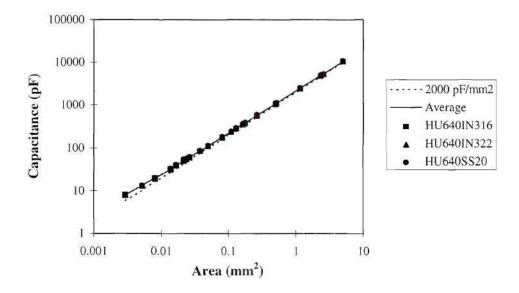

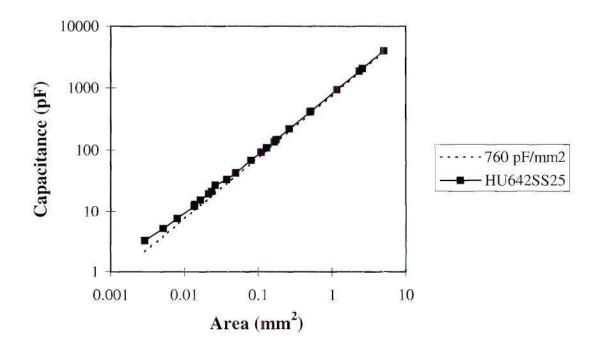

| Figure 6.25 Capacitance verses Area for $1$ kA Ta <sub>2</sub> O <sub>5</sub> on Flex at 10kHz for parallel plate   |

| capacitor design                                                                                                    |

| Figure 6.26 Capacitance verses Area for $1.5$ kA Ta <sub>2</sub> O <sub>5</sub> on Flex at 10kHz for parallel plate |

| capacitor design                                                                                                    |

| Figure 6.27 Capacitance verses Area for 2.3kA $Ta_2O_5$ on Flex at 10kHz for parallel plate                         |

| capacitor design                                                                                                    |

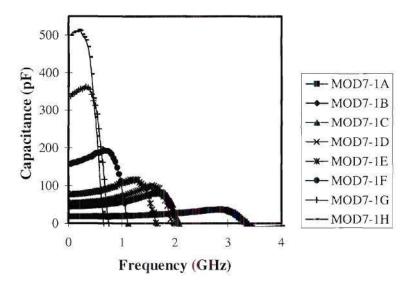

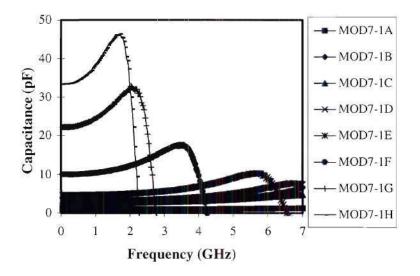

| Figure 6.28 One port measurements showing resonant frequency for 1000A $Ta_2O_5$                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| parallel plate capacitors                                                                                                                                                |

| Figure 6.29 Quality factor vs. frequency for 1000A Ta $_2O_5$ parallel plate capacitors with                                                                             |

| different areas116                                                                                                                                                       |

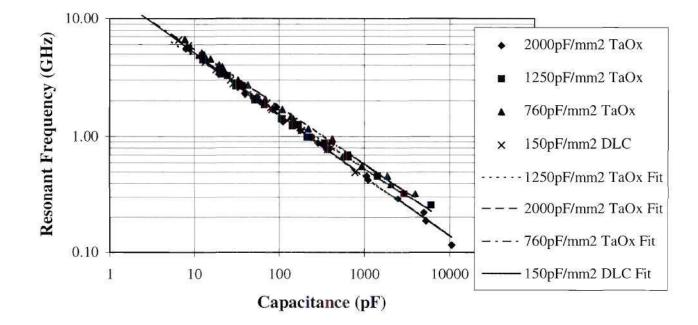

| Figure 6.30 Capacitance verses frequency of some of the 150pF/mm <sup>2</sup> DLC parallel plate                                                                         |

| capacitors extracted from 1-port measurements                                                                                                                            |

| Figure 6.31 Quality factor verses frequency of some of the 150pF/mm <sup>2</sup> DLC parallel                                                                            |

| plate capacitors extracted from 1-port measurements                                                                                                                      |

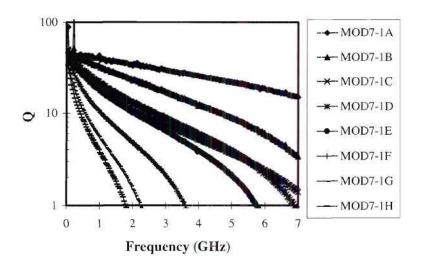

| Figure 6.32 Capacitance per Unit Area (CPUA) verses frequency for the first row of the                                                                                   |

| (a) 1000A $Ta_2O_5$ , (b) 1500A $Ta_2O_5$ , (c) 2500A $Ta_2O_5$ , and (d) 2000A DLC parallel plate                                                                       |

| capacitors                                                                                                                                                               |

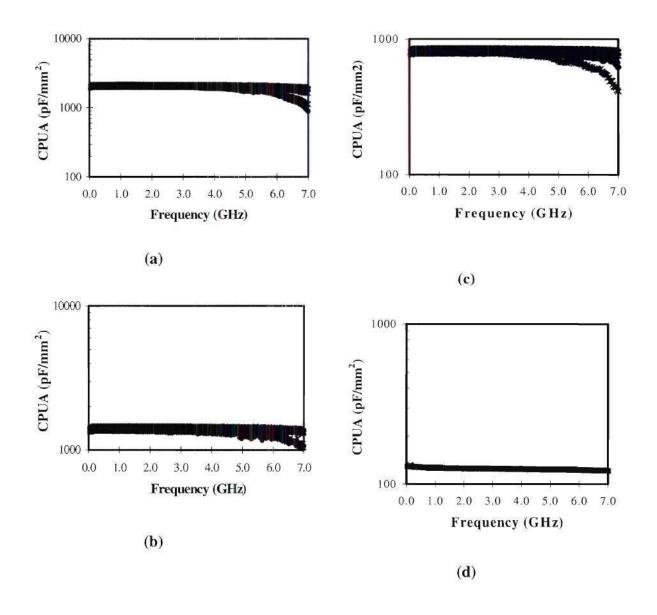

| Figure 6.33 Resonant frequency verses capacitance for different CPUA TaOx and DLC                                                                                        |

|                                                                                                                                                                          |

|                                                                                                                                                                          |

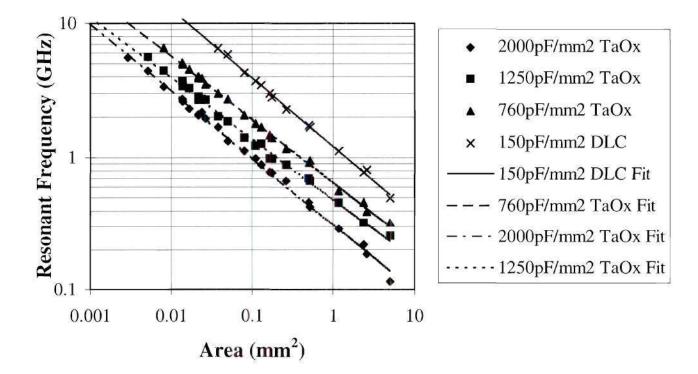

| Figure 6.34 Resonant Frequency vs. Area for Different CPUA of $Ta_2O_5$ and DLC120                                                                                       |

|                                                                                                                                                                          |

| Figure 6.34 Resonant Frequency vs. Area for Different CPUA of $Ta_2O_5$ and DLC120                                                                                       |

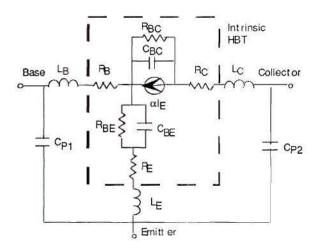

| Figure 6.34 Resonant Frequency vs. Area for Different CPUA of $Ta_2O_5$ and DLC120 Figure 8.1 T-topology small signal equivalent model and element values of an on-wafer |

#### SUMMARY

A great demand for portable and highly integrated high speed electronic components and systems has recently surfaced as a result of the vast expansion of personal communications and other wireless applications. As more and more applications in personal communications require frequencies between 1 and 100 GHz, a reduction in the cost of III-V technology is necessary for a wide distribution of wireless products in the consumer market. III-V technology provides improved and unique functionality compared with silicon CMOS integrated circuit (IC) technology, yet current III-V technologies cannot meet all the demands of low cost, high levels of integration, low power, and performance because of high material costs and low yield compared with the current silicon technology.

In this thesis, thin film mixed material integration is investigated as a method to increase functionality at lower cost. InP active devices are removed from the growth substrate and integrated onto other host substrates such as silicon via substrate removal. Characterization of these devices is performed. Also, thin film passive components via deposition on free standing polyimide are evaluated for lower cost and increased design freedom. By optimizing the passives and III-V active components separately and then integrating the two opens a new realm in mixed material integration.

#### **CHAPTER I**

#### INTRODUCTION

A great demand for portable and highly integrated high speed electronic components and systems has recently surfaced as a result of the vast expansion of personal communications and other wireless applications. As more and more applications in personal communications require frequencies between 1 and 100 GHz, a reduction in the cost of III-V technology is necessary for a wide distribution of wireless products in the consumer market. III-V technology provides improved and unique functionality compared with silicon CMOS integrated circuit (IC) technology, yet current III-V technologies cannot meet all the demands of low cost, high levels of integration, low power, and performance because of high material costs and low yield compared with the current silicon technology. Although silicon ICs possess the benefits of low cost material, high yield, and high component density, conventional silicon circuitry cannot provide the higher frequencies for emerging wireless communication. The need to reduce the cost of wireless technology can be solved through multi-material integration, which is the hybrid integration of III-V high speed components bonded directly to silicon circuitry. RF/microwave applications can be implemented with the high performance III-V components, while the remaining functions can be realized in the silicon circuit,

which also serves as the hybrid integration substrate. Cost is optimized through the sparse distribution of the relatively costly III-V components, by moving the large area components and low performance functions to the low cost, standard silicon circuitry. Each individual high speed component can be optimized for cost and performance independent of the silicon circuit design and fabrication and then the devices of choice can be integrated with the conventional, low cost silicon circuit.

Thin film semiconductor device integration has the advantage of integrating a variety of materials onto a single host substrate without concern for growth nucleation and growth compatibility. The direct growth approach of compound semiconductor material onto Si circuitry has constraints because of lattice and coefficient of thermal expansion mismatches between the Si and the compound semiconductor. Because of these mismatches, III-V material structures grown on silicon have been of worse quality than the growth of the structure on a lattice matched substrate. For example, the peak-to-valley ratio (PVR) of the negative differential region (NDR) of a resonant tunneling diode (RTD) is extremely sensitive to the growth conditions of the material structure. A ten times reduction is seen in the PVR of the same device grown on silicon instead of InP.<sup>4</sup>

Si/SiGe growth is another alternative to mixed material integration for resonant tunneling devices and high speed devices. An RTD grown by IBM using chemical vapor deposition yielded at room temperature a PVR of 1.2.<sup>2</sup> This is a factor of 25 smaller than III-V RTDs grown on lattice matched substrates.<sup>1,2</sup> Progress has been made in the area of high speed electronics using Si/SiGe, but at this time there is not a significant cost

advantage, especially when taking into consideration that substrates on which the Si/SiGe structures are grown are incompatible with the low resistivity substrates used for conventional low cost silicon circuitry.

Mixed material integration has also been achieved by use of flip-chip or bump bonding. One of the disadvantages of using flip-chip instead of thin film integration is that one is not able to process both sides of the devices. Also, it is much easier to planarize thin film devices with polyimide or benzocyclobutene (BCB) since they are on the order of 600 Å to 10  $\mu$ m thick. After planarization a second layer of devices/interconnects can be stacked on top creating a three dimensional circuit. As for the thermal advantage of flip-chip heterojunction bipolar transistors (HBTs), or field effect transistors (FETs), it is mitigated by the fact that the solder must connect the device to the ground plane.

Successful demonstration of thin film device integration on host substrates establishes the feasibility of mixed-material integration for Si-based electronics. The ability to fabricate any type of high speed device with top and bottom processing bonded to virtually any type of substrate will enable significant increases in circuit performance and functionality. Mixed material integration represents a form of wafer scale packaging, in which the thin film devices, the host substrates, and the bonding and processing of these components produce an integrated package.

Thin film semiconductor device integration to host substrates such as Si circuits has already been successfully applied to an optical receiver<sup>3</sup> and an optoelectronic integrated circuit (OEIC)<sup>4</sup> using thin film GaAs-based MESFETs and a 10 GHz

amplifier<sup>5</sup> using a pseudomorphic thin film GaAs-based HEMT device. A thin film HBT has been successfully integrated which produced record high power-gain cutoff frequency in excess of 400 GHz.<sup>6</sup> These thin film devices are created by either substrate removal or epitaxial lift-off (ELO) of the device active layers from the growth substrate. Both of these processes utilize single crystal device epilayers that are grown lattice matched (or near lattice matched) on a growth substrate to ensure high material quality. Between these epilayers of interest and the growth substrate, selective or stop etch layers are grown if necessary, to facilitate removal of the substrate from the epilayers of interest. This material is then generally partially or fully processed into devices, the substrate is removed through selective chemical etching, and the thin film devices are transferred, aligned, and bonded to an arbitrary host substrate (such as a Si circuit). This process has yielded thin film devices that are comparable to or better than (due to removal of the substrate) conventional devices.

The thin film device integration process can be performed before or after the devices of interest have been fabricated. The devices in this study were all pre-processed for higher density of devices fabricated per unit area, thereby lowering cost. Also, all pre-processing of the thin film compound semiconductor device is separate from the manufacture of the host substrate (for example, a complex silicon circuit or a high thermal conductivity, high resistance substrate). Thus, the processes prior to integration can be separately optimized and neither compromises the other.

To complement this work, characterization of thin film deposited passive components on free standing polyimide held taut by a 4 or 6 inch titanium frame

hereinafter termed "flex" were also evaluated. Much interest has been shown in thin film passive devices as an alternative to more conventional passive components.<sup>7-17</sup> This study concentrates on thin film passive components on free standing flex provides an alternative to silicon passives which are frequency limited by the lossy substrate and to the III-V passives components which occupy large amounts of area on costly substrates. These thin film passives on flex have the ability to be integrated via lamination on any host substrate of choice. This gives an added flexibility to integrate mixed materials in a variety of packages ranging from silicon substrates to ceramic or even plastic packages.

The work presented in this thesis is divided into two parts, the Chapters 1 through 5 deal with fabrication, integration and characterization of the active components for use in mixed material integration while Chapter 6 consists of all the passive component fabrication, testing and evaluation. Chapter 7 gives a summary of the completed work, and finally, Chapter 8 will outline future directions.

#### **ENDNOTES**

<sup>1</sup> N. Evers, O. Vendier, C. Chun, M. R. Murti, J. Laskar, N. M. Jokerst, T. S. Moise, and Y.-C. Kao, 38<sup>th</sup> Electronic Materials Conference, (1996).

<sup>2</sup> N. Evers, O. Vendier, C. Chun, M. R. Murti, J. Laskar, N. M. Jokers t, T. S. Moise, and Y.-C. Kao, *IEEE Electron Device Letters*, **17**(9) (1996).

<sup>3</sup> T. Morf, C. Brys, P. De Dobbelaere, P. Van Daele, P. Demeester, T. Martinson, and W. Bachtold, *IEEE GaAs IC Symposium 1995*, 189 (1995).

<sup>4</sup> I. Pollentier, P. Demeester, P. Van Daele, D. Rondi, G. Glastre, A. Enard, and R. Bondeau, 3<sup>rd</sup> Int. Conf. of InP and Rel. Mat. 1991, 268 (1991).

<sup>5</sup> P. G. Young, R. R. Romanofsky, S. A. Alterovitz, R. A. Mena, and E. D. Smith, *IEEE Microwave and Guided Wave Lett.*, **3** 107 (1993).

<sup>6</sup> R. Pullela, Q. Lee, B. Agarwal, D. Mensa, J. Guthrie, L. Saoska, and M. Rodwell, 1997 *IEEE Device Research Conference*, III.B-2 (1997).

<sup>7</sup> H. Yoshino, T. Ihara, S. Yamanaka, and T. Igarashi, *IEEE/CHMT '89 Japan IEMT Symposium*, 156 (1989).

<sup>8</sup> C. P. Yue, C. Ryu, J. Lau, T. H. Lee, and S. S. Wong, *IEEE IEDM*, 6.5.1 (1996).

<sup>9</sup> P. K. Singh, R. S. Cochrane, J. M. Borrego, E. J. Rymaszewski, T. M. Lu, and K. Chen, *1994 IEEE MTT-S*, 1457 (1994).

<sup>10</sup> T. Lenihan, L. Schaper, Y. Shi, G. Morean, and J. Parkerson, *1996 Electronic Components and Technology Conference*, 119 (1996).

<sup>11</sup> H. Okabe, H. Yamada, M. Yamasaki, O. Kagaya, K. Sekine, and K. Yamashita, *IEEE Transactions on Components, Packaging, and Manufacturing Technology - Part B*, **21**(3) 269 (1998).

<sup>12</sup> K. Chen, M. Nielsen, S. Soss, E. J. Rymaszewski, T.-M. Lu, and C. T. Wan, *IEEE Transactions on Components, Packaging, and Manufacturing Technology - Part B*, **20**(2) 117 (1997).

<sup>13</sup> S. Byeon and Y. Tzeng, *IEEE Transactions on Electronic Devices*, **37**(4) 972 (1990).

<sup>14</sup> R. R. Kola, M. Y. Lau, S. Duenas, H. Y. Kumangai, P. R. Smith, R. C. Frye, K. L. Tai, and P. A. Sullivan, *1997 International Symposium on Advanced Packaging Materials*, 71 (1997).

<sup>15</sup> P. Chahal, R. R. Tummala, M. G. Allen, M. Swaminathan, *IEEE Transactions on Components, Packaging, and Manufacturing Technology - Part B*, **21**(2) 184 (1998).

<sup>16</sup> J. Crols, P. Kinget, J. Craninckx, and M. Steyaert, 1996 Symposium on VLSI Circuits Digest of Technical Papers, 28 (1996).

<sup>17</sup> H. Kapadia, H. Cole, M. Nielsen, and N. Krishnamurthy, ATW 1998 Chateau Elan, (1998).

#### CHAPTER II

#### THIN FILM INP-BASED SEMICONDUCTOR DEVICE INTEGRATION PROCESS

Hybrid integration through the bonding of thin film devices to arbitrary host substrates is a powerful emerging tool for mixed material integration. The thin film devices and host substrate can be independently grown, processed, and optimized and joined in the bonding process without concern for lattice matching. The thin film epitaxial structure of interest, as grown, includes a sacrificial or stop etch layer grown between the epitaxial devices of interest and the growth substrate, and sometimes the bottom active layer of the device can be used as the stop etch layer. The thin film epitaxial devices of interest (and any associated metals, dielectrics, etc. used in the pre-bonded device formation) are separated from the growth substrate either by selectively laterally etching the sacrificial layer (called epitaxial lift-off, ELO), or by selectively etching away the substrate, stopping at the stop etch layer (called substrate removal).

Using handling layers and transfer techniques, these thin film materials can be transferred after separation, processed on both sides of the device, aligned, and bonded onto host substrates of arbitrary composition, including silicon circuits, polymers, and high thermal conductivity ceramics. Processing of these thin film materials and devices can be performed without degradation of the quality of the material or the circuit, and, in fact, some devices benefit from the direct top and bottom contact options when the growth substrate is removed. The thin film devices can range from hundreds of angstroms to tens of microns thick, and, after bonding to the host substrate, the integrated host substrate is nearly planar, thus enabling the use of standard microelectronic processing techniques to complete the integration.

In the InP system, selective etching of the InP growth substrate can be accomplished using an HCl or HCl: $H_3PO_4$  ((3:1) or (4:1)) solution to remove the thin film device from the host substrate. There is a high degree of selectivity between InP and undoped InGaAs for these etch solutions, so InGaAs can be used as a stop etch layer. Devices grown and fabricated at Raytheon/TI Systems for the substrate removal process utilize the same growth procedure and processing steps as the conventional devices.

The InP-based devices such as the resonant tunneling diode (RTD), the tunneling hot electron transfer amplifier (THETA), and the heterostructure bipolar transistor (HBT) in this study have a highly doped InGaAs layer as the first growth layer, which may be used as the stop etch layer. However there is a decrease in the selectivity of the etch when the InGaAs is highly doped, which causes the InGaAs to be etched slightly during the substrate removal process. This can be eliminated by the growth of a thin (100 -2000Å) undoped InGaAs layer between the thin film device and the growth substrate.

#### 2.1 Standard Substrate Removal and Bonding

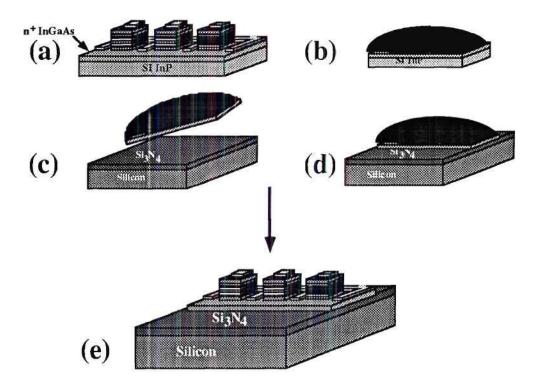

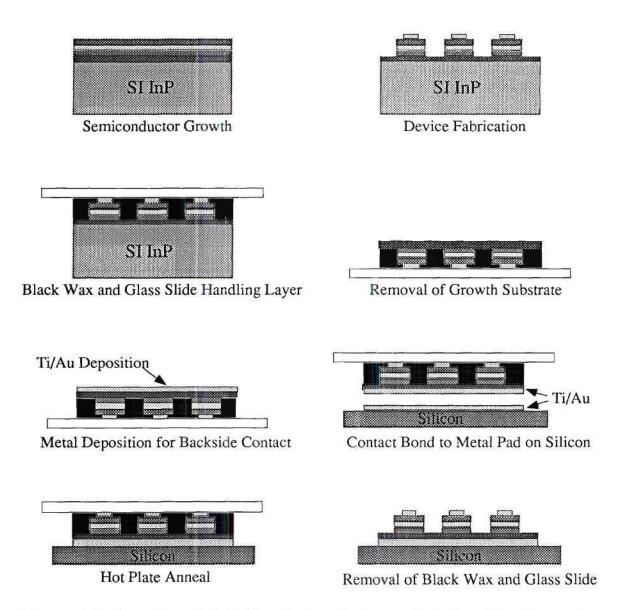

Figure. 2.1 Substrate removal and bonding of RTDs onto silicon host substrates.

Figure 2.1 illustrates the basic steps for substrate removal and bonding to a host substrate. A handling layer is used to preserve the integrity and relative spatial orientation of the thin film devices. This Apiezon W handling layer is applied before the substrate removal and also serves to protect the devices from the substrate removal etch. After the substrate is fully removed, the samples are placed in DI water and then transferred and bonded to the host substrate. The thin film devices can be bonded to the host substrate through either a contact bond of semiconductor-semiconductor or semiconductor-metal, or

a bond using a partially cured epoxy, BCB, or polyimide. The disadvantages of this process are the inability to align, to process both sides of the device, and to flip devices if desired. Also, since the contact bond is not a metal-metal bond, the bond is not as strong and adhesion becomes an issue. Therefore, epoxy or partially cured BCB or polyimide is necessary for a reliable bond.

#### 2.2 Modified Substrate Removal and Bonding

Efforts have been made to study the feasibility of processing both sides of the thin film device and aligning the device using a variety of techniques. Figure 2.2 shows one possible alternative thin film semiconductor integration technique.

The substrates were bonded to a thin glass slide using a small amount of black wax to be used as a rigid handling layer. Removal of the host substrate was performed by placing the devices in a HCl:H<sub>3</sub>PO<sub>4</sub> (4:1) etch. The etch uniformity was improved by the weight of the glass slide keeping the substrate inverted in the etch solution. Metal was deposited onto the backside of the devices using an e-beam evaporator. The devices were then bonded to a metal pad using a hot plate anneal. After the anneal, the devices were submersed in TCE overnight for removal of the black wax and the glass slide was removed. This process kept the devices under constant rigid support while still maintaining the ability to evaporate contacts on both sides of the devices. The adhesion of the devices to the pad on the host substrate was excellent. Issues of alignment are currently being investigated including use of photoresist in place of the black wax layer.

Figure. 2.2 Transfer of thin film devices to host substrate without use of transfer diaphragm. Contacts are made on both sides of the device.

#### 2.3 Integration Utilizing a Transfer Diaphragm

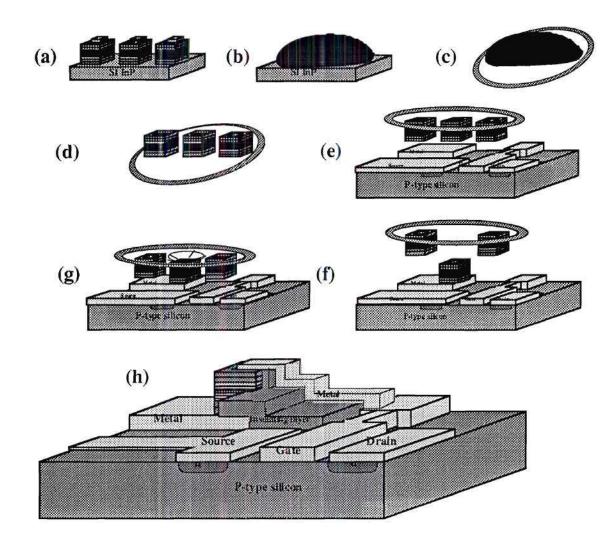

A drawback to the techniques illustrated in Figure 2.1 and 2.2 was the inability to precisely align the thin film devices with respect to features on the host substrate. This causes difficulty in the manufacturable final metallization that may be necessary, in some applications, to connect the thin film devices to a host silicon circuit. An approach that is more consistent with post processing masking steps involves transferring the thin film devices to the host substrate using a transparent transfer diaphragm.<sup>1-3</sup> Thus, the thin film devices can be aligned with respect to features on the host substrate, and there is the versatility to pick and place optimized devices, as shown in Figure 2.3. The devices or arrays of devices are bonded to the silicon circuit using the standard transfer techniques with a transfer diaphragm. This involves the application of the black wax handling layer and removal of the growth substrate as shown in Figure 2.1. The thin film devices are then contact bonded to the transfer diaphragm. After bonding to the transfer diaphragm the handling layer is removed using TCE. The diaphragm is then inverted and lowered into contact with the host substrate. The bond to the host substrate is made so that the metal pads of the device that were deposited on top of the device, but now inverted, are aligned with the pads on the host substrate removal of the handing layer. This enables a thermally and electrically conductive, and mechanically stable metal/metal bond to be realized between the thin film devices and the host substrate (such as a silicon circuit). Finally, this method enables the processing of both sides of the thin film devices while under substrate (either growth or host) support.

Figure. 2.3 Substrate removal and bonding using a transfer diaphragm. The transfer diaphragm enables the alignment and bonding of the thin film devices to the host substrate as well as the ability to process both top and bottom of the device. Post-processing of top contact pads is done after device has been contact bonded to the host substrate.

#### **ENDNOTES**

<sup>1</sup> K. H. Calhoun, C. B. Camperi, and N. M. Jokerst, *IEEE Photonics Tech. Letters*, 5(2), (1993).

<sup>2</sup> S. Fike, B. Buchanan, N. M. Jokerst, M. A. Brooke, T. G. Morris, and S. P. Deweerth, *IEEE Photonics Tech. Letters*, 7(10), 1168 (1995).

<sup>3</sup> O. Vendier, N. M. Jokerst, and R. P. Leavitt, *IEEE Photonics Tech. Letters*, 8(2), (1996).

#### CHAPTER III

#### THIN FILM RESONANT TUNNELING DIODES

Resonant tunneling was first proposed by Tsu and Esaki in 1973.<sup>1</sup> Their theoretical analysis of one-dimensional superlattices with periods shorter than the electron mean free path concluded that interesting transport properties such as negative differential resistance (NDR) would occur in such structures. In 1974, this resonant tunneling producing an NDR region was first observed.<sup>2</sup> The main factor in realizing such a structure was the ability to precisely control the thickness, composition, and quality of the such thin layers. With the technique of growing such thin multilayer structures using molecular beam epitaxy (MBE), resonant tunneling in these structures was finally detected.

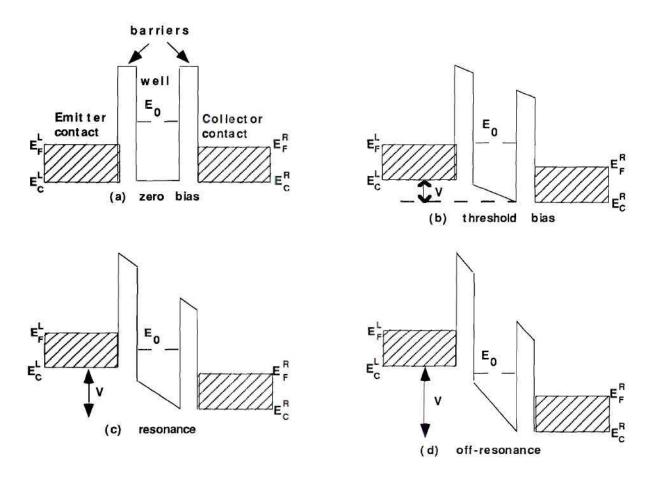

A resonant tunneling diode (RTD) in its simplest form consists of an undoped well sandwiched between two higher conduction band undoped barriers and heavily doped emitter and collector regions. The heavily doped emitter and collector regions are degenerate states in which the donors are present in such high concentrations that they are no longer considered to be composed of discrete non-interacting states. Instead, they are considered to form a band. The Fermi level in these regions may lie within the conduction band if the conduction band electron concentration exceeds the effective density of states. In the well between the barriers and these degenerate regions, there are quasi-bound, or resonant, states that are formed. These resonant states will accommodate electrons when the energy of the electrons in the degenerate region are the same as the resonant state. Figure 3.1 shows the different bias conditions of the RTD: (a) zero bias, (b) threshold bias, (c) resonance, and (d) off-resonance. At (a) zero bias, the energy of the electrons in the emitter is below the energy of the first resonant (or quasi-bound state) in the well. At (b),

threshold, the energy of the local Fermi level in the emitter is equal to the energy of the first resonant well. At (c), resonance, there are electrons in the emitter conduction band that are equivalent to the first resonant state energy and these electrons tunnel through the barriers via this resonant state. At (d) off-resonance, the conduction band edge in the emitter is at a higher energy level than the first resonant state.<sup>3</sup> Resonant tunneling diodes are well known for their high speed switching characteristics and several prototype circuits that take advantage of their unique electrical characteristics have been demonstrated. For example, room temperature operation of a full-adder integrated circuit that uses resonant-tunneling bipolar transistors and conventional transistors has been demonstrated.<sup>4</sup> In related experiments, RTDs have been vertically integrated to achieve a multiple negativedifferential resistance characteristic for use in frequency multiplication<sup>5</sup>, multistate memory<sup>6</sup>, analog-to-digital conversion<sup>7</sup>, and static access memory circuits.<sup>8</sup> By successfully separating prefabricated pseudomorphic AlAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InAs RTDs from their host InP substrate followed by bonding to silicon, the feasibility of future integration of quantum device technology with conventional silicon circuitry may be realized. This future integration offers the possibility of high-speed, enhanced functionality circuits which take advantage of the multistate characteristics of the RTD and the high-integration density and high thermal conductivity associated with silicon technology.<sup>9, 10</sup> Further, multi-stack RTDs integrated with silicon electronics provide high packing density and eliminate the necessity for interconnects between the RTDs after substrate removal.<sup>11</sup> Finally, through this approach, both the RTD and silicon device structures can be separately optimized prior to integration.

Figure 3.1 Conduction band profiles of the RTD under the conditions of (a) zero bias, (b) threshold bias, (c) resonance, and (d) off-resonance. At (a) zero bias, the energy of the electrons in the emitter are below the energy of the first resonant (or quasi-bound state) in the well. At (b), threshold, the energy of the local Fermi level in the emitter is equal to the energy of the first resonant well. At (c) resonance, there are electrons in the emitter conduction band that are equivalent to the first resonant state energy and these electrons tunnel through the barriers via this resonant state. At (d), off-resonance, the conduction band edge in the emitter is at a higher energy level than the first resonant state.<sup>3</sup> The local Fermi levels in the emitter and collector are  $E_{F}^{L}$  and  $E_{F}^{R}$ , and the energies of the conduction-band edge in the emitter and collector are  $E_{C}^{L}$  and  $E_{C}^{R}$ .<sup>3</sup>

#### 3.1 Growth and Fabrication

For this work, the high PVR RTD layers were grown by Raytheon/TI using molecular beam epitaxy using group III and group V elemental sources. A cross-sectional layer schematic of the as-grown RTD sample is shown in Figure 3.2(a). The 20 Å AlAs RTD barrier layers are under a tensile strain of 3.2% when deposited on the larger lattice-constant  $In_{0.53}Ga_{0.47}As$  crystal. The RTD quantum well consists of 30 Å of InAs, which is compressively strained by 3.5%, sandwiched between symmetric 5 Å  $In_{0.53}Ga_{0.47}As$  layers. The InAs layer serves to increase the PVR by decreasing the ground state energy of the quantum well while increasing the energy separation between the quantum-confined bound states as a result of the reduced electron effective mass.<sup>12, 13</sup>

|           |      | Si host                        | substrate |      |   |

|-----------|------|--------------------------------|-----------|------|---|

| si InP    |      | Si <sub>3</sub> N <sub>4</sub> | 5000      |      |   |

| nGaAs:SI  | 5000 | A                              | InGaAs:Si | 5000 | Å |

| nGaAs:Si  | 500  | Á                              | InGaAs:Si | 50 0 | Å |

| nGaAs     | 20   | Å                              | InGaAs    | 20   | Å |

| AIAs      | 20   | Å                              | AIAs      | 20   | Å |

| nGaAs     | 5    | Å                              | InGaAs    | 5    | Á |

| InAs      | 30   | Å                              | InAs      | 30   | Å |

| nGaAs     | 5    | Å                              | InGaAs    | 5    | Å |

| AIAs      | 22   | Å                              | AIAs      | 22   | Å |

| InGaAs    | 20   | Å                              | InGaAs    | 20   | Å |

| InGaAs:Si | 500  | A                              | InGaAs:Si | 50 0 | Å |

| InGaAs:Si | 1500 | A                              | InGaAs:Si | 1500 | Å |

Figure 3.2 Structure of the high PVR RTD (a) before and (b) after substrate removal and bonding to the host substrate.

The thin film devices were bonded to silicon using the standard substrate removal and bonding process explained in Section 2.1. The cross-sectional schematic after bonding to the host substrate is shown in Figure 3.2(b).

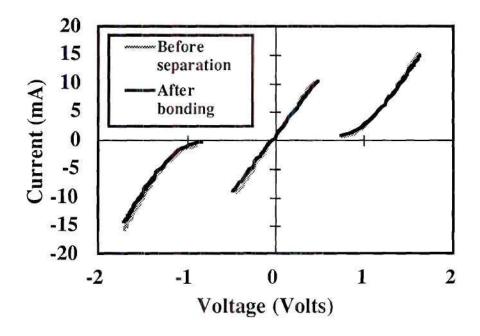

## 3.2 Experimental Results of Thin Film RTDs on Silicon

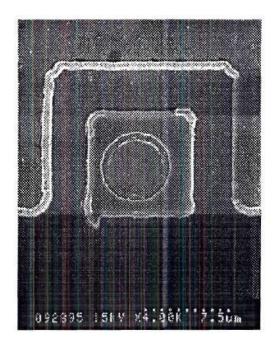

Following the bonding procedure shown in Figure 2.1, the thin film RTDs were placed in a scanning electron microscope (SEM) for inspection. Consistent with the results of previous bonding demonstrations,<sup>14-16</sup> the RTDs exhibited no signs of structural degradation, as shown by the electron micrograph in Figure 3.3. A comparison of the current-voltage characteristics for the as-grown and bonded 256  $\mu$ m<sup>2</sup> area RTD is shown in Figure 3.4 The peak current and PVR are very similar, indicating that the pseudomorphic RTD retains its high quality during the separation and bonding process. Similar trends were observed for all five of the samples investigated independent of device area (16  $\mu$ m<sup>2</sup> - 256  $\mu$ m<sup>2</sup>). The highest measured PVR for the thin film RTD integrated onto Si was 30, as seen in Figure 3.4.

Figure 3.3 SEM of a 64  $\mu m^2$  high PVR RTD after substrate removal and bonding.

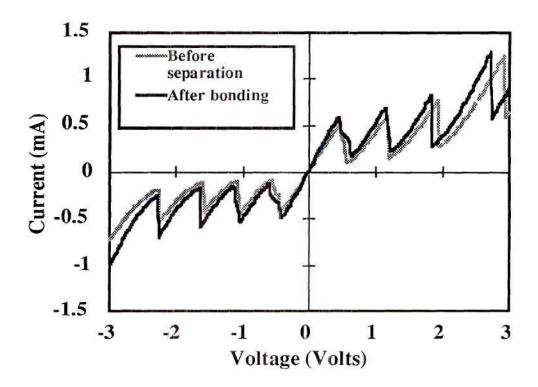

A comparison of the current-voltage characteristics for the as-grown and bonded thin film four-stack resonant tunneling diode heterostructure ( $16 \ \mu m^2$  area) is shown in Figure 3.5. Although the PVRs remain nearly constant before and after integration, some deviations from the as-grown current-voltage characteristics were observed. Since these structures were not optimized for substrate removal and bonding, these deviations from the as-grown structures may be due to the variations in the adhesion of the RTD structure to the host substrate and the non-uniform removal of the InP substrate, which may have caused some areas of the highly doped InGaAs to be partially etched. The combination of spatial variation in etching and bonding quality may have resulted in slight non-uniform variations in the I-V characteristics for different devices. RTD structures optimized for substrate removal and bonding may eliminate the variation in adhesion and etching.

Figure 3.4 256  $\mu m^2$  high PVR RTD before and after substrate removal and bonding. The corresponding positive and negative PVRs were 13 and 21, respectively.

Figure 3.5 Four vertically stacked 16  $\mu m^2$  RTDs before and after substrate removal and bonding.

### 3.3 Empirical SPICE Model and MDS Diode Model

In an effort to better understand the slight variations in the DC characteristics of the RTDs before and after substrate removal and bonding, and for modeling of device performance for design of silicon circuitry utilizing the thin film devices, a simplified empirical SPICE model was used. The Tsu-Esaki formula for current utilizing an effective mass approximation is<sup>1</sup>

$$J = \frac{em^{*}kT}{2\pi^{2}\hbar^{3}} \int_{0}^{\infty} dET(E,V) \bullet \ln\left[\frac{1 + e^{(E_{F} - E)/kT}}{1 + e^{(E_{F} - E - eV)/kT}}\right],$$

(3.1)

where m<sup>\*</sup> is the effective mass, k is Boltzmann's constant (1.38 x  $10^{-23}$  J/K), T is the temperature in Kelvin,  $\hbar$  is Planck's constant (1.054 x  $10^{-34}$  J-s), and  $\Gamma$  is the resonance width.

The transmission coefficient for this simplified analysis is approximated by a Lorentzian,<sup>17</sup>

$$T(E,V) = \frac{\left(\frac{\Gamma}{2}\right)^2}{\left[E - \left(E_r - \frac{eV}{2}\right)\right]^2 + \left(\frac{\Gamma}{2}\right)^2},$$

(3.2)

where E is the energy measured up from the emitter conduction band edge,  $E_r$  is the energy of the resonant level to the bottom of the well at its center and  $\Gamma$  is the resonance width.<sup>17</sup>

The assumptions made are (1) the barriers are equal widths and (2) half the voltage drop falls from the emitter to the center of the well. Since (2) is not always valid, eV/2 can be replaced by eVn with n determined from fitting or analysis. For small  $\Gamma$ , T(E,V) is negative except when E is close to resonance,  $E \approx E_r - eV/2$ . Since  $\Gamma$  is approximately 1 meV or less for even extremely thin barriers,  $\Gamma << kT$ , so substituting  $E = E_r - eV/2$ gives<sup>17</sup>

$$J = \frac{em^{*}kT\Gamma}{4\pi^{2}\hbar^{3}} \ln\left[\frac{1 + e^{(E_{F} - E_{r} + eV/2)/kT}}{1 + e^{(E_{F} - E_{r} - eV/2)/kT}}\right] \bullet\left[\frac{\pi}{2} + \tan^{-1}\left(\frac{E_{r} - \frac{eV}{2}}{\frac{\Gamma}{2}}\right)\right].$$

(3.3)

This formula gives the proper form for the lineshape, but the physical values may depart from their actual values. This is due to an oversimplified model which is effective for circuit model applications, but not for physical modeling of an RTD device. By using the Tsu-Esaki current density formula, a separation of variables approximation was utilized to reduce the current density formula to a one dimensional integral. In any device in which multiple sub-bands are coupled unphysical results such as current spikes can occur in the model. The Lorentzian approximation for the transmission coefficient has a delta-function-like nature which selects out only electrons very close to the resonance, but the dependance of the transmission peak on voltage was neglected. To make the model more realistic, voltage dependance of the transmission coefficient, multiple bands, band bending, as well as a more physical approach to incorporate the voltage drop across the collector spacer layer which physically causes voltage spreading, and a more intense numerical integration of the current density formula must be incorporated.<sup>17,18</sup>

The simplified equation for circuit modeling can be written in the following form<sup>17</sup>:

$$J_1(V) = A \ln \left[ \frac{1 + e^{(B - C + n_1 eV)/kT}}{1 + e^{(B - C - n_1 eV)/kT}} \right] \bullet \left[ \frac{\pi}{2} + \tan^{-1} \left( \frac{C - n_1 eV}{D} \right) \right], \quad (3.4)$$

where  $A = \frac{em^* kT\Gamma}{4\pi^2 \hbar^3}$ ,  $B = E_F$ ,  $C = E_r$ ,  $D = \frac{\Gamma}{2}$ , and  $n_1 = \frac{1}{2}$  or determined from fitting or analysis. A and D are determined by the value of  $\Gamma$  assuming temperature remains constant.

Formula (3.4) gives the resonant tunneling current and the negative differential resistance for the first resonance, but the increasing valley current resulting from inelastic scattering, non-resonant tunneling through higher lying quasi-continuum levels, and the

thermionic current that flows over barriers still need to be included. The increasing valley current can be represented by a simple diode form<sup>17</sup>:

$$J_2(V) = H(e^{n_2 eV/kT} - 1).$$

(3.5)

If second or higher resonances are desired, the addition of more components in the form of  $J_1$  can be used. So the sum of the external and tunneling current give the total current,

$$J(V) = J_1(V) + J_2(V).$$

(3.6)

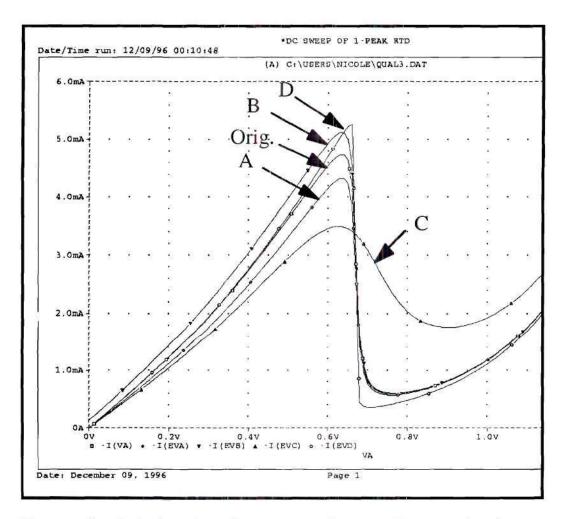

A SPICE simulation was used to investigate the changes in the current-voltage characteristics resulting from the changes in the device structure. The program is shown in Figure 3.6. By varying the parameters A, B, C, and D in  $J_1$ , one can fit the peak height, peak width and valley current to give an understanding of what parameters can cause a shift in the current-voltage curves.

```

*DC SWEEP OF 1-PEAK RTD

.PARAM A = 0.0011

.PARAM B = 0.034

.PARAM C = 0.067

.PARAM D = 0.0009

.PARAM n1=0.10, n2=0.110

.PARAM H = 1.6E-5

.PARAM VT0 = 0.0259; = kT/q

.PARAM PI = 3.1415926

.FUNC NLG(B,C,n1,X) {1+exp((B-C+n1*X)/VT0)}

.FUNC DLG(B,C,n1,X) {1+exp((B-C-n1*X)/VT0)}

.FUNC ATA(C,D,n1,X) {PI/2 + atan((C-n1*X)/D)}

G110VALUE={A*log(NLG(B,C,n1,V(1,0))/DLG(B,C,n1,V(1,0)))*ATA(C,D,n1,V(1,0))}

G220 VALUE = {H * (exp(n2*V(2,0)/Vt0) - 1)}

R1 3 1 100

R2 1 2 65

VA301VOLT

.DC VA 0 2 .01

.probe

.END

```

Figure 3.6 SPICE program for physics-based DC curves

Figure 3.7 Variations in DC response of the RTDs resulting from changes in the parameters in the resonant tunneling current equation.

| Parameters | Fitted Values | Varied Values |  |

|------------|---------------|---------------|--|

| A          | 0.0011        | 0.0010        |  |

| B          | 0.034         | 0.038         |  |

| С          | 0.067         | 0.071         |  |

| D          | 0.0009        | 0.0001        |  |

Table 3.1 Fitted and varied parameter values for the resonant tunneling current equation. Fitted values were used for the InP-based RTD for circuit simulations. Varied values were used to show how the DC characteristics change with changes in  $E_F$  (B),  $E_r$  (C), and  $\Gamma$  (A and D).

Changes were made in the peak and valley currents by the variation of the parameters as shown in Table 3.1. There was little to no shift seen in the voltage where the peak current occurred as the parameters were varied. It had been observed that there was little change in the peak-to-valley ratio of the RTDs before and after substrate removal and bonding, yet there was a shift in the voltage where the peak occurred and some slight changes in the peak and valley current. Changes in the active device because of relaxation of strain after substrate removal and bonding could cause some of the effects observed, or the shift in voltage that is being seen may partially be because of a change in resistance of the contacts due to nonuniform adhesion of the thin film devices on the host substrate.

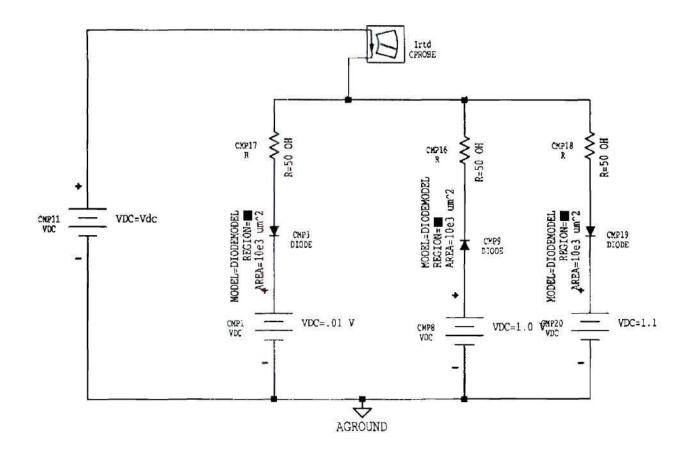

Using MDS, a circuit consisting of diodes was used to simulate the current-voltage characteristics of the RTD as shown in Figure 3.8.

Figure 3.8 A large signal model in MDS for simulation of current-voltage characteristics of RTD.

In Figure 3.9, a resistor is put in series with the RTD model to simulate an increase in series resistance after substrate removal and bonding.

Figure 3.9 A resistor is added in series with the model for simulation of the voltage shift which occurred for the thin film RTDs.

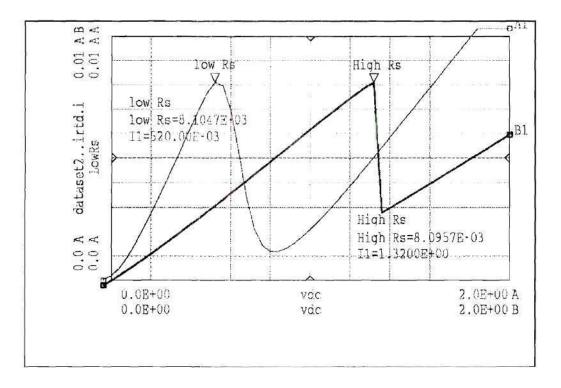

Figure 3.10 shows the DC characteristics of the RTD with increased series resistance. An increased series resistance causes the peak and valley current to shift to the right as well as increasing the valley current and lowering the rise of the extrinsic current. The changes in the DC characteristics before and after substrate removal and bonding differ slightly from device to device. All effects are within the difference of DC characteristics

from device to device on-wafer. An interplay between some relaxation of the strain intentionally incorporated into the device and some stresses induced from nonuniform bonding of the contact pads may have caused the changes in the DC characteristics between the on-wafer and thin film device. Thin film RTDs that were bonded utilizing a semiconductor-metal bond and those utilizing an annealed metal-metal showed more consistent results between the on-wafer and thin film devices. The semiconductor-metal bond maintained the same or a slightly increased voltage for the peak current showing uniform bonding with little to no increased series resistance, while the annealed metal-metal bond consistently showed a decreased series resistance. There were still decreases in the peak and valley currents, which may have been caused by slight changes in the strain of the active layers of the device after substrate removal and bonding.

Figure 3.10 DC characteristics of low and high series resistance RTDs modeled using MDS.

### 3.4 Process Optimization for Circuit Integration

Before integrating resonant tunneling diodes (RTDs) into a silicon circuit, an experiment was performed to determine the most precise way to integrate thin film RTDs which would maintain the DC characteristics. The devices of interest were low current RTDs which had been fabricated with a thick planarizing nitride on-wafer. 6  $\mu$ m devices were chosen for the initial integration since these were the lowest current devices on wafer that had yielded close to 100% on wafer. Initial integrations of thin film RTDs on silicon using the higher current RTDs with a thinner planarizing nitride had produced a slight shift in the I-V characteristics. This shift had been within the range of shift of the on-wafer devices. For the lower current, thicker nitride, the shift after substrate removal and bonding was more significant and could no longer be ignored. I-V characteristics of on-wafer 6  $\mu$ m RTDs is shown in Figure 3.11.

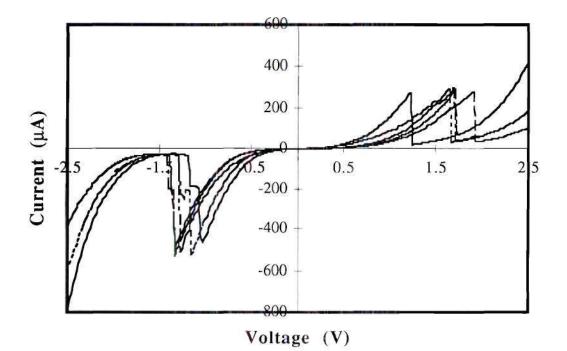

Figure 3.11 On wafer DC characteristics of low current 6  $\mu$ m RTD's with thick planarizing nitride.

After substrate removal and bonding, the DC characteristics of these devices is shown below in Figure 3.12.

Figure 3.12 Low current 6  $\mu$ m RTD's with thick planarizing nitride after substrate removal and bonding.

To reduce the strain of the nitride on the thin film devices, the nitride which was not underneath the contact pads were removed. Two different samples were used in this process. On one sample the nitride was removed using a wet etch while the other was removed by a reactive ion etch (RIE). The sample which under went the wet etch maintained the DC characteristics on-wafer while the RIE sample showed degradation in the DC response of the devices on-wafer, as shown in Figure 3.13.

Figure 3.13 Current-voltage characteristics of on wafer low current 6  $\mu$ m RTD's after RIE nitride removal.

The devices with the wet etch of nitride on wafer proceeded with substrate removal and bonding onto silicon. Figure 3.14 shows the DC characteristics of these thin film devices.

Figure 3.14 Low current 6  $\mu$ m RTD's after wet etch of nitride and substrate removal.

The statistics of the peak current and the voltage at which it was recorded is given in Tables 3.2 and 3.3.

|                    | On Wafer | Integrated with<br>Thick Nitride | On Wafer after<br>RIE of Nitride | Integrated after<br>Wet Etch of<br>Nitride |

|--------------------|----------|----------------------------------|----------------------------------|--------------------------------------------|

| Mean               | -0.5     | -1.23                            | -0.6                             | -0.52                                      |

| Median             | -0.5     | -1.28                            | -0.59                            | -0.51                                      |

| Standard Deviation | 0.0      | 0.13                             | 0.08                             | 0.01                                       |

| Minimum            | -0.5     | -1.34                            | -0.70                            | -0.54                                      |

| Maximum            | -0.5     | -1.04                            | -0.51                            | -0.51                                      |

Table 3.2 Statistics of the peak voltage for the negative NDR.

|                    | On Wafer | Integrated with<br>Thick Nitride | On Wafer after<br>RIE of Nitride | Integrated after<br>Wet Etch of<br>Nitride |

|--------------------|----------|----------------------------------|----------------------------------|--------------------------------------------|

| Mean               | -488.34  | -499.66                          | -425.08                          | -490.14                                    |

| Median             | -517.20  | -506.90                          | -405.60                          | -527.60                                    |

| Standard Deviation | 65.06    | 24.62                            | 45.78                            | 74.25                                      |

| Minimum            | -557.60  | -524.60                          | -493.00                          | -554.90                                    |

| Maximum            | -403.70  | -464.20                          | -396.10                          | -396.10                                    |

Table 3.3 Statistics of the peak current for the negative NDR.

The devices integrated with the thick planarizing nitride maintained their peak current, yet there was a large shift in the voltage corresponding to the peak current. Since the use of the RIE to remove the nitride also degraded the peak voltage of the RTDs, the wet etch of the nitride was used. These RTDs integrated onto silicon after wet etch on the planarizing nitride maintained their current-voltage characteristics.

### 3.5 Thin Film RTD Integrated with a Si Circuit

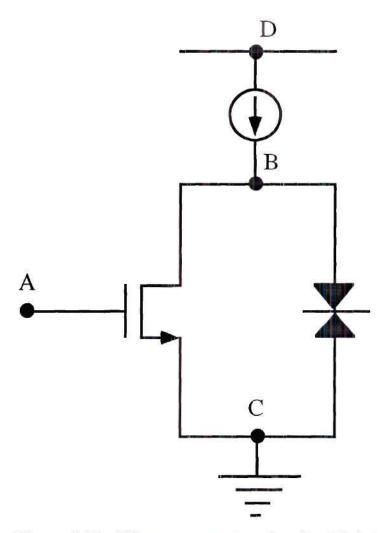

After process optimization of the thin film RTD, circuit integration was ready to begin. Below in Figure 3.15 is a circuit diagram of the silicon comparator circuit designed using an InP RTD. Appendix A gives a detailed step-by-step process of the actual circuit integration process.

Figure 3.15 Silicon comparator circuit with integrated InP RTD.

Figures 3.16 and 3.17 shown a 6  $\mu$ m RTD after successful integration with a silicon comparator circuit. The mesa defined before substrate removal, which defined the area of the entire thin film area after substrate removal, was approximately 200  $\mu$ m by 300  $\mu$ m and included the RTD and the original bonding pad. A contact pad the size of the area of the thin film area was created by metal lift-off in the region provided for circuit integration. After substrate removal, the thin film device was contact bonded to the bottom

pad. Polyimide was spun over the device to encapsulate it. A via was etched down to the contact pad of the RTD and a top contact was again defined by metal lift-off. Figure 3.17 gives a close-up of the RTD after integration.

Figure 3.16 Photograph of RTD integrated with Si comparator circuit.

Figure 3.17 Close-up of RTD integrated with a Si comparator circuit.

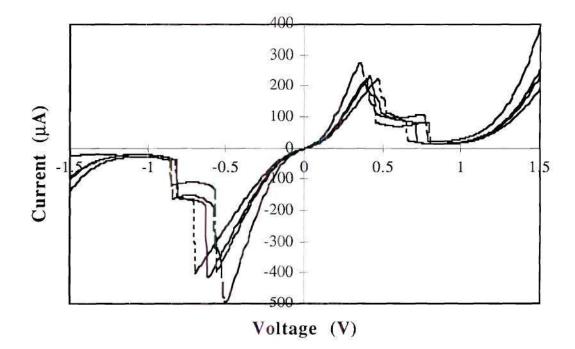

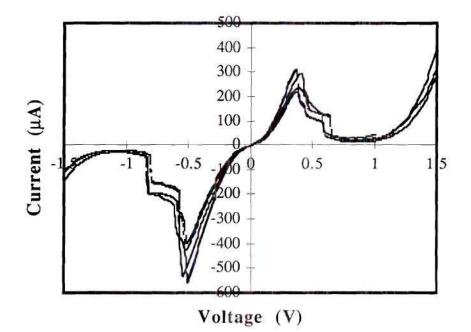

After the top contact was made, the RTD was separately tested to make sure there were no open contacts between the top and bottom contacts due to a break in the metal in the via for the top contact. The negative current voltage characteristics of the RTD which is used by the circuit in this particular configuration are shown in Figure 3.18.

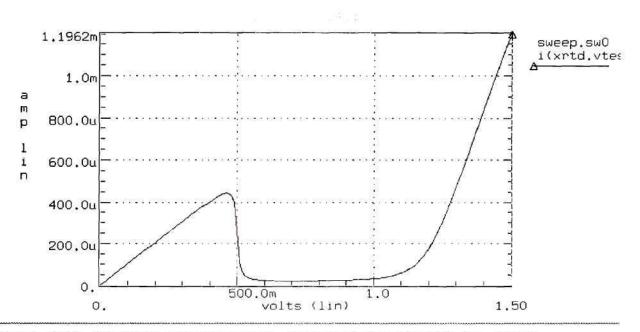

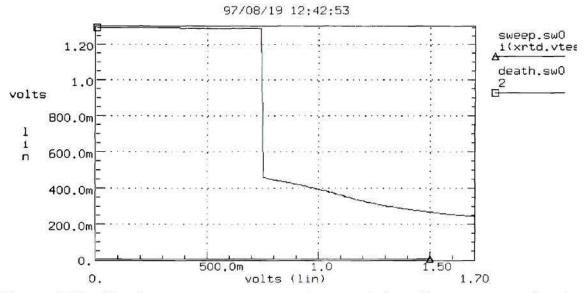

Figure 3.18 Negative region current-voltage characteristics of RTD after integration with comparator circuit.

Simulations utilizing the Pspice model of the RTD were performed before testing of the circuit. The simulated RTD current voltage characteristics and the actual characteristics matched well. The modeled RTD characteristics and the circuit characteristics with and without the RTD are shown in Figures 3.19 - 3.21.

Figure 3.19 Modeled current-voltage characteristics of RTD for circuit simulations.

Figure 3.20 Simulated current-voltage characteristics of comparator circuit without RTD.

Figure 3.21 Simulated current-voltage characteristics of comparator circuit with RTD.

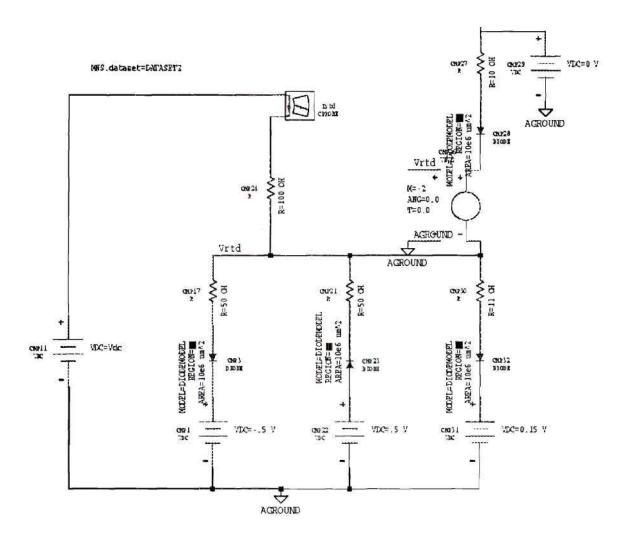

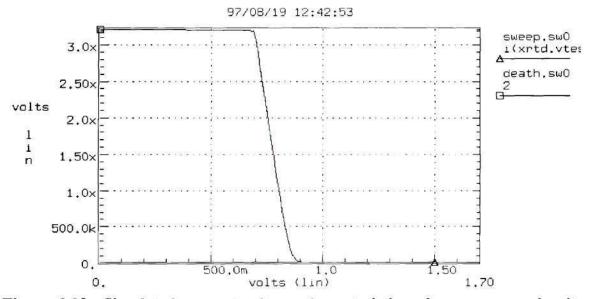

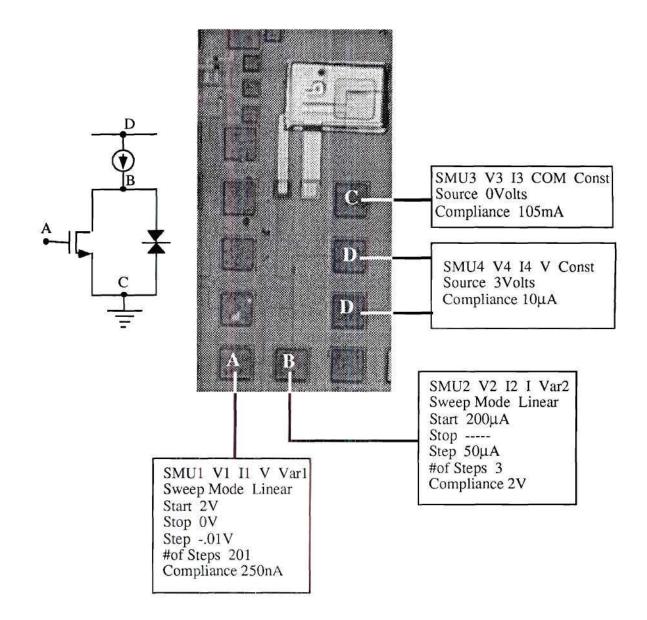

Finally, the comparator circuit was tested with and without an RTD integrated with it to compare the actual circuit performance with the simulated results. To test the circuit, a HP4145 was used. Figure 3.22 shows the bias conditions of the circuit.

Figure 3.22 Bias conditions for testing of comparator circuit with InP-RTD.

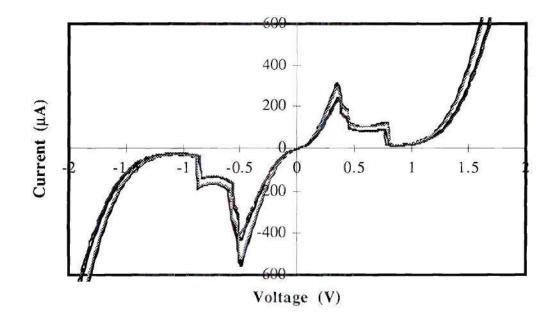

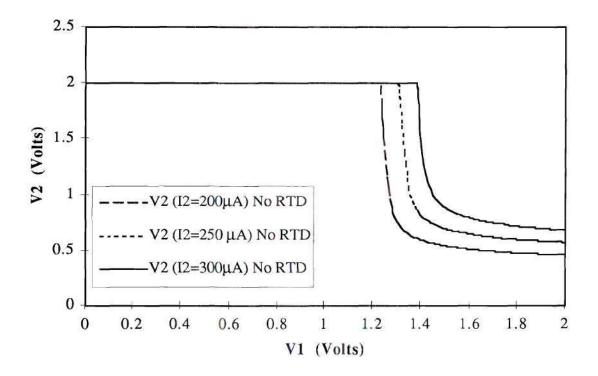

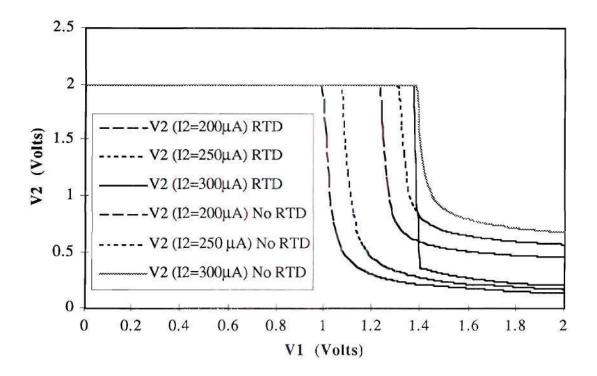

Performance of the comparator circuit without the RTD is shown in Figure 3.23. The comparator circuit with the RTD characteristics are shown in Figure 3.24. The RTD switches when the current defined as  $I_2$  reaches 300  $\mu$ A. The switch occurred at a voltage difference of 0.6 volts since the sweep was in the negative direction, starting at 2 volts.

The performance of the circuit agreed well with the modeled circuit as well as what was expected after initial measurements on the I-V characteristics of the RTD device which had been integrated.

Figure 3.23 Measured current-voltage characteristics of comparator circuit without RTD.

Figure 3.24 Measured current-voltage characteristics of comparator circuit with and without RTD. When the current reached 300  $\mu$ A, the RTD switched.

In conclusion, the PVR of the RTDs represented the highest reported to date on silicon. Substrate removal and bonding provided an effective approach for the integration of high PVR resonant tunneling diodes with silicon electronics. After thin film process optimization, a thin film InP-based high PVR RTD was successfully integrated with a silicon comparator circuit. These results are the first successful demostration of InP based electronics bonded to a silicon host substrate and integrated with a conventional silicon circuit.

#### **ENDNOTES**

<sup>1</sup> R. Tsu and L. Esaki, Appl. Phys. Lett., 22(11), 562 (1973).

<sup>2</sup> L. L. Chang, L. Esaki, and R. Tsu, Appl. Phys. Lett., 24(12), 593 (1974).

<sup>3</sup> H. Mizuta and T. Tanque, *The Physics and Applications of Resonant Tunnelling Diodes*. Cambridge University Press, (1995).

<sup>4</sup> A. C. Seabaugh, A. H. Taddiken, E. A. Beam III, J. N. Randall, Y.-C. Kao, and B. Newell, *IEDM Tech. Dig.*, 419 (1993).

<sup>5</sup> F. Capasso, S. Sen, and F. Beltran, *High Speed Semiconductor Devices*. New York: Wiley, (1990).

<sup>6</sup> S. Sen, F. Capasso, A. Y. Cho, and D. L. Sivco, *IEEE Electron Device Lett.*, 9, 533 (1988).

<sup>7</sup> R. C. Potter, A. A. Lakhani, D. Beyea, H. Hier, E. Hempfling, and A. Fathimulla, *Appl. Phys. Lett.*, **52**, 2163 (1988).

<sup>8</sup> T. Mori, S. Muto, H. Tamura, and N. Yokoyama, Japan. J. Appl. Phys., 33, 790 (1994).

<sup>9</sup> N. Evers, O. Vendier, C. Chun, M. R. Murti, J. Laskar, N. M. Jokerst, T. S. Moise, and Y.-C. Kao, 38<sup>th</sup> Electronic Materials Conference, (1996).

<sup>10</sup> N. Evers, O. Vendier, C. Chun, M. R. Murti, J. Laskar, N. M. Jokerst, T. S. Moise, and Y.-C. Kao, *IEEE Electronic Device Letters*, **17**(9), (1996).

<sup>11</sup> Y.-C. Kao, A. C. Seabaugh, and H. T. Yuan, 4th Int. Conf. on InP and Rel. Mat., 489 (1992).

<sup>12</sup> T. P. E. Broekaert, W. Lee, and C. G. Fonstad, Appl. Phys. Lett., 53, 1545 (1988).

<sup>13</sup> J. H. Smet, T. P. E. Broekaert, and C. G. Fonstad, J. Appl. Phys., 71, 2475 (1992).

<sup>14</sup> O. Vendier, N. M. Jokerst, and R. P. Leavitt, *IEEE Photonics Tech. Letters*, 8(2), (1996).

<sup>15</sup> C. Camperi-Ginestet, Y. W. Kim, N. M. Jokerst, G. Augustine, M. G. Allen, and M. A. Brooke, *IEEE Photon. Tech. and Lett.*, 4(9), 1003 (1992).

<sup>16</sup> S. M. Fike, B. Buchanan, N. M. Jokerst, M. A. Brooke, T. G. Morris, and S. P. DeWeerth, *IEEE Photon. Tech. Lett.*, 7(10), 1168 (1995).