### HIGH PERFORMANCE COMPUTING FOR IRREGULAR ALGORITHMS AND APPLICATIONS WITH AN EMPHASIS ON BIG DATA ANALYTICS

A Thesis Presented to The Academic Faculty

by

Oded Green

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Computational Science and Engineering

> Georgia Institute of Technology May 2014

Copyright  $\bigodot$  2014 by Oded Green

### HIGH PERFORMANCE COMPUTING FOR IRREGULAR ALGORITHMS AND APPLICATIONS WITH AN EMPHASIS ON BIG DATA ANALYTICS

Approved by:

Professor David A. Bader, Committee Chair School of Computational Science and Engineering Georgia Institute of Technology

Professor David A. Bader, Advisor School of Computational Science and Engineering & School of Electrical and Computer Engineering *Georgia Institute of Technology*

Professor Richard Vuduc School of Computational Science and Engineering Georgia Institute of Technology

Professor Srinivas Aluru School of Computational Science and Engineering Georgia Institute of Technology Professor Polo Chau School of Computational Science and Engineering Georgia Institute of Technology

Professor Bo Hong School of Electrical and Computer Engineering Georgia Institute of Technology

Yitzhak Birk Electrical Engineering Department *Technion*

Date Approved: 13 March 2014

To my parents, Itzhak and Esther, and my twin brother, Yoav,

you have always made me shoot to the stars.

To my wife, Ania,

you are my Northern Star and guide me through the worst of storms.

#### ACKNOWLEDGEMENTS

I am thankful for the support of my family throughout my graduate studies. Your support means the world to me and greatly simplified my life.

I want to thank my friends and fellow graduate students. You helped me walk this long and windy road. I am especially thankful to Rob McColl and David Ediger who helped me transition from Windows to Linux and had the patience to show me the basics - it is not easy to teach an old dog new tricks and you were successful.

To my friends, Lluis Miquel Munguia, Aakash Goel, Rajath Prasad, Adam McLaughlin, Xing Liu, Piyush Sao, Marat Dukhan, Aparna Chandramowlishwaran, Aftab Patel, and Zhaoming Yin, thanks for the many discussions (over lunch, coffer, or even a glass water). I learned a lot from you all.

To my advisor, Prof. David A. Bader, thanks for giving me the opportunity to study a new field. I am especially grateful to David for giving me as much leeway as I needed to start any new research problem.

I want to thank my committee: Professor Rich Vuduc, Professor Srinivas Aluru, Professor Polo Chau, and Professor Bo Hong. I had many interesting discussions with you all - some of the computer related and some not. I enjoyed them all.

# TABLE OF CONTENTS

| DE                  | DIC | ATIO   | N                                                       | iii  |  |

|---------------------|-----|--------|---------------------------------------------------------|------|--|

| ACKNOWLEDGEMENTS iv |     |        |                                                         |      |  |

| LIST OF TABLES x    |     |        |                                                         |      |  |

| LIS                 | T O | F FIG  | URES                                                    | xiii |  |

| Ι                   | IN' | TROD   | UCTION                                                  | 1    |  |

|                     | 1.1 | Thesis | S Content                                               | 2    |  |

|                     | 1.2 | Big Da | ata Graph Analytics                                     | 4    |  |

|                     | 1.3 | Social | Network Properties, Challenges, Insights, Opportunities | 6    |  |

|                     | 1.4 | Dynar  | nic Graph Challenges                                    | 10   |  |

|                     | 1.5 | STIN   | GER - A Dynamic Graph Data Structure                    | 10   |  |

|                     | 1.6 | My Pu  | ublications                                             | 12   |  |

| II                  |     |        | EL APPROXIMATE BETWEENNESS CENTRALITY                   | 14   |  |

|                     | 2.1 | Introd | luction                                                 | 15   |  |

|                     | 2.2 | Relate | ed Work                                                 | 17   |  |

|                     |     | 2.2.1  | Brandes's Algorithm                                     | 17   |  |

|                     |     | 2.2.2  | Parallel Algorithms and Implementations                 | 20   |  |

|                     |     | 2.2.3  | Approximate Algorithms                                  | 21   |  |

|                     |     | 2.2.4  | Dynamic Graph Algorithms for Betweenness Centrality     | 22   |  |

|                     |     | 2.2.5  | Additional Results                                      | 24   |  |

|                     |     | 2.2.6  | Real World Graph Properties                             | 25   |  |

|                     | 2.3 | Dynar  | nic Graph Betweenness Centrality                        | 25   |  |

|                     |     | 2.3.1  | BFS Tree Data Structure and Other Structures            | 26   |  |

|                     |     | 2.3.2  | Insertion and Deletion Scenarios                        | 27   |  |

|                     |     | 2.3.3  | Same Level                                              | 29   |  |

|     |     | 2.3.4  | Adjacent Level Insertion and Adjacent Level Deletion with<br>Extra Parent     | 30 |

|-----|-----|--------|-------------------------------------------------------------------------------|----|

|     |     | 2.3.5  | Non Adjacent Level Insertion and Adjacent Level Deletion without Extra Parent | 31 |

|     |     | 2.3.6  | Connecting Components Insertion and Disconnecting Compo-<br>nents Deletion    | 34 |

|     |     | 2.3.7  | Insertion and Deletion in Different Connect Component $\ . \ .$               | 34 |

|     |     | 2.3.8  | Additional Algorithmic Considerations and Optimizations                       | 35 |

|     |     | 2.3.9  | Complexity Analysis                                                           | 36 |

|     | 2.4 | Result | S                                                                             | 36 |

|     |     | 2.4.1  | Speedup Analysis of Dynamic Over Static                                       | 38 |

|     |     | 2.4.2  | Strong Scaling                                                                | 40 |

|     |     | 2.4.3  | Load Balancing                                                                | 41 |

|     |     | 2.4.4  | Large Network Analysis                                                        | 46 |

|     | 2.5 | Conclu | usions                                                                        | 48 |

|     | 2.6 | Forma  | l Proofs for Insertions                                                       | 49 |

|     |     | 2.6.1  | Same Level Insertion                                                          | 49 |

|     |     | 2.6.2  | Adjacent Level Insertion                                                      | 50 |

|     |     | 2.6.3  | Non-Adjacent Level Insertion                                                  | 53 |

| III | FA  | STER   | BETWEENNESS CENTRALITY                                                        | 56 |

|     | 3.1 |        | Structure Experimentation                                                     | 57 |

|     | -   | 3.1.1  | Relevant Terminology                                                          | 57 |

|     |     | 3.1.2  | Ancestor-List implementation                                                  | 57 |

|     |     | 3.1.3  | Neighbor-Traversal                                                            | 58 |

|     | 3.2 |        | ΣS                                                                            | 60 |

|     |     | 3.2.1  | Random Graphs                                                                 | 61 |

|     |     | 3.2.2  | Coarse Grain Parallelism                                                      | 62 |

|     |     | 3.2.3  | Fine Grain Parallelism                                                        | 66 |

|     |     | 3.2.3  | Additional Uses                                                               | 69 |

|     |     | 0.2.4  |                                                                               | 09 |

|               | 3.3                                           | Conclu                                                                                      | sions                                                                                                                                                                                                                                                                                                                                                                     | 70                                                                                                                                          |

|---------------|-----------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| $\mathbf{IV}$ | VE                                            | RTEX                                                                                        | COVER CLUSTERING COEFFICIENTS                                                                                                                                                                                                                                                                                                                                             | 72                                                                                                                                          |

|               | 4.1                                           | Introdu                                                                                     | uction                                                                                                                                                                                                                                                                                                                                                                    | 72                                                                                                                                          |

|               | 4.2                                           | Related                                                                                     | d Work                                                                                                                                                                                                                                                                                                                                                                    | 74                                                                                                                                          |

|               |                                               | 4.2.1                                                                                       | Vertex Covers                                                                                                                                                                                                                                                                                                                                                             | 75                                                                                                                                          |

|               | 4.3                                           | Vertex                                                                                      | Cover Clustering Coefficients                                                                                                                                                                                                                                                                                                                                             | 76                                                                                                                                          |

|               |                                               | 4.3.1                                                                                       | Clustering Coefficients for Static Graphs                                                                                                                                                                                                                                                                                                                                 | 76                                                                                                                                          |

|               |                                               | 4.3.2                                                                                       | Complexity Analysis                                                                                                                                                                                                                                                                                                                                                       | 78                                                                                                                                          |

|               |                                               | 4.3.3                                                                                       | Circuits of length 4 and higher                                                                                                                                                                                                                                                                                                                                           | 80                                                                                                                                          |

|               |                                               | 4.3.4                                                                                       | Clustering Coefficients in Dynamic Graphs                                                                                                                                                                                                                                                                                                                                 | 84                                                                                                                                          |

|               | 4.4                                           | Empiri                                                                                      | cal Results                                                                                                                                                                                                                                                                                                                                                               | 85                                                                                                                                          |

|               |                                               | 4.4.1                                                                                       | Static Clustering Coefficients                                                                                                                                                                                                                                                                                                                                            | 87                                                                                                                                          |

|               |                                               | 4.4.2                                                                                       | Static 4-Circuits                                                                                                                                                                                                                                                                                                                                                         | 93                                                                                                                                          |

|               | 4.5                                           | Conclu                                                                                      | sions                                                                                                                                                                                                                                                                                                                                                                     | 93                                                                                                                                          |

|               |                                               |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                             |

| $\mathbf{V}$  | LO                                            | AD BA                                                                                       | ALANCED CLUSTERING COEFFICIENTS                                                                                                                                                                                                                                                                                                                                           | 99                                                                                                                                          |

| V             | <b>LO</b><br>5.1                              |                                                                                             | ALANCED CLUSTERING COEFFICIENTS                                                                                                                                                                                                                                                                                                                                           | <b>99</b><br>99                                                                                                                             |

| V             |                                               | Introd                                                                                      |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                             |

| V             |                                               | Introd<br>5.1.1                                                                             | uction                                                                                                                                                                                                                                                                                                                                                                    | 99                                                                                                                                          |

| V             | 5.1                                           | Introd<br>5.1.1<br>Relate                                                                   | uction                                                                                                                                                                                                                                                                                                                                                                    | 99<br>101                                                                                                                                   |

| V             | 5.1<br>5.2                                    | Introd<br>5.1.1<br>Relate<br>Load E                                                         | uctionParallel Clustering Coefficient Challenges & and Solutionsed work                                                                                                                                                                                                                                                                                                   | 99<br>101<br>103                                                                                                                            |

| V             | 5.1<br>5.2                                    | Introd<br>5.1.1<br>Relate<br>Load E                                                         | uction                                                                                                                                                                                                                                                                                                                                                                    | 99<br>101<br>103<br>106                                                                                                                     |

| V             | 5.1<br>5.2                                    | Introd<br>5.1.1<br>Relate<br>Load E<br>5.3.1                                                | uction                                                                                                                                                                                                                                                                                                                                                                    | <ul><li>99</li><li>101</li><li>103</li><li>106</li><li>107</li></ul>                                                                        |

| V             | 5.1<br>5.2                                    | Introd<br>5.1.1<br>Relate<br>Load E<br>5.3.1<br>5.3.2                                       | uction       Parallel Clustering Coefficient Challenges & and Solutions       .         ed work       .       .         Balanced Scalable Clustering Coefficients       .       .         Edge-Based Approach       .       .         Vertex-based approach       .       .                                                                                               | <ul> <li>99</li> <li>101</li> <li>103</li> <li>106</li> <li>107</li> <li>109</li> </ul>                                                     |

| V             | 5.1<br>5.2                                    | Introd<br>5.1.1<br>Relate<br>Load E<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4                     | uction       Parallel Clustering Coefficient Challenges & and Solutions       .         ed work       .       .         Balanced Scalable Clustering Coefficients       .       .         Edge-Based Approach       .       .         Vertex-based approach       .       .         Complexity analysis       .       .                                                   | <ul> <li>99</li> <li>101</li> <li>103</li> <li>106</li> <li>107</li> <li>109</li> <li>110</li> </ul>                                        |

| V             | 5.1<br>5.2                                    | Introd<br>5.1.1<br>Relate<br>Load E<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5            | uction       Parallel Clustering Coefficient Challenges & and Solutions       .         ed work       .       .         Balanced Scalable Clustering Coefficients       .       .         Edge-Based Approach       .       .         Vertex-based approach       .       .         Complexity analysis       .       .         Vertex Cover Optimization       .       . | <ul> <li>99</li> <li>101</li> <li>103</li> <li>106</li> <li>107</li> <li>109</li> <li>110</li> <li>111</li> </ul>                           |

| V             | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Introd<br>5.1.1<br>Relate<br>Load E<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>Results | uction       Parallel Clustering Coefficient Challenges & and Solutions       .         ed work       .       .         Balanced Scalable Clustering Coefficients       .       .         Edge-Based Approach       .       .         Vertex-based approach       .       .         Vertex Cover Optimization       .       .         Summary       .       .             | <ul> <li>99</li> <li>101</li> <li>103</li> <li>106</li> <li>107</li> <li>109</li> <li>110</li> <li>111</li> <li>111</li> </ul>              |

| V             | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Introd<br>5.1.1<br>Relate<br>Load E<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>Results | uction       Parallel Clustering Coefficient Challenges & and Solutions         ed work                                                                                                                                                                                                                                                                                   | <ul> <li>99</li> <li>101</li> <li>103</li> <li>106</li> <li>107</li> <li>109</li> <li>110</li> <li>111</li> <li>111</li> <li>112</li> </ul> |

|               | 5.5  | Conclu  | $13 ions \dots \dots$ |

|---------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------|

| $\mathbf{VI}$ | DY   | NAM     | IC PARALLEL CONNECTED COMPONENTS 124                                                                                        |

|               | 6.1  | Introd  | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $125$                                                                            |

|               |      | 6.1.1   | Related Work                                                                                                                |

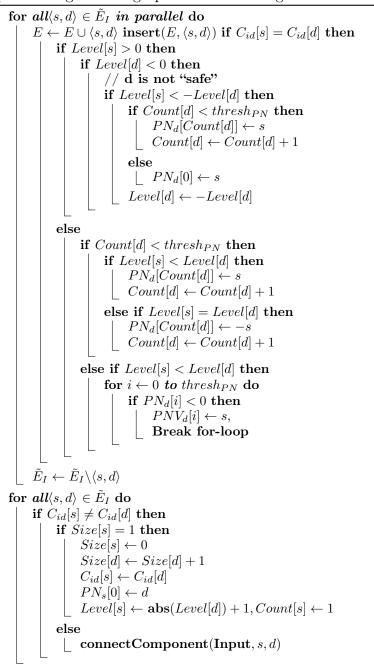

|               | 6.2  | Tracki  | ng Connected Components in a Dynamic Graph 128                                                                              |

|               |      | 6.2.1   | The Parents-Neighbors Sub-graph                                                                                             |

|               |      | 6.2.2   | Data Structure and Algorithm Details                                                                                        |

|               |      | 6.2.3   | Data Structure Initialization                                                                                               |

|               |      | 6.2.4   | Insertions and the Subgraph 133                                                                                             |

|               |      | 6.2.5   | Deletions and the Subgraph                                                                                                  |

|               | 6.3  | Experi  | imental Methodology                                                                                                         |

|               |      | 6.3.1   | Synthetic Graphs and Experiments                                                                                            |

|               |      | 6.3.2   | First Attempts                                                                                                              |

|               | 6.4  | Result  | s                                                                                                                           |

|               |      | 6.4.1   | Quantitative                                                                                                                |

|               |      | 6.4.2   | Performance                                                                                                                 |

|               | 6.5  | Conclu  | sions $\ldots \ldots 147$               |

| VII           | I ME | ERGE    | PATH                                                                                                                        |

|               | 7.1  | Introd  | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $149$                                                                            |

|               | 7.2  | Merge   | e Path                                                                                                                      |

|               |      | 7.2.1   | Construction and basic properties                                                                                           |

|               |      | 7.2.2   | The Merge Path and cross diagonals                                                                                          |

|               |      | 7.2.3   | The Merge Matrix – content & properties                                                                                     |

|               |      | 7.2.4   | The Merge Path and the Merge Matrix                                                                                         |

|               | 7.3  | Paralle | el Merge and Sort                                                                                                           |

|               | 7.4  | Cache   | Efficient Merge Path                                                                                                        |

|               |      | 7.4.1   | Overview                                                                                                                    |

|               |      | 7.4.2   | Memory-hierarchy highlights                                                                                                 |

|    |      | 7.4.3  | Cache-Efficient Parallel Merge                                                                                               |

|----|------|--------|------------------------------------------------------------------------------------------------------------------------------|

|    |      | 7.4.4  | Cache-Efficient Parallel Sort                                                                                                |

|    | 7.5  | Relate | ed work                                                                                                                      |

|    | 7.6  | Result | 172                                                                                                                          |

|    |      | 7.6.1  | x86 System                                                                                                                   |

|    |      | 7.6.2  | HyperCore Architecture                                                                                                       |

|    | 7.7  | Conc   | lusions                                                                                                                      |

| VI | IIGF | PU ME  | CRGE PATH         181                                                                                                        |

|    | 8.1  | Introd | uction $\ldots \ldots 182$ |

|    |      | 8.1.1  | Introduction on GPU                                                                                                          |

|    |      | 8.1.2  | Parallel Sorting                                                                                                             |

|    |      | 8.1.3  | GPU Challanges                                                                                                               |

|    | 8.2  | GPU 2  | MergePath                                                                                                                    |

|    |      | 8.2.1  | Parallel Merge                                                                                                               |

|    |      | 8.2.2  | GPU Partitioning 190                                                                                                         |

|    |      | 8.2.3  | GPU Merge 192                                                                                                                |

|    |      | 8.2.4  | Complexity analysis of the GPU merge 194                                                                                     |

|    |      | 8.2.5  | GPU Optimizations and Issues                                                                                                 |

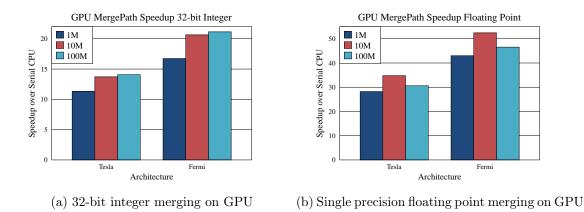

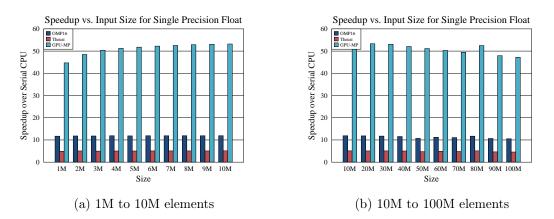

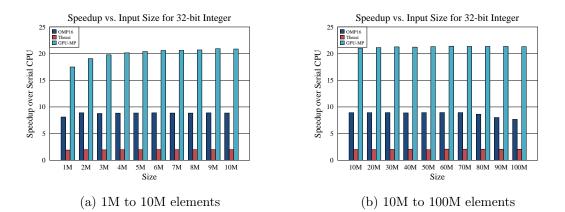

|    | 8.3  | Empir  | ical Results                                                                                                                 |

|    |      | 8.3.1  | Floating Point Merging                                                                                                       |

|    |      | 8.3.2  | Integer Merging                                                                                                              |

|    | 8.4  | Conclu | usion                                                                                                                        |

| IX |      |        | UTATIONALLY EFFICIENT ALGORITHM FOR THE<br>RIANCE METHOD 203                                                                 |

|    | 9.1  | Intro  | duction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $203$                                                 |

|    |      | 9.1.1  | Background                                                                                                                   |

|    |      | 9.1.2  | The Covariance Method                                                                                                        |

|    |      | 9.1.3  | Related Work                                                                                                                 |

|    |      | 9.1.4  | Deficiencies of the Straightforward Algorithm                                                                                |

|    |      | 9.1.5  | Parallelization Challenges                                   | 210 |

|----|------|--------|--------------------------------------------------------------|-----|

|    | 9.2  | Fine-C | Grain Multiplication - Efficient Parallelization             | 212 |

|    |      | 9.2.1  | Product Based Partitioning                                   | 212 |

|    | 9.3  | The N  | Tew Algorithm                                                | 216 |

|    |      | 9.3.1  | Combination $(\Delta r, \Delta c) = (0, 0)$                  | 218 |

|    |      | 9.3.2  | Remaining Combinations                                       | 222 |

|    |      | 9.3.3  | Complexity Analysis                                          | 223 |

|    |      | 9.3.4  | Additional Implementation Details                            | 226 |

|    | 9.4  | Experi | imental Results                                              | 227 |

|    |      | 9.4.1  | Experimental Setup                                           | 228 |

|    |      | 9.4.2  | Moderate-Size Problems                                       | 228 |

|    |      | 9.4.3  | Scaling Up                                                   | 231 |

|    | 9.5  | Conclu | sions                                                        | 232 |

| Х  | CO   | NCLU   | SIONS                                                        | 235 |

|    | 10.1 | Impac  | t of Thesis                                                  | 235 |

|    | 10.2 | Summ   | ary of Results                                               | 235 |

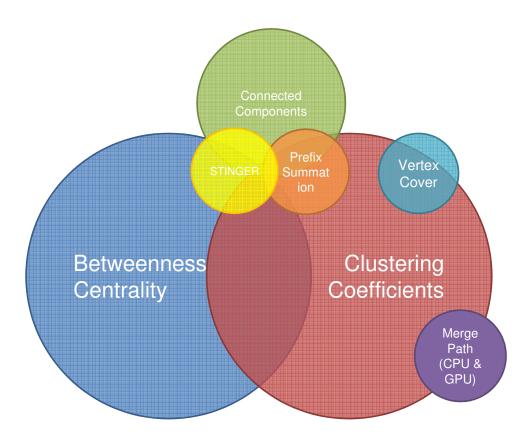

|    | 10.3 | The "N | Melting-Pot"                                                 | 238 |

|    | 10.4 | On the | e Road to Exascale and Beyond - Future Research Directions . | 240 |

| VI | ГА.  |        |                                                              | 258 |

# LIST OF TABLES

| 1  | Memory bounds for different betweenness centrality algorithms. $P$ denotes the number of cores used by each algorithm. $K$ denotes the number of roots used in the the approximation. The dynamic algorithms do not depend on the number of cores as these data structures are maintained as part of the computation                                                         | 22  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Notations used in the chapter                                                                                                                                                                                                                                                                                                                                                | 27  |

| 3  | Graphs from the 10th DIMACS Implementation Challenge used in our scaling experiments. The execution times are for a single thread                                                                                                                                                                                                                                            | 37  |

| 4  | Larger graphs from the 10th DIMACS Implementation Challenge. The execution times are for a single thread.                                                                                                                                                                                                                                                                    | 47  |

| 5  | The scenarios for the medium size graphs where the different approaches have better performance. The array based approach is denoted with o and the neighbor-traversal is denoted as $\diamond$ . The first column denotes the graph size and average edge adjacency. The remaining columns represent the thread count. The neighbor-traversal approach dominates the table. | 65  |

| 6  | Memory bounds for different betweenness centrality algorithms                                                                                                                                                                                                                                                                                                                | 70  |

| 7  | Notations in this chapter                                                                                                                                                                                                                                                                                                                                                    | 74  |

| 8  | Graphs from the 10th DIMACS Implementation Challenge that are used in our experiments, grouped by type and sorted within each group by vertex count.                                                                                                                                                                                                                         | 86  |

| 9  | Notations in this chapter                                                                                                                                                                                                                                                                                                                                                    | 103 |

| 10 | Time complexities of both approaches                                                                                                                                                                                                                                                                                                                                         | 110 |

| 11 | Graphs from the 10th DIMACS Implementation Challenge used in our experiments with the clustering coefficient computation runtimes for the different algorithms. Labels: SF - Straightforward (40 threads), V-B - Vertex-Based (40 threads), and E-B - Edge-Based (40 threads).                                                                                               | 113 |

| 12 | The data structures maintained while tracking dynamic connected co-<br>mponents.                                                                                                                                                                                                                                                                                             | 131 |

| 13 | Graph sizes used in our experiments for testing the algorithm. Multiple graphs of each size were used.                                                                                                                                                                                                                                                                       | 139 |

| 14 | Cache misses for parallel merging algorithms assuming a 3-way asso-<br>ciativity                                                                                                                                                                                                                                                                                             | 169 |

| 15 | Intel X86 systems used                                                                                            | 172 |

|----|-------------------------------------------------------------------------------------------------------------------|-----|

| 16 | GPU test-bench.                                                                                                   | 195 |

| 17 | CPU test-bench.                                                                                                   | 195 |

| 18 | Taxonomy of the Covariance Method                                                                                 | 206 |

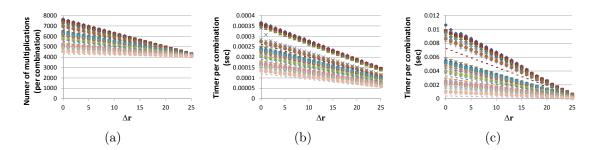

| 19 | The number of operations needed for each combination based on the four types of product-window shift.             | 223 |

| 20 | Performance analysis of larger instances. Several cases timed out for<br>the straightforward algorithm timed out. | 230 |

| 21 | New memory bounds for multiple betweenness centrality algorithms.                                                 | 236 |

## LIST OF FIGURES

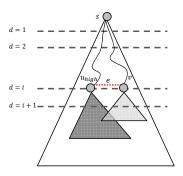

| 1 | The insertion of edge $e = (u, v)$ connects two vertices that are on the same level in the BFS-like tree of root $s$ . This insertion does not create any new shortest paths. In the case of edge deletion, no shortest paths are removed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29 |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

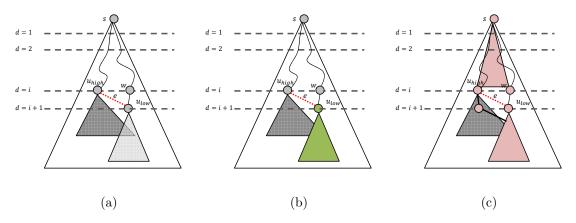

| 2 | (a) The insertion of edge $e = (u_{high}, u_{low})$ connects vertices that are<br>in adjacent levels before the insertion. (b) A BFS traversal is started<br>at $u_{low}$ as the shortest paths above this vertex are not affected by the<br>insertion. (c) Shows the vertices that are affected by the dependency<br>accumulation - this includes vertices that were not found in the BFS<br>traversal beginning at $u_{low}$ . The difference between the insertion and<br>the deletion, is that the vertices found in the BFS traversal (green<br>triangle) will have fewer paths to the root instead of additional paths<br>to the root                                                                                                                 | 30 |

| 3 | (a) The BFS-like tree prior to the insertion of edge $e = (u_{high}, u_{low})$ .<br>(b) The BFS-like tree after the insertion. Note that $u_{low}$ has a single parent in the level above it. For deletions, swap between (a) and (b).<br>(c) The BFS traversal starts at $u_{low}$ and can possibly "pull-up" vertices that are closer to the root following the insertion. (d) The dependency accumulation can find vertices that were not in the BFS traversal.                                                                                                                                                                                                                                                                                          | 32 |

| 4 | (a) Prior to the insertion, the vertices in different connected components. (b) After the insertions, the vertices are in the same connected component. All the paths between vertices that were previously in different connected components go through the inserted edge. For deletions, (b) is before the deletion and (a) is after the deletion. (c) and (d) are for insertions. (c) The BFS traversal starts at the vertex that just got connected to the first connected component. Only vertices in the second component will be found in the BFS traversal. (d) The dependency accumulation will go through all the vertices of the second connected component and work its way back through the newly connect edge and all the way up to the root. | 33 |

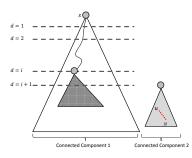

| 5 | Edge insertion or deletion occurs in a different connected component than that of the root                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35 |

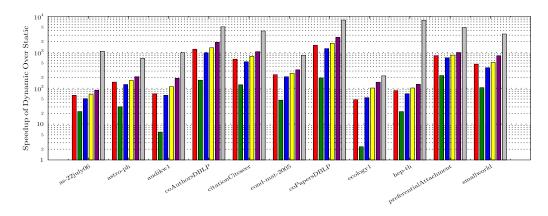

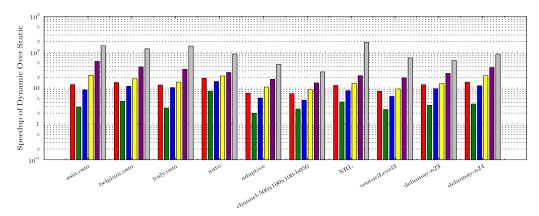

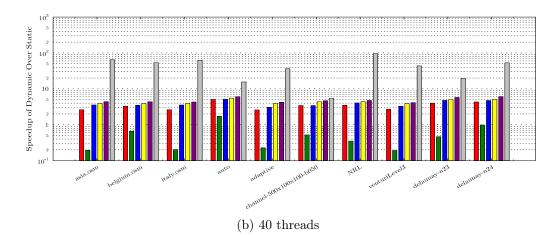

| 6 | Six different speedup bar for each graph (from the left to the right) for single thread execution: 1) average, 2) minimal, 3) the 25th percentile, 4) median, 5) the 75th percentile, and 6) maximal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39 |

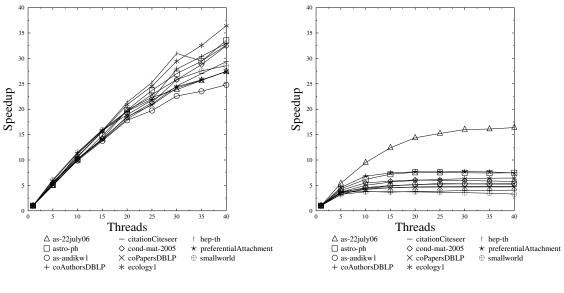

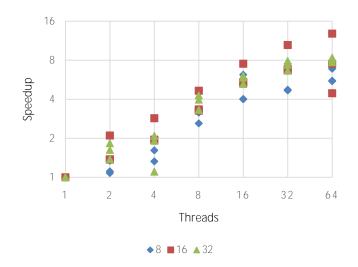

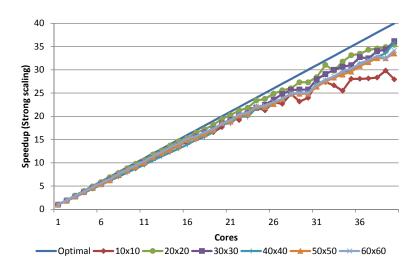

| 7 | Strong scaling of the coarse-grain parallel implementations: (a) static graph algorithm and (b) dynamic graph algorithm. The approximation uses $K = 256$ roots. Each of the curves is for different network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40 |

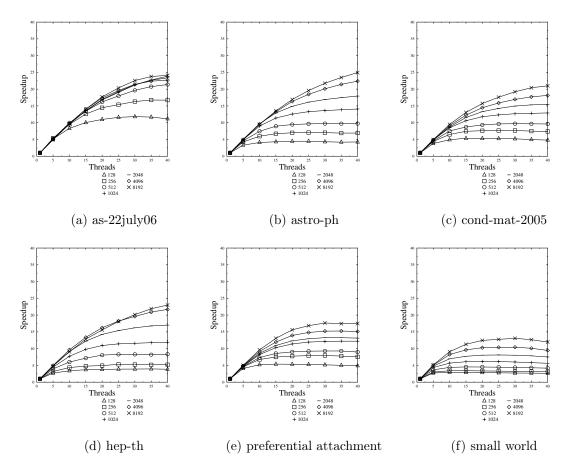

| 8  | Scaling of the dynamic graph algorithm. The multiple curves represent<br>the speedup for different a number of roots as part of the approximation<br>process. The increase in the number of roots increases the amount of<br>work each thread and allows for better load-balancing which allows for<br>better scaling and speedups.                                                                                                                                                                                                                                                                                                                                                                                                 | 42 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

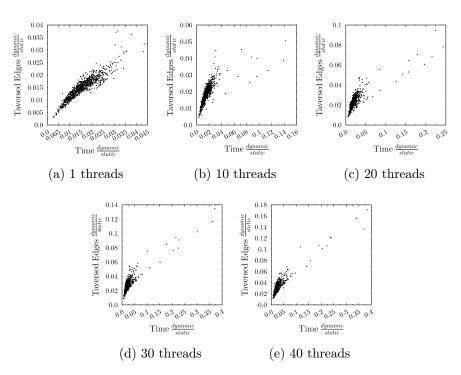

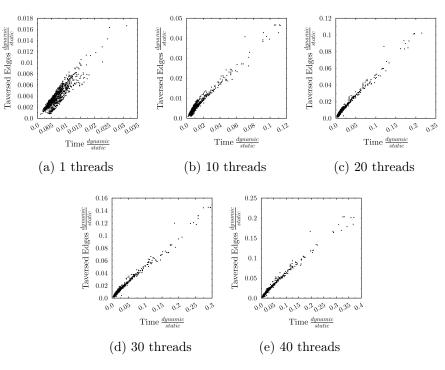

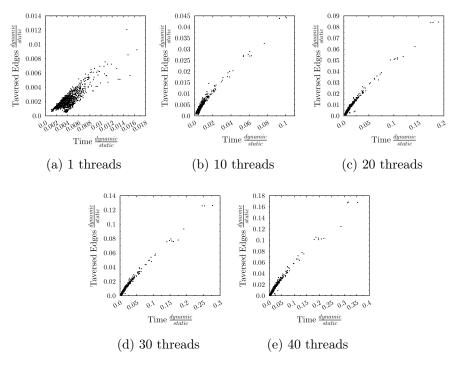

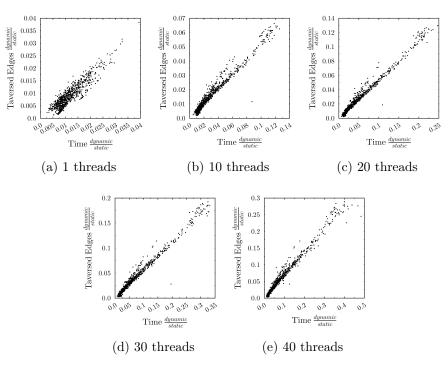

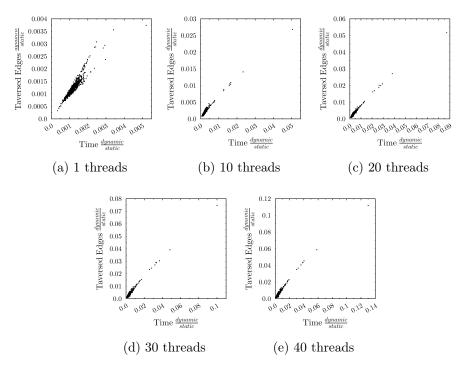

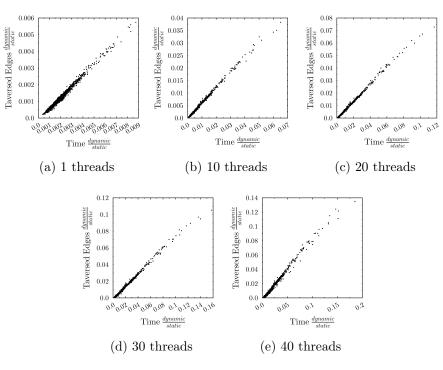

| 9  | The subfigures show the relationship between the execution of the al-<br>gorithms and the number of traversed edges for each of the insertions.<br>The abscissa is the ratio in the execution time of the dynamic graph<br>algorithm and the static graph algorithm (with an equal number of<br>threads). The ordinate is the ratio of traversed edges of the dynamic<br>graph algorithm and the static graph algorithm (with an equal num-<br>ber of threads). We show the results for 1, 10, 20, 30, and 40 threads.<br>These scatter plots show that there is a relationship between execution<br>time and traversed edges. This caption is relevant for Fig. 10 - Fig 14.<br>Results in this figure are for as-22july06 network | 43 |

| 10 | astro-Ph network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44 |

| 11 | cond-mat-2005 network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44 |

| 12 | cond-mat-2005 network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45 |

| 13 | preferentialAttachment network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45 |

| 14 | small-world network.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46 |

| 15 | Six different speedup bar for each graph (from the left to the right):<br>1) average, 2) minimal, 3) the 25th percentile, 4) median, 5) the 75th<br>percentile, and 6) maximal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47 |

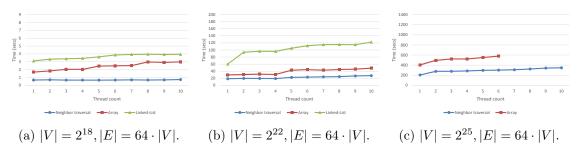

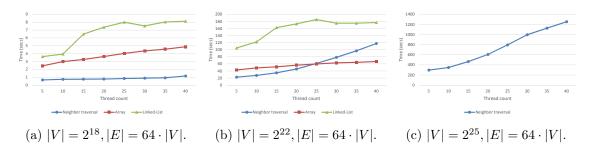

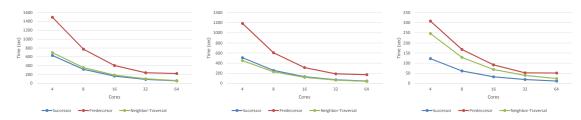

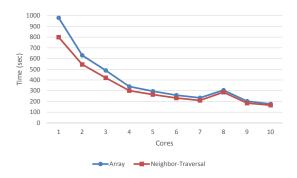

| 16 | Weak scale testing for thread counts of 1 to 10. Lower is better                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63 |

| 17 | Weak scale testing for thread counts of 5 to 40 in multiples of 5. Lower is better                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 63 |

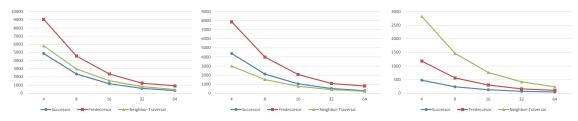

| 18 | Execution time for approximate betweenness centrality on the Cray XMT2 for a considerably sparse graph. An RMAT-24 graph is used with an average edge degree of 8. 256 roots were used as defined in the HPCS SSCA [4] specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67 |

| 19 | Execution time for approximate betweenness centrality on the Cray XMT2 for a slightly denser sparse graph. An RMAT-24 graph is used with an average edge degree of 64. 256 roots were used as defined in the HPCS SSCA [4] specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 68 |

| 20 | Execution time of the fine grain parallelism using the SNAP package.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69 |

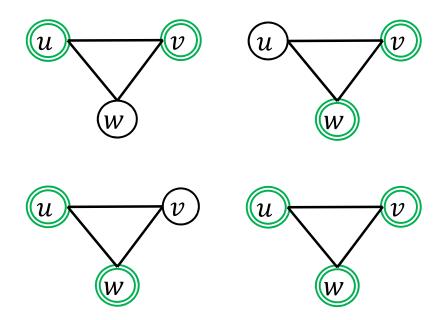

| 21 | All the legal vertex covers of the triangle made up of $u, v, w$ . The vertices in the vertex cover are marked with an additional circle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79 |

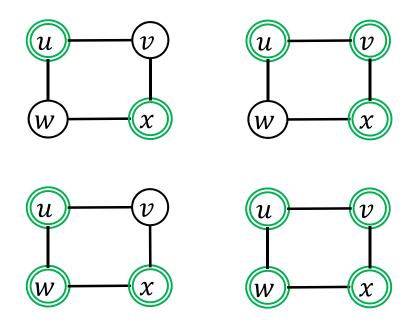

| 22 | All legal vertex covers of the square made up of $u, v, w$ , and $x$ . Additional edges that are non-relevant have been removed. There are additional vertex covers for square. However, these follow one of the presented patterns. The vertices in the vertex cover are marked with an additional circle                                                                                                                                                          | 81 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

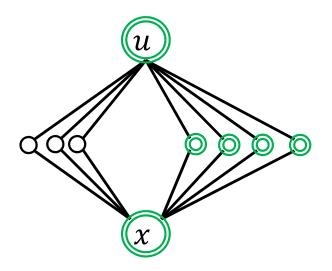

| 23 | The cross-vertices $(u, x)$ and their common neighboring vertices found<br>in adjacency intersection. These neighbors are divided into groups:<br>those in the vertex cover and those not in the vertex cover. The vertices<br>in the vertex cover are marked with an additional circle                                                                                                                                                                             | 83 |

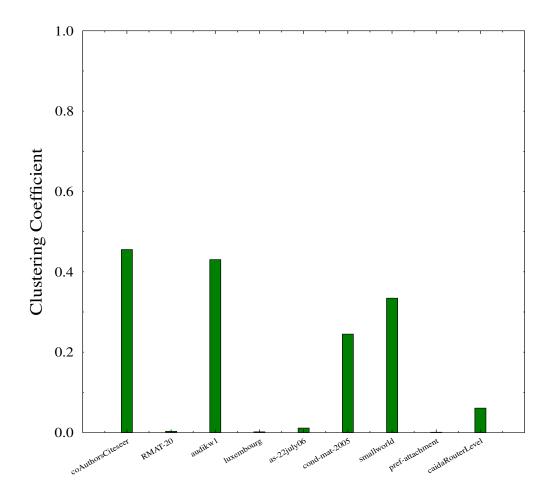

| 24 | This chart shows the global clustering coefficient value for graphs from Table 8                                                                                                                                                                                                                                                                                                                                                                                    | 87 |

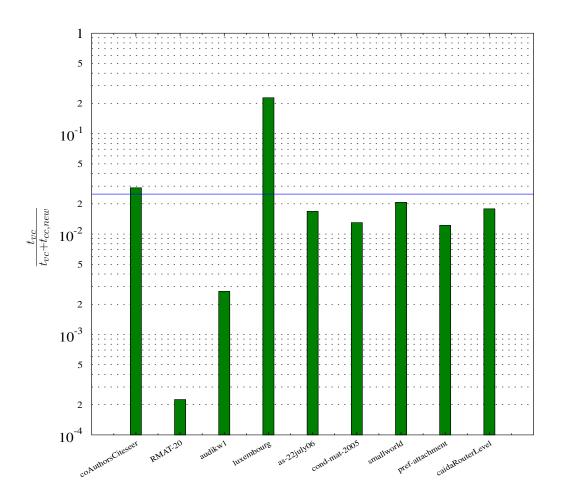

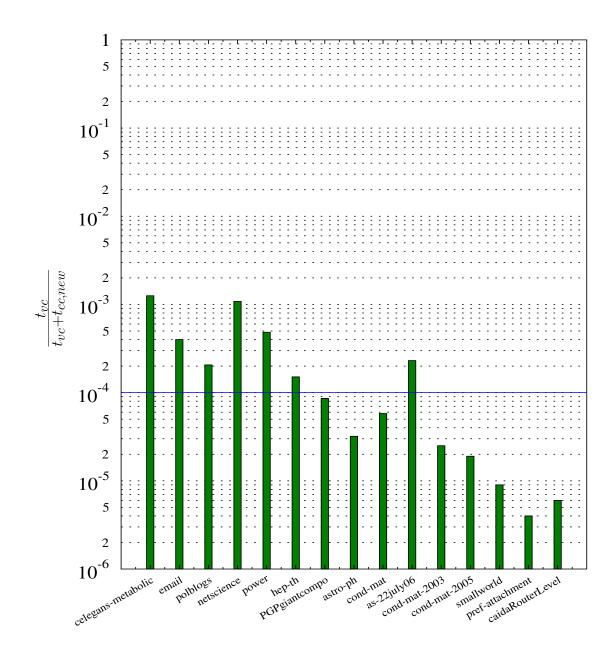

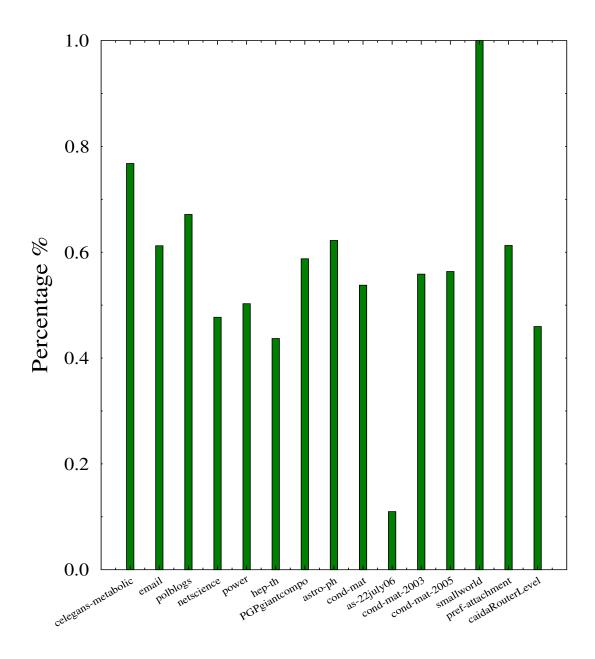

| 25 | The ordinate presents the ratio of time spent finding the vertex cover<br>as a function of the total time spent computing the vertex cover and<br>the clustering coefficients. The ordinate is a logscale. An additional<br>blue curve has been placed at 2.5%. The bars of about 2/3 of the<br>graphs are below this curve                                                                                                                                         | 88 |

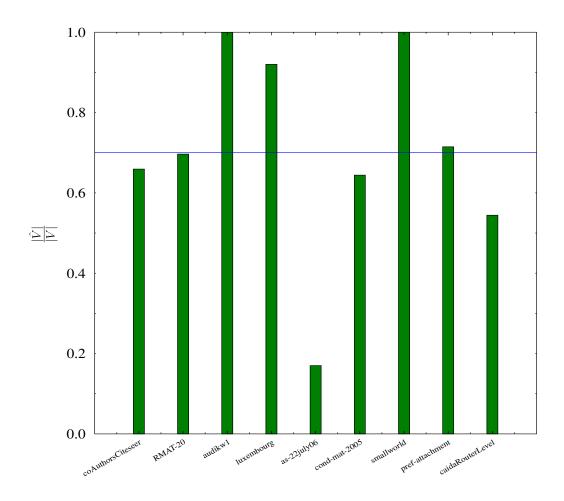

| 26 | The ordinate is the size ratio of the vertex cover, $\hat{V}$ , and the vertex set $V$ . Note that $ \hat{V}  \leq  V $ . An additional blue curve has been added at 70%. The bars of about 3/5 of the graphs are below this curve                                                                                                                                                                                                                                  | 89 |

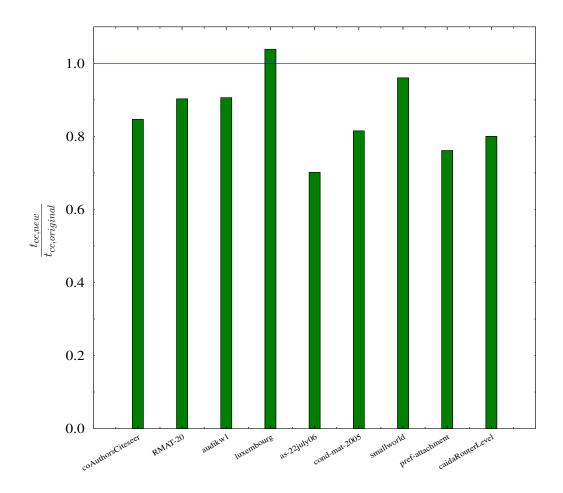

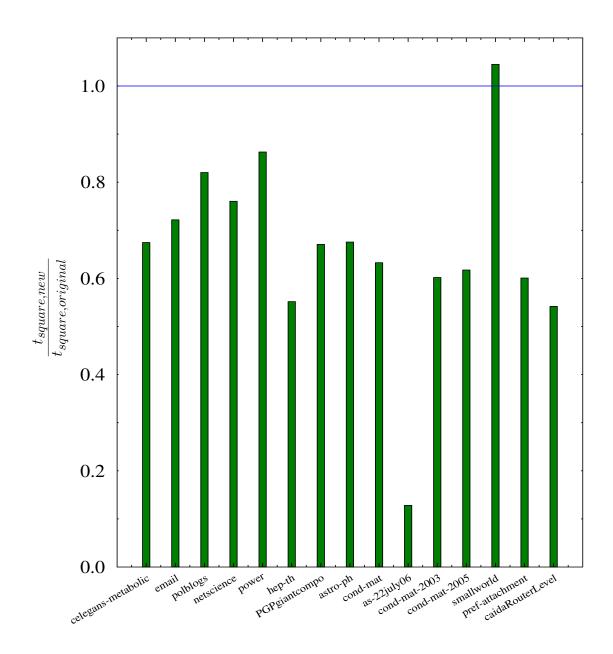

| 27 | The ordinate is the time ratio of the new vertex cover-based clustering coefficients algorithm and the original clustering coefficient algorithm. The time of the new algorithm includes both the time needed to find the vertex cover and the time for computing the clustering coefficients. All bars below the blue curve occur when the new algorithm is faster, as such lower is better.                                                                       | 90 |

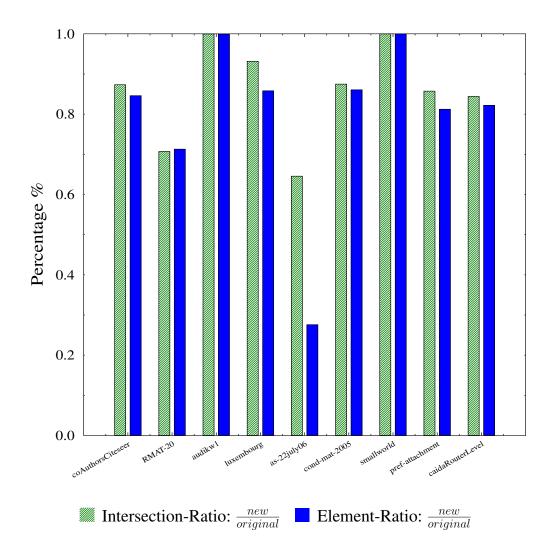

| 28 | The ordinate is the ratio of the number of intersection that are neces-<br>sary by the new algorithm in comparison with the original algorithm.                                                                                                                                                                                                                                                                                                                     | 91 |

| 29 | The ordinate presents the ratio of time spent finding the vertex cover<br>as a function of the total time spent finding all the 4-circuits. Note<br>that the ordinate is a log scale. The abscissa are the Clustering graphs<br>from Table 8                                                                                                                                                                                                                        | 94 |

| 30 | The ordinate is the time ratio of the new vertex cover based clustering coefficients algorithm and the original clustering coefficient algorithm. The time of the new algorithm includes both the time needed to find the vertex cover and the time for computing the clustering coefficients. The blue curve denotes equal run-times for the new and original algorithm. All bars below the blue curve state the new algorithm is faster, as such lower is better. | 97 |

| 31 | The ordinate is the ratio of the number of intersection that are neces-<br>sary by the new algorithm in comparison with the original algorithm.                                                                                                                                                                                                              | 98  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

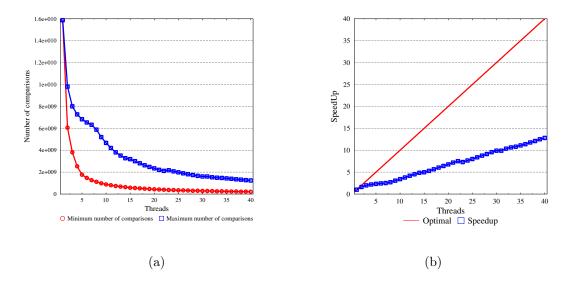

| 32 | (a) Load distribution among parallel processors. (b) Shows the maximum attainable speedup                                                                                                                                                                                                                                                                    | 102 |

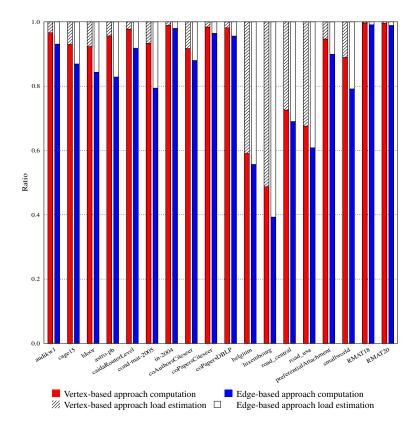

| 33 | The ordinate is the ratio between the thread with the least amount<br>of work with the thread with the most amount of work based on the<br>number comparisons required by the thread in the adjacency list inter-<br>section. The abscissa are the graphs used. Note that for all the graphs<br>the edge-based approach achieves almost perfect partitioning | 115 |

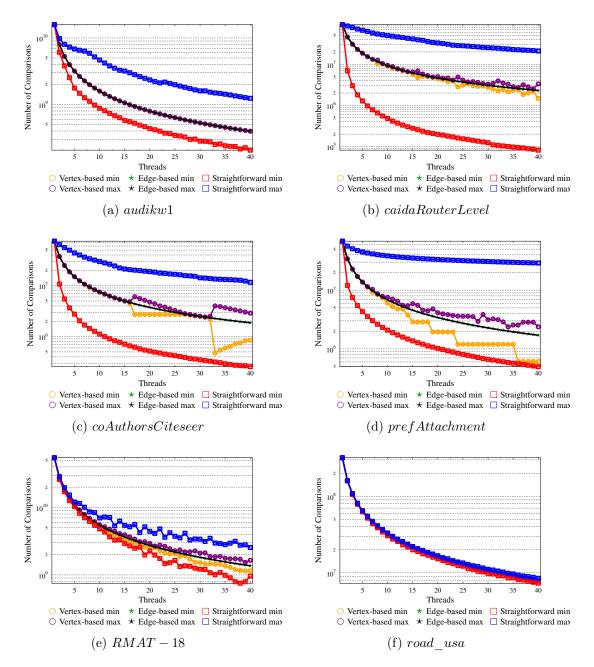

| 34 | The abscissa is the number of threads used. The ordinate is the number<br>of comparisons required for a specific thread count. Two curves are<br>shown for each of the algorithms - for threads that receive the most<br>and least number of comparisons. The straightforward partitioning is<br>the lower and upper for all the figures                     | 119 |

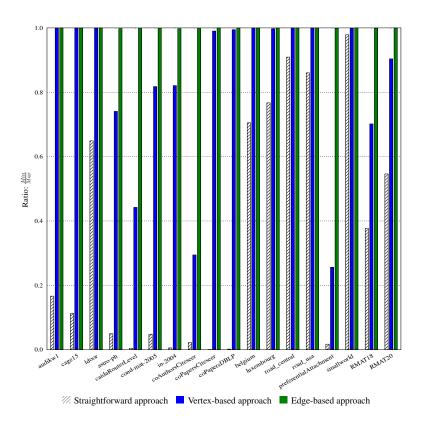

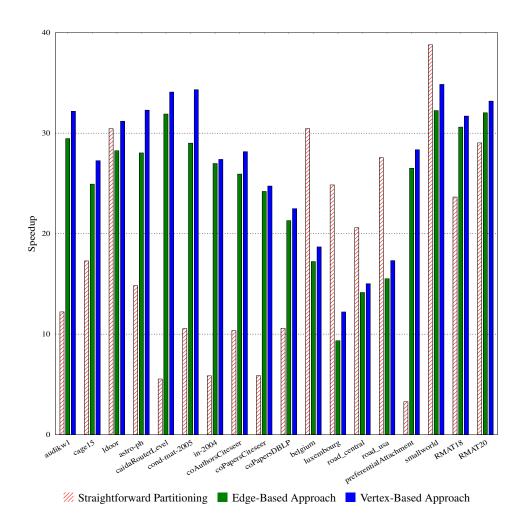

| 35 | Speedup obtained with 40 cores for the different algorithms                                                                                                                                                                                                                                                                                                  | 120 |

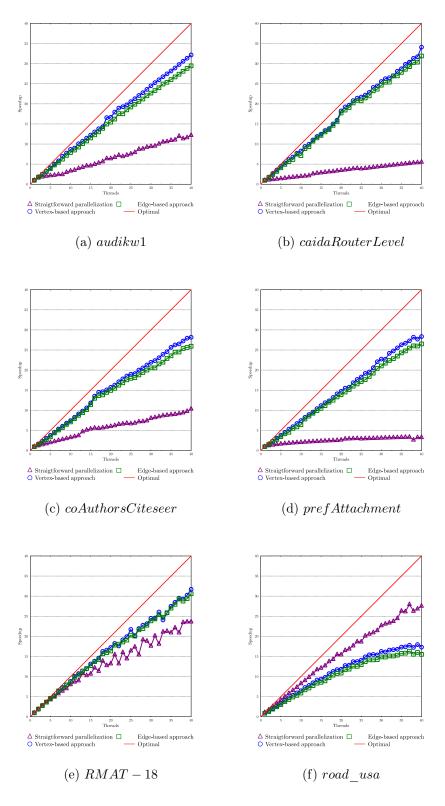

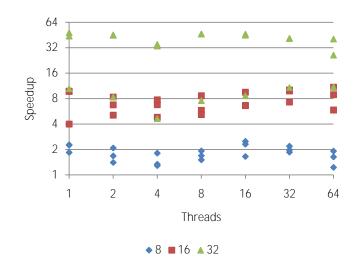

| 36 | The ordinate for all the subfigures is the speedup as a function of the number of threads (the abscissa).                                                                                                                                                                                                                                                    | 121 |

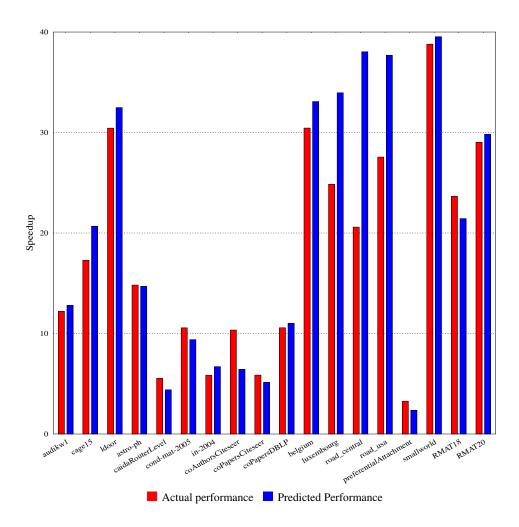

| 37 | Speedup obtained for 40 cores using straightforward division algorithm in comparison with the estimated speedup                                                                                                                                                                                                                                              | 122 |

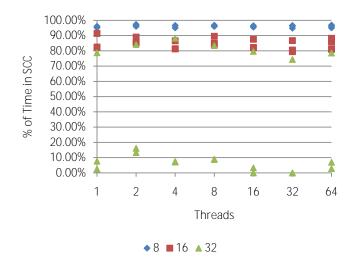

| 38 | Percentage of time spent in both the load balancing phase vs. the list intersection phase for both approaches                                                                                                                                                                                                                                                | 123 |

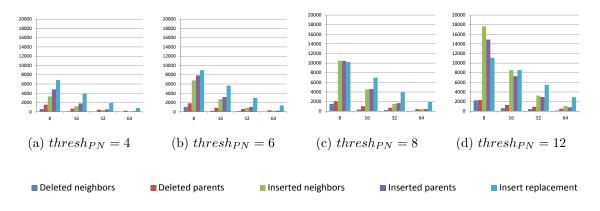

| 39 | Average number of inserts and deletes in $PN$ array for batches of $100K$ updates for RMAT-22 graphs. The subfigures are for different values of $thresh_{PN}$ . Note that the ordinate is dependent on the specific bar chart. The charts for RMAT-21 graphs had very similar structure and have been removed for the sake of brevity.                      | 141 |

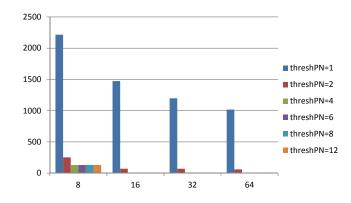

| 40 | Average number of unsafe deletes in $PN$ data structure for batches<br>of 100K updates as a function of the average degree (x-axis) and<br>$thresh_{PN}$ (bars)                                                                                                                                                                                              | 141 |

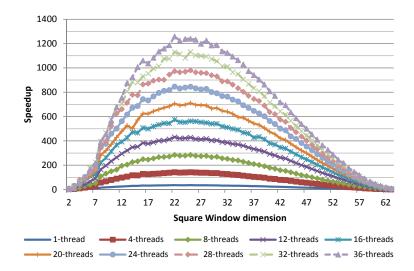

| 41 | Strong scaling results on RMAT-22 graphs with different average de-<br>gree as a function of the number of threads. Results include three<br>graphs at each average degree                                                                                                                                                                                   | 144 |

| 42 | Speed up of the new algorithm over performing parallel static recompu-<br>tation after each batch on three different RMAT-22 graphs with each<br>average degree as a function of the number of threads                                                                                                                                                       | 145 |

| 43 | Fraction of the update time spent updating connected components over<br>time spent updating the graph structure and connected components.                                                                                                                                                                                                                    | 146 |

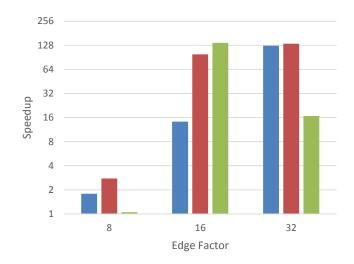

| 44 | Speed up over performing static recomputation after each batch on scale 24 graphs for three graphs at each edge factor using 64 threads.                                                                                                                                                                                                                                                                                       | 147 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

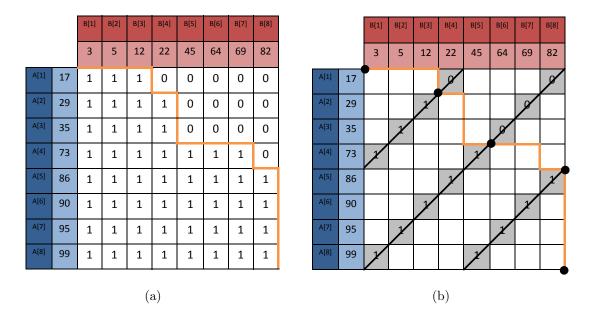

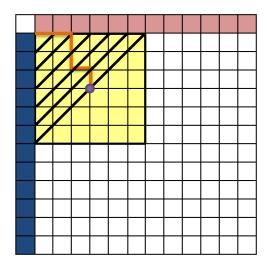

| 45 | Merge Matrix and Merge Path. (a) The Merge Matrix is shown with<br>all the values explicitly computed. The Merge Path is on the boundary<br>between the zeros and the ones. (b) The cross diagonals in a Merge<br>Matrix are used to find the points of change between the ones and the<br>zeros, i.e., the intersections with the Merge Path                                                                                  | 151 |

| 46 | Merge Matrix for the cache efficient algorithm. The yellow circles de-<br>pict the initial and final points of the path for a specific block in the<br>cache algorithm                                                                                                                                                                                                                                                         | 163 |

| 47 | Cache-efficient parallel sort first stage. Each cache sized block is sorted followed by parallel merging                                                                                                                                                                                                                                                                                                                       | 166 |

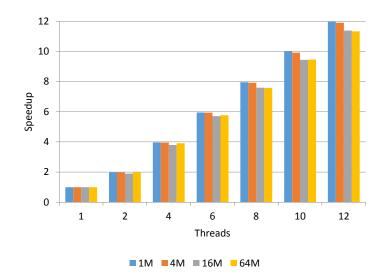

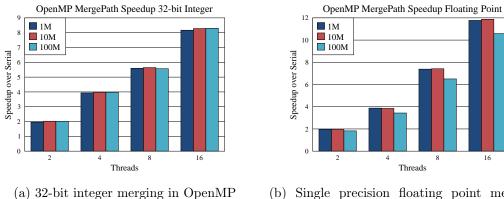

| 48 | Merge Path speedup on a 12-core system. These results can be found<br>in [115]. The different color bars are for different sized input arrays.<br>1M elements refers to $2^{20}$ elements. For each array size, the arrays are<br>equisized.                                                                                                                                                                                   | 171 |

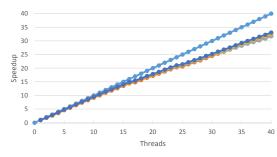

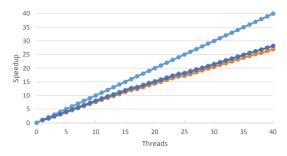

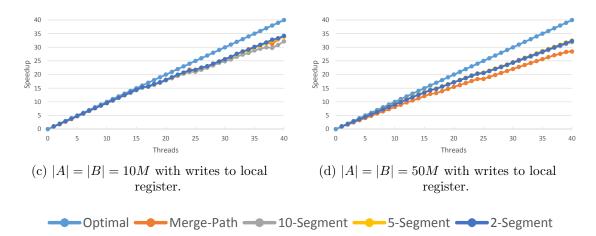

| 49 | Merge Path and Segmented Merge Path speedup on a 40-core system. 1M elements refers to $2^{20}$ elements. For each array size, the arrays are equisized. For the segmented algorithm, the Merge Matrix is divided into 10, 5, and 2 segments.                                                                                                                                                                                  | 173 |

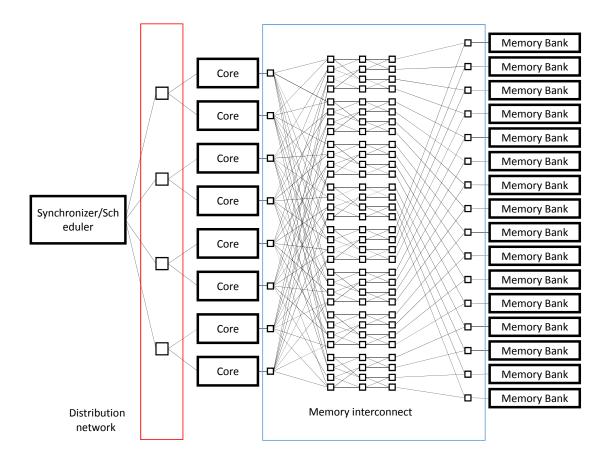

| 50 | Schematic view of the Hypercore for an 8-core system. The memory banks refer to the shared memory. The Hypercore also has DRAM memory which is not shown in this schematic.                                                                                                                                                                                                                                                    | 176 |

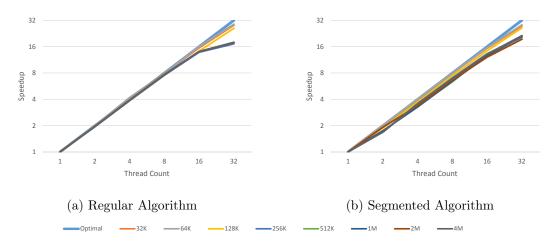

| 51 | Speedup of our algorithm on Plurality's Hypercore [3] system                                                                                                                                                                                                                                                                                                                                                                   | 177 |

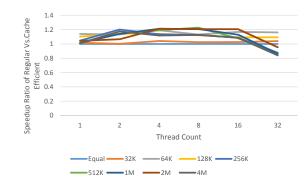

| 52 | Speedup comparison of the regular and segmented algorithms on the Hypercore. A blue curve, <i>Equal</i> , has been added to this chart to denote when the speedups of the algorithm are equal. All curves above <i>Equal</i> mean that the regular algorithm outperforms that segmented algorithm. All curves below <i>Equal</i> mean that the segmented algorithm is more efficient.                                          | 177 |

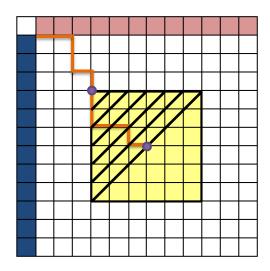

| 53 | Illustration of the MergePath concept for a non-increasing merge. The first column (in blue) is the sorted array $A$ and the first row (in red) is the sorted array $B$ . The orange path (a.k.a. Merge Path) represents comparison decisions that are made to form the merged output array. The black cross diagonal intersects with the path at the midpoint of the path which corresponds to the median of the output array | 186 |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

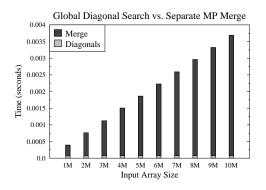

| 54 | Diagonal searches for a single window of one SM. (a) The window is in<br>its initial position. Each SP does a search for the path. (b) The window<br>moves to the farthest position of the path and the new diagonals are<br>searched                                                                                                                                                                                                                                                   | 188 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

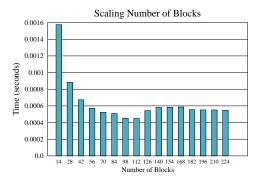

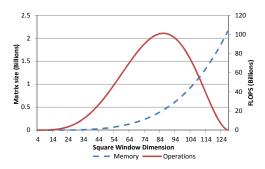

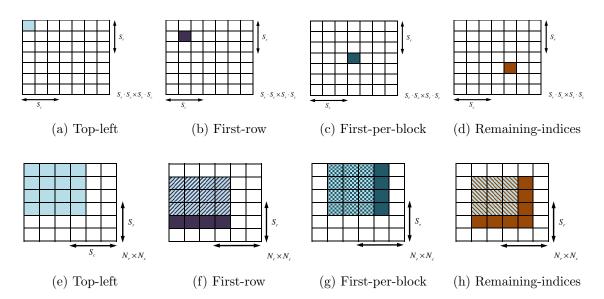

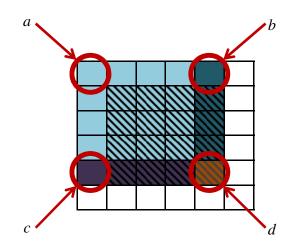

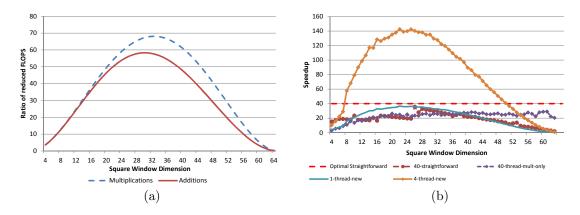

| 55 | Merging one million single-precision floating point numbers in Merge<br>Path on Fermi while varying the number of thread blocks used from<br>14 to 224 in multiples of 14                                                                                                                                                                                                                                                                                                               | 196 |