# DESIGN METHODOLOGY FOR LOW POWER 3D-INTEGRATED IMAGE SENSING SYSTEM FOR NETWORK BASED APPLICATIONS

A Dissertation Presented to The Academic Faculty

By

Denny Lie

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology May 2015

Copyright © 2015 by Denny Lie

# DESIGN METHODOLOGY FOR LOW POWER 3D-INTEGRATED IMAGE SENSING SYSTEM FOR NETWORK BASED APPLICATIONS

Approved by:

Dr. Saibal Mukhopadhyay, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Sudhakar Yalamanchili School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Arijit Raychowdhury School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Sung Kyu Lim School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Peng Qiu School of Biomedical Engineering Georgia Institute of Technology

Date Approved: January 2015

# ACKNOWLEDGEMENTS

First, I would like to acknowledge God, his Son, and the Holly Spirit. I would like to thank for all the blessings, the hope, and the grace that have been poured down in life.

I would like to express my highest gratitude to my advisor, Professor Saibal Mukhopadhyay, for his guidance and support during my PhD program. He taught me to keep pushing the boundary. And I am grateful for his patience and encouragement through my difficult times. These five years have been a tremendous journey of learning, I believe I am prepared to strive through challenges on my career path.

I would like to extend special thanks to Professor Sudhakar Yalamanchili and Professor Arijit Raychowdhury for their critical advice and insight in shaping my thesis. In addition, I would like to acknowledge Professor Sung Kyu Lim and Professor Peng Qiu for investing their valuable time and effort in serving as my PhD Committee Members.

I would like to thank GREEN Lab current and former members Amit Trivedi, Boris Alexandrov, Wen Yueh, Zakir Khondker, Sergio Carlo, Jae Ha Kung, Monodeep Kar, Duckhwan Kim, Jong Hwan Ko, Mohammad Faisal Amir, Arvind Singh, Krishnamurty Yeleswarapu, Swarrnna Karthik Parthasarathy, Dr. Jeremy Tolbert, Dr. Minki Cho, Dr. Subho Chatterjee, and Dr. Kwanyeob Chae for the solidarity, friendship and support that they have offered me. I am surrounded by some of the most brilliant people, and I am honored to have them as my friends. I would also like to extend my special thanks to Dr. Minki Cho who had mentored me through my early years of PhD. I have been fortunate to be part of GREEN Lab.

On several research occasions, I would like to acknowledge Dr. Jeremy Tolbert, Dr. Kwanyeob Chae, Wen Yueh, Amit Trivedi, and Wan-Ning Lee who have contributed to the completion of my thesis.

At last, my greatest thanks to my parents Loenhian Lie and Piefung Wong, my siblings Meriyana Lie and Kevin Lie, and Stella Huang for their continuous love, care, and support.

# TABLE OF CONTENTS

| ACKNOV  | VLEDGEMENTS                                                       | iii  |

|---------|-------------------------------------------------------------------|------|

| LIST OF | TABLES                                                            | vii  |

| LIST OF | FIGURES                                                           | viii |

| SUMMA   | RY                                                                | xiii |

| СНАРТЕ  | <b>CR 1</b> INTRODUCTION                                          | 1    |

| 1.1     | Motivation                                                        | 1    |

| 1.2     | Existing Works                                                    | 2    |

|         | 1.2.1 CMOS Image Sensor                                           | 3    |

|         | 1.2.2 Wavelet Based Image Compression Method                      | 5    |

|         | 1.2.3 3D Integrated Circuits                                      | 7    |

|         | 1.2.4 Existing Work in 3D Integrated Image Sensor                 | 7    |

| 1.3     | Thesis Objective and Organization                                 | 8    |

| СНАРТЕ  | <b>CR 2</b> MULTI-SEGMENT IMAGE COMPRESSION FOR THE 3D IN-        |      |

|         | TEGRATED IMAGE SENSOR                                             | 10   |

| 2.1     | Introduction                                                      | 10   |

| 2.2     | Background                                                        | 11   |

|         | 2.2.1 Core-to-Buffer Network for 3D-Integrated System             | 12   |

|         | 2.2.2 Implementation of the Coding Algorithm                      | 14   |

| 2.3     | System Description                                                | 16   |

| 2.4     | Analysis for Threshold Coding                                     | 19   |

|         | 2.4.1 Die Area of the Multi-Segment Image Compression             | 19   |

|         | 2.4.2 Data Volume Overhead and Image Quality of the Multi-Segment |      |

|         | Image Compression                                                 | 19   |

|         | 2.4.3 Performance and Power Analysis of the Multi-Segment Image   |      |

|         | Compression                                                       | 21   |

|         | 1 11                                                              |      |

| 2.5     | Analysis for Huffman Coding                                       | 28   |

|         | 2.5.1 System Description of the Huffman Coding                    | 28   |

|         | 2.5.2 Die Area of MuSIC with Huffman Coding                       | 29   |

|         | 2.5.3 Data Volume Overhead of MuSIC with Huffman Coding           | 29   |

|         | 2.5.4 Performance and Power of MuSIC with Huffman Coding          | 32   |

| 2.6     | Summary                                                           | 35   |

| СНАРТЕ  | <b>CR 3</b> NOISE ANALYSIS FOR THE 3D-INTEGRATED IMAGE SEN-       |      |

|         | SOR                                                               | 37   |

| 3.1     | Introduction                                                      | 37   |

| 3.2     | Background                                                        | 37   |

|        | 3.2.1   | Operations of a Basic Logarithmic CMOS Image Sensor            | 38 |

|--------|---------|----------------------------------------------------------------|----|

|        | 3.2.2   | Noise Elements in the Logarithmic CMOS Image Sensor            | 38 |

|        | 3.2.3   | Fundamentals for Modeling the Spatial Noise of the Logarithmic |    |

|        |         | CIS                                                            | 40 |

|        | 3.2.4   | Fundamentals for Modeling the Temporal Noise of the Logarith-  |    |

|        |         | mic CIS                                                        |    |

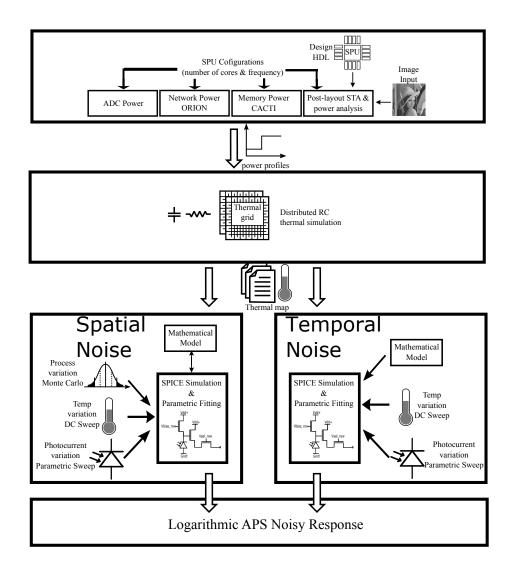

| 3.3    | •       | n Simulation and Analysis Framework                            |    |

|        | 3.3.1   | Power Analysis of SPU, Image Buffer, and Network               |    |

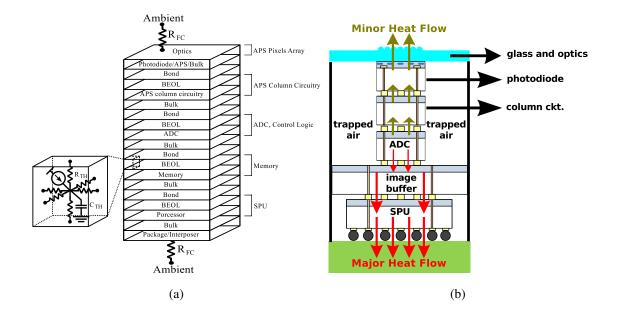

|        | 3.3.2   | Thermal Analysis of 3D Stack                                   |    |

|        | 3.3.3   | Noise Analysis of a Logarithmic CMOS Image Sensor              |    |

| 3.4    | Simula  | ation Results                                                  |    |

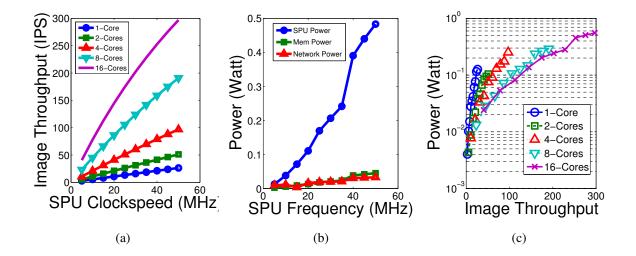

|        | 3.4.1   | Power and Performance of Image Compression Unit                | 50 |

|        | 3.4.2   | Thermal Coupling, and CIS Output Response                      | 53 |

|        | 3.4.3   | Spatial Noise                                                  | 55 |

|        |         | 3.4.3.1 The Effect of Image Throughput on Image Quality        | 55 |

|        |         | 3.4.3.2 The Effect of Output Datarate on Image Quality         | 57 |

|        | 3.4.4   | Temporal Noise                                                 | 60 |

|        | 3.4.5   | The Effect of Spatial and Temporal Noise to Image Quality      | 61 |

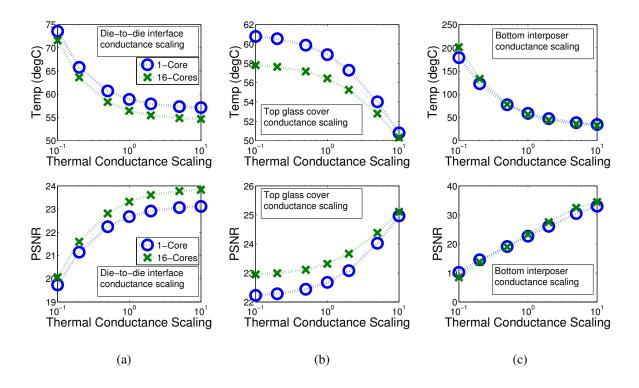

|        | 3.4.6   | The Effect of Varying Thermal Conductance                      | 63 |

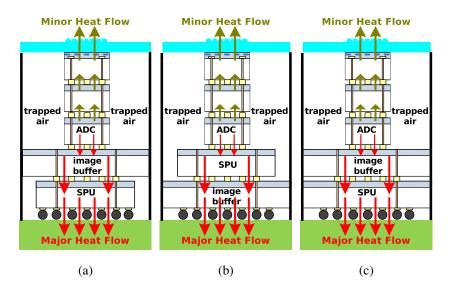

|        | 3.4.7   | Alternate 3D-Stacking Scenarios                                | 65 |

| 3.5    | Summ    | ary                                                            | 67 |

| CHAPTI | ER 4    | ANALYSIS OF HETEROGENEOUS INTEGRATION FOR THE                  | E  |

|        |         | <b>3D STACKED IMAGE SENSOR SYSTEM</b>                          | 68 |

| 4.1    | Introdu | uction                                                         | 68 |

| 4.2    | Motiva  | ation for Technology Scaling                                   | 69 |

| 4.3    | Experi  | ment Setup                                                     | 70 |

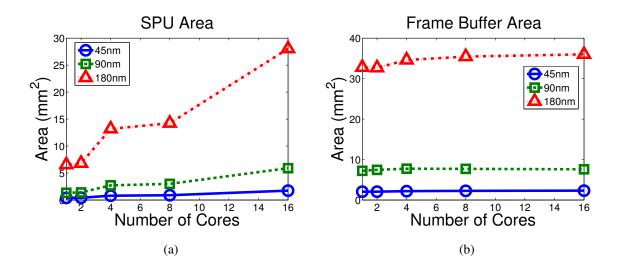

| 4.4    | Effect  | of Heterogeneous Integration to Die Area of the 3D-Stack       | 73 |

| 4.5    | Power   |                                                                | 74 |

|        | 4.5.1   | Effect of Technology Scaling to Power                          | 74 |

|        | 4.5.2   | Second Degree Heterogeneous Integration of the Compression     |    |

|        |         | Module                                                         | 76 |

| 4.6    | Power   | Efficiency for a Wireless Image Sensor Node                    | 79 |

|        | 4.6.1   | Maximizing Throughput for a Given Power Budget                 | 80 |

|        | 4.6.2   | Minimizing Power for a Given Target Throughput                 | 84 |

| 4.7    | Optim   | izing for Low Power Low Throughput Operation                   | 88 |

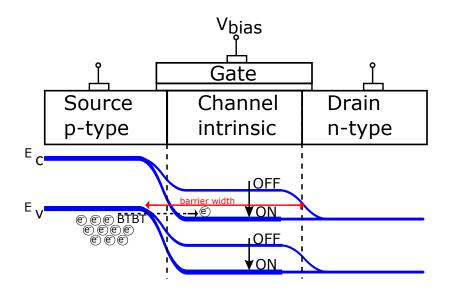

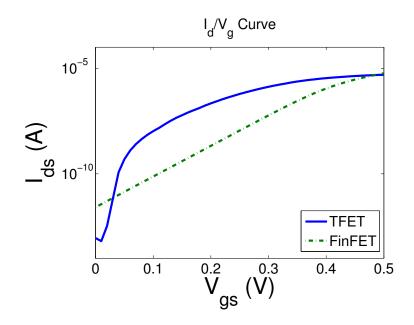

|        | 4.7.1   | Electrical Characteristics of the TFET Device Model            | 88 |

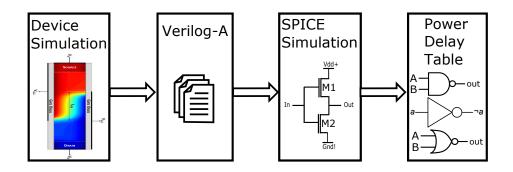

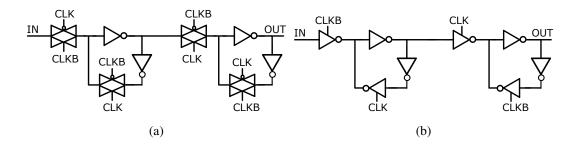

|        | 4.7.2   | TFET Based Digital Logic Library                               | 90 |

|        | 4.7.3   | Simulation Results                                             | 92 |

| 4.8    | Summ    | ary                                                            | 92 |

| CHAPTI | ER 5    | CONCLUSIONS                                                    | 94 |

| 5.1    | Summ    | ary and Contribution                                           | 94 |

| 5.2    |         | mendation for Future Work                                      | 97 |

|        |         |                                                                |    |

| <b>REFERENCES</b> . | • |  |  |  |  |  |  | • |  | • |  |  | • | • |  |  |  |  | • | 9 | 8 |

|---------------------|---|--|--|--|--|--|--|---|--|---|--|--|---|---|--|--|--|--|---|---|---|

|                     |   |  |  |  |  |  |  |   |  |   |  |  |   |   |  |  |  |  |   |   |   |

# LIST OF TABLES

| Table 1 | Discrete Wavelet Transform Filter Pair                              | 16 |

|---------|---------------------------------------------------------------------|----|

| Table 2 | Materials Parameters                                                | 48 |

| Table 3 | Grid and Area Parameters                                            | 49 |

| Table 4 | List of Logic Gates for the Libraries                               | 71 |

| Table 5 | Effect of Heterogeneous Integration to the Die Area of the 3D-Stack | 73 |

| Table 6 | TFET Process Parameters                                             | 89 |

# LIST OF FIGURES

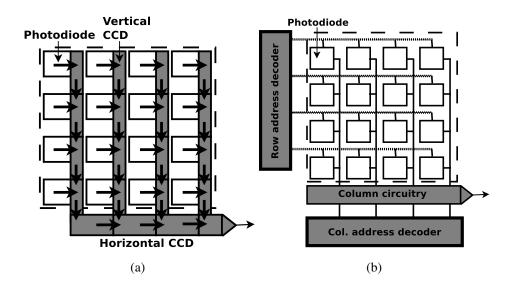

| Figure 1  | Read out mechanism in image sensor. (a) CCD image sensor. (b) CMOS image sensor.                                                                                                                                                                                                                               | 4  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

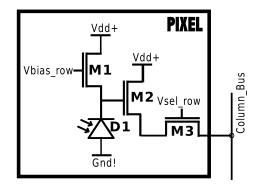

| Figure 2  | Pixel schematic of a typical logarithmic CIS.                                                                                                                                                                                                                                                                  | 4  |

| Figure 3  | Flow diagram of a typical wavelet based image compression                                                                                                                                                                                                                                                      | 5  |

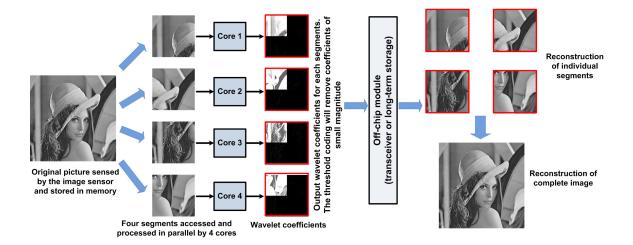

| Figure 4  | A flow diagram of the multi-segment image compression                                                                                                                                                                                                                                                          | 10 |

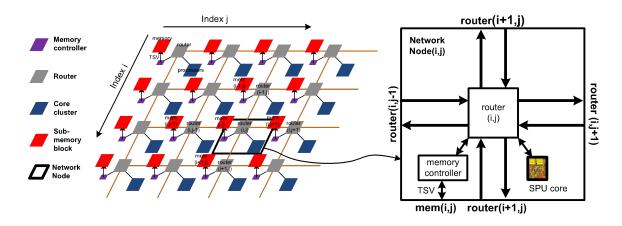

| Figure 5  | An illustration of the X-Y routing scheme for the core-to-buffer network.                                                                                                                                                                                                                                      | 12 |

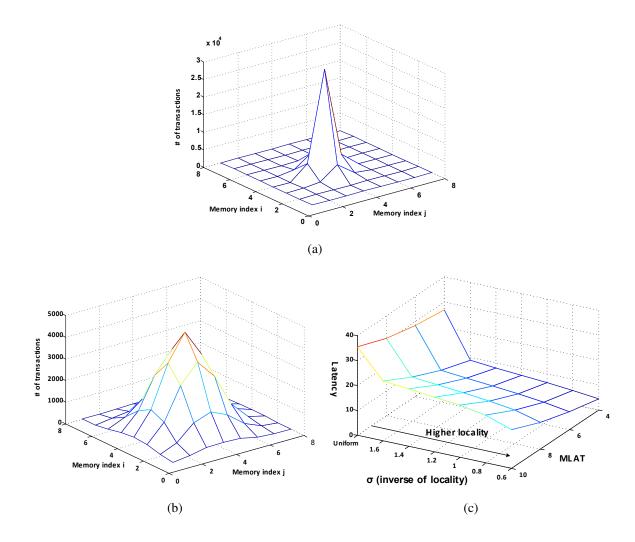

| Figure 6  | Network simulation for varying spatial locality to illustrate the need for MuSIC: (a and b) target access memory((i,j) node) location for (a) higher ( $\sigma = 0.6$ ), (b) lower ( $\sigma = 1.6$ ) spatial locality; (c) Sensitivity of latency to the address locality and the memory latency (8x8 nodes). | 13 |

| Figure 7  | Block diagram of DWT convolution.                                                                                                                                                                                                                                                                              | 14 |

| Figure 8  | Block diagram of memory access for direct implementation of 2D DWT.                                                                                                                                                                                                                                            | 15 |

| Figure 9  | Efficient line based 2D discrete wavelet transform (2D-DWT). (a) Temporary buffer to contain the intermediate coefficients during the 2D transform. (b) A flow diagram of the 2D transform                                                                                                                     | 15 |

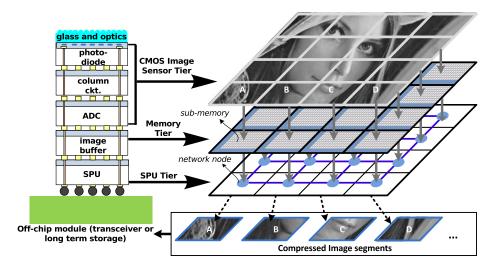

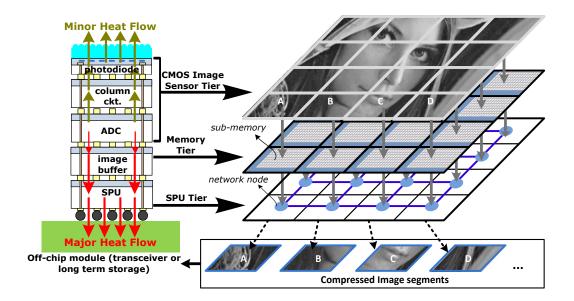

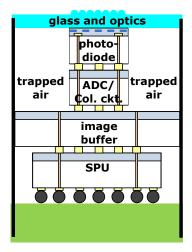

| Figure 10 | An illustration of the 3D-integrated multi-segment image compression system.                                                                                                                                                                                                                                   | 17 |

| Figure 11 | DWT architectural consideration. (a) SPU pipeline stage. (b) Registers for the intermediate buffer.                                                                                                                                                                                                            | 18 |

| Figure 12 | Effect of increasing number of segments to the SPU die area. (a) Area versus number of cores in Threshold coding scheme. (b) Intermediate buffer size expansion with an increase in number of segments along the x-direction (top right) and y-direction (bottom left)                                         | 20 |

| Figure 13 | Effect of increasing number of segments to the SPU data volume for threshold coding.                                                                                                                                                                                                                           | 21 |

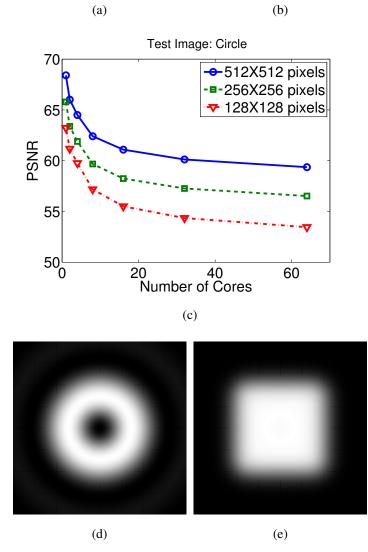

| Figure 14 | Effect of multi-segment compression to the image quality. (a) Circle test image. (b) Square test image. (c) Image degradation of the circle test image introduced by MuSIC. (d) After compression circle image compressed with 64 cores. (e) After compression square image compressed with 64 cores.          | 22 |

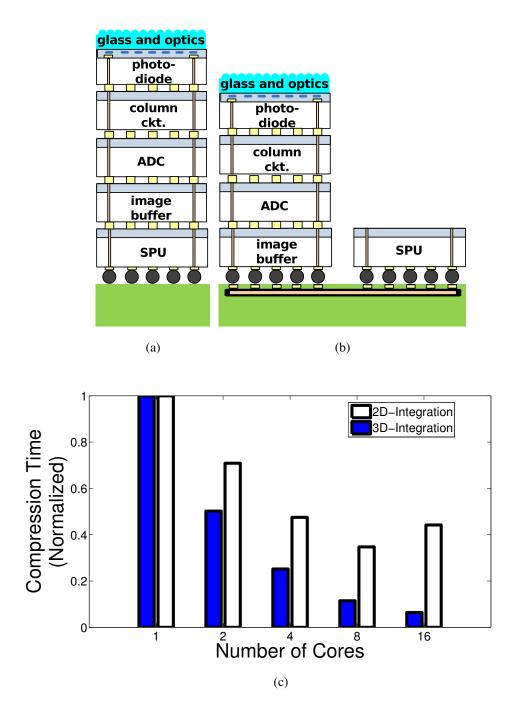

| Figure 15 | Effect of increasing number of segments to the architectural performance<br>in 2D- and 3D-integration. (a) 3D-integration of image buffer and SPU.<br>(b) 2D-integration of image buffer and SPU. (c) Compression time ver-<br>sus number of cores.                                                                                 | 23 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

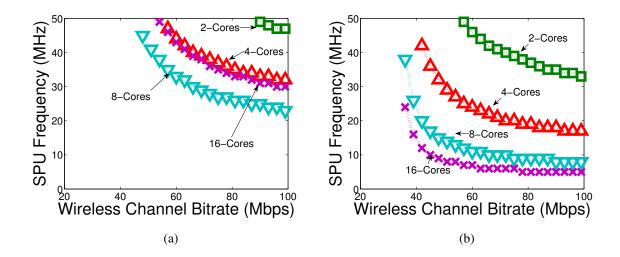

| Figure 16 | System performance of the image compression system in 2D- and 3D-<br>integration, considering variations in wireless channel condition, SPU<br>clock speed, and number of SPU cores. (a) System in 2D-Integration.<br>(b) System in 3D-Integration.                                                                                 | 24 |

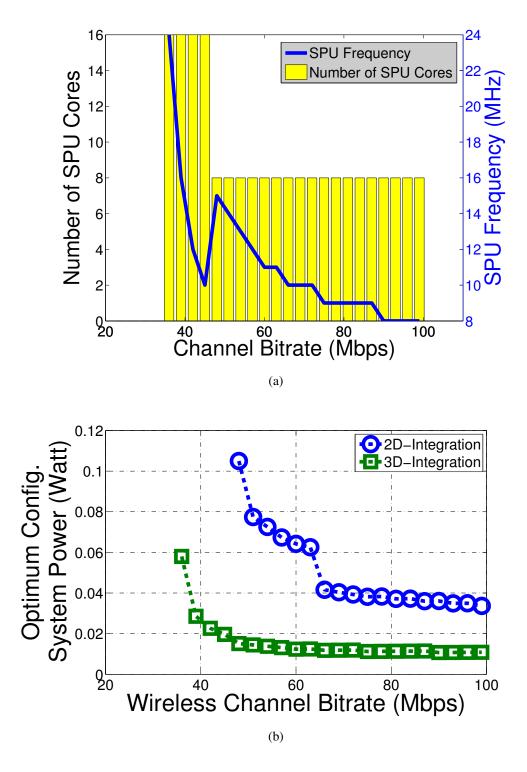

| Figure 17 | Effect of varying channel conditions to the SPU configurations and power dissipation. (a) SPU configurations versus channel bitrate. (b) SPU power versus channel bitrate                                                                                                                                                           | 25 |

| Figure 18 | Multi clock domain scheme                                                                                                                                                                                                                                                                                                           | 27 |

| Figure 19 | Comparison in the SPU power dissipation between the multi-clock-domain scheme and the single-clock-domain scheme.                                                                                                                                                                                                                   | 27 |

| Figure 20 | Flow diagram to illustrate: (a) the parallel Huffman scheme, and (b) the serial Huffman scheme.                                                                                                                                                                                                                                     | 30 |

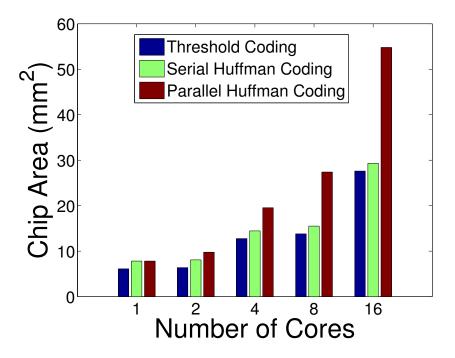

| Figure 21 | Die area comparison between the serial and parallel Huffman schemes.                                                                                                                                                                                                                                                                | 31 |

| Figure 22 | Die area comparison between the Threshold and the Huffman coding shcemes.                                                                                                                                                                                                                                                           | 31 |

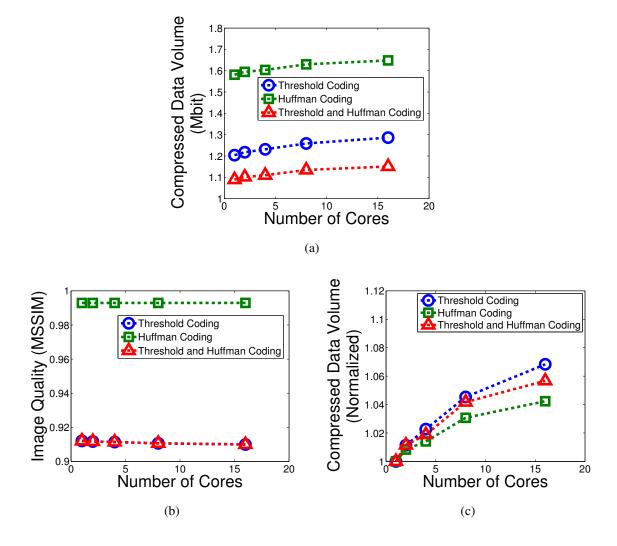

| Figure 23 | Effect of increasing number of segments to: (a) the compressed data volume, (b) the image quality, and (c) the data volume normalized to the single-core case for different coding methods.                                                                                                                                         | 33 |

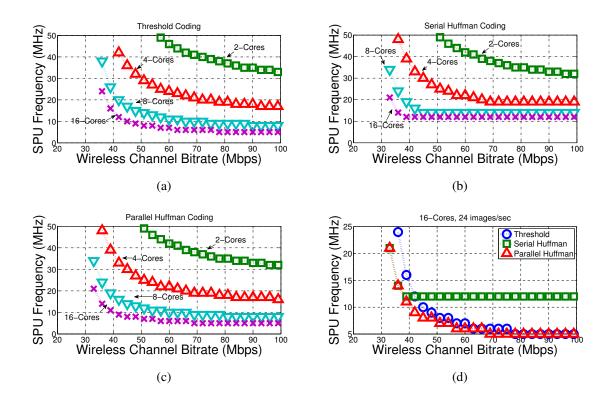

| Figure 24 | Performance of the image compression system considering variations in wireless channel conditions for various encoding schemes: (a) threshold coding, (b) serial Huffman coding, (c) parallel Huffman coding. (d) SPU clock speed comparison between the threshold, serial Huffman, and parallel Huffman coding for a 16-cores SPU. | 34 |

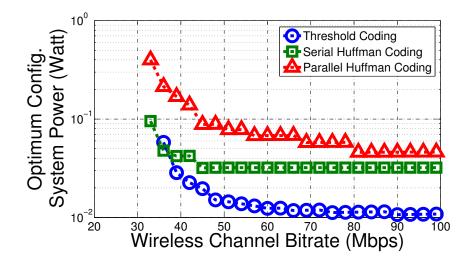

| Figure 25 | Comparison in the SPU power dissipation between the threshold coding, the serial Huffman coding, and the parallel Huffman coding.                                                                                                                                                                                                   | 35 |

| Figure 26 | Conceptual diagram of the 3D integrated image sensing and compression system.                                                                                                                                                                                                                                                       | 38 |

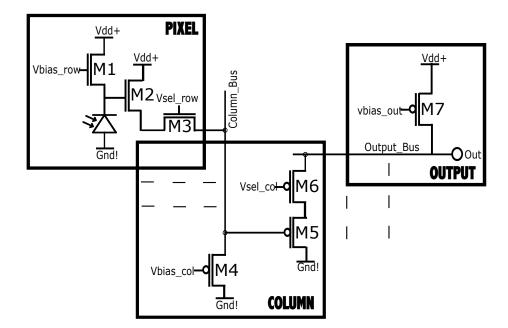

| Figure 27 | Logarithmic CMOS Image Sensor Circuit.                                                                                                                                                                                                                                                                                              | 39 |

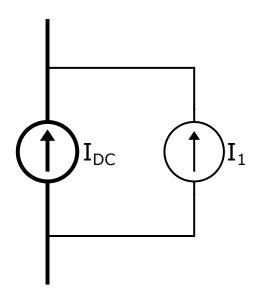

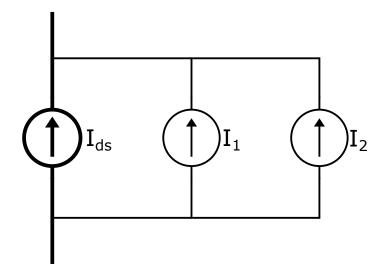

| Figure 28 | Circuit model for thermal and flicker noise.                                                                                                                                                                                                                                                                                        | 41 |

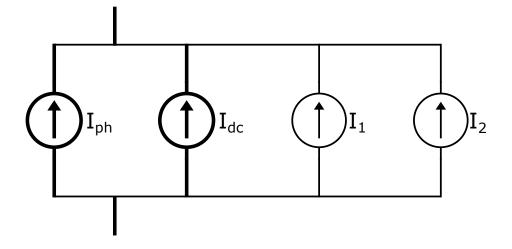

| Figure 29 | Circuit model for temporal noise of a photodiode                                                                                                                                                                                                                                                                                    | 42 |

| Figure 30 | Circuit model for temporal noise of a CMOS transistor                                                                                                                                                                                                                                                                                                                                                     | 43 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 31 | A diagram of the thermal simulation framework for the 3D-integrated image sensor.                                                                                                                                                                                                                                                                                                                         | 45 |

| Figure 32 | Thermal grid model of the 3D image sensor: (a) The grid unit cell and the stacked layers used in the thermal grid model. (b) The 3D stacking scenario of the image sensor system.                                                                                                                                                                                                                         | 48 |

| Figure 33 | The analysis of the performance and power of the 3D image compression<br>unit: (a) Image rate with varying SPU clock speed of the multi-core im-<br>age compression system. (b) Power dissipation versus SPU clock speed<br>of a 16-Cores image compression system. (c) Power versus performance<br>of the multicore image compression system, when the SPU clock speed<br>is varied from 5 MHz to 50 MHz | 51 |

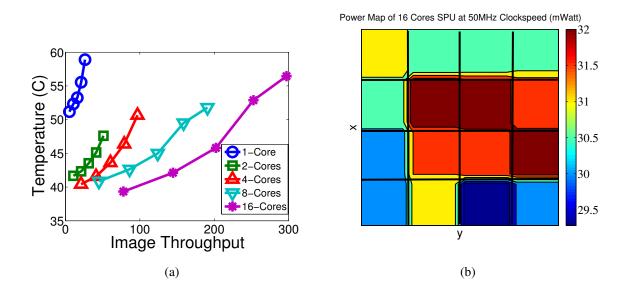

| Figure 34 | Thermal analysis of the 3D image sensor: (a) Temperature variation of the photo-diode tier with varying image rate throughput. The throughput corresponds to the following SPU clock speed: 10, 20, 30, 40, and 50 MHz. (b) Power map of the 16-cores SPU at 50 MHz                                                                                                                                       | 52 |

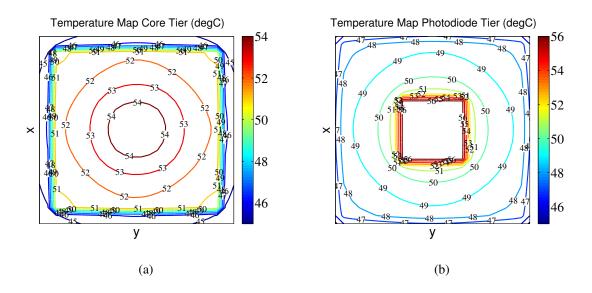

| Figure 35 | Thermal analysis of the 3D image sensor: (a) Temperature map of the core tier, and (b) temperature map of the photodiode tier of the 16-cores system at 50 MHz.                                                                                                                                                                                                                                           | 53 |

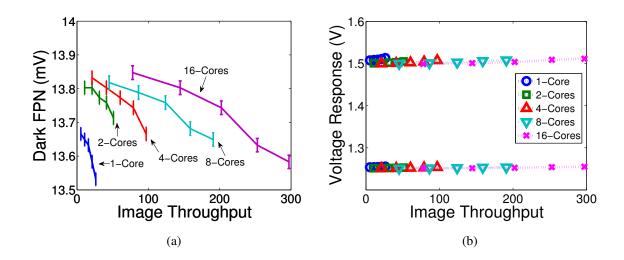

| Figure 36 | Effect of the image throughput to the sensor noise and the output volt-<br>age response considering a plain dark (black) image, and a plain bright<br>(white) image: (a) The fixed pattern noise (FPN) at dark considering<br>variations in 100 imagers, and (b) the output range of the logarithmic<br>CIS with varying image throughput                                                                 | 54 |

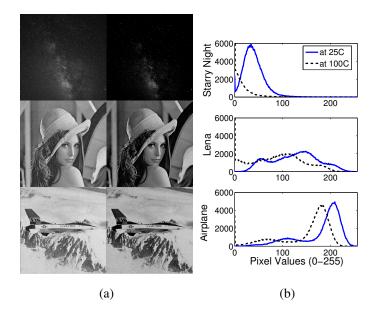

| Figure 37 | A scene of a starry night, Lena, and an airplane from top to bottom. (a) Effect of FPN distortion to the images at 25C (left) and 100C (right). (b) Pixel histogram of the images at 25C and 100C                                                                                                                                                                                                         | 56 |

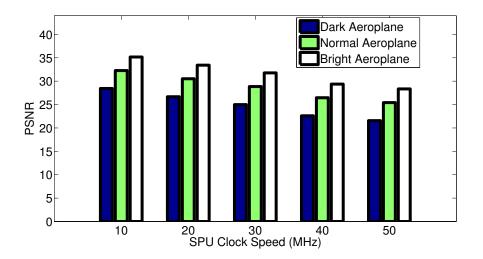

| Figure 38 | Effect of the lighting condition to the image quality of the airplane scene due to spatial noise: PSNR comparisons of the airplane scene in different lighting condition when the image is processed by a 16-cores system                                                                                                                                                                                 | 56 |

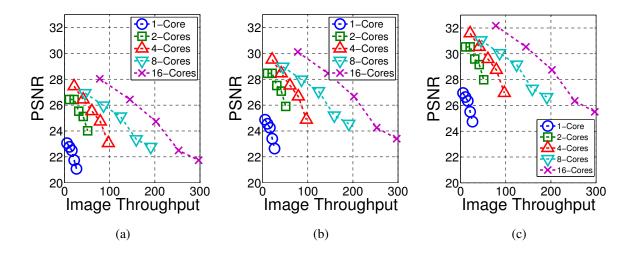

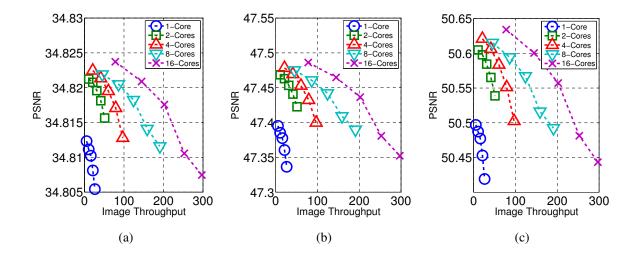

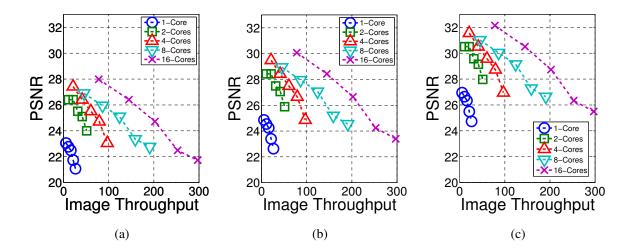

| Figure 39 | Effect of the lighting condition to the image quality due to spatial noise:<br>(a) scene with dark lighting, (b) scene with normal lighting, and (c) scene<br>with bright lighting. The throughput corresponds to the following SPU<br>clock speed: 10, 20, 30, 40, and 50 MHz                                                                                                                            | 58 |

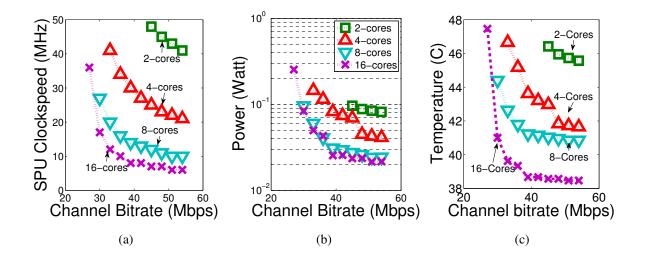

| Figure 40 | Effect of the wireless channel bitrate on the 3D image sensor, assuming<br>a 24 images/sec throughput: (a) SPU clock speed versus channel bitrate.<br>(b) Power (SPU, image buffer, and network power) versus channel bi-<br>trate. (c) Temperature at the photo-diode tier versus channel bitrate                                                                                                        | 58 |

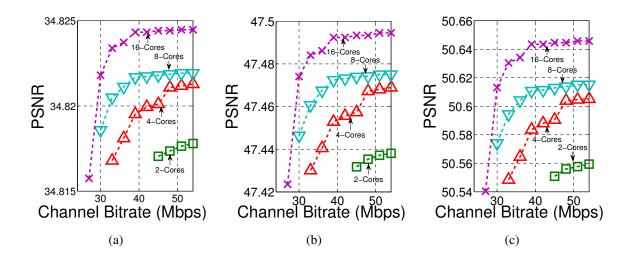

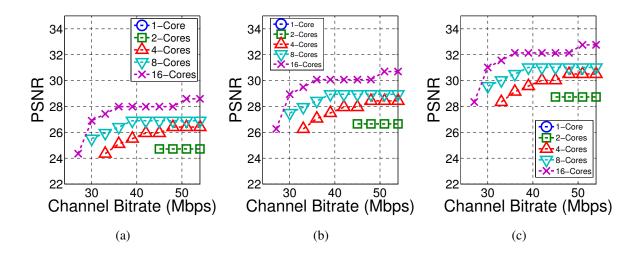

| Figure 41 | Effect of the wireless channel bitrate on the image quality due to spatial noise: (a) scene with dark lighting, (b) scene with normal lighting, and (c) scene with bright lighting. The image throughput is 24 images/sec                                                             | 59 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

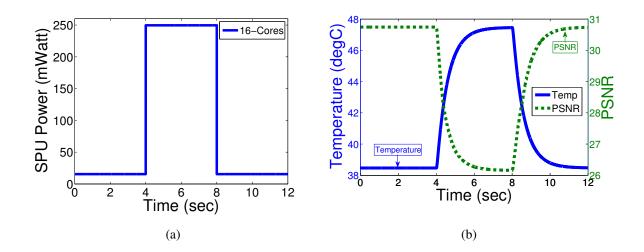

| Figure 42 | Transient analysis of a 16-cores system compressing images at 24 im-<br>ages/sec throughput rate, and the channel bitrate switches from 54Mbps<br>to 27Mbps and back to 54Mbps. (a) SPU versus time. (b) Temperature<br>of the photodiode tier and the corresponding PSNR versus time | 60 |

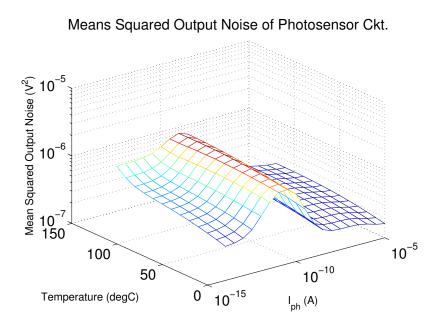

| Figure 43 | Temporal noise squared output voltage across temperature and illumina-<br>tion                                                                                                                                                                                                        | 61 |

| Figure 44 | Effect of the lighting condition to the image quality due to temporal noise: (a) scene with dark lighting, (b) scene with normal lighting, and (c) scene with bright lighting. The throughput corresponds to the following SPU clock speed: 10, 20, 30, 40, and 50 MHz.               | 62 |

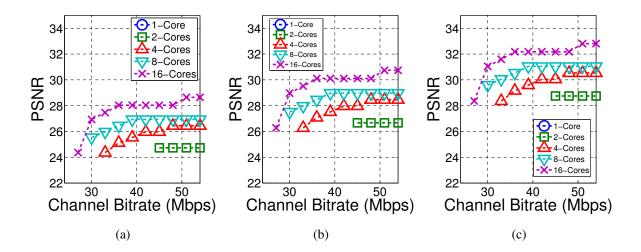

| Figure 45 | Effect of the wireless channel bitrate on the image quality due to temporal noise: (a) scene with dark lighting, (b) scene with normal lighting, and (c) scene with bright lighting. The image throughput is 24 images/sec.                                                           | 62 |

| Figure 46 | Effect of the lighting condition to the image quality due to spatial and temporal noise: (a) scene with dark lighting, (b) scene with normal lighting, and (c) scene with bright lighting. The throughput corresponds to the following SPU clock speed: 10, 20, 30, 40, and 50 MHz    | 63 |

| Figure 47 | Effect of the wireless channel bitrate on the image quality due to spatial and temporal noise: (a) scene with dark lighting, (b) scene with normal lighting, and (c) scene with bright lighting. The image throughput is 24 images/sec.                                               | 64 |

| Figure 48 | Effect of varying thermal conductance in the (a) die-to-die interface, (b) top glass cover, and (c) bottom interposer to the thermal coupling and image quality.                                                                                                                      | 64 |

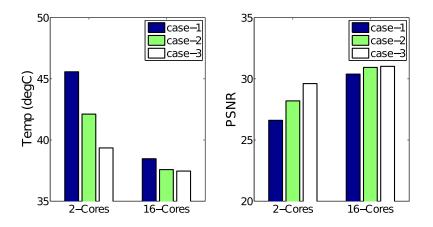

| Figure 49 | Alternative stacking scenarios for the image sensing system. (a) Case 1:<br>SPU at the bottom of the stack. (b) Case 2: image buffer at the bottom<br>of the stack. (c) Case 3: the SPU die area is widened to match the image<br>buffer die area.                                    | 66 |

| Figure 50 | Effect of the alternative stacking scenarios on the temperature of the pho-<br>todiode tier and the image quality.                                                                                                                                                                    | 66 |

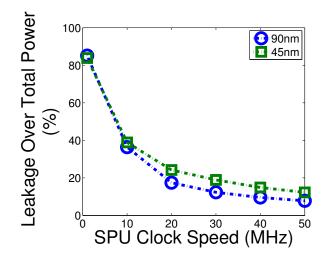

| Figure 51 | Percentage contributions of leakage power of the SPU in 90nm and 45nm process.                                                                                                                                                                                                        | 70 |

| Figure 52 | Effect of technology scaling to die area of the 3D-stack                                                                                                                                                                                                                              | 72 |

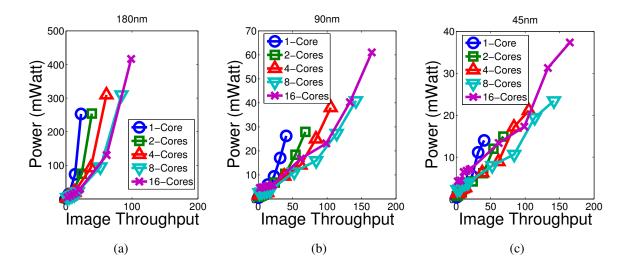

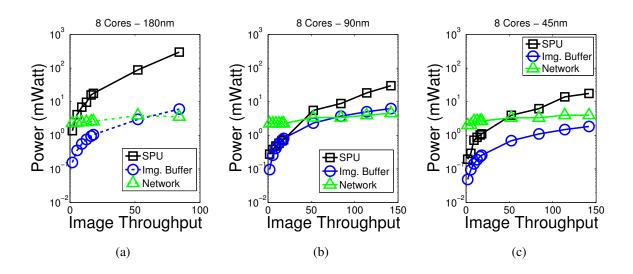

| Figure 53 | Power curves of the multicore system as a function of image throughput simulated in (a) 180nm, (b) 90nm, and (c) 45nm process libraries                                                                                                                                                                                                                                              | 75 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 54 | Power curves of the 16-cores SPU, image buffer, and network as a func-<br>tion of image throughput simulated in (a) 180nm, (b) 90nm, and (c)<br>45nm process libraries.                                                                                                                                                                                                              | 75 |

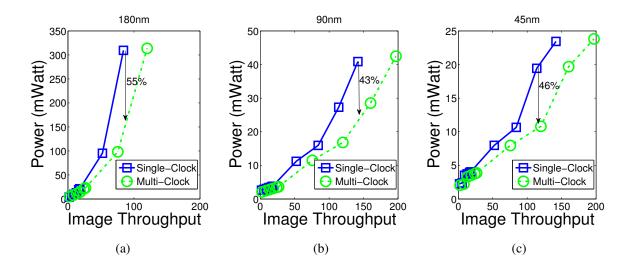

| Figure 55 | Power comparison between the multiclock-domain and singleclock-domain schemes simulated in (a) 180nm, (b) 90nm, and (c) 45nm process libraries.                                                                                                                                                                                                                                      | 76 |

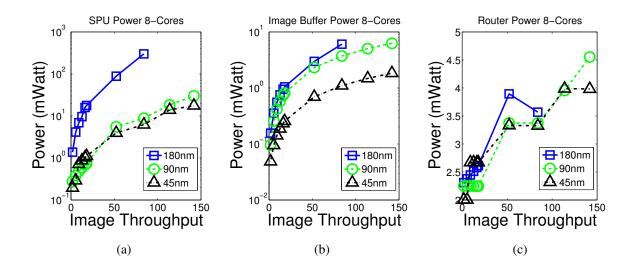

| Figure 56 | Power comparisons of the (a) SPU, (b) image buffer, and (c) network router across different technology nodes.                                                                                                                                                                                                                                                                        | 77 |

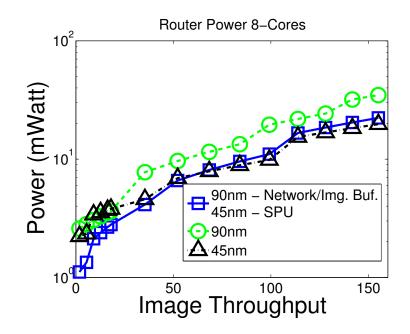

| Figure 57 | Power comparison between 1st degree heterogeneous and 2nd degree heterogeneous integration of the compression module. In 1st degree heterogeneous system, the compression module is implemented in one process node (90nm or 45nm). In 2nd degree heterogeneous system, the compression module is implemented using 90nm and 45nm for the image buffer/network and SPU respectively. | 78 |

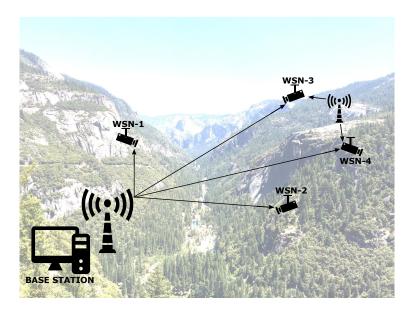

| Figure 58 | Wireless Image Sensor Network                                                                                                                                                                                                                                                                                                                                                        | 80 |

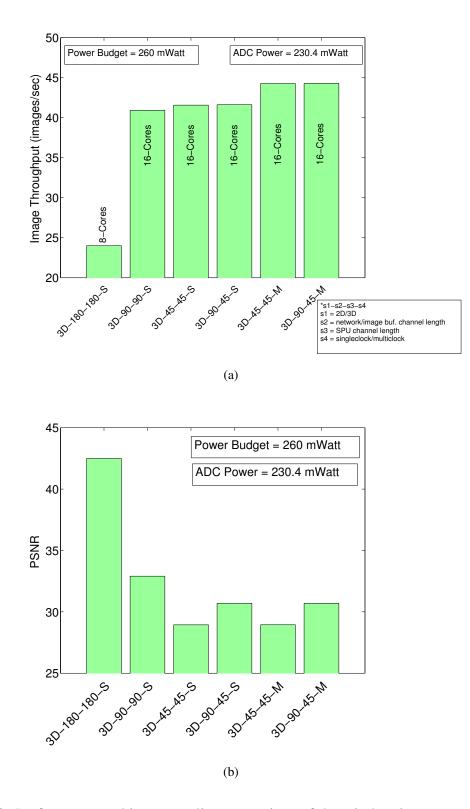

| Figure 59 | Performance and image quality comparison of the wireless image sensor<br>node synthesized in various integration schemes. (a) Change in image<br>throughput. (b) Change in image quality.                                                                                                                                                                                            | 83 |

| Figure 60 | Four stacks structure of the 3D integrated image sensor.                                                                                                                                                                                                                                                                                                                             | 84 |

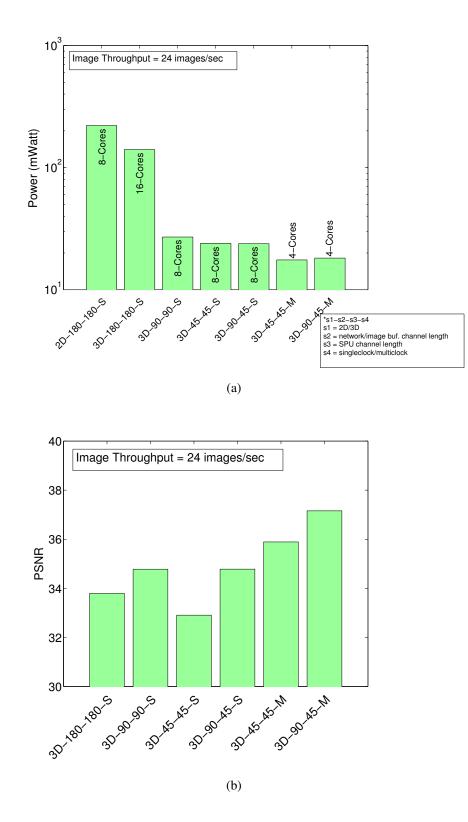

| Figure 61 | Power and image quality comparison of the wireless image sensor node synthesized in various integration schemes. (a) Change in power. (b) Change in image quality.                                                                                                                                                                                                                   | 86 |

| Figure 62 | Schematic and band diagram of a TFET                                                                                                                                                                                                                                                                                                                                                 | 89 |

| Figure 63 | Transconductance of the n-TFET and n-FinFET models                                                                                                                                                                                                                                                                                                                                   | 90 |

| Figure 64 | Flow diagram to build the TFET logic library.                                                                                                                                                                                                                                                                                                                                        | 91 |

| Figure 65 | Master-slave flip flop schematics. (a) Transmission gate implementation commonly found in CMOS libraries. (b) Tristate inverter implementation used for the TFET and FinFET library.                                                                                                                                                                                                 | 91 |

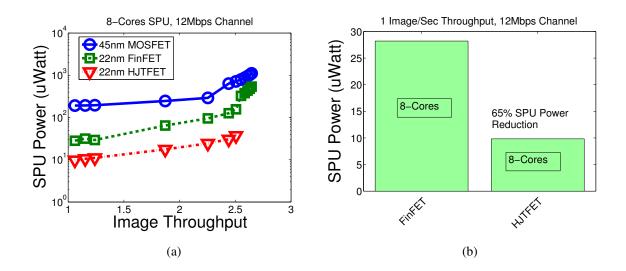

| Figure 66 | Power comparison of the SPU of the low performance wireless image sensor synthesized in (a) 45nm MOSFET, 22nm FinFET, and 22nm HJT-FET with varying throughput, (b) 22nm FinFET and 22nm HJTFET at 1 image/second throughput.                                                                                                                                                        | 93 |

# SUMMARY

Energy-efficient processing of sensor information has emerged as a key challenge for the next generation system. The need for real-time processing while maintaining the quality of the processed information is critical in various applications ranging from ultra-low-power wireless sensor node to high performance mobile systems. To improve image throughput with limited power, a 3D-integration of the image compression module is proposed as a solution in this work. A methodology in designing such system is investigated considering dynamically changing requirements (varying channel condition, and throughput demand), and low power operation through system architecture and device technology choices. First, a multi-segment/multi-core image compression approach is presented as a combined solution with 3D-stacking to reduce the workload of the compression module, effectively increasing power efficiency of the system. Second, vertical stacking reduces the rate of heat removal from the compression module and ADC. This dissertation analyzes the impact of thermal coupling to the noise level of the photosensor and quality of the compressed image. The analysis observes that image quality is strongly influenced by the desired image throughput, architectural configuration of the system, and outside environment factors, as a result of die-to-die thermal coupling in the stack. Third, a heterogeneous integration of the photosensor module and compression module, each designed in different technology nodes, is presented. In particular, the opportunity of scaling the compression engine including image buffers to deep sub-micron technology is analyzed while keeping the CMOS image sensor at less advanced 180nm process. As a result, power dissipation and die area reduce with decreasing channel length, however image quality also degrades due to increased power density and reduced heat spreading. Although 3D-integration is a concrete solution to increase power/performance efficiency of the image sensing system, die-to-die thermal coupling may provide challenges in managing the quality of the compressed images.

# CHAPTER 1 INTRODUCTION

## **1.1 Motivation**

Image sensing is an essential feature used in many fields such as consumer electronics, media, scientific research, security, medicine, and transportation. A typical digital image sensing unit consists of an image sensor, a signal processing unit (SPU), and an off-chip module for storage or transmitting the sensed image. Historically, advancement in the image sensing technology have been motivated by demands for highly functional (i.e. low noise, high dynamic range), high performance (i.e. high speed, high resolution), and low cost digital cameras and video cameras [1]. Recent advancement in portable electronics, such as smart phones and smart appliances, have fueled demands for fully integrated, small sized, and low power image sensors, while still pushing for maximum functionality and performance [1, 2].

In the last fifty years, advancement in system integration and performance has been achieved mainly through technology scaling. However, as the complexity of the system grows, floor planning constraints post new challenges in efficiently routing the interconnects and minimizing the communication bottlenecks. These issues may be minimized with 3D-integration technology [3]. For example, in a traditional 2D-integrated image sensing system, the image sensor and the SPU are placed separately with limited interconnect ports to read out the image data from the sensor to the SPU. With the 3D-integration, these two components can be stacked on top of each other, with many vertical interconnects for high bandwidth read out. In addition, the two tiers can potentially be build using different process technologies, where each component can be highly optimized [4]. This technology has the potential benefits in achieving not only high performance, but also low power and highly portable image sensing unit.

Along with improving the device technology, image processing is also an essential step

in increasing the usability of the image data. Typical examples of image processing includes data compression, noise reduction, smoothing filter, dynamic range enhancement, and features detection. Among the above, image compression is critical in reducing redundancy in the image data. For example, a JPEG2000 compression algorithm [5] typically has a compression gain of 20 percent with a 1920x1080 image resolution. The significant reduction in the image size can potentially minimize power in transferring data across a wireless channel [6], as well as store the image efficiently. However, image compression requires heavy computation, and the computing requirement grows with increasing image resolution. Therefore, it is necessary to develop techniques to maximize the efficiency of the system integration.

3D-integration may restrict heat flow generated by the SPU and other components in the system [4, 7, 8]. A variation in the temperature has direct impact to the device parameters of the photodiode arrays, the pixel circuits, and the column circuits, thus changing the CIS characteristics and affecting image quality. Essentially, there is a complex interactions between the performance, power, and thermal coupling in the integrated system. Understanding and taking the interactions into account can help avoid harmful effects on the image quality.

# **1.2 Existing Works**

Prior works in digital image sensors date back to 1964, with the invention of the first CCD and CMOS based image sensor. Since then, developments in image sensing and compression technology have continued to progress and mature. In addition, recent developments in 3D integrated circuit (3DIC) technology have set a new trend in designing complex digital systems, and may prove beneficial for image sensing application. The following subsections briefly observe existing works in image sensor, compression, and 3DIC.

#### 1.2.1 CMOS Image Sensor

Early development in digital image sensor technology have resulted in the creation of charge coupled device (CCD) and complementary metal oxide semiconductor (CMOS) image sensor. Nevertheless, CCD image sensor had been the primary device of choice since the beginning of its adoption in the early 1970s [9]. At that time, the CCD image sensor was proven to have extremely low noise compared to the CMOS image sensor, producing a superior image quality [1, 10]. For the next 20 years, majority of the research and development efforts had focused primarily on improving performance of the CCD image sensor. Throughout the first half of the 1990s, most of the digital still cameras and video capturing cameras used CCD technology, while only low end imaging functionality, such as an optical mouse, would consider CMOS based implementation. By the early 1990s, the CMOS process technology matured and was extensively use in digital electronics and microprocessors. Research and development efforts to improve image quality in the CMOS image sensor technology restarted, motivated by the possibility for low power operation, miniaturization, and high integration with a vision for camera-on-a-chip devices [11]. Since then, the performance of the CMOS image sensor has been steadily improving to match and potentially surpass its CCD counterpart [12].

Unlike CCD image sensor that use sequential charge transfer mechanism to read out an image (Figure 1a) [13, 14, 15], the CMOS image sensor use an X-Y address mechanism similar to the read out scheme in a digital memory (Figure 1b) [13, 16, 17]. The X-Y address scheme offers ability to access a specific pixel location, allowing for a flexible readout pattern. In addition, the CMOS image sensor has significantly lower power consumption during the readout sequence [10, 13]. In the X-Y address scheme, only activated pixels are switching. Meanwhile, in the charge transfer scheme, all the pixels have to be activated to transfer photo charges from one pixel to the next.

The active pixel sensor (APS) architecture is the prominent choice for the CMOS based pixel design. In the APS, a photo generated charge is amplified before it is read out to help

Figure 1: Read out mechanism in image sensor. (a) CCD image sensor. (b) CMOS image sensor.

Figure 2: Pixel schematic of a typical logarithmic CIS.

suppress noise in the readout path, as opposed to the original MOS passive pixel sensor (PPS) that doesn't have a gain stage in its pixel. During photo conversion, incidental light is linearly converted to photocurrent by the photodiode. Then this photocurrent is integrated into charge during the exposure. Finally, the collected charge is converted into voltage by the readout path. The above method is commonly referred as direct integration, and is used in the CCD image sensor as well as majority of the CMOS based pixel. In direct integration, photo conversion occurs in a highly linear fashion, and the response can be treated as an output of a linear system, hence it is often referred as linear pixel.

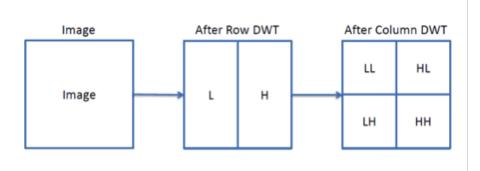

Figure 3: Flow diagram of a typical wavelet based image compression.

Although the current linear CMOS image sensors have surpassed their predecessors in many aspects, its dynamic range is still inferior as compared to the human eyes [18, 19, 20]. One possible option to improve dynamic range is by using a logarithmic photo conversion technique. Figure 2 shows a typical logarithmic CMOS image sensor (logarithmic CIS). Lights incidental to the photodiode generate photocurrent. The photocurrent has to be small enough to keep transistor M1 in the weak inversion region, hence the voltage at the source of transistor M1 has a logarithmic relationship with the photocurrent. The logarithmic CIS has a continuous pixel response, which leads to faster image capture time than direct integration sensor. The main drawback of the logarithmic CIS is its output noise is difficult to eliminate as compared to linear pixel [21, 18, 22].

#### **1.2.2 Wavelet Based Image Compression Method**

Image compression is essential in reducing redundancy in the image data so that data can be transmitted in an efficient way. Image compression can be divided into lossless compression and lossy compression. In a lossless compression, every single bit in the image data can be fully reconstructed to its original strings after the image is uncompressed. Huffman Coding [23], Arithmetic Coding [24], and Lempel-Ziv Coding [25, 26] are examples of famous traditional lossless compression algorithm that are still widely used today. Typical applications for lossless compression include medical imaging and space explorations [27, 28]. In a lossy compression, the image can not be reconstructed to its original image, because part of the detail in the image is discarded during compression. The lossy compression are generally capable of achieving high compression ratio with the expense of adding compression artifacts into the image. Typical applications for lossy compression include multimedia broadcasting and video streaming. Over the years, the use of discrete wavelet transforms (DWT) as a transform stage in the compression process has gained popularity. Figure 3 shows a flowchart for typical wavelet based image compression. First, the image is transformed to its frequency-spatial representation (wavelet coefficients) using the two dimensional discrete wavelet transform (2D-DWT). Next, the wavelet coefficients are quantized, and a coding technique is applied to reduce data representation of the compressed image. A popular wavelet filters pair is the biorthogonal Cohen-Daubechies-Feauveau (CDF) wavelet, which is used in JPEG2000 [29]. After the transform stage, different coding techniques such as Embedded Zerotree Wavelet (EZW) [30, 31], Set Partitioning In Hierarchical Trees (SPIHT) [30, 32], Embedded Bock Coding with Optimized Truncation (EBCOT) [33], or a simple lossy thresholding method can be applied to compress the image.

However, 2D-DWT requires heavy computation [34]. Although it is easy to compute the 2D-DWT in software, it is difficult to achieve a real-time hardware based implementation especially when the desired image size and frame rate are high. In traditional digital signal processing theory, the DWT is computed using a convolution method. Research efforts in the area had developed the lifting method which significantly reduces the number of adders and multipliers [35, 36]. The 2D-DWT is effectively an extension of a 1D-DWT for transforming a two-dimensional data array. In general, the 2D-DWT is a separate twosteps process that involves applying the 1D-DWT horizontally and vertically across the image. After the first DWT step (i.e. the horizontal DWT), a storage module is required to temporarily store the intermediate data, before it is sent to the second DWT step (i.e. the vertical DWT). The size of the intermediate storage is proportional to the length and width of the image. Since then, a line based scheme was developed as a simple and effective solution to significantly reduce the intermediate storage size [37, 38]. In the line based 2D-DWT, the intermediate storage size is proportional to the length of the image and the length of the finite impulse response (FIR) filter. On the other hand, numerous nonseparable techniques that compute the transform in a single step had also been presented [39, 40, 41]. Although, the non-separable techniques offer faster performance than the separable techniques, system implementation is relatively complex and requires significant hardware overhead.

#### **1.2.3 3D Integrated Circuits**

Vertically stacked circuits can be integrated together using the combination of through silicon vias (TSVs) and bonding structures [42, 43, 44, 45]. The die-to-die integration can be organized using a face-to-face stacking, face-to-back stacking, or back-to-back stacking.

The main benefits of 3D-integrated circuits for image sensing application include wide bandwidth interconnects, and reduced footprint of the system [3, 45]. In addition, the technology offers reduction in interconnect length, which leads to reduced interconnect delay and switching power. When an image is captured, electrical signal from each pixel has to be converted to digital signal and transferred to a storage element. In a conventional planar integration, it is a pixel by pixel sequential process. 3D-integration technology provides multiple parallel connections to the pixel array, which can reduce the capture time of the image. This technology also allows the photodiode to be build on a separate layer from the rest of the circuits to increase fill factor. In addition, the reduced footprint can be used to improve the resolution of the sensor.

However, 3D-integration technology have thermal management issues, which may hurt the image sensing application. Components such as analog to digital converter (ADC) and SPU consumes power and generates heat [46, 47]. In a dense 3D-integrated image sensor, heat flow is limited and the photo receptor circuit is thermally coupled with the rest of the system. Temperature variation affects noise behavior and pixel response characteristics of the photo sensor [10, 48].

### 1.2.4 Existing Work in 3D Integrated Image Sensor

3D integrations open new opportunities for high-speed and high-density image sensor design [49, 50, 51, 52, 53, 54]. Kiyoyama et. al. studied a block-parallel image sensing and processing architecture to allow analog to digital conversion and other image processing algorithm tasks be distributed across multiple blocks and performed in parallel [51, 52]. However, the focus of the work is only the design of the ADC and its integration to the pixels block. One of the early 3D stacked pixel sensor circuits was demonstrated by Suntharalingam et. al. [53], and later by Zhang et. al. [54]. Both works demonstrated 3D stacked CIS with high fill factor by separating the photodiode and the rest of the pixel circuitry on different layers. A simple pre-processing module integration with the sensor pixel has also been demonstrated by Zhang. The above research efforts provide initial concepts of an integrated photo sensor and image processor system in a 3D-stack, and demonstrations of the key components.

# 1.3 Thesis Objective and Organization

Although a full integration of photo sensor module and image processing engine has been conceptualized, a thorough analysis and optimization on such system is still yet to be performed. This research builds on the prior works on the 3D image sensors, analysis of temperature effects on CIS, and wavelet based image compressions. The objective of the proposed research is *to investigate a methodology in designing energy efficient 3D-integrated image sensor for network based applications considering dynamically changing requirements (varying channel condition, and throughput demand) and low power operation through system architecture and device technology choices*. This research examines the design integration of a CMOS image sensor (CIS) with image processing unit on a 3D stack. Specifically, a wireless image sensor node is considered in majority of the analysis. The potential of highly parallel image compression using a multicore SPU is explored as the main image processing engine. The effect of thermal coupling between the image sensor and the SPU, due to the power and performance of the system, on the noise characteristics of the CIS pixels is analyzed. Finally, a higher degree of optimization method for different performance range of applications through heterogeneous integration is explored.

The rest of this dissertation is organized as follow:

Chapter 2 proposes a multicore system architecture that is suitable for a 3D integration of a memory (image buffer) and a signal processing unit (SPU) in performing heavy compression task. The implication of the architecture and design parameters to the power, performance, and image quality of the system is discussed.

Chapter 3 investigates the effect of thermal coupling inside the 3D stack of the system. The analysis includes discussions on the power and performance of the system, thermal coupling in the 3D stack, and noise characteristics of the sensor. The quality of the compressed image depends on not only the noise level of the sensor but also the lighting condition of the captured object.

Chapter 4 examines the system level benefits of heterogeneous integration for the system. The idea is to optimize the system by integrating the image sensor elements and image processing elements in different technology nodes.

Chapter 5 presents the final conclusion, thesis contributions, and suggestions for follow up research topics.

# **CHAPTER 2**

# MULTI-SEGMENT IMAGE COMPRESSION FOR THE 3D INTEGRATED IMAGE SENSOR

# 2.1 Introduction

Image sensing is a common functionality in various applications like smart camera, and smart phone. A typical image sensing system includes an image sensor, a signal-processing unit (SPU), and an off-chip module for storage or transmission of the sensed image. Advancing high-speed imaging has been an important objective in many imaging applications. To achieve the goals, a 3D integration of photodiode array, multiple Analog-to-Digital Converters (ADC), and frame memory (image buffer) has been proposed to help fetch the image from the photodiode array faster [49, 50, 52, 53, 54].

Image compression is essential to reduce redundancy in the image data so that the data can be stored or transmitted in an efficient way. Different algorithms had been introduced to maximize compression ratio while maintaining an acceptable image quality. Among the many algorithms, the wavelet based compression has gained popularity. Namely the two-dimensional discrete wavelet transform (2D-DWT) is set as the standard transform function for JPEG2000 [5], MPEG4, and many compression algorithms. However, 2D-DWT

Figure 4: A flow diagram of the multi-segment image compression.

requires heavy computations, and hence various VLSI architectures had been proposed for the benefit of real-time image processing [34, 39, 36, 37, 38]. A key challenge in the DWT is the need for high-bandwidth connection between the SPU and the image buffer. Hence, it is expected that 3D stacking of the SPU and the image buffer can provide major performance gain for the processing unit [3].

In this chapter, a multi-segment image compression method is proposed as a high throughput signal processing architecture for a 3D-integrated image sensing system. In this method, the concept of parallel processing is applied by using a multi-core signal processing unit (multi-core SPU). Essentially, a captured image is divided into multiple segments (Figure 4). Each segment is treated as an independent image, and locally assigned to a signal processing core for compression. By maximizing the spatial locality between the photodiode array and the signal processing unit, the total compression latency of the image is significantly reduced. However, dividing the image into many segments reduces the compression ratio. In the case where off-chip data transmit rate (channel rate) is limited, the reduced compression ratio significantly increases the transmission latency. It also increases the power dissipation of the system. This section describes the design space of the multi-segment (number of cores) and the operating clock speed of the system considering specific target image throughput (frames per second), varying channel rate, and power dissipation of the system.

## 2.2 Background

This section provides background and reasoning for choosing the multi-segment image compression as a suitable signal processing architecture for the 3D-integrated image sensing system. As mentioned in the previous chapter, image compression is crucial in reducing image data volume for efficient transmission and storage. In this work, the wavelet based image compression is presented as the algorithm of choice. Different image coding algorithms such as the threshold coding, the Huffman coding, and a mixed threshold and

Figure 5: An illustration of the X-Y routing scheme for the core-to-buffer network.

Huffman coding are presented.

## 2.2.1 Core-to-Buffer Network for 3D-Integrated System

To understand the algorithms that can successfully benefit from 3D stacking, the coreto-buffer network in the 3D-stack needs to be carefully analyzed. In this work, a mesh type network topology with an X-Y routing scheme is considered. The entire network consists of multiple nodes (Figure 5). Each node comprises of a processor, a memory controller, and a network router. The router has four gates, i.e. north, west, south, and east, which connect it to neighboring nodes. The queue lines inside the router are implemented using FIFOs. In the case of multiple accesses, the arbitration is decided using the round robin algorithm. To motivate the need for MuSIC, we first study the generic behavior of the network considering randomly generated memory traffic from individual cores. The distance distribution of the memory accesses of each core is generated from a Poisson's process. The rate parameter ( $\lambda$ ) of the Poisson's process is determined by the memory access rate (r). A higher spatial locality implies a core is more likely to access the memory banks, which are physically close to the node to which the core is connected. A lower spatial locality implies that a core is more likely to access memory banks connected to the far nodes. We model the spatial locality behavior of the program using the Gaussian random process. Lower  $\sigma$  value indicates higher spatial locality i.e. transactions will be

consumed at near memories and less likely to traverse to the far node. As  $\sigma$  value increases, cores tend to access far memories. As shown in Figure 6, a higher access locality leads to lower core-to-memory latency (assuming one cycle latency for each link) due to closer signal routing that minimizes latency through the 2D network and maximally exploit the 3D bandwidth.

Figure 6: Network simulation for varying spatial locality to illustrate the need for MuSIC: (a and b) target access memory((i,j) node) location for (a) higher ( $\sigma = 0.6$ ), (b) lower ( $\sigma = 1.6$ ) spatial locality; (c) Sensitivity of latency to the address locality and the memory latency (8x8 nodes).

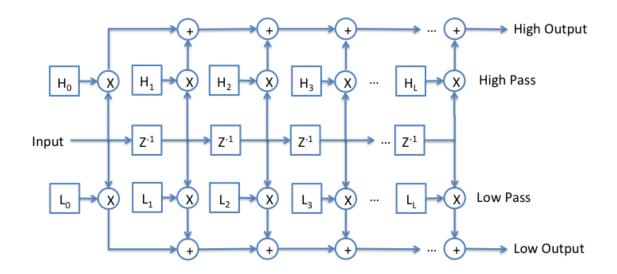

Figure 7: Block diagram of DWT convolution.

#### 2.2.2 Implementation of the Coding Algorithm

In this work, we implement the line-based 2D DWT scanning architecture with convolutionbased 1D DWT FIR filters [37]. First, let us consider the convolution-based DWT FIR filter as shown in Figure 7. Given that our FIR filters has a length L, a shift register of the length L-1 is needed for the input data. The input data is shifted into the register one at a time. Let us now consider that the maximum length of our FIR filter is L = 2S when the filter length is even, or L = 2S + 1 if the filter length is odd, where S is an arbitrary positive number. Then, the minimum length of input needed to perform the convolution is S if the filter length is even, or S + 1 if the filter length is odd. This is because symmetric extension is applied to the input data to create a 2S or 2S + 1 input data for the even or odd length FIR filters. Figure 7 also shows that the input data can be fed into both the high-pass filter (HPF) and low-pass filter (LPF) in parallel.

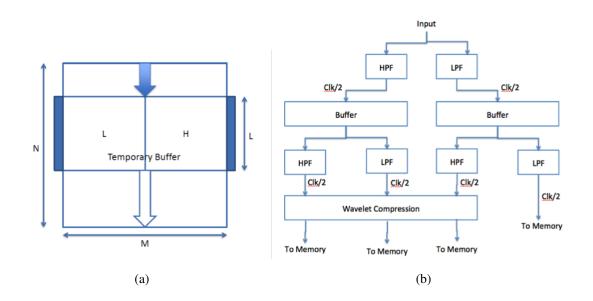

A 2D DWT is an extension of a 1D DWT. Considering a RAM based 2D DWT architecture, a temporary storage element is needed to store intermediate results. The conventional and simple way to perform 2D DWT is to first do row-wise 1D DWT filtering to all the rows, save the intermediate results in the temporary storage element, and then perform

Figure 8: Block diagram of memory access for direct implementation of 2D DWT.

column-wise 1D DWT filtering, as shown in Figure 8. Assuming an image of size N by M, a temporary storage element of size NxM is needed to store the intermediate results. These coefficients are fed in as inputs for the column-wise 1D DWT filtering. A more efficient method to perform a 2D DWT is the line-based method, shown in Figure 9a. We first start by doing the row-wise filtering. But then, the difference is the column-wise filtering starts

Figure 9: Efficient line based 2D discrete wavelet transform (2D-DWT). (a) Temporary buffer to contain the intermediate coefficients during the 2D transform. (b) A flow diagram of the 2D transform.

| Low Pass Decomposition Filter   | 0 | -1/8 | 1/4  | 3/4  | 1/4  | -1/8 |

|---------------------------------|---|------|------|------|------|------|

| High Pass Decomposition Filter  | 0 | -1/2 | 1    | -1/2 | 0    | 0    |

| Low Pass Reconstruction Filter  | 0 | 1/2  | 1    | 1/2  | 0    | 0    |

| High Pass Reconstruction Filter | 0 | -1/8 | -2/8 | 6/8  | -2/8 | -1/8 |

Table 1: Discrete Wavelet Transform Filter Pair

as soon as sufficient rows of the intermediate values are present. With line-based architecture, the size of temporary storage element is reduced to NL, where L is the length of the FIR filters. Normally the filter length (L) is significantly lower than the image length (M) itself. Once the temporary storage is filled up, the column-wise DWT is executed. After that, the next row of input data is taken in for another set of row-wise and column-wise filtering. In the case of a multilevel 2D DWT, the lowpass-lowpass (LL) sub-band, referred as the approximate coefficients, is used as the input for the next level of decomposition, however in this work we present a one-level 2D DWT. Figure 9b shows a flow diagram of the DWT. Table 1 shows the coefficients of the 5/3 LeGall filter pair used in this work [55].

# 2.3 System Description

The discussion in Section 2.2.1 shows that minimum latency in the memory-core stack can be achieved when each core only accesses the nearest memory port, and provides the reason for choosing the multi-segment image compression scheme. A conceptual diagram of the 3D-integrated image sensor with multi-segment compression is shown in Figure 10. The system consists of five tiers: 1) the photodiode tier; 2) the column circuitry tier; 3) the ADC and control logic tier; 4) the image buffer (image storage) tier; 5) the SPU tier. The tiers are connected vertically by through-silicon vias (TSVs). The imaging procedure consists of three stages: 1) sensing: the image is captured and converted into digital signal; 2) compression: the digital data is compressed using the discrete wavelet transform method

Figure 10: An illustration of the 3D-integrated multi-segment image compression system.

followed by threshold or/and huffman coding; 3) transmission: the compressed digital data is then transmitted to an off-chip module. This module can be a wireless transceiver. The next image is captured (sensed) only after the previous image is completely transmitted. The SPU and the image buffer is connected by a mesh type network topology with X-Y routing scheme. Detail explanation of the network is presented in Section 2.2.1. Essentially, the simulation framework can be divided into two main parts:

- 1. Architectural timing analysis the architectural performance of the compression algorithm is estimated by simulating the data patterns in the network nodes. The generated traffic pattern is discussed below.

- Power and performance analysis the power dissipation of the SPU, network router, and image buffer is extracted from a synthesized design, ORION [56], and CACTI [57], respectively, considering a 180nm CMOS process technology.

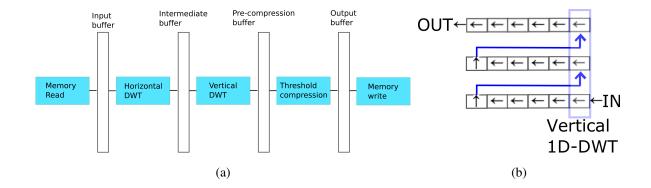

In generating the traffic pattern, we consider a pipelined line based architecture (Figure 11a) with a finite impulse response (FIR) filter of length 6 (L = 6) that fits with 5/3 LeGall filter pair. The DWT starts with a memory read operation to fetch input data from the frame memory (image buffer). The input data is then used to perform horizontal 1D-DWT, and

the result is stored in the intermediate buffer in the next clock cycle. The intermediate data is not immediately used for vertical 1D-DWT. Sufficient amount of intermediate data points need to be collected before the vertical 1D-DWT can be computed. Once the vertical DWT is computed, threshold based compression is performed only on the detailed coefficients (namely LH, HL, and HH sub-bands), before they are written back to the frame memory (image buffer). To generate the pattern, at the beginning, three consecutive memory-read operations are needed to prepare the first input set. After the third read operation, horizontal 1D-DWT calculation is performed to generate the first intermediate coefficient. The generated coefficient is then stored in the temporary storage buffer for column filtering. The temporary storage buffer is implemented as two separate buffer chains of moving registers, one chain for L sub-bands, other for H sub-bands. Figure 11b illustrates data movement in one of the buffers chain. Data from horizontal 1D-DWT gets into the buffer chain from the bottom right corner, and move to the next neighboring register every clock cycle. Six registers of the intermediate buffer are connected to the input ports of the vertical 1D-DWT filters, as shown in Figure 11b. Vertical 1D-DWT calculation starts as soon as three coefficients are available to the vertical filter. The output of the vertical calculation is then stored back to the memory. If we assume a 512X512 image, that means there is 512X3 memory read operations before the first memory write operation starts. After this point, the traffic

Figure 11: DWT architectural consideration. (a) SPU pipeline stage. (b) Registers for the intermediate buffer.

pattern becomes an alternating write and read access up to the end of an image frame. The remaining part of the pattern consists of write accesses until the last pixel is calculated.

# 2.4 Analysis for Threshold Coding

The first part of the analysis focuses on the performance of the multi-segment image compression with threshold coding algorithm. The key benefit of the threshold coding is that the algorithm is relatively simpler to implement compare to the Huffman coding, thus requiring a smaller hardware and die area.

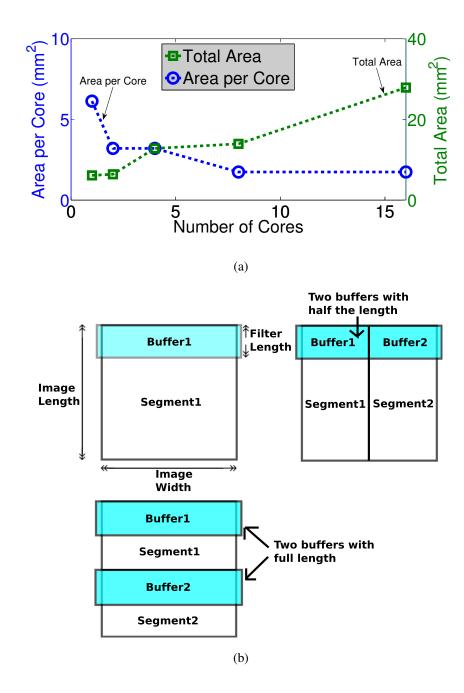

### 2.4.1 Die Area of the Multi-Segment Image Compression

Figure 12a illustrates the increase in die area of the signal processing unit (SPU) with increasing number of cores for the DWT with Threshold coding scheme. The die area of the signal processing unit increases with increasing number of cores (image segments). However, the increase in the die area is not linearly dependent with the number of segments. Majority of the signal processing unit core die area is occupied by a set of registers to store intermediate data during the wavelet transform computation. The size of the register file is determined by the width, but not by the length, of the image (Figure 12b). Therefore, the die area of the signal processing unit depends on the method in which the image is divided into segments. In this research, the image is first divided along the image length direction to create the 2-cores system, and then it is divided along the image length direction to create the 4-cores system. This alternating division method is also used to create the 8-, and 16-cores system.

# 2.4.2 Data Volume Overhead and Image Quality of the Multi-Segment Image Compression

Dividing the image into many segments reduces the compression ratio. As the number of segments increases, the image data associated with the borders of the image segments also increases. Thus, output data volume expands as a result of the wavelet transform calculation. Figure 13 shows the expansion of output data packets with increasing number of segments for the threshold coding. The black solid line represents the average data

Figure 12: Effect of increasing number of segments to the SPU die area. (a) Area versus number of cores in Threshold coding scheme. (b) Intermediate buffer size expansion with an increase in number of segments along the x-direction (top right) and y-direction (bottom left).

Figure 13: Effect of increasing number of segments to the SPU data volume for threshold coding.

volume for the 80 test images.

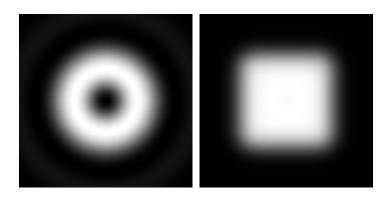

To test for effect of multi-segment image compression to the image quality, a test image (Figure 14a and Figure 14b) is generated in different sizes: 512X512, 256X256, 128X128 [58]. The image quality is measured using the peak signal to noise ratio (PSNR), in which a low distortion level yields a high PSNR value [59]. Figure 14c - 14e show the rising distortion level with increasing number of segments. This increased distortions come from limitation in the convolution of the image data along the edges of a segment, and the increased amount of edges with increasing number of segments. On the other hand, PSNR reduces as the image size is reduced because the edges to non-edges ratio increases.

## 2.4.3 Performance and Power Analysis of the Multi-Segment Image Compression

It is possible to integrate the image buffer and the SPU in a 2D fashion for multi-segment compression, although the 3D-integrated system (Figure 15a) yields better performance. In the 2D-integrated system the image buffer is stacked vertically with the ADCs, the column

Figure 14: Effect of multi-segment compression to the image quality. (a) Circle test image.(b) Square test image. (c) Image degradation of the circle test image introduced by MuSIC.(d) After compression circle image compressed with 64 cores. (e) After compression square image compressed with 64 cores.

Figure 15: Effect of increasing number of segments to the architectural performance in 2D- and 3D-integration. (a) 3D-integration of image buffer and SPU. (b) 2D-integration of image buffer and SPU. (c) Compression time versus number of cores.

Figure 16: System performance of the image compression system in 2D- and 3Dintegration, considering variations in wireless channel condition, SPU clock speed, and number of SPU cores. (a) System in 2D-Integration. (b) System in 3D-Integration.

circuitry, and the photodiodes. However, the SPU is placed horizontally next to the image buffer, thus limiting the number of access path between the SPU and the image buffer (Figure 15b). Figure 15c demonstrates how 3D-integration of multi-segment is more effective than 2D-integration. As the number of segments increases, architectural compression time reduces. However, reduction in the compression time for the 2D-integration is not as high as in the 3D-integration, due to lateral traffic movement in the network router in the 2D-integration. This lateral traffic becomes more congested with increasing number of segments, and may eventually penalize the benefit of the multi-segment compression. The chart in Figure 15c shows that the 2D-integration of a 16-cores system performs worse than the 8-cores system.

The performance of the image sensor system (i.e. how many images is sensed and compressed per second) is governed by the total time required to capture, compress, and transmit the image, as shown by the following formula:

$$f_{image} = \frac{1}{t_{total}} = \frac{1}{t_{capture} + t_{compress} + t_{transmit}}$$

(1)

Figure 17: Effect of varying channel conditions to the SPU configurations and power dissipation. (a) SPU configurations versus channel bitrate. (b) SPU power versus channel bitrate.

The analysis framework in this chapter assumes a wireless sensor node that captures and compresses a constant number of frames per second (image throughput). In a wireless sensor network, the transmit time depends on the available bandwidth and the noise level of the wireless channel. To continuously meet the performance target (image throughput target) under varying channel condition, the SPU clock speed needs to remodulated to account for the degrading/improving wireless channel condition. The SPU clock speed can be controlled by dynamically changing the supply voltage. Figure 16 shows the minimum system clock speed that satisfies the target image throughput assuming a performance target (image throughput target) of 24 images/sec for the 2D- and the 3D-integrated system under varying wireless channel condition. The plot demonstrates that by moving to the 3D-integration of the system and increasing the number of core the performance target can be satisfied with reduced system clock speed, which leads to a potential reduction in power dissipation. Figure 16 also shows that as the wireless channel bitrate deteriorates, the SPU clock speed needs to be boost up to compensate for the slow transmit time. The power dissipation of the system is related to the number of cores and clock speed of the SPU. The optimum core configuration (number of cores and clock speed) can be determined through a design space exploration method across the varying channel condition. The goal is to pick the number of cores and clock speed that leads to the lowest system power on a given channel bitrate. Figure 17a indicates that the least number of cores or the lowest SPU clock speed does not always guarantee lowest power dissipation in meeting the performance target. Figure 17b illustrates the power dissipation for the optimally configured system for both 2D- and 3D-integration. If the channel condition degrades, the system has to spend more power to keep performance up. In addition, the multi-segment image compression is more effective in 3D-integration than in 2D-integration.

### 2.4.4 Multiple Clock Domain Approach

In the case where the SPU power accounts for the majority of the system power, minimizing the SPU clock speed may reduce the overall power dissipation. Since the multi-core

\*SPU – Signal Processing Unit

Figure 18: Multi clock domain scheme.

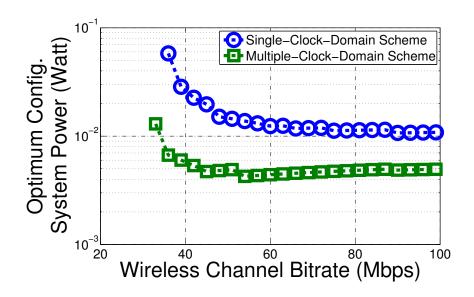

Figure 19: Comparison in the SPU power dissipation between the multi-clock-domain scheme and the single-clock-domain scheme.

SPU and the image buffer is connected by a router network, read and write access takes multiple cycles to complete. The SPU spends multiple cycles without useful load, thus reducing hardware utilization. To reduce the number of idle cycles in the SPU, the SPU clock domain can be separated from the join buffer-network clock domain such that the read and write access is completed within one clock cycle for the SPU 18. In applications such as the wavelet based compression, the read and write access pattern is fix and predictable. Therefore it is possible to estimate the wait time for each read and write access request, and determine a clock ratio between the SPU and the network. A discussion on how to estimate the wait time and clock ratio can be found in [60]. Figure 19 illustrates the potential power reduction that can be achieved from the clock separation. In this experiment, the 3D-integrated system assumes optimal core configurations across varying channel condition with 24 images/sec performance target. By implementing the multiple-clock-domain scheme, the SPU clock speed is reduced to one sixth with the cost of a slight increase in the buffer-network clock speed.

# 2.5 Analysis for Huffman Coding

In this section, the application of the Huffman coding to the MuSIC engine is discussed and compared with the threshold coding. The Huffman coding is a lossless compression, thus the original image can be perfectly reconstructed. However, in practice, minor distortions are introduced during the quantization stage. Several architectural implementations of the Huffman coding for the MuSIC platform are discussed, and their respective impacts towards the die area, data volume, performance, and power are compared.

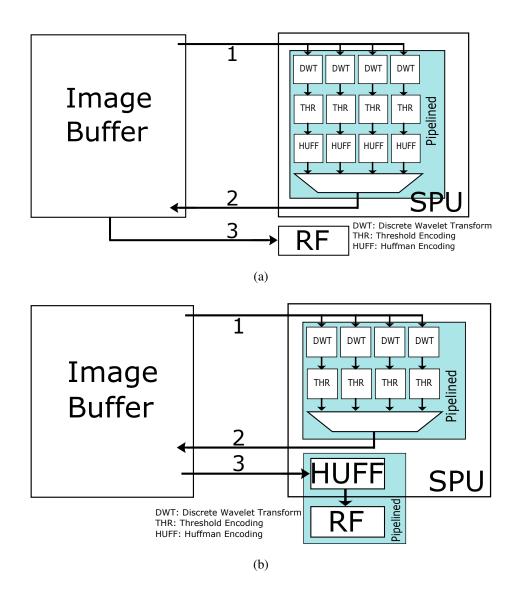

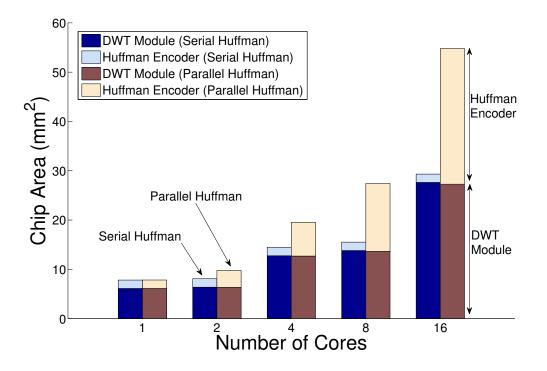

## 2.5.1 System Description of the Huffman Coding