# EXPLOITING INTRINSIC FLASH PROPERTIES TO ENHANCE MODERN STORAGE SYSTEMS

A Dissertation

Presented to

The Academic Faculty

By

Jian Huang

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Computer Science

Georgia Institute of Technology

August 2017

# EXPLOITING INTRINSIC FLASH PROPERTIES TO ENHANCE MODERN STORAGE SYSTEMS

# Approved by:

Dr. Moinuddin K. Qureshi, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Umakishore Ramachandran School of Computer Science Georgia Institute of Technology

Dr. Taesoo Kim School of Computer Science Georgia Institute of Technology Dr. Steven Swanson School of Computer Science and Engineering University of California, San Diego

Dr. James Mickens School of Computer Science Harvard University

Dr. Anirudh Badam Systems Research Group Microsoft Research, Redmond

Date Approved: July 20, 2017

Dedicated to my parents, sister, and wife for their infinite love, encouragement, and support

#### **ACKNOWLEDGEMENTS**

I would like to express my deepest gratitude to my thesis advisor, Moinuddin K. Qureshi, for his continuous support, guidance, and patience. He always inspires me to be a better researcher in many ways. I will remember many of our discussions on research in his office or the Starbucks Cafe in Clough Commons at Georgia Tech. All these bits and pieces make up a precious part of the memory of my Ph.D. life. His principles and dedication will have a great influence on me.

I owe an immeasurable debt to my another advisor, Karsten Schwan, for his kindness and mentorship. I really appreciate the opportunity to work with him to start a new journey of my Ph.D. study. His helpful nature and smile are an endless source of energy to keep me going forward. We all miss you, Karsten.

I would like to express my sincere gratitude to my mentor Anirudh Badam for his mentorship and friendship. This thesis would not have been possible without his gracious advice and encouragement. I am thankful for the opportunities to work with him at Microsoft Research and enable me to see the beauty of systems research. And most importantly, we made a friendship that would last a lifetime. I would also like to thank my other research mentors Ranveer Chandra, Ed Nightingale, Laura Caulfield, Suman Nath, Sudipta Sengupta, and Bikash Sharma at Microsoft Research for their guidance and support. The research projects we have done were always full of adventure and expectations, which made me have many wonderful summers in Seattle.

Special thanks to my recent collaborator Peng Liu for his mentorship. Peng was always available for discussions and gave me useful advice on my career development. I would also like to thank Xuechen Zhang, Nitin Agrawal, Dawei Li, Xiaolong Wang, Xiangyong Ouyang, Hao Wang, Harry Xu, Xingyu Xin, and Feng Qin for their discussions, suggestions, and feedback on my research.

I would like to thank Umakishore Ramachandran, Steven Swanson, Taesoo Kim, and

James Mickens for their time to serve on my thesis committee and their valuable feedback on my thesis proposal and the final dissertation.

Thank you to the group members of the memory systems lab, including Chia-Chen Chou, Vinson Young, Swamit Tannu, Gururaj Saileshwar, Prashant Nair, and Mohammad Arjomand. I am so proud to be part of such a talented, fun and motivated team.

Thanks also goes to my CERCS office-mates, especially Alexander Merritt, Yanwei Zhang, Chao Chen, Anshuman Goswami, Chengwei Wang, and Fang Zheng. They are always available for discussions and help. I would also like to thank Ada Gavrilovska, Greg Eisenhauer, and Susie Y. McClain for keeping the CERCS lab running during the most difficult time to provide a stable and helpful environment for our studies.

I am especially grateful to my parents, sister, and wife for their infinite love, endless patience, and unconditional support. They always encourage me in all of my pursuits and inspire me to follow my heart. For years my parents have set personal examples to show the value of hard work for me. The efforts they put in educating my sister and me always motivate us to become better persons. My sister is much more than just a sister, her continuous support and encouragement empower me to pursue my dreams. Finally, I would like to thank my wife who has made my Ph.D. journey worthwhile. We look forward to starting a new chapter in our lives together.

# TABLE OF CONTENTS

| Dedicat   | <b>ion</b>                                          |

|-----------|-----------------------------------------------------|

| Acknov    | vledgments iv                                       |

| List of   | <b>Γables</b> vii                                   |

| List of l | F <b>igures</b>                                     |

| Summa     | <b>ry</b>                                           |

| Chapte    | r 1: Introduction                                   |

| 1.1       | The Problem                                         |

| 1.2       | Thesis Statement                                    |

| 1.3       | Contributions                                       |

| 1.4       | Dissertation Organization                           |

| Chapte    | r 2: Background and Related Work 6                  |

| 2.1       | Flash Memory: Background and Terminology 6          |

| 2.2       | Related Work in Improving Storage Isolation         |

| 2.3       | Related Work in Improving Storage Performance       |

| 2.4       | Related Work in Improving Storage Energy Efficiency |

| 2.5       | Related Work in Improving Storage Security          |

| Cha | ptei           | r 3: Fla     | shBlox: Hardware Isolated Virtual SSDs                 | 13 |  |  |  |  |  |  |

|-----|----------------|--------------|--------------------------------------------------------|----|--|--|--|--|--|--|

| -   | 3.1            | Introduction |                                                        |    |  |  |  |  |  |  |

| 2   | 3.2            | Motiva       | ntion                                                  | 15 |  |  |  |  |  |  |

|     |                | 3.2.1        | Hardware Isolation vs. Wear-Leveling                   | 16 |  |  |  |  |  |  |

|     |                | 3.2.2        | Leveraging Parallelism for Isolation                   | 18 |  |  |  |  |  |  |

| 3   | 3.3            | FlashB       | Blox Design                                            | 18 |  |  |  |  |  |  |

|     |                | 3.3.1        | Channel Isolated Virtual SSDs                          | 21 |  |  |  |  |  |  |

|     |                | 3.3.2        | Die Isolated Virtual SSDs                              | 25 |  |  |  |  |  |  |

|     |                | 3.3.3        | Software Isolated Virtual SSDs                         | 26 |  |  |  |  |  |  |

|     |                | 3.3.4        | Intra Channel/Die Wear-Leveling                        | 27 |  |  |  |  |  |  |

| 3   | 3.4            | FlashB       | Blox Implementation                                    | 28 |  |  |  |  |  |  |

| 3   | 3.5            | Results      | s and Analysis                                         | 29 |  |  |  |  |  |  |

|     |                | 3.5.1        | Hardware Isolation vs. Software Isolation              | 29 |  |  |  |  |  |  |

|     |                | 3.5.2        | Migration Overhead                                     | 30 |  |  |  |  |  |  |

|     |                | 3.5.3        | Migration Frequency Analysis                           | 31 |  |  |  |  |  |  |

| 3   | 3.6            | Summ         | ary                                                    | 32 |  |  |  |  |  |  |

| Cha | ptei           | r 4: Fla     | shMap: Unifying Indirection Layers Across System Stack | 33 |  |  |  |  |  |  |

|     | <b>4</b> .1    |              | action                                                 |    |  |  |  |  |  |  |

| 2   | 4.2            |              | ntion                                                  |    |  |  |  |  |  |  |

|     | - <del>-</del> | 4.2.1        | Overhead from Redundant Software                       |    |  |  |  |  |  |  |

|     |                | 4.2.2        | Challenges for Combining Indirection Layers            |    |  |  |  |  |  |  |

| ,   | 13             |              | Man Design                                             | 40 |  |  |  |  |  |  |

|     |                |              |                                                        |    |  |  |  |  |  |  |

|                       | 4.3.1                                                          | Preserving File System Permissions               | 41                                     |

|-----------------------|----------------------------------------------------------------|--------------------------------------------------|----------------------------------------|

|                       | 4.3.2                                                          | Preserving PTE Behavior                          | 43                                     |

|                       | 4.3.3                                                          | Preserving Memory Protection Behavior            | 44                                     |

|                       | 4.3.4                                                          | Preserving the FTL Properties                    | 45                                     |

| 4.4                   | FlashN                                                         | Map Implementation                               | 46                                     |

| 4.5                   | Result                                                         | s and Analysis                                   | 47                                     |

|                       | 4.5.1                                                          | Experimental Methodology                         | 47                                     |

|                       | 4.5.2                                                          | Benefits from Saving DRAM                        | 48                                     |

|                       | 4.5.3                                                          | Latency Benefits                                 | 50                                     |

|                       | 4.5.4                                                          | DRAM vs. SSD                                     | 52                                     |

| 4.6                   | Summ                                                           | ary                                              | 53                                     |

|                       |                                                                |                                                  |                                        |

| Chapte                | r 5: We                                                        | earDrive: Energy-Efficient Storage for Wearables | 55                                     |

| C <b>hapte</b><br>5.1 |                                                                | earDrive: Energy-Efficient Storage for Wearables |                                        |

|                       | Introd                                                         |                                                  | 55                                     |

| 5.1                   | Introd                                                         | uction                                           | 55<br>58                               |

| 5.1                   | Introde<br>Motiva<br>5.2.1                                     | uction                                           | 55<br>58<br>58                         |

| 5.1                   | Introde<br>Motiva<br>5.2.1                                     | uction                                           | 55<br>58<br>58<br>58                   |

| 5.1                   | Introde  Motiva  5.2.1  5.2.2                                  | uction                                           | 55<br>58<br>58<br>58                   |

| 5.1                   | Introde<br>Motiva<br>5.2.1<br>5.2.2<br>5.2.3                   | uction                                           | 555<br>588<br>588<br>599<br>599        |

| 5.1                   | Introde<br>Motiva<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5 | uction                                           | 555<br>588<br>588<br>599<br>599        |

| 5.1<br>5.2            | Introde<br>Motiva<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5 | uction                                           | 555<br>588<br>588<br>599<br>600<br>600 |

|    |        | 5.3.3    | KV-store Design                                       | 63 |

|----|--------|----------|-------------------------------------------------------|----|

|    |        | 5.3.4    | Communication                                         | 67 |

|    | 5.4    | WearD    | Prive Implementation                                  | 69 |

|    | 5.5    | Experi   | mental Methodology                                    | 70 |

|    |        | 5.5.1    | WearBench                                             | 70 |

|    |        | 5.5.2    | Experimental Setup                                    | 71 |

|    | 5.6    | Result   | s and Analysis                                        | 73 |

|    |        | 5.6.1    | Local Memory vs. Local Flash                          | 73 |

|    |        | 5.6.2    | Passive Sensor Data Aggregation                       | 73 |

|    |        | 5.6.3    | Extended Display Workload                             | 74 |

|    |        | 5.6.4    | Impact on Smart-phone                                 | 76 |

|    | 5.7    | Summ     | ary                                                   | 78 |

| Cł | naptei | r 6: Fla | shGuard: Hardware-Assisted Defense Against Ransomware | 80 |

|    | 6.1    | Introdu  | action                                                | 81 |

|    | 6.2    | Ranson   | mware Study                                           | 83 |

|    |        | 6.2.1    | Study Methodology                                     | 84 |

|    |        | 6.2.2    | Our Findings                                          | 86 |

|    | 6.3    | Threat   | Model                                                 | 87 |

|    | 6.4    | FlashC   | Guard Design                                          | 88 |

|    |        | 6.4.1    | Approach overview                                     | 88 |

|    |        | 6.4.2    | Ransom-Aware FTL                                      | 89 |

|    |        | 6.4.3    | Read and Write Operations in RFTL                     | 92 |

|         | 6.4.4   | Garbage Collection in RFTL                      | 93  |

|---------|---------|-------------------------------------------------|-----|

|         | 6.4.5   | Data Recovery                                   | 97  |

|         | 6.4.6   | Metadata Recovery                               | 99  |

| 6.5     | FlashC  | Guard Implementation                            | 99  |

| 6.6     | Result  | s and Analysis                                  | 100 |

|         | 6.6.1   | Experimental Setup                              | 100 |

|         | 6.6.2   | Efficiency on Data Recovery                     | 102 |

|         | 6.6.3   | Impact on Storage Performance                   | 103 |

|         | 6.6.4   | Impact on SSD Lifetime                          | 104 |

| 6.7     | Securi  | ty Analysis and Discussion                      | 105 |

|         | 6.7.1   | Exploiting storage capacity                     | 105 |

|         | 6.7.2   | Timing attacks                                  | 106 |

|         | 6.7.3   | Secure deletion                                 | 106 |

| 6.8     | Summ    | ary                                             | 107 |

| Chapte  | r 7: Co | nclusions and Future Work                       | 108 |

| 7.1     | Conclu  | usions                                          | 108 |

| 7.2     | Future  | Work                                            | 109 |

|         | 7.2.1   | Achieving Predictable Storage Performance       | 109 |

|         | 7.2.2   | Unifying Management for Memory and Storage      | 110 |

|         | 7.2.3   | Improving Storage Security on Various Platforms | 110 |

| Doforon | 200     |                                                 | 111 |

| Vito 1 |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |

|--------|------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|

|        | Vita |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 1 |

# LIST OF TABLES

| 3.1 | Virtual SSD types supported in FlashBlox                                                                                                                                                                            | 19  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Monte Carlo simulation (10K runs) of SSD lifetime with randomly sampled workloads on the channels                                                                                                                   | 31  |

| 4.1 | FlashMap's Overhead                                                                                                                                                                                                 | 51  |

| 4.2 | Cost-effectiveness of FlashMap for 1 TB workload sizes, compared with the ideal large DRAM-only system.                                                                                                             | 52  |

| 5.1 | WearDrive API                                                                                                                                                                                                       | 69  |

| 5.2 | Workloads included in WearBench                                                                                                                                                                                     | 70  |

| 5.3 | Reference wearable device used for evaluation                                                                                                                                                                       | 71  |

| 5.4 | WearDrive saves wearable's battery by trading it with the phone's battery. The battery capacities of the wearable and phone used in the experiments are 300 mAh and 2000 mAh respectively                           | 77  |

| 6.1 | Ransomware families, their encryption time, and behaviors of deleting backup files (backup spoliation)                                                                                                              |     |

| 6.2 | File distribution in a normal user's computer                                                                                                                                                                       | 85  |

| 6.3 | A variety of real-world application workloads used for evaluating Flash-Guard. R: <i>Read</i> , W: <i>Write</i>                                                                                                     | 100 |

| 6.4 | The additional page movements (%) for retaining invalid pages in Flash-Guard over the time period from 2 to 20 days. For the workloads that do not incur additional page movements, they are not shown in the table | 104 |

# LIST OF FIGURES

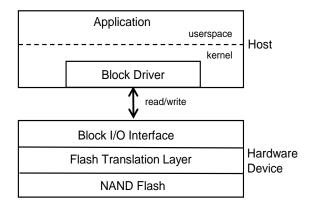

| 2.1 | The system architecture of using an SSD with block I/O interface                                                                                                                                                                                                                                                                      | 6  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

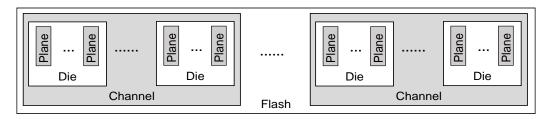

| 2.2 | The internal parallelism in an SSD                                                                                                                                                                                                                                                                                                    | 7  |

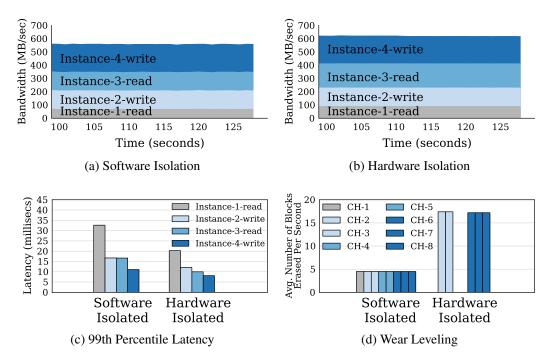

| 3.1 | Tenants sharing an SSD get better bandwidth (compare (a) vs. (b)) and tail latency as shown in (c) when using new hardware isolation. However, dedicating channels to tenants can lead to wear-imbalance between the various channels as shown in (d). A new design for addressing such a wear-imbalance is proposed                  | 17 |

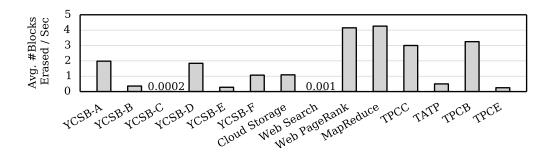

| 3.2 | The average rate at which flash blocks are erased for various workloads, including NoSQL, SQL, and batch processing workloads                                                                                                                                                                                                         | 18 |

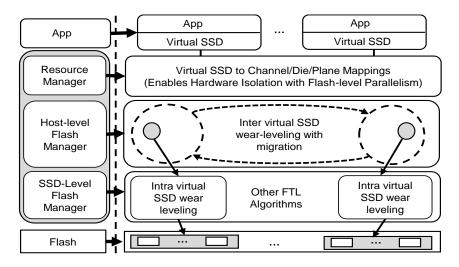

| 3.3 | The system architecture of FlashBlox                                                                                                                                                                                                                                                                                                  | 19 |

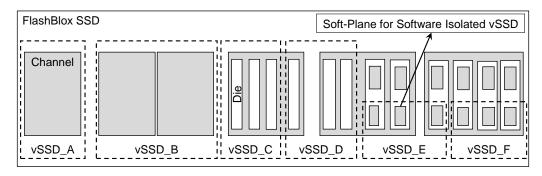

| 3.4 | A FlashBlox SSD: vSSD_A and B use one and two channels respectively. vSSD_C and D use three dies each. vSSD_E, and F use three soft-planes each.                                                                                                                                                                                      | 20 |

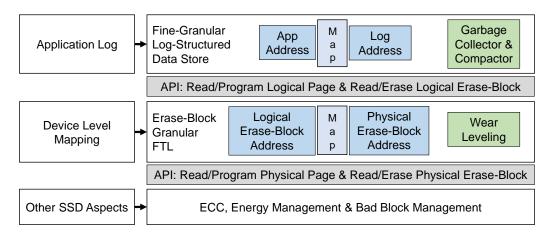

| 3.5 | Applications manage a fine-granular log-structured data store and align compaction units to erase-blocks in FlashBlox. A device level indirection layer is used to ensure all erase-blocks are aging at the same rate                                                                                                                 | 27 |

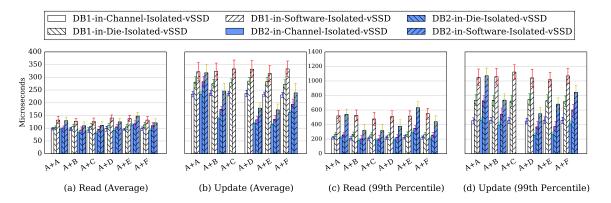

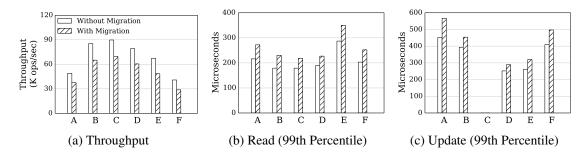

| 3.6 | The average and 99th percentile latencies of LevelDB+YCSB workloads running at various levels of storage isolation. Compared to die and software isolated vSSDs, channel isolated vSSD reduces the average latency by 1.2x and 1.4x respectively, and decreases the 99th percentile latency by 1.2 - 1.7x and 1.9 - 2.6x respectively | 30 |

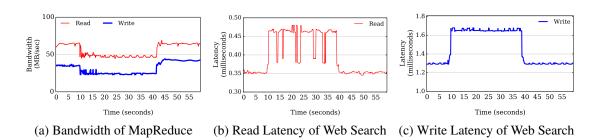

| 3.7 | The impact of a channel migration on workloads. LevelDB's throughput falls by 33.8%, its tail percentile of reads and updates increase by 22.1% and 18.7% respectively.                                                                                                                                                               | 30 |

| 3.8 | The overhead of migrating 1GB of data as MapReduce and web search are running on the channels involved. MapReduce's bandwidth falls by up to 36.7% while web search's latency increases by up to 34.2%                                           | 31 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

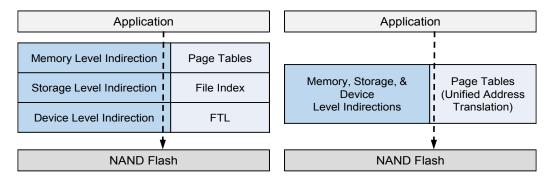

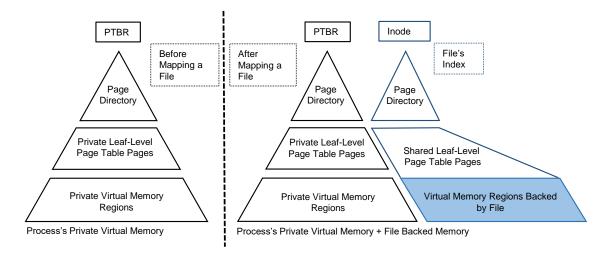

| 4.1 | Comparison of (a) conventional memory-mapped SSD-file's IO stack and (b) FlashMap that combines all the address translations for mapping files into page tables                                                                                  | 37 |

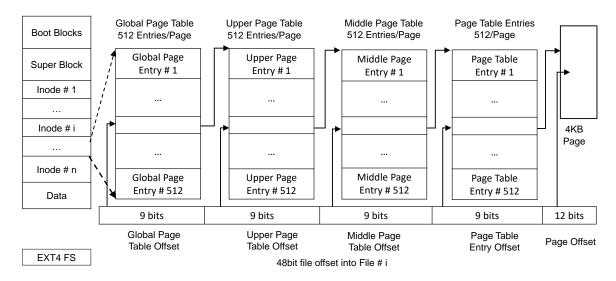

| 4.2 | FlashMap uses a page table design for indexing files                                                                                                                                                                                             | 40 |

| 4.3 | File brings leaf-level page tables with itself to a process that maps it. Higher-level page table pages are not shared, they are created on-demand for mapping the file                                                                          | 42 |

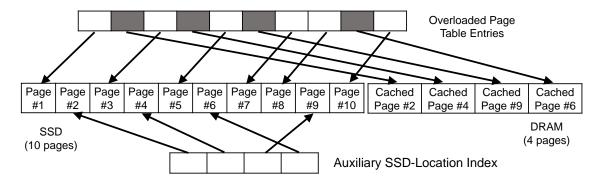

| 4.4 | Page table entries are overloaded to store both SSD and DRAM locations of pages. When a page table entry stores the DRAM location of a cached page, the corresponding auxiliary SSD-location entry remembers it's SSD-location                   | 43 |

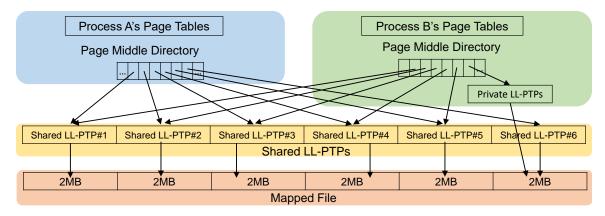

| 4.5 | Processes A and B map the same file. However, process B has custom memory protections for a small memory region with private leaf-level pagetable pages (LL-PTP)                                                                                 | 44 |

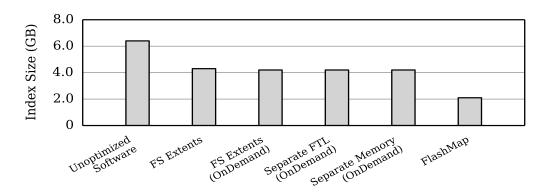

| 4.6 | Index size for 1 TB SSD                                                                                                                                                                                                                          | 48 |

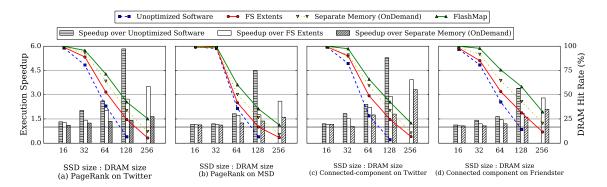

| 4.7 | Improvements for analytics on Twitter, Friendster and MSD dataset, with varied DRAM size. Compared to Separate Memory (OnDemand), FlashMap performs 1.15–1.64x better for PageRank, and up to 3.32x better for the connected component labeling. | 49 |

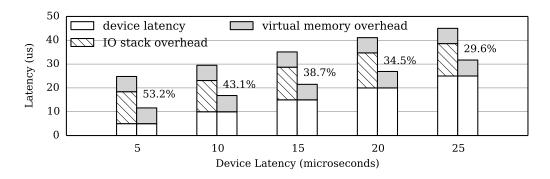

| 4.8 | For faster SSDs, FlashMap provides tangible improvements in the latency over Unoptimized Software.                                                                                                                                               | 50 |

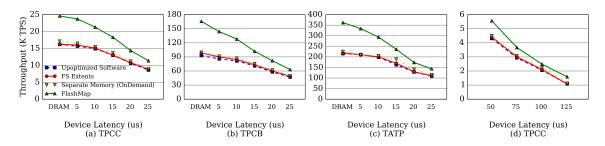

| 4.9 | For faster SSDs, FlashMap provides up to 1.78x improvements on throughput over Unoptimized Software with TPCC, TPCB and TATP benchmarks. As for Flash with 100 $\mu$ s device latency, FlashMap still performs 1.21x more TPS than others        | 50 |

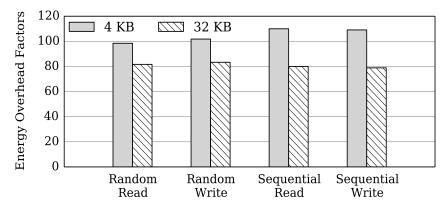

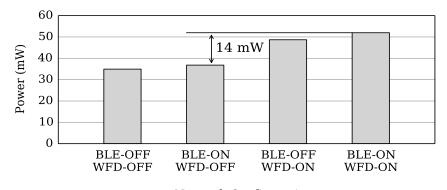

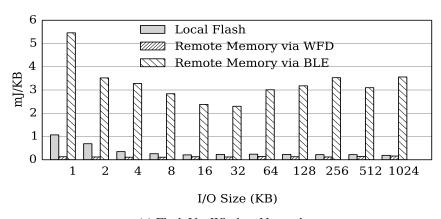

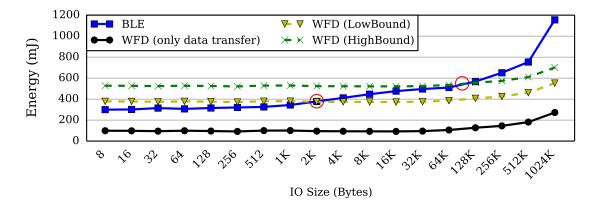

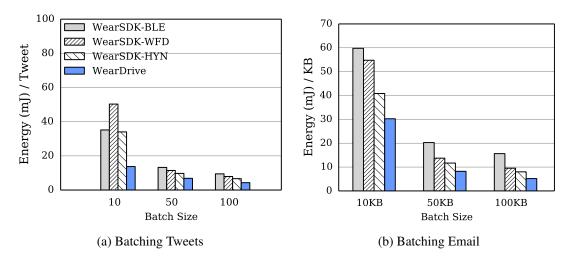

| 5.1 | Motivating scenarios for WearDrive: (a) Mobile storage stacks are energy-intensive because storage software consumes 80–110x more energy than flash. (b) To maintain a connection to the phone for the wearable, WiFi-Direct consumes 10–15mW extra power, while Bluetooth Low-Energy requires only 1–2mW. (c) In terms of energy consumption of the whole system when sequentially writing 32 MB data set with various I/O granularities, it is more energy efficient to write to remote phone's memory via WiFi-Direct than to write data locally to flash on the wearable | 57 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

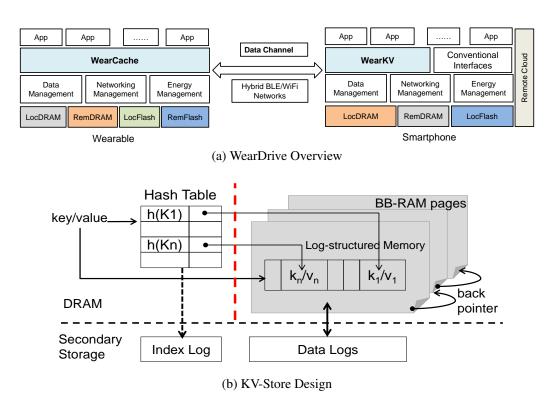

| 5.2 | (a) WearDrive expands wearable's memory and storage capacity by leveraging phone's capabilities. LocDRAM/RemDRAM represents local/remote DRAM, LocFlash/RemFlash are local/remote Flash. (b) BB-RAM pages are held in a linked list. The pages contain a sequential log of key-value pairs as they arrive. The hashtable stored in regular DRAM contains the index for the key-value store whose state can be efficiently recovered after failures                                                                                                                           | 61 |

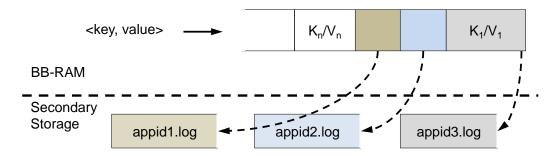

| 5.3 | WearDrive creates individual logs per application and per sensor to isolate on secondary storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66 |

| 5.4 | Energy consumption of data transfer via BLE and WFD. WFD is efficient if connection establishment, tail latency, and connection-teardown are not included                                                                                                                                                                                                                                                                                                                                                                                                                    | 68 |

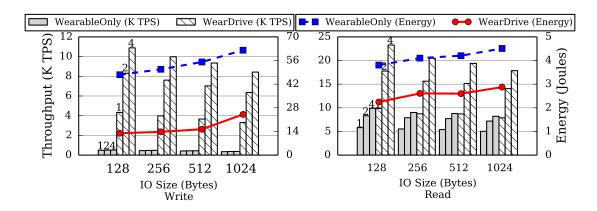

| 5.5 | Performance and energy comparison of WearableOnly and WearDrive with a varied number (1, 2, 4) of threads                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72 |

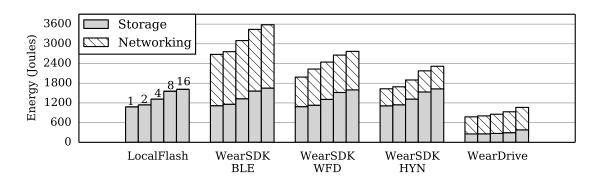

| 5.6 | Energy used by various storage systems with varied number (1–16) of sensors sampling values continuously at 1Hz for 24 hours. A typical smartwatch battery contains between 3000–6000 Joules of energy                                                                                                                                                                                                                                                                                                                                                                       | 72 |

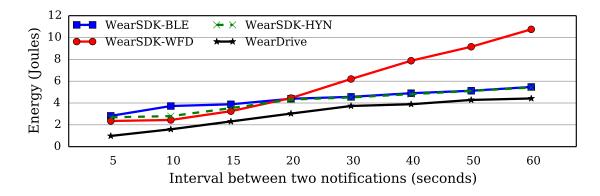

| 5.7 | Energy usage of receiving 10 notifications (10KB size) with the varied interval between notifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75 |

| 5.8 | Performance and energy usage of notification workload with different data size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76 |

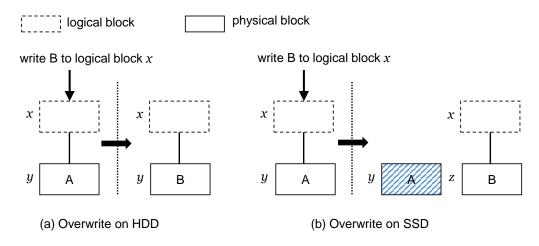

| 6.1 | The fundamental difference between HDD and SSD for an overwrite operation. When a logical block $x$ is overwritten, HDD will update the mapped physical block $y$ with the new data $B$ , while SSD will place the new data $B$ on a free block $z$ and garbage collect the block $y$ later                                                                                                                                                                                                                                                                                  | 89 |

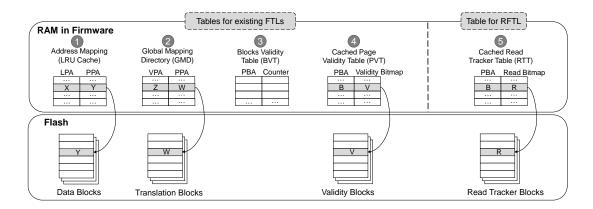

| 6.2  | Overview of RFTL in FlashGuard. RFTL slightly modifies the existing FTLs by adding a read tracker table (RTT) to track whether a page has been read. Cooperating with other tables, RTT helps RFTL track the pages that could be encrypted by ransomware. LPA: logical page address, PPA: physical page address, VPA: virtual page address, PBA: physical block address | 90  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

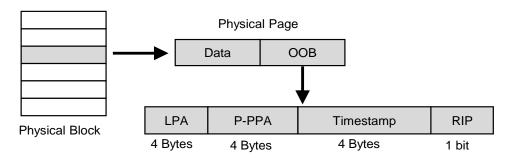

| 6.3  | The out-of-band (OOB) metadata in each physical page. It includes the LPA mapped to this physical page, the previous physical page address (P-PPA) mapped to the current LPA, the timestamp when the page is written, the retained invalid page (RIP) bit indicating whether this page should be retained if it becomes invalid                                         | 93  |

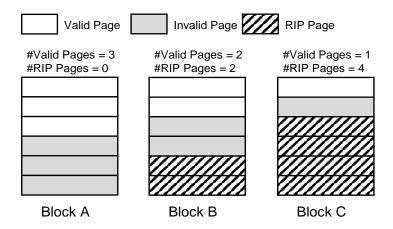

| 6.4  | An example of candidate block selection in state-of-the-art GC vs. RFTL's GC. Traditionally, block <i>C</i> is selected, as the number of the valid pages is the least. In RFTL, block <i>A</i> is selected, since RFTL counts the retained invalid pages (RIP) as valid pages                                                                                          | 94  |

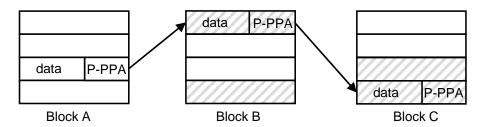

| 6.5  | FlashGuard restores all the overwritten pages by travelling back to their previous versions with the previous physical page address stored in each page's OOB metadata                                                                                                                                                                                                  | 98  |

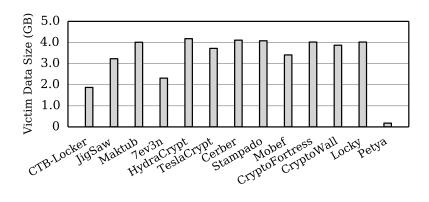

| 6.6  | The total size of the data encrypted by each ransomware family                                                                                                                                                                                                                                                                                                          | 101 |

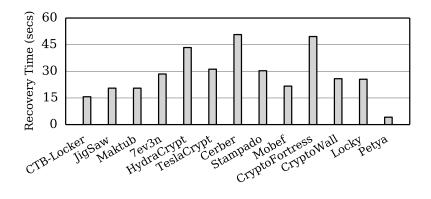

| 6.7  | The time of restoring the data that have been encrypted by ransomware                                                                                                                                                                                                                                                                                                   | 101 |

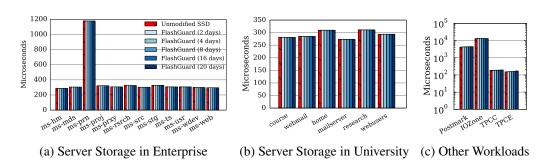

| 6.8  | The average latency of running real-world workloads with FlashGuard vs. Unmodified SSD. The time of holding retained invalid pages in FlashGuard ranges from 2 days to 20 days. FlashGuard's average latency is almost the same as that of the unmodified SSD for a variety of workloads                                                                                | 102 |

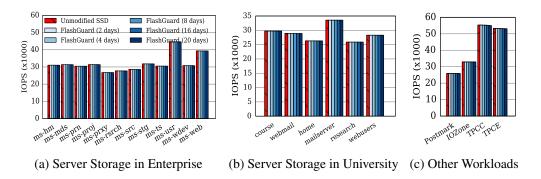

| 6.9  | The average throughput of running real-world workloads with FlashGuard vs. Unmodified SSD. FlashGuard has negligible impact on the I/O throughput for most of these workloads.                                                                                                                                                                                          | 103 |

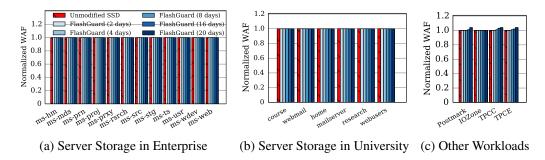

| 6.10 | The normalized write amplification factor (WAF) of FlashGuard compared to Unmodified SSD (lower is better).                                                                                                                                                                                                                                                             | 105 |

#### **SUMMARY**

The longstanding goals of storage system design have been to provide simple abstractions for applications to efficiently access data while ensuring the data durability and security on a hardware device. The traditional storage system, which was designed for slow hard disk drive with little parallelism, does not fit for the new storage technologies such as the faster flash memory with high internal parallelism. The gap between the storage system software and flash device causes both resource inefficiency and sub-optimal performance. This dissertation focuses on the rethinking of the storage system design for flash memory with a holistic approach from the system level to the device level and revisits several critical aspects of the storage system design including the storage performance, performance isolation, energy-efficiency, and data security.

The traditional storage system lacks full performance isolation between applications sharing the device because it does not make the software aware of the underlying flash properties and constraints. This dissertation proposes FlashBlox, a storage virtualization system that utilizes flash parallelism to provide hardware isolation between applications by assigning them on dedicated chips. FlashBlox reduces the tail latency of storage operations dramatically compared with the existing software-based isolation techniques while achieving uniform lifetime for the flash device.

As the underlying flash device latency is reduced significantly compared to the conventional hard disk drive, the storage software overhead has become the major bottleneck. This dissertation presents FlashMap, a holistic flash-based storage stack that combines memory, storage and device-level indirections into a unified layer. By combining these layers, FlashMap reduces critical-path latency for accessing data in the flash device and improves DRAM caching efficiency significantly for flash management.

The traditional storage software incurs energy-intensive storage operations due to the need for maintaining data durability and security for personal data, which has become a significant challenge for resource-constrained devices such as mobiles and wearables. This dissertation proposes WearDrive, a fast and energy-efficient storage system for wearables. WearDrive treats the battery-backed DRAM as non-volatile memory to store personal data and trades the connected phone's battery for the wearable's by performing large and energy-intensive tasks on the phone while performing small and energy-efficient tasks locally using battery-backed DRAM. WearDrive improves wearable's battery life significantly with negligible impact to the phone's battery life.

The storage software which has been developed for decades is still vulnerable to malware attacks. For example, the encryption ransomware which is a malicious software that stealthily encrypts user files and demands a ransom to provide access to these files. Prior solutions such as ransomware detection and data backups have been proposed to defend against encryption ransomware. Unfortunately, by the time the ransomware is detected, some files already undergo encryption and the user is still required to pay a ransom to access those files. Furthermore, ransomware variants can obtain kernel privilege to terminate or destroy these software-based defense systems. This dissertation presents FlashGuard, a ransomware-tolerant SSD which has a firmware-level recovery system that allows effective data recovery from encryption ransomware. FlashGuard leverages the intrinsic flash properties to defend against the encryption ransomware and adds minimal overhead to regular storage operations.

#### **CHAPTER 1**

#### INTRODUCTION

For decades, storage systems have been designed for block-based devices such as hard disk drive (HDD) that has little parallelism and long access latency. The widely used solid state disk (SSD) out-performs HDD by orders of magnitude, providing up to 5000x more IOPS, at 1% of the latency [1] without any physical seek operation. Such performance characteristics make SSD more similar to DRAM than to HDD. Moreover, SSD behaves intrinsically different from HDD. For example, typical SSDs have high internal parallelism by organizing their flash blocks into a hierarchy of multiple chips; they employ a flash translation layer (FTL) for out-of-place writes in order to mitigate the long erase latency of flash memories and also ensuring uniform wear for flash blocks. These unique properties make their storage management fundamentally different from that of HDDs.

#### 1.1 The Problem

To be compatible with the existing computer systems and simplify the software development, the storage systems that were originally made for HDD are employed for flash memory today, which causes a large gap between storage system software and hardware device. The gap not only causes resource inefficiency across the whole storage system stack but also results in the uncertainty for data security and durability, since the flash device is taken as a 'black box' under the conventional block abstraction. To fully exploit the hardware benefits, it is important to rethink the system design for flash memory with a holistic cross-layer approach.

The storage system is normally virtualized and shared by multiple applications for resource efficiency and these applications can interfere with each other. Therefore, a longstanding goal of storage virtualization has been to provide performance isolation between multiple applications sharing the device. Virtualizing SSDs, however, has traditionally been a challenge because of the fundamental tussle between resource isolation and the lifetime of the flash device. The SSDs aim to uniformly age all the regions of flash and this violates the isolation assumption in traditional storage systems. Although the storage system software has provided isolation mechanisms such as token bucket rate limiters and intelligent IO throttling [2, 3, 4], the FTL in SSDs, which is responsible for address translation and wear leveling for flash blocks, does not provide any isolation guarantee underneath the flash controller and this makes the storage performance highly unpredictable. This dissertation proposes utilizing flash parallelism to improve isolation between applications by running them on dedicated chips. It also proposes allowing the wear of different chips to diverge at fine time granularities in favor of performance isolation and adjusting the imbalance at a more coarse time granularity in a principled manner.

As flash device out-performs hard disk drive by orders of magnitude in terms of the device latency and throughput, the storage software has become the major bottleneck when accessing data on physical device. To improve the storage performance, an emerging approach to using SSDs treats them as a slower form of non-volatile memory. For example, NoSQL databases like MongoDB [5, 6], LMDB [7] which are widely deployed use SSDs via the existing memory-mapped file interface. Such an approach eases application development and automatically tiers SSD under the DRAM by the operating system (OS) manager. Using SSDs in this manner, unfortunately, is inefficient as there are three software layers with redundant functionalities between the application and flash device. The first of these, memory-level indirection, involves page table translations and sanity checks by the OS memory manager. The second of these, storage-level indirection, involves converting file offsets to blocks on the SSD and permission checks by the file system. The final one, device-level indirection, is for the FTL of the SSD. Redundant indirections and checks not only increase the latency of flash accesses but also affect performance by requiring precious DRAM space to cache indirection data across all the three layers. This dissertation

proposes a holistic SSD architecture that combines memory, storage and device-level indirections into a unified layer.

Beyond the performance issues, the storage software also incurs energy-intensive storage operations which consume up to 110x more energy compared to flash hardware for accessing data [8]. These energy overheads pose a big challenge for resource-constrained platforms such as wearables because the size and weight constraints on wearables limit their battery capacity and restrict them from providing rich functionality. The need for durable and secure storage for personal data further compounds this problem as these features incur energy-intensive operations. This dissertation presents WearDrive, a fast in-memory storage system for wearables by treating the battery-backed DRAM as non-volatile memory to avoid the energy-intensive storage operations and leveraging the low-power network connectivity on wearables to trade the resources on the phone for the wearable.

Finally, this dissertation also investigates the security aspect of the storage system stack. Although the storage system has been developed for decades, it is still vulnerable to malware attacks. For instance, the encryption ransomware which is a malicious software that stealthily encrypts user files and demands a ransom to provide access to these files. Several prior studies have developed systems to detect ransomware by monitoring the activities that typically occur during a ransomware attack. Unfortunately, by the time the ransomware is detected, some files already undergo encryption and the user is still required to pay a ransom to access those files. Furthermore, ransomware variants can obtain kernel privilege, which allows them to terminate software-based defense systems, such as anti-virus. While periodic backups have been explored as a means to mitigate ransomware, such backups incur storage overheads and are still vulnerable as ransomware can obtain kernel privilege to stop or destroy backups. Therefore, it is important to defend against ransomware without relying on software-based solutions and without incurring the storage overheads of backups. This dissertation proposes FlashGuard, a ransomware-tolerant SSD which has a firmware-level recovery system that allows quick and efficient data recovery from encryp-

tion ransomware without relying on explicit software-based solutions.

#### 1.2 Thesis Statement

Redesigning the storage system to exploit the intrinsic properties of flash memory can substantially improve the scalability, reliability, and security of flash-based storage systems.

#### 1.3 Contributions

This dissertation makes the following contributions:

- This dissertation proposes hardware isolation for flash-based storage system by utilizing the internal parallelism of flash memory and assigning applications on dedicated chips. It also presents a new wear-leveling scheme to manage the wear of flash chips at fine time granularities. Such a new design makes SSD wears uniformly while the tail latency of storage operations are reduced significantly compared to the traditional software-based isolation techniques.

- This dissertation presents a holistic SSD architecture for scalable SSD with larger capacity. It combines memory, storage, and device-level indirections into a unified layer while preserving the properties of each layer. Such an architecture significantly improves DRAM caching efficiency and reduces the latency of accessing a page on SSD. It also presents a way of unifying the new and emerging memory and storage technologies such as 3D XPoint memory.

- This dissertation proposes an energy-efficient storage system based on the battery-backed DRAM to avoid the energy-intensive storage operations to the flash device.

The DRAM on mobile and wearable devices can be treated as non-volatile memory for free because they are backed by non-removable batteries. Such a type of non-volatile memory opens a new field for persistent memory research.

• This dissertation also presents a ransomware-tolerant SSD which has the capability of defending against encryption ransomware by leveraging the intrinsic flash properties. Such an SSD can protect user data from encryption ransomware without relying on the software-based defense systems, while adding minimal overhead to regular storage operations and avoiding storage overhead of explicit data backups.

# 1.4 Dissertation Organization

The rest of the dissertation is organized as follows. Related work is discussed in Chapter 2. Chapter 3 describes the hardware isolation for multi-tenant applications. Chapter 4 discusses the unified address translation for memory-mapped SSDs. The energy-efficient storage system for wearables is presented in Chapter 5. Chapter 6 presents the ransomware-tolerant SSD. Finally, Chapter 7 summarizes the dissertation and discusses the directions of future work.

#### **CHAPTER 2**

#### BACKGROUND AND RELATED WORK

As the replacement to conventional persistent storage devices – hard disk drives (HDDs), Solid-State Drives (SSDs) have been widely used on many kinds of computing platforms, because they provide orders of magnitude better performance than HDDs while their cost is fast approaching to that of HDDs [9, 10, 11, 12]. This chapter describes the technical background of SSDs. Related work for the specific problems in the storage system stack will be further discussed in the corresponding chapter.

Figure 2.1: The system architecture of using an SSD with block I/O interface.

## 2.1 Flash Memory: Background and Terminology

Same as conventional HDDs, a commodity SSD employs a block interface to encapsulate the idiosyncrasies of flash devices as shown in Figure 2.1. As such, it gives upper-level software systems (such as file systems) an impression that both SSD and HDD perform storage operations in the same manner. At the hardware level, however, an SSD is fundamentally different from HDD.

Given an SSD, each physical page can be written only after it is erased. Unfortunately, erase operation can be performed only at block (which has multiple pages) granularity and

Figure 2.2: The internal parallelism in an SSD.

such operations are time-consuming. Therefore, SSDs issue the writes to free pages which have been erased in advance (i.e., out-of-place write) rather than waiting for the expensive erase operation for every write, and garbage collection (GC) will be executed later to clean the stale data on SSDs. Moreover, each flash block has limited endurance: it is rated only for a few thousand erase operations, therefore it is important for the blocks to age uniformly. SSDs employ both out-of-place write and GC to overcome the shortcomings of SSDs and maintain indirections in the Flash Translation Layer (FTL) for indexing the virtual-to-physical address mapping.

Typical SSDs organize their flash array into a hierarchy of channels, dies and planes [13, 14]. As shown in Figure 2.2, each SSD has multiple channels, each channel has multiple dies, and each die has multiple planes. The number of channels, dies and planes varies by vendor and generation. Typically, there are 2 - 4 planes per die, 4 - 8 dies per channel, and 8 - 32 channels per drive.

Channels, which share only the resources common to the whole SSD, provide the strongest isolation. Dies execute their commands with complete independence, but they must share a bus with other dies on the same channel. Planes' isolation is limited – the controller may isolate data to different planes, but operations on these data must either happen at different times or to the same address on each plane in a die [15].

### 2.2 Related Work in Improving Storage Isolation

SSDs have become indispensable for large-scale cloud services as their cost is fast approaching to that of HDDs. The rapidly shrinking process technology has allowed SSDs

to boost their bandwidth and capacity by increasing the number of chips. However, the limitations of SSDs' management algorithms have hindered these parallelism trends from efficiently supporting multiple tenants on the same SSD.

Previous work had proposed novel techniques to help application tenants place their data such that underlying flash pages are allocated from separate blocks. This helps improve performance by reducing the write amplification factor (WAF) [16]. Lack of block sharing has the desirable side effect of clumping garbage into fewer blocks, leading to more efficient garbage collection (GC), thereby reducing tail latency of SSDs [17, 18, 19, 20].

However, significant interference still exists between tenants because when data is striped, every tenant uses every channel, die and plane for storing data and the storage operations of one tenant can delay other tenants. Software isolation techniques [21, 22, 23] split the SSD's resources fairly. However, they cannot maximally utilize the flash parallelism when resource contention exists at a layer below because of the forced sharing of independent resources such as channels, dies, and planes.

New SSD designs, such as open-channel SSDs that explicitly expose channels, dies and planes to the operating system [24, 25, 26], can help tenants avoid some of these pitfalls by using dedicated channels. However, the wear imbalance problem between channels that ensues from different tenants writing at different rates remains unsolved.

### 2.3 Related Work in Improving Storage Performance

To further improve the performance of storage operations against SSDs, an emerging approach to using SSDs treats them as a slower form of non-volatile memory. For example, NoSQL databases like MongoDB [5, 6], LMDB [7] (backend for OpenLDAP) and others [27, 28, 29] which are widely deployed [30] use SSDs via a memory-mapped file interface. There are three advantages to this approach. First, the virtual memory interface eases development. For example, MongoDB uses TCMalloc [31] to manage SSD-file backed memory to create data structures like its B-tree index, and for using the Boost template li-

brary. Second, SSDs are automatically tiered under DRAM by the OS's memory manager. Finally, memory that is backed by a file enables durability for data. Such hybrid memory systems have also been proposed in the academic community [32, 33, 34, 35, 36].

However, these systems do not present optimizations for reducing the address translation overhead. Nameless writes [37] and DFS [38] combine the FTL with the file system's index. But, when mapping a file that uses nameless writes or DFS into virtual memory, page tables are created separately on top which increases the address translation and other software overhead.

DFTL [39] proposes caching only the "hot" mappings in memory while other mappings can be stored on the SSD. While such techniques reduce the space requirement of RAM at the FTL, they do not reduce the indirection overheads in higher software layers.

# 2.4 Related Work in Improving Storage Energy Efficiency

Beyond the storage performance of flash memories, the energy efficiency of storage operations is also a major concern of system design (especially for resource-constrained platforms such as mobiles and wearables). Kim et al. [40] provided the evidence that slow flash technologies such as SD and eMMC are the primary performance bottleneck for several classes of mobile applications. Li et al. [8] studied the energy overhead of mobile storage systems and found that the mobile software stack consumes more power than storage hardware. These findings motivate the research on the energy efficiency of storage systems in this dissertation, as these overheads become more prominent on wearables where the battery is more constrained than on phones.

Recent optimizations to mobile storage [41, 42] address some of the performance problems, but flash is still 10,000x slower compared to DRAM. Emerging non-volatile memory (NVM) technologies like PCM [43, 44, 45] are not yet available in the market. Battery-backed RAM [46, 47, 48] is viable because batteries, DRAM, and flash are pervasive in mobile systems. Luo et al. [46] proposed QuasiNVRAM that is a dedicated, known, con-

tiguous region of physical memory to provide performance benefits for phone applications that use SQLite on Android.

Rio [49], BlueFS [50], EnsemBlue [51] Simba [52], Segank [53], Bayou [54] and PersonalRAID [55] are distributed file system techniques to share personal data efficiently across mobile consumer electronic devices. For wearable devices, their workload characteristics are different. The wearable workloads like extended-display and sensor data analysis focus on the newest data. A quick and energy-efficient mechanism can be exploited to span data and computation across the wearable and the phone.

## 2.5 Related Work in Improving Storage Security

To ensure the data reliability and security in modern storage systems, a large number of backup systems have been proposed [56, 57, 58]. The ones that have been commonly adopted on Unix systems are dump and tar utilities. They both support full and incremental backup strategies [56]. On Microsoft Windows system, the most popular backup system is Volume Shadow Copy Service that archives user data on local and external volumes in an incremental manner [57]. Another line of work capable of achieving data recovery are log-structured file systems [59] and journaling file systems [60]. They both maintain data updates in persistent logs. Once data loss or inconsistency occurs, they can recover the data back to previous states by rolling back the logs.

Apart from the backup systems integrated into OSes, other well-developed backup systems include the IBM Tivoli Storage Manager [58] that performs selective, incremental backup in conjunction with deduplication, and those cloud based storage systems [61] that synchronize file updates and creation with the backup storage running on the cloud.

As a defense mechanism, however, none of them is sufficient and proper. To avoid loss of files newly updated or created, they have to perform backup frequently. From the perspective of efficiency, this is particularly time-consuming. Since malware has already run with the kernel privilege, the backup systems proposed can be easily disabled or circum-

vented. For example, a backup process that synchronizes user files with a cloud storage can be terminated by ransomware with the kernel privilege.

Looking beyond file backups, researchers proposed to integrate proactive defense mechanisms into the existing software systems recently. For example, ShieldFS [62] monitors the low-level file access activities to detect ransomware and implements a protection layer with the copy-on-write mechanism to recover data. PayBreak [63] hooks crypto functions in the standard libraries to identify the invocations from ransomware and logs the encryption key for future data decryption. Similar to the attacks against file backups, ransomware can easily undermine these mechanisms by disabling them with kernel privilege or obfuscating the execution of its critical functions.

#### **CHAPTER 3**

#### FLASHBLOX: HARDWARE ISOLATED VIRTUAL SSDS

A longstanding goal of storage virtualization has been to provide performance isolation between multiple tenants sharing the device. Virtualizing SSDs, however, has traditionally been a challenge because of the fundamental tussle between resource isolation and the lifetime of the device – existing SSDs aim to uniformly age all the regions of flash and this hurts performance isolation.

We propose utilizing flash parallelism to improve isolation between virtual SSDs by running them on dedicated channels and dies. Furthermore, we offer a complete solution by also managing the wear. We propose allowing the wear of different channels and dies to diverge at fine time granularities in favor of isolation and adjusting that imbalance at a coarse time granularity in a principled manner. Our experiments show that the new SSD wears uniformly while the 99th percentile latencies of storage operations in a variety of multi-tenant settings are reduced by up to 3.1x compared to software isolated virtual SSDs.

## 3.1 Introduction

SSDs have become indispensable for large-scale cloud services as their cost is fast approaching to that of HDDs. They outperform HDDs by orders of magnitude, providing up to 5,000x more IOPS, at 1% of the latency [64]. The rapidly shrinking process technology has allowed SSDs to boost their bandwidth and capacity by increasing the number of chips. However, the limitations of SSDs' management algorithms have hindered these parallelism trends from efficiently supporting multiple tenants on the same SSD.

The tail latency of SSDs in multi-tenant settings is one such limitation. Cloud storage systems have started collocating multiple tenants on the same SSDs [65, 66, 67] which further exacerbates the already well-known tail latency problem of SSDs [17, 68, 69, 70].

The cause of tail latency is the set of complex flash management algorithms in the SSD's controller, called the Flash Translation Layer (FTL). The fundamental goals of these algorithms are decades-old and were meant for an age when SSDs had limited capacity and little parallelism. The goals were meant to hide the idiosyncrasies of flash behind a layer of indirection and expose a block interface. These algorithms, however, conflate wear leveling (to address flash's limited lifetime) and resource utilization (to exploit parallelism) which increases interference between tenants sharing an SSD.

While application-level flash-awareness [38, 71, 72, 73, 74] improves throughput by efficiently leveraging the device level parallelism, these optimizations do not directly help reduce the interference between multiple tenants sharing an SSD. These tenants cannot effectively leverage flash parallelism for isolation even when they are individually flash-friendly because FTLs hide the parallelism. Newer SSD interfaces [25, 26] that propose exposing raw parallelism directly to higher layers provide more flexibility in obtaining isolation for tenants but they complicate the implementation of wear-leveling mechanisms across the different units of parallelism.

This dissertation proposes leveraging the inherent parallelism present in today's SSDs to increase isolation between multiple tenants sharing an SSD. We propose creating virtual SSDs that are pinned to a dedicated number of channels and dies depending on the capacity and performance needs of the tenant. The fact that the channels and dies can be more or less operated upon independently helps such virtual SSDs avoid adverse impacts on each other's performance. However, different workloads can write at different rates and in different patterns, this could age the channels and dies at different rates. For instance, a channel pinned to a TPC-C database instance wears out 12x faster than a channel pinned to a TPC-E database instance, reducing the SSD lifetime dramatically. This non-uniform aging creates an unpredictable SSD lifetime behavior that complicates both provisioning and load-balancing aspects of data center clusters.

To address this problem, we propose a two-part wear-leveling model which balances

wear within each virtual SSD and across virtual SSDs using separate strategies. Intravirtual SSD wear is managed by leveraging existing SSD wear-balancing mechanisms while inter-virtual SSD wear is balanced at *coarse-time granularities* to reduce interference by using new mechanisms. We control the wear imbalance between virtual SSDs using a mathematical model and show that the new wear-leveling model ensures near-ideal lifetime for the SSD with negligible disruption to tenants.

We design and implement FlashBlox and its new wear-leveling mechanisms inside an open-channel SSD stack (from CNEX labs [75]), and demonstrate benefits for a Microsoft data centers' multi-tenant storage workloads: the new SSD delivers up to 1.6x better throughput and reduces the 99th percentile latency by up to 3.1x. Furthermore, our wear leveling mechanism provides 95% of the ideal SSD lifetime even in the presence of adversarial write workloads that execute all the writes on a single channel while only reading on other channels.

#### 3.2 Motivation

Premium storage Infrastructure-as-a-Service (IaaS) offerings [76, 77, 78], persistent Platform-as-a-Service (PaaS) systems [79] and Database-as-a-Service (DaaS) systems [80, 81, 82, 83] need SSDs to meet their service level objectives (SLO) that are usually outside the scope of HDD performance. For example, DocDB [81] guarantees 250, 1,000 and 2,500 queries per second respectively for the S1, S2 and S3 offerings [84].

Storage virtualization helps such services make efficient use of SSDs' high capacity and performance by slicing resources among multiple customers or instances. Typical database instances in DaaS systems are 10 GB – 1 TB [84, 85] whereas each server can have more than 20 TB of SSD capacity today.

Bandwidth, IOPS [86, 87] or a convex combination of both [21, 88] is limited on a perinstance basis using token bucket rate limiters or intelligent IO throttling [2, 3, 4] to meet SLOs. However, there is no analogous mechanism for sharing the SSD while maintaining

Figure 3.1: Tenants sharing an SSD get better bandwidth (compare (a) vs. (b)) and tail latency as shown in (c) when using new hardware isolation. However, dedicating channels to tenants can lead to wear-imbalance between the various channels as shown in (d). A new design for addressing such a wear-imbalance is proposed.

low IO tail latency – an instance's latency still depends on the foreground reads/writes [17, 18, 20] and background garbage collection [16] of other instances.

Moreover, it is increasingly becoming necessary for diverse workloads (e.g., latency-critical applications and batch processing jobs) to be collocated for improving efficiency while being isolated from each other [89, 18]. Virtualization and container technologies are evolving to exploit hardware isolation of memory [90, 91], CPU [92, 93], caches [94, 95], and networks [96, 97] to support such scenarios. We extend this line of research to SSDs by providing hardware isolated SSDs while solving the wear-imbalance problem that arises due to the physical flash partitioning across diverse applications.

# 3.2.1 Hardware Isolation vs. Wear-Leveling

To understand this problem, we compare the two different approaches to hardware sharing using a representative workload. The first approach stripes data from all the workloads

Figure 3.2: The average rate at which flash blocks are erased for various workloads, including NoSQL, SQL, and batch processing workloads.

across all the flash channels (eight total) much like existing SSDs. This scheme provides the maximum throughput for each IO and uses the software rate limiter which has been used for Linux containers and Docker [98, 99] to implement weighted fair sharing of the resources (the scenario for Figure 3.1a). Note that each instance in software isolated case does not share physical flash blocks with other collocated instances to eliminate the unpredictability stemming from SSD firmware [16]. The second approach uses a configuration from our proposed mechanism that provides the hardware isolation by assigning a certain number of channels to each instance (the scenario for Figure 3.1b).

In both scenarios, there are four IO-intensive workloads. These workloads request 1/8th, 1/4th, 1/4th, and 3/8th of the shared storage resource. The rate limiter uses these as weights in the first approach, while FlashBlox assigns 1, 2, 2 and 3 channels respectively. Workloads 2 and 4 perform 100% writes and workloads 1 and 3 perform 100% reads. All workloads issue sequentially-addressed and aligned 64 KB IOs.

Hardware isolation not only reduces the 99th percentile latencies by up to 1.7x (Figure 3.1c), but also increases the aggregate throughput by up to 10.8% compared to software isolation. However, pinning instances to channels prevents the hardware from automatically leveling the wear across all the channels, as shown in Figure 3.1d. We exaggerate the variance of write rates to better motivate the problem: a need to balance wear between hardware isolated virtual SSDs. However, we will explore applications' typical write rates (see Figure 3.2) and tailor our solution to this side effect. To motivate the problem further,

Figure 3.3: The system architecture of FlashBlox.

we must first explore the parallelism available in SSD hardware, and the aspects of FTLs which cause interference in the first approach.

# 3.2.2 Leveraging Parallelism for Isolation

As shown in Figure 2.2, the architecture of flash memories plays an important role in defining isolation boundaries. In current drives, none of this flexibility is exposed to the host. Drives instead optimizes for a single IO pattern: extremely large or sequential IO. The FTL logically groups all planes into an array, effectively creating large super-pages and super-blocks. Striping increases the throughput of large, sequential IOs, but introduces the negative side effect of interference between multiple tenants sharing the drive. As all data is striped, every tenant's reads, writes and erases can potentially conflict with every other tenant's operations.

#### 3.3 FlashBlox Design

We now describe FlashBlox whose architecture is shown in Figure 3.3. At a high level, FlashBlox consists of the following three components: (1) A resource manager that allows tenants to allocate and deallocate virtual SSDs (vSSD); (2) A host-level flash manager that implements inter-vSSD wear-leveling by balancing wear across channels and dies at

Table 3.1: Virtual SSD types supported in FlashBlox.

| Virtual SSD Type       | Isolation Level | Allocation Granularity |

|------------------------|-----------------|------------------------|

| Channel Isolated vSSD  | High            | Channel                |

| Die Isolated vSSD      | Medium          | Die                    |

| Software Isolated vSSD | Low             | Plane/Block            |

| Unisolated vSSD        | None            | Block/Page             |

coarse time granularities; (3) An SSD-level flash manager that implements intra-vSSD wear-leveling and other FTL functionalities.

One of the key new abstractions provided by FlashBlox is that of a virtual SSD (vSSD) which can reduce tail latency. It uses dedicated flash hardware resources such as channels and dies that can be operated independently from each other. It can be created using the following simple API:

Instead of asking tenants to specify absolute numbers, FlashBlox enables them to create different types of vSSDs with different levels of isolation and throughput, and various storage capacity in GBs (see Table 3.1). These parameters are compatible with the performance and economic cost levels such as the ones [100, 84] advertised in DaaS services to ease usage and management. Tenants scale up capacity by creating multiple vSSDs of advertised sizes just as it is done in DaaS systems today. A vSSD is deallocated with void DeallocVirtualSSD (vssd\_t vSSD).

Channels, dies and planes are used for providing different levels of performance isolation. This brings significant performance benefits to multi-tenant scenarios because they can be operated independently from each other.

Higher levels of isolation have larger resource allocation granularities as channels are larger than dies. Therefore, channel-granular allocations can have higher internal fragmentation compared to die-granular allocations. However, this is less of a concern for FlashBlox's design for several reasons. First, capacities of flash's channels/dies/planes can

Figure 3.4: A FlashBlox SSD: vSSD\_A and B use one and two channels respectively. vSSD\_C and D use three dies each. vSSD\_E, and F use three soft-planes each.

be modified by vendors according to the design specifications of data center operators. Moreover, the tiered storage offerings of DaaS systems [100, 84, 85] allows the flexibility for the cloud provider to choose sizes and granularities such that fragmentation is reduced. Finally, the differentiated isolation levels match with the well-known pay-as-you-go cost model for cloud platforms, in which better services are subject to increased pricing such the overhead is offset.

Beyond providing different levels of hardware isolation, FlashBlox has to overcome the unbalanced wear-leveling challenge to prolong the SSD lifetime. We describe the design of each vSSD type and its corresponding wear-leveling mechanism respectively as follows.

# 3.3.1 Channel Isolated Virtual SSDs

A vSSD with high isolation receives its own dedicated set of channels. For instance, the resource manager of an SSD with 16 channels can host up to 16 channel isolated vSSDs, each containing one or more channels inaccessible to any other vSSD. Figure 3.4 illustrates vSSD A and B that span one and two channels respectively.

Channel Allocation. The throughput level and target capacity determine the number of channels allocated to a channel isolated vSSD. FlashBlox allows the data center/PaaS administrator to implement the size\_t tptToChannel(int tptLevel) function that maps between throughput levels and required number of channels. The number of channels allocated to the vSSD is, therefore, the maximum of tptToChannel (tptLevel)

and [capacity / capacityPerChannel].

Within a vSSD, the system stripes data across its allocated channels similar to traditional SSDs. This maximizes the peak throughput by operating on the channels in parallel. Thus, size of the super-block of vSSD\_A in Figure 3.4 is half that of vSSD\_B. Pages within the super-block are also striped across the channels similar to existing physical SSDs.

The hardware-level isolation present between the channels by virtue of hardware parallelism allows the read, program and erase operations on one vSSD to largely be unaffected by the operations on other vSSDs. Such an isolation enables latency sensitive applications to significantly reduce their tail latencies.

Compared to an SSD that stripes data from all applications across all channels, a vSSD (over fewer channels) delivers a portion of the SSD's all-channel bandwidth. Customers of DaaS systems are typically given and charged for a fixed bandwidth/IOPS level, and software rate-limiters actively keep their consumption in check. Thus, there is no loss of opportunity for not providing the peak-bandwidth capabilities for every vSSD.

**Unbalanced Wear-Leveling Challenge.** A significant side effect of channel isolation is the risk of uneven aging of the channels as different vSSDs may be written at different rates. Figure 3.2 shows how various storage workloads erase blocks at different rates indicating that channels pinned naively to vSSDs will age at different rates if left unchecked.

Such uneven aging may exhaust a channel's life long before other channels fail. Premature death of even a single channel would render significant capacity losses (> 6% in our SSD). Furthermore, premature death of a single channel leads to an opportunity loss of never being able to create a vSSD that spans all the 16 channels for the rest of the server's lifetime. Therefore, it is necessary to ensure that all the channels are aging at the same rate.

**Inter-Channel Wear-Leveling.** To ensure uniform aging of all channels, FlashBlox uses a simple yet effective wear-leveling scheme: *periodically, the channel that has incurred the maximum wearout thus far is swapped with the channel that has the minimum rate of wearout.*

A channel's wearout rate is the average rate at which it erased blocks since the last time the channel was swapped. This prevents the most-aged channels from seeing high wearout rates, thus intuitively extending their lifetime to match that of the other channels in the system. We analytically derive the minimum necessary frequency and present the design of the migration mechanism as follows.

Swap Frequency Analysis. Let  $\sigma_i$  denote the wear (total erase count of all the blocks till date) of the  $i^{th}$  channel.  $\xi = \sigma_{max}/\sigma_{avg}$  denotes the wear imbalance<sup>1</sup> which must not exceed  $1 + \delta$ ; where  $\sigma_{max} = Max(\sigma_1, ..., \sigma_N)$ ,  $\sigma_{avg} = Avg(\sigma_1, ..., \sigma_N)$ , N is the total number of channels, and  $\delta$  measures the imbalance.

When the device is new, it is obviously not possible to ensure that  $\xi \leq 1 + \delta$  without aggressively swapping channels. On the other hand, it must be brought within bounds fairly early in the lifetime of the server (L=150–250 weeks typical) such that all the channels are available for as much of the server's lifetime as possible.

SSDs are provisioned with a target erase workload and we analyze for the same – let's say M erases per week. We mathematically study the wear-imbalance vs. frequency of migration (f) tradeoff and show that manageable values of f can provide acceptable wear imbalance where  $\xi$  comes below  $1 + \delta$  after  $\alpha L$  weeks, where  $\alpha$  is between 0 and 1.

Worst-case write workload for FlashBlox is when all the provisioned writes go to a single channel while the other channels are read-only workloads.<sup>2</sup> The assumption that a single channel's bandwidth can handle the entire provisioned bandwidth is valid for modern SSDs: most data center SSDs are provisioned with 3,000-10,000 erases to last 150–250 weeks. This implies that provisioned erase rate for a 1TB SSD is M=21–116 MBPS which is significantly lower than a channel's erase bandwidth (typically 64–128MBPS).

<sup>&</sup>lt;sup>1</sup>The ratio of maximum to average is an effective way to quantify imbalance [101]. This is especially true in our case, as the lifetime of the new SSD will be determined by the maximum wearout of a single channel, whereas the lifetime of ideal wear-leveling is determined by the average wearout of all the channels. The ratio of maximum to average thus represents the loss of lifetime due to imperfect wear leveling.

<sup>&</sup>lt;sup>2</sup>This worst-case is from a non-adversarial point of view. An adversary could change the vSSD write bandwidth at runtime such that no swapping strategy can keep up. But data center workloads are not adversarial and have predictable write patterns.