# MANAGING SIGNAL, POWER, AND THERMAL INTEGRITY FOR THREE-DIMENSIONAL INTEGRATED CIRCUITS AND SYSTEMS

A Dissertation Presented to The Academic Faculty

by

Sung Joo Park

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

Georgia Institute of Technology August 2016

# **COPYRIGHT ©2016 BY SUNG JOO PARK**

# MANAGING SIGNAL, POWER, AND THERMAL INTEGRITY FOR THREE-DIMENSIONAL INTEGRATED CIRCUITS AND SYSTEMS

#### Approved by:

Dr. Madhavan Swaminathan, Advisor School of Electrical & Computer Engineering *Georgia Institute of Technology*

Dr. David Keezer School of Electrical & Computer Engineering *Georgia Institute of Technology*

Dr. Sung-Kyu Lim School of Electrical & Computer Engineering *Georgia Institute of Technology*  Dr. Muhannad S. Bakir School of Electrical & Computer Engineering *Georgia Institute of Technology*

Dr. Yogendra K. Joshi School of Mechanical Engineering *Georgia Institute of Technology*

Date Approved: July 13, 2016

To my family and friends

# TABLE OF CONTENTS

| ACKNO                         | WLEDGEMENTS                                 | vii |

|-------------------------------|---------------------------------------------|-----|

| LIST OF                       | TABLES                                      | ix  |

| LIST OF                       | FIGURES                                     | Х   |

| CHAPTE                        | <b>CR 1 INTRODUCTION</b>                    | 1   |

| 1.1 Background and Motivation |                                             | 1   |

| 1.2 Prior                     | 1.2 Prior Work                              |     |

| 1.3 This                      | Work                                        | 8   |

| 1.4 Contr                     | ributions                                   | 9   |

| 1.5 Organ                     | nization of the Dissertation                | 12  |

| СНАРТЕ                        | <b>CR 2 ELECTRICAL-THERMAL MODELING AND</b> |     |

| SIMULA                        | TION                                        | 14  |

| 2.1 Introd                    | duction                                     | 14  |

| 2.2 Syste                     | m Configuration                             | 15  |

| 2.3 Elect                     | rical and Thermal Modeling                  | 17  |

| 2.3.1                         | Electrical Modeling                         | 19  |

| 2.3.2                         | Thermal Modeling                            | 24  |

| 2.4 Elect                     | rical-thermal Simulation                    | 27  |

| 2.4.1                         | Simulation Results                          | 27  |

| 2.4.2                         | Analysis of Delay                           | 29  |

| 2.5 There                     | nal Impact on Power Delivery Network Design | 34  |

| 2.5.1                         | On-Chip Decoupling Capacitors               | 37  |

| 2.5.2                         | PDN Simulation with Temperature Effects     | 42  |

| 2.5.3                         | Case Study                                  | 44  |

| 2.6 Summ    | ary                                                | 47 |

|-------------|----------------------------------------------------|----|

| CHAPTEI     | R 3 COMPENSATION OF THERMALLY INDUCED              | )  |

| DELAY       |                                                    | 50 |

| 3.1 Introdu | action                                             | 50 |

| 3.2 Adapti  | ve Supply Voltage Using Variable Reference Voltage | 51 |

| 3.3 Contro  | llable Path Delay with Redundant Paths             | 55 |

| 3.4 Variab  | le Driving Strength for Clock Repeaters            | 58 |

| 3.5 Compa   | arison of Methods                                  | 60 |

| 3.6 Summ    | ary                                                | 63 |

| CHAPTEI     | R 4 VALIDATION USING MEASUREMENTS                  | 66 |

| 4.1 Introdu | action                                             | 66 |

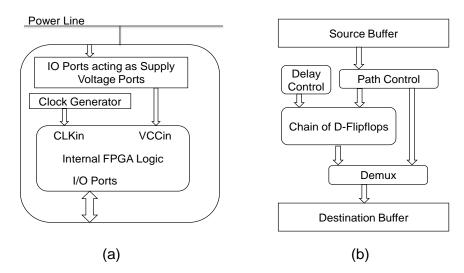

| 4.2 FPGA    | Implementation                                     | 66 |

| 4.3 Custor  | n IC Design                                        | 69 |

| 4.3.1       | Design Concept                                     | 69 |

| 4.3.2       | IC Test Board                                      | 74 |

| 4.4 Measu   | rement Setup                                       | 77 |

| 4.5 Measu   | rement Results                                     | 78 |

| 4.5.1       | FPGA-based Board                                   | 78 |

| 4.5.1       | Custom IC-based Test Vehicle                       | 81 |

| 4.6 Summ    | ary                                                | 84 |

| CHAPTEI     | R 5 SYSTEM OPTIMIZATION FOR 3-D ICS                | 86 |

| 5.1 Introdu | action                                             | 86 |

| 5.2 Machin  | ne-Learning (ML) Algorithms for Optimization       | 90 |

| 5.2.1       | Bayesian Optimization (BO)                         | 91 |

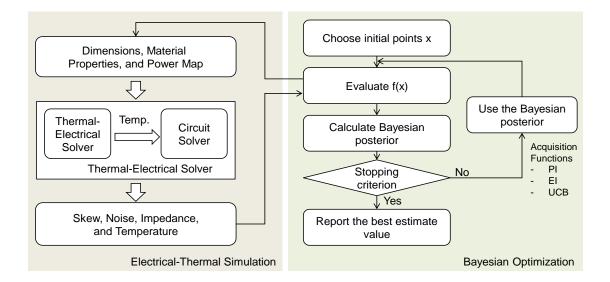

| 5.2.2               | Flow of Electrical-Thermal Simulation including Bayesian | Optimization 96 |

|---------------------|----------------------------------------------------------|-----------------|

| 5.3 Appli           | cation of ML Algorithms                                  | 100             |

| 5.4 Analy           | vsis                                                     | 101             |

| 5.4.1               | One-Dimensional Optimization                             | 101             |

| 5.4.2               | Multi-Dimensional Optimization                           | 103             |

| 5.5 Sumn            | nary                                                     | 110             |

| СНАРТЕ              | R 6 CONCLUSIONS AND FUTURE WORK                          | 112             |

| 6.1 Sumn            | nary and Conclusion                                      | 112             |

| 6.2 Future Work 113 |                                                          |                 |

| 6.3 Contr           | 6.3 Contributions 114                                    |                 |

| 6.4 Public          | cations                                                  | 116             |

| 6.4.1               | Journals                                                 | 116             |

| 6.4.2               | Conferences                                              | 117             |

| REFERE              | NCES                                                     | 119             |

| VITA                | <b>VITA</b> 13                                           |                 |

### ACKNOWLEDGEMENTS

This dissertation would not have been possible without invaluable support and help from many people. I would like to express my sincere appreciation to all of them. First, I would like to express my appreciation to my advisor, Professor Madhavan Swaminathan, for his guidance and consistent support. I may not have accomplished and finished the Ph.D. course without him. I also would like to extend my gratitude to the Ph.D. dissertation reading committee, Dr. David Keezer and Dr. Sung-Kyu Lim, for their review about my dissertation and valuable comments for the dissertation and proposal. I also would like to thank the other dissertation committee members, Dr. Muhannad S. Bakir, and Dr. Yogendra K. Joshi, for their valuable comments and contribution to the improvement of my dissertation.

I would like to give my special thanks to current and former members of the Mixed Signal Design group, Mr. Colin Pardue, Dr. Jianyong Xie, Dr. Biancun Xie, Dr. Ming Yi, Mr. Rishik Bazaz, Dr. Kyu Hwan Han, Dr. Jae Young Choi, Dr. Myunghyun Ha, Dr. Suzanne Huh, and Mr. Sang Kyu Kim, and visiting researchers, Dr. Jun Ki Min, Mr. You Keun Han, Dr. Sebastian Mueller, and Dr. Anto K Davis. In addition, I would like to extend my thanks for interesting and helpful discussions to Satyan Tellikepali, David Zhang, and Nitish Natu.

I would like to extend my gratitude to my friends at Georgia Tech and I also would like to thank Samsung Electronics for providing funds for my graduate study at Georgia Tech. Lastly, I could not have finished my doctorate course without my family, my wife Hoonee and beloved daughters Seohyun and Seojin. I would like to extend my appreciation to them. And, I also would like to thank my parents, parents-in-law, and relatives.

# LIST OF TABLES

| Table 1  | Comparison of the optimization algorithms ( $X_1$ and $X_2$ represent optimized |  |

|----------|---------------------------------------------------------------------------------|--|

|          | values)                                                                         |  |

| Table 2  | Geometrical dimension of the system configuration [37] 17                       |  |

| Table 3  | Dimension and electrical parasitics of unit components [8]                      |  |

| Table 4  | Electrical parasitics of the full-system power delivery network [37]            |  |

| Table 5  | Material parameters for thermal model                                           |  |

| Table 6  | Capacitance components in a CMOS inverter                                       |  |

| Table 7  | Delay values with buffers and wire [8]                                          |  |

| Table 8  | Types of on-chip decoupling capacitors (ODCs) 40                                |  |

| Table 9  | Comparison of PDN design cases [52]                                             |  |

| Table 10 | Comparison of the adaptive voltage method with the previous method;             |  |

|          | modified from [37]55                                                            |  |

| Table 11 | Comparison of the controllable delay method with the previous method;           |  |

|          | modified from [37]                                                              |  |

| Table 12 | Comparison of the variable strength method with the previous method;            |  |

|          | modified from [37] 60                                                           |  |

| Table 13 | Fabrication process specifications                                              |  |

| Table 14 | Pinout of the fabricated chip77                                                 |  |

| Table 15 | Comparison of classification-based machine-learning algorithms                  |  |

| Table 17 | Input variables for optimization of thermal and electrical performance 101      |  |

| Table 18 | One-dimensional optimization results                                            |  |

| Table 19 | Optimization results with various power maps 108                                |  |

# LIST OF FIGURES

| Figure 1                                       | Electronic system trend in million transistors per chip, size of computing       |

|------------------------------------------------|----------------------------------------------------------------------------------|

|                                                | system in mm <sup>3</sup> and clock speed in MHz; modified from [2]1             |

| Figure 2                                       | Signal integrity and power integrity for high speed designs                      |

| Figure 3                                       | 3-D integration options. (a) 2.5-D with silicon or glass interposer and (b) 3-D  |

|                                                | integration with TSVs                                                            |

| Figure 4                                       | Temperature gradient in a 3-D integrated system [8]                              |

| Figure 5                                       | (a) Inclusion of thermal integrity to electrical design and (b) interactions of  |

|                                                | signal, power and thermal integrity                                              |

| Figure 6                                       | Comparison of global optimization algorithms available in MATLAB with            |

|                                                | Bayesian optimization for a predefined function; (a) multi-start, (b) global     |

|                                                | search, (c) pattern search, (d) genetic algorithm, and (e) Bayesian optimization |

|                                                |                                                                                  |

|                                                | [81]                                                                             |

| Figure 7                                       | [81]                                                                             |

| Figure 7<br>Figure 8                           |                                                                                  |

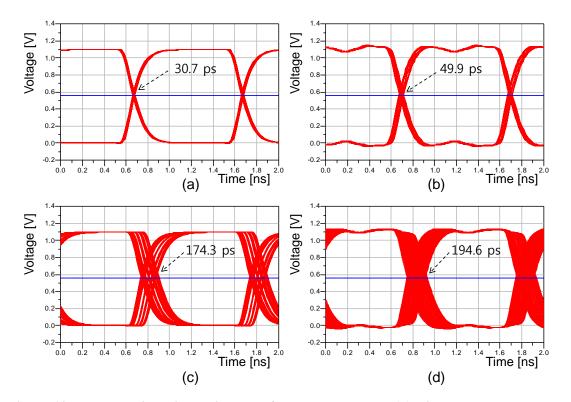

| C                                              | Flow of electrical-thermal analysis for 3-D system design                        |

| Figure 8                                       | Flow of electrical-thermal analysis for 3-D system design                        |

| Figure 8<br>Figure 9                           | Flow of electrical-thermal analysis for 3-D system design                        |

| Figure 8<br>Figure 9                           | Flow of electrical-thermal analysis for 3-D system design                        |

| Figure 8<br>Figure 9<br>Figure 10              | Flow of electrical-thermal analysis for 3-D system design                        |

| Figure 8<br>Figure 9<br>Figure 10<br>Figure 11 | Flow of electrical-thermal analysis for 3-D system design                        |

| Figure 8<br>Figure 9<br>Figure 10<br>Figure 11 | Flow of electrical-thermal analysis for 3-D system design                        |

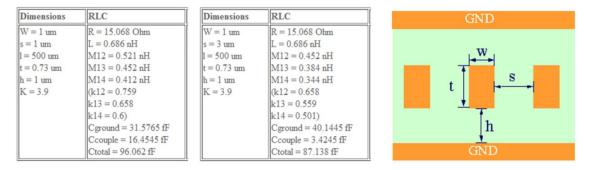

| Figure 14 | Dimension and unit schematic of the simulation model of meshed-PDN 21           |

|-----------|---------------------------------------------------------------------------------|

| Figure 15 | Schematic of the full system power model; (a) conventional model and (b)        |

|           | new model having TSVs and bumps                                                 |

| Figure 16 | Equivalent thermal resistance of the structure                                  |

| Figure 17 | Flow of electrical-thermalsolver [13]26                                         |

| Figure 18 | Power maps for thermal simulations                                              |

| Figure 19 | Transient simulation waveforms at clock ends (a) without the PDN model, (b)     |

|           | with the PDN model, (c) with the thermal gradient and (d) with both the PDN     |

|           | model and the temperature gradient [8]                                          |

| Figure 20 | Transient simulation waveforms at clock ends: (a) without the temperature       |

|           | gradient (@ 25°C, 75°C, and 125°C) and (b) with the temperature gradient        |

|           | [37]                                                                            |

| Figure 21 | Capacitance of buffer and interconnect model                                    |

| Figure 22 | Four parts of the propagation delay of a CDN: (a) an inverter driving wire cap, |

|           | (b) an inverter, (c) wire delay, and (d) a wire driving an inverter [8]         |

| Figure 23 | Temperature effect on delay [8]                                                 |

| Figure 24 | Cascaded buffers and interconnects [8]                                          |

| Figure 25 | A clock tree with a temperature gradient [37]                                   |

| Figure 26 | (a) The temperature profile for delay calculation. (b) Comparison of path       |

|           | delay with calculation [34]                                                     |

| Figure 27 | Target impedance and PDN response; modified from [49]35                         |

| Figure 28 | Impedance of PDN with temperature variation; (a) off-chip and (b) on-chip. 36   |

| Figure 29 | PDN noise with temperature variation (a) With ODC. (b) Without ODC 37           |

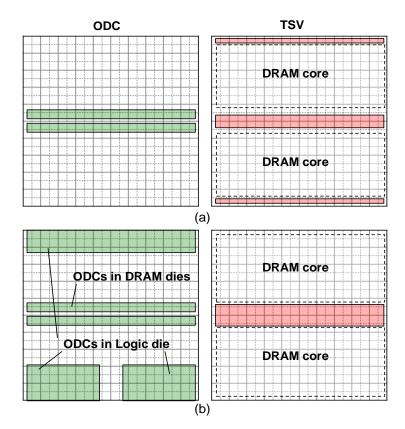

| Figure 30 | Example structures of ODCs: (a) MOS, (b) MIM, and PIP [51]38                   |

|-----------|--------------------------------------------------------------------------------|

| Figure 31 | Variations of the MOS capacitor [52]                                           |

| Figure 32 | Comparison of on-chip decoupling capacitors [52]41                             |

| Figure 33 | Block diagram of a 3-D PDN                                                     |

| Figure 34 | Simulated PDN impedances with and without temperature gradient: (a)            |

|           | impedance, (b) impedance distribution measured at 1 GHz, and (c) impedance     |

|           | difference measured at 1 GHz [52]                                              |

| Figure 35 | Current excitation for transient simulation [52]                               |

| Figure 36 | Simulated PDN noise: (a) without temperature gradient and (b) with             |

|           | temperature gradient [52]                                                      |

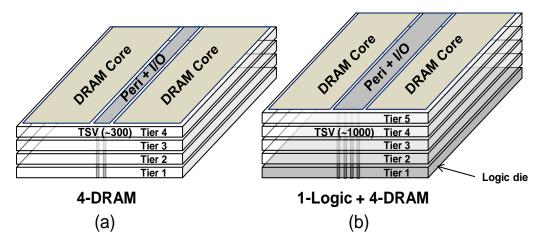

| Figure 37 | 3-D IC applications for high-speed memory products: (a) DDR3 [67] and (b)      |

|           | high bandwidth memory (HBM) [68]; Modified from [52] 45                        |

| Figure 38 | Locations of on-chip decoupling capacitors for: (a) DDR3 and (b) HBM [52].     |

|           |                                                                                |

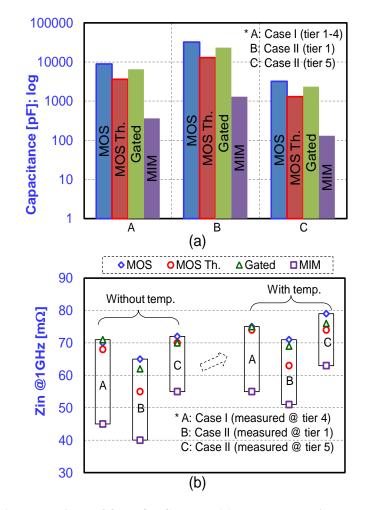

| Figure 39 | A comparison of four ODC types: (a) total decoupling capacitance and (b)       |

|           | PDN impedance @ 1GHz [52]47                                                    |

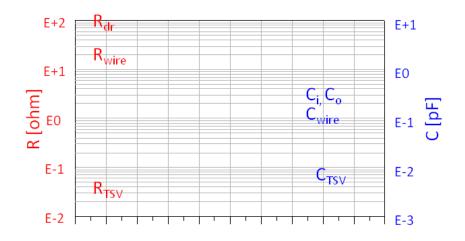

| Figure 40 | Resistance and capacitance of buffer, interconnects, and TSV 50                |

| Figure 41 | Concepts of the compensation methods: (a) a block diagram and (b) a simple     |

|           | circuit diagram [37]51                                                         |

| Figure 42 | Sensitivity with bias voltage (VDD and VBB) compared with temperature          |

|           | variation                                                                      |

| Figure 43 | Schematic of adaptive supply voltage using variable reference voltage [37]. 53 |

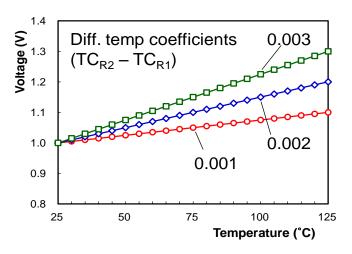

| Figure 44 | Generated reference voltages with differences of temperature coefficients of |    |

|-----------|------------------------------------------------------------------------------|----|

|           | R2 and R1 [37]5                                                              | 53 |

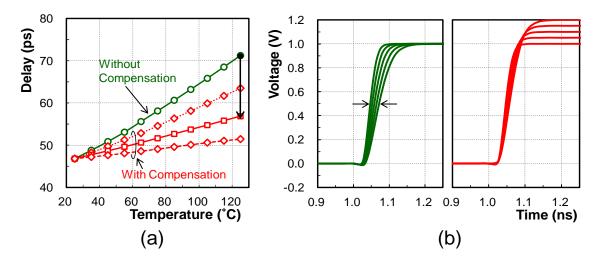

| Figure 45 | Simulated skew of a repeater unit of the CDN using the adaptive voltage      |    |

|           | method: (a) variations of delay compensation with temperature coefficients   |    |

|           | and (b) waveforms [37]5                                                      | 54 |

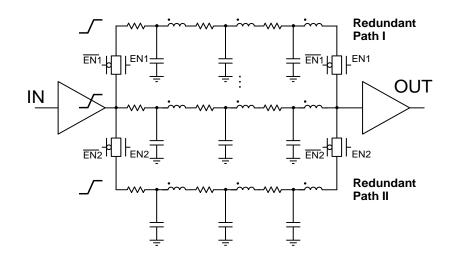

| Figure 46 | Schematic of controllable delay compensation using redundant interconnect    |    |

|           | [37]                                                                         | 56 |

| Figure 47 | Delay effect by odd mode coupling (Lm: 0.7, Cm: 0.5)                         | 57 |

| Figure 48 | Simulated skew of a repeater unit of the CDN using the controllable delay    |    |

|           | method: (a) variations of delay compensation with redundant paths and (b)    |    |

|           | waveforms [37]5                                                              | 57 |

| Figure 49 | Schematic of variable driving strength buffer5                               | 59 |

| Figure 50 | Simulated skew of a repeater unit of the CDN using the variable strength     |    |

|           | method: (a) variations of delay compensation with drive strengths and (b)    |    |

|           | waveforms [37]5                                                              | 59 |

| Figure 51 | Simulated delay of the repeater unit using the three methods [37]            | 51 |

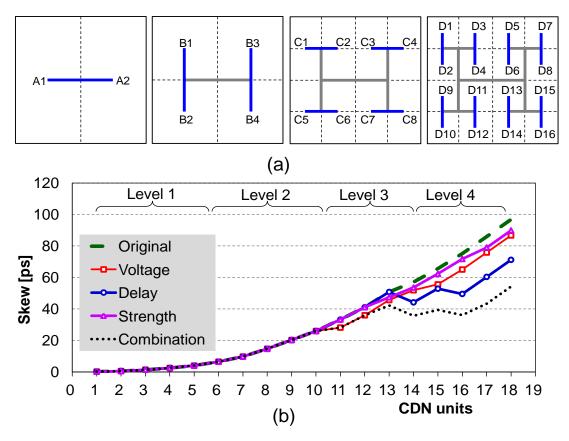

| Figure 52 | (a) Level of an H-tree clock. (b) Delay compensation with circuit allocation |    |

|           | for compensation implementation [37]                                         | 52 |

| Figure 53 | Comparison of (a) skew, (b) power consumption, and (c) area [37]6            | 53 |

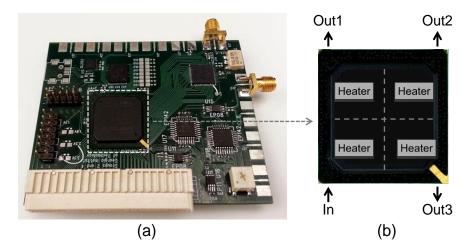

| Figure 54 | (a) FPGA (Spartan 6)-based test vehicle. (b) Placement of four PTC heaters   |    |

|           | on the FPGA to mimic the thermal condition [70]6                             | 57 |

| Figure 55 | A CDN structure in FPGA [37].                                                | 58 |

| Figure 56 | FPGA implementation of compensation techniques with (a) Adaptive supply       |  |

|-----------|-------------------------------------------------------------------------------|--|

|           | voltage and (b) Controllable path delay [71] 68                               |  |

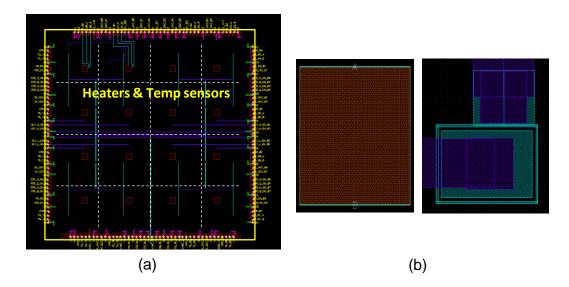

| Figure 57 | (a) Location of designed heaters and temperature sensors. (b) Layout of an n- |  |

|           | poly-based heater and a temperature monitoring diode71                        |  |

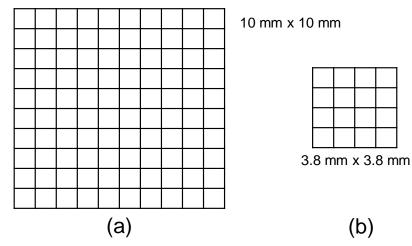

| Figure 58 | Die area for the heater and the temperature sensor. (a) 10 mm x 10 mm for     |  |

|           | simulations and (b) 3.8 mm x 3.8 mm for the chip design                       |  |

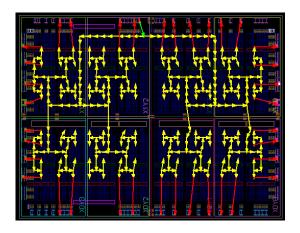

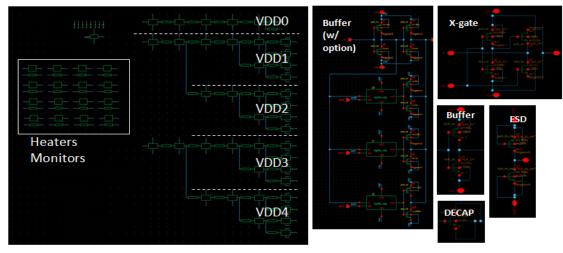

| Figure 59 | Schematic of CDN circuits                                                     |  |

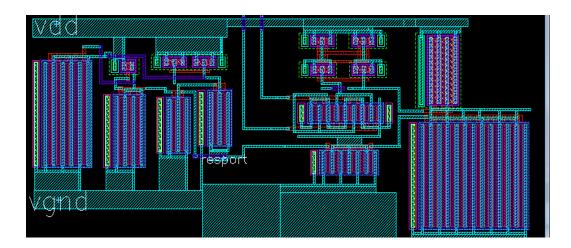

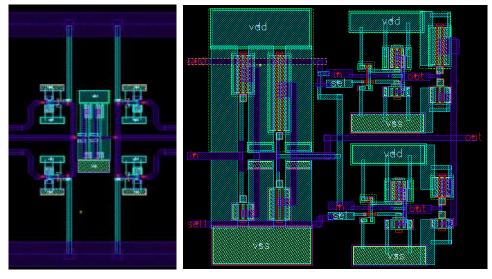

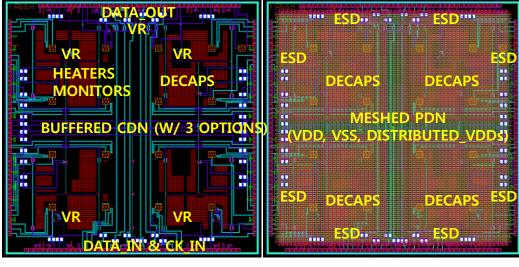

| Figure 60 | Layout results of the compensation circuits                                   |  |

| Figure 61 | Overview of layout and power distribution network                             |  |

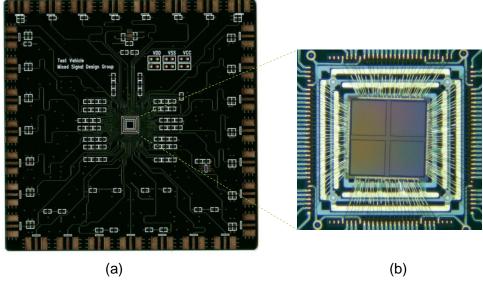

| Figure 62 | Fabricated chips using 180 nm process                                         |  |

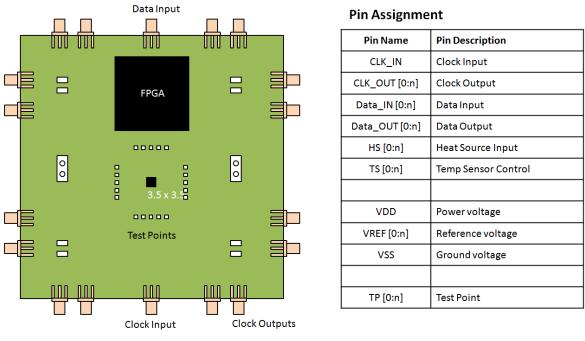

| Figure 63 | Concept of the test vehicle and pin assignment75                              |  |

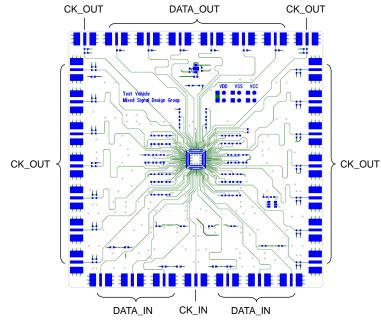

| Figure 64 | PCB design and input/output port location                                     |  |

| Figure 65 | (a) Fabricated PCB and (b) the wire-bonded chip                               |  |

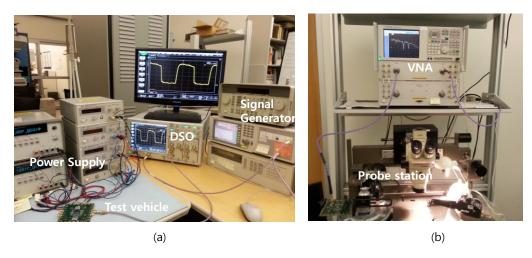

| Figure 66 | Test setup for (a) digital sampling oscilloscope (DSO) and (b) vector network |  |

|           | analyzer (VNA)                                                                |  |

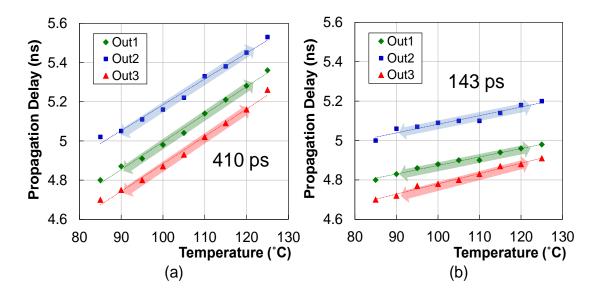

| Figure 67 | Propagation delay with temperature using the adaptive voltage method (a)      |  |

|           | without compensation and (b) with compensation [70]                           |  |

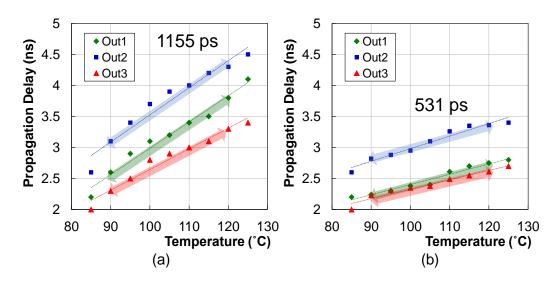

| Figure 68 | Propagation delay with temperature using the controllable delay method (c)    |  |

|           | without compensation and (d) with compensation [70]                           |  |

| Figure 69 | Real time compensation test with (a) the adaptive voltage method and (b) the  |  |

|           | controllable delay method [70]                                                |  |

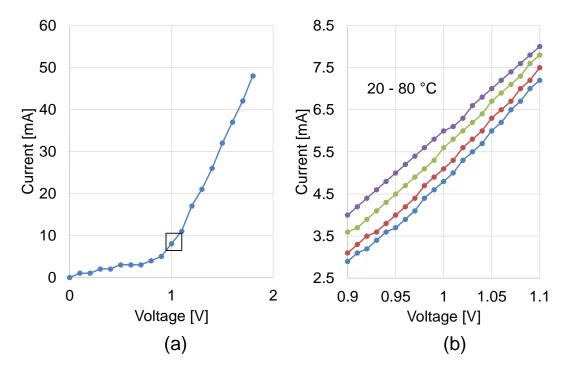

| Figure 70 | (a) Measured I-V profile of temperature monitoring circuits and (b)           |  |

|           | temperature variations                                                        |  |

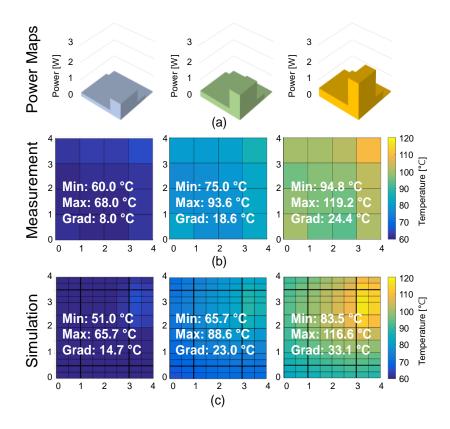

| Figure 71 | (a) Power maps used for simulation and measurement (b) measured                    |

|-----------|------------------------------------------------------------------------------------|

|           | temperature profiles, and (c) simulated temperature profiles                       |

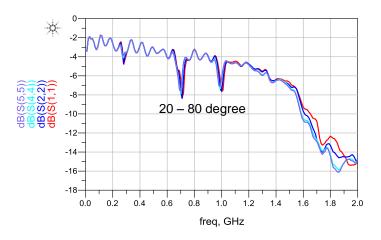

| Figure 72 | Measured scattering parameters of PDN with temperature variations                  |

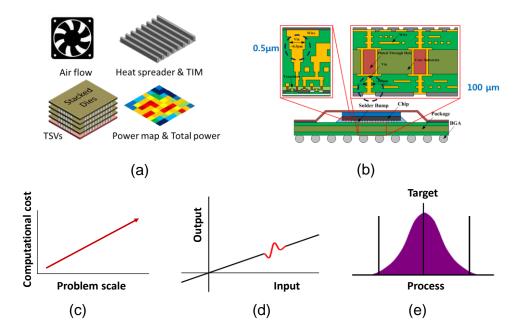

| Figure 73 | Challenges of electrical-thermal simulations; (a) large number of input            |

|           | variables, (b) multi-scale structure (> $10^2$ ), (c) computational cost, (d) non- |

|           | linearity, and (e) process variation                                               |

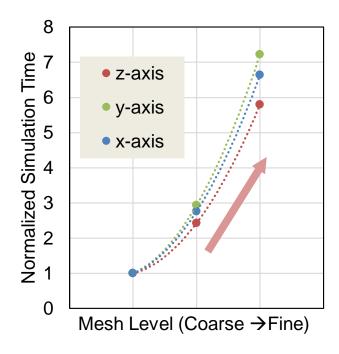

| Figure 74 | Increase in simulation time from a coarse mesh level to a find mesh level 87       |

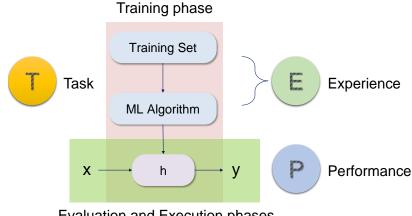

| Figure 75 | Concept of machine learning consists of training and evaluation/execution          |

|           | phases                                                                             |

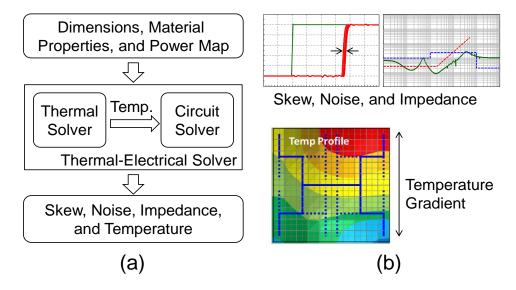

| Figure 76 | (a) Electrical-thermal analysis for 3-D systems. (b) Simulated skew, noise,        |

|           | PDN impedance, and temperature gradient [37]                                       |

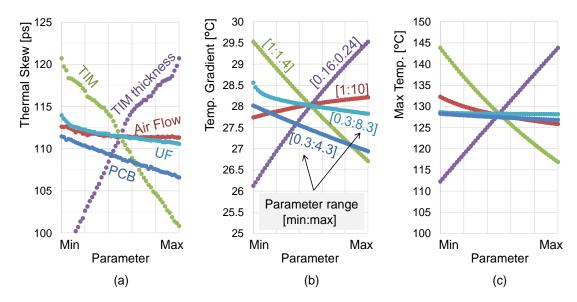

| Figure 77 | Sensitivity of parameters with the available range of each parameter: (a)          |

|           | thermal skew, (b) temperature gradient, and maximum temperature                    |

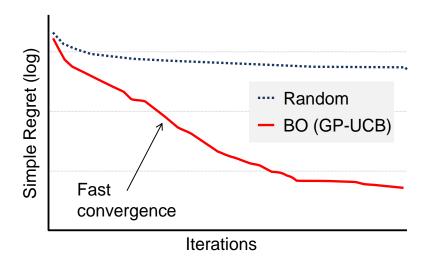

| Figure 78 | Performance of Bayesian optimization algorithm compared with random                |

|           | optimization [79]94                                                                |

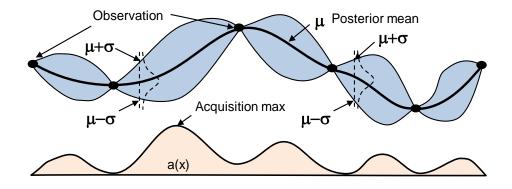

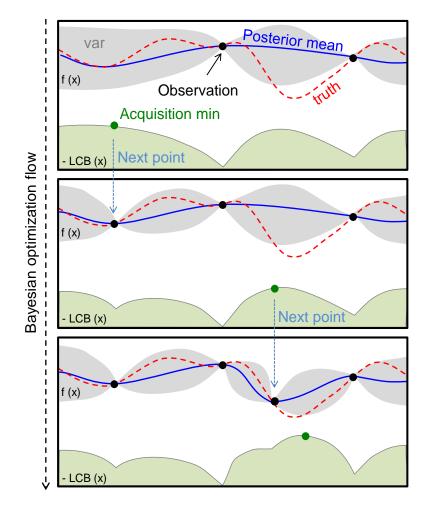

| Figure 79 | Bayesian optimization with prior, observation, acquisition function, and           |

|           | posterior [80]                                                                     |

| Figure 80 | Flow of Bayesian optimization [81]                                                 |

| Figure 81 | Bayesian optimization flow with prior, observation, acquisition function, and      |

|           | posterior [85]                                                                     |

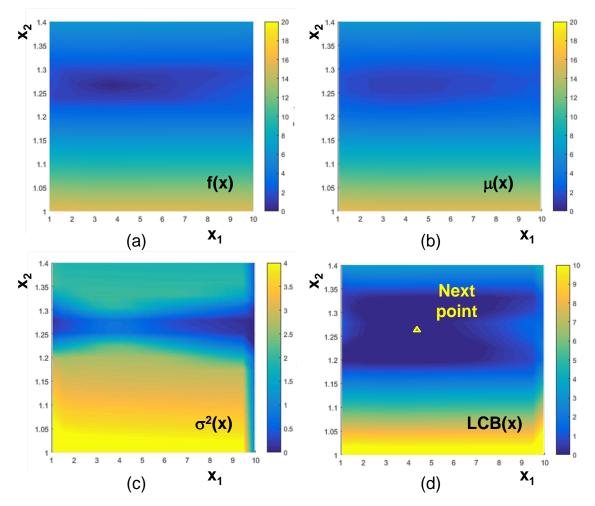

| Figure 82 | Distribution plots of (a) Function, (b) posterior mean, (c) posterior variance,    |

|           | and (d) LCB acquisition function in 2-D optimization of a 3-D system 99            |

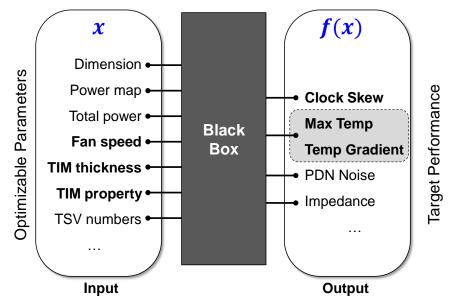

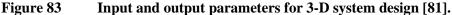

| Figure 83 | Input and output parameters for 3-D system design [81] 100                         |

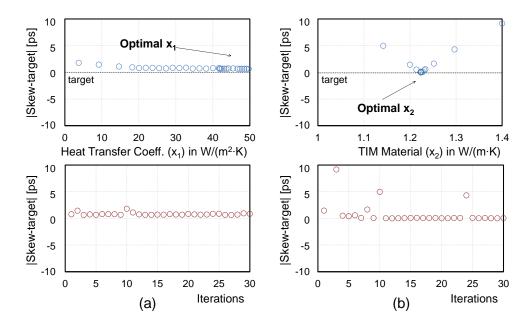

| Figure 84 | Optimization of each input parameter for clock skew of 110ps showing           |  |

|-----------|--------------------------------------------------------------------------------|--|

|           | convergence. (a) Heat transfer coefficient and (b) thermal conductivity of TIM |  |

|           | [86]                                                                           |  |

| Figure 85 | Optimization of each input parameter for clock skew of 110ps showing           |  |

|           | convergence. (a) Thickness of TIM and (b) thermal conductivity of PCB [86].    |  |

|           |                                                                                |  |

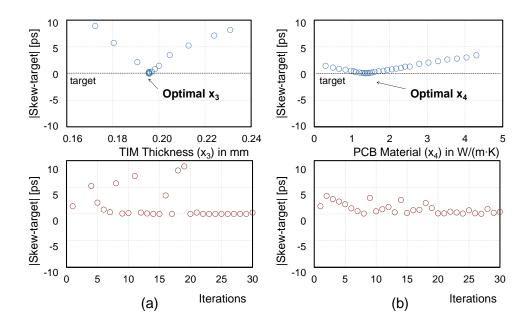

| Figure 86 | (a) Optimized parameters for lowering the maximum temperature and (b)          |  |

|           | optimized temperature [81] 104                                                 |  |

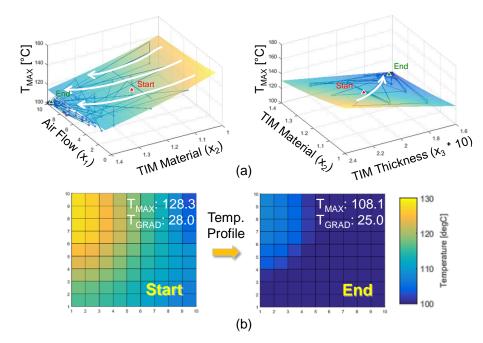

| Figure 87 | Non-linear behavior applied to Bayesian optimization using multiple            |  |

|           | objectives: (a) maximum temperature, (b) temperature gradient, and (c) both    |  |

|           | maximum and gradient [81] 106                                                  |  |

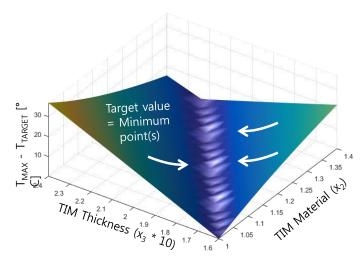

| Figure 88 | Non-linear trend showing minima with a target value [81] 107                   |  |

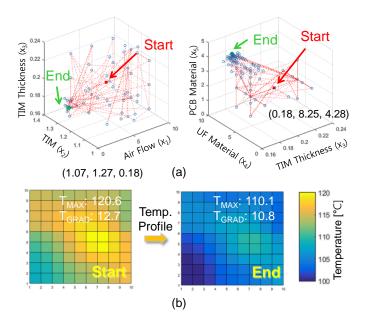

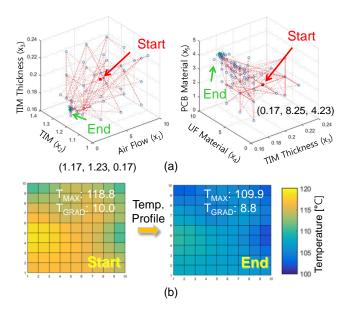

| Figure 89 | Optimization with power map II; (a) Iterations shown as a function of 3        |  |

|           | parameters only and (b) temperature distribution [81] 109                      |  |

| Figure 90 | Optimization with power map III; (a) Iterations shown as a function of 3       |  |

|           | parameters only and (b) temperature distribution [81] 109                      |  |

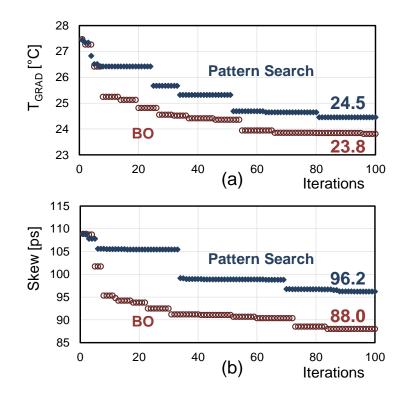

| Figure 91 | Comparison of convergence between BO and Pattern Search [81] 110               |  |

# LIST OF SYMBOLS AND ABBREVIATIONS

| 3-D  | Three-Dimension                         |

|------|-----------------------------------------|

| IC   | Integrated Circuit                      |

| SI   | Signal Integrity                        |

| PI   | Power Integrity                         |

| TI   | Thermal Integrity                       |

| TSV  | Through-Silicon Via                     |

| CMOS | Complementary Metal Oxide Semiconductor |

| CDN  | Clock Distribution Network              |

| PDN  | Power Distribution Network              |

| SSN  | Simultaneous Switching Noise            |

| РСВ  | Printed Circuit Board                   |

| ESL  | Equivalent Series Inductance            |

| ESR  | Equivalent Series Resistance            |

| VRM  | Voltage Regulator Module                |

| РТС  | Positive Temperature Coefficient        |

| FPGA | Field-Programmable Gate Array           |

### CHAPTER 1 INTRODUCTION

### **1.1 Background and Motivation**

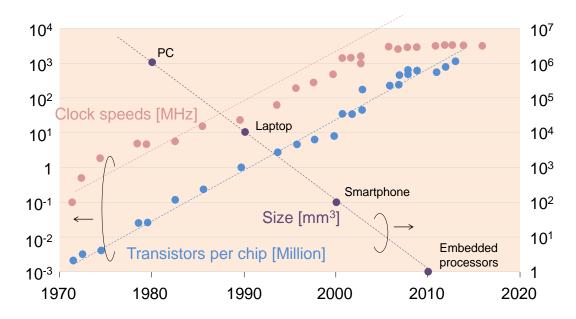

The perpetual growth of information technology has demanded that the electronics industry continues to improve in performance, density, functionality, and reliability. Many technical innovations have overcome technical hurdles to enable and achieve these improvements. One of the improvements, transistor density in the last several decades, has increased with Moore's law [1] accompanied by increased operation frequency of electronic systems. In addition, advancements in integration have led to smaller size devices, as shown in Figure 1 [2].

Figure 1 Electronic system trend in million transistors per chip, size of computing system in mm<sup>3</sup> and clock speed in MHz; modified from [2].

However, this trend of continuous growth challenges the electrical integrity of electronic systems. Integrity, a nomenclature which means an undiminished status, is

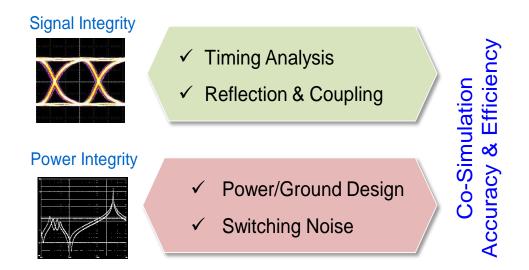

widely used to guarantee the performance of electronics systems through simulations. The goal of signal integrity (SI) is to ensure perfect timing and minimum reflection without any kind of coupling or distortion. In contrast, power integrity (PI) estimates non-ideal effects of the power/ground network with minimum switching noise. Both are crucial to meet the operational specifications of digital systems and guarantee better performance, as shown in Figure 2.

Figure 2 Signal integrity and power integrity for high speed designs.

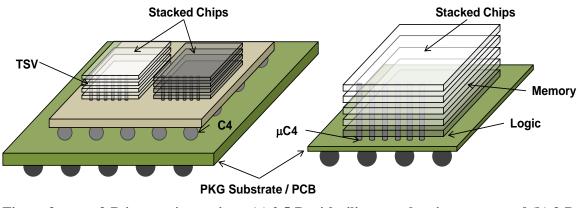

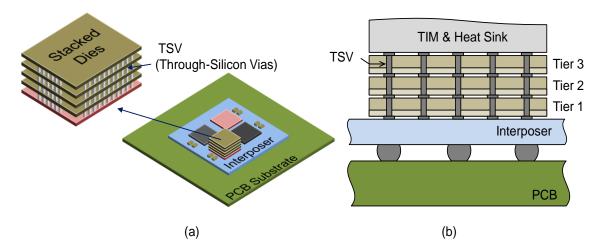

One of the most significant discussions in electronic system packaging is three dimensional integration. Many design challenges, such as performance, form factor, and density, have been overcome using this technique. Therefore, three-dimensional integrated circuits (3-D ICs) have many advantages, such as dramatically improved transistor density, electrical performance, and functionality [3]. However, 3-D technology also has some engineering related issues in modeling, design, fabrication, testing, and thermal management. Figure 3 shows the most widely used application options of TSV-based 3-D integration with and without an interposer, which are referred to as 2.5-D and 3-D integration.

Figure 3 3-D integration options. (a) 2.5-D with silicon or glass interposer and (b) 3-D integration with TSVs.

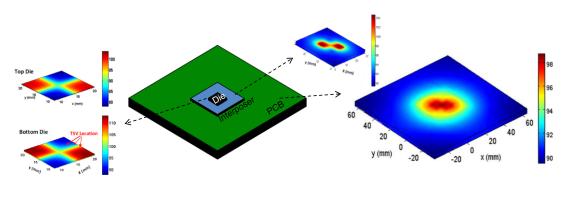

Increased circuit and system density result in increased power and thermal density of 3-D ICs which requires consideration of thermal management solutions. Hot spots and temperature gradients, as shown in Figure 4, significantly affect signal quality and degrade system performance. Those temperature-induced problems originate from increased power density in 3-D ICs [4]. Previous literature has indicated that temperature gradients in 3-D ICs are three times more severe than conventional ICs [5] and highest on-chip temperature gradients in some systems can be over 50 degrees Celsius [6], which pose significant problems for ensuring system reliability [7].

Figure 4 Temperature gradient in a 3-D integrated system [8].

For example, consider a 3-D system shown in Figure 4 comprised of two stacked dies with different power maps. They are stacked on top of a silicon interposer which is in turn mounted on a printed circuit board. The hot spots in various parts of the system shown in Figure 4 affect active as well as passive circuits due to changes in resistivity, mobility, and threshold voltages.

Temperature-induced problems affect the integrity of signals and system performance which can cause reliability issues. With higher operation frequencies and tighter timing budgets, the timing margin of system operation is continually shrinking. Furthermore, higher frequency operation of globally distributed clock signals is more sensitive to temperature variations across the chip. Because the clock signal synchronizes data signals, design of the clock distribution network is very critical in modern digital systems [11].

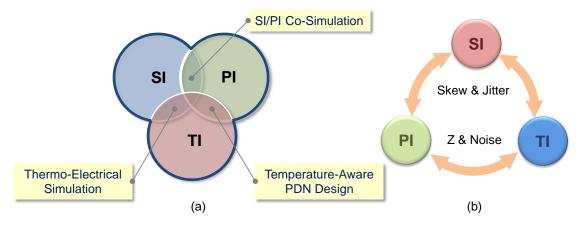

The interaction between thermal and electrical integrity is becoming increasingly difficult to ignore because they closely interact and the amount of interaction can become non-negligible, as described in Figure 5. In this research, interactions between signal integrity (SI), power integrity (PI), and thermal integrity (TI) have been investigated. Power integrity and signal integrity are both affected by temperature gradients on the clock distribution network (CDN) in 3-D ICs. This poses unique problems for both modeling and design.

Figure 5 (a) Inclusion of thermal integrity to electrical design and (b) interactions of signal, power and thermal integrity.

#### **1.2 Prior Work**

In this thesis, (1) development of a flow for estimating signal, power, thermal integrity, (2) thermal skew compensation methods, and (3) optimization approaches are described and proposed. Several researchers have investigated and presented on these topics before. The differences between this research and prior work are discussed below.

First, most conventional circuit simulations have been using the global temperature for PVT (process, voltage, and temperature) variations to reflect thermal effects instead of using the local temperature in a die. With respect to electrical and thermal simulations, previous studies have shown that, (1) co-design of signal and power integrity [12] and (2) electro-thermal simulation approach for estimating temperature and voltage drop in a PDN [13]. In contrast, this dissertation provides a full system model for inclusion of thermal integrity into signal and power integrity and quantifies thermal effects on them.

Second, researchers have proposed temperature control approaches to mitigate the effect of temperature in electronic circuits and systems. These techniques are based on controlling physical heat to reduce maximum temperature [14], managing power using

optimized voltage and frequency operation, also known as dynamic voltage and frequency scaling (DVFS) [15], and performing thermal-aware floor planning of the chip layout for uniform heat distribution [16].

In comparison, this dissertation investigates that circuit-based approaches can be specialized for unique target parameters such as delay, noise, and jitter. The focus of this dissertation is to propose and optimize the efficiency of a few methods which have specific compensation performance and overhead associated with them, as discussed in chapter 4. Compensation methods presented in previous literature have been implemented using temperature-variable supply voltage level converters [17], multiple-threshold voltage design [18], dynamic body biasing [19], adaptive body biasing with  $V_T$  detection [20], and tuning pull-up and pull-down transistors with a programmable temperature compensation device [21]. In addition, previous work has used a dynamically-modified clock tree using tunable delay [22], adjusting the drive strength of buffers [23], using a reversal of temperature dependency [24], [25], and adapting temperature-dependent gate delay [26].

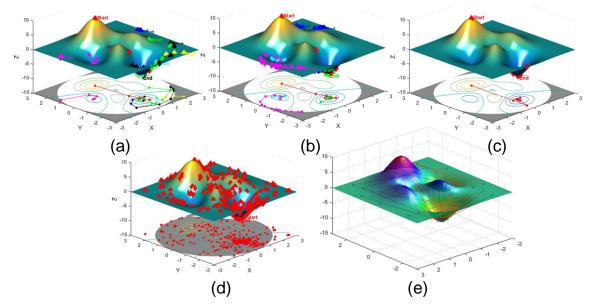

Last but not the least, several studies have proposed statistical methods such as worst case and Monte Carlo analyses [27] to optimize a large number of design parameters. Due to the large number of simulation cases and costly calculation overhead of these methods, others have proposed approaches that reduce the number of simulations, using design of experiments (DOE) [28]. However, the DOE approach has restrictions such as 1) interactions between parameters need to be minimal and 2) the number of levels is normally limited to below three. Moreover, some electrical and thermal parameters in electronic systems have continuous range, so quantization error can create problems during optimization. Other approaches for global optimization are available with multiple algorithms [29]. However, global optimization algorithms require a lot of computing resources because of the number of data sets and compute time for each data set. Optimization of a non-linear function using the global optimization algorithms available in MATLAB is compared with a machine-leaning method, namely Bayesian optimization, as illustrated in Figure 5. Table 1 also compares the number of iterations and optimization results by using global optimization algorithms and Bayesian Optimization which will be further discussed in Chapter 5. As Figure 6 illustrates, global optimization algorithms can find an optima in less than 100 iterations. As shown in Chapter 5, the optimized value using Bayesian optimization was superior to the value obtained using a more conventional global search algorithm, for a fixed number of iterations.

Figure 6 Comparison of global optimization algorithms available in MATLAB with Bayesian optimization for a predefined function; (a) multi-start, (b) global search, (c) pattern search, (d) genetic algorithm, and (e) Bayesian optimization [81].

|     | Algorithm                 | $X_1$   | $X_2$   | Iterations |

|-----|---------------------------|---------|---------|------------|

| (a) | Multi-start               | -1.6255 | 0.2283  | 345        |

| (b) | Global-search             | 0.2045  | -1.3474 | 273        |

| (c) | Pattern-search            | -1.6255 | 0.2283  | 272        |

| (d) | Genetic-algorithm         | -1.6255 | 0.2283  | 2650       |

| (e) | Bayesian opt. (this work) | -1.6251 | 0.2283  | 100        |

Table 1Comparison of the optimization algorithms (X1 and X2 represent optimized values).

Recently, machine-learning (ML) algorithms have become popular and have been applied for various applications [30]-[33]. These techniques have enabled machines to learn from the training sequences by accumulating data sets through automated learning algorithms. Some of these methods have been adapted to electromagnetic problems [30], static timing analysis [31], high speed interconnect systems [32], and time domain performance estimation [33]. In this dissertation, we apply machine learning algorithms for design optimization of 3-D ICs and systems.

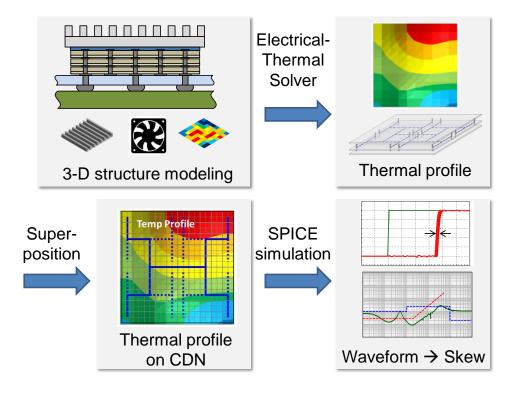

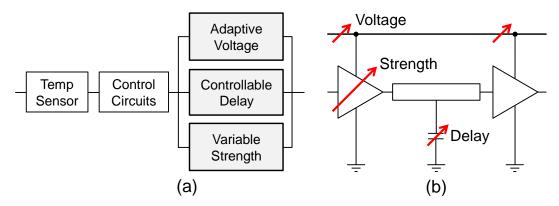

#### 1.3 This Work

As discussed in the previous section, this dissertation presents a flow for electricalthermal simulation, thermal skew compensation methods and optimization approaches. Three-dimension integrated systems require temperature-aware electrical simulations and analysis due to increased thermal density and operating frequency. This dissertation presents a flow for electrical-thermal simulations (Figure 7) and quantifies the impact of temperature in 3-D systems. To mitigate the temperature effects, this dissertation also proposes three energy-efficient mitigation methods to compensate for thermally induced skew. These methods include adaptive voltage, controllable delay, and variable strength. These methods have been discussed with measurements using two test vehicles.

Figure 7 Flow of electrical-thermal analysis for 3-D system design.

Simulating 3-D systems requires large computing resources due to the large number of design parameters and multi-scale structure. To improve efficiency, a machine-learning algorithm is applied for the optimization of 3-D systems. The algorithm shows fast convergence with a large number of parameters for the examples considered.

### **1.4 Contributions**

The objective of this dissertation is to develop a co-design methodology for 3-D ICs that can be used in electronic systems. This study also quantifies the effects of temperature on 3-D ICs and systems having high thermal density, thermal hot spots, and

temperature gradient. Temperature-related issues degrade not only signal quality but also the power distribution network (PDN) characteristics.

The work completed as part of this research include the following:

- Simulation model of the clock distribution network (CDN) and power distribution network (PDN) in a 3-D system has been built and electricalthermal simulations were performed. From the results of these thermoelectrical simulations, thermal effects such as increased skew and noise in 3-D systems were quantified.

- 2. To reduce and to compensate for temperature-induced skew in a clock distribution network, three skew compensation methods were proposed. The proposed methods use adaptive voltages, controllable delays, and variable strengths for clock repeaters and interconnect. The concepts were implemented with a recent technology node (45 nm) and their performance and design overhead were compared.

- 3. As a verification procedure, two types of test vehicles were designed. One was an FPGA-based test vehicle, and the other is a custom IC-based test vehicle. An H-tree CDN was implemented in the test vehicle. Measurement results using the designed test vehicles were correlated with electrical-thermal simulation results such as temperature profile and delay including temperature and compensation methods.

- 4. Design optimization using the proposed electrical-thermal simulation approach requires considerable computing resources because of many parameters involved and due to the multi-scale geometries. In this work,

machine learning methods were applied for design optimization. Bayesian optimization using Gaussian process shows that this approach is beneficial for optimization of 3-D systems.

In summary, the key contributions of this dissertation are as follows:

- A temperature-aware signal and power integrity simulation method for 3-D ICs and systems with high thermal density and temperature gradient was introduced.

- The delay, PDN impedance, and noise induced by temperature in 3-D ICs was simulated and analyzed, and optimal delay compensation methods were developed.

- Test vehicles using FPGA and custom IC were designed and fabricated and the proposed methods were validated using measurements.

- 4) A machine-learning (ML) methods was applied for 3-D IC and system optimization, and the results quantified.

## **1.5 Organization of the Dissertation**

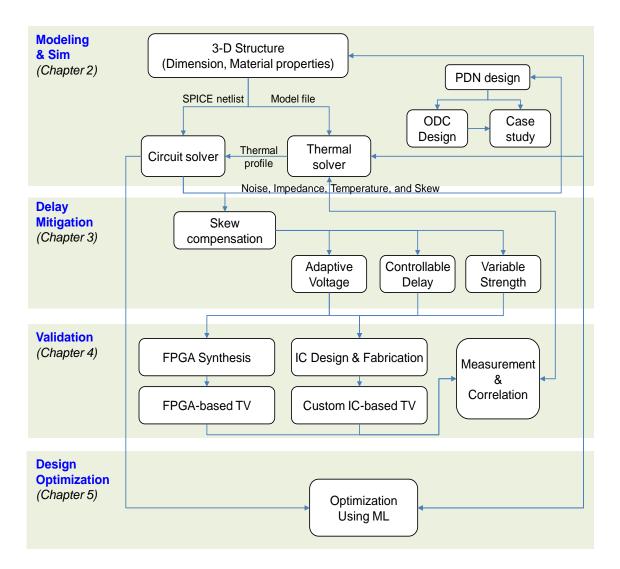

Figure 8 Organization of the dissertation.

As described in Figure 8, the rest of this dissertation is organized as follows. Electrical-thermal modeling with the target system configuration, the proposed electricalthermal simulation flow and results including power delivery network design considering thermal effects are addressed in Chapter 2. The following chapters, Chapter 3 and Chapter 4, provide details on thermal-skew mitigation methods and measurement results for verification and correlation, respectively. Chapter 5 presents a new optimization approach using machine-learning followed by summary in Chapter 6.

# CHAPTER 2 ELECTRICAL-THERMAL MODELING AND SIMULATION

### **2.1 Introduction**

First, this chapter defines system configuration comprised of the 3-D IC stack with power maps, clock distribution network, and system details. 3-D integrated systems, as in the example shown in Figure 9 (a), having interposer and stacked dies, have configuration options with respect to number, type, and layout of the integrated dies [8]. This dissertation examines a TSV-based 3-D system comprised of three dies stacked and mounted on an interposer as shown in Figure 9 (b). The assumed configuration with an interposer covers feasible integration options available. The clock distribution network is placed inside of the stack, between two dies of logic, and are integrated and connected to a PCB through the interposer by using TSVs.

Figure 9 System configuration with a 3-D IC; (a) comprised of multiple dies, interposer, and PCB and (b) cross-sectional view of the target system.

#### 2.2 System Configuration

In this chapter, clock distribution network and power distribution network, especially for timing skew in the clock distribution network and power supply fluctuation in the power distribution network (PDN), are the main focus for signal and power integrity evaluation. First, the clock was chosen because it is one of the most critical signals in synchronous digital systems because the signal is the timing reference for other signals. Furthermore, the clock signal becomes more sensitive with tighter timing margin under faster operation and temperature variation conditions [11]. Second, the power/ground network provides electrical sources, distribution rails, and reference of the voltage. Non-ideal effects of parasitics, such as inductance of planes and packages, return path discontinuity, and resonance, cause power supply fluctuation during simultaneous switching of the circuits. Even though simultaneous switching noise analysis has different consideration with specific types as shown in [34], it becomes more critical with faster switching rates during high speed operation.

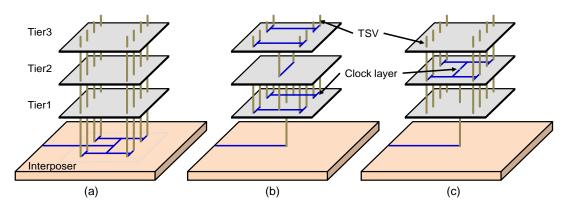

The structure of the clock distribution network (CDN) in 3-D integration is important since it affects thermal and electrical characteristics. Previous approaches to the CDN architecture in 3-D systems are discussed in [35], [36]. The first method shown in [35] was implemented with clock routing on an interposer, and distributed through the TSVs. The second method in [36] uses multiple but symmetrical tree-structure TSVs to distribute loads.

Figure 10 3-D CDN structures: (a) CDN on an interposer [35], (b) CDN with treestructure TSV [36], and (c) centered CDN; modified from [37].

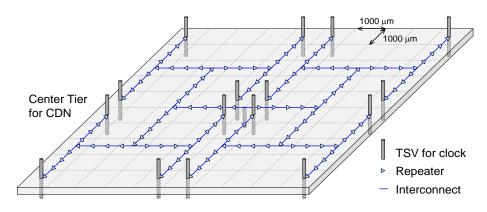

The structure proposed in this study uses a CDN structure constructed in the centered die, which requires fewer TSVs and routing of interposer layer and minimizes the effect of die to die variations. Electrical modeling shown in Chapter 3 will describe a more detailed structure containing cascaded chains of clock repeaters and metal interconnects. Figure 10 shows the three options for the CDN in 3-D ICs.

This chapter provides geometrical information and parameter values for the configuration in Figure 10 (c). Sizes of the die, interposer, and substrate PCB are 10 mm x 10 mm, 30 mm x 30 mm, and 100 mm x 100 mm, respectively. Layers of the PCB, the interposer, and the die are connected with C4 bumps and micro-bumps. In addition, the interposer and stacked dies are vertically connected using through-silicon vias. The detailed dimensions of the system configuration are listed in Table 2.

|                  | Unit            | Value           | Note                        |

|------------------|-----------------|-----------------|-----------------------------|

| Die              | mm <sup>3</sup> | 10 x 10 x 0.2   | Height x Length x Thickness |

| Interposer       | mm <sup>3</sup> | 30 x 30 x 0.2   | Height x Length x Thickness |

| PCB              | mm <sup>3</sup> | 100 x 100 x 0.2 | Height x Length x Thickness |

| C4 Bump          | μm              | 300             | Diameter                    |

| Micro-bump       | μm              | 100             | Diameter                    |

| TSV (interposer) | μm              | 30   100   100  | Diameter   Height   Pitch   |

| TSV (die)        | μm              | 5   50          | Diameter   Height           |

Table 2Geometrical dimension of the system configuration [37].

## 2.3 Electrical and Thermal Modeling

Most electrical parameters are affected by temperature. For example, the electrical resistivity of metal is linearly proportional to the temperature as shown in (1). Metals mainly used for interconnects in a chip (either aluminum or copper) have a temperature coefficient of resistivity ( $\alpha_R$ ) of 0.0039 degree Celsius. Because temperature can cause an almost 3.9% resistance change with a 10-degree increase, its effect on resistance is not negligible:

$$R(T) = R_0 [1 + \alpha_R (T - T_0)]$$

<sup>(1)</sup>

Operation of a complementary metal-oxide semiconductor (CMOS) transistor, one of the most widely used active devices, is mainly affected by temperature. Therefore, temperature has been one of the main variations for estimating performance of electronic systems with process and voltage, known as PVT (process-voltage-temperature) variations. As temperature increases, semiconductor mobility decreases by lattice scattering, both for n-type or p-type semiconductors. Temperature also varies the threshold voltage of transistor and its drain current, as shown in Equations (1) – (4), where  $\alpha_{\mu}$ ,  $\alpha_{VT}$ , and  $\alpha$  are temperature coefficients of mobility, threshold voltage, and drain current, respectively [9], [10].

$$\mu(T) = \mu_0 (T/T_0)^{\alpha_{\mu}}$$

(2)

$$I_{d}(T) = \mu(T) \frac{W}{L_{eff}} P_{l} \left[ V_{gs} - V_{T}(T) \right]^{\alpha/2} V_{ds}$$

(3)

$$V_T(T) = V_{T0} + \alpha_{V_T}(T - T_0)$$

(4)

The key objective of this electrical simulation modeling is to estimate signal and power integrity effects, specifically skew and power ground noise, in a single clock domain for 3-D ICs with temperature gradients. The CDN has cascaded buffers and interconnects also called as a "buffered clock tree." The shape of the clock is a symmetrical H-tree with the clock buffers placed every 500 µm on the metal interconnect. The symmetrical structure and cascaded buffer maximize the temperature effect. Figure 11 illustrates the buffered CDN structure with TSVs to connect clock distribution into other tiers. On-chip interconnects are in the resistance dominant range, therefore recent finer technology nodes having higher resistance show a significant effect on the delay of the signal.

Figure 11 An H-tree CDN structure in the centered die [37].

## 2.3.1 Electrical Modeling

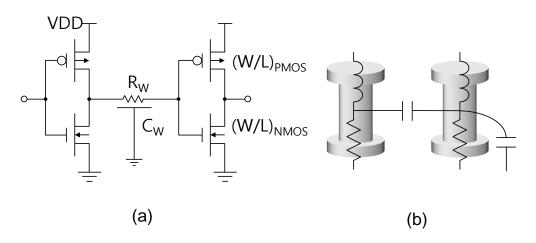

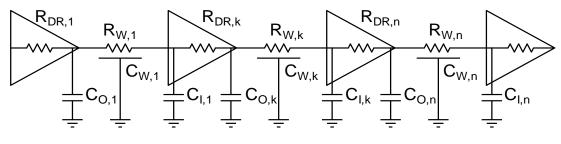

To build the electrical model for the entire structure, a BSIM4 model of the 45-nm technology node [38], [39] was used for clock repeaters having 2-stage inverter. Initial widths of the buffer are 315/95 nm 630/195 nm with the length of 50 nm referring to a standard buffer-size profile described in [8]. The initial size of the buffer is optimized to have the width of the unit repeater for fan-out 1 (FO1) (for PMOS/NMOS) and fan-out 2 (FO2) was 2.52/0.8 µm (for PMOS/NMOS) to ensure more immunity to variation. The optimized size has a ratio of 3-4 for PMOS and NMOS size and 4-5 and 8-10 times larger than initial sizing for FO1 and FO2, respectively. Simulation results with buffer sizing will be discussed in Chapter 4. Cascaded buffers are connected through metal interconnects, as shown in Figure 12 (a). Lumped RLC values from [40] for the metal interconnect are 30 ohm and 200 fF per mm.

Figure 12 Unit schematic of the simulation model: (a) CDN having buffers and interconnect and (b) TSV.

RLC values of clock interconnect in Figure 13 show inductance with RC values, and mutual values of capacitance and inductance. As indicated earlier, clock is the most critical signal in a digital system, thus more room with approaches with wider interconnect width and spacing are required. Optimization of RLC values of clock interconnect helps to reduce temperature effect of the delay.

Figure 13 Dimension and RLC values of clock interconnects [40].

Resistance of TSVs have been modeled using DC term and AC term including skin effect, as shown in Equation (5) - (8) [41], [42], and [43]. The value of self-inductance, shown in Equation (9), is used rather than mutual values because pitch of TSVs are much longer than its height.

$$R_{TSV} = \sqrt{R_{DC,TSV}^2 + R_{AC,TSV}^2} \left[\Omega\right]$$

(5)

$$R_{DC,TSV} = \frac{\rho l}{A} = \frac{\rho_{TSV} h_{TSV}}{\pi \left( d_{TSV} / 2 \right)^2} [\Omega]$$

(6)

$$R_{AC,TSV} \approx \frac{\rho l}{\pi (D-\delta)\delta} = \frac{\rho_{TSV} h_{TSV}}{\pi (d_{TSV} - \delta_{TSV}) \delta_{TSV}} [\Omega]$$

(7)

$$\delta_{TSV} = \sqrt{\frac{2\rho}{\omega\mu}} = \sqrt{\frac{\rho_{TSV}}{\pi f \mu_{TSV}}} [m]$$

(8)

$$L_{Self} = \frac{\mu l}{2\pi} \left[ \ln\left(\frac{2l}{R}\right) - \frac{3}{4} \right] = \frac{\mu h_{TSV}}{2\pi} \left[ \ln\left(\frac{2h_{TSV}}{d_{TSV}/2}\right) - \frac{3}{4} \right]$$

(9)

Figure 14 Dimension and unit schematic of the simulation model of meshed-PDN.

Because of the increased power density of 3-D ICs, accurate power distribution network modeling is required for power ground noise estimation. A meshed on-chip PDN model, shown in [44], was used with an on-chip decoupling capacitor model from [45]. To mimic a noisy chip condition, the output buffers of a 64-bit data bus were distributed on other tiers as simultaneous switching noise sources. With the noise sources, a full model consisting of CDN, TSV, and PDN with decoupling capacitors was used for simulations.

Table 3 shows the dimension and equivalent parasitic values of the CDN, the TSV, and the PDN. For more accurate power integrity estimation, the PDN model includes a voltage regulator module (VRM) providing power to the three-dimensional stacked dies through the PCB, decoupling capacitors, package, and TSVs, which will be further described in the following sections.

|     | Width | Length | Height | R                      | L       | С      | Note                |

|-----|-------|--------|--------|------------------------|---------|--------|---------------------|

| CDN | 1 µm  | 1 mm   | N/A    | 30.1 Ω                 | 1.4 nH  | 192 fF | per mm              |

| TSV | 5 µm  | 5 µm   | 50 µm  | $61.4 \text{ m}\Omega$ | 29.4 pH | 4.0 fF | per TSV             |

| PDN | 10 µm | 5 µm   | 1 µm   | 430 mΩ                 | 22.3 pH | 1.7 pF | per mm <sup>2</sup> |

Table 3Dimension and electrical parasitics of unit components [8].

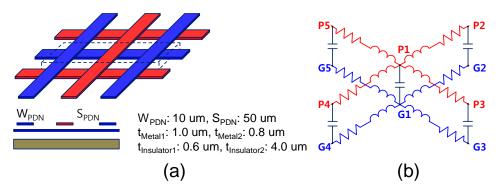

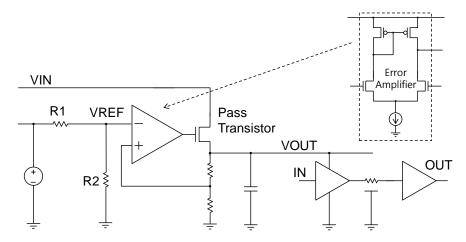

The objective of the PDN is to provide ideal and stable power for the load circuits. To design a PDN, complete modeling from voltage generator to load circuits, as shown in Figure 15 is required. Input impedance from load circuits and voltage fluctuation at the load points have been simulated for the PDN design.

Figure 15 Schematic of the full system power model; (a) conventional model and (b) new model having TSVs and bumps.

An accurate full-system PDN model is critical for the analysis. In this research, the off-chip decoupling parasitics for the PDN model were chosen from [46]. Table 4 shows electrical parasitics of the system-level PDN. From a thermal-effect perspective in PDN design, equivalent series resistance (ESR) parasitics are more temperature dependent than decoupling capacitor parasitics because temperature-dependent resistance. The manufacturing class also describes temperature dependency of capacitances of off-chip decoupling capacitors. The temperature dependency for ESR and capacitance changes the PDN impedances. Resistance and transistors characteristics also have temperature dependency as previously described in Chapter 1.

| Component    | C [F] | R [Ω] | L [H]   | Quantity | Note            |

|--------------|-------|-------|---------|----------|-----------------|

| VRM          | 3.3m  | 60m   | 17n     | 1        |                 |

| Bulk         | 4.7u  | 16m   | 2.1n    | 2        |                 |

| PCB Plane    |       | s-pai | ameters |          |                 |

| Decap        | 100n  | 20m   | 0.8n    | 10       |                 |

| Package      | 1p    | 50m   | 1.5n    |          |                 |

| TSV          | 4.0f  | 61.4m | 29.4p   | 40       |                 |

| Meshed PDN   | 1.7p  | 430m  | 22.3p   | 100      | mm <sup>2</sup> |

| On-die decap | 3p    | 100   | N/A     | 16       | unit            |

Table 4Electrical parasitics of the full-system power delivery network [37].

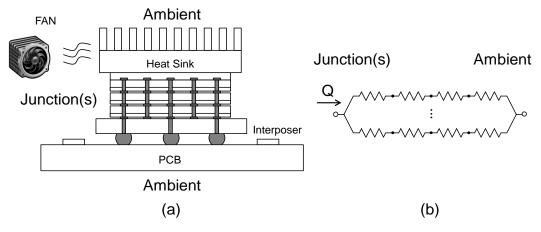

## 2.3.2 Thermal Modeling

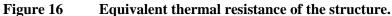

The thermal modeling for electrical systems was initiated with the thermal resistance model shown in Figure 16. The model exploits conduction heat transfer to address thermal dissipation. The heat resistances from heat sources to ambient are in parallel as shown in Figure 16 (b).

In this study, convection condition with air flow from a fan was assumed for the system level cooling. The solver used [13] requires not only electrical excitations in the form of voltage and current sources, but also for thermal that includes power sources and boundary conditions to enable electrical-thermal simulations. The detailed material parameters including thermal conductivity and coefficients are listed in Table 5. Ambient temperature of 25 degree Celsius and fan speed for air convection condition are also shown in the table.

|                     | <b>T</b> 1 <b>*4</b>  | Value       | Nata                   |

|---------------------|-----------------------|-------------|------------------------|

| Ambient temperature | Unit<br>°C            | Value<br>25 | Note<br>T <sub>A</sub> |

| Air convection      | W/(m <sup>2</sup> ·K) | 20          | fan speed              |

| TIM conductivity    | W/(m ·K)              | 1.2         | *                      |

| Under-fill material | W/(m·K)               | 4.3         |                        |

Table 5Material parameters for thermal model.

To analyze the system structure and obtain thermal profiles, a solver using the finite volume method [13] was used. The finite volume formulation assumes nodes surrounded by finite volume cells and applies the finite difference approximation, by solving the voltage distribution equation and heat equation. Therefore, the solver can be used to compute distributions of voltage, current, and temperature with Joule heating effect. For steady-state thermal analysis, heat equation for solid medium can be expressed as:

$$\nabla \cdot [k(x, y, z) \nabla T(x, y, z)] = -P(x, y, z)$$

<sup>(10)</sup>

where k and T are thermal conductivity of medium and temperature distribution. Using Equation (10) based on conduction, the finite volume formulation along with the convection boundary condition can be expressed as in Equation (11) and (12).

$$\frac{T_{i,j} - T_{i,-1j}}{\frac{\Delta x_1}{kd}} + \frac{T_{i,j} - T_{i+1,j}}{\frac{\Delta x_2}{kd}} + \frac{T_{i,j} - T_{i,j+1}}{\frac{\Delta y_1}{kw}} + \frac{T_{i,j} - T_{i,j+1}}{\frac{\Delta y_2}{kw}} = P_{\text{total}}$$

$$k \frac{\partial T}{\partial n}\Big|_{convection} = -h_c (T - T_a)$$

(12)

where  $P_{total}$  is the total heat source in a cell, and  $T_a$  and  $h_c$  are ambient temperature and convention coefficient for the convection boundary, respectively.

The solver is capable of stretching the mesh between multiple regions with multiple materials such as die, interposer, and package by using a non-uniform grid. Figure 17 shows the flow of the electrical-thermal solver used.

Figure 17 Flow of electrical-thermalsolver [13].

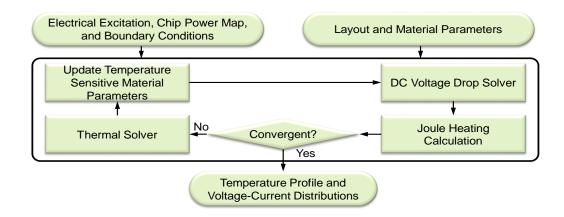

The solver was used to simulate the 3-D configuration with randomly distributed power maps on the two layers (top and bottom die). Total power of the three dies was 50 W which is 20 W for the bottom and the top die respectively, and 10 W for the center die for CDN. The used sample power maps were generated to reflect varying temperature gradient cases. Figure 18 shows the generated power maps for electrical-thermal simulations.

Figure 18 Power maps for thermal simulations.

## 2.4 Electrical-thermal Simulation

## 2.4.1 Simulation Results

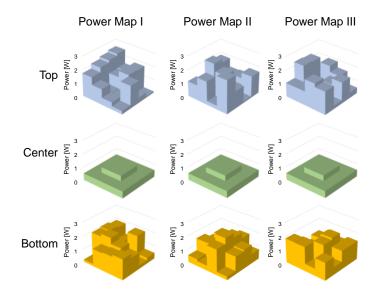

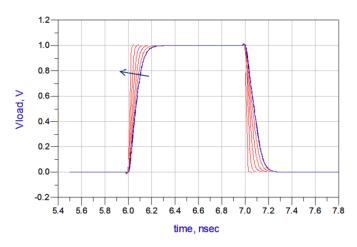

Electrical simulations to estimate clock skew and PDN noise are feasible with electrical-thermal modeling described in the previous section. The operating condition assumption for initial simulation shown in Figure 19 uses 1.1 V operation. The initial results show that the base condition of an ideal PDN has a skew of 30.7 ps. The addition

of PDN and temperature effects increases the skew by 19.2 ps (62.5%) and 143.6 ps (467.8%), respectively. Additional skew of 20.3 ps (68.2%) occurs with temperature gradient superimposed on the PDN. The amount of total skew shown in the results present summation of additional skew portions by PDN noise and thermal [8].

Figure 19 Transient simulation waveforms at clock ends (a) without the PDN model, (b) with the PDN model, (c) with the thermal gradient and (d) with both the PDN model and the temperature gradient [8].

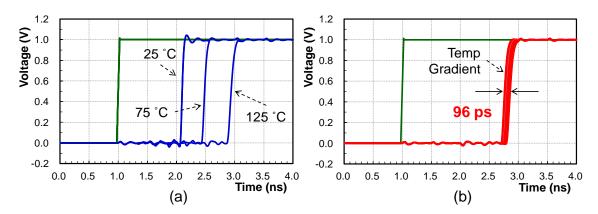

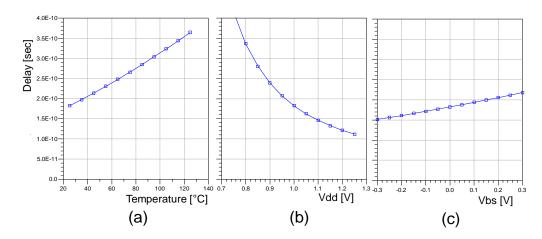

The initial simulation results show the thermal and PDN impact. The simulation condition was further updated for reflecting more recent technology node, as shown in Figure 19. Repeater sizing described in Section 2.3.1 show a reasonable range of skew and thermal variation as shown in Figure 20. Delay of the clock tree varied with the global temperature (25 degrees to 125 degrees), as shown in Figure 20 (a), but thermal-induced skew, shown in Figure 20, caused by temperature gradient in a single die reached up to 96 ps, which is not a negligible number for global skew.

Figure 20 Transient simulation waveforms at clock ends: (a) without the temperature gradient (@ 25°C, 75°C, and 125°C) and (b) with the temperature gradient [37].

## 2.4.2 Analysis of Delay

Capacitor components in CMOS integrated circuits include gate-drain, diffusion, wire, and gate structures [47]. Both intrinsic capacitance and overlap/fringing capacitance need to be analyzed because they are all related with body bias, short channel, drain-induced barrier lowering (DIBL), overlap, and fringing. As Figure 21 indicates, many components of capacitances are present in the buffer and interconnect model. Table 6 shows parasitic capacitance components and values of the model used.

Figure 21 Capacitance of buffer and interconnect model.

| Parasitics             | 5               | Expression                                           | NMOS           | PMOS           | Note                                |

|------------------------|-----------------|------------------------------------------------------|----------------|----------------|-------------------------------------|

| Gate-Drain Cap         | $C_{gd}$        | 2*CGDO*W                                             | 0.23           | 0.61           | Overlap cap                         |

| Diffusion Cap<br>(H-L) | C <sub>db</sub> | k <sub>eq</sub> AD*CJ +<br>K <sub>eqsw</sub> PD*CJSW | 0.66           | 1.50           | Junction cap<br>(Bottom, Side-wall) |

| Diffusion Cap<br>(L-H) | C <sub>db</sub> | k <sub>eq</sub> AD*CJ +<br>K <sub>eqsw</sub> PD*CJSW | 0.90           | 1.15           | Junction cap<br>(Bottom, Side-wall) |

| Wire Cap               | $C_{\rm w}$     | Extraction from layout                               | 0.12           | 0.12           | Negligible                          |

| Gate Cap               | Cg              | $(CGDO+CGSO)^*$<br>W + C <sub>ox</sub> *W*L          | 0.76           | 2.28           |                                     |

| Total Load Cap         | CL              |                                                      | 1.77 /<br>2.01 | 4.51 /<br>4.16 | H-L / L-H                           |

Table 6Capacitance components in a CMOS inverter.

In this research, analytical analysis based on the Elmore delay model has been performed to estimate propagation delay of RC interconnects [47]. It calculates propagation delay based on Equation (14).

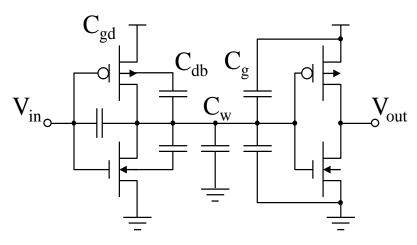

This section shows analytical calculations used to compute the propagation delay. The calculation comes from the Elmore delay model, which has proven to be an efficient method for analyzing RC interconnects [47]. The propagation delay, which is comprised of inverters and interconnects, can be divided into four parts, as shown in Figure 22.

$$t_p = 0.69R_{DR}C_W + 0.69R_{DR}(C_O + C_I) + 0.38R_WC_W + 0.69R_WC_I$$

(13)

Combinations of resistance and capacitance from the inverter and the wire create resistor-capacitor (RC) delay components. The input/output capacitance ( $C_I$  and  $C_O$ ) and wire resistance ( $R_W$ ) have relatively smaller values than the capacitance of the wire ( $C_W$ ) and the resistance of the driver ( $R_{DR}$ ). Therefore, the latter significantly increases delay but it is closely dependent on temperature. The resistance of copper interconnects has a linear

dependency on temperature while the capacitance built on a silicon substrate has negligible dependency and is comparatively stable with temperature variations.

Figure 22 Four parts of the propagation delay of a CDN: (a) an inverter driving wire cap, (b) an inverter, (c) wire delay, and (d) a wire driving an inverter [8].

RC delay of the CDN has been divided into four parts. As shown in Figure 22, each part is defined as a combination of resistance and capacitance with an inverter or a wire. Capacitance of the wire ( $C_W$ ) and resistance of the driver ( $R_{DR}$ ) provide the largest impact on delay, based on the calculations shown in Table 7.

|     | Formula     |                 |                                | Values |       |       | Deley [re] | NT-4-  |

|-----|-------------|-----------------|--------------------------------|--------|-------|-------|------------|--------|

|     | Network     | R               | С                              | Coeff. | R [Ω] | C [F] | Delay [ps] | Note   |

| (a) | Lumped      | R <sub>DR</sub> | Cw                             | 0.69   | 1.25k | 100f  | 86.3       | 82.7 % |

| (b) | Lumped      | R <sub>DR</sub> | C <sub>0</sub> +C <sub>I</sub> | 0.69   | 1.25k | 20f   | 17.3       | 16.6 % |

| (c) | Distributed | Rw              | Cw                             | 0.38   | 15    | 100f  | 0.6        | 0.6 %  |

| (d) | Lumped      | Rw              | CI                             | 0.69   | 15    | 10f   | 0.2        | 0.2 %  |

Table 7Delay values with buffers and wire [8].

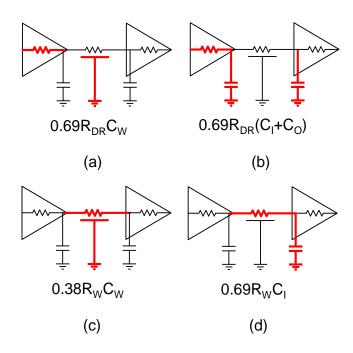

The values for the delay shown in Table 7 also vary with temperature. Figure 23 shows temperature dependency of the four parts shown above. Resistance of copper has a linear dependency on temperature with a coefficient of 0.0039 per degree Celsius. However, thermal dependency of capacitance built on a silicon substrate is negligible and the value is very stable with a small temperature coefficient. From the figure it can be concluded that RC delay has a linear relationship with temperature.

Figure 23 Temperature effect on delay [8].

Temperature coefficient of interconnect resistance and lumped electro-thermal modeling with thermal effects have been discussed in [48]. The formula shown in [48] has thermal variation for interconnect. In this research, the formula is extended to include driver resistance along with capacitance of the buffer, as shown in Equation (15).

Figure 24 Cascaded buffers and interconnects [8].

Therefore, Equation (15) provides a delay (D) for the clock network comprised of cascaded buffers and interconnects. Equations (16) and (17) capture the effects of temperature on buffers and interconnects, respectively. In Equation (15), the constants for the RC delay are 0.69 ("a" for lumped networks) and 0.38 ("b" for distributed networks), respectively, for calculating the propagation delay [39].

$$D = a \sum_{i=1}^{n} R_{DR,i} \left( C_{O,i} + C_{W,i} + C_{I,i} \right) + \sum_{i=1}^{n} R_{W,i} \left( b C_{W,i} + a C_{I,i} \right)$$

(14)

$$R_{DR,k} = R_{DR,0} \left( 1 + \beta_{DR} \left( T_k - T_0 \right) \right)$$

(15)

$$R_{W,k} = R_{W,0} \left( 1 + \beta_W (T_k - T_0) \right)$$

(16)

Figure 25 A clock tree with a temperature gradient [37].

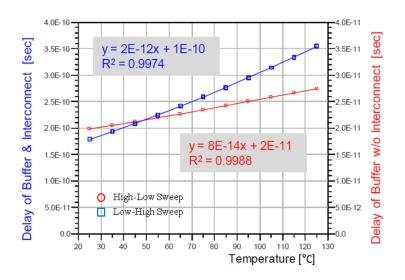

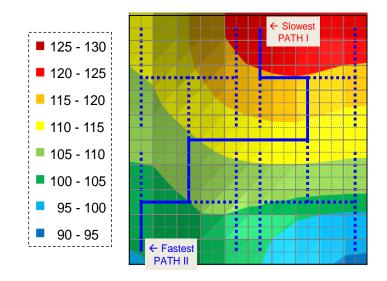

Thermal simulation provides a temperature profile, as shown in Figure 25, which can impact the CDN based on location. The simulated temperature profile is superimposed on the electrical model to generate a delay profile. Figure 26 (a) shows temperature along with the CDN position from center to four edges. Equation (15) captures temperature dependency. Using Equation (15), correlations between calculations and simulations from the previous section are shown in Figure 26 (b).

Figure 26 (a) The temperature profile for delay calculation. (b) Comparison of path delay with calculation [34].

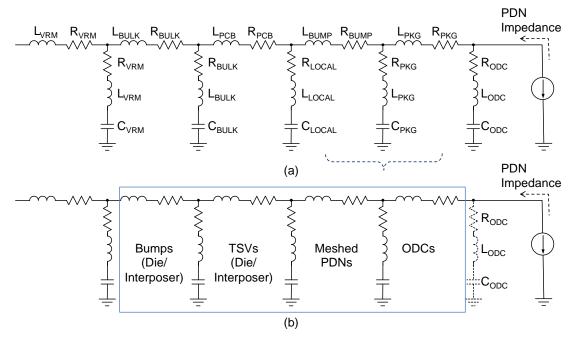

#### **2.5 Thermal Impact on Power Delivery Network Design**

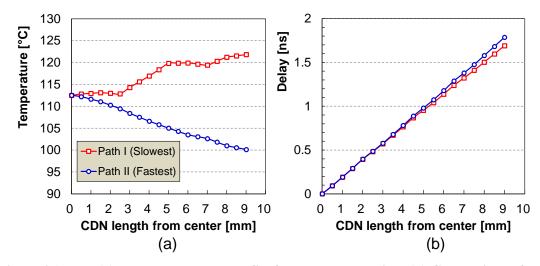

The focus of this chapter is on the impact of temperature effect on power integrity (PI). PI estimates the quality of power delivery, including the non-ideal effects of power distribution network (PDN). The goal of PDN design is to lower PDN impedance below a target value, also called as target impedance. In real applications the actual impedance is increased by parasitics such as resistance and inductance at higher operating frequencies [49], as shown in Figure 27. As discussed in the previous chapter, because of higher temperature, increase of ohmic loss (ESR; Equivalent Series Resistance) increases impedance of the on-chip decoupling capacitors. Therefore, variations of resistance are critical for the design of the power distribution network.

Figure 27 Target impedance and PDN response; modified from [49].

For PDN simulation, both frequency and time domain simulations were performed for calculating impedance profile and voltage transient, where the same simulation flow discussed in the previous chapter was used. With the same operating condition described in the previous chapter, a clock signal operating at 500 MHz with supply voltage of 1.0 V was used for transient simulations using a PDN model connected to an off-chip voltage regulator module. The results of the simulations illustrate that the PDN impedance increases as the temperature rises.

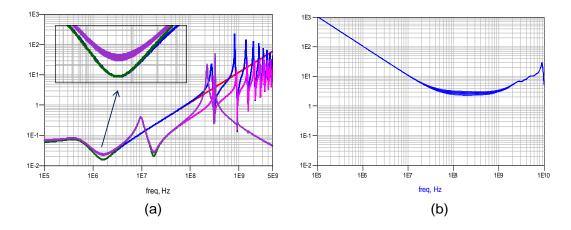

Figure 28 Impedance of PDN with temperature variation; (a) off-chip and (b) on-chip.

Delay variation caused by temperature gradient in 3-D ICs were investigated in the previous section. PDN impedance also has a linear dependency with temperature because the resistance of PDN changes linearly with temperature. Resistance of PDN affects ESR (Equivalent Series Resistance) of a full PDN. The PDN impedance of the full PDN model in Figure 28 (a) shows variation with temperature. The lowest point in impedance curve is determined by the ESR of decoupling capacitors which is affected by temperature. It is important to note that the ESR is dependent upon not only temperature gradient but chip global temperature, as compared to the skew effect which is affected by temperature gradient condition only.

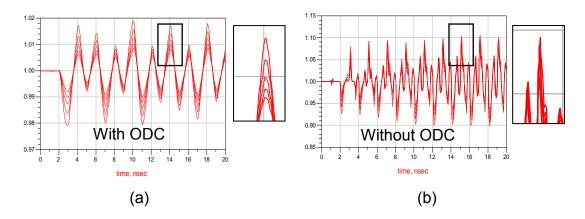

In this section, temperature dependency of electrical resistance is the main focus. On-chip PDN and on-chip decoupling capacitors (ODCs) have larger series resistance as compared to decoupling capacitor in the package. A larger number of off-chip decoupling capacitors, such as Bulk or SMT capacitors, are used for achieving small series inductance and resistance. However, the absolute value of ESR of ODC is much larger and the number of ODC is often limited for overcoming the ESR values. Therefore, temperature dependency of ODC's ESR is more dominant than off-chip decoupling capacitors, as shown in Figure 28 (b). Variations of simulated impedances illustrate that ODCs are operating in the ESR dominant range. Transient simulation results in Figure 29 show how the effect ESR on noise waveform. The two waveforms (with and without ODC) show a different amount of noise, but they show different temperature dependency.

Figure 29 PDN noise with temperature variation (a) With ODC. (b) Without ODC.

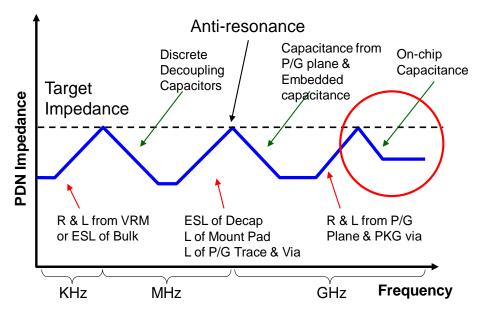

## 2.5.1 On-Chip Decoupling Capacitors

Important elements in a PDN design are the various types of decoupling capacitors (off-chip or on-chip) that can be used. Traditionally, off-chip decoupling capacitors have been used to optimize PDN designs. By contrast, on-chip decoupling capacitors are mainly design-dependent because multiple types of ODCs are available [50]. The various types of ODCs have implementation variations [51]. In this chapter, the effects of temperature on PDN design are estimated and quantified since thermal variations of PDN using various decoupling capacitors have not yet been fully analyzed in the open literature [52].

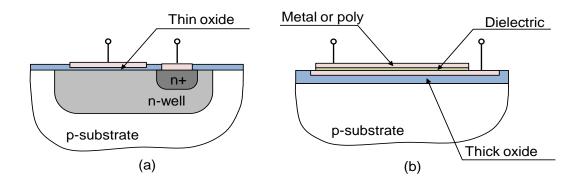

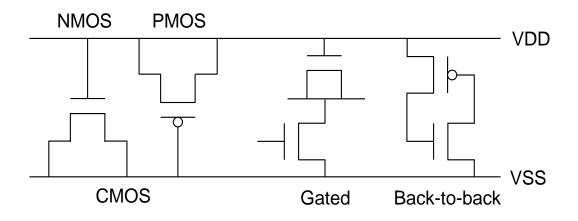

In PDN design, decoupling capacitors are used to lower impedance looking into the power supply. In this chapter, on-chip decoupling capacitors are the main focus because ODCs are more resistance (ESR) dominant because of lower inductance. The values of ESR mainly depend on the types of ODC and their implementation. Regardless of the implementation of ODCs, the values of resistance are mainly dependent on temperature. This section discusses the various types of ODCs, their parasitics for various structures, for example metal-oxide semiconductor (MOS), metal-insulator-metal (MIM), or poly-insulator-poly (PIP) [51], as shown in Figure 30.

The most widely used types of ODCs are MOS-based capacitors because they are fully compatible with CMOS circuits and have larger capacitance with simpler implementation. With the trend toward low power consumption, the leakage of MOS capacitors becomes an important design parameter. The leakage decreases with increase in oxide thickness. Thus, the thickness of a MOS capacitor can be optimized for less leakage with the use of thin- and thick-oxide capacitors [53]. In addition, gated- and activedecoupling capacitors have been presented in the open literature to reduce the leakage current and power-ground noise [54], [55], and [56]. Figure 31 shows schematics of the various MOS capacitors.

Figure 31 Variations of the MOS capacitor [52].

Other types such as MIM and PIP are also available for ODCs, as shown in Table 8. MIM capacitors provide precise capacitance with a relatively lower temperature coefficient [57], and larger capacitance is achievable with a higher permittivity of the dielectric [58]. Deep-trench capacitors with a vertical structure are also available for ODCs using TSV technology [59]. In contrast to MIM and PIP capacitors, various design variations of MOS capacitors have been presented in [50]. The purpose of these approaches is for improved area-efficiency and power-efficiency and less leakage. Optimization of design, including number of fingers, is feasible by modifying the layout of decoupling capacitors [60], with various design implementations and verifications presented in [61].

| Туре      | Description                 |

|-----------|-----------------------------|

| NMOS      | NMOS decap                  |

| NMOS_TH   | NMOS with thick oxide       |

| NMOS_LVT  | NMOS with low Vt            |

| NMOS_ACC  | NMOS with accumulation mode |

| PMOS      | PMOS decap                  |

| CMOS      | NMOS + PMOS                 |

| NMOS_GATE | Gated NMOS decap            |

| CMOS_B2B  | Back-to-back decap          |

| MIM       | MIM decap                   |

| PIP       | PIP decap                   |

Table 8Types of on-chip decoupling capacitors (ODCs).

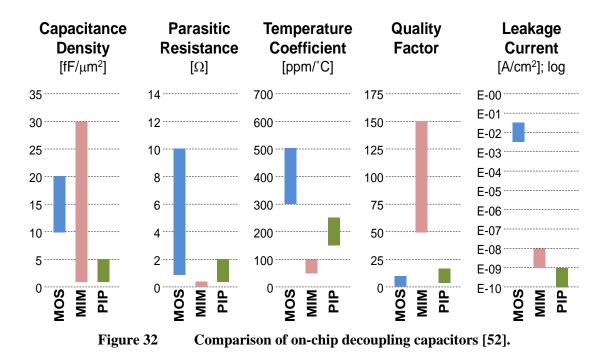

Previous studies have provided modeling of parasitic resistance in MOS-based decoupling capacitors [62] which included gate-oxide leakage [63] and substrate effect [64]. Layout of decoupling capacitors determines detailed values of their parasitics. However, the parasitics are also determined by the structure of decoupling capacitors. Characteristics of materials provide various range of parasitics, as shown in [51]. Figure 32 shows a comparison of parasitics of the three types of decoupling capacitors, namely MOS, MIM, and PIP.

The three types of MOS decoupling capacitors have been chosen in this section because MOS-based capacitors have variations in capacitance density and leakage current. In addition, MIM type capacitor was also chosen for comparison, because MIM and PIP have similar structure. The values of the parasitics, such as capacitance, ESR [65], and temperature coefficients [51], were chosen to estimate the PDN response. Parasitics have various resistance and temperature dependencies. Each type of decoupling capacitor has capacitance density and parasitic resistance, so impedance of decoupling capacitors varies with the type used.

Using the temperature variations of the ODCs, the temperature-aware PDN design for 3-D ICs and systems was investigated. Temperature-aware power integrity simulations were used to quantify the degradation caused by high temperature. Sensitivity analysis was used to verify the impact of various components such as meshed PDN, TSVs, and on-chip decoupling capacitors in 3-D structures.

## 2.5.2 PDN Simulation with Temperature Effects

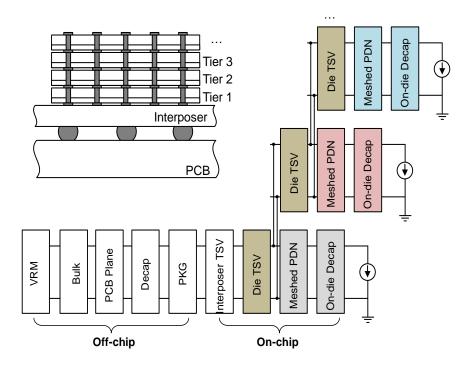

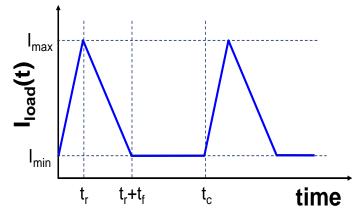

To simulate the PDN impedance and voltage transient, a 3-D PDN model using segmentation method [66] was constructed, as shown in Figure 33. All components of the model are segmented and cascaded with parasitics included, as presented in the previous section. The parasitics of decoupling capacitors and current excitation points are distributed across the entire chip area using the temperature profile in [8].

Figure 33 Block diagram of a 3-D PDN.

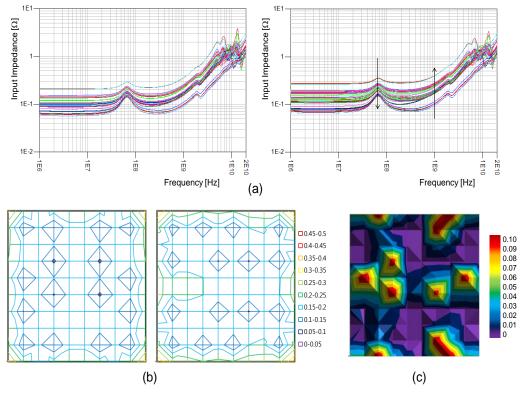

In addition to signal integrity being affected by temperature, power integrity, especially impedance of the PDN is affected by temperature and gradients as well, as shown in Figure 34 (a). Variations in impedance plot represent the location of probe points across a die. Figure 34 (b) shows impedances at probe points modeled at 1 GHz. Figure 34 (c) also illustrates the difference of impedance measured at a frequency of 1 GHz. The maximum difference is  $\leq 0.1$  ohm, which is caused by temperature changes.

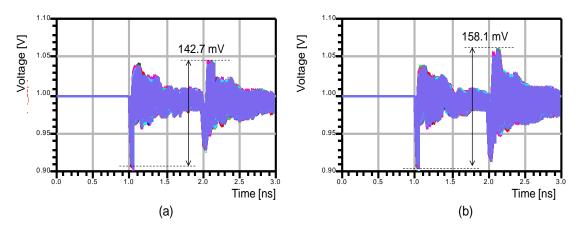

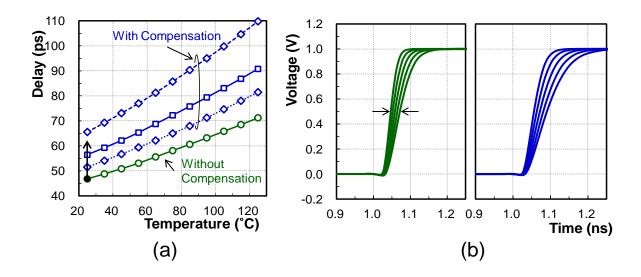

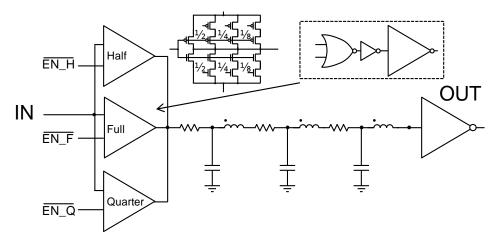

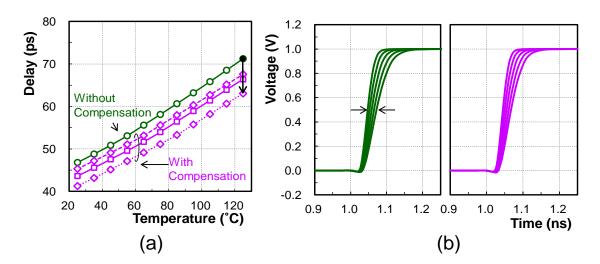

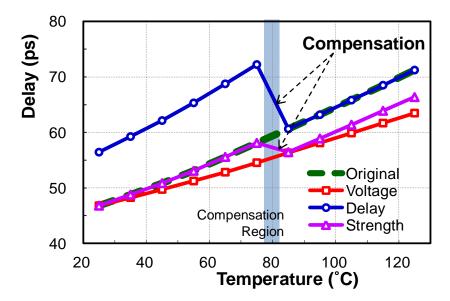

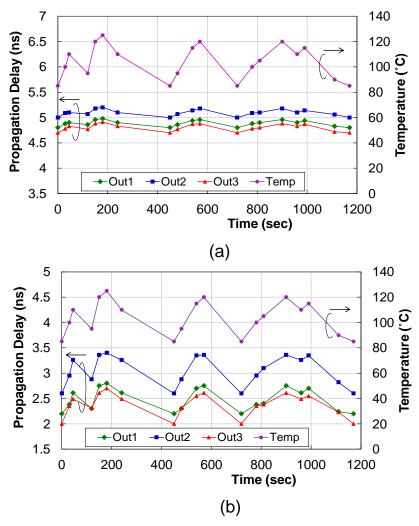

Figure 34 Simulated PDN impedances with and without temperature gradient: (a) impedance, (b) impedance distribution measured at 1 GHz, and (c) impedance difference measured at 1 GHz [52].