# A Comprehensive Study of Safe-Operating-Area, Biasing Constraints, and Breakdown in Advanced SiGe HBTs

A Thesis Presented to The Academic Faculty

by

## **Curtis M. Grens**

In Partial Fulfillment of the Requirements for the Degree Master of Science in School of Electrical and Computer Engineering

> Georgia Institute of Technology August 2005

# A Comprehensive Study of Safe-Operating-Area, Biasing Constraints, and Breakdown in Advanced SiGe HBTs

Approved by:

Professor John D. Cressler, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Professor Emmanouil Tentzeris School of Electrical and Computer Engineering *Georgia Institute of Technology*

Professor John Papapolymerou School of Electrical and Computer Engineering *Georgia Institute of Technology*

Date Approved: May 6, 2005

## ACKNOWLEDGEMENTS

I am grateful to Dr. John D. Cressler for his patience, guidance, and support throughout my master's program. His passion for research and teaching is truly inspirational, and it is a pleasure working under his leadership in such an exciting field. I would also like to thank the other members of my thesis advisory committee, Dr. Emmanouil Tentzeris and Dr. John Papapolymerou.

I would also like to acknowledge my fellow graduate students for their assistance this work and helpful answers to numerous questions. Extra thanks to Joel Andrews, Tianbing Chen, Jon Comeau, and Qingqing Liang.

I am grateful for the support of IBM Microelectronics, Samsung Electronics, and the Georgia Electronic Design Center at Georgia Tech. In addition, I wish to thank Alvin J. Joseph and the IBM SiGe team for their contributions.

Finally, I would like to thank my family and friends, and most of all my beautiful wife, Nina, for her support, encouragement, and understanding.

# TABLE OF CONTENTS

| AC  | ACKNOWLEDGEMENTS |         |                                              |     |

|-----|------------------|---------|----------------------------------------------|-----|

| LIS | T OF             | TABL    | ES                                           | vi  |

| LIS | T OF             | FIGUI   | RES                                          | vii |

| SUI | ММА              | RY.     |                                              | xi  |

| I   | INT              | RODU    | CTION                                        | 1   |

|     | 1.1              | Motiva  | ation                                        | 1   |

|     | 1.2              | SiGe H  | IBT BiCMOS Technology                        | 3   |

|     | 1.3              | Device  | Physics of SiGe HBTs                         | 5   |

|     | 1.4              | Breako  | lown Fundamentals                            | 10  |

|     | 1.5              | Summ    | ary                                          | 15  |

| II  | BRE              | EAKDO   | WN CHARACTERISTICS IN SIGE HBTS              | 16  |

|     | 2.1              | Introdu | uction                                       | 16  |

|     | 2.2              | Backg   | round                                        | 17  |

|     |                  | 2.2.1   | Pinch-in Effects                             | 17  |

|     |                  | 2.2.2   | Common-emitter bias with forced base current | 21  |

|     |                  | 2.2.3   | Common-emitter bias with forced base voltage | 22  |

|     |                  | 2.2.4   | Common-base bias with forced emitter current | 28  |

|     | 2.3              | Experi  | mental Characterization                      | 31  |

|     |                  | 2.3.1   | Experiment                                   | 31  |

|     |                  | 2.3.2   | High Performance Results                     | 31  |

|     |                  | 2.3.3   | High Breakdown Results                       | 36  |

|     |                  | 2.3.4   | Geometry Dependence                          | 40  |

|     | 2.4              | Summ    | ary                                          | 43  |

| III | IMP              | PLICAT  | TIONS OF OPERATING VOLTAGE CONSTRAINTS       | 45  |

|     | 3.1              | Introdu | uction                                       | 45  |

|    | 3.2  | Model   | ing of Breakdown Effects    | 46 |

|----|------|---------|-----------------------------|----|

|    |      | 3.2.1   | Six-Transistor Model        | 46 |

|    |      | 3.2.2   | Model Perturbation          | 48 |

|    | 3.3  | Circuit | t Implications              | 53 |

|    |      | 3.3.1   | Experiment                  | 53 |

|    |      | 3.3.2   | Results and Discussion      | 53 |

|    |      | 3.3.3   | Further Circuit Simulations | 54 |

|    | 3.4  | Device  | e Reliability               | 56 |

|    |      | 3.4.1   | Experiment                  | 57 |

|    |      | 3.4.2   | Results and Discussion      | 58 |

|    | 3.5  | Self-H  | leating                     | 59 |

|    |      | 3.5.1   | Experiment                  | 60 |

|    |      | 3.5.2   | Results and Discussion      | 61 |

|    | 3.6  | Therm   | al Coupling                 | 64 |

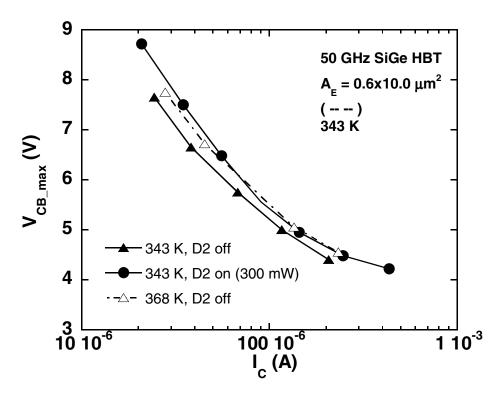

|    |      | 3.6.1   | Theory                      | 66 |

|    |      | 3.6.2   | Experiment                  | 66 |

|    |      | 3.6.3   | Results and Discussion      | 67 |

|    |      | 3.6.4   | Breakdown Implications      | 72 |

|    | 3.7  | Summ    | ary                         | 73 |

| IV | CON  | ICLUS   | ION                         | 75 |

|    | 4.1  | Conclu  | usion                       | 75 |

|    | 4.2  | Future  | Directions                  | 76 |

| RE | FERE | NCES    |                             | 78 |

|    |      |         |                             |    |

# LIST OF TABLES

| 1 | Characteristic device parameters for three SiGe BiCMOS technology genera-<br>tions              | 5  |

|---|-------------------------------------------------------------------------------------------------|----|

| 2 | Relevant breakdown parameters for HB devices for three SiGe BiCMOS tech-<br>nology generations. | 36 |

# **LIST OF FIGURES**

| 1  | Vertical SIMS profile showing doping concentration and Ge profile within a first generation SiGe HBT.                                          | 3  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | A schematic device cross-section of a third generation BiCMOS SiGe HBT                                                                         | 4  |

| 3  | Energy band diagram for a graded base SiGe HBT and a Si BJT                                                                                    | 7  |

| 4  | Representative Gummel plot for a SiGe HBT as compared to a Si BJT                                                                              | 8  |

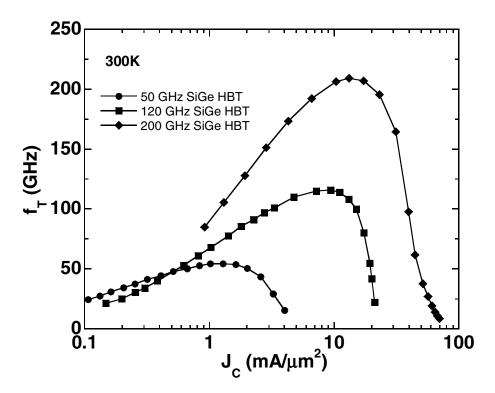

| 5  | Cutoff frequency as a function of collector current density for three generations of SiGe HBT BiCMOS technology.                               | 11 |

| 6  | Schematic illustration of the avalanche multiplication process in a reversed bias p-n junction.                                                | 11 |

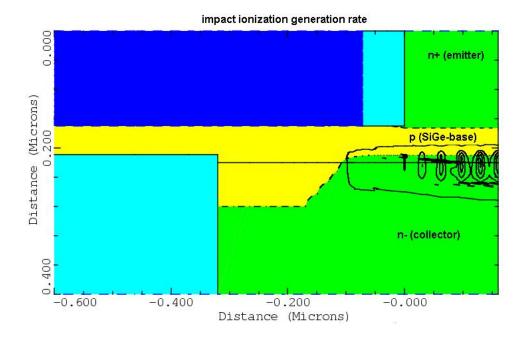

| 7  | MEDICI device simulation of a 120 GHz SiGe HBT showing contours of im-<br>pact ionization generation rate with respect to the device profile.  | 12 |

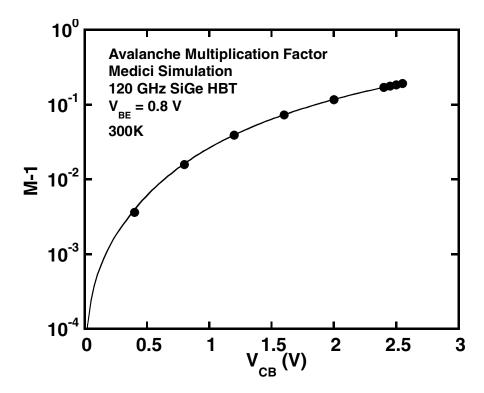

| 8  | MEDICI device simulation of a 120 GHz SiGe HBT showing $M - 1$ as a function of collector voltage.                                             | 13 |

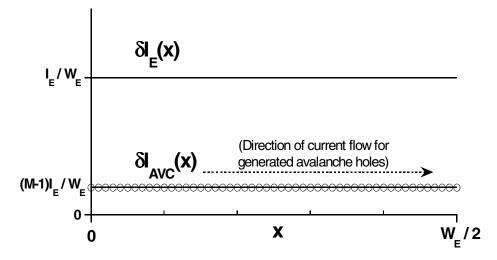

| 9  | Simplified depiction of injected current $(A/\mu m)$ and avalanche generation as a function of position within the device.                     | 17 |

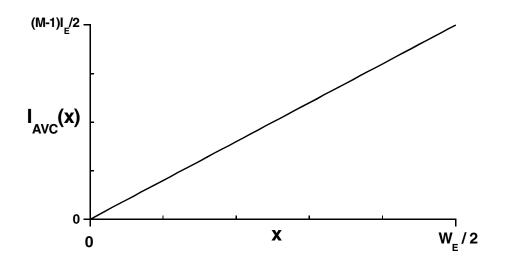

| 10 | Simplified depiction of avalanche current (A) as a function of position within the active device.                                              | 18 |

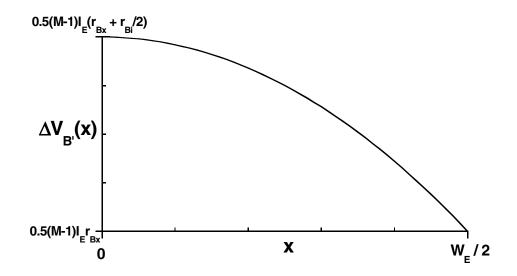

| 11 | Simplified depiction of intrinsic base potential (V) as a function of position within the active device.                                       | 19 |

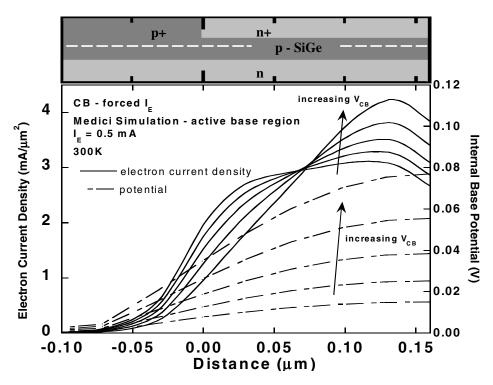

| 12 | MEDICI simulation of a 120 GHz SiGe HBT showing the intrinsic potential distribution and onset of current constriction within the neutral base | 21 |

| 13 | CE - forced $I_B$ output characteristic with BV thresholds indicated                                                                           | 22 |

| 14 | CE - forced $V_{BE}$ output characteristic with associated BV thresholds                                                                       | 25 |

| 15 | Reverse base current and emitter current characteristics resulting from CE - forced $V_{BE}$ measurement.                                      | 26 |

| 16 | CE - forced $V_{BE}$ output characteristic with $I_C$ swept and $V_{CE}$ measured                                                              | 26 |

| 17 | $V_{BE}$ and $I_B$ characteristics from CB - forced $I_E$ measurements at low and high injection.                                              | 28 |

| 18 | CB - forced $I_E$ output characteristic with associated BV thresholds                                                                          | 30 |

| 19 | $V_{BE}$ characteristics from CB - forced $I_E$ measurements at low and high injection for three generations of SiGe HBTs.                     | 31 |

| 20 | M - 1 characteristics for three generations of high performance SiGe HBT technology.                                                                                                                                                                 | 32 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

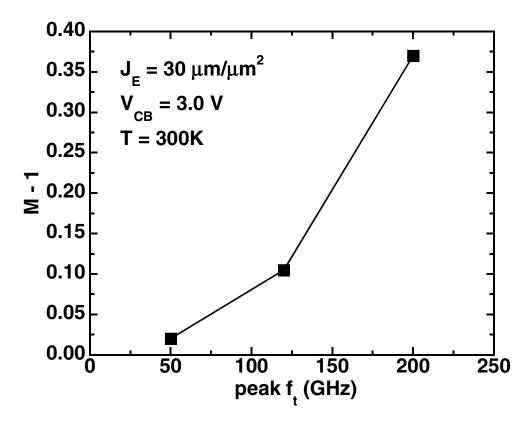

| 21 | $M - 1$ at constant $V_{CB} = 3$ V as a function of SiGe HBT technology generation.                                                                                                                                                                  | 33 |

| 22 | CE - forced $I_B$ BV thresholds for three generations of SiGe HBT technology.<br>An external resistance on the base terminal is varied between 0 $\Omega$ (CE operation with fixed $V_{BE}$ drive) and 1 M $\Omega$ for the 50 GHz peak $f_T$ device | 34 |

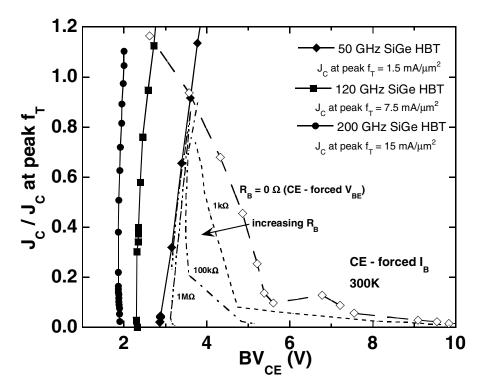

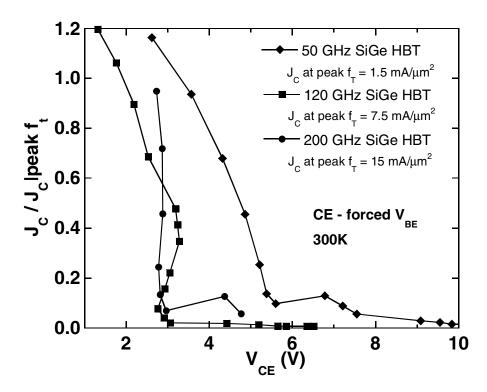

| 23 | CE - forced $V_{BE}$ BV thresholds for three generations of SiGe HBT technology.                                                                                                                                                                     | 34 |

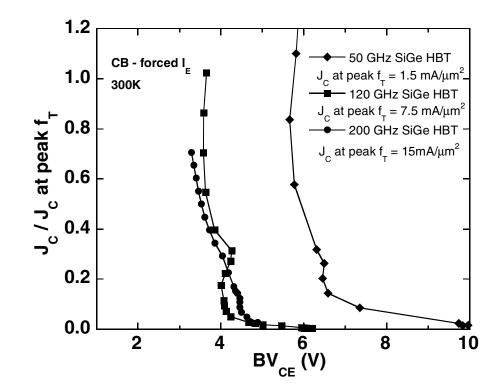

| 24 | CB - forced $I_E$ BV threshold for three generations of SiGe HBT technology                                                                                                                                                                          | 35 |

| 25 | Comparison between measured and calculated $CB-I_E$ pinch-in instabilities                                                                                                                                                                           | 36 |

| 26 | M - 1 characteristics for HB devices from three generations of SiGe HBT technology.                                                                                                                                                                  | 37 |

| 27 | CE - forced $I_B$ BV threshold for HB devices from three generations of SiGe HBT technology.                                                                                                                                                         | 38 |

| 28 | CE - forced $V_{BE}$ BV threshold for HB devices from three generations of SiGe HBT technology.                                                                                                                                                      | 38 |

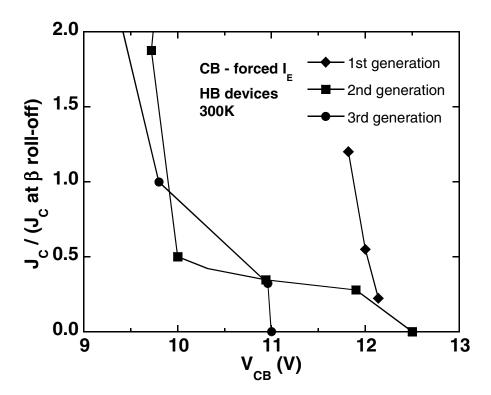

| 29 | CB - forced $I_E$ BV threshold for HB devices from three generations of SiGe HBT technology.                                                                                                                                                         | 39 |

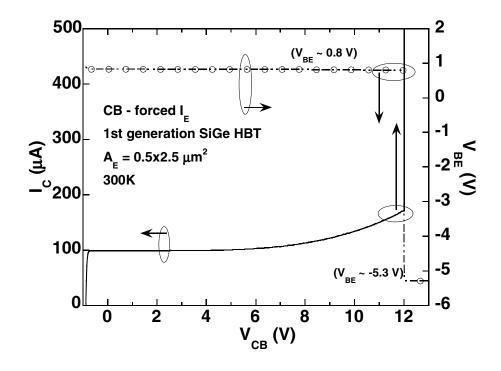

| 30 | $I_C$ and $V_{BE}$ characteristics from a 1st generation HB SiGe HBT operating in the $CB$ - $I_E$ configuration.                                                                                                                                    | 40 |

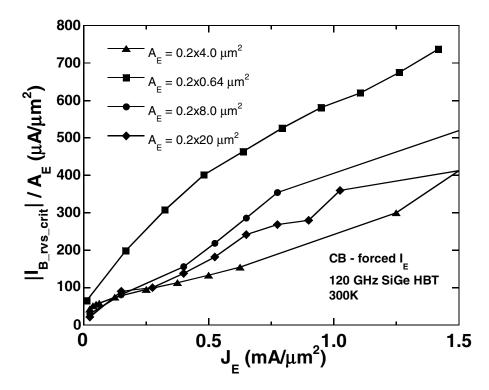

| 31 | Critical reverse base current (scaled by $A_E$ ) as a function of $J_E$ for several geometries of 120 GHz SiGe HBTs.                                                                                                                                 | 41 |

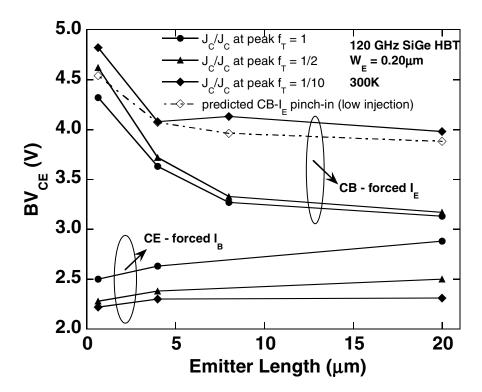

| 32 | BV vs. emitter length for $CE$ - $I_B$ and $CB$ - $I_E$ modes at low, medium, and high bias. For low injection $CB$ - $I_E$ , the critical $V_{CB}$ predicted by Equation (27) is also shown.                                                        | 42 |

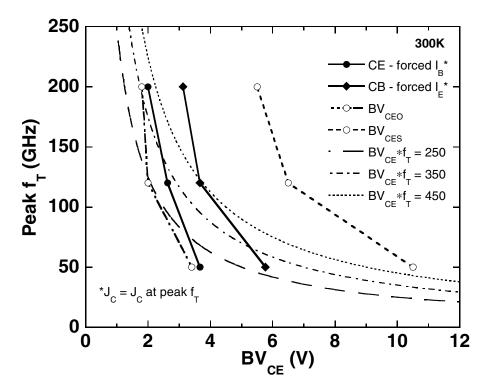

| 33 | Peak $f_T$ vs. BV for three generations of SiGe HBT technology. Contours of constant BV- $f_T$ products are also shown.                                                                                                                              | 43 |

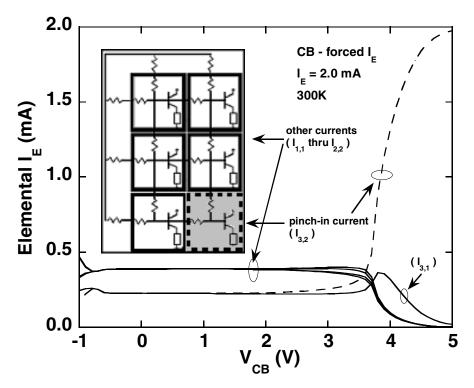

| 34 | Current constriction in six-transistor VBIC model during CB - forced $I_E$ oper-<br>ation.                                                                                                                                                           | 46 |

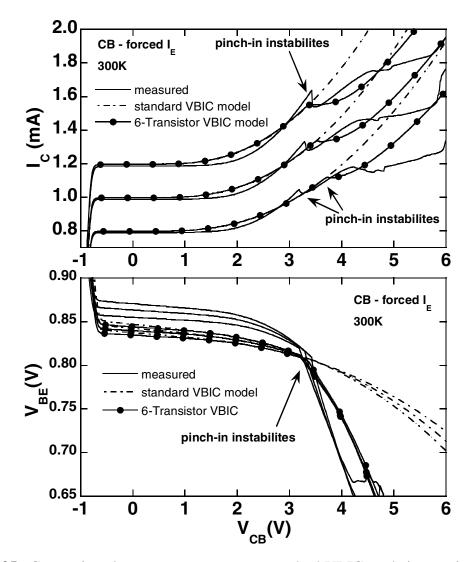

| 35 | Comparison between measurement, standard VBIC, and six-transistor VBIC models.                                                                                                                                                                       | 47 |

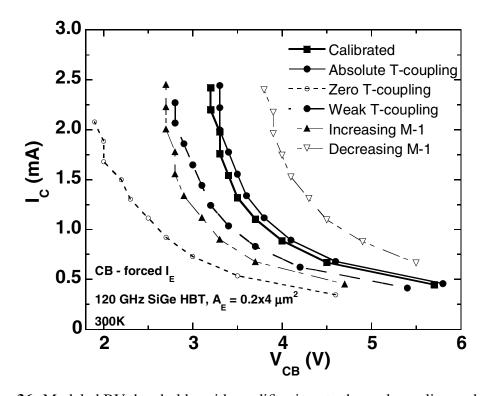

| 36 | Modeled BV thresholds, with modifications to thermal coupling and avalanche multiplication factors in six-transistor model.                                                                                                                          | 49 |

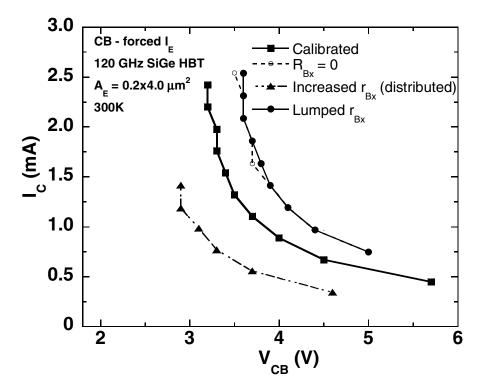

| 37 | Modeled BV thresholds, with modifications to extrinsic base resistance in six-transistor model.                                                                                                                                                      | 49 |

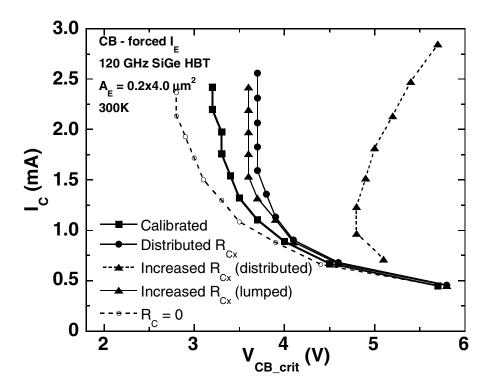

| 38 | Modeled BV thresholds, with modifications to thermal coupling and avalanche multiplication factors in six-transistor model.                                                                                                                                          | 51 |

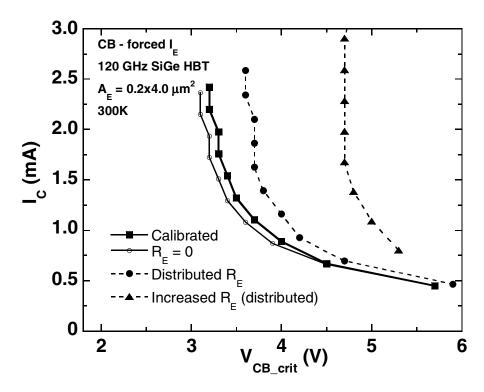

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 39 | Modeled BV thresholds, with modifications to emitter resistance in six-transistor model.                                                                                                                                                                             | 52 |

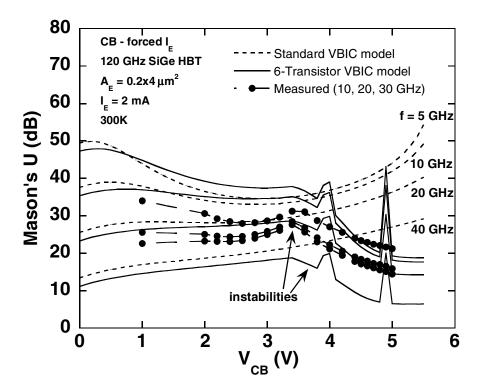

| 40 | Mason's U vs. $V_{CB}$ extracted at various frequencies for the standard VBIC and six-transistor VBIC models.                                                                                                                                                        | 53 |

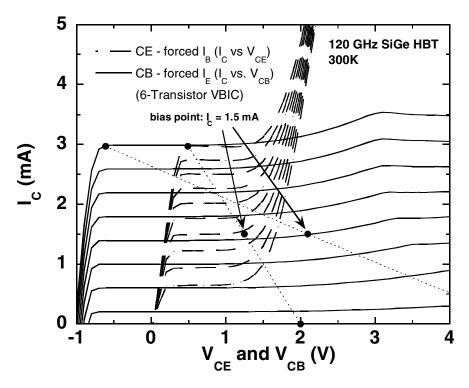

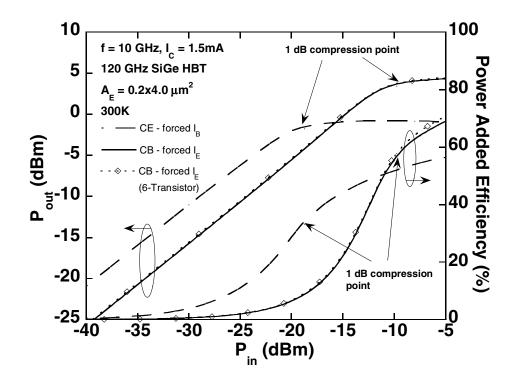

| 41 | Modeled <i>dc</i> characteristics and <i>dc</i> bias points associated with class A large signal CE and CB operation.                                                                                                                                                | 54 |

| 42 | Modeled output power and PAE vs. input power for CE and CB class A operation.                                                                                                                                                                                        | 55 |

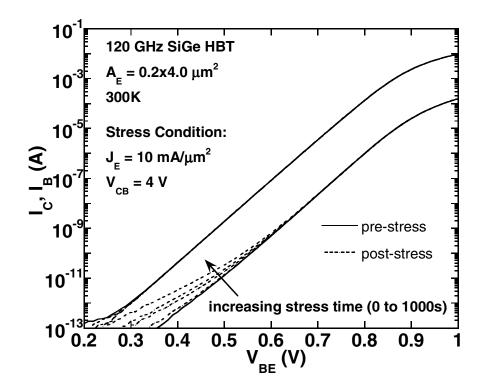

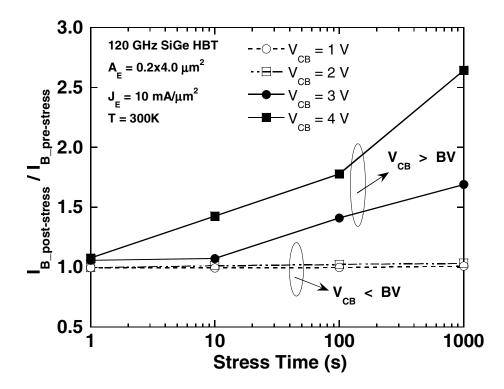

| 43 | Forward Gummel characteristic pre- and post- stressing at $J_E = 10 \text{ mA}/\mu\text{m}^2$<br>and $V_{CB} = 4 \text{ V}$ for various stress times.                                                                                                                | 57 |

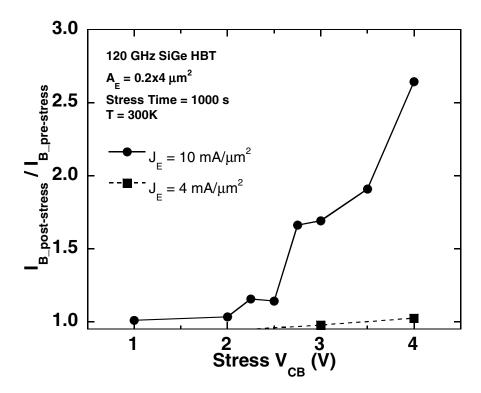

| 44 | Base current degradation vs. time for various levels of stress $V_{CB}$                                                                                                                                                                                              | 58 |

| 45 | Base current degradation as a function of stress $V_{CB}$                                                                                                                                                                                                            | 59 |

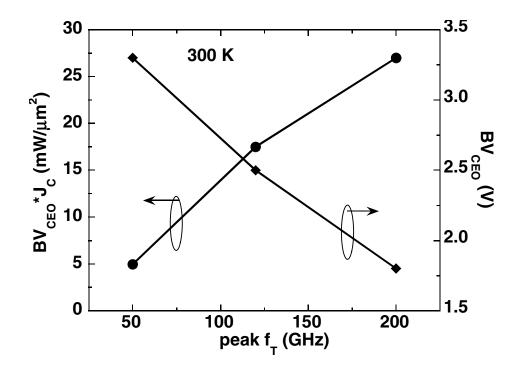

| 46 | Breakdown voltage, current density product vs. peak $f_T$ in various SiGe device technologies.                                                                                                                                                                       | 60 |

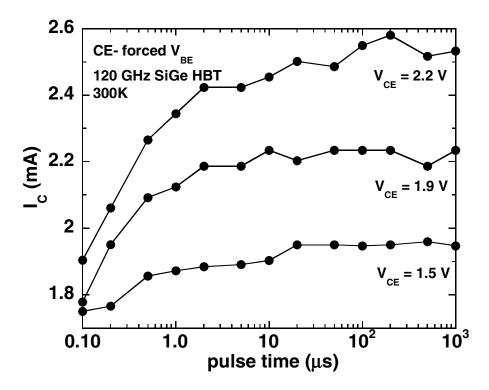

| 47 | $I_C$ at fixed $V_{BE}$ (0.84 V) and $V_{CE}$ as a function of time                                                                                                                                                                                                  | 61 |

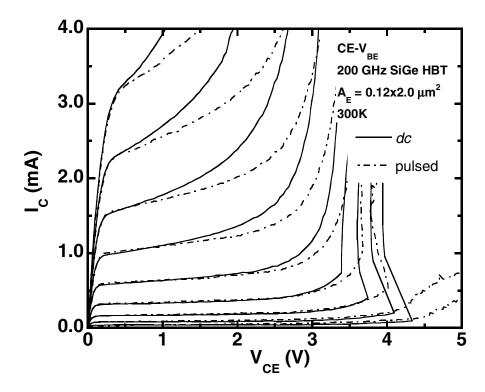

| 48 | Comparison between $dc$ and pulsed measurements during CE - forced $V_{BE}$ operation for a 200 GHz SiGe HBT.                                                                                                                                                        | 62 |

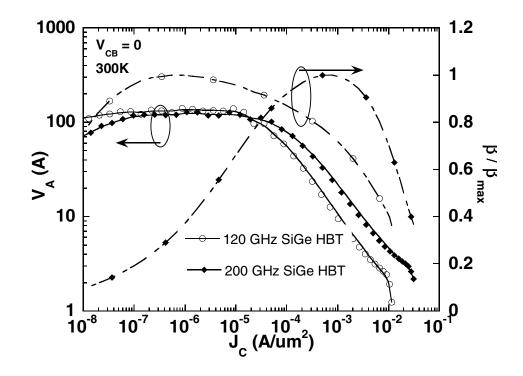

| 49 | Current gain and Early voltage characteristics versus $J_C$ during CE - forced $V_{BE}$ operation for 120 and 200 GHz SiGe HBTs                                                                                                                                      | 63 |

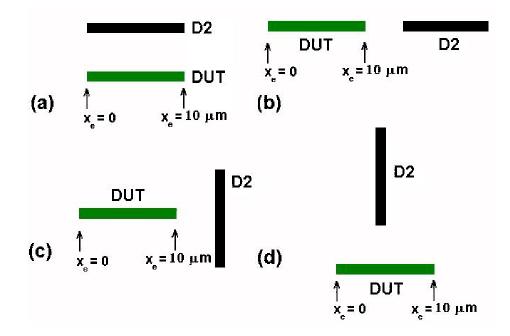

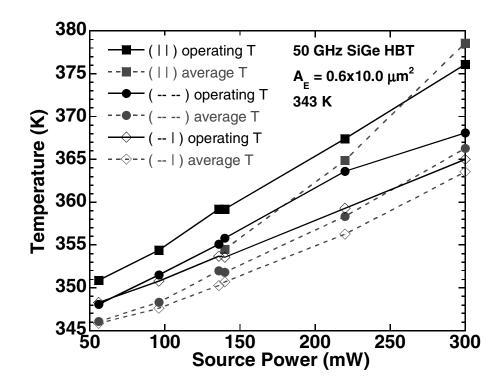

| 50 | Four measured transistor orientations, with the measured device shown in green<br>and heat source device shown in black. In subsequent plots, these orientations<br>will be referred to as a) $  , b), c) -  , d)  -$ , where the left device is the<br>measured one | 65 |

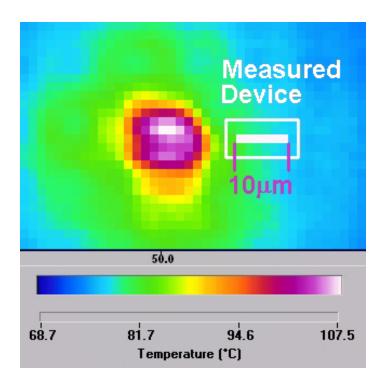

| 51 | Infrared picture of the heat source transistor and the resultant thermal distribu-<br>tion that is seen across the measured device                                                                                                                                   | 65 |

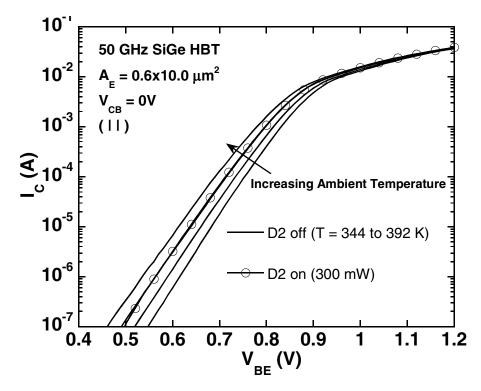

| 52 | Gummel characteristics on measured device at different ambient temperatures.<br>The characteristic for the measured device operating with the heat source on is<br>superimposed.                                                                                     | 67 |

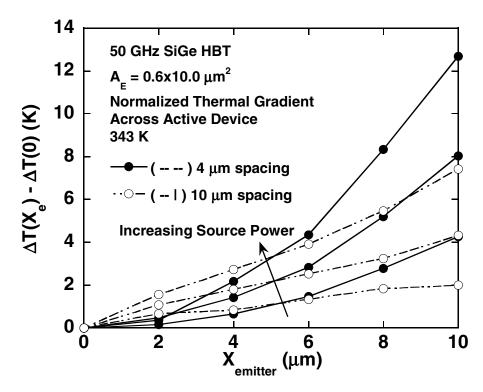

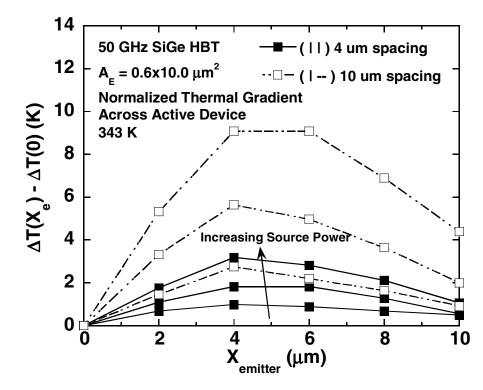

| 53 | Temperature variations across horizontal measured devices normalized to the minimum temperature rise per configuration.                                                                                                                                              | 68 |

| 54 | Temperature variations across vertical measured devices normalized to the min-<br>imum temperature rise per configuration                                                                                                                                            | 68 |

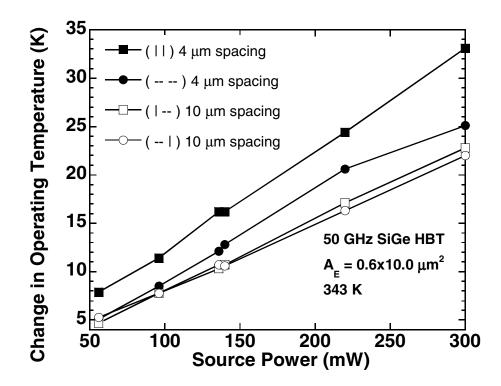

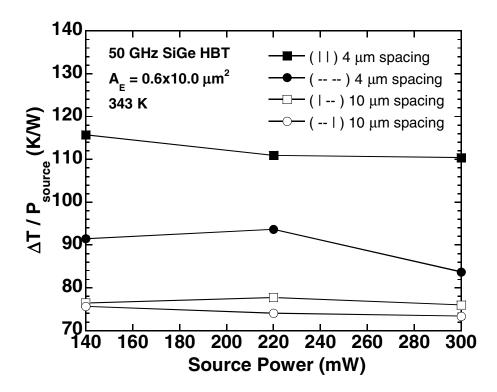

| 55 | Average infrared measured temperature change vs. heat source power                                                                                                                                                                                                   | 69 |

| 56 | Infrared temperature measured variation independence across heat source power.                                                                                                                | 70 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 57 | Average infrared measured temperature and electrically extracted temperature of the measured devices.                                                                                         | 71 |

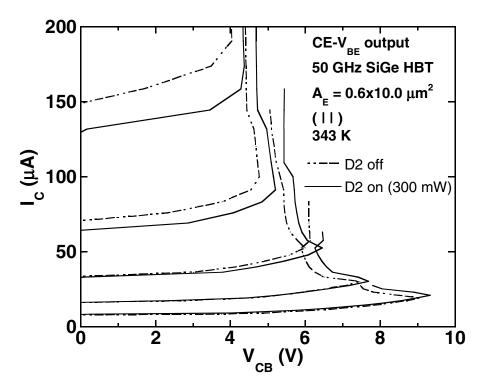

| 58 | Common-emitter output characteristics under forced $V_{BE}$ , with and without thermal coupling from adjacent heat source ("D2")                                                              | 72 |

| 59 | Safe-operating-region characteristics of the SiGe HBTs in the $()$ configura-<br>tion, comparing operation with and without thermal coupling, and operation at<br>raised ambient temperature. | 73 |

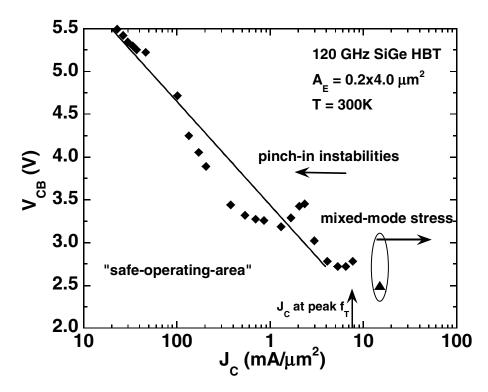

| 60 | Practical safe-operating-area considering both low-bias instabilities and high-<br>bias mixed-mode stressing for the 120 GHz SiGe HBT                                                         | 74 |

### SUMMARY

This thesis presents a comprehensive assessment of breakdown and operational voltage constraints in state-of-the-art silicon-germanium (SiGe) heterojunction bipolar transistor (HBT) BiCMOS technology. Technology scaling of SiGe HBTs for high frequency performance results on lower breakdown voltages, making operating voltage constraints an increasingly vital consideration in SiGe HBTs. In Chapter I, important technology aspects and the device physics of state-of-the-art SiGe HBT BiCMOS are discussed, and a brief overview of breakdown mechanisms is presented.

In Chapter II, operating voltage constraints are experimentally characterized as a function of technology generation, device geometry, and operating condition, to provide practical guidelines for stable device operation, and show the influence of technology scaling on breakdown voltage constraints and safe-operating-area (SOA).

Chapter III experimentally investigates the practical implications associated with of operating voltage constraints at the device and circuit level, addressing compact modeling issues, small signal instabilities, mixed-mode reliability, self-heating, and thermal coupling issues.

## **CHAPTER I**

### INTRODUCTION

#### 1.1 Motivation

Next-generation communications systems will place increasingly stringent demands upon the supporting technologies. Market and industry expectations call for emerging wireless communications infrastructure to support data and multimedia alongside voice, providing high value content to wireless communications, thereby requiring extremely high data rates. Additionally, the transmission of this content should be of high quality, with interruptionfree data transfer and mobile voice indistinguishable from wireline voice. Also, these systems will be required to operate at higher frequencies (well into the GHz range) as regulators allocate these higher frequency ranges for wireless communications in order to provide bandwidth for additional subscribers and content [1]. Finally, perhaps representing the most crucial component to the success of emerging wireless communications systems, customers expect mobile handsets to decrease in size, increase in functionality, sustain longer battery life, and remain affordable.

Silicon-Germanium (SiGe) Heterostructure Bipolar Transistor (HBT) BiCMOS technology can address all of these concerns, and has established itself as strong technology contender for a host of circuit applications including analog, mixed signal, RF and millimeter wave. The peak unity gain frequency ( $f_T$ ) of state-of-the-art SiGe HBTs far exceeds that of standard Si BJTs and rivals the best of III-V technologies. The compatibility of SiGe with Si permits higher yield and superior levels of system complexity and integration, leveraging the benefits of best-of-breed Si CMOS to offer powerful "mixed-signal" solutions. With the ability fabricate high performance analog circuits alongside powerful CMOS logic on a single silicon wafer, SiGe HBT BiCMOS technology enables powerful "system-on-a-chip" (SoC) architectures that facilitate reduced chip count, reduced power consumption, reduced packing complexity, and overall reduced cost [2].

However, achieving higher performance (in terms of peak  $f_T$ ) in SiGe HBTs inherently requires a tradeoff in transistor breakdown voltage, raising important considerations for circuit designers. The ever-decreasing operating voltage limits of scaled SiGe HBTs often pose non-obvious constraints on the biasing and operation of SiGe HBTs used in mixed-signal circuits [3], [4]. The understanding, for instance, of how much "usable" voltage actually exists in the region between the open-base breakdown voltage  $(BV_{CEO})$  and the open-emitter breakdown voltage  $(BV_{CBO})$  remains to be sufficiently addressed, particularly when considering the complex interactions between impact-ionization, self-heating, and avalanche-induced, current-crowding instabilities (often referred to as "pinch-in" effects), and their corresponding dependence on current density. In addition, important issues concerning the practical, circuit-level implications of operating a device up to and even beyond its conventionally-defined operating voltage constraints (the so-called "safeoperating-area" (SOA)) remain unclear. Moreover, standard industry compact models (e.g., VBIC, HICUM, MEXTRAM) often fail to accurately capture important features such as breakdown instabilities, and robust 2-D simulation of such effects remains particularly difficult [4].

This thesis presents a comprehensive assessment of breakdown and operational voltage constraints in state-of-the-art SiGe HBTs, experimentally examining these characteristics as functions of technology generation, device geometry, bias configuration, and operating point. New definitions for breakdown voltage, adopted from standard measurements, are developed and utilized. Practical design implications and physical origins of breakdown are explored using 2-D simulations and quasi-3D compact models. Device and circuit level re-liability implications of breakdown effects operating voltage constraints in SiGe HBTs will be emphasized. Some of these results were presented at the 2005 *IEEE International Re-liability Physics Symposium* [5], and others submitted to the 2005 *IEEE Bipolar/BiCMOS*

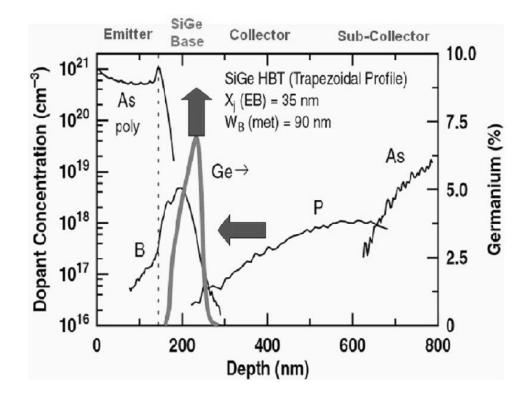

**Figure 1:** Vertical SIMS profile showing doping concentration and Ge profile within a first generation SiGe HBT.

Circuits and Technology Meeting [6].

### 1.2 SiGe HBT BiCMOS Technology

Several generations of SiGe HBT BiCMOS technology exist in commercial production worldwide, and are deployed in a wide variety of applications including cellular handsets, wireless LAN, satellite communications, radar systems, and beyond. The key difference between SiGe HBTs and standard Si BJTs is the inclusion of the compositionally graded SiGe alloy within the boron doped epitaxial layer of the active base region of the transistor. This feature, depicted in the SIMS doping and Ge profile of a first generation SiGe HBT shown in Figure 1, facilitates bandgap engineering for optimized device performance while maintaining process compatibility with standard Si CMOS. The Ge layer is typically grown using ultra-high vacuum/chemical vapor deposition (UHV/CVD), allowing for a lower thermal cycle and excellent process control during deposition. This extra process

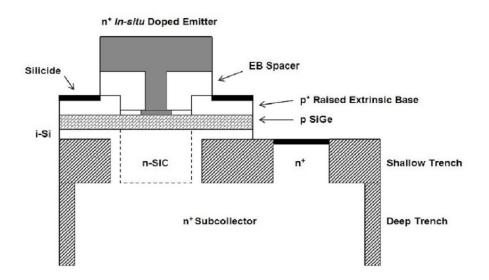

Figure 2: A schematic device cross-section of a third generation BiCMOS SiGe HBT.

step can be added in modular fashion to standard Si CMOS processes with relatively little impact on HBT performance, CMOS characteristics, fabrication yield, and overall throughput [2].

The vertical self-alignment scheme, shown in Figure 2 for a third generation SiGe HBT, is typically employed in SiGe HBT fabrication due to several advantages, including reduced parasitics and thin base region. These factors result in reduced carrier transit time, and thus higher device performance. The low thermal budget of UHV/CVD is necessary to maintain the thinness of the base region due to the diffusive nature of boron in Si. Small amounts of carbon doping may also be included in the active base region to suppress boron out-diffusion and maintain a narrow base profile and enhance device performance [2]. Shallow and deep trench isolation is incorporated, as shown in Figure 2. Selectively implanted collector (SIC) doping allows devices with different breakdown voltages to be fabricated side by side in a given SiGe HBT technology. Typically, devices come in at least two flavors: "high performance" with high collector doping and low breakdown voltage, and "high breakdown" with reduced collector doping and higher breakdown voltage.

| 1                              |         |         |         |

|--------------------------------|---------|---------|---------|

| SiGe BiCMOS Technology         | IBM 5HP | IBM 7HP | IBM 8HP |

| SiGe HBT Parameters            |         |         |         |

| Drawn Emitter Width ( $\mu$ m) | 0.5     | 0.2     | 0.12    |

| peak β                         | 100     | 200     | 400     |

| $V_A$ (V)                      | 65      | 120     | > 150   |

| $BV_{CEO}(V)$                  | 3.3     | 2.5     | 1.7     |

| $BV_{CBO}$ (V)                 | 10.5    | 7.5     | 5.5     |

| Peak $f_T$ (GHz)               | 48      | 120     | 207     |

| Peak $f_{max}$ (GHz)           | 69      | 100     | 285     |

| min. $NF_{min}$ (dB)           | 0.8     | 0.4     | < 0.3   |

**Table 1:** Characteristic device parameters for three SiGe BiCMOS technology generations.

Trans-generational SiGe HBT performance enhancements may be achieved through lateral and vertical scaling and Ge profile optimizations. The SiGe HBT BiCMOS technology generations examined in this thesis are referred to as SiGe 5HP, SiGe 7HP, and SiGe 8HP, and are in commercial production at IBM. Important HBT technology and performance characteristics are summarized in Table 1. At times, these technologies may be referred to by their approximate peak  $f_T$  performance: 50 GHz, 120 GHz, and 200 GHz, respectively.

As mentioned previously, compatibility with state-of-the-art Si CMOS technology is a major feature of the SiGe HBT. For the SiGe 5HP BiCMOS technology, the respective CMOS has an effective length of 0.35  $\mu$ m with 3.3V  $V_{DD}$  [7]. The SiGe 7HP BiCMOS technology incorporates 0.18  $\mu$ m (1.8V  $V_{DD}$ ) and 0.3  $\mu$ m (3.3V  $V_{DD}$ ) Si CMOS devices [8]. Two types of 130 nm Si CMOS devices are available in the SiGe 8HP BiCMOS technology, with minimum channel lengths of 0.12  $\mu$ m (1.2V  $V_{DD}$ ) and 0.24  $\mu$ m (2.5V  $V_{DD}$ ).

#### **1.3 Device Physics of SiGe HBTs**

Simply stated, SiGe HBT technology enables bandgap engineering in a Si system to obtain impressive performance metrics in terms of high speed, high current gain, high linearity, and low noise. A well-engineered Ge profile in the base region of the transistor can effectively decouple key device parameters that otherwise lead to critical performance tradeoffs in standard Si BJT devices.

From a physical perspective, the crystalline lattice constants differ between Si and Ge, and as a result, a SiGe alloy naturally has a slightly larger lattice constant than does Si. This lattice mismatch results in compressive straining on the SiGe layer grown pseudomorphically on Si. For a given Ge content, therefore, the SiGe film must be thinner than a certain critical value to retain thermodynamic stability and avoid relaxation defects. The compressive strain in the SiGe film also has important features in carrier mobility enhancement, and aids in transport properties of the device. The bandgap of Ge (0.66 eV at 300K) is considerably smaller than that of Si (1.12 eV at 300K). As a result, the bandgap in a SiGe alloy is effectively tunable through respective Si and Ge content (approx. -7.5 meV per 1% Ge), insofar as thermodynamic stability allows.

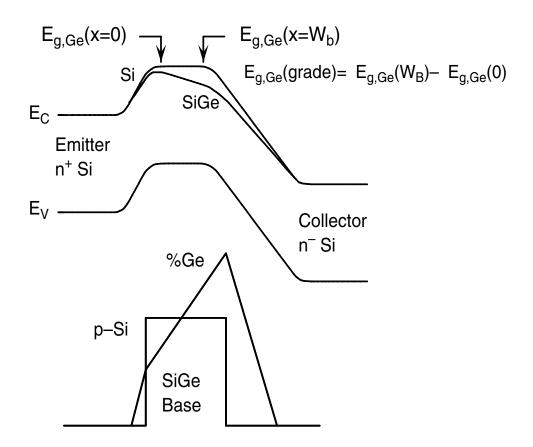

The energy band diagram for a standard Si BJT and a comparable SiGe HBT, biased in forward active mode, is shown in Figure 3. The effect of the graded Ge content in the base region is apparent in the offset between the respective conduction bands. As a result, the potential barrier for minority carrier injection into the base region is reduced for a given  $V_{BE}$ , resulting in increased collector current density ( $J_C$ ) and thus increased gain for the SiGe device. This result can be physically expressed using the generalized Moll-Ross relation for collector current density [9],

$$J_{C} = \frac{q(e^{qV_{BE}/kT-1)}}{\int_{0}^{W_{b}} \frac{p_{b}(x)dx}{D_{nb}(x)n_{ib}^{2}(x)}}$$

(1)

and an equation relating the Ge-induced offset of the bandgap to the intrinsic carrier concentration as a function of position:

$$n_{ib}^2 = \gamma n_{io}^2 e^{\Delta E_{gb}^{app}/kT} e^{[\Delta E_{g,Ge}(grade)]x/(W_bkT)} e^{\Delta E_{g,Ge}(0)/kT}$$

(2)

where  $\Delta E_{gb}^{app}/kT$  is the apparent bandgap narrowing resulting from heavy doping in the base. The low-doping intrinsic carrier density for Si is  $n_{io}^2 = N_C N_V e^{-E_{go}/kT}$  and  $\gamma = (N_C N_V)_{SiGe}/(N_C N_V)_{Si} < 1$  is the effective density-of-states ratio between SiGe and

Figure 3: Energy band diagram for a graded base SiGe HBT and a Si BJT.

Si [10]. Combining Equations (1) and (2), and assuming a linearly graded Ge profile  $(\Delta E_{g,Ge}(grade) = \Delta E_{g,Ge}(W_b) - \Delta E_{g,Ge}(0))$  results in an overall expression for collector current density ( $J_C$ ) in a SiGe HBT [11],[12]:

$$J_{C,SiGe} = \frac{q D_{nb}}{N_{ab}^{-} W_b} \left( e^{q V_{BE}/kT} - 1 \right) n_{io}^2 e^{\Delta E_{gb}^{app}/kT} \left\{ \frac{\widetilde{\gamma} \widetilde{\eta} e^{\Delta E_{g,Ge}(0)/kT} \Delta E_{g,Ge}(grade)/kT}{1 - e^{-\Delta E_{g,Ge}(grade)/kT}} \right\}$$

(3)

where the symbol "~" denotes a position-averaged quantity,  $N_{ab}^-$  is the ionized doping level in the base, and  $\tilde{\eta} = \left(\widetilde{D_{nb}}\right)_{SiGe} / (D_{nb})_{Si} > 1$  is the minority electron diffusivity ratio between SiGe and Si. The influence of the Ge-induced energy band offset on collector current density is contained entirely in the second term of this relation, and thus can be described as the SiGe current gain enhancement factor:

$$\frac{\beta_{SiGe}}{\beta_{Si}} \cong \frac{J_{C,SiGe}}{J_{C,Si}} = \frac{\widetilde{\gamma}\widetilde{\eta}\Delta E_{g,Ge}(grade)/kT e^{\Delta E_{g,Ge}(0)/kT}}{1 - e^{-\Delta E_{g,Ge}(grade)/kT}}$$

(4)

The SiGe current gain enhancement factor demonstrates that Ge-induced energy band

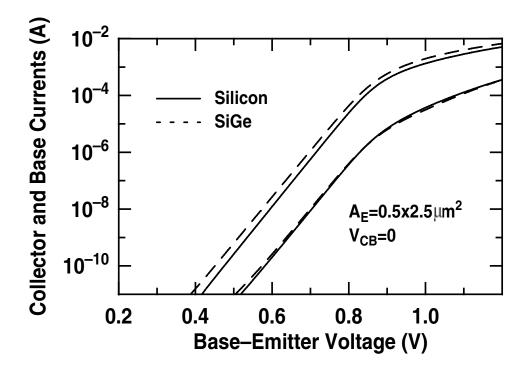

Figure 4: Representative Gummel plot for a SiGe HBT as compared to a Si BJT.

offset at the EB junction ( $\Delta E_{g,Ge}(0)$ ) exerts a exponential influence on the gain increase of the device. This enhancement is depicted in Figure 4, which compares the Gummel characteristics for a typical SiGe HBT and a similarly constructed Si BJT. The SiGe HBT clearly exhibits higher collector current with approximately the same base current as the Si BJT, and hence, increased current gain.

In the case of "strong Ge grading" ( $\Delta E_{g,Ge}(grade) >> kT$ ), characteristic of a triangular Ge profile, the exponential term on the denominator becomes very small and this factor approximately reduces to  $\approx (\tilde{\gamma}\tilde{\eta}\Delta E_{g,Ge}(grade)/kT)e^{\Delta E_{g,Ge}(0)/kT}$ . In the case of "weak Ge grading" ( $\Delta E_{g,Ge}(grade) << kT$ ), characteristic of a box Ge profile, the SiGe current gain enhancement factor is shown to be approximately  $\tilde{\gamma}\tilde{\eta}e^{\Delta E_{g,Ge}(0)/kT}$ .

In addition to current gain ( $\beta$ ), the output conductance ( $\partial I_C / \partial V_{CE}$  at fixed  $V_{BE}$ ) of a transistor is a key consideration in analog design. This factor is equivalently described using the output resistance  $r_o$ , with output conductance equal to  $1/r_o$ . The ideal transistor

possesses infinite output resistance, and thus zero output conductance. However, it is well known that actual transistors possess finite values of  $r_o$  due to what is referred to as the "Early Effect". Increasing  $V_{CB}$  causes backside depletion on the neutral base. This reduces the effective width of the active base region, which increases the minority carrier (electron) concentration gradient across the base and thus increases the collector current. This behavior is commonly characterized using an experimental parameter known as the Early voltage  $(V_A)$ :

$$V_A = J_C(0) \left\{ \left. \frac{\partial J_C}{\partial V_{CB}} \right|_{V_{BE}} \right\}^{-1} - V_{BE} \approx \left\{ \left. \frac{\partial J_C}{\partial W_b} \right|_{V_{BE}} \frac{\partial W_b}{\partial V_{CB}} \right\}^{-1}$$

(5)

The  $V_A$  enhancement ratio between a comparable SiGe HBT and Si BJT is given by

$$\frac{V_{A,SiGe}}{V_{A,Si}}\Big|_{V_{BE}} = e^{\Delta E_{g,Ge}(grade)/kT} \left[\frac{1 - e^{-\Delta E_{g,Ge}(grade)/kT}}{\Delta E_{g,Ge}(grade)/kT}\right]$$

(6)

This relation shows the exponential influence of the Ge-induced bandgap grading on Early voltage. Thus, the Ge profile in a SiGe HBT provides separate "levers" for optimizing  $\beta$  and  $V_A$  ( $\Delta E_{g,Ge}(0)$  and  $\Delta E_{g,Ge}(Grade)$ , respectively). In standard Si BJTs, enhancement of one of these two factors fundamentally requires degradation of the other since they both are related to the base doping. But with the effective decoupling of  $\beta$  and  $V_A$  from base doping (and, thus, each other) in a well constructed Ge profile, this tradeoff is sidestepped and the overall  $\beta \cdot V_A$  product, an important device parameter in analog circuits, of a SiGe HBT is substantially higher than that of a similar Si BJT.

SiGe HBTs also show substantial improvement in *ac* performance over conventional Si BJTs, allowing SiGe HBTs to achieve frequency response characteristics suitable for even high frequency RF and microwave applications. The base transit time comprises a significant portion of the total transport delay time for carriers in bipolar devices, and thus can be a limiting factor in overall ac performance. Ge grading induces a drift field in neutral base that accelerates minority carriers and reduces the base transit time ( $\tau_b$ ), given by

$$\frac{\tau_{b,SiGe}}{\tau_{b,Si}} = \frac{2}{\widetilde{\eta}} \frac{kT}{\Delta E_{g,Ge}(grade)} \left\{ 1 - \frac{kT}{\Delta E_{g,Ge}(grade)} \left[ 1 - e^{-\Delta E_{g,Ge}(grade)/kT} \right] \right\}$$

(7)

Additionally, since the emitter charge storage delay time ( $\tau_e$ ) is proportional to  $1/\beta$ , the higher  $\beta$  of a SiGe HBT will reduce this factor according to

$$\frac{\tau_{e,SiGe}}{\tau_{e,Si}} \simeq \frac{J_{C,Si}}{J_{C,SiGe}} = \frac{1 - e^{-\Delta E_{g,Ge}(grade)/kT}}{\widetilde{\gamma}\widetilde{\eta}\frac{\Delta E_{g,Ge}(grade)}{kT}}e^{\Delta E_{g,Ge}(0)/kT}$$

(8)

and thus improve the total transit time.

A standard figure-of-merit for dynamic transistor performance is the unity-gain cutoff frequency  $(f_T)$ . For low-injection, this parameter can be written as

$$f_T = \frac{1}{2\pi} \left[ \frac{1}{g_m} (C_{eb} + C_{cb}) + \tau_b + \tau_e + \frac{W_{CB}}{2v_{sat}} + r_c C_{cb} \right]^{-1}$$

(9)

As stated above and shown explicitly here in Equation (9), reduction of  $\tau_b$  and  $\tau_e$  will result in reduced overall transit time ( $\tau_{ec}$ ) and thus increase  $f_T$ . Likewise, the unity power-gain frequency (or, maximum oscillation frequency,  $f_{max}$ ) will also improve since it is a function of  $f_T$ , given by

$$f_{max} = \sqrt{\frac{f_T}{8\pi C_{cb} r_b}} \tag{10}$$

Thus, the Ge grading in the base region of the SiGe significantly improves both  $f_T$  and  $f_{max}$ , and thus overall *ac* performance.

#### 1.4 Breakdown Fundamentals

As demonstrated in Equation (9), with reduction in  $\tau_b$  and  $\tau_e$ , the time delay imposed by the parasitic capacitances within the device becomes more significant. To counter this limiting factor to performance enhancement, an increase in collector current density ( $J_C$ ) is required to decrease the charging times of the parasitic capacitances ( $C_{eb}$  and  $C_{cb}$ ). Therefore, increased  $J_C$  is a common characteristic associated with technology scaling and  $f_T$ optimization in SiGe HBTs, as shown in Figure 5.

At high  $J_C$ , carriers in the collector-base space charge region (CB-SCR) will compensate the local ionized charge, leading to a collapse of the electric field in this region. As a result, the base region will "push-out" into the CB-SCR (the Kirk effect), decreasing the

**Figure 5:** Cutoff frequency as a function of collector current density for three generations of SiGe HBT BiCMOS technology.

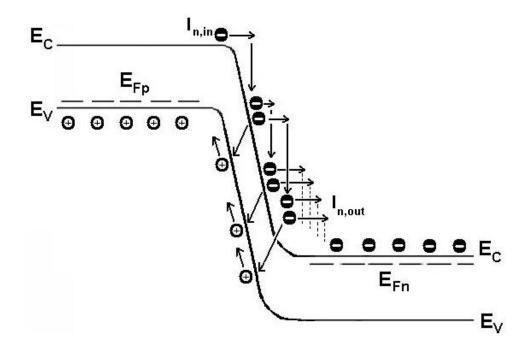

**Figure 6:** Schematic illustration of the avalanche multiplication process in a reversed bias p-n junction.

**Figure 7:** MEDICI device simulation of a 120 GHz SiGe HBT showing contours of impact ionization generation rate with respect to the device profile.

current gain and degrading the performance of the transistor. Therefore, in order to operate at high  $J_C$ , higher collector doping is required to suppress the Kirk effect. Increasing the collector doping will increase the magnitude of the drift field within the CB-SCR, causing conduction electrons in this region to obtain high kinetic energy. In the event that an electron of sufficient velocity collides with the lattice, excess energy may be transferred to an electron in the valence band, promoting this carrier to the conduction band and creating an electron-hole pair (EHP). This generation process is the inverse of the Auger effect, and is known as impact ionization [13]. As an electron generated during an impact ionization event is accelerated due to the drift field, it too may undergo a lattice collision and generate an additional EHP, and so on, as illustrated in Figure 6. This "snowballing" phenomenon of impact-ionized carriers is referred to as avalanche multiplication. Figure 7 shows the location of impact ionization centers as determined by a two dimensional device simulation in MEDICI for a 120 GHz SiGe HBT at  $I_E = 500 \ \mu A$  and  $V_{CB} = 4$  V.

As the reverse bias potential across the junction ( $V_{CB}$  in a bipolar transistor) increases, the probability that each carrier in the depletion region will undergo an impact ionization

Figure 8: MEDICI device simulation of a 120 GHz SiGe HBT showing M-1 as a function of collector voltage.

event increases, eventually leading to junction breakdown. This probability is typically represented as the avalanche multiplication factor (M), which is the ratio of reverse-biased junction current without impact ionization to the junction current with impact ionization, or

$$M = I_{n,out} / I_{n,in} \tag{11}$$

for  $I_{n,in}$  being the electron current entering the CB-SCR and  $I_{n,out}$  being the electron current exiting the CB-SCR. The avalanche multiplication factor can be extracted from standard measurements ([14]) and is commonly plotted as (log) M - 1 verses (linear) collectorbase voltage ( $V_{CB}$ ), as shown in Figure 8 taken from a MEDICI simulation of a 120 GHz SiGe device. The holes generated during the avalanche multiplication process flow into the neutral base region and out of the base terminal, causing the total current at the terminal  $I_B$ to be reduced according to

$$I_B = I_{p,e} - (M - 1)I_{n,in}$$

(12)

for which neutral base recombination (NBR) is neglected and  $I_{p,e}$  defined as the base current due to holes injected into the emitter. As M - 1 increases with  $V_{CB}$ , the second term, which represents the avalanche current, eventually becomes equal to  $I_{p,e}$ , at which point  $I_B = 0$ . This condition results when the product  $\beta(M - 1) = 1$ , which is equivalent to the condition of open-base breakdown  $BV_{CEO}$  [15] [16], a standard breakdown Figure of merit given in Table 1 for the 50, 120, and 200 GHz SiGe HBT technologies. If  $V_{CB}$  is allowed to increase further, the sign of  $I_B$  becomes negative and holes generated by avalanche multiplication flow out of the base terminal. This situation is known as base current reversal, and is an important factor in breakdown related transistor instabilities at high  $V_{CB}$ , as shall be discussed further in Chapter II [17] [18] [19]. If  $V_{CB}$  continues to increase, the CB junction will eventually undergo full reverse biased junction breakdown at the open-emitter breakdown voltage  $BV_{CBO}$ . Thus,  $BV_{CBO}$ , as given in Table 1 for the 50, 120, and 200 GHz SiGe HBT technologies, represents the absolute maximum collector voltage of a transistor.

For simplicity, in many cases M - 1 for a given  $V_{CB}$  is treated as a constant with respect to current density,  $J_C$ , and for low injection this approximation is usually acceptable. However, it is well known that at high injection M - 1 shows a stronger dependence on  $J_C$ , due to high carrier charge concentration reducing the effective doping, and thus the effective electric field, within the CB-SCR [2]. Also, M - 1 possess a negative temperature coefficient due to changes in carrier mean free path and phonon scattering, which absorbs energy during carrier-lattice collisions and reduces the probability of EHP creation [20]. As a result, we expect and observe breakdown effects to be aggravated for low temperature (cryogenic) operating conditions.

Overall, increasing the collector doping, as required to achieve higher device performance in SiGe HBTs, increases the rate of avalanche multiplication within the device and thus reduces its breakdown voltage. This is reflected in Table 1, which shows the openemitter reverse bias collector junction breakdown voltage ( $BV_{CBO}$ ) to decrease from 10.5 V to 5.5 V over the three technology generations as peak  $f_T$  increases from 50 GHz to 200 GHz. Thus, an inherent (and well known) tradeoff exists between peak  $f_T$  and breakdown voltage in SiGe HBT device design. This fundamental limit is more accurately described by the (larger)  $BV_{CES} \cdot f_T$  product ( $BV_{CES} \approx BV_{CBO}$ ) than the traditional  $BV_{CEO} \cdot f_T$  product [21], but clearly the ever-decreasing operating voltage limits of scaled SiGe HBTs reveal the growing importance breakdown related issues, particularly in the realm of mixed-signal circuit design.

### 1.5 Summary

In this chapter, we highlighted the emerging needs of next-generation communications systems, and introduced the silicon-germanium heterostructure bipolar transistor, describing the strengths that make SiGe HBT BiCMOS technology a suitable candidate for a variety of high frequency applications. However, with performance gains in SiGe HBTs come reductions in breakdown voltage, making operating voltage constraints an increasingly vital consideration in SiGe HBTs. Important technology aspects of state-of-the-art SiGe HBT BiCMOS were reviewed, and the relevant physics of the SiGe HBT device was discussed. Also, a brief overview of breakdown voltage and avalanche multiplication in bipolar devices was given.

In Chapter II, additional discussion will be paid to breakdown for different transistor biasing configurations, and operating voltage constraints will be experimentally characterized as a function of technology generation, device geometry, and operating condition. Chapter III will experimentally address the practical implications of operating voltage constraints at the device and circuit level, discussing compact modeling issues, small signal instabilities, mixed-mode reliability, self-heating, and thermal coupling between devices. Finally, Chapter IV will provide overall conclusions and discuss future directions for further study.

## **CHAPTER II**

### **BREAKDOWN CHARACTERISTICS IN SIGE HBTS**

#### 2.1 Introduction

As shown in Chapter I, breakdown voltages ( $BV_{CEO}$ ,  $BV_{CBO}$ ) in SiGe HBTs can be expected to become lower as high frequency device performance improves. As a result, circuit designers are faced with increasingly stringent device operating restrictions as maximum limits of usable collector voltage are compressed. However,  $BV_{CEO}$  and  $BV_{CBO}$  do not tell the full story of breakdown voltage constraints, and transistors are often required to operate in the region between the two breakdown voltages for many practical circuits. We find, in fact, that SOA limits vary considerably between different bias configurations and have a strong dependence on current injection level.

In this chapter, we will experimentally examine breakdown and practical operational voltage constraints in state-of-the-art SiGe HBTs as they relate to technology generation, device geometry, bias configuration, and operating point. First, a more detail background of breakdown related instabilities in SiGe HBTs will be presented and supported by qualitative, simulated, and experimental analysis. The key breakdown-related differences between different bias configurations will be addressed. New definitions for breakdown voltage, adopted from standard measurements, will be presented and examined. Next, the breakdown characteristics for three generations of SiGe HBT technology (50 GHz, 120 GHz, and 200 GHz peak  $f_T$ ) will be examined experimentally for different bias configurations and device geometries in order to generate practical design guidelines to ensure stable device operation under high voltage conditions.

**Figure 9:** Simplified depiction of injected current  $(A/\mu m)$  and avalanche generation as a function of position within the device.

### 2.2 Background

#### 2.2.1 Pinch-in Effects

Avalanche-induced base current reversal, as described in Chapter I, may cause constriction of current flow within the device which result in unstable device behavior. These current flow non-uniformities are referred to as "pinch-in" effects. Starting with a few basic assumptions, this section will provide a simplified and qualitative examination of pinch-in related phenomena.

To illustrate the origin on the pinch-in effect, consider a simplified 1-dimensional horizontal cross section through the neutral base of a transistor profile with two extrinsic base contacts on either side of the emitter window (as shown in Figure 2). We will assume the active device is horizontally symmetrical about the center of the neutral base region, which we will denote as position x = 0. Therefore, for drawn emitter width  $W_E$ , the boundaries of the active base occur at  $x = +W_E/2$  and  $x = -W_E/2$ . For a moment we will make the assumption that current distribution  $I_E$  is uniform within the device. Therefore, the current passing within the small segment between x and  $x + \delta x$  is simply a constant with respect

**Figure 10:** Simplified depiction of avalanche current (A) as a function of position within the active device.

to position, or

$$\delta I_E(x) = \delta I_E = \frac{I_E}{W_E} \tag{13}$$

This scenario is depicted in Figure 9. The excess current generated by impact ionization in the CB-SCR is

$$I_{AVC} = \frac{I_E}{(\beta+1)} [(M-1)\beta - 1] \approx (M-1)I_E$$

(14)

for current gain  $\beta >> 1$ . We will likewise assume that the product  $(M-1)\beta >> 1$ , and thus the forward injected hole current  $(I_{p,e}, \text{ in Equation (12)})$  is very small compared to  $I_{AVC}$ and can be neglected. The avalanche current consists of both an electron current component, which is swept into the collector, and as hole current component, which is swept into the base. Therefore, the avalanche hole current generated within the small segment between x and  $x + \delta x$  within the base region is

$$\delta I_{AVC}(x) \approx \frac{(M-1)I_E}{W_E} \tag{15}$$

Assuming the base current  $(I_B)$  is not fixed externally, the excess holes generated by avalanche multiplication will flow from their point of origin  $(0 < x < W_E/2)$  to the extrinsic base boundary  $(x = W_E/2)$  and exit through the base terminal. The total avalanche

**Figure 11:** Simplified depiction of intrinsic base potential (V) as a function of position within the active device.

current at a particular point x within the base is the summation of the generated avalanche current for each small segment  $\delta x$  between the center of the device (x = 0) and the position x, and therefore can be represented as

$$I_{AVC}(x) = \int_0^x \delta I_{AVC}(y) dy \approx \frac{(M-1)I_E}{W_E} x$$

(16)

This is plotted in Figure 10. Clearly, the hole current is vanishingly small at the center of the symmetric device, and equals half of the total avalanche current at  $x = +W_E/2$ . (The other half of the avalanche current exits the device through the other extrinsic base contact at  $x = -W_E/2$ .) We define the intrinsic base potential  $V_{B'} = V_B + \Delta V_{B'}$ . Treating the intrinsic base resistance  $r_{Bi}$  as a uniformly distributed factor yields  $\delta r_{Bi}(x) = \delta r_{Bi} = \frac{r_{Bi}}{W_E/2}$ . Therefore

$$\Delta V_{B'}(x) = \int_{x}^{W_E/2} \delta r_{Bi} I_{AVC}(y) dy$$

(17)

Substituting the result from Equation (16) into (17), and assuming a potential drop across the extrinsic base resistance is equal to  $r_{Bx}I_{AVC}(0)$ , we obtain

$$\Delta V_{B'}(x) = \frac{r_{Bi}(M-1)I_E}{4} - r_{Bi}(M-1)I_E(x/W_E)^2 + r_{Bx}(M-1)I_E/2$$

(18)

as plotted in Figure 11. At this point we are forced to reevaluate our initial assumption of uniform current distribution, given that  $I_E(x)$  is a function of intrinsic base potential  $V_{B'E'}(x)$ , according to

$$I_C = I_S e^{V_{BE}/(kT/q)} \tag{19}$$

Therefore, for saturation current  $I_S$ , and  $I_E = \frac{\beta}{\beta+1}I_C \approx I_C$ ,

$$\delta I_E(x) = I_E(x) / W_E \approx \frac{I_S}{W_E} e^{V_{B'E'}(x)/(kT/q)}$$

(20)

Ignoring the potential drop across the parasitic emitter resistance  $(r_E)$  we define  $V_{B'E'}(x) = V_{BE} + \Delta V_{B'}(x)$ . We also define the thermal voltage  $V_T = kT/q$ . Thus,

$$\Delta V_{B'}(x) = \int_{x}^{W_{E}/2} \left[ \frac{2r_{Bi}}{W_{E}^{2}} (M-1) I_{S} e^{V_{BE}/V_{T}} \right] e^{\Delta V_{B'}(y)/V_{T}} y dy$$

(21)

The terms enclosed within the brackets may be treated as a constant factor. It is clear, however, that the change in intrinsic base potential  $(\Delta V_{B'}(x))$  is an exponential function of itself, and that this integral must be solved iteratively. Forgoing that, we can use this expression to note the positive-feedback mechanism associated with pinch-in, concluding that the intrinsic base potential distribution is stable for  $\Delta V_{B'} \ll V_T$ , and unstable for  $\Delta V_{B'} \approx V_T$ , at which point pinch-in occurs. If we consider the voltage drop across the emitter resistance  $(r_E)$ , then  $V_{B'E'}(x) = V_{BE} + \Delta V_{B'}(x) - \Delta V_{E'}(x)$ . Clearly this additional term produces a stabilizing effect, particularly as the emitter current increases. This will be discussed further from an experimental side in the sections to follow.

A 2-D device simulation of was performed using MEDICI (including hydrodynamic energy balance and impact ionization) for various values of  $V_{CB}$ . Figure 12, taken from these simulations, shows the onset of distributed current and voltage non-uniformities within a cross-section of the active base region. The relevant device profile is aligned with the spatial dimensions of the plot in the inset above Figure 12, and the examined cross-section is highlighted. The severe current localization associated with pinch-in is then subject to a myriad of instabilities associated with self-heating and electric field collapse [22]. Attempting to simulate within this unstable region at higher  $V_{CB}$  results only in

**Figure 12:** MEDICI simulation of a 120 GHz SiGe HBT showing the intrinsic potential distribution and onset of current constriction within the neutral base.

non-convergent numerical solutions.

#### 2.2.2 Common-emitter bias with forced base current

For the common-emitter bias configuration driven by a constant base current (*CE-I<sub>B</sub>*), *I<sub>B</sub>* is held constant by an external current source (similar to the constant zero current "driven" during open-base operation), so excess holes, generated in the CB-SCR by impact ionization and swept into the base region, must then be injected into the emitter [15]. Thus, the avalanche current is amplified by the forward current gain  $\beta$  across the E-B junction, which in turn increases the collector current and thus the avalanche current via positive feedback, leading to premature breakdown. As a net result, the open-base breakdown voltage ( $BV_{CEO}$ , for  $I_B = 0$ ) and corresponding fixed  $I_B$  breakdown voltages (constant  $I_B > 0$ ) are much lower than the collector-base reverse junction breakdown voltage ( $BV_{CBO}$ ). In many SiGe technologies, the ratio between the two breakdown voltages has been observed to be approximately one-third [4].

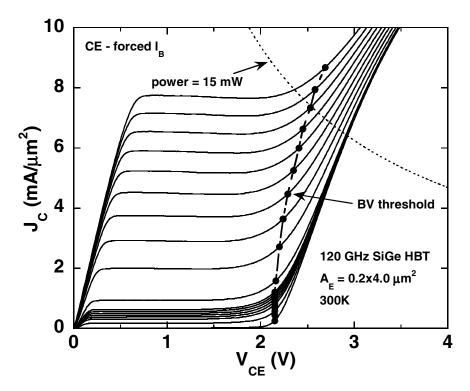

Figure 13: CE - forced  $I_B$  output characteristic with BV thresholds indicated.

For this study, the  $CE-I_B$  BV threshold is defined as the point at which the slope of  $J_C$  on  $V_{CE}$  exceeds the ratio of  $J_C$  at peak  $f_T$  over  $BV_{CEO}$  for that technology. For demonstration, this constant-slope BV threshold is plotted together with an output characteristic family in Figure 13 for a typical 120 GHz SiGe HBT in this bias configuration. It should be noted, however, that in typical mixed-signal circuit design devices are usually subjected to finite external impedance between the base and emitter terminals. In light of this, one might consider  $BV_{CEO}$ , or the similar (non-zero) fixed base current breakdown voltages, to be irrelevant from a practical standpoint. In any case, open-base and  $CE-I_B$  breakdown presents a worst-case (lowest) BV threshold [4], and in this sense is useful for technology performance comparisons.

#### 2.2.3 Common-emitter bias with forced base voltage

A second biasing condition we will examine is the common-emitter bias driven by a constant base-emitter voltage ( $CE-V_{BE}$ ). As noted above, practical circuits are not typically driven by a constant current source as occurs in the  $CE - I_B$  cause, and the  $CE - V_{BE}$  configuration is more commonly encountered in practical circuits. The  $CE - V_{BE}$  driving condition differs fundamentally from the forced- $I_B$  case because excess hole current resulting from impact ionization is allowed to freely exit the base terminal due to the low series impedance  $(R_s = 0 \ \Omega)$  in the ideal case) of the applied voltage source. At sufficiently high collector voltage (approximately  $BV_{CEO}$ ) the product of current gain and avalanche multiplication factor exceeds unity and the base current reverses sign. As discussed in a previous section, this reversal of base current, with increased  $V_{CB}$ , can eventually lead to central current crowding and bias instabilities. However, depending on the circuit application, stable bias can still be achieved (and may in fact be required) in regions of considerable base current reversal, thus  $CE - V_{BE}$  bias allows operation at higher voltages (between  $BV_{CEO}$  and  $BV_{CBO}$ ) than does  $CE - I_B$  bias [3], [22].

A complex set of interactions determine the  $CE-V_{BE}$  breakdown voltage constraints [15], [16], [17] [18], [19], [22], [23], [24], [25]. The primary driving mechanism is impactionization, which, at sufficiently high levels, causes base current reversal, as described above. As qualitatively illustrated in a previous section, the current flowing over the parasitic intrinsic base resistance creates a potential distribution within the neutral base favoring current flow at the center of the device (highest internal  $V_{BE}$ ). As  $|I_{B_rvs}|$  increases further, this potential distribution eventually becomes unstable and a significant portion of the current collapses to the center of the device in a phenomenon described as "pinch-in" [3], [22].

The stable voltage limits for  $CE-V_{BE}$  operation were explored in [22] in terms of a critical reverse base current  $I_{B_{rvs}crit}$  (< 0):

$$I_{B\_rvs\_crit} = -\frac{V_T + r_E I_E}{(r_B G)}$$

(22)

for  $(I_E > 0)$  with

$$G = 1.5 + \frac{2.6}{(3 + l_E/w_E)} \tag{23}$$

The parameters  $l_E$  and  $w_E$  correspond to the device emitter length and width, respectively. As shown in Equations (22) and (23), this factor is dependent on device geometry and the parasitic emitter and base resistances. Reverse base current can then be related to the avalanche multiplication factor:

$$I_{B_{rvs}} = \frac{-I_E}{(\beta+1)} [(M-1)\beta - 1] \approx -(M-1)I_E.$$

(24)

Therefore, for  $\beta >> 1$ ,

$$(M-1)_{critical} \approx -\frac{I_{B\_rvs\_crit}}{I_E}.$$

(25)

For low injection (neglecting the M - 1 dependence on operating current), the avalanche multiplication factor can be related to  $V_{CB}$  via the following empirical fit [22]:

$$(M-1) = c \left(\frac{V_{CB}}{1 \text{ volt}}\right)^a.$$

(26)

For accurate extension of avalanche current to high bias, a more complicated current dependant M - 1 relation, as discussed in [26] and [27], may also be used.

Combining Equations (25) and (26) and rearranging the terms yields a functional relation between forced emitter current and maximum stable  $V_{CB}$ , based either on critical base current  $I_{B_rvs\_crit}$ , or more generally, on the parasitic emitter and base resistances:

$$V_{CB\_crit} = \left(\frac{|I_{B\_rvs\_crit}|}{cI_E}\right)^{1/a} \cdot (1volt)$$

(27)

$$= \left[\frac{(V_T + r_E I_E)}{c I_E r_B G}\right]^{1/a} \cdot (1 \text{ volt}).$$

(28)

Overall, these relations illustrate that pinch-in will occur when the magnitude of the internal base potential distribution becomes non-negligible with respect to the thermal voltage  $V_T = kT/q$ , taking into account the proportionality factor G and the series potential drop across the parasitic emitter resistance,  $r_E I_E$ . Limiting the discussion to low injection operation allows a degree of simplification of the relevant parameters comprising the critical reverse base current. For instance, the avalanche factor M - 1 possesses a much stronger dependence on  $V_{CB}$  than  $I_E$ , particularly at lower injection. To extend the discussion to higher injection, the current dependence of the M - 1 should likewise be accounted

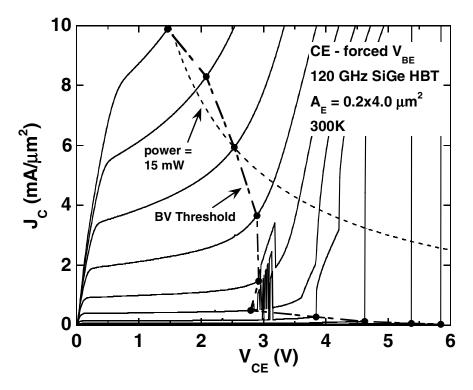

Figure 14: CE - forced  $V_{BE}$  output characteristic with associated BV thresholds.

for [26], [27]. In addition, it is appropriate to consider the dependence of base sheet resistance on  $V_{CB}$  and collector current [22], [25], [28]. At increased injection levels, the role of the parasitic emitter resistance becomes non-negligible since, with increased  $I_E$ , the potential drop across  $r_E$  (also dependent on current level and current crowding) significantly (with respect to the thermal voltage  $V_T$ ) debiases the center of E-B junction and thus increases the magnitude of the maximum sustainable reverse base current, allowing the device to remain in stable operation at higher M - 1, and thus higher  $V_{CB}$  [22]. Self-heating also becomes an important consideration at high-injection. These considerations shall be explored further in Chapter III.

Similar to the CE- $I_B$  case, for this study the CE- $V_{BE}$  BV threshold is defined as the point at which the slope of  $J_C$  on  $V_{CE}$  exceeds the ratio of  $J_C$  at peak  $f_T$  over  $BV_{CEO}$  for that technology. A typical family of CE- $V_{BE}$  output characteristics is provided in Figure 14. The breakdown voltage threshold and a contour of constant power are also provided for comparison. The output characteristic shows considerable differences in behavior as  $V_{BE}$

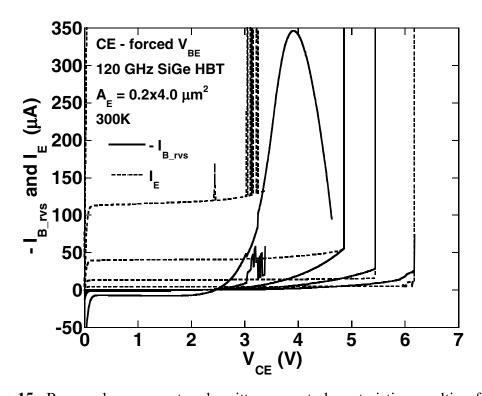

Figure 15: Reverse base current and emitter current characteristics resulting from CE - forced  $V_{BE}$  measurement.

Figure 16: CE - forced  $V_{BE}$  output characteristic with  $I_C$  swept and  $V_{CE}$  measured.

increases. For the cases at low  $V_{BE}$  (and thus low  $J_C$ ), at high  $V_{CE}$  the device undergoes electro-thermal runaway, abruptly entering breakdown as the collector current rapidly increases (with a slope approaching infinity) until reaching the external limit (or destroying the device). However, for the curves at high  $V_{BE}$  (and thus high  $J_C$ ), the collector current increases smoothly with  $V_{CE}$ . This difference is also reflected in base and emitter currents, as shown in Figure 15. At low  $V_{BE}$ , both  $I_E$  and  $|I_{B_rvs}|$  increase rapidly at  $V_{CB_crit}$ . However, for higher  $V_{BE}$ ,  $|I_{B_rvs}|$  reaches a peak, then begins to decrease as  $I_E$  increases due to self-heating and forward injected base current component ( $I_{p,e}$  from Equation (12) discussed in Chapter I) becomes more dominant. At sufficiently high current, base current reversal is suppressed entirely.

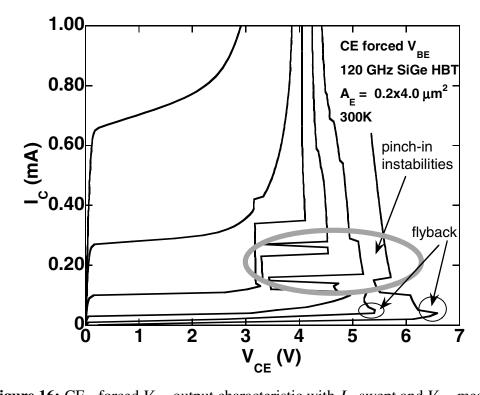

For additional insight, Figure 16 shows a similar  $CE-V_{BE}$  characteristic, except with the  $I_C$  swept and  $V_{CE}$  measured. For low  $V_{BE}$ , device breakdown occurs at the collector current "fly back" point, at which  $V_{CE}$  decreases for increased  $I_C$  due to a combination of self heating and the increased intrinsic base potential due to the flow of  $I_{B_rvs}$  over the parasitic base resistance. Note that while this "fly back" characteristic is aggravated by the pinch-in effect, as observed in the severe instabilities measured in this region, this characteristic of decreasing  $V_{CE}$  with increasing  $I_C$  is observable in  $CE-V_{BE}$  simulations that do not take into account current flow non-uniformities or pinch-in related effects. Clearly, the fly back of the collector current during  $CE-V_{BE}$  operation introduces a bistability to the output characteristic [29]. This, when considered in relation to unpredictable nature of pinch-in in instabilities, may explain the unstable region in the output characteristic (as shown in Figure 14) observed in the transition between the low injection snapback behavior and high injection self-heating behavior. However, we note with caution that the precise structure of the resulting instabilities, as shown, may well be an artifact of the particular measurement setup, and thus should be investigated further.

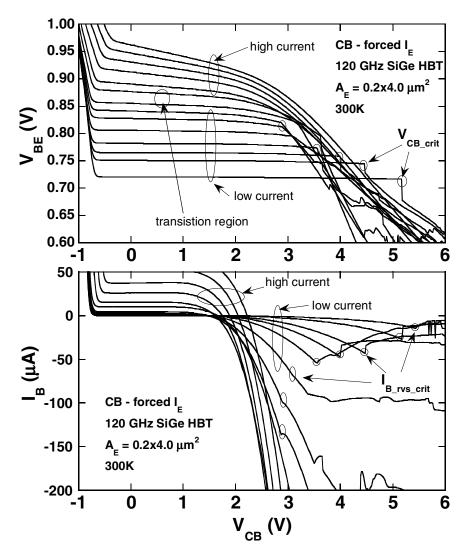

Figure 17:  $V_{BE}$  and  $I_B$  characteristics from CB - forced  $I_E$  measurements at low and high injection.

#### 2.2.4 Common-base bias with forced emitter current

A common-base bias configuration driven by a constant emitter current  $(CB-I_E)$  will be an important focal point for this study, since it lends itself to many practical circuit applications (e.g., amplifier output stages). Like  $CE-V_{BE}$ , the  $CB-I_E$  driving condition allows excess hole current resulting from impact ionization is allowed to freely exit the base terminal, which, at high  $V_{CB}$ , can lead to central current crowding and pinch-in instabilities. However, since stable bias is possible under conditions of considerable base current reversal, thus  $CB-I_E$  bias allows operation at higher voltages (between  $BV_{CEO}$  and  $BV_{CBO}$ ) than does  $CE-I_B$  bias [3]. Moreover, since the  $I_E$  is held constant, electro-thermal runaway, as may occur in the case where  $V_{BE}$  is held constant, is prevented during  $CB-I_E$  operation as long as  $V_{CB} < BV_{CBO}$ .

From [22], the critical reverse base current under  $CB-I_E$  operating conditions is

$$I_{B\_rvs\_crit} = I'_{B\_rvs\_crit} \left[ 1 + \left(\frac{w_E}{l_E}\right)^2 \right]$$

(29)

where  $I'_{B\_rvs\_crit}$  represents the critical reverse base current for constant base voltage drive  $(CE-V_{BE})$ . For  $l_E >> w_E$  (as is assumed for the device geometries examined in the present paper)  $I_{B\_rvs\_crit} \approx I'_{B\_rvs\_crit}$ . Given this assumption, the final result for  $V_{CB\_crit}$  is identical to that shown in Equations (27) and (28).

During  $CB-I_E$  operation a considerable roll-off of  $V_{BE}$  with increased  $V_{CB}$  is commonly observed [3], [22]. One cause is the voltage drop of  $I_{B_rvs}$  across  $r_B$ . For example, momentarily neglecting self-heating, for emitter potential  $V_E$  (< 0 and equal to  $-V_{BE}$ ),  $|V_E|$  must decrease to maintain a constant  $V_{B'E'}$  as the internal base potential  $V_{B'}$  increases above the zero volt potential of the common-base terminal. Self-heating becomes an important factor in the  $V_{BE}$  on  $V_{CB}$  characteristic at higher current densities and during pinched-current operation, resulting in a decrease of the internal  $V_{B'E'}$  to maintain constant  $I_E$  at elevated operating temperature.

The contrast between low-injection (minimal self-heating) and high-injection (considerable self-heating)  $V_{BE}$  on  $V_{CB}$  behavior is depicted in Figure 17. Points at which pinch-in occurs are indicated. Figure 17 also shows the reverse-base-current characteristics across bias, with the threshold  $I_{B_{rvs}crit}$  indicated on each curve. Similar to findings presented in [22], these results show a considerable bias dependence on the magnitude of  $I_{B_{rvs}crit}$ . This dependence, and its relation to device geometry, is discussed further in Section 2.3.

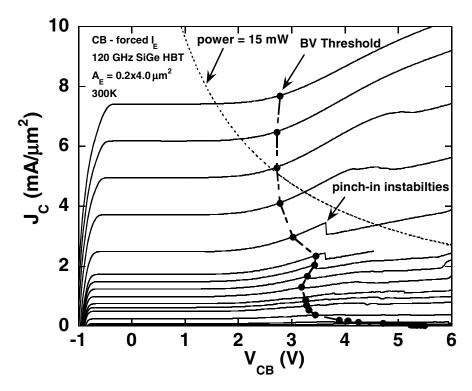

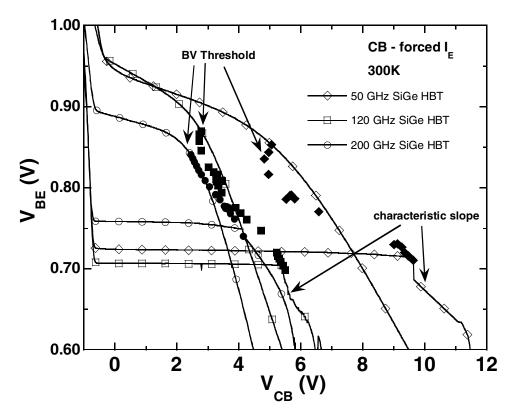

For the CB- $I_E$  bias configuration, the BV threshold, as depicted in Figure 18, is conveniently defined with respect to a constant  $V_{BE}$  on  $V_{CB}$  slope. The critical  $V_{BE}$  on  $V_{CB}$  slope (< 0) for a given technology is determined from the characteristic  $V_{BE}$  roll-off under pinched-current operation (observable at  $V_{CB} > V_{CB\_crit}$  at low  $J_C$ ), as shown in Figure 19 for three generations of SiGe HBT technology. This BV definition for CB- $I_E$  operation

Figure 18: CB - forced  $I_E$  output characteristic with associated BV thresholds.

is similar to, and provides consistent results with, the approach detailed in [30], but is better suited to BV extraction at very high operating current densities found in advanced SiGe HBTs, and takes into account the role of self-heating and parasitic base resistance under both pinched (low current and high voltage) and non-pinched (high current and low voltage) conditions.

A dramatic change in the nature of the BV threshold is observed at higher currents (for  $V_{BE} > 0.85$  V in Figure 17, and  $J_C > 2\text{mA}/\mu\text{m}^2$  in Figure 18), as self-heating becomes an important factor in the roll-off of  $V_{BE}$  with increasing  $V_{CB}$ . In this high-injection region, the defined BV threshold no longer corresponds with pinch-in instabilities, and at sufficiently high current levels, pinch-in is effectively suppressed [22]. Defining the  $CB-I_E$  BV with respect to  $V_{BE}$  acknowledges these important considerations at high injection, providing clear indication of the prudent bias limits, even in regions where pinch-in no longer plays a significant role in device behavior. Reliability aspects of this voltage limit associated with hot-carrier degradation at high current will be explored further in Chapter III.

Figure 19:  $V_{BE}$  characteristics from CB - forced  $I_E$  measurements at low and high injection for three generations of SiGe HBTs.

### 2.3 Experimental Characterization

#### 2.3.1 Experiment

Samples from three generations of commercially available SiGe HBT technology (50 GHz, 120 GHz, and 200 GHz peak  $f_T$ ) were measured at dc under various bias conditions (*CE*- $I_B$ , *CE*- $V_{BE}$ , *CB*- $I_E$ ) to characterize and compare breakdown effects and operating voltage constraints across technology generation. These measurements were performed on-wafer using the Agilent 4155C Semiconductor Parameter Analyzer. For this study, both high  $f_T$  (HP, or low BV) and high breakdown (HB) devices were characterized.

#### 2.3.2 High Performance Results

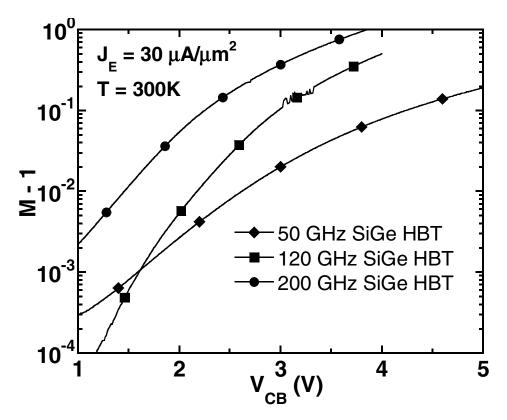

The M - 1 characteristics for the three SiGe HBT technology generations of interest are plotted as a function of  $V_{CB}$  in Figure 20. Figure 21 shows, for a specified  $V_{CB}$ , the significant increase in the avalanche multiplication factor as peak  $f_T$  rises, as was described

**Figure 20:** M - 1 characteristics for three generations of high performance SiGe HBT technology.

in Chapter I. Measured CE- $I_B$ , CE- $V_{BE}$ , and CB- $I_E$  BV thresholds, as defined in the previous section and normalized to  $J_C$  at peak  $f_T$ , are shown as a function of technology generation in Figures 22, 23, and 24. The transition from CE operation driven by constant  $V_{BE}$  (zero  $\Omega$  external impedance between base and emitter terminals) to constant  $I_B$  drive (infinite external impedance on the base terminal) is depicted in the set of curves of increased external base resistance in Figure 22. As demonstrated in these results, transgenerational device scaling for increased peak  $f_T$  is accompanied with strong decreases in BV for all bias configurations, although  $r_B$  optimization between the 120 GHz and 200 GHz generations dramatically offsets this trend, allowing the 200 GHz SiGe device to sustain approximately the same pinch-in  $V_{CE}$  as the 120 GHz SiGe device [3].

Overall, these results also show that the CB- $I_E$  bias configuration allows a substantially higher maximum collector voltage than does the CE- $I_B$  for all three SiGe HBT generations. The corresponding dependency of BV on injection level is also apparent.

Figure 21: M - 1 at constant  $V_{CB} = 3$  V as a function of SiGe HBT technology generation.

At low injection, the  $CE-V_{BE}$  and  $CB-I_E$  results are strikingly similar, as predicted by Equations (22) through (29), which describe the critical reverse base current and critical collector-base voltage thresholds. However, at high injection these characteristics diverge as self-heating effects begin to strongly influence the *dc* behavior of the device operating in the  $CE-V_{BE}$  configuration and degrade its SOA. Self-heating will be discussed in further detail in Chapter III.

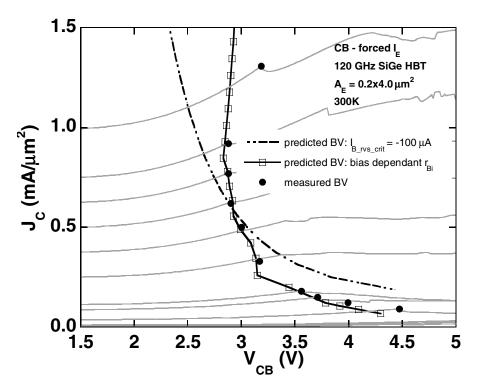

Figure 25 shows a comparison between measured  $V_{CB}$  at pinch-in (solid circles) and the maximum  $V_{CB\_crit}$  calculated using Equation (27) (broken and solid lines) for low injection values of  $I_E$  in a 120 GHz SiGe HBT. M-1 was measured using the forced emitter-current method [14]. The resulting avalanche factor fitting parameters c and a (see Equations (26), (27), and (28)) for this device were found to be 0.0015414 and 4.8164, respectively. For the device geometry examined, (0.2 x 4.0  $\mu$ m<sup>2</sup>) the factor G (see Equations (22), (23), and (28)) was determined to be approximately 1.6. The broken line in Figure 25 shows

**Figure 22:** CE - forced  $I_B$  BV thresholds for three generations of SiGe HBT technology. An external resistance on the base terminal is varied between 0  $\Omega$  (CE operation with fixed  $V_{BE}$  drive) and 1 M $\Omega$  for the 50 GHz peak  $f_T$  device.

Figure 23: CE - forced  $V_{BE}$  BV thresholds for three generations of SiGe HBT technology.

Figure 24: CB - forced  $I_E$  BV threshold for three generations of SiGe HBT technology.

the approximation that can be achieved by simply assuming a constant  $I_{B_rvs\_crit}$  of  $-100 \ \mu$ A for all biases. This simplification can serve as a quick-and-dirty guide for predicting low-injection breakdown instabilities by simply using the voltage dependent M - 1 characteristic. However, typical *CB*-*I*<sub>E</sub> measurements show a significant bias dependence for  $I_{B_rvs\_crit}$  (increases strongly as  $I_E$  increases), primarily due to changes in  $r_B$  and  $I_E$ . Therefore, a much better fit can be achieved if the bias dependence of  $r_B$  (even assuming constant  $r_E$  across bias, as in this case) is accounted for, as demonstrated by the close fit between these calculated values (open squares) and the measured pinch-in  $V_{CB}$  values in Figure 25. Extending this close fit to even higher injection levels (above approximately 1.0 mA in this case) requires careful characterization of the bias dependence of both M - 1and  $r_E$ .

Figure 25: Comparison between measured and calculated CB- $I_E$  pinch-in instabilities.

**Table 2:** Relevant breakdown parameters for HB devices for three SiGe BiCMOS technology generations.

| SiGe BiCMOS Technology                                | 1st generation | 2nd generation | 3rd generation |

|-------------------------------------------------------|----------------|----------------|----------------|

| SiGe HBT BV Parameters                                | (IBM 5HP)      | (IBM 7HP)      | (IBM 8HP)      |

| $BV_{CEO}(V)$                                         | 5.4            | 5              | 4              |

| $BV_{CBO}$ (V)                                        | 14.5           | 12.5           | 11             |

| $J_C$ at $\beta$ roll-off (mA/ $\mu$ m <sup>2</sup> ) | 0.30           | 0.20           | 1.60           |

#### 2.3.3 High Breakdown Results

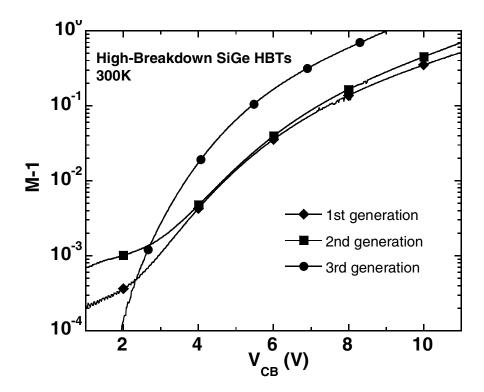

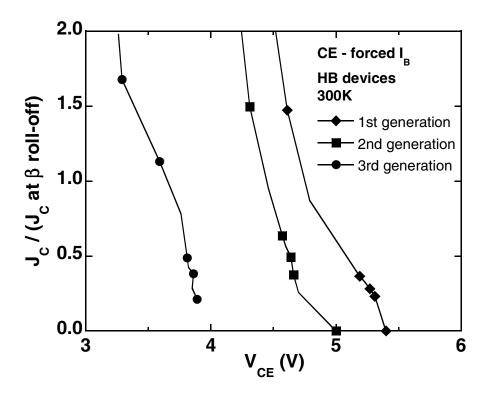

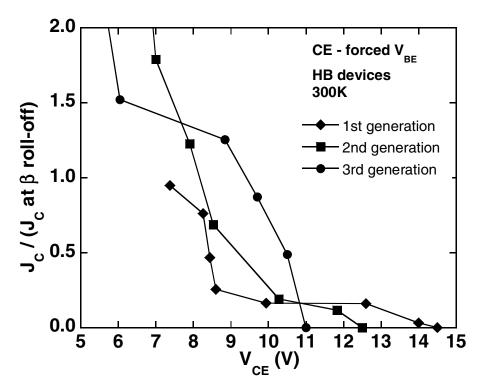

An overview of the relevant BV parameters for the high breakdown (HB) devices from the three SiGe HBT BiCMOS technology generations of interest is provided in Table 2. The M - 1 characteristics were experimentally measured and plotted as a function of  $V_{CB}$ for these HB devices in Figure 26. It is worth noting that M - 1 for the first and second generation HB devices is quite similar, although the third generation HB device shows significantly higher M - 1. Figure 27 shows the  $CE - I_B$  BV characteristics for the HB devices experimentally extracted across the three technology generations. The characteristics are

Figure 26: M - 1 characteristics for HB devices from three generations of SiGe HBT technology.

normalized to the  $J_C$  at which strong  $\beta$  degradation is observed (as given in Table 2) to allow comparison between technology generations. Similar to the HP results shown in Figure 22, degradation in the BV threshold is observed between technology generations due to increases in M - 1 and  $\beta$  with technology scaling. However, in the HB case, the  $CE-I_B$ BV thresholds show a decrease with increasing injection.