# A COORDINATED APPROACH TO RECONFIGURABLE ANALOG SIGNAL PROCESSING

A Dissertation

Presented to

The Academic Faculty

By

Craig R. Schlottmann

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology August 2012

Copyright © 2012 by Craig R. Schlottmann

## A COORDINATED APPROACH TO

## RECONFIGURABLE ANALOG SIGNAL PROCESSING

## Approved by:

Dr. Jennifer Hasler, Advisor Professor, School of ECE Georgia Institute of Technology Atlanta, GA

Dr. David V. Anderson Professor, School of ECE Georgia Institute of Technology Atlanta, GA

Dr. Aaron D. Lanterman Assoc. Professor, School of ECE Georgia Institute of Technology Atlanta, GA Dr. James H. McClellan Professor, School of ECE Georgia Institute of Technology Atlanta, GA

Dr. Mark T. Smith

Professor, Dept. of Communications Systems

Kungliga Tekniska Högskolan

Swedish Royal Institute of Technology

Stockholm, Sweden

Date Approved: June 13, 2012

## **ACKNOWLEDGMENTS**

First, I would like to thank my advisor, Jennifer Hasler, for her support and guidance. I would also like to thank my committee for their insight and helpful comments: David Anderson, Aaron Lanterman, Jim McClellan, and Mark Smith. Of course, this work would have been impossible without my ICE Lab colleagues. I thank them for creating a fun and interesting atmosphere.

I am very fortunate to have a loving and supportive family. I thank my Mom, Dad, and sister, Dawn, for their encouragement. Most of all, I can never repay my ever patient wife and editor, Shannon.

# TABLE OF CONTENTS

| ACKNOWLEDGMENTS iii |        |                                                  |      |

|---------------------|--------|--------------------------------------------------|------|

| LIST O              | F TABL | LES                                              | vii  |

| LIST O              | F FIGU | RES                                              | viii |

| SUMM                | ARY .  |                                                  | xii  |

| СНАРТ               | ER 1   | INTRODUCTION TO ANALOG SIGNAL PROCESSING $\dots$ | 1    |

| СНАРТ               | ER 2   | FUNDAMENTAL BACKGROUND                           | 6    |

| 2.1                 | Floati | ing-Gate MOSFETs                                 | 6    |

|                     | 2.1.1  | Floating-Gate Transistor Characteristics         | 7    |

|                     | 2.1.2  | Floating-Gate Charge Modification                | 8    |

|                     | 2.1.3  | Array Programming                                | 10   |

| 2.2                 | The F  | Field-Programmable Analog Array                  |      |

|                     | 2.2.1  | FPAA Topologies                                  | 12   |

|                     | 2.2.2  | The Reconfigurable Analog Signal Processor       | 14   |

| СНАРТ               | ER 3   | THE MITE FPAA                                    | 20   |

| 3.1                 | Multi  | ple Input Translinear Elements                   | 22   |

|                     | 3.1.1  | Building Block: Translinear Loops                | 23   |

|                     | 3.1.2  | Building Block: Filters                          |      |

| 3.2                 | Recor  | nfigurable Architecture                          | 27   |

|                     | 3.2.1  | System Architecture                              |      |

|                     | 3.2.2  | The MITE CAB                                     | 28   |

|                     | 3.2.3  | The I/O CAB                                      | 30   |

| 3.3                 | The D  | Design Flow                                      | 31   |

|                     | 3.3.1  | Network Synthesis                                | 31   |

|                     | 3.3.2  | Place-and-Route                                  |      |

| 3.4                 | Resul  | ts                                               | 34   |

|                     | 3.4.1  | Static Examples                                  | 36   |

|                     | 3.4.2  | Dynamic Examples                                 | 36   |

| 3.5                 | Concl  | lusion                                           | 43   |

| СНАРТ               | ER 4   | A DIGITALLY ENHANCED FPAA: THE RASP 2.9V         | 45   |

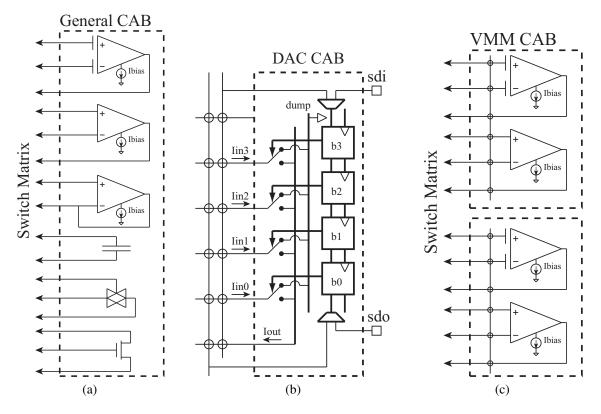

| 4.1                 | Proce  | ssing Elements                                   | 47   |

|                     | 4.1.1  | The General Analog CAB                           | 49   |

|                     | 4.1.2  | The DAC CAB                                      | 50   |

|                     | 4.1.3  | The VMM CAB                                      | 51   |

| 4.2                 |        | ng and Analog Switches                           | 52   |

|                     | 4.2.1  | Routing                                          | 52   |

|                     | 4.2.2  | Non-Volatile Switches                            | 54   |

|       | 4.2.3       | Volatile Switches                           | 56  |

|-------|-------------|---------------------------------------------|-----|

| 4.3   | Progra      | mming Methods                               | 59  |

| 4.4   | Result      | s and Applications                          | 60  |

|       | 4.4.1       | Programmable DAC Core                       | 61  |

|       | 4.4.2       | VMM Applications                            | 63  |

|       | 4.4.3       | Arbitrary Waveform Generator                | 65  |

|       | 4.4.4       | Mixed-Signal FIR Filter                     | 68  |

| 4.5   | Conclu      | asion                                       | 71  |

| CHAPT | ER 5        | SYSTEM DESIGN: THE VECTOR-MATRIX MULTIPLIER | 72  |

| 5.1   | Buildi      | ng a VMM on FPAA Hardware                   | 73  |

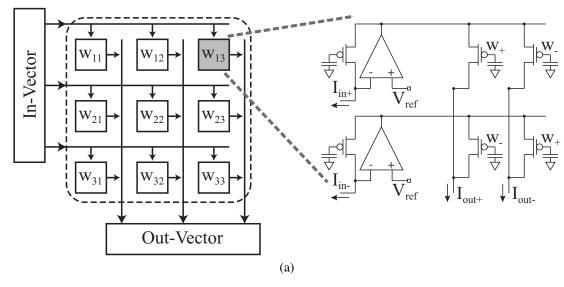

|       | 5.1.1       | Analog Vector-Matrix Multiplication         | 73  |

|       | 5.1.2       | Signal Conditioning                         | 77  |

| 5.2   | Power.      | , Speed, Noise, and Temperature Performance | 78  |

|       | 5.2.1       | The Power-Speed Tradeoff                    | 78  |

|       | 5.2.2       | Noise Performance                           | 81  |

|       | 5.2.3       | Temperature Dependence                      | 83  |

| 5.3   | Metho       | ds and Tools for FPAA VMMs                  | 86  |

|       | 5.3.1       | FPAA Density                                | 86  |

|       | 5.3.2       | Compiler Tools                              | 88  |

|       | 5.3.3       | Supporting Blocks                           | 91  |

| 5.4   | Conclu      | asion                                       | 91  |

| CHAPT | <b>ER 6</b> | HIGH-LEVEL DESIGN TOOLS                     | 93  |

| 6.1   |             | g Synthesis                                 | 94  |

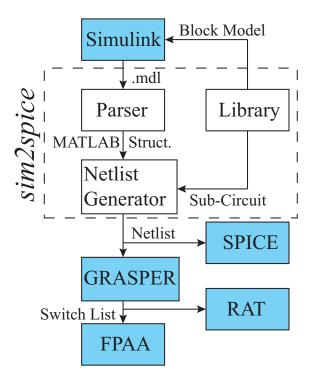

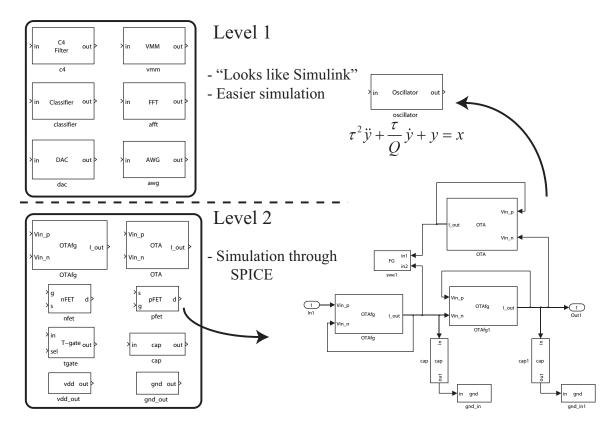

| 6.2   | From        | Simulink to SPICE: Sim2Spice                | 95  |

|       | 6.2.1       | Simulink Model Parser                       | 95  |

|       | 6.2.2       | SPICE Netlist Generator                     | 96  |

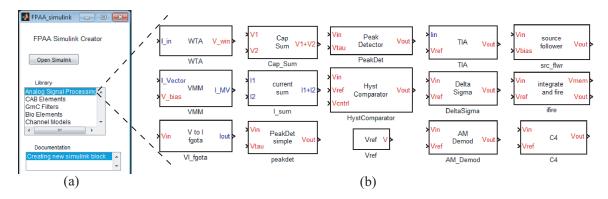

|       | 6.2.3       | Component Library                           | 97  |

|       | 6.2.4       | Macromodeling                               | 99  |

| 6.3   | From S      | SPICE to Analog Hardware                    |     |

|       | 6.3.1       | Place-and-Route                             | 102 |

|       | 6.3.2       | SPICE Library                               | 102 |

|       | 6.3.3       | RAT Visualization Tool                      | 104 |

|       | 6.3.4       | Program & Evaluation Board                  | 105 |

|       | 6.3.5       | Current FPAA Chips                          | 106 |

| 6.4   | Examp       | ole Systems                                 | 108 |

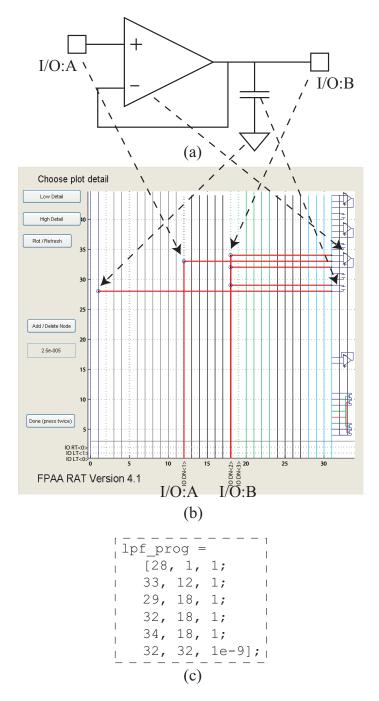

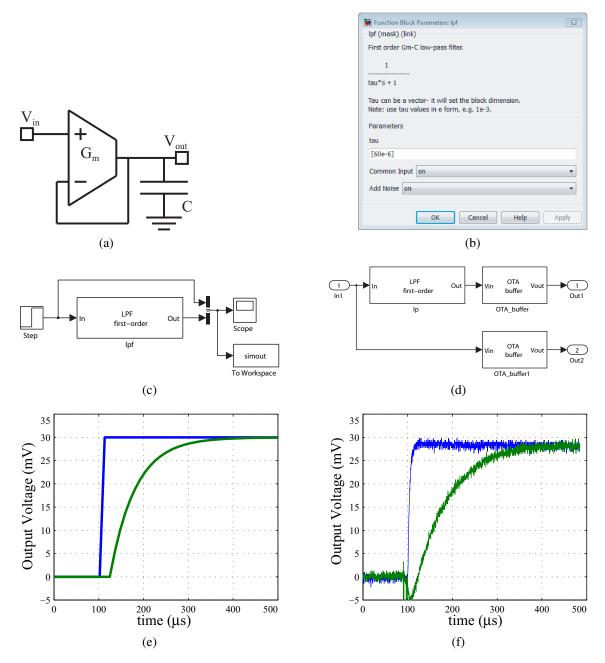

|       | 6.4.1       | Low-Pass Filter                             | 108 |

|       | 6.4.2       | Computational Neuron Systems                | 109 |

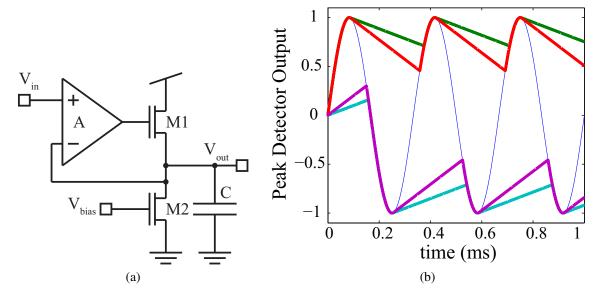

|       | 6.4.3       | VMM-WTA                                     | 110 |

| 6.5   | Conclu      | asion                                       | 113 |

| <b>CHAPTE</b> | CR 7  | ANALOG MACROMODELING                   | . 116 |

|---------------|-------|----------------------------------------|-------|

| 7.1           | Basic | c Analog Signal Processing Blocks      | . 117 |

|               | 7.1.1 | Vector-Matrix Multiplier               | . 117 |

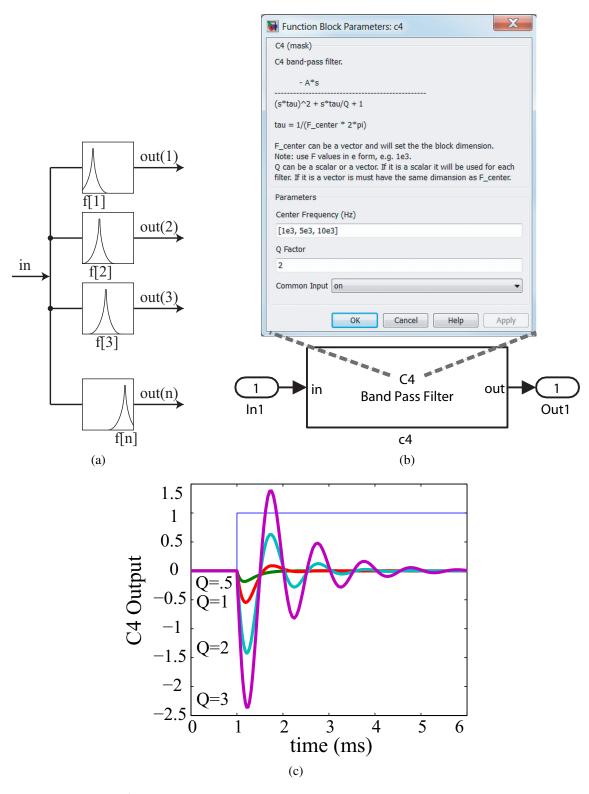

|               | 7.1.2 | Band-Pass Filter                       | . 117 |

|               | 7.1.3 | Winner-Take-All                        | . 118 |

| 7.2           | Analo | og Abstraction Concepts                | . 118 |

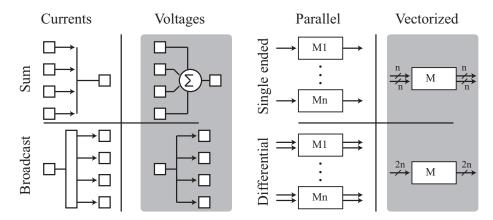

|               | 7.2.1 | High-Level Analog Design With Simulink | . 118 |

|               | 7.2.2 | Voltage Mode Systems                   | . 120 |

|               | 7.2.3 | Vectorized Signals                     | . 121 |

|               | 7.2.4 | Biasing                                | . 121 |

| 7.3           | Analo | og Modeling Techniques                 | . 122 |

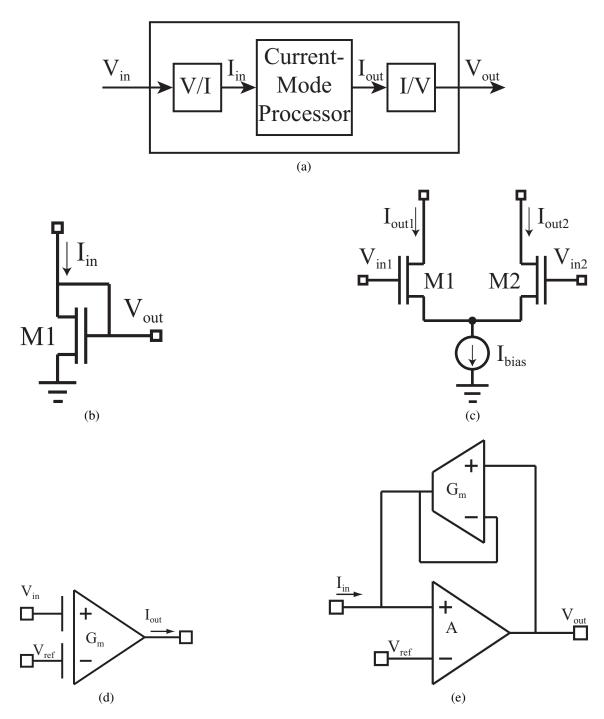

|               | 7.3.1 | Nonlinearities                         | . 122 |

|               | 7.3.2 | Noise                                  | . 128 |

|               | 7.3.3 | Voltage-In to Voltage-Out              | . 129 |

| 7.4           | The P | Process of Functional-Level Modeling   | . 132 |

|               | 7.4.1 | Vector-Matrix Multiplier               | . 132 |

|               | 7.4.2 | C <sup>4</sup> Band-Pass Filter        | . 136 |

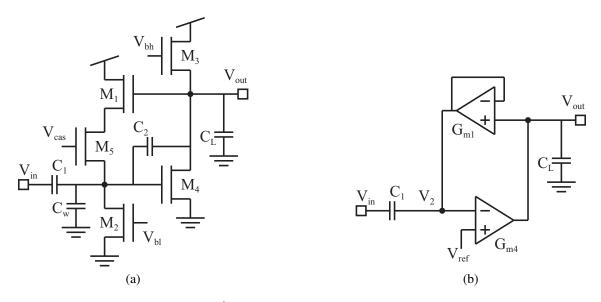

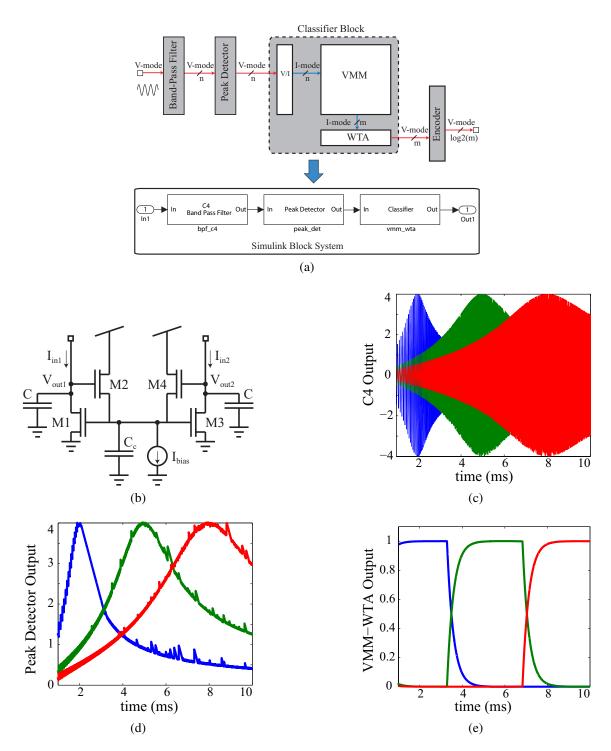

|               | 7.4.3 | Peak Detector                          | . 140 |

| 7.5           | Case  | Study: Classifier System               | . 142 |

| 7.6           | Tools | s for IC Experts                       | . 146 |

| 7.7           | Conc  | clusion                                | . 148 |

| СНАРТЕ        | CR 8  | CONCLUSION                             | . 150 |

| 8.1           | Sumn  | mary of this Dissertation              | . 150 |

| 8.2           | Perso | onal Contributions                     | . 152 |

| 8.3           | Futur | re Directions of this Work             | . 153 |

| REFERE        | NCES  | S                                      | . 155 |

| VITA          |       |                                        | 162   |

# LIST OF TABLES

| Table 1  | RASP 2.8a device parameters                  |

|----------|----------------------------------------------|

| Table 2  | RASP 2.8a routing line capacitance values    |

| Table 3  | MITE FPAA translinear loop exponent patterns |

| Table 4  | MITE FPAA device parameters                  |

| Table 5  | RASP 2.9v device parameters                  |

| Table 6  | RASP 2.9v system performance                 |

| Table 7  | Analog VMM performance parameters            |

| Table 8  | Macromodel of the first-order linear filter  |

| Table 9  | Macromodel of the VMM                        |

| Table 10 | Macromodel of the $C^4$ linear filter        |

# LIST OF FIGURES

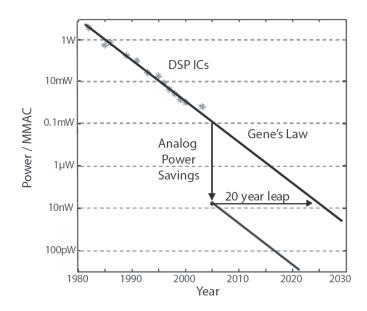

| Figure 1  | Gene's law of DSP power efficiency                                         | 2  |

|-----------|----------------------------------------------------------------------------|----|

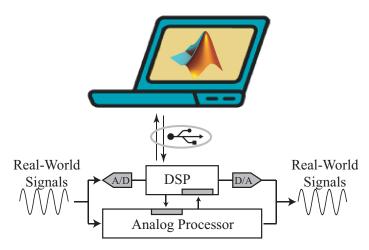

| Figure 2  | Embedded analog signal processing flow                                     | 3  |

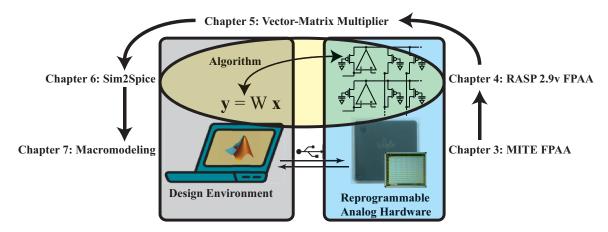

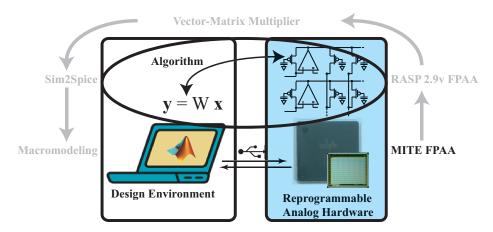

| Figure 3  | Diagram of the coordinated approach to FPAA design                         | 4  |

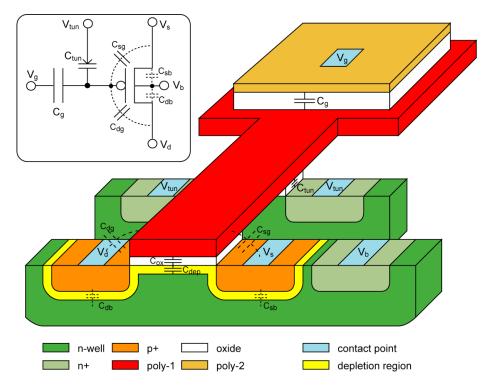

| Figure 4  | Floating-gate transistor schematic and layout                              | 7  |

| Figure 5  | Band diagram of electron tunneling                                         | 8  |

| Figure 6  | Channel diagram of hot-electron injection                                  | 9  |

| Figure 7  | Floating-gate array isolation                                              | 10 |

| Figure 8  | Indirect floating-gate switch cell                                         | 11 |

| Figure 9  | The three types of FPAA switches                                           | 15 |

| Figure 10 | The architecture of the RASP 2.8 FPAA                                      | 16 |

| Figure 11 | RASP 2.8a layout                                                           | 18 |

| Figure 12 | RASP 2.8a die photo                                                        | 19 |

| Figure 13 | The coordinated approach to FPAA design: MITE FPAA                         | 20 |

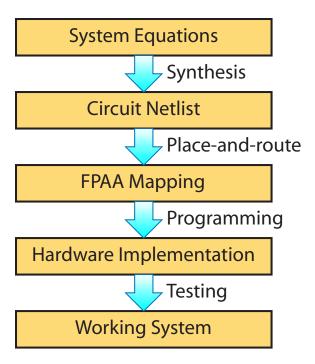

| Figure 14 | Design flow using a translinear FPAA                                       | 21 |

| Figure 15 | Subthreshold pFET realization of a MITE                                    | 22 |

| Figure 16 | MITE implementation of a $2^{nd}$ -order translinear loop                  | 24 |

| Figure 17 | MITE implementation of a 1 <sup>st</sup> -order low-pass log-domain filter | 26 |

| Figure 18 | Architecture of the MITE FPAA                                              | 27 |

| Figure 19 | Layout of the MITE FPAA                                                    | 28 |

| Figure 20 | Basic MITE computation element of the MITE FPAA                            | 29 |

| Figure 21 | V-to-I converter used in the MITE FPAA                                     | 31 |

| Figure 22 | A representation of equation parsing for the MITE FPAA                     | 32 |

| Figure 23 | Visualization GUI for interfacing with the MITE FPAA                       | 35 |

| Figure 24 | Results of a multiplication circuit implemented with the MITE FPAA         | 37 |

| Figure 25 | Results of a squaring circuit implemented with the MITE FPAA               | 38 |

| Figure 26 | Cube root circuit implemented with the MITE FPAA                        | 39 |

|-----------|-------------------------------------------------------------------------|----|

| Figure 27 | Results of a cube root circuit on the MITE FPAA                         | 40 |

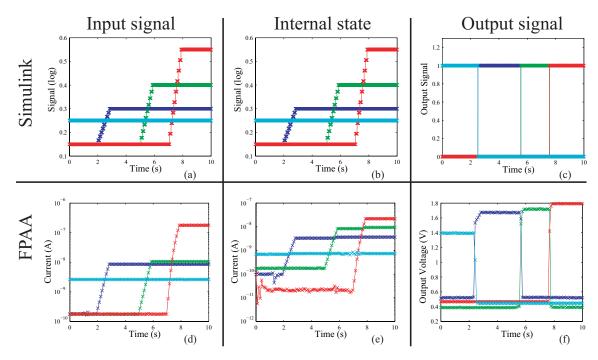

| Figure 28 | Results of a log-domain filter implemented with the MITE FPAA           | 41 |

| Figure 29 | Results of a log-domain high-pass filter implemented with the MITE FPAA | 42 |

| Figure 30 | Results of the RMS-to-DC converter implemented with the MITE FPAA.      | 44 |

| Figure 31 | The coordinated approach to FPAA design: RASP 2.9v                      | 45 |

| Figure 32 | Layout and architecture of the RASP 2.9v FPAA                           | 48 |

| Figure 33 | Structure of the RASP 2.9v CABs                                         | 49 |

| Figure 34 | Schematic of the 9-transistor OTA                                       | 51 |

| Figure 35 | The RASP 2.9v CABs are arranged in 13 rows and 6 columns                | 53 |

| Figure 36 | The indirect and direct routing FG switches                             | 55 |

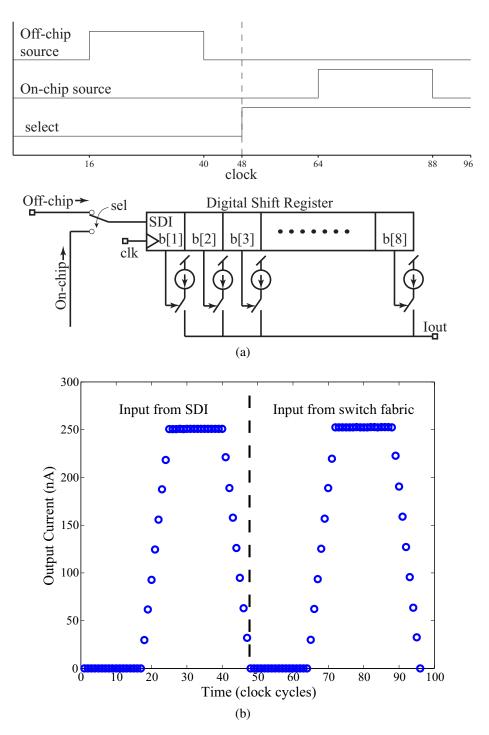

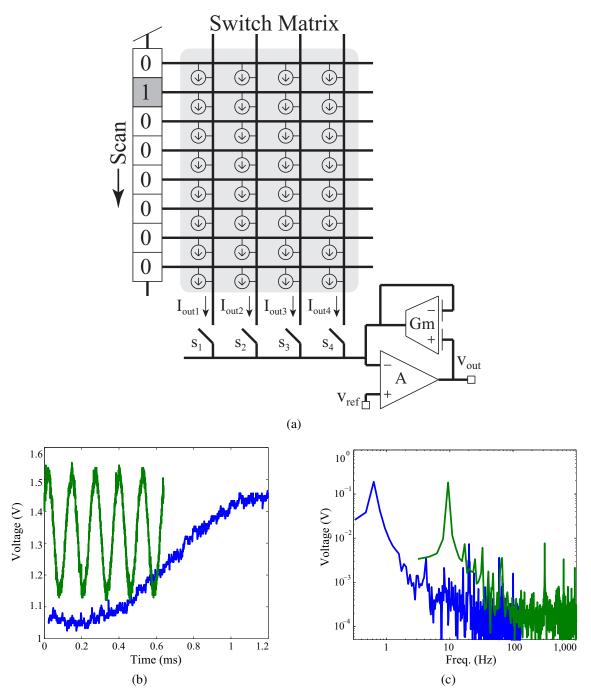

| Figure 37 | Diagram of a measurement test with the volatile switches                | 57 |

| Figure 38 | Example of the volatile registers using on- and off-chip data           | 58 |

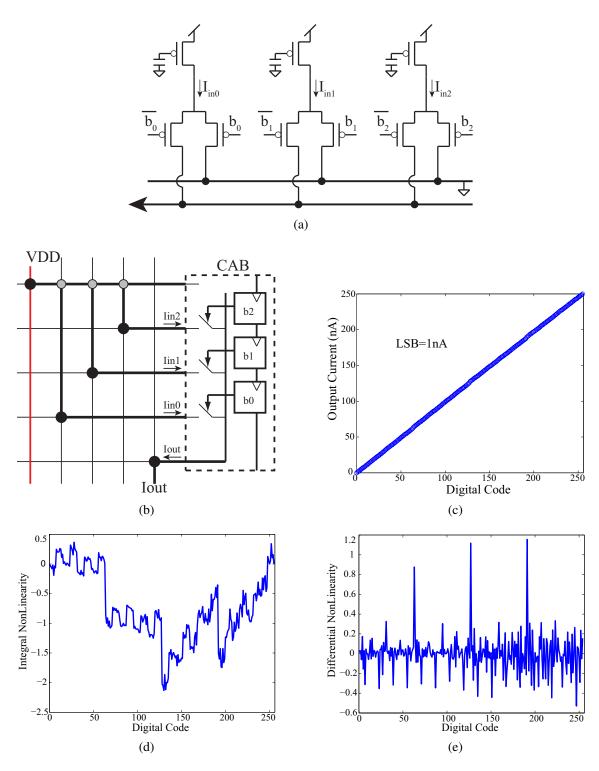

| Figure 39 | The RASP 2.9v on-chip compilable DAC                                    | 62 |

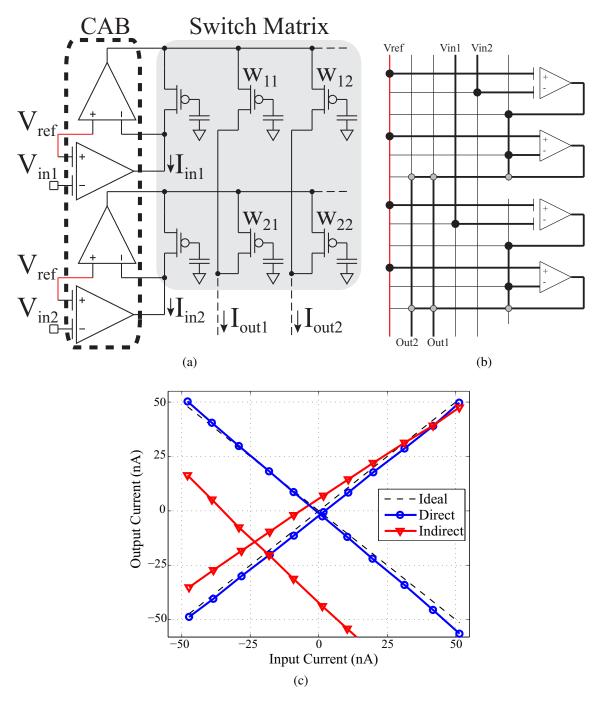

| Figure 40 | The RASP 2.9v implementation of a VMM                                   | 64 |

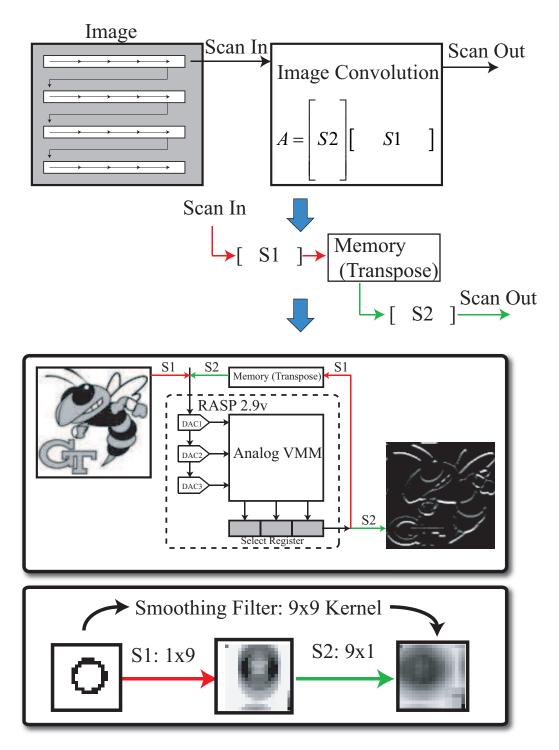

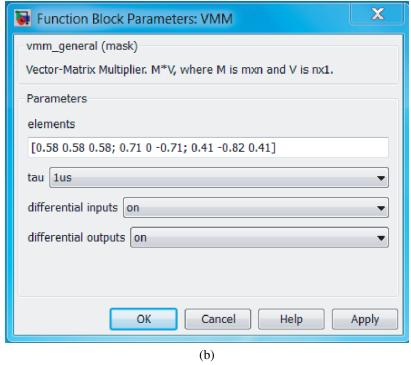

| Figure 41 | Image transform with the RASP 2.9v VMM                                  | 66 |

| Figure 42 | The RASP 2.9v implementation of an arbitrary waveform generator         | 67 |

| Figure 43 | The RASP 2.9v implementation of a mixed-signal FIR filter               | 70 |

| Figure 44 | The coordinated approach to FPAA design: VMM                            | 72 |

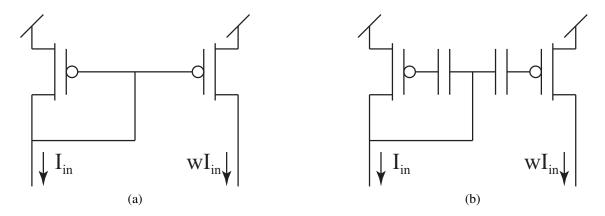

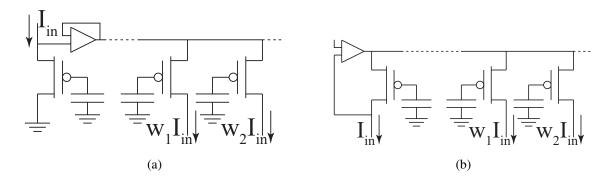

| Figure 45 | Two implementations of a current-scaling mirror                         | 74 |

| Figure 46 | Two implementations of a source-coupled FG current mirror               | 75 |

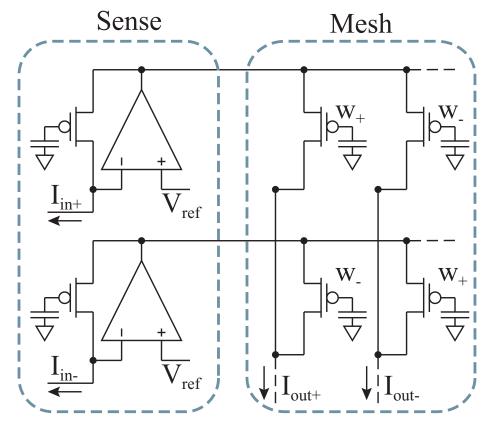

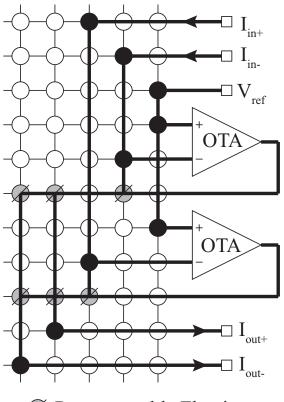

| Figure 47 | Schematic of the analog VMM circuit                                     | 76 |

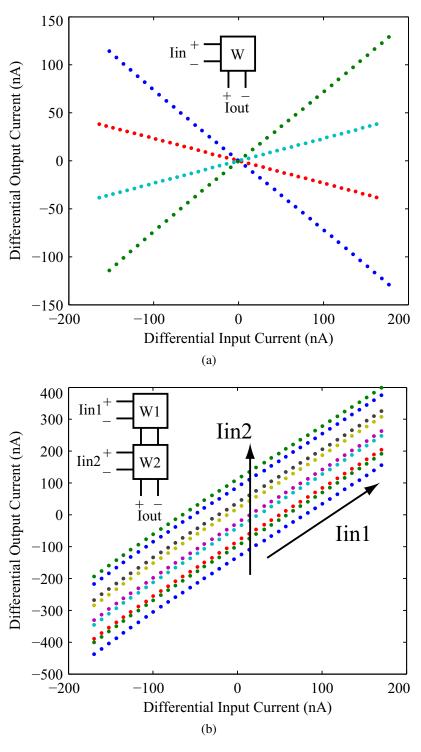

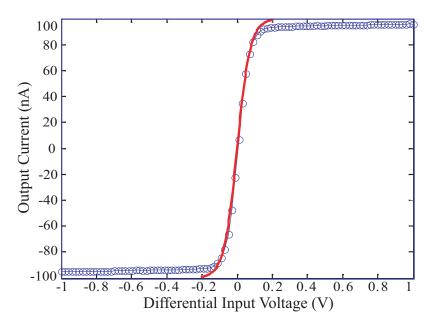

| Figure 48 | VMM current mode sweeps                                                 | 79 |

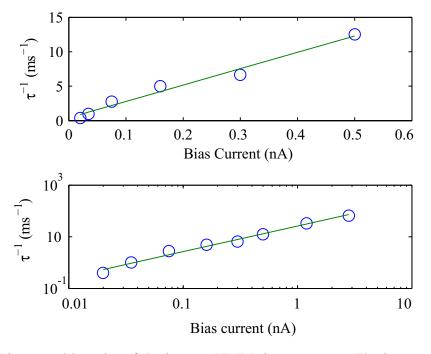

| Figure 49 | The VMM time constant                                                   | 80 |

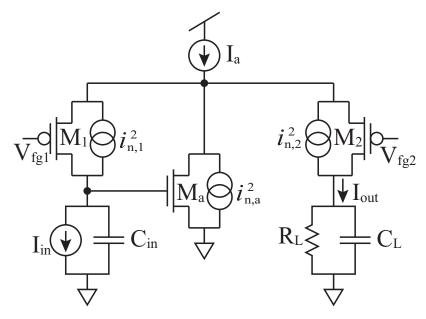

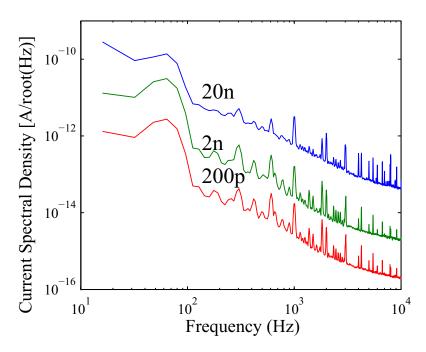

| Figure 50 | Schematic of the VMM noise model                                        | 81 |

| Figure 51 | Current spectral density of the VMM noise                               | 83 |

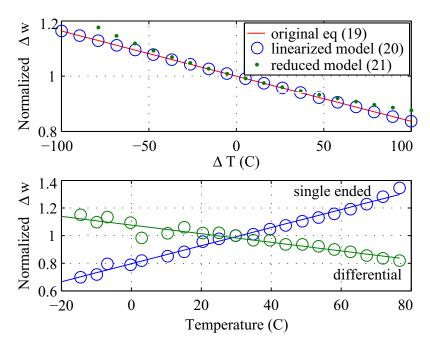

| Figure 52 | Temperature dependence of the VMM weight                             |

|-----------|----------------------------------------------------------------------|

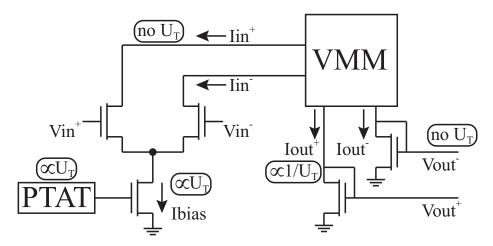

| Figure 53 | Schematic of the VMM temperature compensation circuitry 85           |

| Figure 54 | Map of the $2 \times 2$ VMM implemented with FPAA switches 87        |

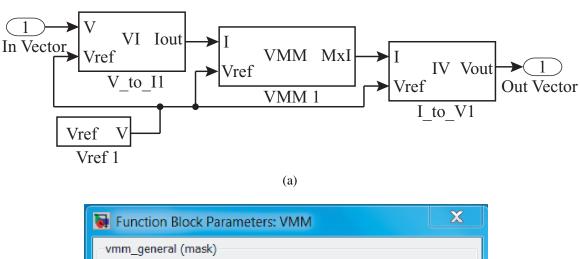

| Figure 55 | Simulink block-level design for a VMM system                         |

| Figure 56 | VMM visualization with the RAT tool                                  |

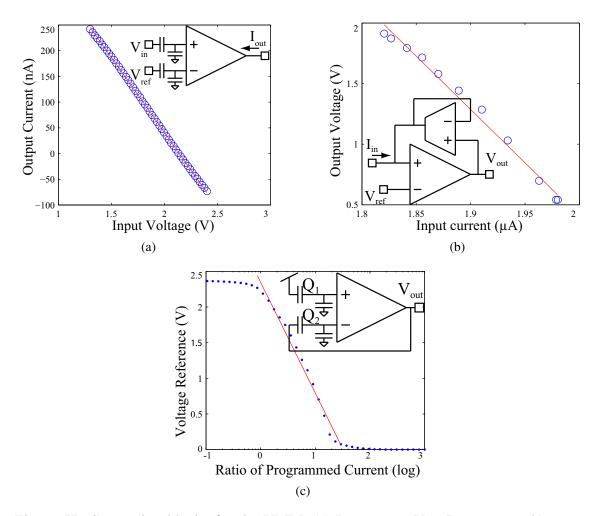

| Figure 57 | Supporting blocks for the VMM                                        |

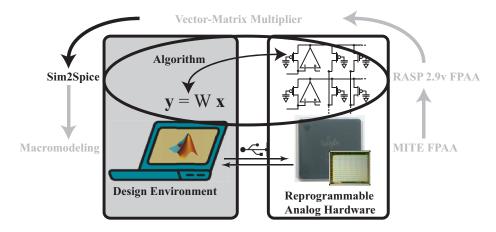

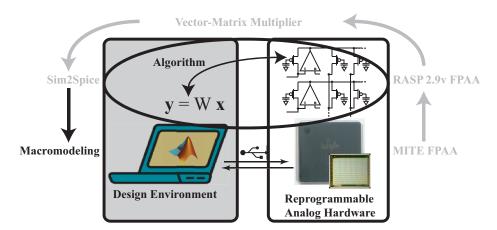

| Figure 58 | The coordinated approach to FPAA design: Sim2Spice                   |

| Figure 59 | The Sim2Spice program flow                                           |

| Figure 60 | Example Simulink model file                                          |

| Figure 61 | The Simulink component library                                       |

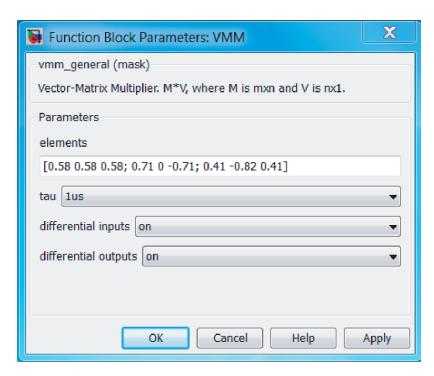

| Figure 62 | The Simulink parameter window                                        |

| Figure 63 | The OTA model                                                        |

| Figure 64 | RAT visualization of a low-pass filter                               |

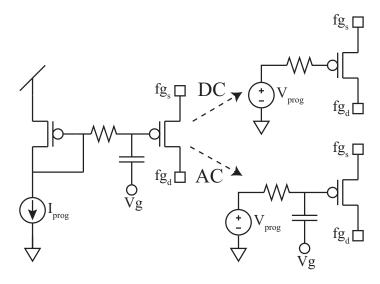

| Figure 65 | Floating gate SPICE model                                            |

| Figure 66 | The Program & Evaluation board                                       |

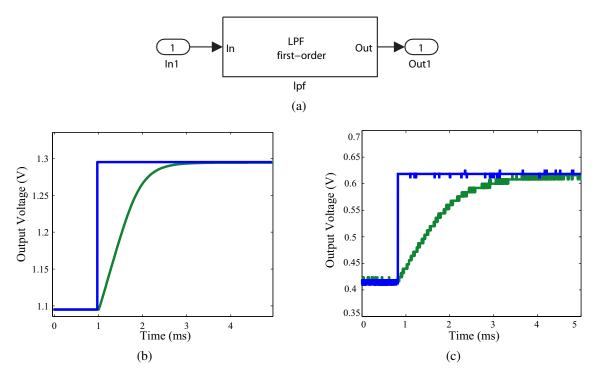

| Figure 67 | Simulink model of the low-pass filter                                |

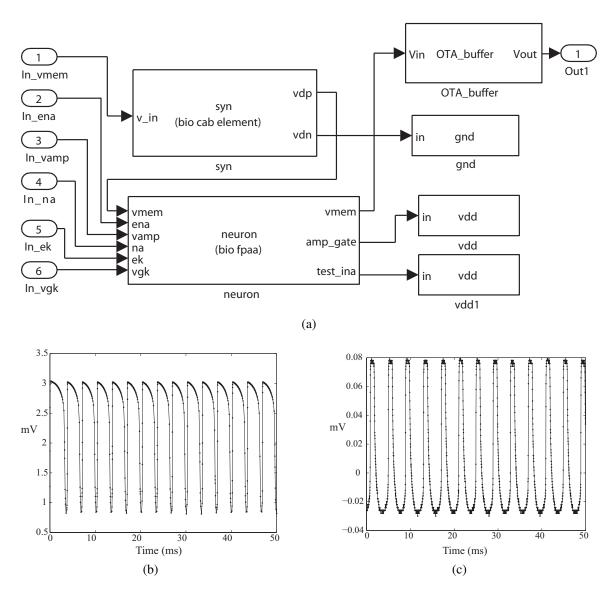

| Figure 68 | Simulink model of the spiking neuron system                          |

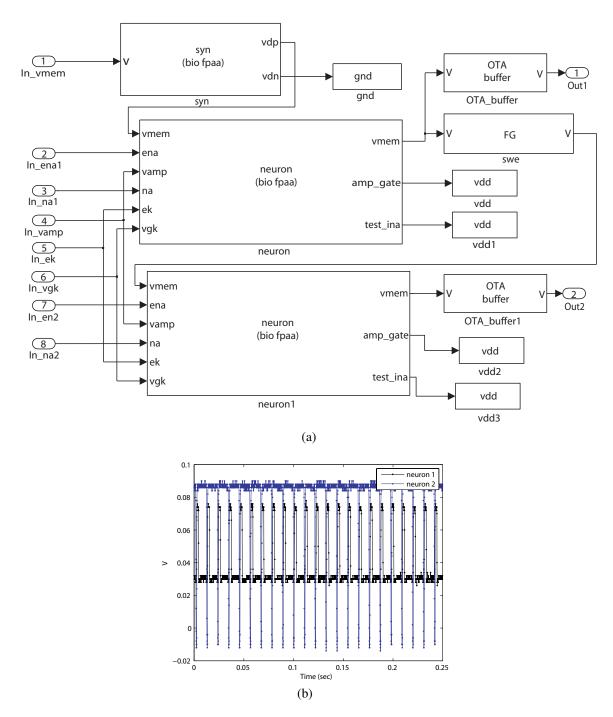

| Figure 69 | Simulink model of two neurons and a synapse                          |

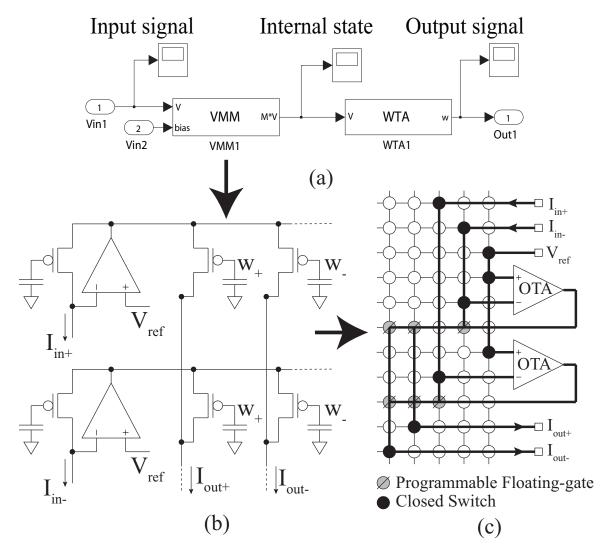

| Figure 70 | The three phases of implementation for the VMM-WTA system 114        |

| Figure 71 | Output of the VMM-WTA system                                         |

| Figure 72 | The coordinated approach to FPAA design: Macromodeling               |

| Figure 73 | Analog system abstraction and signal protocol                        |

| Figure 74 | Design and simulation of the LPF Simulink block                      |

| Figure 75 | Dynamics of the sinh function                                        |

| Figure 76 | Simulink simulation of the first order filter with noise enabled 128 |

| Figure 77 | Embedded voltage-mode stages into Simulink blocks                    |

| Figure 78 | Design of the VMM Simulink block                                     |

| Figure 79 | The $C^4$ band-pass filter system       |

|-----------|-----------------------------------------|

| Figure 80 | Schematics of the $C^4$ bandpass filter |

| Figure 81 | The peak detector system                |

| Figure 82 | The analog classifier system            |

| Figure 83 | The Level-1 and Level-2 libraries       |

#### **SUMMARY**

The purpose of this research is to create a solid framework for embedded system design with field-programmable analog arrays (FPAAs). To achieve this goal, we've created a unified approach to the three phases of FPAA system design: (1) the hardware architecture; (2) the circuit design and modeling; and (3) the high-level software tools.

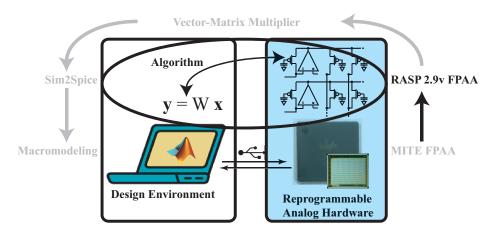

First, we describe innovations to the reconfigurable analog hardware that enable advanced signal processing and integration into embedded systems. We introduce the multiple-input translinear element (MITE) FPAA and the dynamically-reconfigurable RASP 2.9v FPAA, which was designed explicitly for interfacing with external digital systems. This compatibility creates a streamlined workflow for dropping the FPAA hardware into mixed-signal embedded systems.

The second phase, algorithm analysis and modeling, is important to create a useful and reliable library of components for the system designer. We discuss the concept and procedure of analog abstraction that empowers non-circuit design engineers to take full advantage of analog techniques. We use the analog vector-matrix multiplier as an example for a detailed discussion on computational analog analysis and system mapping to the FPAA.

Lastly, we describe high-level software tools, which are an absolute necessity for the design of large systems due to the size and complexity of modern FPAAs. We describe the Sim2Spice tool, which allows system designers to develop signal processing systems in the Simulink environment. The tool then compiles the system to the FPAA hardware.

By coordinating the development of these three phases, we've created a solid unified framework that empowers engineers to utilize FPAAs.

## CHAPTER 1

## INTRODUCTION TO ANALOG SIGNAL PROCESSING

Cooperative analog-digital signal processing (CADSP) is the design approach whereby the two domains (analog and digital) are used in combination to achieve advanced system performance [1]. In traditional systems, analog processing is used primarily for front-end amplification and data conversion, whereas the digital signal processor (DSP) handles the mathematical operations. By repartitioning the boundary between the processing domains, we stand to take advantage of extreme power and area savings. For instance, the natural physics of the subthreshold transistor can be used to perform many mathematical operations with a fraction of the number of devices required for digital computation [2] and a much lower total current draw.

Figure 1 illustrates Gene's law—a trend fit of the power efficiency progress for DSPs. The y-axis for this plot is in terms of the power required for performing a million multiply accumulate cycles a second (MMACS)—the most enlightening figure of merit for DSP power efficiency [3]. The result is striking when the performance of a *functionally equivalent* analog signal processor (ASP) is added to the plot [4]. Analog's computational efficiency is *several orders of magnitude* greater. This result was a (then) 20-year leap in efficiency, but the analog signal processor's advantage is compounded by the recent observation that the DSP is asymptotically approaching a power efficiency wall [5]. Now, analog processing is no longer simply just a "nice" opportunity for a quick leap, but rather, analog techniques will be *required* to meet future signal processing efficiency needs.

It is the efficient balancing of the analog and digital domains that the highest performance can be achieved. A popular subset of this concept is the notion of *digitally enhanced analog systems*, whereby digital processing is utilized to add resolution to analog blocks [6]. As a broader approach, CADSP additionally promotes the use of analog techniques to increase the power efficiency of digital blocks, as illustrated in the system of

Figure 1: Gene's law shows the power efficiency trend for digital signal processors. Analog signal processing poses a 20-year leap in efficiency.

Figure 2. CADSP techniques have been successfully utilized in such systems as compressive sensing [7] and classifiers [8]. However, two very important hurdles have prevented the wide-spread use of analog computation—the traditional lack of both programmability and intuitive system design tools.

The recent development of large-scale field-programmable analog arrays (FPAAs) has provided a stable platform for programmable analog systems. The reconfigurable analog signal processor (RASP) FPAA is a VLSI system that contains hundreds of configurable analog blocks (CABs) and allows for on-the-fly synthesis of large-scale analog systems.

The FPAA has provided the hardware platform to develop ASP systems, but the remaining fundamental problem is that it is not always easy for the typical DSP engineer to utilize analog techniques. To solve this problem, intuitive design tools are needed to empower the non-circuit designer to take advantage of the FPAA hardware. Simulink has been chosen as the top level design space for analog systems on FPAAs in order to appeal to the broadest audience of DSP engineers. Although this design space is intuitive and makes systems easy to visualize and simulate, there has yet to be an established framework for the proper abstraction of analog design. The development of a high-level framework for abstracting

Figure 2: The analog processor embedded with a digital processor provides a power efficient platform. The incoming signal can be processed by the FPAA, the DSP, or by a combination of both. A custom Matlab toolbox is used to program and control the mixed-mode processor.

analog design and creating behavioral analog blocks is necessary to bridge the analog and digital design gap for the system engineer.

The goal of this work is to define a coordinated approach for FPAA system design. A guiding role model in this endeavor is the Mead-Conway digital revolution of the 1980s [9]. Carver Mead and Lynn Conway helped to spark the VLSI boom by unifying the fields of computer architecture, integrated circuit design, and semiconductor device physics. Their work demystified the process for the system designer and increased the number of engineers entering the field. Their methodology for the merging of disciplines was based on presenting a small set of key concepts from a range of topics in order to carry along the least amount of mental baggage from topic to topic.

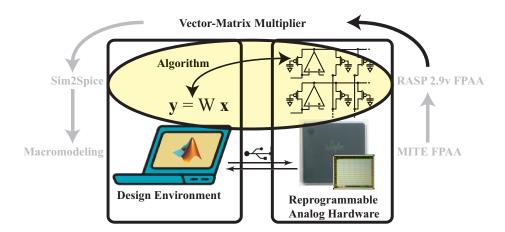

With the Mead-Conway approach in mind, we are attempting to unify the three phases of FPAA design: (1) the hardware architecture; (2) the circuit design and modeling; and (3) the high-level software tools. We are attempting to abstract the analog design to allow the system design engineer to take advantage of the benefits of analog technology. This approach is illustrated in Figure 3. The figure shows how the three areas of FPAA design overlap and how this dissertation will proceed.

Figure 3: Diagram of the coordinated approach to FPAA design.

Chapter 2 provides a review the fundamental background technology. The two key elements covered are floating-gate transistors and field-programmable analog arrays. The floating gate (FG) is important for analog storage, and the FG transistor is used as a switch as well as for computation. We review the device characteristics—including subthreshold operation—as well as the processes for adding and removing charge from the gate. In the review of FPAA technology, we go over a brief history of their evolution and describe some of the various architectures that have been tried. We then provide a detailed description of the RASP FPAA, which will be the hardware platform used in the rest of this dissertation.

Chapter 3 introduces the multiple-input translinear element (MITE) FPAA. This architecture is based on the MITE as a circuit primitive, which is ideal for computing polynomial equations. There is a robust body of work on the synthesis of high-order static and dynamic equations to systems of MITEs, which makes it an ideal platform to get started with analog signal processing.

Chapter 4 introduces the RASP 2.9v, a next-generation FPAA architecture that is optimized for embedded systems. This architecture was motivated by the need for higher-level digital control for dynamic reconfigurability. The controllability allows the FPAA to be much more easily fielded in embedded electronic systems.

Chapter 5 presents the analog vector-matrix multiplier (VMM) as a bottom-up case

study for the analysis of a computational analog element and its mapping to the FPAA architecture. The VMM is one of "killer apps" of analog computation in that it efficiently computes a very common signal processing function. The circuit design process includes the step-by-step choices motivated by the architecture of the FPAA hardware. The circuit analysis includes a description of the system's power, speed, noise, and temperature dependence.

Chapter 6 introduces the high-level software tools for FPAA configuration. The top-level design space is Simulink, which provides an intuitive platform for designing signal processing systems with functional blocks. The core elements of this system are the component library and the FPAA compilers. The component library contains abstracted analog blocks that allow non-circuit designers to create large systems with analog blocks. The compilers include two main tools: (1) Sim2Spice for converting Simulink designs to a circuit netlist; and (2) the GRASPER tool for converting the netlist to FPAA targeting code.

Chapter 7 discusses the challenges and opportunities of abstracted analog design. By defining a standard interface for the analog block library, designers can treat analog blocks more like their digital counterparts. This standardization provides a low barrier-to-entry for engineers who are skilled in the *problem domain* of signal processing, but may have limited experience in the *solution domain* of analog hardware. A major focus of this work is the creation of accurate, yet elegant, macromodels for the simulation and overall understanding of the function of the analog signal processing blocks.

Lastly, Chapter 8 recaps the overall impact of this dissertation. Personal contributions are noted and some directions are provided for the future of this work.

## **CHAPTER 2**

## FUNDAMENTAL BACKGROUND

This chapter provides a brief background on two core elements of technology for reconfigurable analog systems—the floating-gate transistor and the field-programmable analog array. Our intent is to introduce these topics and provide a self-contained document, but not delve too deep onto them (as per the Mead-Conway approach). We've provided a thorough set of references for further reading about each topic.

## 2.1 Floating-Gate MOSFETs

The fundamental piece of technology for the reconfigurable system is the floating-gate transistor. Originally reported in 1967 [10], these are ordinary transistors whose gates are then entirely surrounded by electrical insulation (i.e., with no DC path to ground), which allows stored charge to be retained. Floating-gate transistors have firmly established themselves in digital circuits as a reliable non-volatile memory storage, used in Flash and EEPROM. Recent research has been exploring their applications in analog circuits such as multiplier weights, neuromorphic synapses, analog memory, bias generation, and offset removal.

An important feature of these devices is that they can be fabricated in a standard CMOS process. The schematic and layout for a floating-gate pFET is shown in Figure 4. The polysilicon (poly 1) gate is shown in red has no direct contacts; it is completely surrounded by oxide. The floating node is actively controlled by two voltage signals capacitively coupled onto it: the tunneling voltage and the gate voltage. A MOS capacitor is used for tunneling because a high quality oxide is needed and a poly-poly capacitor is used for the gate voltage for its linearity.

Figure 4: Floating-gate transistor technology. The distinguishing feature is that the polysilicon gate is completely insulated by oxide. The input gate voltage is coupled in through a poly capacitor and the tunneling voltage through a MOS capacitor.

## 2.1.1 Floating-Gate Transistor Characteristics

To accurately use floating-gate transistors, the I-V relationship along with the stored charge's affects need to be defined. For low power operation, all FETs discussed in this dissertation will be operated in the subthreshold (weak inversion) region. In subthreshold, the drain current ( $I_D$ ) is given as

$$I_D = I_0 e^{\frac{V_S - \kappa V_{fg}}{U_T}} e^{\frac{V_D}{V_A}}, \tag{1}$$

where  $\kappa$  is the capacitive division between the oxide capacitance and the depletion capacitance  $\left[C_{ox}\left(C_{ox}+C_{dep}\right)\right]$ ,  $U_T$  is the thermal voltage (kT/q), and  $V_A$  is the Early voltage. Rather than a fixed gate voltage,  $V_{fg}$  is the capacitive sum of the control voltages and the stored charge,

$$V_{fg} = \frac{1}{C_T} \left( C_g V_g + C_{tun} V_{tun} + Q \right), \tag{2}$$

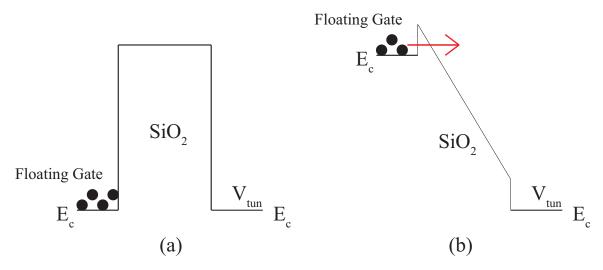

Figure 5: Band diagram of electron tunneling.

where  $C_T = C_g + C_{tun}$  is the total capacitance at the gate and Q is the charge trapped on the floating node. Note that all of the voltages are referenced to the bulk, which is  $V_{DD}$  for the pFET. For the condition where  $V_{tun}$  is 0 V, Equation 2 can be reduced to

$$V_{fg} = \frac{C_g}{C_T} V_g + V_{offset},\tag{3}$$

where  $V_{offset}$  is  $Q/C_T$ .

Equation 3 shows that this floating-gate transistor behaves very similar to a traditional pFET, but with a programmable offset on the gate. Precise control over this offset (the stored charge) is what makes floating-gate technology so important as an analog memory.

## 2.1.2 Floating-Gate Charge Modification

There are two well-documented procedures that are used to accurately modify the charge on a floating-gate transistor. Fowler-Nordheim tunneling is used to remove electrons and hot-electron injection is used for add electrons. With this combination of processes, one can precisely program the transistor to have any stored value at its gate.

Tunneling is the process for removing charge from the floating gate. The charge removal occurs when an electron is made to pass through a barrier rather than following its conduction band. Fowler-Nordheim tunneling is the procedure commonly used to induce this phenomena. The concept of tunneling is shown in Figure 5.

Figure 6: Channel diagram of hot-electron injection.

For a reasonably sized silicon-dioxide insulator, such as the MOS capacitor shown in Figure 5a, the electronic barrier is high enough to prevent conduction under normal conditions. However, when a large electric field is applied across the capacitor, the bands are bent so steeply that the electrons see a much thinner barrier. At a certain point, the barrier is thin enough that the electrons can pass right through it, as shown in Figure 5b. The ultimate result of this process is a decrease in electrons on the floating node and thus an increase in the effective gate voltage by means of  $V_{offset}$  in Equation 3.

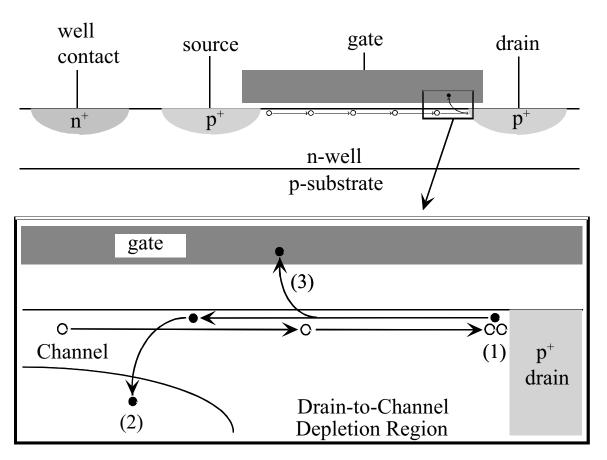

Hot-electron injection is the process used to add electrons back to the floating gate. This process is shown in Figure 6. Injection is performed by providing two conditions to the floating-gate transistor—a high drain-source potential and a high gate-source potential. The gate potential creates a conducting channel in the device and the high drain potential creates a large field between the drain and source. Under these conditions, when a minority

Figure 7: Floating-gate array isolation.

carrier enters the channel, it is accelerated with high energy toward the drain. When this carrier collides with the drain, it impact ionizes and creates an electron-hole pair. At this stage, with the high field from the gate, some of these "hot" electrons have enough energy to pass through the oxide to the gate region. The net effect is an addition of negative charge to the floating gate, lowering the effective gate voltage  $(V_{offset})$ .

## 2.1.3 Array Programming

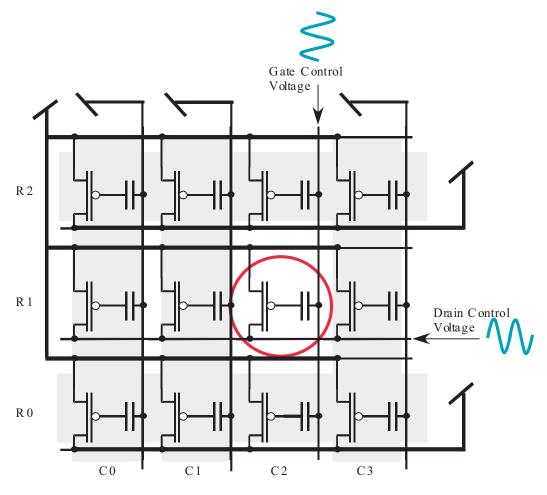

An intelligent selection procedure has been developed to rapidly program arrays of multiple floating-gate devices [11]. This array programming plays off the requirement for two control voltages to perform injection. By arranging the transistors in a two-dimensional array, shown in Figure 7, each floating-gate transistor can be individually targeted based

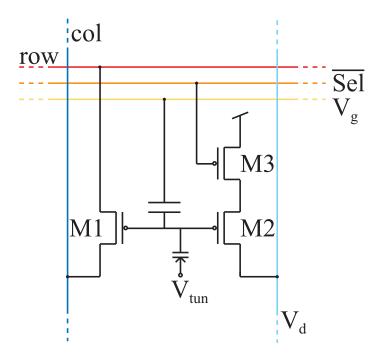

Figure 8: Indirect floating-gate switch cell.

on its row and column address. This two-dimensional addressing lends itself nicely to the two-parameter injection. By tying all of the gates of a particular dimension together and the drains of the other dimension together and then applying an appropriate gate/drain voltage to the desired row/column, only the element at the intersection will be under the right conditions to inject. On the other hand, tunneling only involves one parameter—the voltage coupled across the MOS capacitor. Therefore, in array programming, tunneling is used as a global erase and injection is used to program particular elements.

Figure 8 shows the architecture of a single floating-gate element as it appears in an array. This device illustrates the detail involved to incorporate indirect programming [12]. Transistor M1 is at the intersection of the row and column lines and is therefore in the signal path. If directly programmed, the floating-gate transistor needs to be disconnected from the circuit to provide proper control and isolation to not create unintended injection. To disconnect, a 2-to-1 multiplexer would be needed for each floating-gate transistor's source and drain. The addition of this multiplexer increases the overall switch count and thus, parasitics in the signal path.

By using indirect programming, the in-circuit transistor (M1) does not have to be disconnected, the other pFET (M2) is tied to the drain line and the select circuitry. Transistor M2 shares M1's floating gate so programming one will generate the same bias on the other. Now, injection can be performed on M2, with the resulting charge being deposited on the common floating gate without the need for any disconnection circuitry. In addition to decreasing the parasitics, this layout also decreases the area of the cell and increases the programming speed.

## 2.2 The Field-Programmable Analog Array

Field-programmable analog arrays (FPAAs) are mixed-signal systems that provide a platform for rapidly implementing analog systems in real hardware. FPAAs consist of a programmable network of switches and routing used to electrically connect analog elements, arranged in computational analog blocks (CABs). The user of such a device can design, program, and test large scale analog systems in a matter of minutes. This platform provides the engineer a considerable decrease in fabrication costs and speedup in time-to-market.

While FPGAs have been developed for commercial use, FPAAs have not had the same success. The chief barrier to commercial success is the lack of a universal block from which analog circuits could be systematically built, as gates are to digital circuits. A survey of the FPAA landscape illustrates this lack of consensus as to the appropriate level of granularity.

## 2.2.1 FPAA Topologies

Originally reported about twenty years ago, FPAAs have seen several architectural revisions. Most have been of modest proof-of-concept size and contained CAB elements that target particular applications.

An early FPAA work was Gulak's, in which he used "switch blocks" of cross-bar switches and a shift register to control the connections between CABs [13]. The CABs in his design were arranged so that they could only implement one of seven limited functions (variations of comparing and multiplying), which was determined by a three-bit code

applied to it. A later, more fine-grained approach was the field-programmable transistor array (FPTA), which used a sea of single transistor that had to be connected together to realize a system [14].

On the other end of the granularity spectrum are the coarse-grained architectures that target a specific application. The analog ODE co-processor from Tsividis's group is one such chip [15]. His chip is composed of analog mathematical computational blocks like integrators and gains stages for accelerating computer simulations. Although limited in general application, the chip advanced the field of embedded FPAA systems by pushing the importance of having easy digital control from a master device. Another example of a very coarse-grained FPAA is the hexagonal  $G_m - C$  architecture from Becker's group [16]. This chip was explicitly targeted to OTA-C filters where precise knowledge of node capacitance is important for high-order filters. His novel approach was to hexagonally arrange 55 OTAs where there are no "switches" between blocks, but systems are synthesized by only turning on certain OTAs. The chip reported good performance for signal continuous filters—its only application.

There have also been a couple commercially available FPAAs. Anadigm's FPAA and their software package, Anadigm Designer, use switched-capacitor circuits to realize circuits [17]. Anadigm demonstrates how important an intuitive tool flow is to a chip's acceptance. They have a graphical top-level design tool that makes systems easy to draw and understand. However, their hardware is not only extremely small (4 CABs), it is really only targeted to switched-capacitor systems. Another player in the commercial market is the Cypress PSoC (programmable embedded system on chip) [18]. Although not a true FPAA—the analog components are limited to a few tunable ADCs, DACs, 4 op-amps, 4 comparators, etc.—it introduces the concept of integrating a microcontroller with configurable analog and digital peripherals.

## 2.2.2 The Reconfigurable Analog Signal Processor

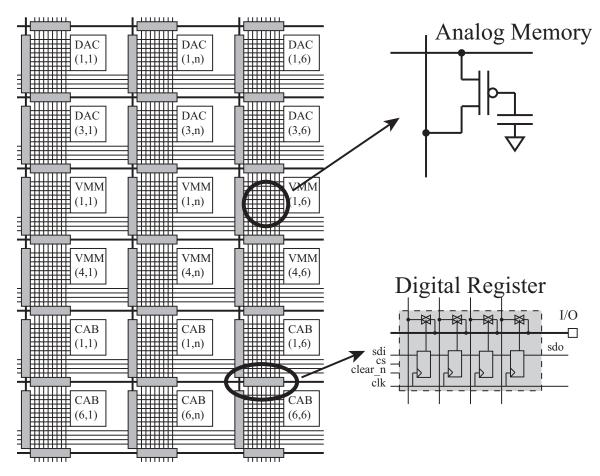

The largest advancement in FPAA technology, in terms if size and versatility, has been the reconfigurable analog signal processor (RASP) line of FPAAs. The RASP 2.8 is composed of 32 CABs, multilevel routing, and on-chip programming structures. While there are several versions of FPAAs in the 2.8 family—defined by the CAB components—it is the general-purpose RASP 2.8a that is suitable for most applications [19, 20].

Of the 32 CABs in the RASP 2.8a, 28 each contain 16 common analog components: 1 programmable bias operational transconductance amplifier (OTA), 2 programmable input and bias OTAs, 1 OTA buffer, 4 n/pFETs, 2 multiple-input translinear elements, 4 500 fF capacitors, and 1 transmission gate. The other 4 CABs contain elements for signal-by-signal multiplication, i.e., Gilbert multipliers. The routing is a full crossbar switch matrix. There are multiple levels of routing lines to reduce the capacitance nodes: local, nearest neighbor, and global.

The core element that facilitates highly dense FPAA systems is the floating-gate (FG) MOS transistor. No external memory is required when utilizing this switch because it stores its own value. The FPAA switch topologies are shown in Figure 9, which includes an indirect programmed FG [12]. One of the most beneficial features of FG switches is that they can also be used as computational elements [21]. FGs can be programmed to hold any value between on and off, essentially providing a free bias source.

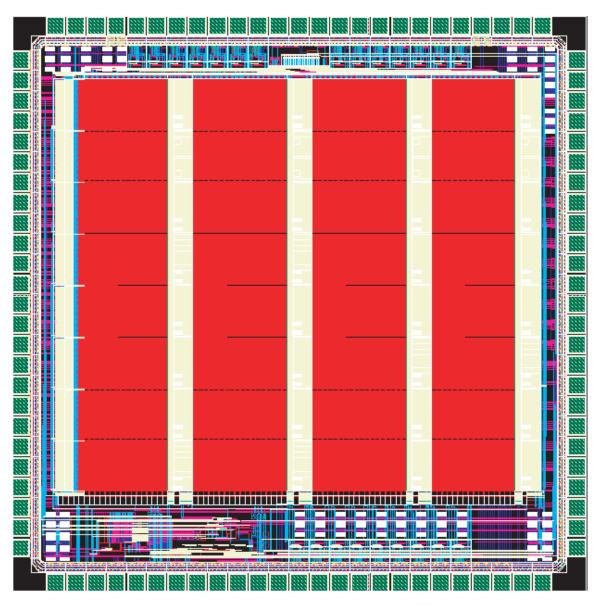

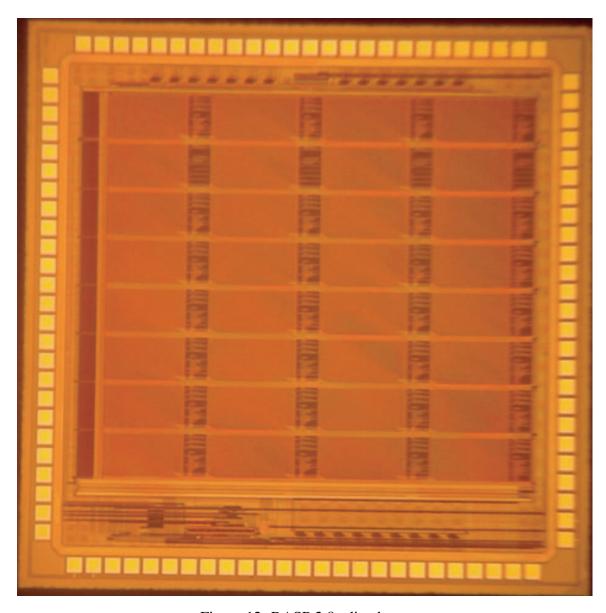

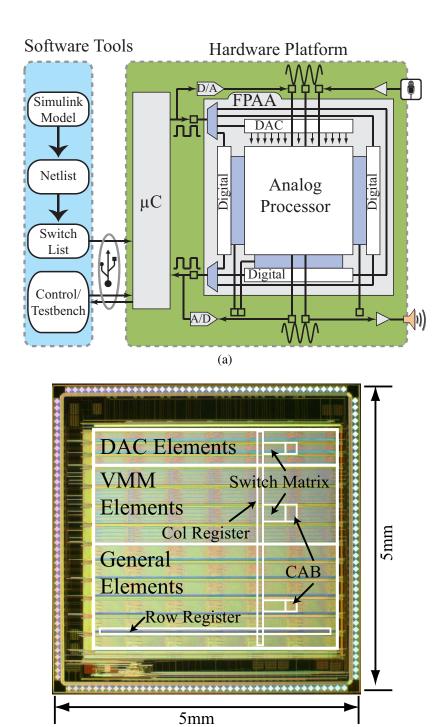

Figure 10 shows the architecture of the RASP 2.8a FPAA and the connections between the CABs, routing, and FG switches. The layout is shown in Figure 11, a die photo is in Figure 12, and relevant parameters are given in Table 1. The chip has been fabricated in a 350 nm double-poly CMOS process through TSMC and is 3 mm × 3 mm. One advancement in this line of FPAAs is the use of nearest-neighbor routing as an alternative to the existing horizontal/vertical globals and locals. This extra layer of routing creates direct connections to the nearest CAB to the left, right, top, and bottom. A system of bridge switches was also introduced. The bridges allow for more lines to be drawn as locals and

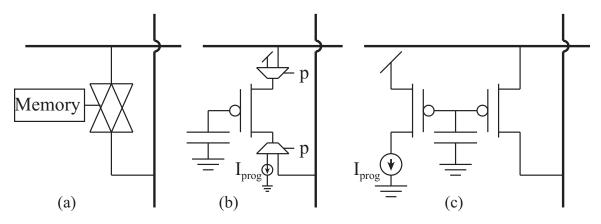

Figure 9: The three types of FPAA switches. (a) The traditional switch with a separate memory element. (b) Floating gate switch elements store their programmed value, allowing for a very area efficient design. (c) Indirect programming reduces the switches in the signal path.

Table 1: RASP 2.8a device parameters.

| Process                        | 350 nm                             |

|--------------------------------|------------------------------------|

| Die Size                       | $3 \text{ mm} \times 3 \text{ mm}$ |

| Power Supply                   | 2.4 V                              |

| Injection $V_{DD}$             | 5.6 V                              |

| Number of CABs                 | 32                                 |

| Switch programming time        | $N_{rows} \times 100 \mu s$        |

| Bias programming time          | 5 ms/element                       |

| Programming accuracy and range | 9 bits over 100 fA to 10 $\mu$ A   |

then connected to the top and bottom local lines if needed. Table 2 shows that by using these shorter connections, the line capacitance is greatly reduced.

Another advantage presented by the RASP 2.8 line of FPAAs is the incorporation of on-chip programming [22]. Moving the programming on chip has allowed for much higher speed operation. The major contributor to this increase in speed comes from the floating-point current ADC. This is a ramp ADC with an adaptive logarithmic I-V converter on the front end, which allows for conversions of seven decades of current in 200  $\mu$ s, which is much faster than off-chip measurements would take. DACs are also on-chip for setting

Figure 10: The architecture of the RASP 2.8 FPAA. The routing is a full crossbar switch matrix with floating-gate switches. The FG switches can be used for computation, such as for vector-matrix multiplier (VMM) weights.

Table 2: RASP 2.8a routing line capacitance values.

| Nearest neighbor vertical   | 151 fF |

|-----------------------------|--------|

| Nearest neighbor horizontal | 228 fF |

| Global                      | 763 fF |

the gate and drain voltages during injection. When precisely programming (injecting) a device, the present current value is measured and digitized with the I-to-V ADC. This voltage reading is then sent off-chip to a microcontroller and used to calculate how many and what size pulses are needed to converge on the target current. These values are then passed back to the chip's shift register through an SPI interface. This register is used to control the selection lines as well as the gate/drain DACs. A custom printed circuit board (PCB) was built to control all of the off-chip aspects of the programming, as well as for testing the chip.

To increase the size of synthesizable systems, the RASP 2.9a was recently introduced. This FPAA maintains the exact same architecture of the RASP 2.8a, but on a larger scale. The RASP 2.9a was fabricated in 350 nm CMOS and with a size of 5 mm × 5 mm was able to hold 84 CABs. By using the same architecture, all of the infrastructure from the RASP 2.8a is able to be utilized. This chip can synthesize much larger systems by virtue of it having more CABs. However, in Chapters 3 and 4 we will introduce two RASP FPAAs with new architectures that change the whole FPAA application space.

Figure 11: RASP 2.8a layout.

Figure 12: RASP 2.8a die photo.

## **CHAPTER 3**

## THE MITE FPAA

The coordinated approach to analog signal processing begins with looking at the right hardware *primitives*. To maximize the computational efficiency of FPAAs, we need to pick a core processing element that can be readily applied to many common signal processing systems. Whereas in FPGAs, it is easy to abstract almost any digital system to look-up tables (LUTs) and flip-flops, the reconfigurable analog processor is much more open ended as to what the most efficient primitive should be.

This chapter presents the MITE FPAA (MFPAA), which utilizes multiple input translinear elements (MITEs) as the core computational unit [23]. This FPAA utilizes a novel MITE unit, which takes advantage of commonly connected nodes while still fitting into a reconfigurable framework. By carefully designing this hardware structure, we can fully utilize existing synthesis algorithms for large-scale MITE systems. This novel architecture allows for a synthesis procedure that is elegant in its simplicity and lets us fully abstract the circuit design for the user. Thus, by using this full-system approach to FPAA design, a complete tool chain is possible: the abstracted software design environment, the place-and-route and programming tools, and the analog hardware. This entire platform will open up MITEs to new audiences as a design tool for implementing low-power signal-processing

Figure 13: The coordinated approach to FPAA design: MITE FPAA.

Figure 14: Design flow using a translinear FPAA. Using translinear circuits allows the user to enter a set of equations, which is then netlisted using existing synthesis procedures. The circuit is then place-and-routed, and the system is programmed onto the FPAA.

systems. Figure 13 shows how the MFPAA fits into the coordinated-design framework.

The use of translinear circuits as the universal analog block to reduce the trade off between flexibility and abstraction level has been gaining a lot of recent attention [23, 24, 25]. Using translinear circuits for which known network synthesis procedures exist [26, 27], it is possible to build a system in which the only input necessary is the set of equations that describe the system to be implemented. The translinear FPAA will be able to implement a wide range of circuits, including all linear static equations and most differential equations, while requiring the user to perform no actual analog design. This idea is illustrated by the translinear FPAA design flow, shown in Figure 14. Unlike the traditional FPAA design flow, there are no design or simulation steps required to create the working system. This will allow users with a background in math, controls, physics, or many other fields to easily interact with the FPAA.

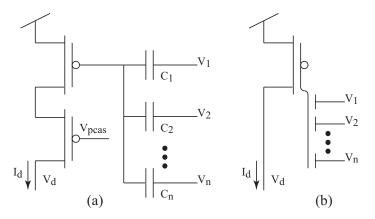

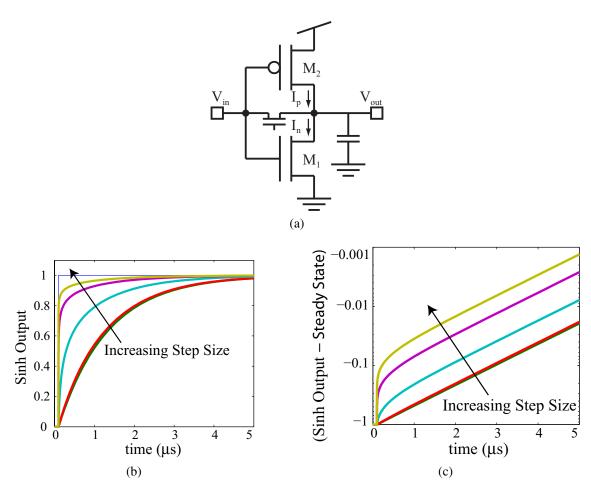

Figure 15: Subthreshold pFET realization of a MITE. (a) Components used to realize a MITE in a standard CMOS process. (b) Symbol used to represent a MITE.

## 3.1 Multiple Input Translinear Elements

Ideal translinear elements have infinite input impedance and an exponential voltage to current relationship independent of the current level at which they are operating. In addition, any translinear element can be made to have multiple inputs by simply applying resistive or capacitive division at the voltage input. MITEs can thus be built using either subthreshold MOSFETs or BJTs, each of which is stronger in one of the two above specifications [26]. Subthreshold pFETs were chosen for the MITE FPAA to allow the practical implementation in common CMOS process. The pFET has a current that is exponentially related to its gate voltage given by

$$I_d = I_0 e^{\frac{V_S - \kappa V_g}{U_T}} \left( 1 - e^{\frac{V_d - V_s}{U_T}} \right),\tag{4}$$

where  $I_0$  is a pre-exponential constant term,  $\kappa$  is the capacitive division between the oxide capacitance and the depletion capacitance, and  $U_T$  is the thermal voltage (kT/q). Note that all voltages are referenced to the bulk, which is the well voltage for the pFET. Furthermore, as long as the device is in saturation,  $V_{sd} > 100$  mV, the second exponential term can be neglected.

Figure 15 shows the subthreshold pFET realization of a MITE, with capacitive division used for the introduction of multiple inputs. The current-voltage relationship for this

element is given by

$$I_d = I_0 e^{\frac{V_S - \kappa \sum (w_i V_i)}{U_T}},\tag{5}$$

where  $w_i$ , the dimensionless weight applied to an input, is given by  $C_i/C_T$ , and  $C_T$  is the total capacitance at the gate of the pFET. Figure 15b shows the symbol that will be used for this realization of a MITE. Note that while the subthreshold MOSFET does have nearly infinite input impedance, the range in which the relationship between current and voltage is exponential is limited. However, by making the W/L ratio of the MITEs larger, this range can be increased.

To precisely set the charge on the floating node of the floating-gate pFET, a programming method is used that utilizes two quantum processes: Fowler-Nordheim tunneling and hot-election injection. This method of programming is vastly superior to simply removing the charge with UV radiation, because the charge can be precisely set, thus removing any offset between devices. Historically, gain errors induced by charge mismatch between devices have had a crippling affect on large-scale MITE systems [28]. The specialized MITE structure in [29] was developed for it to be compatible with the FPAA programming core. Of particular importance, the use of the on-chip programming core comes at no additional overhead as it is already built in to program the floating-gate switches [22].

To build complex systems using MITEs, it is necessary to explore what higher level components are commonly used. Translinear loops and log-domain filters will be emphasized because they are commonly used as core elements in most synthesis procedures.

## 3.1.1 Building Block: Translinear Loops

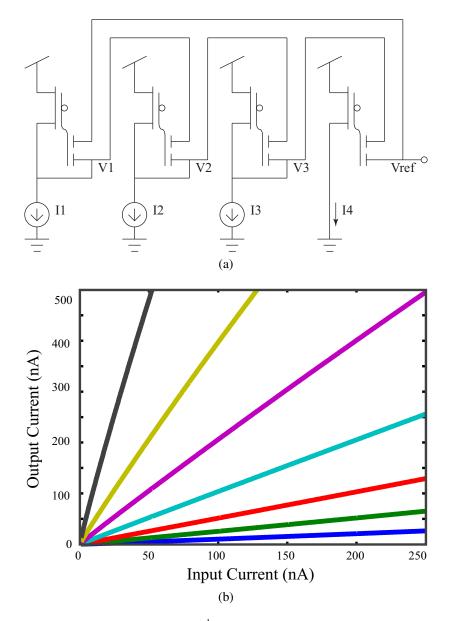

Translinear loops are well documented building blocks of almost every translinear system [26, 30]. In a reconfigurable system, fixed loops are used to reduce the amount of reconfigurability needed. For the reconfigurable system we will use the translinear loop shown in Figure 16, which can be analyzed by simply solving for each MITE's diode connected voltage. For the analysis, we can assume that the floating gates have an equal amount of

Figure 16: MITE implementation of a  $2^{nd}$ -order translinear loop. (a) Schematic of a  $2^{nd}$ -order translinear loop. (b) Simulation results of the translinear loop. The multiplication coefficients were chosen to be  $\frac{1}{10}$ ,  $\frac{1}{4}$ ,  $\frac{1}{2}$ , 1, 2, 4, and 10.

charge on them and that both of the MITE's input capacitors are equal  $(\kappa w_1 = \kappa w_2 \equiv w)$ . Under these assumptions (with  $V_{ref} \equiv V_0$ ), the equations are

$$V_i = \frac{U_T}{w} \log \frac{I_i}{I_0} - V_{i-1}, \ i = 1, 2, 3$$

(6)

$$V_3 + V_0 = \frac{U_T}{w} \log \frac{I_4}{I_0}. (7)$$

Substituting Equation 6 into Equation 7, gives

$$log\frac{I_1}{I_0} + log\frac{I_3}{I_0} = log\frac{I_2}{I_0} + log\frac{I_4}{I_0},$$

(8)

which can be written as

$$I_1 I_3 = I_2 I_4. (9)$$

This circuit is most often used as a multiplier with

$$I_{out} = \frac{I_a I_b}{I_c}. (10)$$

Simulation results of the translinear loop are shown in Figure 16b. Data was taken as  $I_a$  was swept and the coefficient  $I_b/I_c$  was held constant. For higher coefficients, the trace is not completely straight because the MITEs leave the subthreshold region due to the higher current levels. The dynamic range (DR) for such a system follows the discussion given in [31].

#### 3.1.2 Building Block: Filters

Log-domain filters were included in this system as higher level blocks because they are a building block of almost every dynamic system and are commonly utilized in synthesis procedures. The synthesis of the circuit, found in [26], is similar to the synthesis of the loop, but first the constraint equations are needed. The differential equation for a first-order low-pass filter is

$$\tau \frac{dI_{y}}{dt} + I_{y} = I_{x},\tag{11}$$

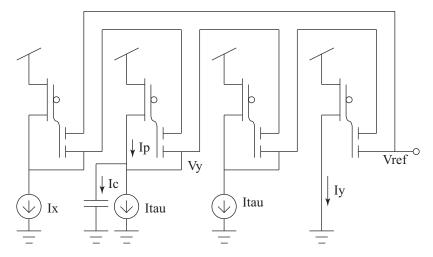

Figure 17: MITE implementation of a 1<sup>st</sup>-order low-pass log-domain filter. The  $I_{\tau}$  bias current connected to the capacitor is used to set the corner frequency of the filter. The second bias current is set to  $I_{\tau}$  in order to maintain unity gain.

where  $I_x$  is the input current,  $I_y$  is the output current, and  $\tau$  is the time constant of the filter. The chain rule can be applied to the derivative of the current giving

$$\tau \frac{\partial I_{y}}{\partial V_{y}} \frac{dV_{y}}{dt} + I_{y} = I_{x}, \tag{12}$$

where  $V_y$  is the log compressed voltage associated with  $I_y$ . Taking the derivative of the current through the 2-input MITE with respect to a single controlling voltage results in

$$-\tau \frac{wI_y}{U_T} \frac{dV_y}{dt} + I_y = I_x, \tag{13}$$

where w is the weight of the controlling voltage  $V_y$ . Noting that  $CdV_y/dt$  is a capacitive current  $(I_c)$  and  $\tau w/U_TC$  can be written as a reciprocal of a bias current  $(I_\tau^{-1})$  we can arrange Equation 13 as

$$I_{\tau} - I_{c} = \frac{I_{x}I_{\tau}}{I_{y}}.\tag{14}$$

This equation is implemented by the circuit in Figure 17, where the right hand side is the same as the loop derived in Equation 10, and the left hand side is simply the KCL of  $I_p$ . In addition, a gain term can be added to the transfer function by multiplying the second  $I_\tau$ , the bias current for the MITE without the capacitor on its drain, by the coefficient desired.

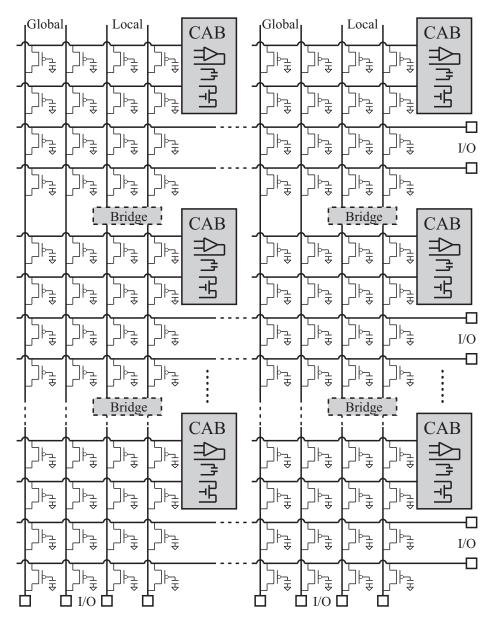

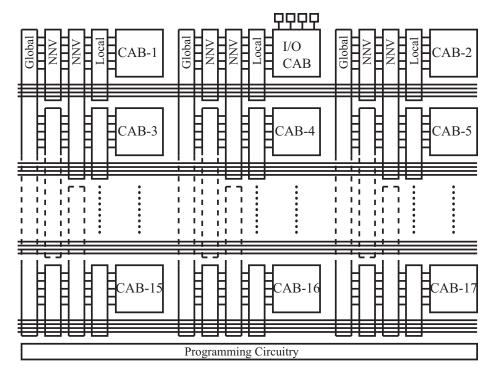

Figure 18: Architecture of the MITE FPAA. The FPAA consists of 17 MITE CABs and a single IO CAB. The vertical routing between CABs is organized into local, nearest-neighbor vertical (NNV), and global. The horizontal routing is only global.

# 3.2 Reconfigurable Architecture

The MFPAA utilizes the base architecture developed for the general RASP 2.8 line of FPAAs [19]. This results in a system that is a vast advancement over the Reconfigurable Analog Array of MITEs [24] by using a more computationally efficient MITE element, incorporating a more complex routing scheme in order to reduce the parasitic capacitance of the switch matrix, and utilizing on-chip programming [22].

## 3.2.1 System Architecture

The architecture of the MFPAA is shown in Figure 18. The FPAA is laid out with 18 CABs in a  $6 \times 3$  array, with 17 being MITE CABS and one being the I/O CAB. The RASP infrastructure incorporates a cross-bar switch matrix for connecting the elements to one another. The connection between the horizontal and vertical lines is controlled by a single floating-gate switch, which allows it to store its own value without a separate memory.

Within each CAB, the vertical routing is organized into 10 global, 20 nearest neighbor

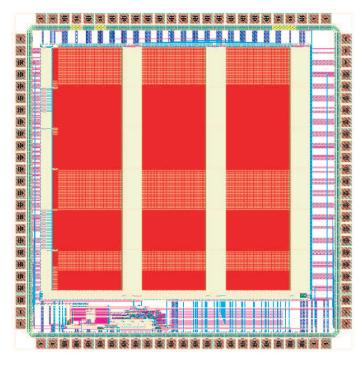

Figure 19: Layout of the MITE FPAA. The FPAA was fabricated in a 350 nm standard CMOS process on a 3 mm  $\times$  3 mm die.

(10 up, 10 down) and 10 local lines. The shorter lines are used whenever possible to reduce parasitic line capacitance. Each CAB also has 10 global horizontal lines. At the lower end of the IC is the on-chip programming structure, which selects and programs all necessary floating-gate switches and MITEs. The layout of the MFPAA is shown in Figure 19, which was fabricated in 350 nm standard CMOS with a  $V_{DD}$  of 2.4 V.

#### 3.2.2 The MITE CAB

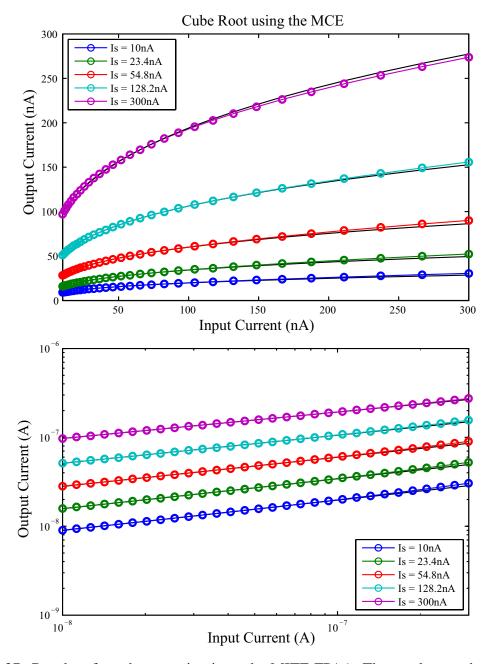

The most significant advancements in the architecture of the MFPAA are within the MITE CAB. To improve the density of computation elements to switch elements, single MITEs must be replaced with computational blocks with less reconfigurability. The computation element in Figure 20 was chosen to avoid losing flexibility by trying to maximize the number of equations the element could implement while minimizing the reconfigurability needed. This structure is similar to the one analyzed in Section 3.1.1, with  $V_{ref}$  taken from  $V_1$ . Two of these elements, called MITE computational elements (MCEs), are contained in

Figure 20: Basic MITE computation element of the MITE FPAA. The computation element consists of 5 input MITEs in a translinear loop configuration and 1 output MITE. The gates of the output MITE are sent into the switch matrix where they are connected to any of the input MITE gate voltages.

#### each CAB.

The CAB also includes a first-order log-domain filter, shown in Figure 28. This is the same structure discussed in Section 3.1.2, with  $V_{ref}$  taken from  $V_{tau}$ . Again, this was done to increase the density of the computational elements without losing too much reconfigurability. This also lends itself to implementing previously developed synthesis procedures on the MFPAA, as dynamic functions can be implemented by combining static functions with first-order filters [27]. Both the MCE and filter were drawn with  $W/L = 48 \ \mu m/1.2 \ \mu m$  to increase the subthreshold range.

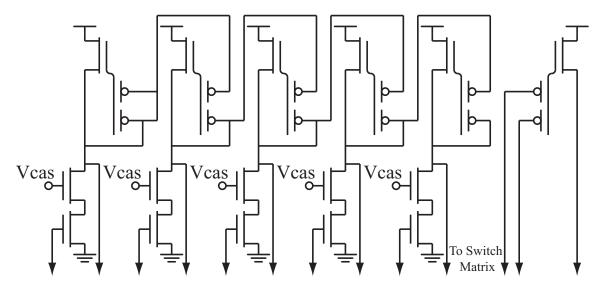

In addition to the two MCEs and the filter, the CAB includes six bias current generators, six nFET current mirrors, and a cascode-bias generator. The bias currents are programmed with floating-gate current sources and are used for implementing coefficients and scaling currents in the input equations. The current mirrors are used for adding and subtracting as well as signal routing. The cascode-bias generator, based on Minch's design [32], creates all of the cascode biases needed.

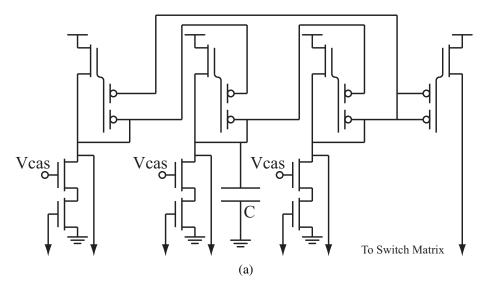

## **3.2.3** The I/O CAB

The input/output (I/O) CAB is the CAB that interfaces the MITE systems to the outside world. This CAB contains input voltage-to-current (V/I) converters, output drivers, and broadcast drivers for inputs. The chip was designed with banks of 10 of each of these components. The V/I converter is necessary because MITEs are mainly current-mode elements, but it is much easier to generate voltage-mode signals off chip, via DACs or function generators. The output driver is a current mirror with a gain factor of 10 to help off-chip current meters read the subthreshold MITE currents. In this system, a current-to-voltage ADC was not incorporated because it was easy enough for to read currents with off-the-shelf instruments. This capability should be pursued in future systems to allow interfacing with a programmable processor. The broadcast driver is equivalent to half of a current mirror to log-compress the current into a gate voltage by a diode connected nFET, which can then be broadcast to many input nFET devices.

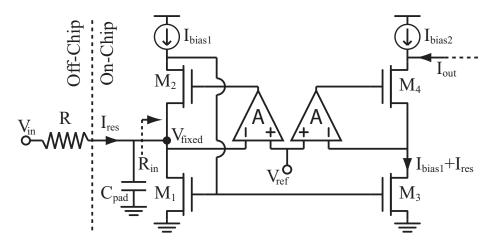

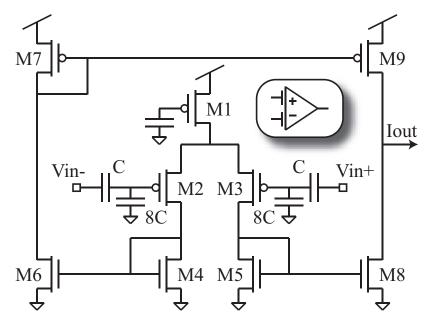

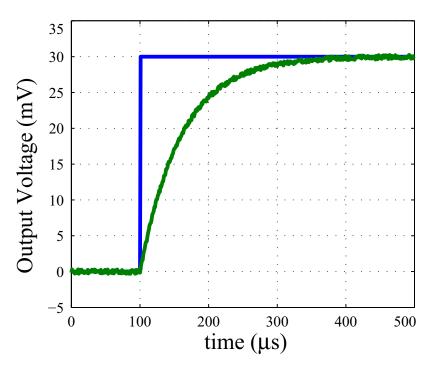

The V/I converter on the MFPAA was designed for both accuracy and speed considerations. The V/I must be able to convert currents on the order of nanoamps without sacrificing the speed of the entire system. This requires an extremely low input resistance to compensate for the large capacitance of the bonding pad. This is accomplished by using active feedback, shown in Figure 21, which is similar to the one presented in [33]. The speed of the V/I can be written as

$$f_{-3dB} = \frac{1}{2\pi (R \parallel R_{in}) C_{pad}} \approx \frac{1}{2\pi R_{in} C_{pad}},$$

(15)

and its accuracy can be written as

$$Error \approx \frac{R_{in}}{R},$$

(16)

where

$$R_{in} \approx \frac{1}{g_{m1}[g_{m2}r_{ds2}(A+1)+1]}. (17)$$

The amplifiers used are simple pFET-input 5 transistor OTAs with a voltage gain of approximately  $g_m r_{ds}$ .  $V_{ref}$  is usually set to 0.4 V and R (off chip) is usually 10 M $\Omega$ .

Figure 21: Voltage-to-current converter used in the MITE FPAA. The amplifier on the input side provides an extremely low input resistance allowing for high speed and good accuracy. The amplifier on the output side reduces mismatch between the input and output currents by matching the drain voltages of the mirror transistors. The bias currents are provided by floating gates.

## 3.3 The Design Flow

An entire software chain has been developed in order to effectively utilize the MFPAA. The collective purpose of this chain is to implement, in hardware, the equation entered by the user. The main components of the chain are network synthesis, place-and-route, visualization and programming.

#### 3.3.1 Network Synthesis

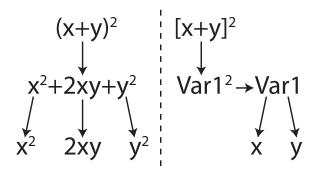

The first step in the software chain is the synthesis of a circuit topology from the input equation. This topic was thoroughly explored in [27]. To take full advantage of this work, a set of Matlab functions were written to parse the input equation into modules capable of being processed by the MCE. First, the expression is prepared for parsing by expanding it using Matlab's symbolic toolbox. Since expanding the expression blindly may not lead to optimal use of components in the MFPAA, an option for the user to create sub-blocks was included. This is done by using '[' and ']' instead of parenthesis while entering the equation. Anything included in brackets is treated as its own expression and is replaced by a new variable in the original expression. Once expanded, each expression is split at the

Figure 22: A representation of equation parsing for the MITE FPAA. Equations are split at addition and subtraction signs to create units that will be implemented by MCEs. The user's expression is expanded first in order to create a simple parsing tree (left). However, the user can define sub-blocks by using brackets to replace an expression with an intermediate variable [right].

'+' and '-' signs in order to break it into units containing only multiplication, division, and powers. These ideas are illustrated in Figure 22.

Now that expressions containing only multiplication, division, and powers have been obtained, a few special cases must be checked for and taken care of. One of these cases is an expression that contains fractional exponents. Since MITEs with only two gate capacitors can only implement powers with magnitudes of 1 or 2, the final expression that will be implemented can only have integer exponents. This is accomplished by raising the expression to the lowest integer power that will result in all integer exponents. While the new expression is now capable of being implemented, the output now has an exponent other than one. To correct this, the output signal will be fed back to produce an equation that results in the intended output. An example of this process is shown here:

$$I_{out} = I_1^{1/2} I_2^{1/4} I_3^{1/4} \Rightarrow I_{out}^4 = I_1^2 I_2 I_3 \Rightarrow I_{out} = \frac{I_1^2 I_2 I_3}{I_{out}^3}.$$

(18)

Once functions capable of being implemented with the MITEs are obtained, previous work can be leveraged to map the functions to an MCE. As described in [27], the fixed gate connections of the 5 input MITEs contained in each MCE produces a set pattern in the exponents of the expression implemented. This pattern can be altered by changing where the gates of the output MITE are connected. The possible patterns are shown in Table 3.

Table 3: MITE FPAA translinear loop exponent patterns.

| Gate Connections | Input Exponent Pattern |

|------------------|------------------------|

| 1, 3             | +1, -1, +1, 0, 0       |

| 1, 5             | +1, -1, +1, -1, +1     |

| 2, 2             | -1, +2, 0, 0, 0        |

| 2, 4             | -1, +2, -1, +1, 0      |

| 3, 3             | +1, -2, +2, 0, 0       |

| 3, 5             | +1, -2, +2, -1, +1     |

| 4, 4             | -1, +2, -2, +2, 0      |

| 5, 5             | +1, -2, +2, -2, +2     |

Exponents with a magnitude greater than two must be realized by connecting the input signal to multiple MITEs. For example,

$$I_{out} = \frac{I_1^3 I_2^2}{I_3^4} = \frac{I_1 I_1^2 I_2^2}{I_3^2 I_3^2}.$$

(19)

In addition, expressions that cannot be implemented in a single MITE Computation Element must be broken up into multiple elements. For example,

$$I_{out} = \frac{I_1^4 I_2^3}{I_3^5 I_4} = \left[ \frac{I_1^2 I_1^2 I_2}{I_3^2 I_3^2} \right] \frac{I_2^2}{I_3 I_4}.$$

(20)

While the MITE elements realize the multiplication, division, and powers found in the user's expression, addition and subtraction is done through the use of KCL. Intermediate expressions are summed by simply connecting the current-mode output of each MITE together, and subtracted by connecting the appropriate output of each MITE to different sides of a current mirror.

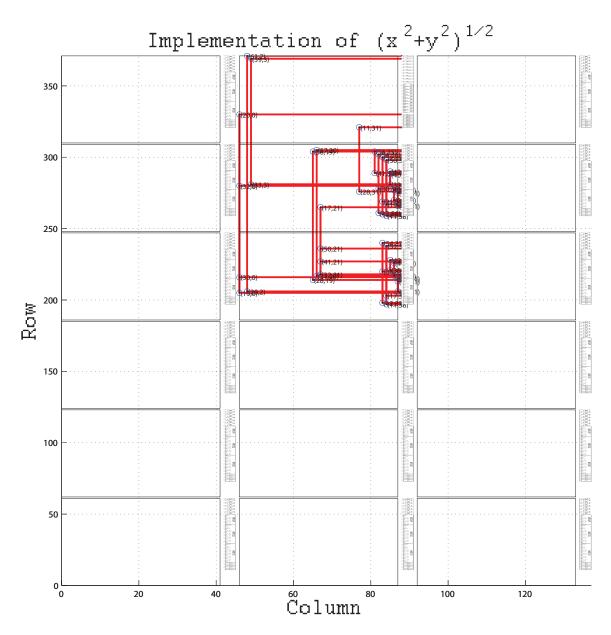

#### 3.3.2 Place-and-Route

While place-and-route algorithms are an area of active research in both FPGAs [34] and FPAAs [35], the simple algorithm used here is meant to show the possibilities of using a translinear FPAA in simplifying the software algorithms needed. The algorithm, which uses the output of the synthesis function, can be broken into two distinct functions—placement of the components used and routing of the signals between them.

The placement function breaks the input structure into five main categories—inputs, outputs, loops, scaling currents, and mirrors. They are placed in that order by searching for the closest available elements to the I/O CAB. The current biases and mirrors are placed in the same CAB as the MCE they are operating on. The routing is then performed by picking the shortest line between elements. To reduce parasitic capacitance, the local lines have the lowest cost and the globals have the highest cost.

The last major functions in the software chain are visualization and hardware programming. While programming floating-gate transistors has been developed previously [36], functions have been added to make interfacing with an FPAA much easier. Most importantly, a GUI has been created to show the output of the synthesis and place-and-route functions. This GUI shows the FPAA and draws the switches that will be turned on and the connections between them. It also includes diagrams of the CABs so the user can easily understand what is being connected. A sample of the GUI is in Figure 23. In addition to allowing the user to easily understand how the equation is being implemented on the FPAA, the GUI also allows the user to modify the implementation if they desire.

Once the equation has been synthesized and routed, the list of switches and programmable elements are programmed on the chip. The setup that allows for this to happen includes a printed circuit board (PCB), a microcontroller, and a computer for communication [37]. Routines for selecting devices, programming switches, and programming computational elements are stored on the microprocessor and initiated by communication from the computer. The computer communicates, over either serial or USB, directly from Matlab allowing easy interfacing between the synthesis, place-and-route, and programming code.

#### 3.4 Results

To the test the MFPAA, a wide range of circuits were compiled onto it. First, some static functions were tested including circuits for multiplying, squaring, and cube root. Next, dynamic functions were tested. These included a low-pass filter, a high-pass filter, and a

Figure 23: Visualization GUI for interfacing with the MITE FPAA. The GUI output is shown for a vector magnitude circuit.

RMS-to-DC converter. The circuits were compiled using the synthesis procedures previously discussed.

## 3.4.1 Static Examples

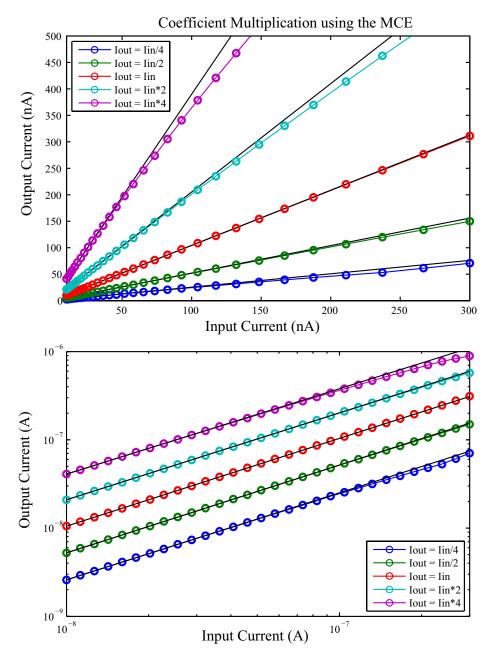

The first static example compiled onto the MFPAA implements the equation

$$I_{out} = \frac{I_a I_b}{I_c}. (21)$$

To test this circuit,  $I_a$  was swept while  $I_b$  and  $I_c$  were held constant. In addition,  $I_b/I_c$ , was set to produce a variety of coefficients. The results are shown in Figure 24.

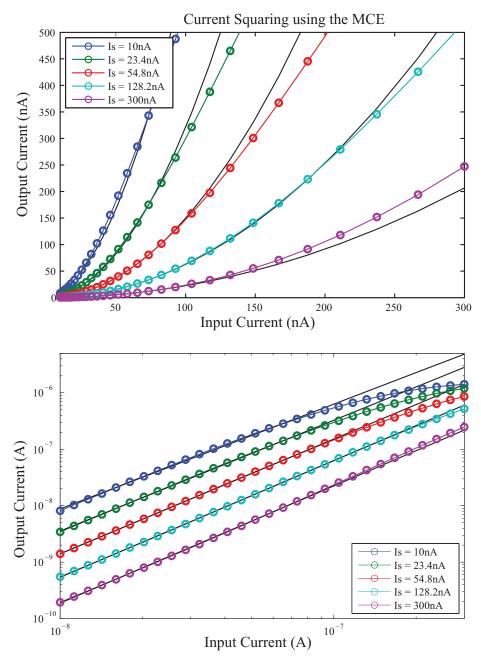

Next, a squaring circuit was compiled onto the MFPAA. The circuit uses a scaling current,  $I_s$ , that determines the value of unity in the system. This idea is illustrated in the equation

$$I_{out} = \frac{I_{in}^2}{I_s},\tag{22}$$

which describes the system's input-output relationship. The results of the squaring circuit are shown in Figure 25. The most important feature of the output characteristic is its inaccuracy for large input to scaling current ratios. This causes currents larger than the subthreshold range to flow through the output MITE.

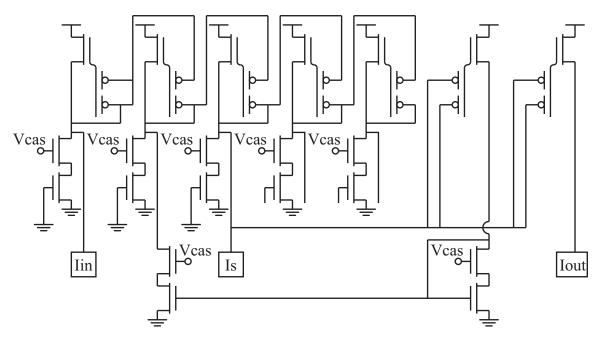

A cube root circuit was also compiled on the MFPAA. The circuit is shown in Figure 26. The output MITE of another MCE is used to gain access to the output current. Again, a scaling current is used set the value of unity in the system. The equation that describes the system is

$$I_{out} = I_{in}^{1/3} I_{s}^{2/3}. (23)$$

The results of the cube root are shown in Figure 27. In contrast to the squaring circuit, the cube root results are more accurate because of its compressive nature.

### 3.4.2 Dynamic Examples

The first dynamic circuit compiled onto the MFPAA was a first-order low-pass filter. The filter is included as one of the CAB components on the MFPAA, shown in Figure 28. The

Figure 24: Results of a coefficient multiplication circuit implemented with the MITE FPAA. The results are shown in a linear plot (top) and a log plot (bottom) to show both the accuracy and the dynamic range of the computation.

Figure 25: Results of a squaring circuit implemented with the MITE FPAA. The results are shown in a linear plot (top) and a log plot (bottom) to show both the accuracy and the dynamic range of the computation. Note that the inaccuracy at high output currents is due to devices leaving subthreshold operation.

Figure 26: Circuit that implements a cube root on the MITE FPAA. A second output MITE, from the other MCE in the CAB, is used to gain access to the output current. In addition, a current mirror is used to feed back the output current to create the cube root.

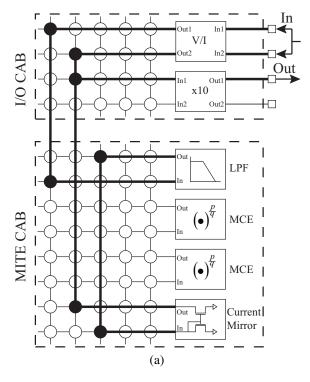

filter was tested by adjusting the bias currents that set the corner frequency of the filter and measuring the transfer function. The results are shown in Figure 28b.

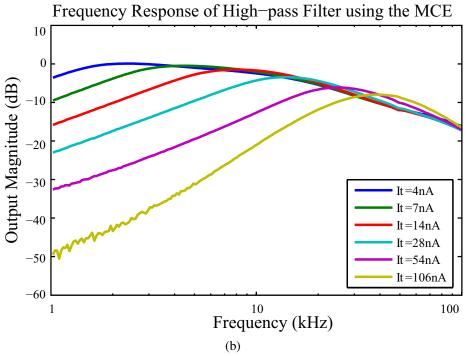

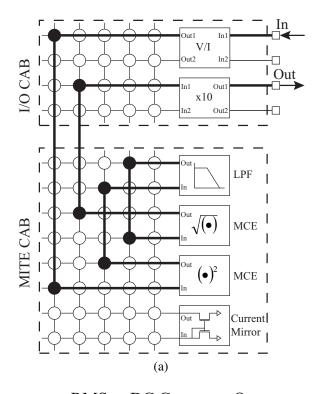

Next, a first-order high-pass filter was compiled onto the MFPAA. The filter was built by subtracting a low-pass filtered version of the input from the original signal. The MFPAA implementation of this design is shown in Figure 29. Again, the filter was tested by measuring the transfer function for multiple bias currents. The frequency response of the entire system is more apparent here than in the low-pass filter case. Here, the pass-band shows the effects of the mismatch due to the current mirror. The results are shown in Figure 29b.

An RMS-to-DC converter was also compiled onto the MFPAA. A combination of three static and dynamic circuits, in addition to the V/I converter, are needed in order to realize the converter. First, the input, which has been rectified by the input V/I structure, is squared. Second, it is passed through a low-pass filter to find the mean. Third, the square root of the mean is found. The MFPAA implementation of this design is shown in Figure 30. The converter was tested by varying the input amplitude of a sine wave and measuring the

Figure 27: Results of a cube root circuit on the MITE FPAA. The results are shown in a linear plot (top) and a log plot (bottom) to show both the accuracy and the dynamic range of the computation.

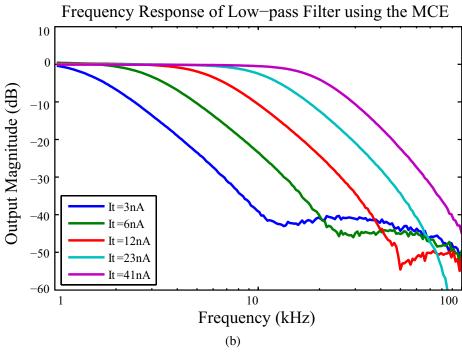

Figure 28: Log-domain filter of the MITE FPAA. (a) The MITE FPAA uses a standard first-order MITE log-domain filter in order to implement dynamic functions. (b) The transfer function of a first-order low-pass filter for various bias currents is shown. The bias currents used were logarithmically spaced between 3 nA and 41 nA. Note that the highest achievable corner frequency is 200 kHz.

Figure 29: Log-domain high-pass filter. (a) The log-domain high-pass filter can easily be complied into a single MITE CAB. To implement the high-pass filter a low-pass version of the signal is subtracted from the original signal using the current mirror. (b) The transfer function of the filter for various bias currents is shown. The bias currents used were logarithmically spaced between 4 nA and 106 nA.

Table 4: MITE FPAA device parameters.

|                      | This work          | [38]                |

|----------------------|--------------------|---------------------|

| Process              | 350 nm CMOS        | 350 nm CMOS         |

| Die Size             | 9 mm <sup>2</sup>  | .92 mm <sup>2</sup> |

| Power Supply         | 2.4 V              | not given           |

| Number of CABs       | 18                 | 25                  |

| No. of T-L elements  | 272                | 25                  |

| Largest order filter | $17^{th}$          | $4^{th}$            |

| Bandwidth            | 200 kHz (measured) | 7 MHz (simulated)   |

| Current Range        | 1 nA - 1 μA        | 1 nA - 10 μA        |

| Synthesis tools      | Complete           | none reported       |

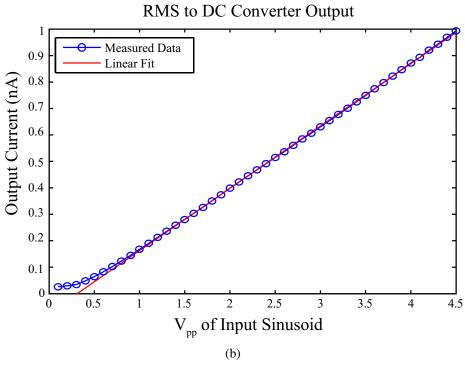

output current. The results are shown in Figure 30b.

## 3.5 Conclusion

In this chapter, we have discussed the design of a reconfigurable MITE system, the MF-PAA. This MITE-based FPAA was designed, fabricated in 350 nm CMOS, and tested. A summary of this technology and comparison to another translinear FPAA is given in Table 4. It was designed using the floating-gate switch matrix framework of the RASP 2.8 line of FPAAs. Floating-gate switches are a natural choice for MITE systems because they can share the programming overhead that is already required to program the MITEs. Along with the MFPAA IC, we also presented an entire chain of design tools: a synthesis tool, a place-and-route tool, a routing visualization GUI, an evaluation board, and the programming system. This complete system allows the user to go from a system of equations all the way to a working hardware MITE implementation. In addition to presenting the hardware and design tools, we demonstrated several working circuits. Static systems such as multipliers and squaring circuits, as well as dynamic systems such as filters and an RMS-to-DC converter were successfully tested on the hardware system.

Figure 30: RMS-to-DC converter. (a) The RMS-to-DC converter as it is complied into a single MITE CAB. The three computational stages are: square, filter, and square-root. These three functions can each be performed by a single MCE. (b) The output characteristic of the RMS-to-DC converter. The amplitude of the input sinusoid was swept from 0.1 - 4.5 V. The frequency of the input was held at 500 Hz.

### **CHAPTER 4**

## A DIGITALLY ENHANCED FPAA: THE RASP 2.9V

After discussing the concept of core FPAA primitives, the next step of the coordinated approach to analog signal processing is to design efficient hardware *architectures*. As monolithic integration of analog and digital circuitry pervades the market, integrated circuit designers are faced with the increasingly difficult task of verifying complex mixed-signal systems. The most common approach for this task is to simulate the analog sub-system, fabricate, test the mixed-signal system, and then repeat [39]. We propose that a faster and more efficient approach is to prototype mixed-signal systems using reconfigurable hardware. In this scenario, the digital portion is compiled to a reconfigurable digital platform (such as an FPGA) and the analog portion is compiled to reconfigurable analog hardware (an FPAA). For this mixed system to work harmoniously, the analog portion needs to have the capability of being digitally controlled. In addition to simple prototyping, digitally enhanced reconfigurable analog systems are extremely powerful for embedded computing applications, providing enhanced controllability to digital elements.

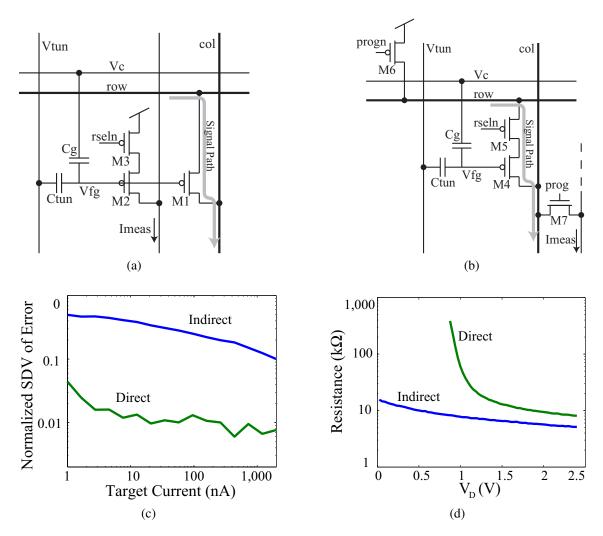

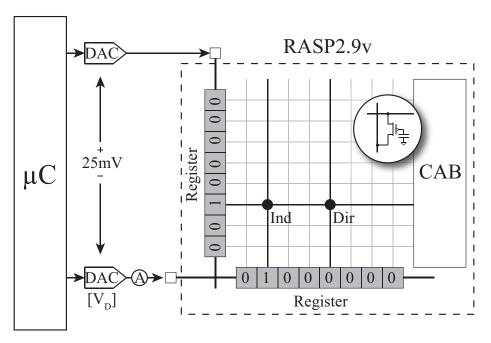

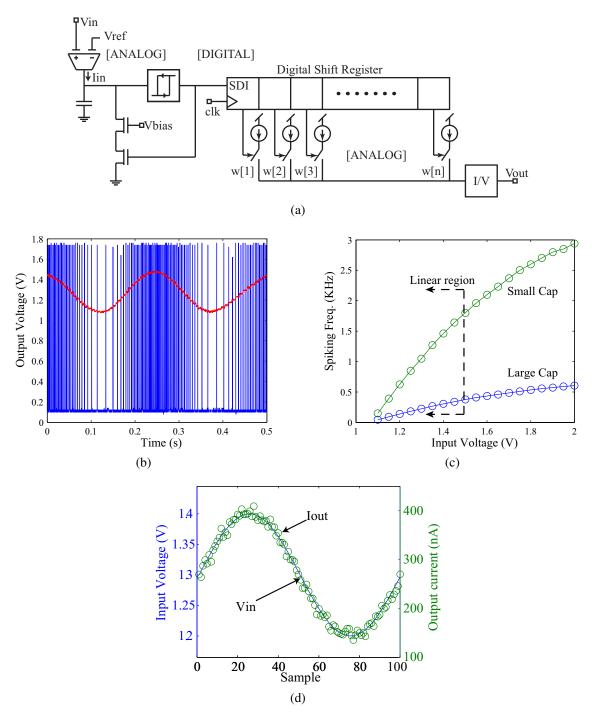

This chapter presents the RASP 2.9v, the next generation of FPAA architecture [40, 41].