# LOW-POWER, HIGH-EFFICIENCY, AND HIGH-LINEARITY CMOS MILLIMETER-WAVE CIRCUITS AND TRANSCEIVERS FOR WIRELESS COMMUNICATIONS

A Dissertation Presented to The Academic Faculty

by

Eric A. Juntunen

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology August 2012

# LOW-POWER, HIGH-EFFICIENCY, AND HIGH-LINEARITY CMOS MILLIMETER-WAVE CIRCUITS AND TRANSCEIVERS FOR WIRELESS COMMUNICATIONS

Approved by:

Professor Ioannis Papapolymerou, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Debasis Dawn, Adjunct Faculty and Co-Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Professor John D. Cressler School of Electrical and Computer Engineering Georgia Institute of Technology Professor Gee-Kung Chang School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Emmanouil M. Tentzeris School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Christos Alexopoulos School of Industrial and Systems Engineering Georgia Institute of Technology

Date Approved: April 16, 2012

To Clyde,

### ACKNOWLEDGEMENTS

First I would like to thank my Advisor, Dr. Ioannis "John" Papapolymerou who was an excellent professor in RF engineering during the beginning of my graduate work and has been an excellent PhD advisor during the conclusion of it. Second, I would like to thank my Co-Advisor, Dr. Debasis Dawn, who has given me superb technical guidance in field of millimeter-wave CMOS and helped me navigate the often uncertain waters of academia. Next, I would like to thank the rest of my dissertation defense committee: Drs. John Cressler, G.K. Chang, Manos Tentzeris, and Christos Alexopoulos. I am supremely privileged to have had the chance to discuss my research with them and improve upon it under their expert guidance.

Thank you to Dr. Swapan Bhattacharya, Wasif Khan, Chad Patterson and other members of the MircTech Research Group. Thank you to Dr. Stephane Pinel, Dr. Saikat Sarkar, Dr. Padmanava Sen, Dr. Bevin Perumana, Dr. David Yeh, Dr. Francesco Barale, Dr. Kevin Chuang, Dr. Patrick Melet, Romain Pelard, Matthew Leung and other former members of the Microwave Applications Group. Thank you to Dr. Edward Gebara for his technical guidance and encouragement. Thank you to DeeDee Bennet, Agelika Braig, and Lisa Gardner for their patience and expertise in handling whatever crisis I brought to them at 5:01pm on a Friday. Thank you to Dr. Joy Laskar, my previous advisor, who while being one of the hardest working people I know, always kept a 100% open-door policy with me to talk about any issue or concern I had, technical or nontechnical. Without his tireless and enthusiastic efforts, the worldwide state of 60-GHz communications would not be where it is today and neither would I.

There were of course many individuals outside the walls of Georgia Tech without

whose nontechnical contributions, this work would also never have been possible. Thank you to my father, Terry Juntunen, who has worked tirelessly for decades to provide me with anything and everything I have ever needed to make my way in the world. Thank you to my mother, Deanne Juntunen, who has been a permanent source of unwaivering support behind any undertaking, large or small, willing or unwilling, that I have ever attempted in my life. Thank you to my brother Jason Juntunen, who was my first true friend and who remains my best example of a genuinely kind human being. I feel privileged to have watched him transform into the wise and thoughtful man he is today and I hereby formally revoke the negative comments I made about our relationship in my 5th grade autobiography. Thank you to my brother Ryan Juntunen, who is maybe the best natured person I know. I am delighted that the 6-year gap between us is rapidly shrinking. Thank you to my late grandmother Ireta Fleischmann. Thank you to my grandmother Margaret Juntunen and her late husband, my grandfather Clyde, to whom this dissertation is dedicated. They have been spoiling me my entire live, but as it has turned out, with love.

Thank you to my graduate school roommate, Dr. Anthony Fredenburg, who was a pleasure to live with and whose work ethic and play ethic provided tremendous inspiration during a uniquely demanding period of my life. Thank you to my wife Anne Andrews Juntunen for her compassion, understanding, and support. She is among the very few people I have met who are truly leaving the world a better place than they found it.

Finally, I would like to thank Andrew Harrington who has been a better friend to me than I would have ever thought possible for nearly half of my life.

# TABLE OF CONTENTS

| DE                  | DIC          | ATIO   | Ν                                                                   | iii |

|---------------------|--------------|--------|---------------------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS iv |              |        |                                                                     | iv  |

| LIST OF TABLES is   |              |        | ix                                                                  |     |

| LIST OF FIGURES     |              |        | x                                                                   |     |

| SU                  | MM.          | ARY .  |                                                                     | xiv |

| Ι                   | INTRODUCTION |        |                                                                     | 1   |

|                     | 1.1          | Motiv  | ation                                                               | 1   |

|                     | 1.2          | Backg  | round                                                               | 1   |

|                     |              | 1.2.1  | The evolution of CMOS-based radio                                   | 1   |

|                     |              | 1.2.2  | Millimeter-Wave CMOS                                                | 3   |

|                     |              | 1.2.3  | SOI versus Bulk CMOS                                                | 4   |

|                     |              | 1.2.4  | Liquid Crystal Polymer Substrate for Millimeter-Wave Pack-<br>aging | 6   |

|                     | 1.3          | Millim | neter-Wave Applications                                             | 7   |

|                     |              | 1.3.1  | 60-GHz Band for Multi-Gigabit Wireless Communications               | 8   |

|                     |              | 1.3.2  | Q-band for Terrestrial and Space Communications                     | 10  |

|                     |              | 1.3.3  | 77-GHz Band for Automotive RADAR                                    | 11  |

|                     |              | 1.3.4  | W-band for Passive Imaging                                          | 11  |

|                     |              | 1.3.5  | E-band for Wireless Backhaul                                        | 12  |

|                     |              | 1.3.6  | Millimeter-Wave Medical Therapy                                     | 12  |

|                     | 1.4          | Organ  | ization of the Dissertation                                         | 13  |

| II                  | MII          | LLIME  | TER-WAVE MODELING                                                   | 14  |

| III                 | 60-0         | GHZ (  | OOK RECEIVER INTEGRATION                                            | 18  |

|                     | 3.1          | 60-GH  | Iz OOK Receiver                                                     | 18  |

|                     | 3.2          | 60-GH  | Iz LNA Measured Results                                             | 18  |

|                     | 3.3          | 60-GE  | Iz Direct-Conversion Demodulator                                    | 20  |

|    | 3.4                            | Integr                                                                                                | ated OOK Receiver Measured Results                                  | 25                                                                                                                                 |

|----|--------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| IV |                                |                                                                                                       | OWER, HIGH-EFFICIENCY 45-GHZ OSCILLATORS FOR ERHEAD LO DISTRIBUTION | DR<br>28                                                                                                                           |

|    | 4.1                            | Power                                                                                                 | amplifier classes of operation                                      | 29                                                                                                                                 |

|    |                                | 4.1.1                                                                                                 | Linear Power Amplifiers                                             | 30                                                                                                                                 |

|    |                                | 4.1.2                                                                                                 | Switch-mode Power Amplifiers                                        | 34                                                                                                                                 |

|    | 4.2                            | High-l                                                                                                | Efficiency, High-Power Millimeter-wave Class-E VCO                  | 40                                                                                                                                 |

|    |                                | 4.2.1                                                                                                 | Millimeter-wave Class-E PA Core                                     | 40                                                                                                                                 |

|    |                                | 4.2.2                                                                                                 | Millimeter-wave Class-E VCO                                         | 44                                                                                                                                 |

|    |                                | 4.2.3                                                                                                 | Millimeter-wave Class-E Oscillator Packaging on LCP $\ . \ . \ .$   | 48                                                                                                                                 |

|    |                                | 4.2.4                                                                                                 | Millimeter-wave Class-E VCO Measured Results                        | 52                                                                                                                                 |

|    | 4.3                            | Injecti                                                                                               | ion-Locked Oscillator                                               | 60                                                                                                                                 |

|    |                                | 4.3.1                                                                                                 | Injection-Locked Oscillator Design                                  | 60                                                                                                                                 |

|    |                                | 4.3.2                                                                                                 | Injection-Locked Oscillator Measured Results                        | 61                                                                                                                                 |

|    |                                |                                                                                                       |                                                                     |                                                                                                                                    |

| V  |                                |                                                                                                       | -CHANNEL VECTOR MODULATOR FOR LINC/BEA<br>G TRANSMITTERS            | M-<br>65                                                                                                                           |

| V  |                                | RMIN                                                                                                  |                                                                     |                                                                                                                                    |

| V  | FO                             | RMIN<br>LINC,<br>Low-F                                                                                | G TRANSMITTERS                                                      | 65                                                                                                                                 |

| V  | <b>FO</b><br>5.1               | RMIN<br>LINC,<br>Low-F                                                                                | G TRANSMITTERS                                                      | <b>65</b><br>66                                                                                                                    |

| V  | <b>FO</b><br>5.1               | RMIN<br>LINC,<br>Low-F<br>LINC                                                                        | G TRANSMITTERS                                                      | <b>65</b><br>66<br>68                                                                                                              |

| V  | <b>FO</b><br>5.1               | RMIN<br>LINC,<br>Low-F<br>LINC<br>5.2.1<br>5.2.2                                                      | G TRANSMITTERS                                                      | <b>65</b><br>66<br>68<br>69                                                                                                        |

| V  | <b>FO</b><br>5.1<br>5.2        | RMIN<br>LINC,<br>Low-F<br>LINC<br>5.2.1<br>5.2.2                                                      | G TRANSMITTERS                                                      | <ul> <li>65</li> <li>66</li> <li>68</li> <li>69</li> <li>75</li> </ul>                                                             |

| V  | <b>FO</b><br>5.1<br>5.2        | RMIN<br>LINC,<br>Low-F<br>LINC<br>5.2.1<br>5.2.2<br>Measu                                             | G TRANSMITTERS                                                      | <ul> <li>65</li> <li>66</li> <li>68</li> <li>69</li> <li>75</li> <li>77</li> </ul>                                                 |

| V  | <b>FO</b><br>5.1<br>5.2        | <b>RMIN</b><br>LINC,<br>Low-F<br>LINC<br>5.2.1<br>5.2.2<br>Measu<br>5.3.1                             | G TRANSMITTERS                                                      | <ul> <li>65</li> <li>66</li> <li>68</li> <li>69</li> <li>75</li> <li>77</li> <li>78</li> </ul>                                     |

| V  | <b>FO</b><br>5.1<br>5.2        | RMIN<br>LINC,<br>Low-F<br>LINC<br>5.2.1<br>5.2.2<br>Measu<br>5.3.1<br>5.3.2                           | G TRANSMITTERS                                                      | <ul> <li>65</li> <li>66</li> <li>68</li> <li>69</li> <li>75</li> <li>77</li> <li>78</li> <li>81</li> </ul>                         |

|    | <b>FO</b><br>5.1<br>5.2<br>5.3 | RMIN<br>LINC,<br>Low-F<br>LINC<br>5.2.1<br>5.2.2<br>Measu<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4         | G TRANSMITTERS                                                      | <ul> <li>65</li> <li>66</li> <li>68</li> <li>69</li> <li>75</li> <li>77</li> <li>78</li> <li>81</li> <li>86</li> </ul>             |

|    | <b>FO</b><br>5.1<br>5.2<br>5.3 | RMIN<br>LINC,<br>Low-F<br>LINC<br>5.2.1<br>5.2.2<br>Measu<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>NCLU | G TRANSMITTERS                                                      | <ul> <li>65</li> <li>66</li> <li>68</li> <li>69</li> <li>75</li> <li>77</li> <li>78</li> <li>81</li> <li>86</li> <li>89</li> </ul> |

| APPENDIX A   | — ACRONYM LIST | 100 |

|--------------|----------------|-----|

| APPENDIX B   | — MATLAB CODE  | 102 |

| REFERENCES . |                | 117 |

| VITA         |                | 128 |

# LIST OF TABLES

| 1 | 60-GHz OOK receiver comparison                                                | 27 |

|---|-------------------------------------------------------------------------------|----|

| 2 | Power amplifier classes of operation                                          | 30 |

| 3 | Class-E VCO version 1 performance comparison packaged versus un-<br>packaged. | 57 |

| 4 | Class-E VCO version 2 performance versus recent publications                  | 60 |

| 5 | $360^{\circ}$ Vector modulator performance comparison                         | 86 |

# LIST OF FIGURES

| 1  | Maturation of CMOS technology $f_T$                                                                           | 4  |

|----|---------------------------------------------------------------------------------------------------------------|----|

| 2  | Cross-sectional view of (a) bulk, (b) partially depleted SOI, and (c) fully depleted SOI CMOS.                | 6  |

| 3  | Millimeter-wave spectrum opportunities.                                                                       | 7  |

| 4  | Worldwide spectrum allocation in the 60-GHz band                                                              | 8  |

| 5  | Examples of Gbps connectivity in the 60-GHz band                                                              | 9  |

| 6  | Automotive RADAR location and function on commercial vehicles.                                                | 11 |

| 7  | Passive millimeter-wave imaging in the W-band                                                                 | 12 |

| 8  | Millimeter-wave modeling using added parasitic elements                                                       | 15 |

| 9  | Measured versus modeled versus PEX $S_{11}$ for a 120- $\mu$ m NMOS, 1-90 GHz                                 | 15 |

| 10 | Measured versus modeled versus PEX $S_{22}$ for a 120- $\mu$ m NMOS, 1-90 GHz                                 | 16 |

| 11 | Measured versus modeled versus PEX $ S_{21} $ for a 120- $\mu$ m NMOS, 1-90 GHz                               | 16 |

| 12 | Measured versus modeled versus PEX phase( $S_{21}$ ) for a 120- $\mu$ m NMOS, 1-90 GHz                        | 17 |

| 13 | Measured versus modeled versus PEX $ S_{12} $ for a 120- $\mu$ m NMOS, 1-90 GHz                               | 17 |

| 14 | 60-GHz OOK receiver architecture                                                                              | 18 |

| 15 | Four-stage 60-GHz LNA schematic.                                                                              | 19 |

| 16 | 60-GHz LNA: (a) die photograph, simulated versus measured (b) $ S_{21} $ ,<br>(c) $ S_{11} $ , (d) $ S_{22} $ | 19 |

| 17 | Demodulator schematic.                                                                                        | 20 |

| 18 | Small-signal transconductance, $g_m$ , of $M_1$ modulated by $M_2$                                            | 22 |

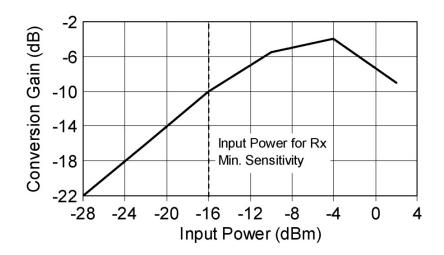

| 19 | Detector conversion gain versus input power for a 61-GHz carrier. $\ .$ .                                     | 24 |

| 20 | Detector test structure die photograph                                                                        | 24 |

| 21 | Detector test structure measured versus simulated $ S_{11} $                                                  | 25 |

| 22 | 60-GHz OOK receiver die photograph.                                                                           | 26 |

| 23 | Receiver bit error rate versus input power                                                                         | 26 |

|----|--------------------------------------------------------------------------------------------------------------------|----|

| 24 | Measured eye diagrams for (a) 1.728-Gbps and (b) 3.456-Gbps data                                                   | 27 |

| 25 | Example system using high-efficiency LO distribution                                                               | 29 |

| 26 | Example linear PA schematic.                                                                                       | 31 |

| 27 | Class-A power amplifier waveforms                                                                                  | 32 |

| 28 | Class-B power amplifier waveforms.                                                                                 | 33 |

| 29 | Class-AB power amplifier waveforms.                                                                                | 33 |

| 30 | Class-C Power Amplifier Waveforms.                                                                                 | 34 |

| 31 | Class-D power amplifier schematic.                                                                                 | 35 |

| 32 | Class-D power amplifier waveforms                                                                                  | 36 |

| 33 | Class-F power amplifier schematic.                                                                                 | 37 |

| 34 | Class-F power amplifier waveforms                                                                                  | 37 |

| 35 | Class-E power amplifier schematic.                                                                                 | 38 |

| 36 | Class-E power amplifier waveforms                                                                                  | 39 |

| 37 | Optimizing the $f_0/f_{max}$ ratio.                                                                                | 42 |

| 38 | Millimeter-wave parallel-circuit class-E PA core                                                                   | 42 |

| 39 | Class-E PA core simulated impedance looking out of the device drain.                                               | 43 |

| 40 | Simulated device drain voltage and current waveforms                                                               | 44 |

| 41 | Millimeter-wave class-E VCO schematic.                                                                             | 44 |

| 42 | VCO simplified model                                                                                               | 45 |

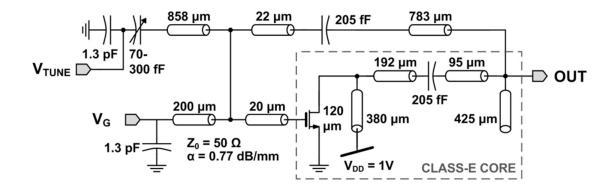

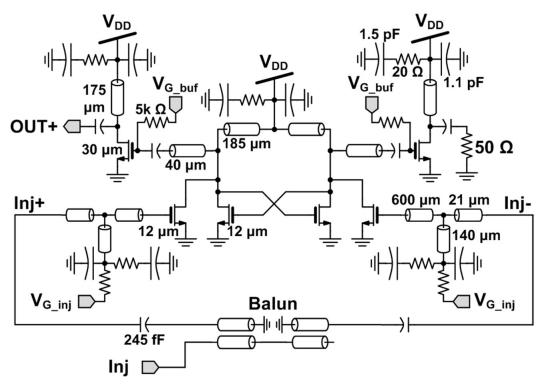

| 43 | Class-E VCO version 1 schematic.                                                                                   | 47 |

| 44 | Class-E VCO version 2 schematic.                                                                                   | 48 |

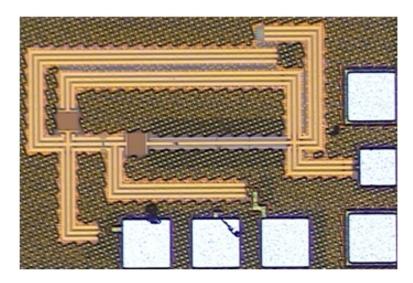

| 45 | Class-E VCO version 1 die photograph                                                                               | 49 |

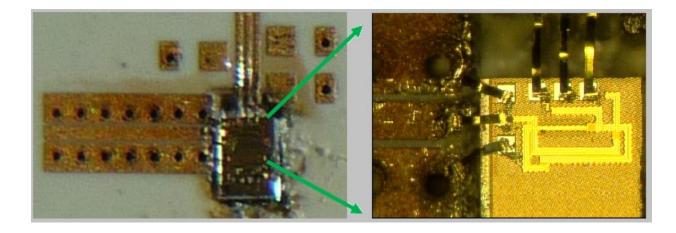

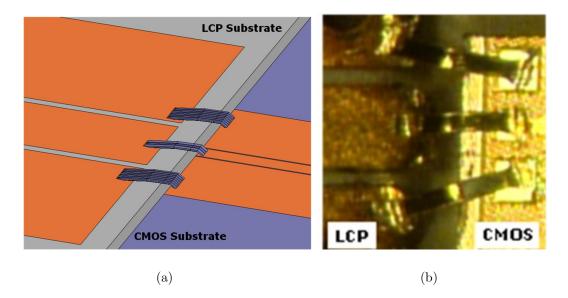

| 46 | Class-E VCO packaged on LCP substrate.                                                                             | 50 |

| 47 | Screen shot of the HFSS simulation setup, (a), and photograph of the wire bonds, (b)                               | 50 |

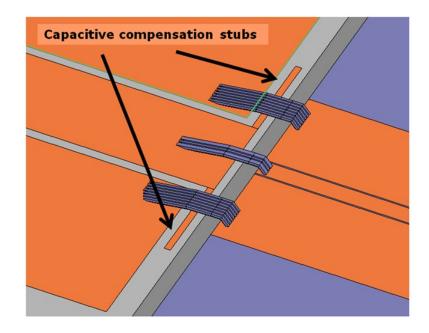

| 48 | HFSS screen shot showing capacitive compensation stubs                                                             | 51 |

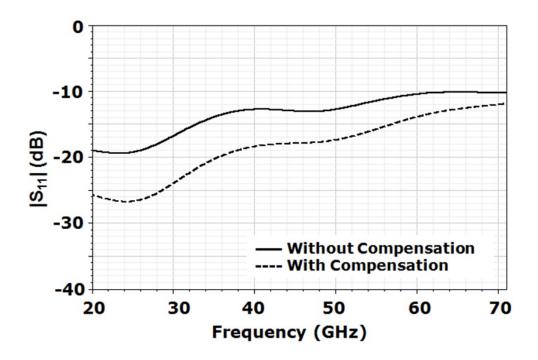

| 49 | Simulated results of the packaging input reflection coefficient with and without the capacitive compensation stub. | 52 |

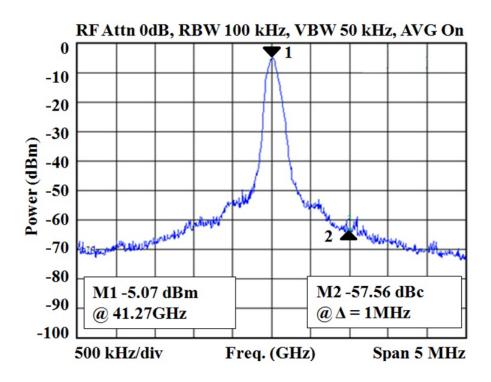

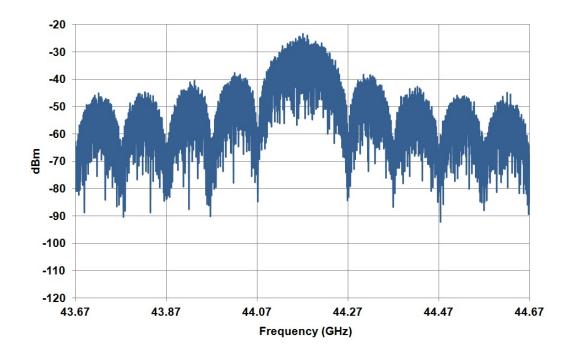

| 50 | Class-E VCO version 1 measured output spectrum, unpackaged                              | 53 |

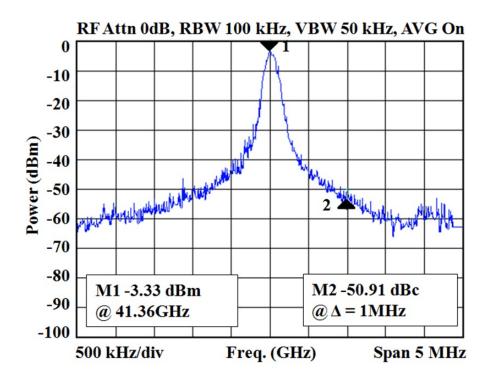

|----|-----------------------------------------------------------------------------------------|----|

| 51 | Class-E VCO version 1 measured output spectrum, packaged. $\ . \ . \ .$                 | 53 |

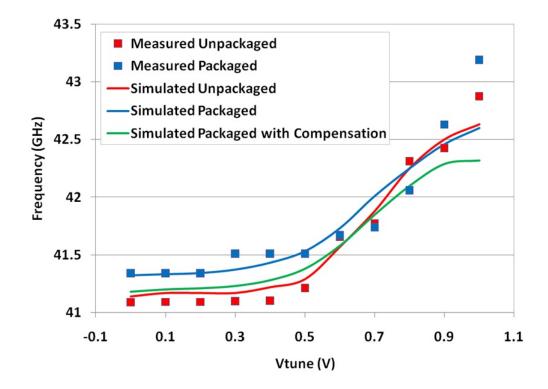

| 52 | Class-E VCO version 1 output frequency, packaged versus unpackaged.                     | 54 |

| 53 | Class-E VCO version 1 output power, packaged versus unpackaged. $% \mathcal{L}^{(1)}$ . | 55 |

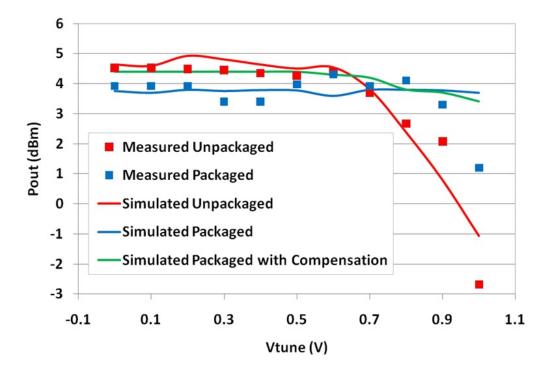

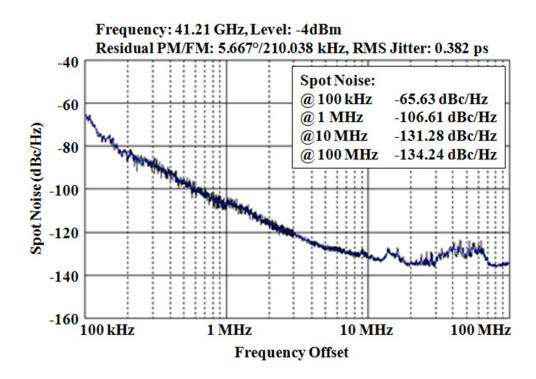

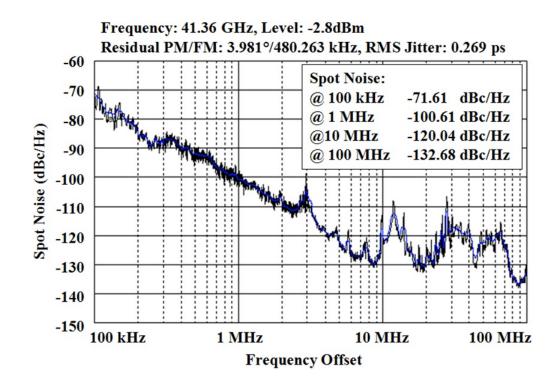

| 54 | Class-E VCO version 1 measured phase noise, unpackaged                                  | 56 |

| 55 | Class-E VCO version 1 measured phase noise, packaged                                    | 56 |

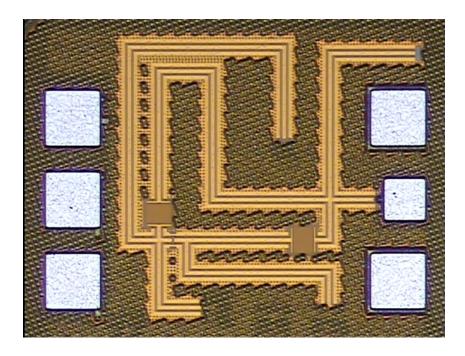

| 56 | Class-E VCO version 2 die photograph                                                    | 58 |

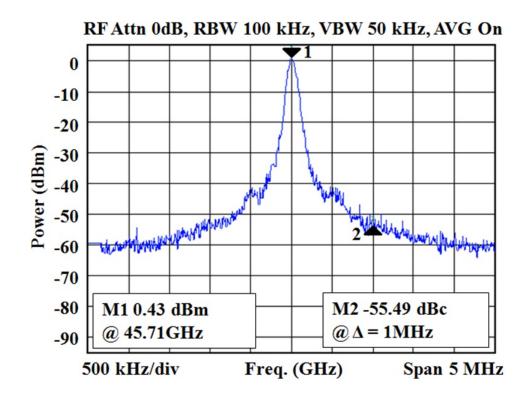

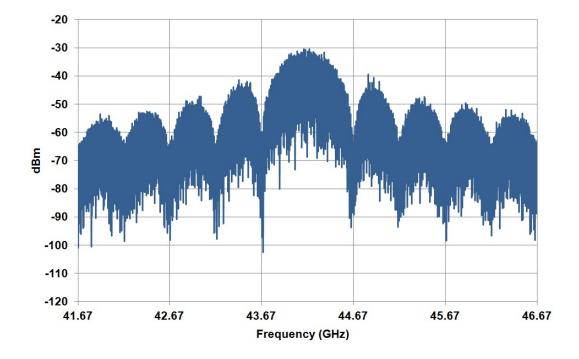

| 57 | Class-E VCO version 2 measured output spectrum                                          | 58 |

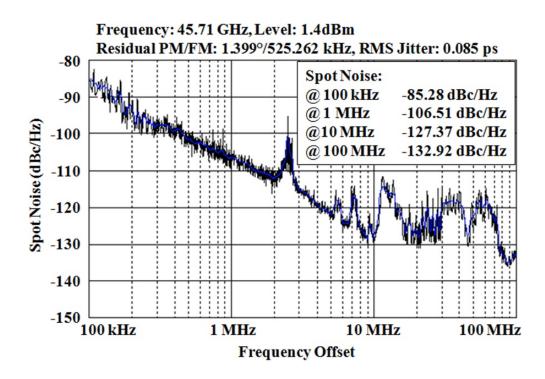

| 58 | Class-E VCO version 2 measured phase noise.                                             | 59 |

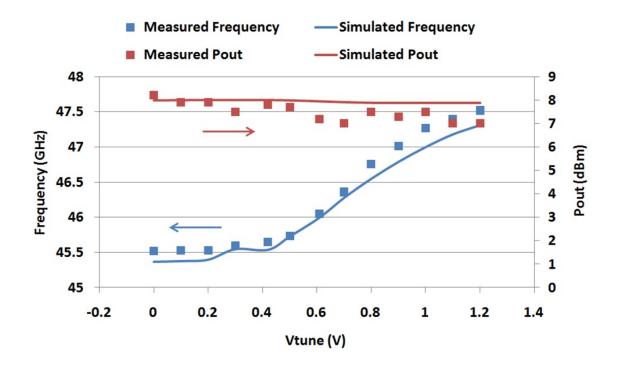

| 59 | Class-E VCO version 2 measured versus simulated output power and frequency.             | 59 |

| 60 | Millimeter-wave ILO schematic.                                                          | 61 |

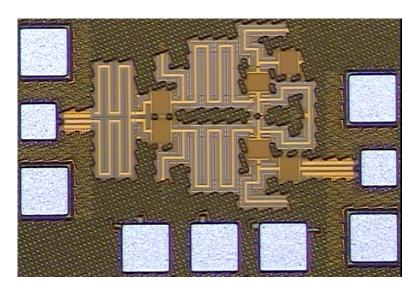

| 61 | ILO die photograph.                                                                     | 62 |

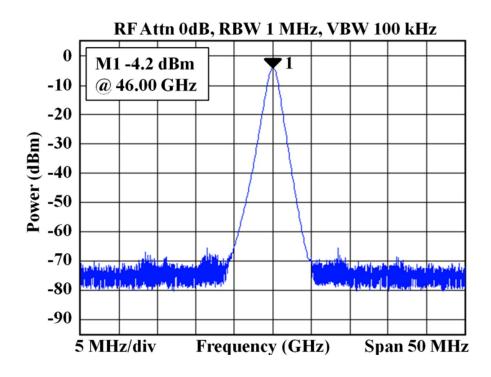

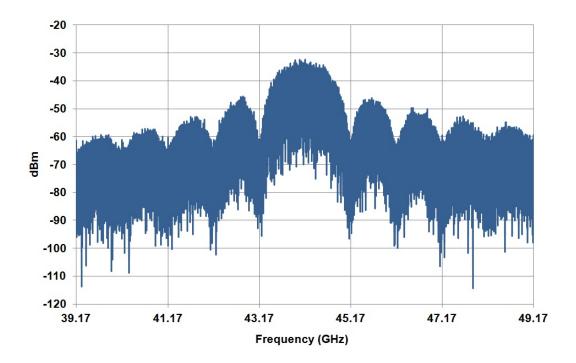

| 62 | ILO locked output spectrum                                                              | 63 |

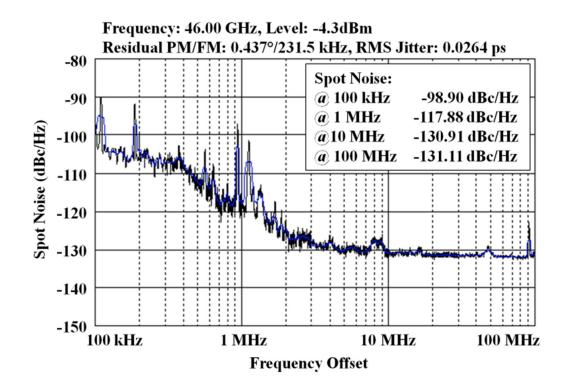

| 63 | ILO locked phase noise                                                                  | 63 |

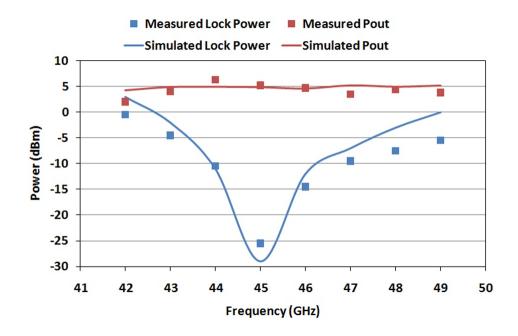

| 64 | ILO locking injected and output power levels versus frequency                           | 64 |

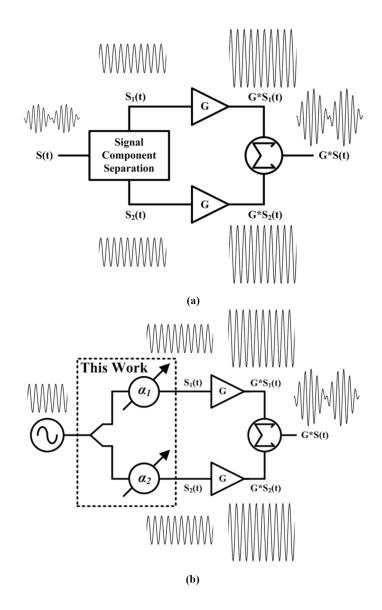

| 65 | (a) Classical LINC architecture (b) Phase modulation LINC                               | 68 |

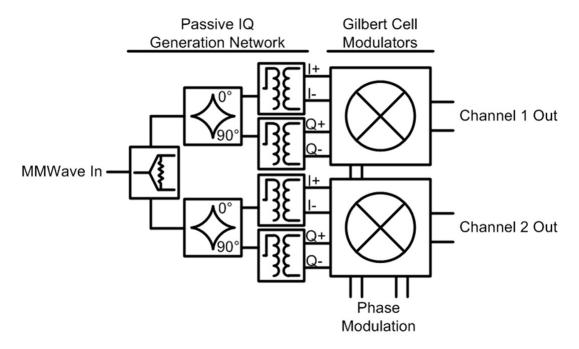

| 66 | 2-Channel millimeter-wave vector modulator block diagram                                | 69 |

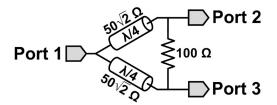

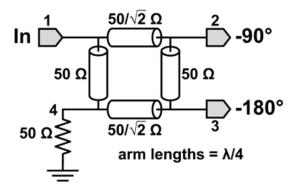

| 67 | CMOS Wilkinson power divider schematic.                                                 | 70 |

| 68 | CMOS branchline coupler 90° hybrid schematic                                            | 70 |

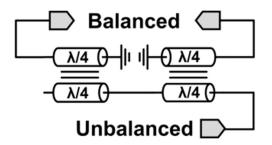

| 69 | CMOS Marchand balun schematic.                                                          | 70 |

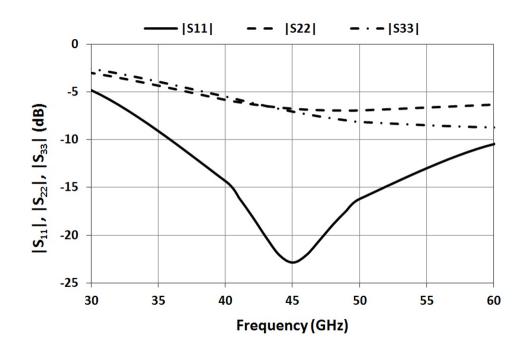

| 70 | CMOS Wilkinson power divider simulated $ S_{11} $ , $ S_{22} $ , and $ S_{33} $         | 71 |

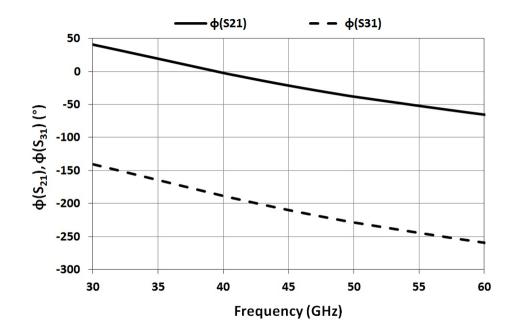

| 71 | CMOS Wilkinson power divider simulated $ S_{21} $ and $ S_{31} $                        | 72 |

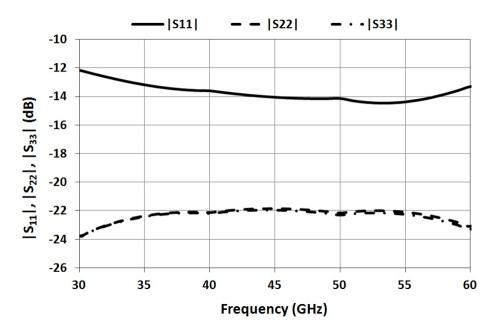

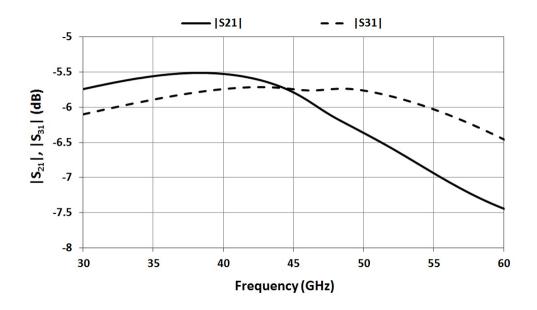

| 72 | Balun simulated $ S_{11} ,  S_{22} ,  S_{33} $ .                                        | 72 |

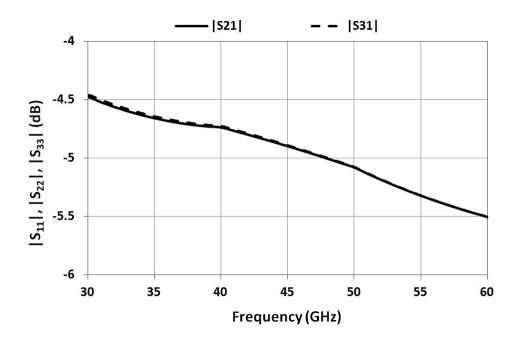

| 73 | Balun simulated $ S_{21} $ and $ S_{31} $ .                                             | 73 |

| 74 | Balun simulated $\phi(S_{21})$ and $\phi(S_{31})$ .                                     | 73 |

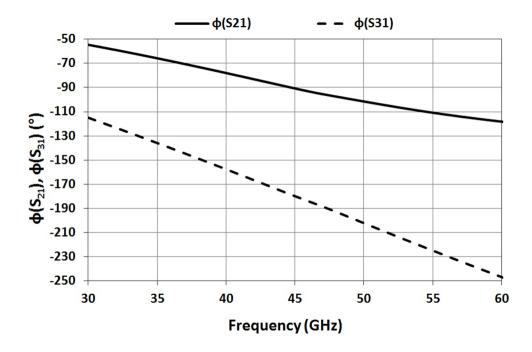

| 75 | Quadrature hybrid simulated $ S_{21} $ and $ S_{31} $ .                                 | 74 |

| 76 | Quadrature hybrid simulated $\phi(S_{21})$ and $\phi(S_{31})$                           | 74 |

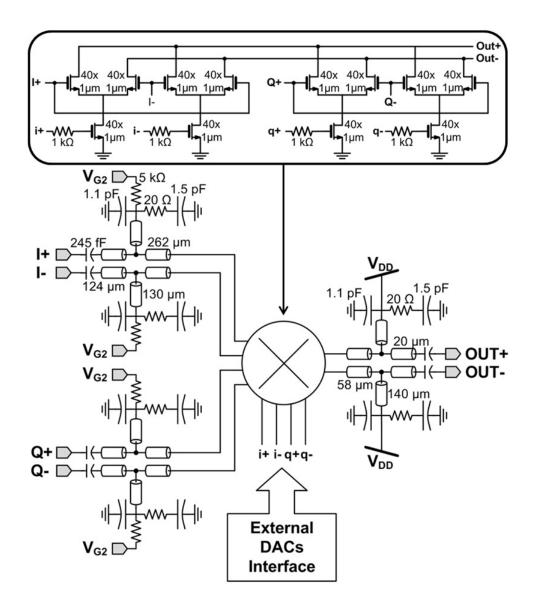

| 77 | Vector modulator Gilbert-cell core.                                                     | 76 |

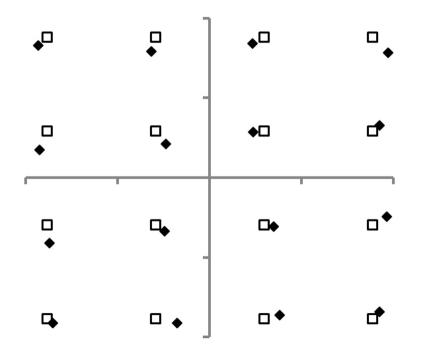

| 78 | Ideal versus simulated 16-QAM                                                                                                           | 77 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------|----|

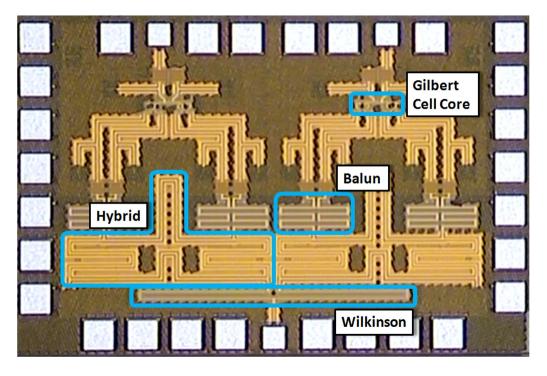

| 79 | 2-Channel vector modulator die photograph                                                                                               | 78 |

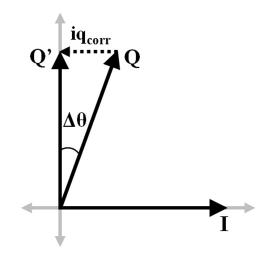

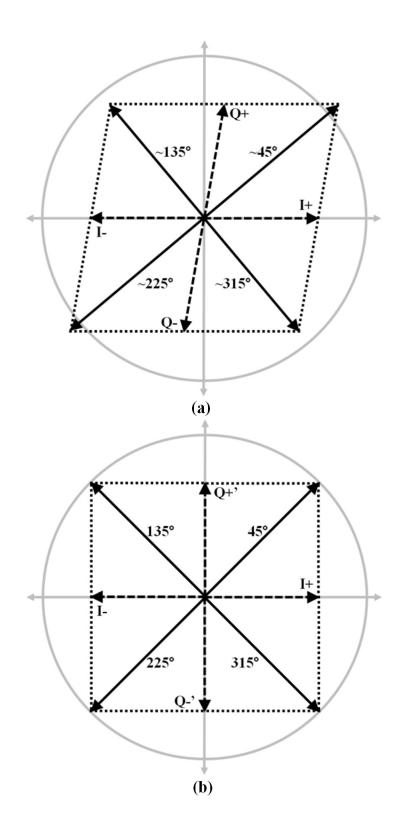

| 80 | IQ imbalance correction illustrated graphically                                                                                         | 81 |

| 81 | Using the relative magnitudes of the 45°, 135°, 225°, and 315° test vectors to correct for IQ imbalance (a) Uncalibrated (b) Calibrated | 82 |

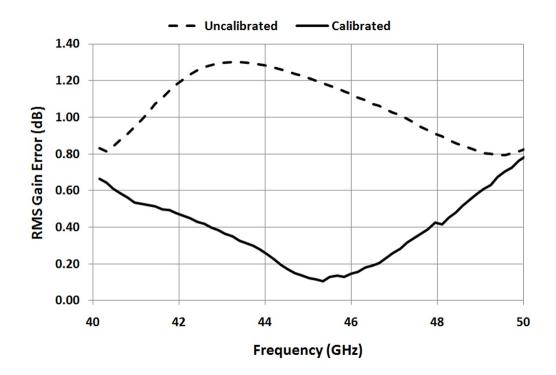

| 82 | Vector modulator RMS gain error, calibrated verus uncalibrated                                                                          | 84 |

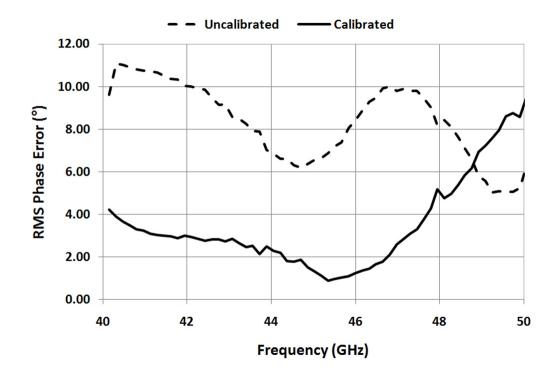

| 83 | Vector modulator RMS phase error, calibrated versus uncalibrated                                                                        | 84 |

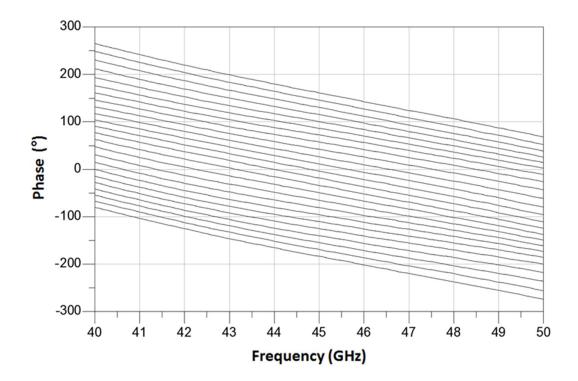

| 84 | Vector modulator phase shift for different tuning voltages, calibrated.                                                                 | 85 |

| 85 | Vector modulator gain for different tuning voltages, calibrated                                                                         | 85 |

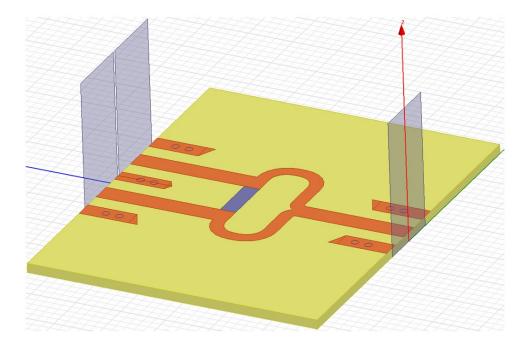

| 86 | HFSS simulation setup for the Wilkinson power combiner on LCP                                                                           | 87 |

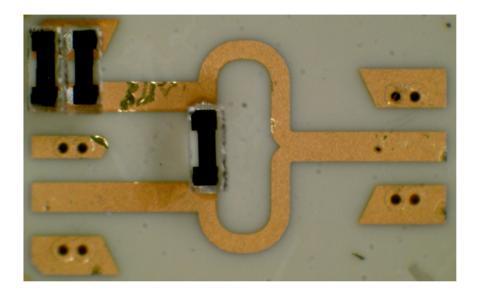

| 87 | Wilkinson power combiner on LCP, with port 3 terminated using sur-<br>face mount resistors.                                             | 88 |

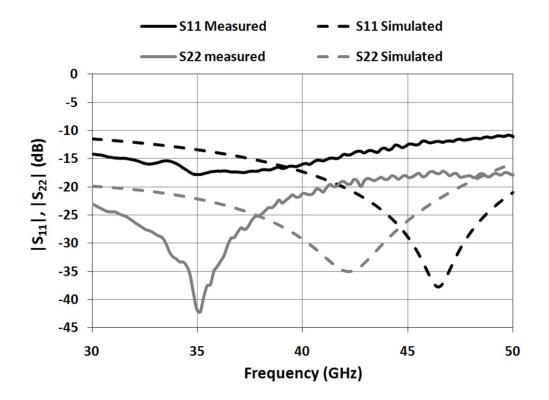

| 88 | Measured versus simulated $ S_{11} $ and $ S_{22} $ for the Wilkinson power combiner on LCP.                                            | 88 |

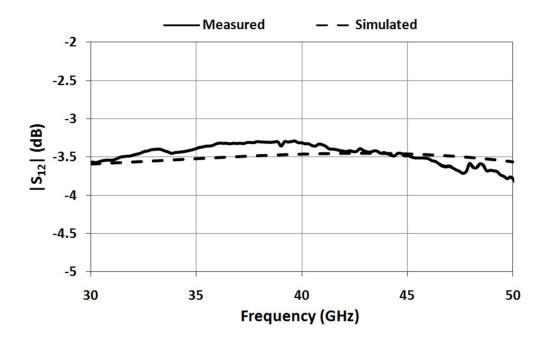

| 89 | Measured versus simulated $ S_{12} $ for the Wilkinson combiner on LCP.                                                                 | 89 |

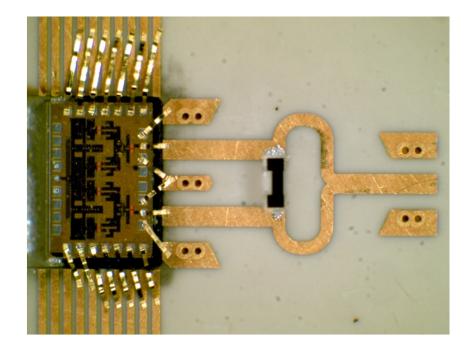

| 90 | Vector modulator die packaged with Wilkinson combiner on LCP. $\ .$ .                                                                   | 90 |

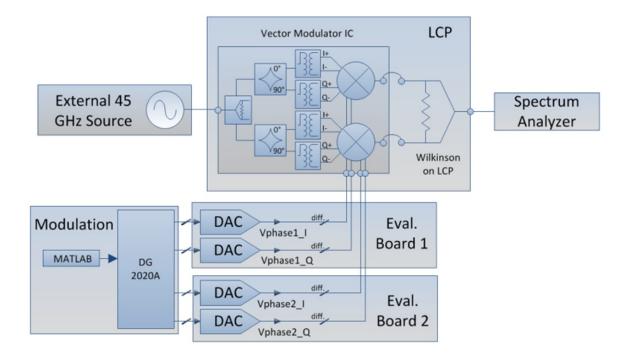

| 91 | LINC measurement setup                                                                                                                  | 91 |

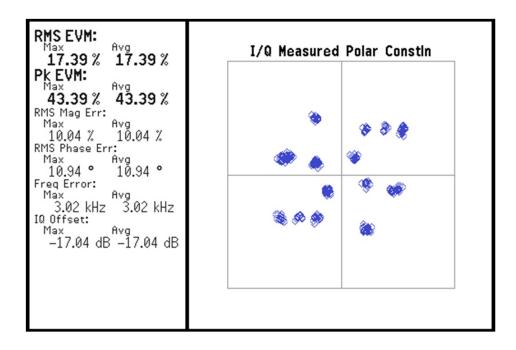

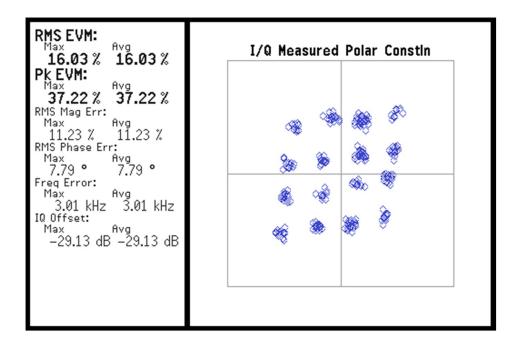

| 92 | Measured 16-QAM constellation, uncalibrated (1 Msps)                                                                                    | 92 |

| 93 | Measured 16-QAM constellation, vector magnitude cal. only (1 Msps).                                                                     | 92 |

| 94 | Measured 16-QAM constellation, full calibration (1 Msps)                                                                                | 93 |

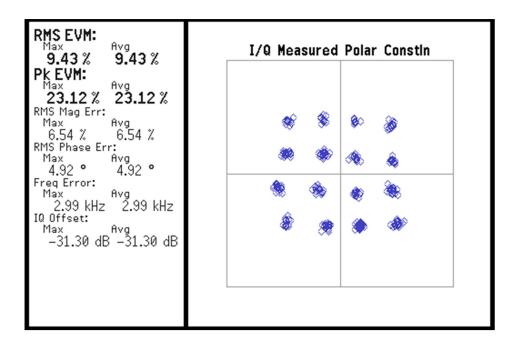

| 95 | Measured output spectrum with fully calibrated 16-QAM                                                                                   | 93 |

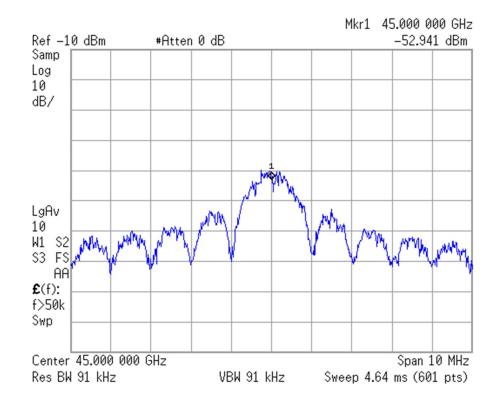

| 96 | Measured constellation and eye diagram for 100-Mbps BPSK. $\ . \ . \ .$                                                                 | 94 |

| 97 | Measured 100-Mbps BPSK spectrum                                                                                                         | 95 |

| 98 | Measured 500-Mbps BPSK spectrum                                                                                                         | 95 |

| 99 | Measured 1-Gbps BPSK spectrum.                                                                                                          | 96 |

### SUMMARY

Advancements in standard CMOS technology over the past decade have provided dramatic increases in speed and reductions in both chip area and power consumption of digital circuits. Consequently, the usable operating frequencies for analog circuits have risen as well. This has created the opportunity for consumer-volume applications in the millimeter-wave regime (30-300 GHz), an area that has historically been used almost exclusively for government and non-consumer products due to the high cost of applicable semiconductor technologies.

This dissertation presents the design and implementation of circuits and transceivers in CMOS technology to enable many new millimeter-wave applications. Chapter I first gives a brief introduction to the development of CMOS technology to support millimeter-wave design, then provides several examples of emerging millimeter-wave applications. Chapter II discusses a simple approach utilized for accurately modeling the millimeter-wave characteristics of transistors not fully captured by contemporary parasitic extraction techniques. Chapter III presents the integration of a low-power 60-GHz CMOS on-off keying (OOK) receiver in 90-nm CMOS for use in multi-gigabit per second wireless communications. The use of non-coherent OOK demodulation by a novel demodulator enabled a data throughput of 3.5 Gbps and resulted in the lowest power budget (31pJ/bit) for integrated 60-GHz CMOS OOK receivers at the time of publication. Chapter IV presents the design of a high-power, high-efficiency 45-GHz VCO in 45-nm SOI CMOS. The design is a class-E power amplifier placed in a positive feedback configuration. This circuit achieves the highest reported output power (8.2 dBm) and efficiency (15.64%) to date for monolithic silicon-based millimeter-wave VCOs. Results are provided for the standalone VCO as well as after packaging in a liquid crystal polymer (LCP) substrate. In addition, a high-power high-efficiency (5.2 dBm/6.1%) injection locked oscillator is presented. In chapter IV, the design of a 2-channel 45-GHz vector modulator in 45-nm SOI CMOS for LINC transmitters is presented. A zero-power passive IQ generation network and a low-power Gilbert cell modulator are used to enable continuous 360° vector generation. The IC is packaged with a Wilkinson power combiner on LCP and driven by external DACs to demonstrate the first ever 16-QAM generated by outphasing modulation in CMOS at in the Q-band. Finally, chapter V summarizes the techical contributions of this dissertation and provides suggestions for future research.

# CHAPTER I

### INTRODUCTION

### 1.1 Motivation

The millimeter-wave spectrum is defined as 30-300 GHz. Historically, millimeter-wave bands have been used almost exclusively for government and non-consumer products due to the cost barrier of semiconductor technologies like Gallium Arsenide (GaAs) and Indium Pohosphide (InP) that could operate at such high frequencies [1],[2]. However, the maturation of silicon technologies like CMOS and SiGe BiCMOS has created the possibility for consumer-volume products and low-cost non-consumervolume products uniquely suited for millimeter-wave operation [3],[4]. The following sections will introduce some of these applications.

#### 1.2 Background

#### 1.2.1 The evolution of CMOS-based radio

During the late 1980s, when the cellular telephone market was emerging, silicon bipolar technologies were developed with transit frequencies near 10 GHz. This provided enough margin to support devices with carrier frequencies below 1 GHz [5]. Earlier in the decade, RF design had been dominated by GaAs, but the prospect of expanding the role of less expensive silicon bipolar technologies compatible with common CMOS fabrication equipment motivated the industry to develop high performance RF silicon technology.

By the mid 1990s, industry leaders were in a race for market share in the rapidly expanding cellular handset market. At that time CMOS processes were far inferior to silicon bipolar technologies and III-V devices such as Gallium Arsenide (GaAs) with respect to high-frequency analog design. Therefore, due to time-to-market constraints and the limited availability of designers familiar with differing radio architectures, silicon bipolar and GaAs development dominated the private sector.

The systems developed in industry during that time were characterized by low levels of integration, with many discrete elements assembled on PC boards. Academia, however, was not bound by market constraints and began to explore the possibility of developing highly integrated CMOS chips for the RF domain in the hopes that its success in the baseband wireline market could soon be applied to the wireless arena [6]. RF CMOS research drove the development of on-chip inductors with practical usage for high-volume production. This enabled CMOS front-end circuits previously unavailable to the system engineer. The first inductors to appear were suspended spiral inductors that eliminated the prohibitive problems of substrate capacitance and eddy current loss [7]. The availability of these new on-chip inductors allowed for the design of fully integrated, tuned low-noise amplifiers [8].

Later, improved layout approaches suitable for mass-production replaced the suspended inductor and were offered in RF CMOS processes [9]. The major roadblock for on-chip spiral inductors had been their lossy nature compared to discrete components [10]. Resistive losses were mitigated by implementing processes with a thick top metal layer available to the designer. More problematic, however, were substrate losses due to eddy currents. This led to the development of new generations of CMOS substrates with low doping levels. In addition, shielding metal layers were placed below the spirals whose geometry prevented the flow of eddy currents [11]. The availability of these new higher-Q inductors led to fully on-chip CMOS oscillators whose phase noise performance could complete with that of discrete transistor oscillators. The ability of the MOSFET to function as a switch enabled frequency tuning using switched reactive elements [12]. This led to band switching techniques that could extend the useful range of frequency selection and/or correct for frequency shift due to process variation. The emergence of markets for IEEE 802.11 and Bluetooth® products came with a different set of rules for engineering firms. In contrast to cellular handsets, the success of WLAN chipsets would be determined more by production costs because service providers would no longer subsidize the technology. This would require higher levels of integration to eliminate the need for costly off-chip discrete components. The solution was the development of complete systems on single chips in the least expensive semiconductor process available, CMOS. Emerging standards were written with specifications relaxed in such a way that CMOS radios became viable solutions. This brought CMOS development to the forefront of industrial development.

#### 1.2.2 Millimeter-Wave CMOS

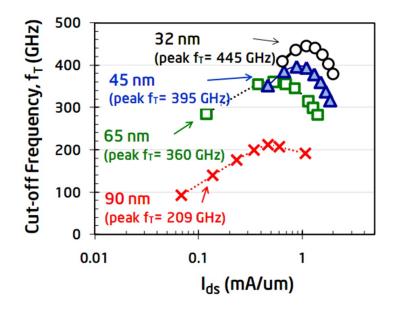

The continued maturation of CMOS technology to operate at millimeter-wave frequencies is in some ways a byproduct of the research and development driven by digital concerns. Over the past decade, CMOS geometry scaling motivated primarily by the need for smaller area, faster speeds, and lower power consumption in digital circuits has pushed the transit frequency,  $f_T$ , and maximum frequency of oscillation,  $f_{max}$ , of standard, production-level CMOS into the many hundreds of GHz [13],[14]. This has enabled robust millimeter-wave front-end design in standard CMOS technology [3]. Seen in Figure 1 is a plot from [13] illustrating the scaling of  $f_T$  with CMOS process node. The opportunity now exists for highly integrated CMOS transceivers with reliable millimeter-wave front-ends, mixed-signal content, and full digital back ends on a single die.

**Figure 1:** Maturation of CMOS technology  $f_T$ .

#### 1.2.3 SOI versus Bulk CMOS

This work advocates the use of CMOS technology for millimeter-wave System on Chips (SoCs) that will combine millimeter-wave front end radios with digital back end signal processing and calibration. Therefore, a brief discussion of the implications that modern CMOS technology advances driven by digital concerns will have on analog front ends is included.

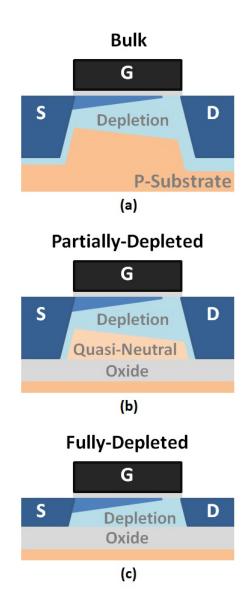

Seen in Figure 2 are cross-sections of an nMOS transistor in conventional bulk CMOS, partially-depleted (PD) silicon-on-insulator (SOI) CMOS, and fully-depleted (FD) SOI CMOS. In bulk CMOS, the body of the transistor is formed by the psubstrate. In SOI CMOS, there exists an electrically insulating layer, usually silicon dioxide, below the transistor structure, separating it from the wafer substrate. This geometry has a number of well-understood benefits to digital circuitry. The decreased junction capacitances result in higher speed and a 30-40% reduction in power consumption [15]. Decoupling the transistor body from the substrate eliminates the possibility of latchup and increases the isolation between devices, which allows for tighter transistor packing. Furthermore, substrate coupled noise is dramatically reduced, benefiting both digital and analog circuits. Specific benefits for analog and RF circuits include an increase in  $f_T$  due to the reduction of parasitic junction capacitance, and an increase in transconductance from a decreased bulk effect [16].

SOI CMOS does, however, present a number of challenges when it is used for analog and RF circuit design. Temperature rise due to thermal insulation from the buried oxide can cause a degradation in charge carrier mobility and saturation velocity [17]. This effect is not an issue for digital circuits because it is seen only during switching periods, but it can be very detrimental for analog circuits biased well into saturation. In PD SOI, the body is in a floating, or quasi-static, state. This causes memory effects whereby the residual charge contained in the body resulting from past operation affects the present device characteristics [16]. The floating body also leads to a parasitic BJT structure formed by the drain, body, and source regions. For high enough drain to source voltages, this BJT will turn on, creating an additional current path parallel to the CMOS channel. This results in a "kink" effect in the I<sub>D</sub> versus  $V_{DS}$  curves [16]. The use of body contacts eliminates these effects, but comes at the cost of larger transistor area.

In FD SOI, the distance between the gate oxide and the buried oxide is made much smaller. Therefore, the depletion region extends all the way down to the buried oxide layer. This eliminates the floating body effects seen in PD SOI, but the tradeoff is a threshold voltage sensitivity to the thickness of the silicon layer [16]. This yields an increased risk of process variation induced mismatch between devices.

The continued attraction of CMOS for RF and millimeter-wave designs will be driven largely by its ability to incorporate dense, low-power digital subsystems on the same die as analog circuitry. Therefore, because of the many benefits SOI technology provides for digital circuits, RF and analog designers must understand the implications of SOI CMOS technology.

**Figure 2:** Cross-sectional view of (a) bulk, (b) partially depleted SOI, and (c) fully depleted SOI CMOS.

### 1.2.4 Liquid Crystal Polymer Substrate for Millimeter-Wave Packaging

CMOS technology is an attractive solution for bringing millimeter-wave systems to a large consumer market because of its low cost and high digital integration for back-end functionality. However, a low-cost package with good performance at millimeter-wave frequencies must be utilized to enable the complete solution. Liquid Crystal Polymer (LCP) has gained considerable attention recently as a lowcost millimeter-wave substrate and packaging material since it became commercially available in 2003 [18]-[20]. Its stable dielectric constant (2.95-3.16), low loss tangent (0.002-0.004) over a wide frequency range (30-110 GHz), inherent near-hermetic property and low processing temperature make LCP a very attractive packaging solution for microwave applications [21]. LCP was demonstrated to be a suitable substrate for creating high-quality resonant microwave structures in [22] and an appropriate packaging material for MMICs in [23]. Recently, a millimeter-wave SiGe VCO packaged in LCP was demonstrated in [24].

# 1.3 Millimeter-Wave Applications

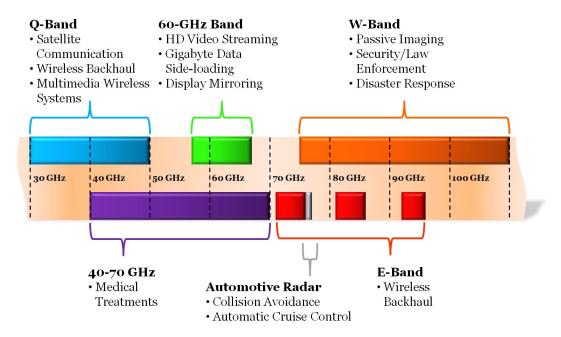

The following sections describe a number of emerging opportunities in the lower portion (< 110GHz) of the millimeter-wave spectrum. Figure 3 summarizes these applications.

Figure 3: Millimeter-wave spectrum opportunities.

#### 1.3.1 60-GHz Band for Multi-Gigabit Wireless Communications

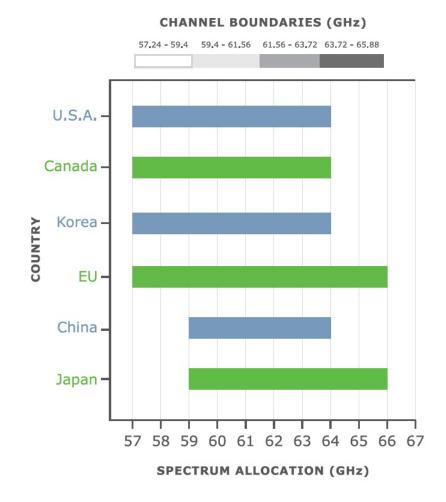

The proliferation of high-definition digital multimedia content and increasing data storage capabilities on fixed and mobile devices alike will drive the need for higher data-rate wireless connectivity than can be provided with existing commercial standards such as 802.11n [25]. For this reason, governments worldwide have made large spectral allocations to support unlicensed multi-gigabit wireless communications as seen in Figure 4.

Figure 4: Worldwide spectrum allocation in the 60-GHz band.

The 60-GHz band has a number of characteristics that make it particularly attractive for short-range wireless communications. The free space path loss is given by (1), where the distance d is in meters and the frequency f is in GHz.

$$FSPL(dB) = 20log(d) + 20log(f) + 32.45$$

(1)

Based on this phenomenon alone, the link budget at 60 GHz is approximately 21 dB less than for an equidistant 5-GHz 802.11 WLAN link. However, there exists an atmospheric oxygen absorption peak at 60 GHz that contributes additional loss [26]. Furthermore, since antenna directivity increases with frequency, millimeter-wave links will be strongly line-of-sight [27]. Although a drawback for long-distance terrestrial communications, both of these characteristics can be leveraged to enable frequency reuse such that many multi-gigabit links between various devices may coexist within close proximity. The types of connectivity that can be enabled using the 60-GHz band include wireless high-definition multimedia streaming and Gbps data side-loading as depicted in Figure 5.

Figure 5: Examples of Gbps connectivity in the 60-GHz band.

In pursuit of these types of connectivity, many organizations have been in competition to drive the standardization of 60-GHz interoperability. In 2005, the IEEE 802.15.3c technical committee was formed to develop a millimeter-wave based physical layer (PHY) specific to the 60-GHz band as an extension of the existing 802.15.3 wireless personal area network (WPAN). Later, in 2007, the IEEE 802.11 working group for wireless local area network (WLAN) standards formed the very high throughput study group (VHT-SG) that would work to define a new task group organized under 802.11. In early 2009 the VHT-SG completed its work with the formation of the 802.11ad task group, which would also focus on 60-GHz standardization. In late 2009 the 802.15.3c entered hibernation after ratifying the *802.15.3c Multi-gigabit speed Wireless PAN Standard*. During the same period, ECMA International was developing yet another 60-GHz standard. The ECMA-387 standard was released in late 2008. In 2009 ISO/IEC JTC 1 amended and approved the first version of ECMA-387.

In addition, a number of industry consortia have formed to leverage influence on the development of 60-GHz standardization including Wireless HD, The Wireless Gigabit Alliance (WiGiG), The WiMedia Alliance, and the Wireless Home Digital Interface (WHDI) Consortium. Currently, WiGig appears to have the most traction and is currently drafting PHY and medium access control (MAC) specifications that will serve as the basis for the IEEE 802.11ad draft standard [28]. The WiGig specification will define a common MAC shared between existing Wi-Fi devices operating at 2.4 and 5 GHz with the new 60-GHz devices, the goal being to provide seamless switching between these three bands to support connectivity modes with different requirements.

#### 1.3.2 Q-band for Terrestrial and Space Communications

A large spectral space that heretofore has received less attention from academia and industry is the Q-band, defined from 30 GHz to 50 GHz. This band is used primarily for high data-rate satellite communications as well as high-resolution radar [29]. However, there exists growing interest in exploiting this spectrum for high-bandwidth terrestrial links such as fixed point to point cellular backhaul applications or multimedia distribution systems [30].

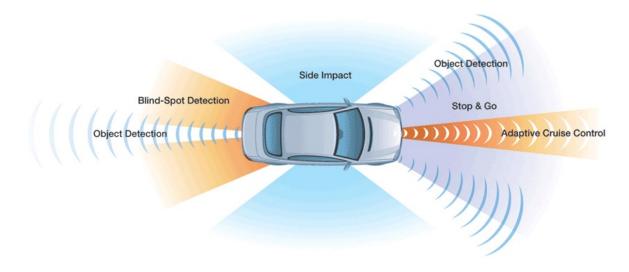

#### 1.3.3 77-GHz Band for Automotive RADAR

Another millimeter-wave application with large-scale commercial viability is automotive radar [31]. The 77-GHz band has been reserved for the implementation of features such as automatic cruise control, blind-spot monitoring, and front and rear object detection for collision avoidance as illustrated in Figure 6 [32]. Both Freescale and Infineon have developed integrated SiGe transceivers for Automotive RADAR in the 77-GHz band. Until the present, Automotive RADAR systems have mainly found adoption in the high-end car market. However, as the cost of these systems is brought down through further development in inexpensive silicon technologies, they will soon be feasible for the mid-rage automobile market. This will allow these increased safety benefits to reach a larger number of drivers.

Figure 6: Automotive RADAR location and function on commercial vehicles.

#### 1.3.4 W-band for Passive Imaging

It has been demonstrated that the W-band (75-110 GHz) is well suited for passive radar imaging [33],[34]. At these frequencies, there is a unique intersection of high spatial resolution, material penetration, and low atmospheric absorption. Potential applications include security, law enforcement, and body detection in low or zerovisibility conditions such as fires or natural disasters. Seen in Figure 7 is a passive radar image showing the discovery of a concealed weapon that would have gone unnoticed using a metal detector [35].

Figure 7: Passive millimeter-wave imaging in the W-band.

#### 1.3.5 E-band for Wireless Backhaul

In 2003, the FCC designated 13 GHz of previously unused spectrum from 71-76 GHz, 81-86 GHz, and 92-95 GHz for licensed, fixed wireless communications [36]. These three bands, collectively termed the E-band, can enable multi-gigabit links with distances on the order of one mile. The high transmission-power of these systems prohibits the use of full CMOS transceivers. However, moving all but perhaps the PA and LNA to a silicon-based design can yield tremendous cost savings in the deployment of backhaul networks.

#### **1.3.6** Millimeter-Wave Medical Therapy

It has been shown that exposure to low-levels of millimeter-wave energy may have a number of medical benefits [37],[38]. Potential areas of application include treatment

of cardiovascular disease, mitigation of chronic pain such as arthritis, and tissue regeneration stimulus. Treatments are typically administered at hospitals using large, expensive machines. However, the ability to generate low-power millimeter-wave energy in low-cost silicon technologies can enable inexpensive in-home treatment options for such conditions.

# 1.4 Organization of the Dissertation

Chapter II discusses the simple approach utilized for accurately modeling the millimeterwave characteristics of transistors that are not fully captured by contemporary parasitic extraction techniques. Next, Chapter III presents the integration of a lowpower 60-GHz CMOS OOK receiver in 90-nm CMOS for use in multi-gigabit per second wireless communications. Chapter IV presents the design of a high-power, high-efficiency 45-GHz voltage controlled oscillator (VCO) and an injection-locked oscillator (ILO) in 45-nm SOI CMOS. One version of the VCO is packed in LCP to demonstrate the suitability of LCP for millimeter-wave packaging. In chapter V, the design of a 2-channel 45-GHz vector modulator in 45-nm SOI CMOS for LINC transmitters is presented. The IC is packaged with a Wilkinson power combiner on LCP and driven by external DACs to demonstrate the first ever 16-QAM generated by outphasing modulation in CMOS in the Q-band. Finally, chapter VI summarizes the technical contributions of this dissertation and provides suggestions for future research.

# CHAPTER II

### MILLIMETER-WAVE MODELING

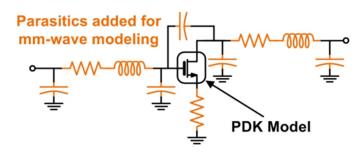

To perform reliable millimeter-wave CMOS design, additional modeling effort is needed beyond what would likely be required at lower frequencies. Typically, scalable compact models with accuracy beyond 30 GHz are not readily available to the designer. Furthermore, conventional post-layout parasitic extraction software cannot capture the small inductances introduced by metal interconnects that have a large impact on the frequency response and port impedances of active and passive circuit elements at millimeter-wave frequencies. This requires that models for transistors, capacitors, transmission lines, and inductors be verified and fine-tuned using in-house empirical data.

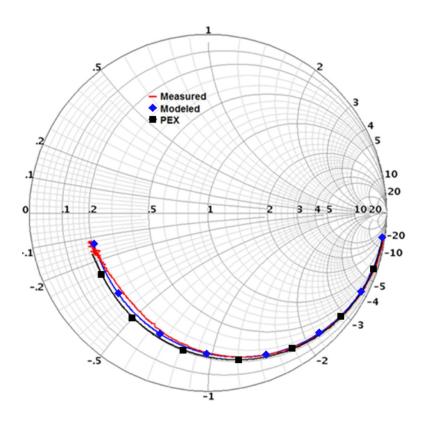

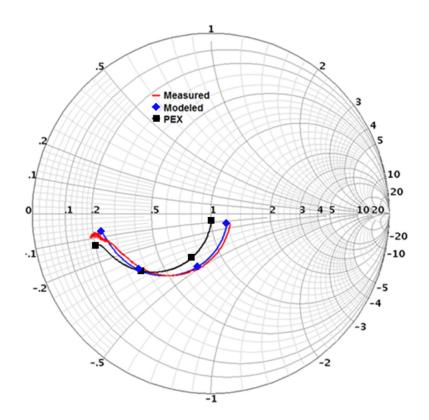

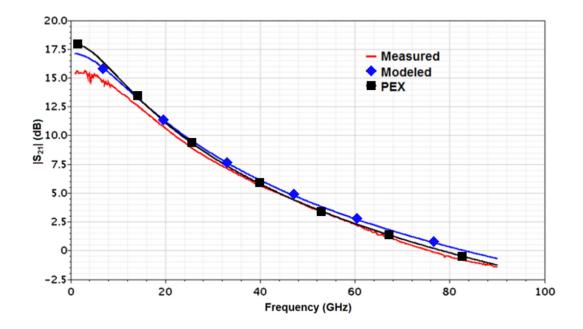

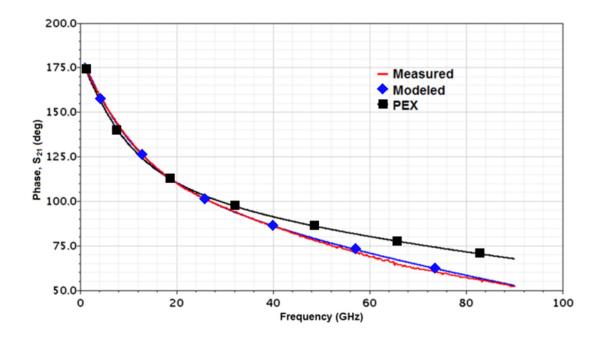

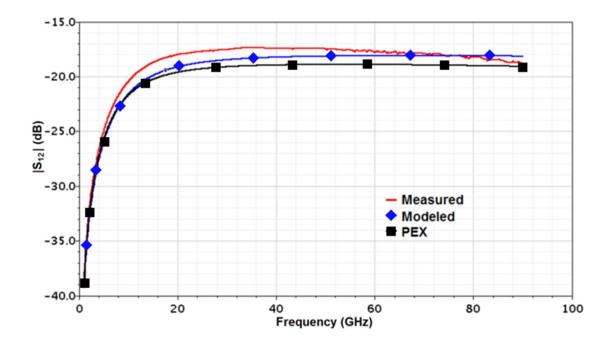

A simple and effective modeling approach, which may be used directly in the native design environment of the circuit, is to take the PDK element provided by the foundry and add parasitic components surrounding it to match its simulated performance with its measured performance [39], as seen in Figure 8. Shown in Figures 9 - 13 are the measured versus modeled versus post-layout RC parasitic extracted (PEX) S-parameters for a 120- $\mu$ m common-source NMOS device. Note in particular that the phase of  $S_{21}$  seen in Figure 12, which is of critical importance in determining the oscillation frequency of the VCO in Chapter 4, has the largest discrepancy between PEX and measurement.

Figure 8: Millimeter-wave modeling using added parasitic elements.

Figure 9: Measured versus modeled versus PEX  $S_{11}$  for a 120- $\mu$ m NMOS, 1-90 GHz.

Figure 10: Measured versus modeled versus PEX  $S_{22}$  for a 120- $\mu$ m NMOS, 1-90 GHz.

**Figure 11:** Measured versus modeled versus PEX  $|S_{21}|$  for a 120- $\mu$ m NMOS, 1-90 GHz.

Figure 12: Measured versus modeled versus PEX phase( $S_{21}$ ) for a 120- $\mu$ m NMOS, 1-90 GHz.

**Figure 13:** Measured versus modeled versus PEX  $|S_{12}|$  for a 120- $\mu$ m NMOS, 1-90 GHz.

# CHAPTER III

### 60-GHZ OOK RECEIVER INTEGRATION

### 3.1 60-GHz OOK Receiver

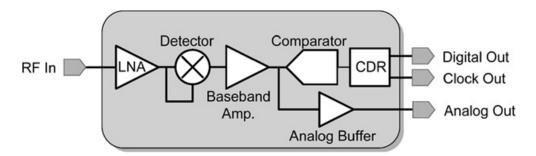

Component design for a proposed 60-GHz on-off keying (OOK) Receiver was performed in [40]. These components were subsequently integrated into a receiver that was part of a fully-integrated single-chip 60-GHz transceiver [41]. The receiver architecture is shown in Figure 14. The lineup includes a four-stage 60-GHz low noise amplifier (LNA), a 60-GHz power detector for OOK demodulation, and a high-gain baseband amplifier. In addition, a 1-bit comparator and a linear Hodge clock and data recovery (CDR) circuit are integrated to provide a clocked serial output of digital data.

Figure 14: 60-GHz OOK receiver architecture.

### 3.2 60-GHz LNA Measured Results

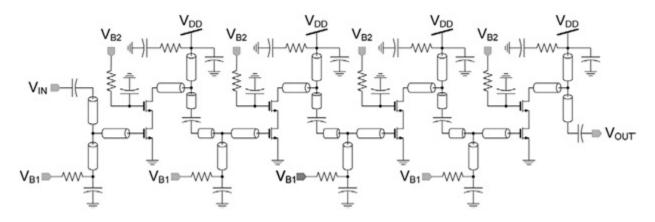

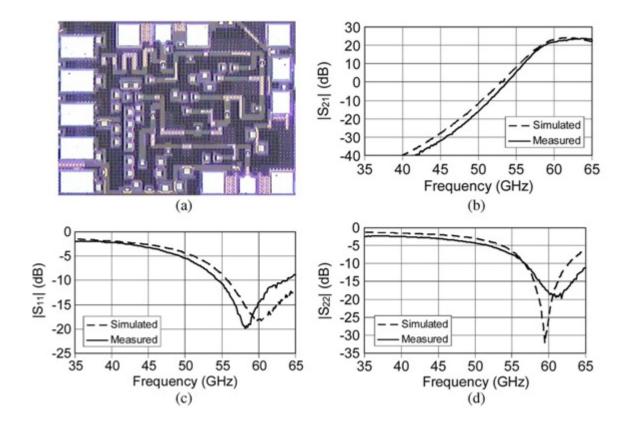

Seen in Figure 15 is the schematic diagram of the 4-stage LNA [41]. A die photograph of a four-stage LNA test structure along with its measured s-parameter performance is seen in Figure 16. The LNA occupies a die area of 0.6 mm x 0.75 mm while delivering a peak gain of 24 dB and a 7.5-dB noise figure at a DC power consumption

of  $64\ \mathrm{mW}.$

Figure 15: Four-stage 60-GHz LNA schematic.

Figure 16: 60-GHz LNA: (a) die photograph, simulated versus measured (b)  $|S_{21}|$ , (c)  $|S_{11}|$ , (d)  $|S_{22}|$ .

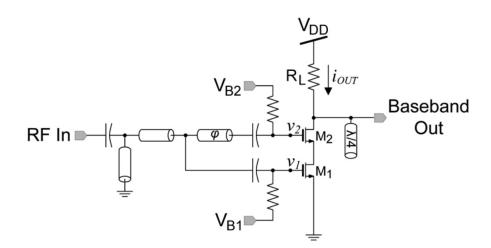

## 3.3 60-GHz Direct-Conversion Demodulator

An innovative demodulator circuit, seen in Figure 17, was designed to extract baseband data from a 60-GHz OOK-modulated signal. The circuit is an autocorrelator based upon dual-gate mixer architecture. The input is matched to 50  $\Omega$  using a seriesstub micro-strip matching network. Power detection is performed by multiplying the 60-GHz input signal by a 180° delayed version of itself. The series transmission line at the  $v_2$  port creates a phase delay  $\phi = 180^\circ$  between the waveforms at the  $v_1$  and  $v_2$ ports. Additionally, this line functions as a resonant structure that provides a voltage gain due to the high-impedance loading at the  $v_2$  port. This voltage boost, denoted by  $\beta$ , was simulated to be a factor of approximately 1.5. The  $\lambda/4$  open-circuit stub is a short at 60 GHz to suppress the RF signal at the output.

Figure 17: Demodulator schematic.

Extraction of the baseband data is described as follows: The small-signal output current given by (2) is the input voltage to  $M_1$  multiplied by its small-signal transconductance,  $g_{m1}$ . Shown in (3) is the small-signal transconductance,  $g_m$ , for an above-threshold MOSFET, where  $K = \mu_n C_{ox} W/L$  is the large-signal transconductance.

$$i_{OUT} = g_{m1}v_1 \tag{2}$$

$$g_m = \begin{cases} K(V_{GS} - V_T) & (V_{DS} > V_{GS} - V_T) & (saturation) \\ K(V_{DS}) & (V_{DS} < V_{GS} - V_T) & (linear) \end{cases}$$

(3)

The  $g_m$  in the saturation region is dependent on the overdrive voltage,  $V_{DS-Sat} = V_{GS} - V_T$ , whereas in the linear region it is dependent upon the drain to source voltage,  $V_{DS}$ . Mixing action can be enabled in (2) if the drain voltage, and therefore the  $g_m$ , of  $M_1$  can be modulated via the source follower stage of  $M_2$ .

The AC waveforms at the gates of  $M_1$  and  $M_2$  are expressed by (4) and (5), respectively, where  $v_2$  is a 180° shifted version of  $v_1$  boosted by the series resonator and  $V_M$  is the magnitude of the OOK modulated signal that contains the baseband data.

$$v_1 = V_M sin(\omega t) \tag{4}$$

$$v_2 = -\beta V_M \sin(\omega t) \tag{5}$$

The use of direct-conversion multiplication is taken advantage of by applying 180° out of phase signals at the  $v_1$  and  $v_2$  ports. This allows for a larger swing at the drain of  $M_1$  from the constructively-interfering voltage outputs of the common-source  $M_1$ stage and the source-follower  $M_2$  stage. This effect is accounted for by the parameter  $\alpha$  and has been simulated to provide a signal swing at the drain of  $M_1$  nearly twice as large as the case where  $v_1$  and  $v_2$  are in phase. This effect has a direct increase on the conversion gain as will be shown in the following discussion. If the drain of  $M_1$  is biased at the edge of the linear/saturation region, i.e.  $V_{DS1} = V_{DS-Sat}$ , the periodically-varying  $g_{m1}(t)$  can be described as in (6) where f(t) is a half-waverectified sine wave described by the Fourier series in (7). This action is illustrated in Figure 18, where  $g_{m1-Sat} = KV_{DS-Sat}$ .

$$g_{m1} = K(V_{DS-Sat} - \alpha\beta V_M f(t)) \tag{6}$$

$$f(t) = \frac{1}{\pi} + \frac{\sin(\omega t)}{2} + \frac{2}{\pi} \sum_{n=1}^{\infty} \frac{\cos(2n\omega t)}{1 - 4n^2}$$

(7)

Figure 18: Small-signal transconductance,  $g_m$ , of  $M_1$  modulated by  $M_2$ .

To evaluate the baseband mixing product, only the  $sin(\omega t)/2$  term in f(t) needs to be considered since the high-frequency terms will be filtered by the low-pass nature of the circuit. Therefore, the small-signal output current is given by (8). Expanding and again removing the high-frequency terms yields the small-signal output current given by (9).

$$i_{OUT} = v_1 g_{m1}(t) \approx V_M sin(\omega t) \left( g_{m1-Sat} - \frac{K\alpha\beta V_M sin(\omega t)}{2} \right)$$

(8)

$$i_{OUT} \approx -\frac{K\alpha\beta V_M^2}{4} \tag{9}$$

The voltage conversion gain is defined as the baseband output voltage divided by the magnitude of the input voltage. Assuming the output resistance is approximately equal to  $R_L$ , this is given by (10).

$$A_V = -\frac{i_{OUT}R_L}{V_M} \tag{10}$$

Plugging (9) into (10) shows the voltage conversion gain is proportional to input voltage magnitude, as in (11).

$$A_V = V_M \left(\frac{K\alpha\beta R_L}{4}\right) \tag{11}$$

Therefore doubling the LNA gain will quadruple the conversion gain of the entire receiver. Shown in Figure 19 is the simulated detector conversion gain versus input power where the conversion gain at the receiver minimum sensitivity (plus the LNA gain) has been indicated.

Figure 19: Detector conversion gain versus input power for a 61-GHz carrier.

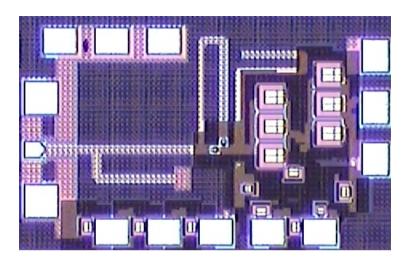

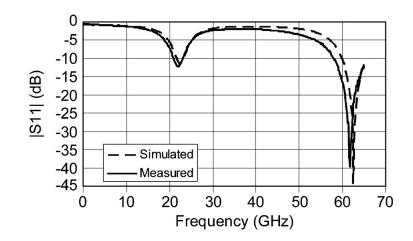

Figs. 20 and 21 show a fabricated detector test structure and its measured  $|S_{11}|$  performance, respectively. The measured results show a very good input matching around 60 GHz with greater than 10 GHz 10-dB input-matching bandwidth. The demodulator consumes 16 mW of DC power. The simulated 3-dB RF bandwidth is greater than 4 GHz.

Figure 20: Detector test structure die photograph.

Figure 21: Detector test structure measured versus simulated  $|S_{11}|$ .

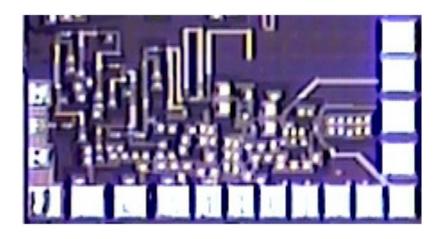

# 3.4 Integrated OOK Receiver Measured Results

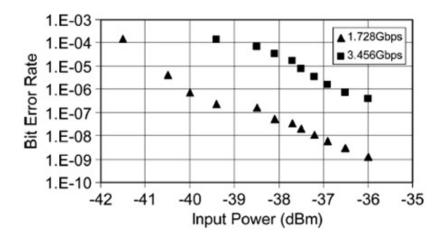

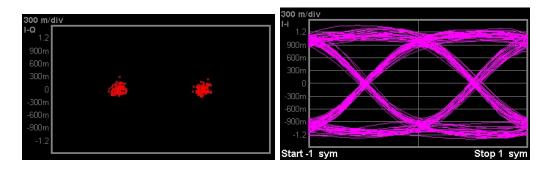

Figure 22 shows the 60-GHz OOK receiver die photograph. The receiver occupies a die area of 1.8 mm x 1 mm. An external 60-GHz OOK modulator with pseudo-random binary sequence (PRBS) input was used to perform bit error rate (BER) measurements on the receiver for swept-power inputs at multiple data rates. Figure 23 shows the BER versus received input power. Figure 24 shows measured eye-diagrams of the digital baseband output for 1.728-Gbps and 3.456-Gbps data. The receiver consumes 108 mW of DC power and exhibits a noise figure of 8.5 dB at -40 dBm input. The minimum sensitivity of the receiver for 1.728-Gbps data at a BER of less than  $10^{-6}$  is -40 dBm at the probing pad. Table 1 summarizes the measured performance along-side other reported 60-GHz OOK receivers.

Figure 22: 60-GHz OOK receiver die photograph.

Figure 23: Receiver bit error rate versus input power.

Figure 24: Measured eye diagrams for (a) 1.728-Gbps and (b) 3.456-Gbps data.

| Reference        | This Work, [41] | [42] | [43]       |

|------------------|-----------------|------|------------|

| DC Power (mW)    | 108             | 800  | 103        |

| Data Rate (Gbps) | 3.5             | >1   | 2.5        |

| pJ/Bit           | 31              | 800  | 41         |

| Modulation       | OOK             | ASK  | OOK        |

| NF (dB)          | 8.5             | -    | 7          |

| Process          | 90-nm CMOS      | GaAs | 90-nm CMOS |

Table 1: 60-GHz OOK receiver comparison.

## CHAPTER IV

# HIGH-POWER, HIGH-EFFICIENCY 45-GHZ OSCILLATORS FOR LOW-OVERHEAD LO DISTRIBUTION

Mobile devices such as smartphones or tablets have very stringent power consumption requirements. Therefore as additional functions are added it is critical that they place as little burden as possible on the existing power budget of a given device or system platform. Due to the high degree of loss and directionality of wireless propagation at millimeter-wave frequencies, multi-element beam-forming transceivers will be an attractive solution for point to point communications [27]. Phase-shifting in the local oscillator (LO) path as opposed to the signal path is advantageous from a linearity perspective. However, a compelling argument against phase-shifting in the LO path is the increased power consumption resulting from parallel signal conversion paths and LO distribution [44]-[46]. However, this problem can be mitigated with the integration of a high-power, high-efficiency voltage controlled oscillator (VCO) that can reduce or eliminate the need for buffer stages or redundant oscillator structures, which must be phase-locked to a central signal.

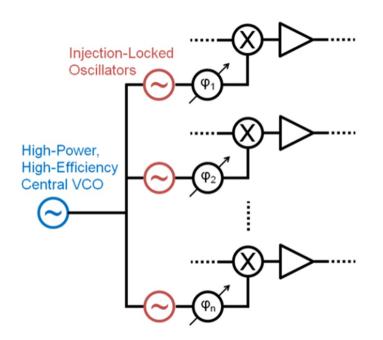

This work presents the design of a single-ended output VCO based on a class-E power amplifier (PA) core and a single-ended input/differential output injectionlocked oscillator (ILO) using a cross-coupled design in 45-nm SOI CMOS. These oscillators in conjunction with a passive distribution network can enable highly-efficient LO distribution for multi-element CMOS millimeter-wave transceivers such as MIMO or phased-array architectures. An example transmitter architecture utilizing the elements presented in this work is shown in Figure 25. For a specified central VCO output power,  $P_{VCO}$ , required input power to lock the injection-locked oscillator,  $P_{INJ}$ , and the insertion loss of each power division in the LO distribution path, IL, the number of transceiver elements this type of architecture could support is given by (12).

$$No.of elements = 2^{\frac{P_{VCO} - P_{INJ}}{3 + IL}}$$

(12)

Figure 25: Example system using high-efficiency LO distribution.

# 4.1 Power amplifier classes of operation

Power amplifiers can be broadly classified into two categories: linear and switch-mode. In the linear case, the active device produces an amplified version of the input signal with varying degrees of non-linear distortion depending on its conduction angle. The conduction angle is defined as the period of the input waveform during which the active device is conducting current, in degrees. In the switch-mode case, the active device is utilized as a switch that is driven open and closed by the input waveform in a manner that results in all DC power being transfered to RF power, achieving a theoretical efficiency of 100%. The penalty is completely non-linear behavior. Table 2 compares the basic classes of PA operation in terms of their conduction angle, linearity, and theoretical efficiency. Classes A through C are of the linear variety whereas classes D and above are switch-mode PAs. Although there are many more types of switch-mode amplifiers only the basic D, E, and F classes will be discussed in this work to explain the unique suitability of the class-E PA for millimeter-wave applications.

| Class   | Conduction Angle          | Linearity  | Theoretical Efficiency |

|---------|---------------------------|------------|------------------------|

| А       | 360°                      | Best       | 50%                    |

| AB      | $180^{\circ}-360^{\circ}$ | Good       | 50-78.5%               |

| В       | 180°                      | Moderate   | 78.5%                  |

| C       | < 180°                    | Poor       | 78.5 - 100%            |

| D, E, F | 0°                        | Non-Linear | 100%                   |

Table 2: Power amplifier classes of operation.

#### 4.1.1 Linear Power Amplifiers

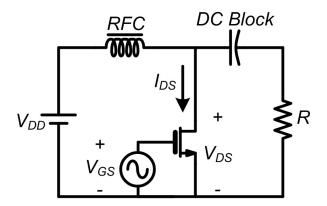

An example schematic of a linear power amplifier can be seen in Figure 26. It consists of an active device for amplification, an RF choke to the supply,  $V_{DD}$ , a DC blocking capacitor, and a resistive load.

Figure 26: Example linear PA schematic.

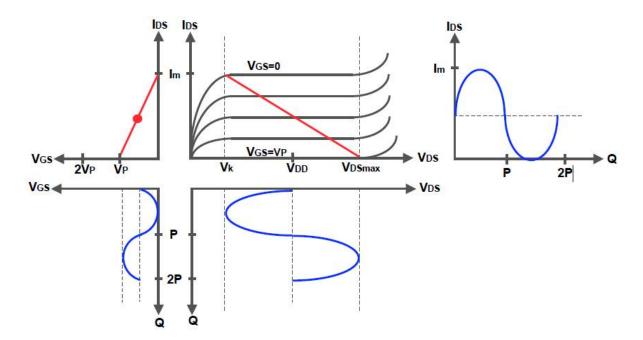

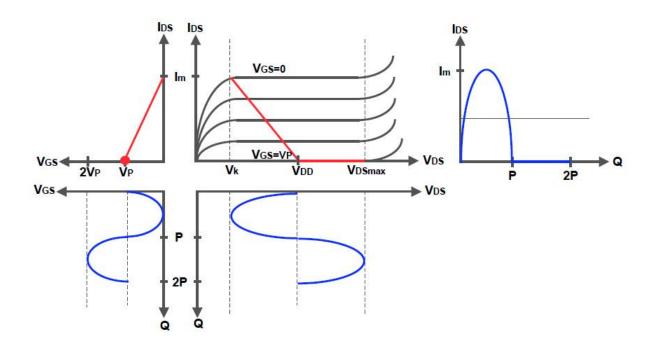

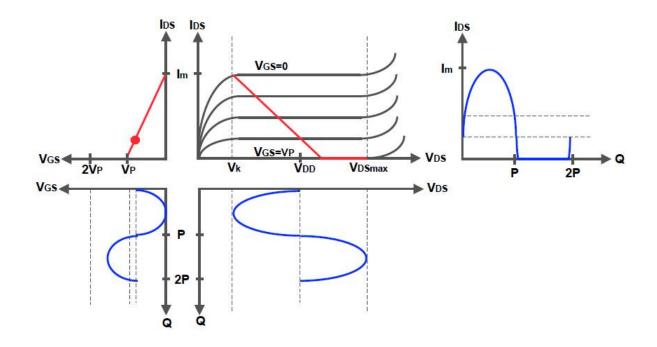

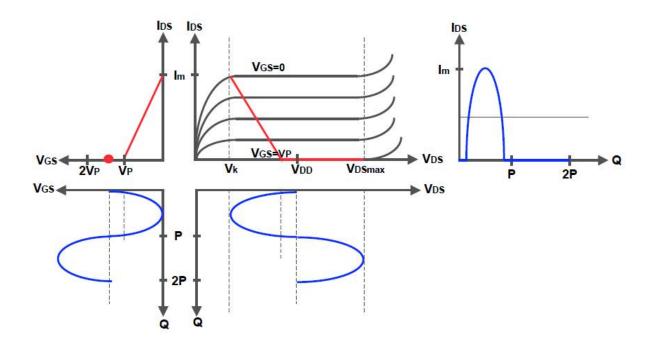

The class-A power amplifier has a 360° conduction angle and therefore exhibits the highest linearity and poorest efficiency of all the PA classes. As shown in Figure 27, the active device conducts the output current  $I_{DS}$  during 100%, or 360°, of the input votage waveform,  $V_{GS}$ , resulting in a perfectly amplified copy of the sinusoidal input at the output. The theoretical efficiency,  $\eta$ , can be calculated by (13). Assuming a sinusoidal signal and for the ideal case where the knee voltage  $V_K = 0$  and  $V_{DD} = V_{DSmax}/2$ , this reduces to 50%.

$$\eta = \frac{P_{RF}}{P_{DC}}$$

$$= \frac{V_{rms}I_{rms}}{V_{DC}I_{DC}}$$

$$= \frac{\frac{V_{DS}max - V_{K}}{2\sqrt{2}}\frac{I_{M}}{2\sqrt{2}}}{V_{DD}\frac{I_{M}}{2}}$$

(13)

Similar waveform plots for the class-B, class-AB, and class-C PAs can be seen in Figs. 28- 30. Class-B PAs exhibit a 180° conduction angle and a theoretical efficiency of 78.5%. Class-AB PAs do not have as strict a definition and represent a popular tradeoff between linearity and efficiency whose operation lies somwhere between class A and class B, the exact value of which can be optimized for a specific application. Class C PAs have a conduction angle  $< 180^{\circ}$  resulting in a highly-distorted output but high efficiency. Although the class-C PA allows for a 0° conduction angle in its extreme case, it is classified among the linear PAs due to its use of a linear active device for amplification. A more detailed and comprehensive discussion of linear power amplifiers can be found in [47].

Figure 27: Class-A power amplifier waveforms.

Figure 28: Class-B power amplifier waveforms.

Figure 29: Class-AB power amplifier waveforms.

Figure 30: Class-C Power Amplifier Waveforms.

#### 4.1.2 Switch-mode Power Amplifiers

4.1.2.1 Class-D Power Amplifier

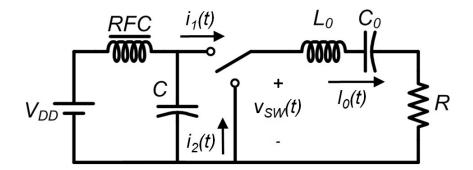

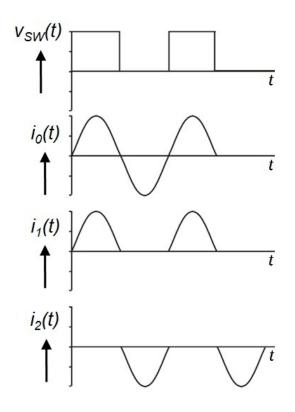

The circuit schematic of the ideal class-D PA can be seen in Figure 31. It consists of a series resonant circuit formed by  $L_0$  and  $C_0$  connected to a single-pole double-throw switch. The series resonator is designed to force a sinusoidal current to flow through it and to the load R at the desired frequency. Figure 32 shows the voltage and current waveforms that constitute class-D operation.

The ideal switch is driven by a square wave at the desired frequency. While the switch is connected to the capacitor C, it is discharged by the current  $i_1(t)$  that flows to the load resistor R contributing the positive-half sine wave at the output. When the switch is connected to ground, the capacitor C is charged from the  $V_{DD}$  through an RF choke. At the same time, the current  $i_2(t)$  flows through the resonator in the opposite direction of  $i_1(t)$  thus contributing the negative-half sine wave at the output. The summation of these two currents forms  $i_0(t)$  at the output. Since there is no V-I

overlap in the switch waveforms, no DC power is consumed. Therefore all DC power is delivered to the output resulting in 100% efficiency.

This analysis is that of an ideal amplifier and therefore makes a number of assumptions about the circuit elements and their behavior. First, all elements are assumed to have infinite Q, such that no power is dissipated in the reactive components. Second, the existence of a perfect switch is assumed. In the practical case, a series/shunt configuration of transistors can be used to implement the switch. These transistors will have parasitic resistances and capacitances that will dissipate power and result in finite opening and closing times for the switch. At low frequencies, these parasitic elements will be easier to model or may even be negligible from an initial design standpoint. However, at millimeter-wave these non-idealities may play a dominant role in determining the waveforms of the circuit. In CMOS technology, two transistors will be needed to implement the single-pole double-throw switch, one in a common-source configuration and the other in a common-gate configuration. The common-gate transistor, which conducts the  $i_1(t)$  path current, will be particularly difficult to model using empirical data. Because of the design and modeling complexity resulting from the need for two transistors the class-D PA is not chosen for millimeter-wave applications.

Figure 31: Class-D power amplifier schematic.

Figure 32: Class-D power amplifier waveforms.

## 4.1.2.2 Class-F Power Amplifier

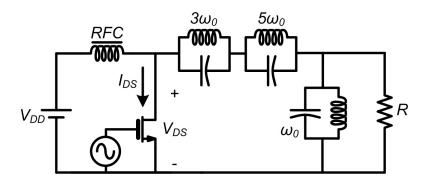

If a rigorous definition is applied, the class-F PA might not truly be considered a switch-mode amplifier as its "switching device" is more likely biased like a class-B PA. However, harmonic control at the device output using parallel resonant circuits, as seen in Figure 33, causes the voltage waveform at the device drain to behave as if it were switched completely on and off. The voltage and current waveforms,  $V_{Drain}(t)$ and  $I_{Drain}(t)$ , respectively, are shown in Figure 34. Looking out of the device drain, the odd harmonics of the fundamental signal see an open-circuit as a result of the parallel resonators in the signal path. The ideal case includes an infinite number of odd-harmonic resonators. This forces a square wave in  $V_{Drain}(t)$  and a half-rectified sinusoid in  $I_{Drain}(t)$ . Therefore, no V-I overlap occurs at the device drain resulting in 100% efficiency. Clearly, the fundamental practical limitation of the class-F amplifier is that an infinite number of parallel harmonic circuits cannot be included. The design choice then becomes how many harmonic circuits to include at the expense of circuit area and cost. Because of the large number of resonators required for harmonic control in the class-F and the unavailability of measurement equipment to verify suppression of harmonics of a millimeter-wave amplifier, the class-F structure is not chosen.

Figure 33: Class-F power amplifier schematic.

Figure 34: Class-F power amplifier waveforms.

#### 4.1.2.3 Class-E Power Amplifier

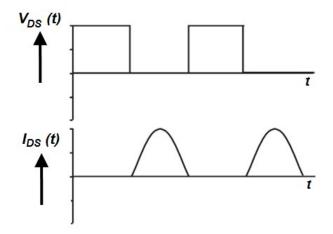

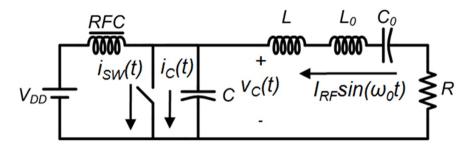

Class-E PA operation was first described by Sokal and Sokal in [48] and optimal design equations were first presented by Raab in [49]. Raab also analyzed sub-optimum operation in [50]. The parallel-circuit class-E PA was introduced by Grebennikov and Jaeger in [51]. An examination of the loss mechanisms in parallel-circuit class-E PAs was later given by Lee et al. in [52]. The ideal Class-E power amplifier, as seen in Figure 35, consists of an ideal switch shunted by a capacitor C, a series resonant circuit formed by  $L_0$  and  $C_0$ , the load resistance R, and an RF choke to  $V_{DD}$ . The effects of series inductor L can be separated mathematically from the series resonant circuit when designing, but L and  $L_0$  are typically lumped together in one device. When a MOSFET is used as the switching device, its drain capacitance can be included in the shunt capacitor C and is no longer considered strictly "parasitic" to the circuit performance. At RF and millimeter-wave frequencies the drain capacitance will likely form the majority if not all of the shunt capacitance. It is for this reason that the class-E PA is chosen as a suitable structure for millimeter-wave operation, as will be discussed further in section 4.2.1.

Figure 35: Class-E power amplifier schematic.

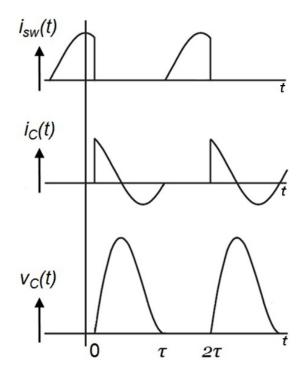

100% theoretical efficiency is achieved by implementing non-overlapping current and voltage waveforms in the switch. The series resonator  $L_0 - C_0$  forces a sinusoidal current at the design frequency,  $\omega_0$ . Given a specified load resistance R, the reactive components L and C can be chosen to produce waveforms like those shown in Figure 36 such that the currents flowing into the switch and the capacitor during the switch closed and switch open periods, respectively, sum to form the sinusoidal current delivered to the load.

Figure 36: Class-E power amplifier waveforms.

The boundary conditions for the ideal switching condition are given by (14) and (15). At the time,  $t=\tau$ , when the switch closes, the capacitor voltage and the first time derivative of the capacitor voltage must equal zero. Otherwise the resultant discharging of the capacitor through the closed switch would violate ideal class-E behavior and degrade efficiency. The parallel-class class-E amplifier has essentially the same functionality as the basic class-E amplifier. However, the RF choke at the VDD connection is replaced by a finite-valued inductor and explicitly accounted for in the design equations [11].

$$v_c(t)|_{t=\tau} = 0 \tag{14}$$

$$v_c(t)|_{t=\tau} = 0 \tag{15}$$

The ideal class-E (or parallel class-E) power amplifier can achieve an efficiency of 100%. This, of course, can never be realized in practice. However, the practical efficiency can be maximized through careful examination of major departures from ideal behavior that must happen in any real implementation, as will be discussed in section 4.2.1. Recent examples of class-E operation applied to oscillating structures in CMOS at RF frequencies can be seen in [53]-[55].

# 4.2 High-Efficiency, High-Power Millimeter-wave Class-E VCO

An essential piece of implementing a power efficient millimeter-wave phased array or LINC transmitter is low-overhead LO distribution. Integration of a high-power, highefficiency oscillator can reduce or eliminate the need for buffer stages or redundant oscillator structures which must be injection locked to a central signal. This work utilizes the class-E PA topology to enable high-efficiency millimeter-wave oscillators for integration in such systems.

#### 4.2.1 Millimeter-wave Class-E PA Core

In any real design, the class-E power amplifier can never achieve its theoretical 100% efficiency. However, the practical efficiency can be maximized through careful examination of major departures from ideal behavior that must happen in any real implementation.

The fundamental assumption for ideal class-E operation is the existence of a switch that can be opened or closed with zero rise/fall time and that dissipates no power. When using a transistor as a switch there will be an associated ON-resistance,  $r_{ds}$  for a MOSFET, which will dissipate power during the switch closed state thus degrading efficiency. A simple approximation for the associated power loss is given by (16), where  $P_{r_{ds}}$  and  $P_{DC}$  are the power dissipated by the switching transistor ON-resistance and the DC power, respectively [52].

$$\frac{P_{r_{ds}}}{P_{DC}} \approx 3.138 \frac{r_{ds}}{R} \tag{16}$$

When designing at high frequencies, the parasitic drain capacitance  $C_{drain}$  of the switching transistor itself will often be used as the shunt capacitor. Based upon  $C_{drain}$ , the maximum operating frequency  $f_{max}$  (not to be confused with the  $f_{max}$  figure of merit for a transistor) can be defined for a parallel-circuit class-E PA by (17) [51].

$$f_{max} = 0.0798 \frac{P_{out}}{C_{drain} V_{dd}^2} \tag{17}$$

If  $C_{drain}$  for the chosen transistor size is larger than the ideal class-E parallel capacitance,  $f_{max}$  will be pushed below the operating frequency  $f_0$ . This will result in an efficiency degradation caused by the inability of  $C_{drain}$  to be discharged completely before the device is switched on, causing an undesired current flow that violates ideal class-E behavior.

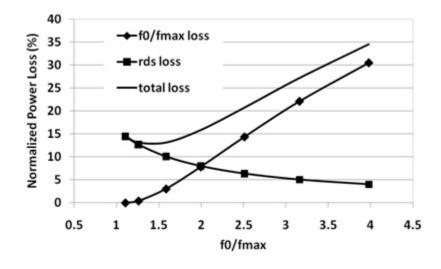

The efficiency degradations due to non-zero  $r_{ds}$  and  $f_0/f_{max} > 1.1$  present a tradeoff when selecting the size of the switching transistor. Using a larger device, for example, will have lower ON-resistance loss, but its increased drain capacitance may push the  $f_{max}$  below the operation frequency resulting in a diminishing return on efficiency improvement. Based upon the  $f_0/f_{max}$  efficiency degradation detailed in [50] and the  $r_{ds}$  degradation described by (16) an optimum  $f_0/f_{max}$  ratio of 1.4 was chosen resulting in a device size of 120  $\mu$ m. This tradeoff is depicted graphically in Figure 37. Other sources of loss include the matching network, typically required to transform the 50- $\Omega$  system impedance to a lower impedance for the PA to drive, and the low-Q DC feed inductance at the device drain.

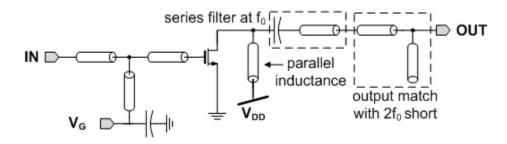

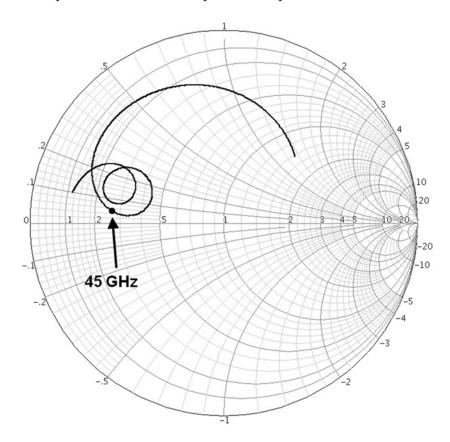

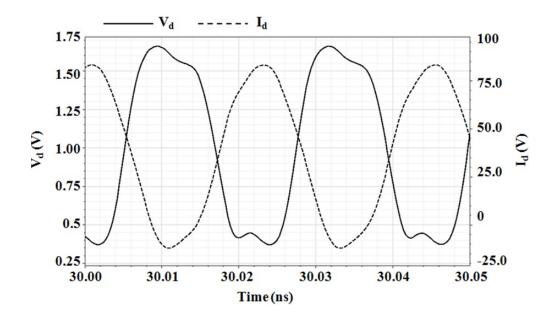

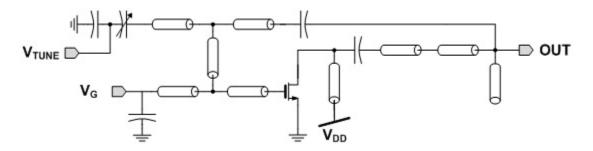

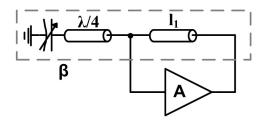

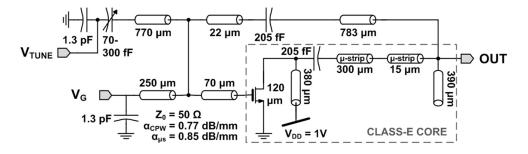

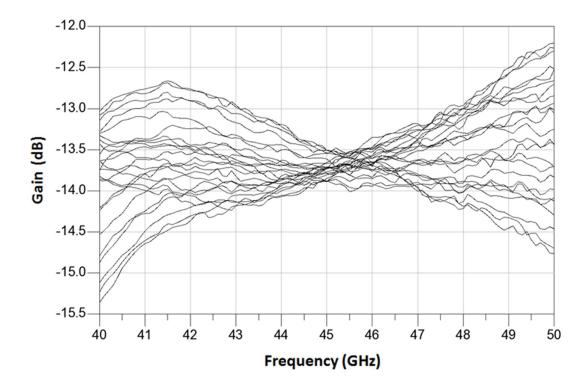

Figure 37: Optimizing the  $f_0/f_{max}$  ratio.