# CIRCUIT AND ALGORITHM DESIGN TO ENABLE EDGE INTELLIGENCE

A Dissertation Presented to The Academic Faculty

By

Ningyuan Cao

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

Georgia Institute of Technology

August 2020

Copyright © Ningyuan Cao 2020

# CIRCUIT AND ALGORITHM DESIGN TO ENABLE EDGE INTELLIGENCE

Approved by:

Dr. Arijit Raychowdhury, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Sung-kyu Lim School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Madhavan Swaminathan School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Muhannad S Bakir School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Shreyas Sen School of Electrical and COmputer Engineering *Purdue University*

Date Approved: June 27, 2020

Unless he is indifferent to fame and fortune, he cannot have aspirations; unless he stays calm and quiet, he cannot reach afar. *Zhuge Liang, a Chinese politician during Three Kingdom period*  For the young man may who stays curious and passionate along the journey.

#### ACKNOWLEDGEMENTS

I would like to thank the members of my thesis committee for their help in preparation of this work – Dr. Sung-kyu Lim, Dr. Madhavan Swaminathan, Dr. Shreyas Sen and Dr. Muhannad S Bakir. And beyond this work, the committee members have also been so kind to support me in my academic faculty job search and award applications. Without their help, I can not go this far both as a Ph.D. candidate as well as a young man pursuing academic opportunities.

I would like to also thank my colleagues from ICSRL, especially early members: Saad, Samantak, Ahbinav, Anvesha, Insik and Muya. The discussions with them from chip tapeout to research selections are important to the successs of my research endeavors. And the enjoyable morning coffee hours with my colleagues have become the most precious memory.

Special thanks to my advisor Dr. Arijit Raychowdhury. As an understanding and knowledgeable advisor, he has never given me any hard times but instead uses his insights to motivate me and help me reach my goals. As a kind friend, he selflessly shares his stories and gives suggestions, especially in this hard time that every graduates are struggling with the worldwide pandemics.

The author gratefully acknowledges the support for this work offered by Semiconductor Research Corporation. Any views and conclusions contained herein are those of the author, and do not necessarily represent the official positions, express or implied, of the funders.

Finally, I would like to thank my parents for giving me life and I enjoy it so far very much. I would also like to thank my wife Sabrina for bringing beautiful love into life.

# TABLE OF CONTENTS

| Acknow    | vledgments                                                        | v  |

|-----------|-------------------------------------------------------------------|----|

| List of 1 | Figures                                                           | xi |

| Chapte    | r 1: Introduction                                                 | 1  |

| 1.1       | Edge Intelligence                                                 | 2  |

| 1.2       | EI Design Landscape, FoM and Design Methodology                   | 5  |

|           | 1.2.1 EI Design Examples                                          | 5  |

|           | 1.2.2 EI Design Landscape and FoM                                 | 6  |

|           | 1.2.3 Conventional IoT Design Methodology                         | 7  |

|           | 1.2.4 Proposed EI Design Methodology                              | 9  |

| 1.3       | Literature Survey                                                 | 10 |

| 1.4       | Dissertation Overview                                             | 14 |

| Chapte    | r 2: EI for Data-fusion-based Occupancy Detection in HVAC Control | 15 |

| 2.1       | Introduction                                                      | 15 |

| 2.2       | Platform description                                              | 16 |

| 2.3       | Occupancy detection via Collaborative Intelligence                | 18 |

|           | 2.3.1 Overview                                                    | 19 |

|           | 2.3.2 Fusion-based detection                                      | 24 |

|        | 2.3.3 OP/IR hard detection and sensor lifetime                                                   | 26 |

|--------|--------------------------------------------------------------------------------------------------|----|

| 2.4    | Smart sensor network                                                                             | 27 |

|        | 2.4.1 Intelligent LoRa front-end                                                                 | 28 |

|        | 2.4.2 Collaborative dynamic network control                                                      | 31 |

| 2.5    | System measurements                                                                              | 33 |

| 2.6    | Conclusion                                                                                       | 38 |

|        |                                                                                                  |    |

| Chapte | r 3: Computation-Communication Trade-off in EI Sensor Nodes for Wire-<br>less Video Surveillance | 39 |

| 3.1    | Introduction                                                                                     | 39 |

| 3.2    | Prototype Hardware Platform                                                                      | 43 |

| 3.3    | Embedded Computation                                                                             | 45 |

|        | 3.3.1 Objection Localization and Segmentation:                                                   | 46 |

|        | 3.3.2 Compression                                                                                | 49 |

|        | 3.3.3 Feature Extraction                                                                         | 49 |

|        | 3.3.4 Classification                                                                             | 50 |

|        | 3.3.5 Comparative Analysis of Classification Schemes                                             | 52 |

| 3.4    | Adaptive Wireless Communication                                                                  | 53 |

| 3.5    | Self-optimization Procedure and System Setup                                                     | 56 |

|        | 3.5.1 Energy Model                                                                               | 56 |

|        | 3.5.2 Self-optimization Procedure                                                                | 59 |

| 3.6    | End-to-end System Demonstration and Measurements                                                 | 61 |

| 3.7    | Conclusion                                                                                       | 66 |

| 3.8    | Discussions                                                                                      | 66 |

|        | 3.8.1    | System Inefficiency                                                     | 66 |

|--------|----------|-------------------------------------------------------------------------|----|

|        | 3.8.2    | Control Overhead                                                        | 67 |

|        | 3.8.3    | DNN Computation Architecture                                            | 67 |

| Chapte | r 4: A V | Wireless Image Processing SoC Enabling EI                               | 69 |

| 4.1    | Introd   | uction                                                                  | 69 |

| 4.2    | System   | n Analysis                                                              | 70 |

|        | 4.2.1    | DNN Image Processing Pipeline                                           | 71 |

|        | 4.2.2    | Adaptive Communication                                                  | 73 |

|        | 4.2.3    | Optimal Control                                                         | 74 |

| 4.3    | System   | n Architecture                                                          | 76 |

| 4.4    | Circui   | t Design                                                                | 78 |

|        | 4.4.1    | Reconfigurable PE Spatial Array                                         | 78 |

|        | 4.4.2    | Reconfigurable RF-DAC Tx and ULP OOK Rx                                 | 81 |

|        | 4.4.3    | NN-based Actor-Critic Controller                                        | 84 |

| 4.5    | Measu    | rements                                                                 | 87 |

| 4.6    | Conclu   | usions                                                                  | 92 |

| 4.7    | Discus   | ssions                                                                  | 93 |

|        | 4.7.1    | On-chip System                                                          | 93 |

|        | 4.7.2    | Sequential BL Operation Non-linearity                                   | 95 |

|        | 4.7.3    | Thermometer-based Encoding                                              | 96 |

| Chapte |          | stributed EI: A Unified Computational ASIC for Swarm Robotic plications | 97 |

| 5.1     | Introduction                                                                                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2     | An Overview of Swarm Algorithms                                                                                                                                             |

|         | 5.2.1 Algorithms Based on Physical Models                                                                                                                                   |

|         | 5.2.2 Learning-Based Algorithms                                                                                                                                             |

| 5.3     | A Common Computing Platform                                                                                                                                                 |

| 5.4     | Scalability with Swarm Size                                                                                                                                                 |

| 5.5     | Hybrid Digital-Mixed-Signal Computing                                                                                                                                       |

|         | 5.5.1 Time-Domain Multiplication and Accumulation                                                                                                                           |

|         | 5.5.2 Hybrid-Digital-Mixed-Signal Computing Platform                                                                                                                        |

| 5.6     | System Overview                                                                                                                                                             |

| 5.7     | Measurements                                                                                                                                                                |

| 5.8     | Outlook                                                                                                                                                                     |

| 5.9     | Conclusions                                                                                                                                                                 |

| 5.10    | Discussions                                                                                                                                                                 |

|         | 5.10.1 Charge-domain vs. Time-domain $\ldots \ldots \ldots$ |

|         | 5.10.2 Memory Static Power Issues in Time-domain ASIC                                                                                                                       |

| Chapter | <b>: 6: Conclusions</b>                                                                                                                                                     |

| 6.1     | EI Expands the IoT Solution Space                                                                                                                                           |

| 6.2     | EI is More Than 'Edge Computation'                                                                                                                                          |

| 6.3     | Integrated Circuits to Enable EI                                                                                                                                            |

| 6.4     | Future EI Research Directions                                                                                                                                               |

| Referen | <b>ces</b>                                                                                                                                                                  |

| Vita | •• | • • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 14 | 19 | ) |

|------|----|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|----|---|

|------|----|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|----|---|

# LIST OF FIGURES

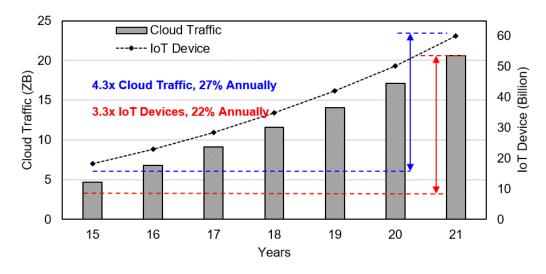

| 1.1 | Cloud traffic and IoT device analysis [1, 2]                                                                                                                                                                                                              | 1  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

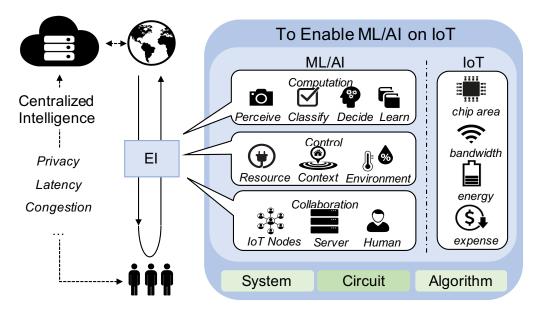

| 1.2 | Edge intelligence overview.                                                                                                                                                                                                                               | 2  |

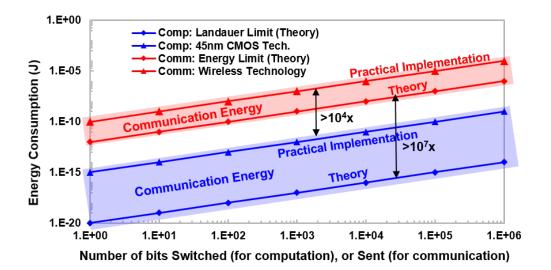

| 1.3 | Computation vs. communication energy analysis [3]                                                                                                                                                                                                         | 3  |

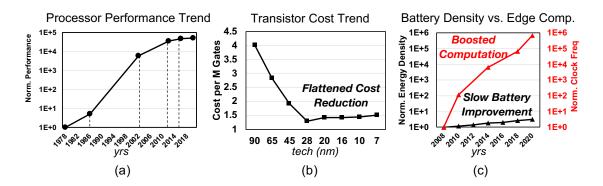

| 1.4 | (a) processor performance scaling [4], (b) transistor cost scaling [5] and (c) battery density improvement [6] vs. edge computation required clock frequency in order to process in real time [7]                                                         | 4  |

| 1.5 | Example EI works.                                                                                                                                                                                                                                         | 6  |

| 1.6 | EI design landscape and figure-of-merit.                                                                                                                                                                                                                  | 7  |

| 1.7 | Conventional IoT design methodology.                                                                                                                                                                                                                      | 8  |

| 1.8 | Proposed EI design methodology.                                                                                                                                                                                                                           | 9  |

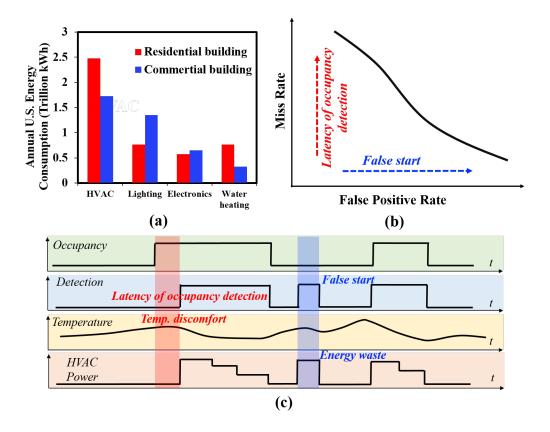

| 2.1 | (a) Residential and commercial energy use [52]; (b) Qualitative assessment<br>of the trade-off between miss rate and false positive rate; (c) The impact of<br>miss/false positive on latency of occupancy detection/energy waste respec-<br>tively.      | 17 |

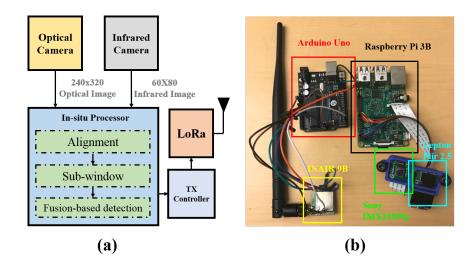

| 2.2 | (a) System architecture of the platform prototype; (b) Hardware setup                                                                                                                                                                                     | 18 |

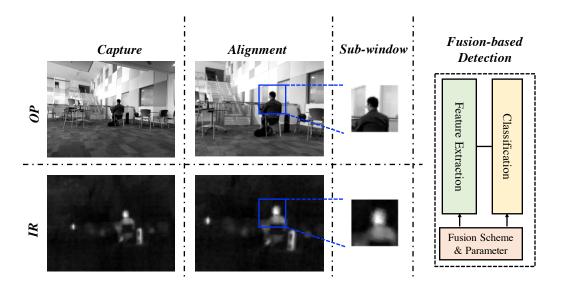

| 2.3 | Demonstration of the algorithm.                                                                                                                                                                                                                           | 18 |

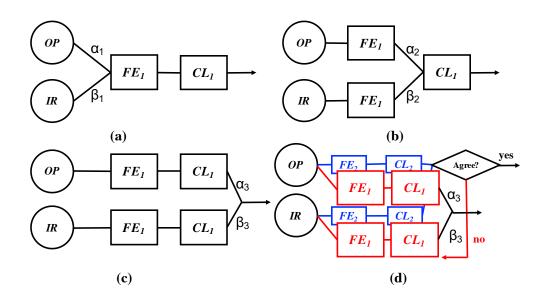

| 2.4 | (a) Data-level fusion; (b) Feature-level fusion; (c) Decision-level fusion;<br>and (d) The proposed collaborative, hierarchical and adaptive template (CHAT)<br>algorithm. Here FE and CL denote feature extraction and classification re-<br>spectively. | 22 |

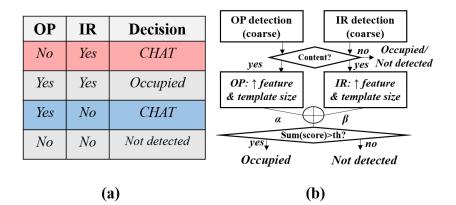

| 2.5 | (a) OP/IR decision table for CHAT; (b) Flow chart of CHAT                                                                                                                                                                                                 | 23 |

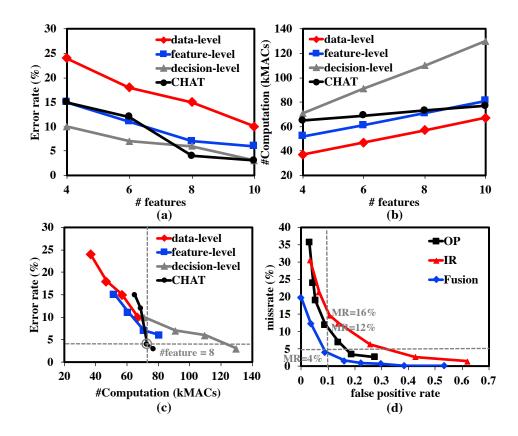

| 2.6  | (a) Error rate vs. number of feature bins; (b) Computation load vs. number of feature bins; (c) Error rate vs. computation cost for different fusion scheme; (d) ROC of OP, IR and "OP+IR" fusion-based detection                         | 23       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

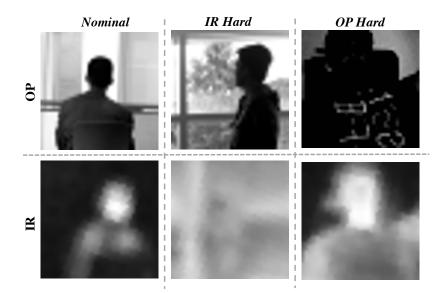

| 2.7  | Prototypical example of nominal, IR hard and OP hard data sets                                                                                                                                                                            | 24       |

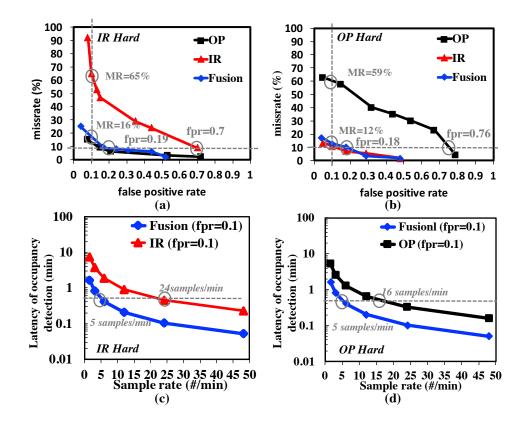

| 2.8  | Measured (a) ROC in IR hard scenario; (b) ROC for OP hard scenario; (c) latency of occupancy detection vs. sample rate in IR hard scenario; (d) latency of occupancy detection vs. sample rate in OP hard scenario                        | 25       |

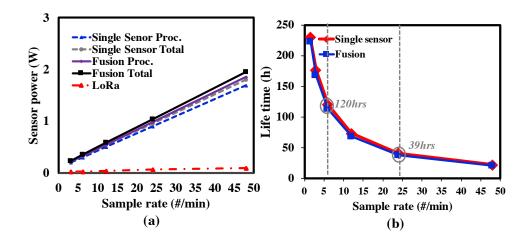

| 2.9  | Measured (a) sensor power consumption vs. sample rate, including pro-<br>cessing power, LoRa and total power; (b) sensor life-time vs. sample rate<br>for single and fusion-based sensor                                                  | 26       |

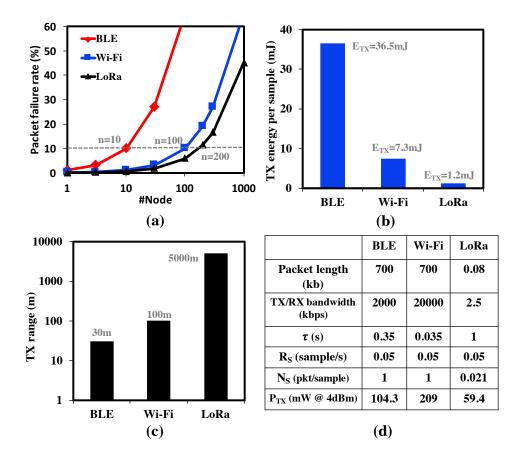

| 2.10 | Estimated (a) packet failure rate vs. number of node in a wireless network for BLE, Wi-Fi and LoRa respectively; (b) transmission energy consumption per sample; (c) transmission range; (d) parameter table                              | 29       |

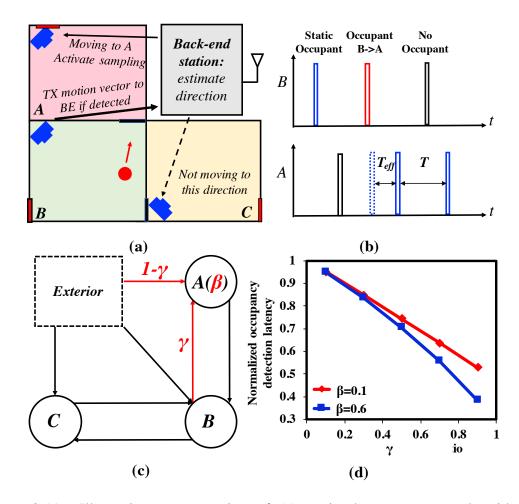

| 2.11 | Illustrative representation of (a) a simple sensor network with inter-dependency (b) demonstration of event-driven sampling; (c) network topology; (d) estimated latency of occupancy detection reduced within the collaborative network. | ;<br>30  |

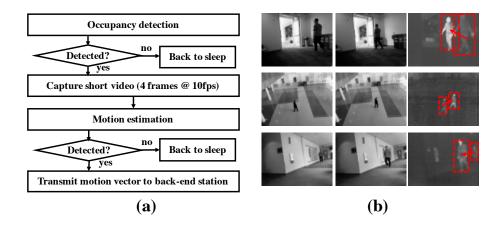

| 2.12 | (a) Flow chart of occupancy/motion detection and sampling rate; (b) Demonstration of a Case Study.                                                                                                                                        | 31       |

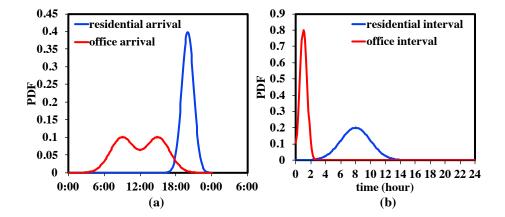

| 2.13 | (a) PDF of arrival time; (b) PDF of time interval between an individual entering and leaving a region                                                                                                                                     | 33       |

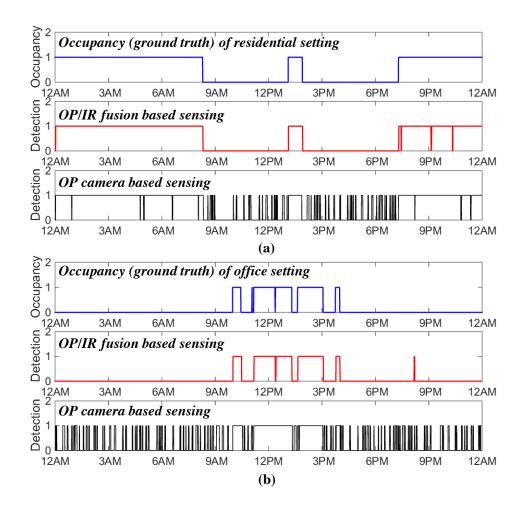

| 2.14 | Simulated system performance showing occupancy (ground truth), fusion based detection and single sensor based detection in (a) a residential and in (b) an office setting.                                                                | 34       |

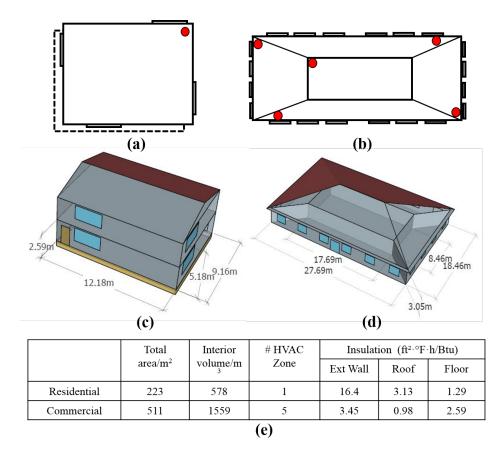

| 2.15 | HVAC zone floor plan and sensor placement for (a) residential building (b) and commercial building; corresponding 3D model and dimension in (c) and (d); table in (e) lists all the model parameters.                                     | 35       |

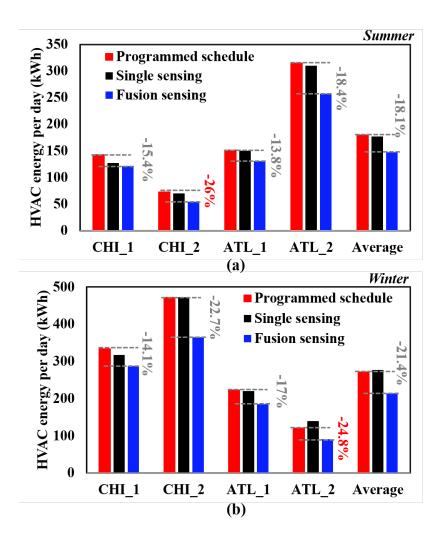

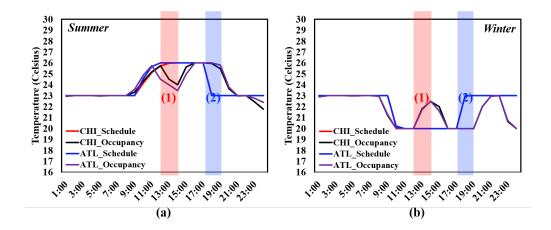

| 2.16 | HVAC energy consumption per day in (a) summer and (b) winter. "CHI"/"ATL <sup>2</sup> stands for Chicago/Atlanta and "_1"/"_2" stand for residential/office                                                                               | .,<br>36 |

| 2.17 | HVAC region temperature change in (a) summer and (b) winter                                                                                                                                                                               | 37       |

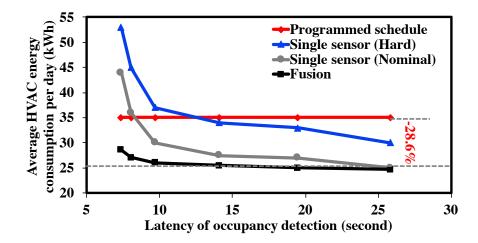

| 2.18 | HVAC energy vs. latency of occupancy detection.                                                                                                                                                                                           | 37       |

| 2.19 | Comparison with existing literature and competing technologies                                                                                                                                                                            | 38       |

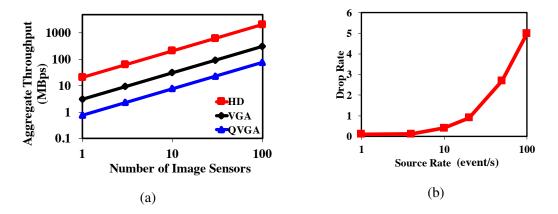

| 3.1 | (a) Aggregate throughput increases with number of sensor node in the net-<br>work and the data volume the sensor acquired. (b) Drop rate of the network<br>increased significantly with source rate [64]                                                                                                                                                                                                                                                                                    | 40 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

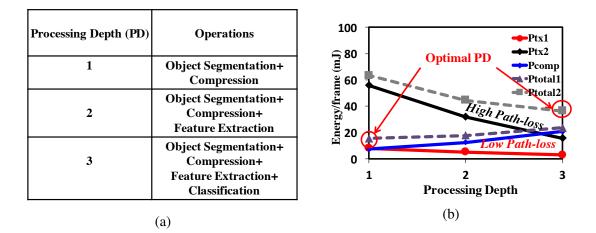

| 3.2 | (a) Pipelined operations at different processing depth (PD), including tem-<br>poral difference of consecutive frames (TD), compression (CR), feature ex-<br>traction (FE) and classification (CL). (b) Power consumption changes with<br>PD and the optimal PD for minimum-power consumption also varies under<br>different channel conditions. For example, a noisy channel results in more<br>embedded processing.                                                                       | 41 |

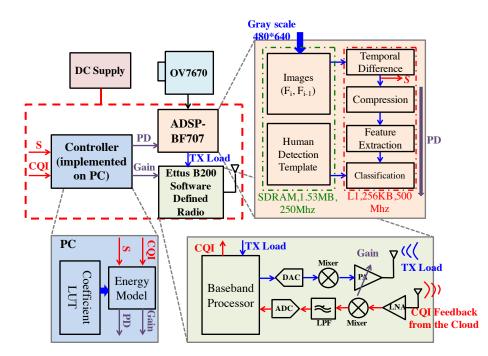

| 3.3 | End-to-end system architecture showing the different hardware components, the data processing pipeline and the software defined transceiver. CQI is the channel quality index quantified by path-loss and S is the information content size which will be defined in Section 3.3.                                                                                                                                                                                                           | 44 |

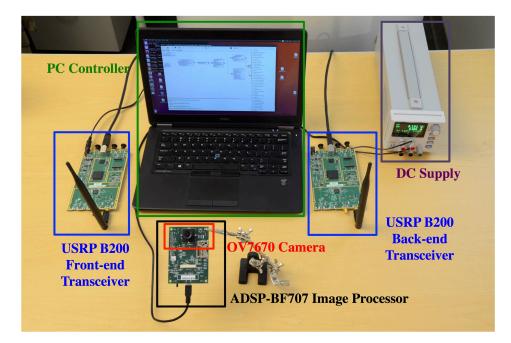

| 3.4 | Experimental setup showing the system components                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45 |

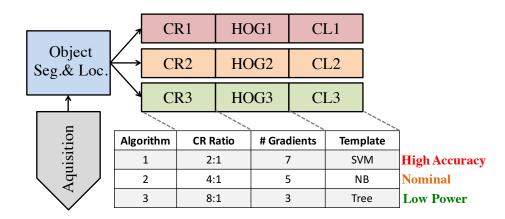

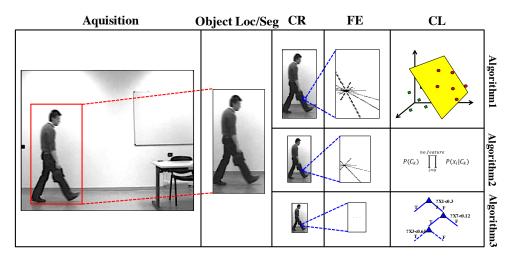

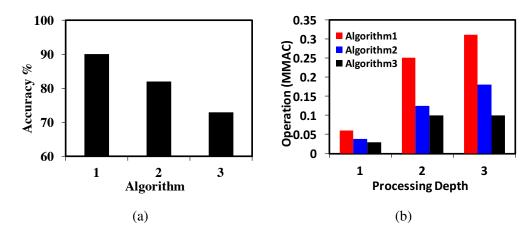

| 3.5 | Embedded human detection computation and design points of different algorithms/operations.Algorithm-1 (highest accuracy) applies CR ratio of 2:1, 7 feature gradients and SVM classification template; Algorithm-2 (nom-<br>inal) compresses input frame 4 times, extracts 5 gradients per feature and applies NB human detection template; Algorithm-3 (most energy-efficient) heavily compresses input frame 8 times, extracts 3 feature gradients and classifies with the tree template. | 46 |

| 3.6 | Algorithm demonstration with a real video frame                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47 |

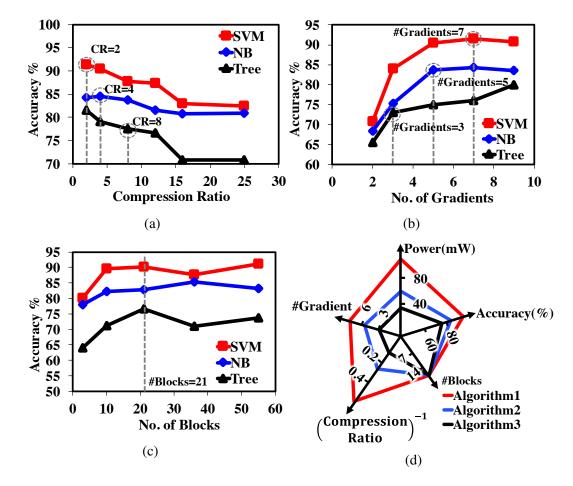

| 3.7 | (a) Measured detection accuracy vs. compression ratio. (b) Measured de-<br>tection accuracy vs. number of gradients extracted from HOG feature ex-<br>traction. (c) Measured detection accuracy vs. number of blocks to extract<br>feature vectors in HOG feature extraction. (d) Power consumption and ac-<br>curacy at design points in different algorithms                                                                                                                              | 48 |

| 3.8 | (a) Measured human detection accuracy with three different algorithms. (b)<br>Number of estimated operations in millions of multiplication-accumulation-<br>counts (MMAC) for different algorithms/depths                                                                                                                                                                                                                                                                                   | 49 |

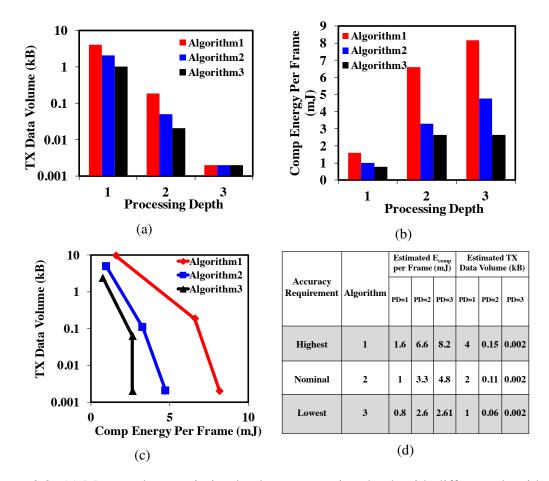

| 3.9 | (a) Measured transmission load vs. processing depth with different al-<br>gorithms and PD. (b) Measured front-end computation energy per frame<br>vs. processing depth. (c) Estimated Tradeoff between transmission data<br>volume with computation energy (d) different detection accuracy require-<br>ments result in different algorithm chosen, computation energy (Ecomp)<br>and transmission data volume                                                                              | 51 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

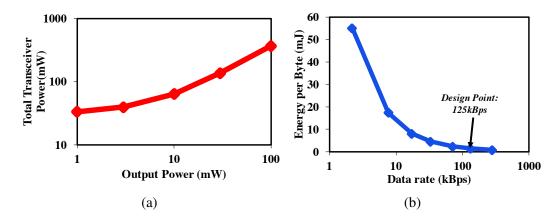

| 3.10 | Measured (a) transceiver power vs. output power. (b) energy per byte vs. data rate                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 52 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

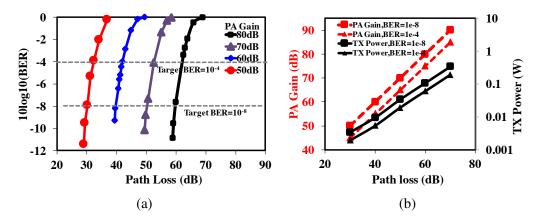

| 3.11 | Measured (a) Bit-error-rate vs. path-loss under different PA gain. (b) PA gain and transceiver power vs. path loss under BER requirement of $10^{-4}$ and $10^{-8}$ .                                                                                                                                                                                                                                                                                                                                                                      | 53 |

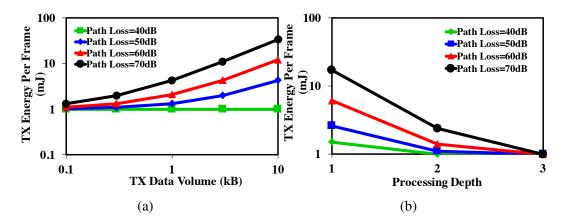

| 3.12 | Measured (a) transmission energy per frame vs. transmission data volume<br>under various channel conditions. (b) Transmission energy per frame vs.<br>processing depth under different path-loss conditions                                                                                                                                                                                                                                                                                                                                | 54 |

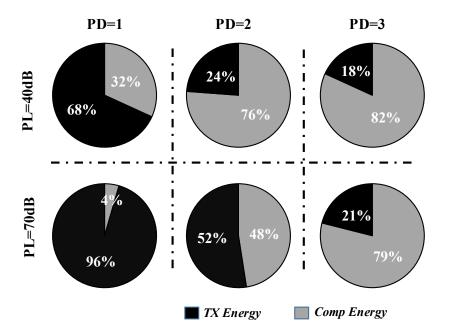

| 3.13 | Breakdown of computation energy and TX energy in different processing depth and path-loss                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55 |

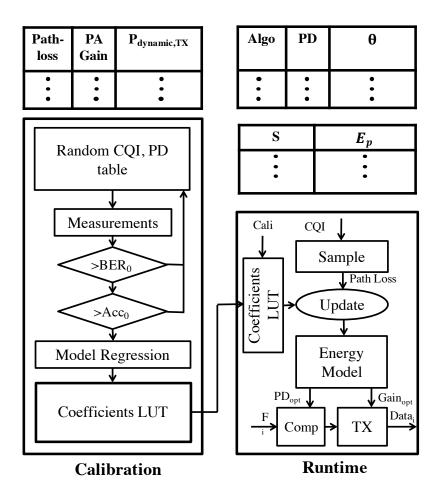

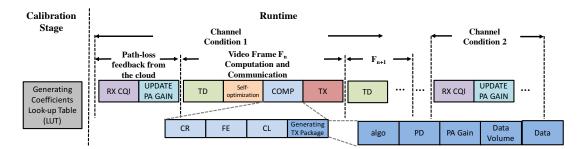

| 3.14 | Calibration and runtime self-optimization scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57 |

| 3.15 | Data packet configuration and modes of transmission-reception for the wire-<br>less link                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 58 |

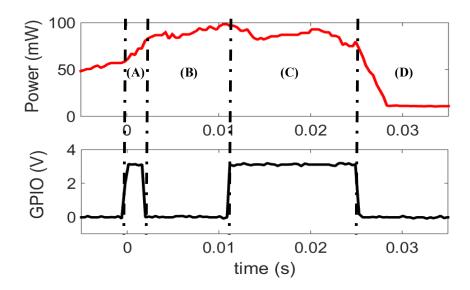

| 3.16 | Measured embedded computation power consumption where transient con-<br>grol signal of each processing stage is indicated by GPIO output voltage<br>level: (A), object segmentation and localization through temporal differ-<br>ence (TD) together with compression (CR); (B), feature extraction(FE);<br>(C), classification (CL) and finally (D), idle power down state. Note that<br>alternative opertions have alternative active-high and active-low control sig-<br>nals. For example, (A) is active-high, (B) active-low and so on | 59 |

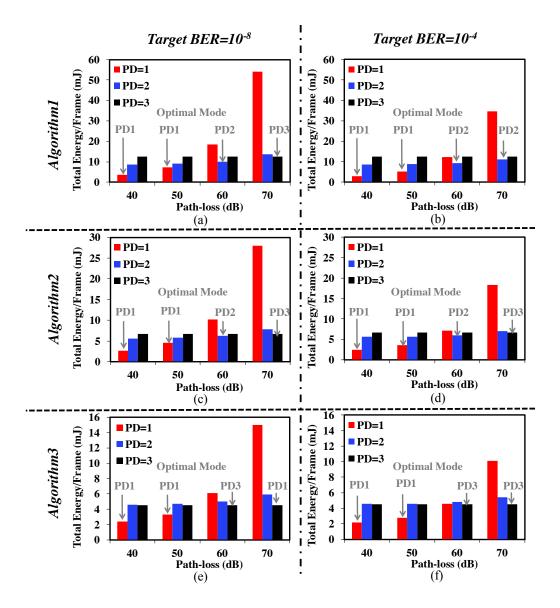

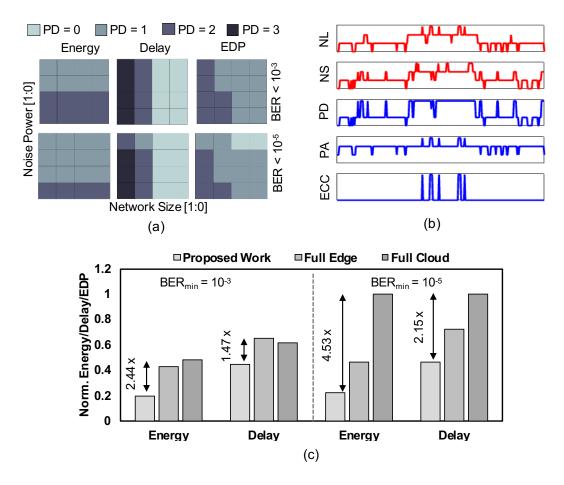

| 3.17 | Measured total energy (computation+communication) per frame for differ-<br>ent PD with increasing path-loss. Experimental results are demonstrated<br>for the three algorithms described here and two BER targets.When path-<br>loss is high, the general trend is that optimal mode moves to more front-end<br>embedded processing                                                                                                                                                                                                        | 62 |

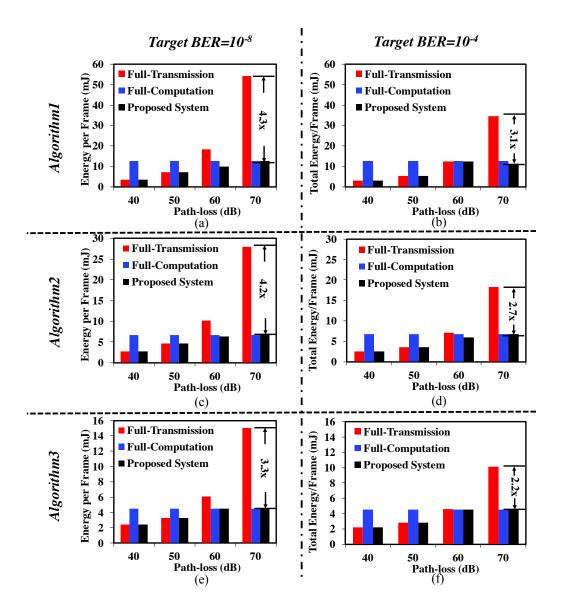

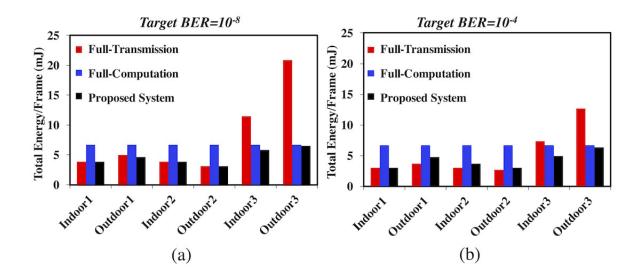

| 3.18 | Measured total energy (computation+communication) per frame for the proposed system comapred against two static designs.Experimental results are demonstrated for three algorithms and two BER targets                                                                                                                                                                                                                                                                                                                                     | 63 |

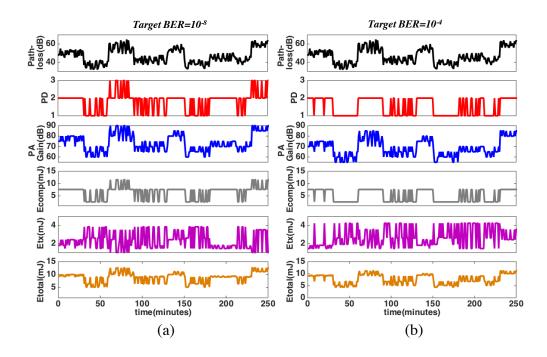

| 3.19 | Case Study: Random and dynamic path-loss condition created by a mobile IoT node and the corresponding PD, PA gain, computation, transmission and total energy per frame under BER constraints of (a) $10^{-8}$ and (b) $10^{-4}$ .                                                                                                                                                                                                                                                                                                         | 64 |

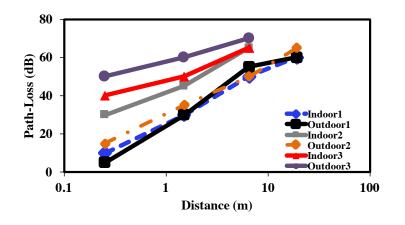

| 3.20 | Path-loss measurements under different indoor and outdoor environments                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64 |

| 3.21 | Measured total energy (average) per frame in different environments vis-a-<br>vis static designs under BER targets of (a) $10^{-8}$ and (b) $10^{-4}$                                                                                                                                                                                                                                                                                                                                                                                      | 65 |

| 3.22 | Comparison table: The proposed system has been compared with state-<br>of-the-art video based sensor nodes which either (1) perform "in-sensor"<br>video processing, or (2) improve energy-efficiency of the wireless trans-<br>mitter through real-time adaptation. The proposed system performs self-<br>optimization between the computation and communication to enable the |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | lowest power consumption in a dynamic environment.                                                                                                                                                                                                                                                                                                                              | 66 |

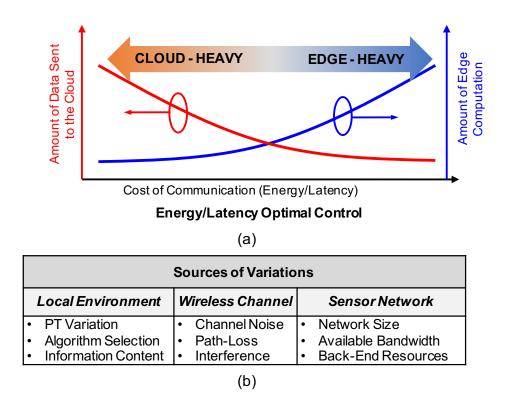

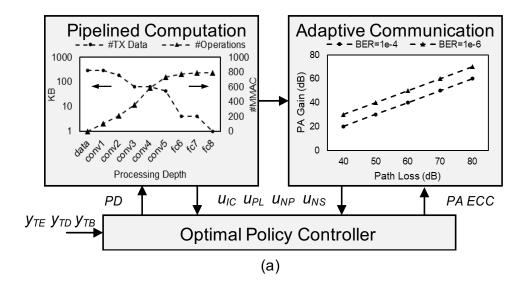

| 4.1  | Edge computation and cloud communication trade-off                                                                                                                                                                                                                                                                                                                              | 71 |

| 4.2  | Self-optimizing platform.                                                                                                                                                                                                                                                                                                                                                       | 72 |

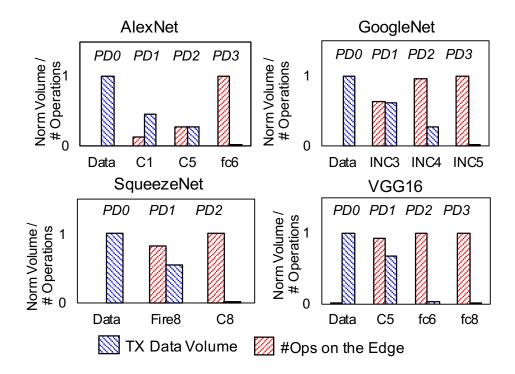

| 4.3  | Output data volume and accumulative number of computations across lay-<br>ers for various DNN architectures.                                                                                                                                                                                                                                                                    | 73 |

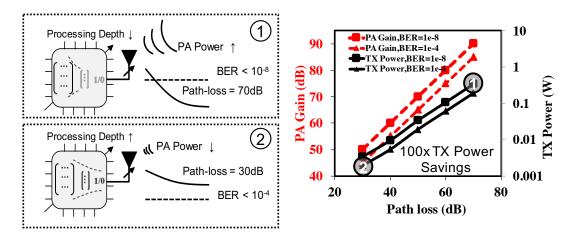

| 4.4  | Adaptive communication example that PA gain adapt to path-loss and BER requirements to preserver energy.                                                                                                                                                                                                                                                                        | 74 |

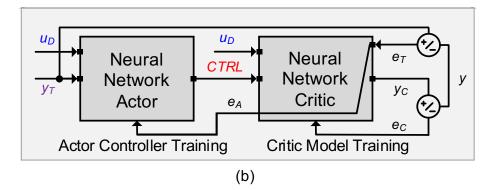

| 4.5  | (a) Neural-network-based actor-critic controller; (b) optimal policy control scheme comparisons.                                                                                                                                                                                                                                                                                | 75 |

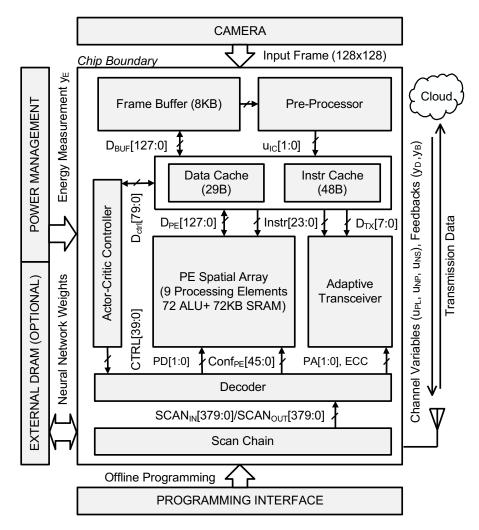

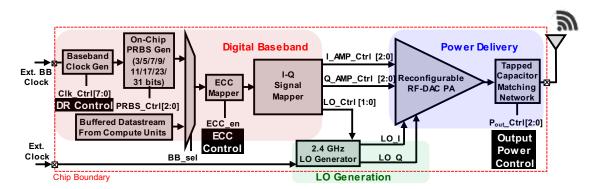

| 4.6  | System architecture                                                                                                                                                                                                                                                                                                                                                             | 77 |

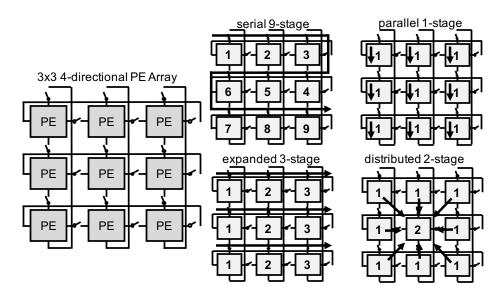

| 4.7  | 3x3 PE spatial array for reconfigurable DNN pipelines                                                                                                                                                                                                                                                                                                                           | 78 |

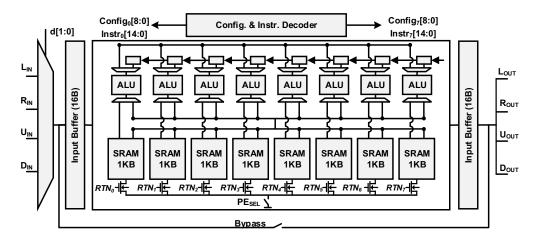

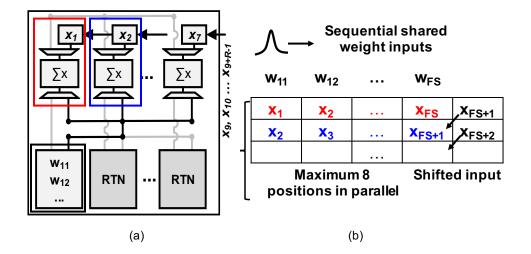

| 4.8  | Reconfigurable PE for various DNN layers                                                                                                                                                                                                                                                                                                                                        | 79 |

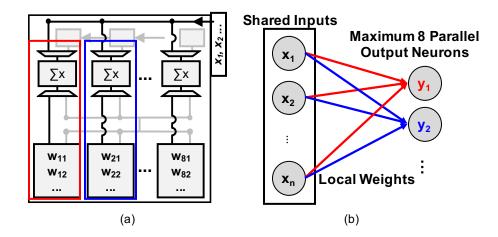

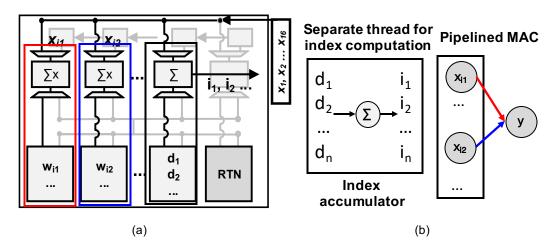

| 4.9  | Fully-connected layers (a), configurations and (b), computation                                                                                                                                                                                                                                                                                                                 | 80 |

| 4.10 | Convolution layers (a), configuration and (b), computation                                                                                                                                                                                                                                                                                                                      | 81 |

| 4.11 | Sparsely-connected layers (a), configuration and (b), computation                                                                                                                                                                                                                                                                                                               | 82 |

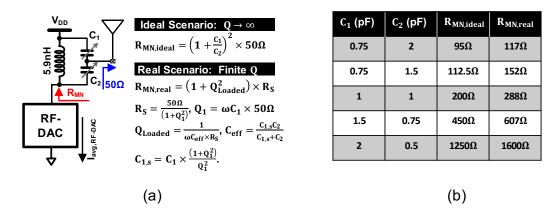

| 4.12 | Adaptive transmitter circuit                                                                                                                                                                                                                                                                                                                                                    | 82 |

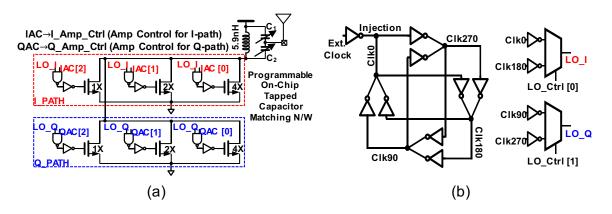

| 4.13 | TX programmable (a), modulation circuit, (b), clock synthesis circuit                                                                                                                                                                                                                                                                                                           | 83 |

| 4.14 | Capacitor matching                                                                                                                                                                                                                                                                                                                                                              | 84 |

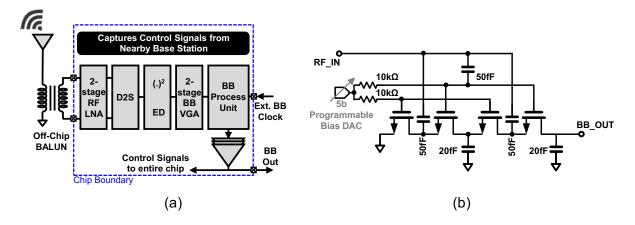

| 4.15 | Receiver circuit design.                                                                                                                                                                                                                                                                                                                                                        | 84 |

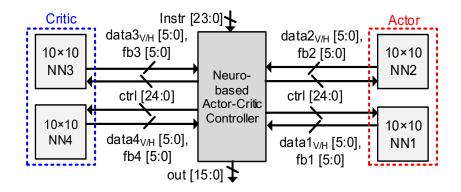

| 4.16 | NN-based actor-critic controller circuit.                                                                                                                                                                                                                                                                                                                                       | 85 |

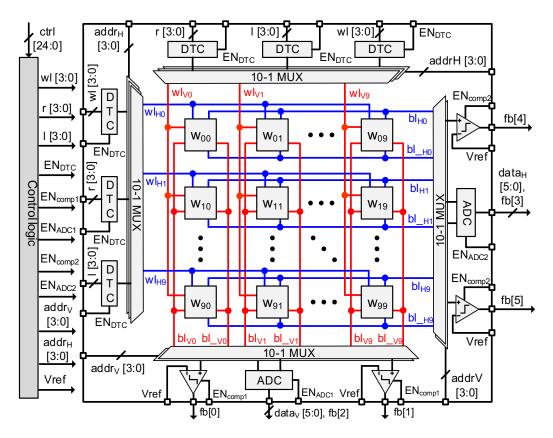

| 4.17 | 10-by-10 compute-update-in-memory block circuit.                                                                                                                                                                                                                                                                                                                                | 86 |

| 4.18 | 8b thermometer-encoded memory cell                                                                                                                                                                                                                                                                                       | 86  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.19 | Bit cell circuit                                                                                                                                                                                                                                                                                                         | 87  |

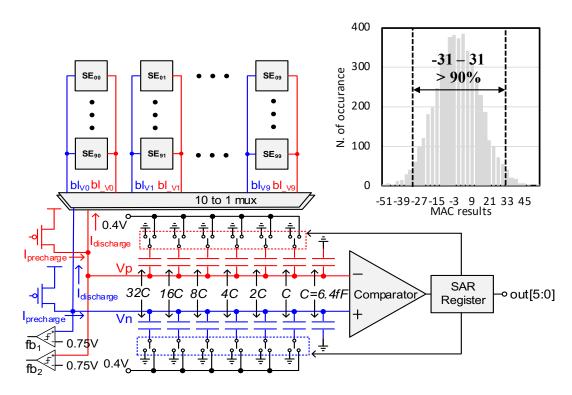

| 4.20 | 6b ADC design and data distribution                                                                                                                                                                                                                                                                                      | 88  |

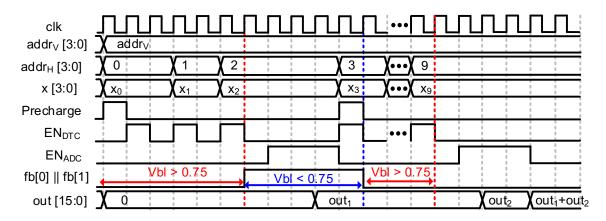

| 4.21 | Bitline MAC timing diagram.                                                                                                                                                                                                                                                                                              | 88  |

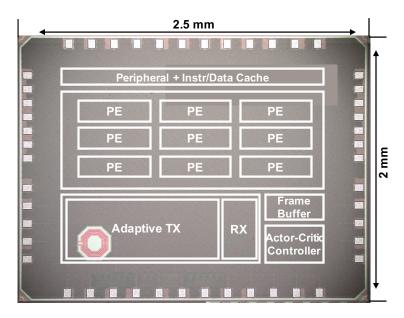

| 4.22 | Chip die phot and characteristics.                                                                                                                                                                                                                                                                                       | 89  |

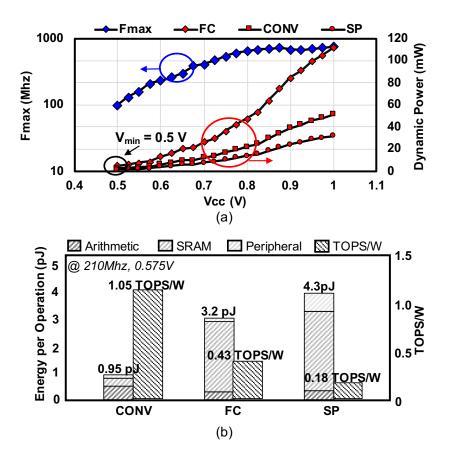

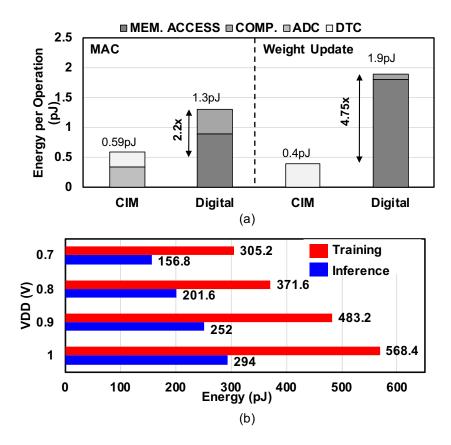

| 4.23 | Measured (a), computation pipeline frequency/power characteristics and (b), energy consumption per operations for various layers                                                                                                                                                                                         | 90  |

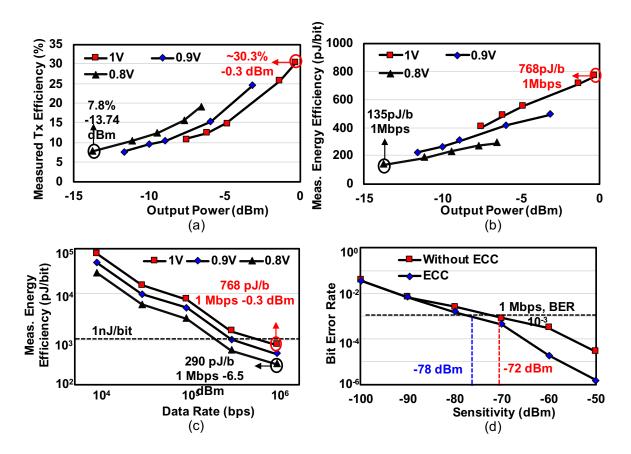

| 4.24 | Measured transceiver energy performance                                                                                                                                                                                                                                                                                  | 91  |

| 4.25 | Oscilloscope capture of bitline discharge of CUIM module                                                                                                                                                                                                                                                                 | 92  |

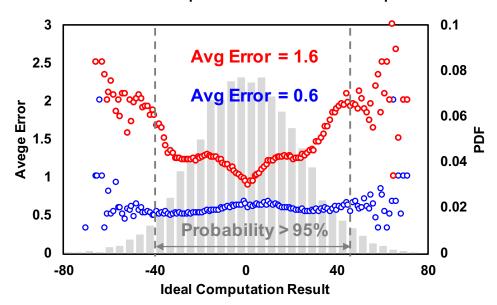

| 4.26 | Measured CUIM module non-linearities                                                                                                                                                                                                                                                                                     | 92  |

| 4.27 | Measured CUIM energy efficiency.                                                                                                                                                                                                                                                                                         | 93  |

| 4.28 | System measurements compared with baseline designs                                                                                                                                                                                                                                                                       | 94  |

| 4.29 | State-of-art comparison                                                                                                                                                                                                                                                                                                  | 95  |

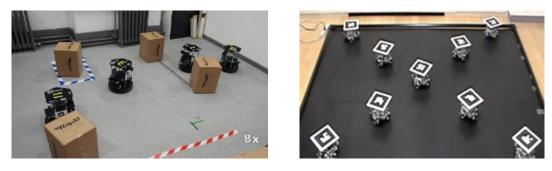

| 5.1  | Swarm algorithms that can successfully accomplish (a) collaborative path-<br>planning (b) pattern formation; (c) multi-agent patrolling; (d) multi-agent<br>predator-prey.                                                                                                                                               | 98  |

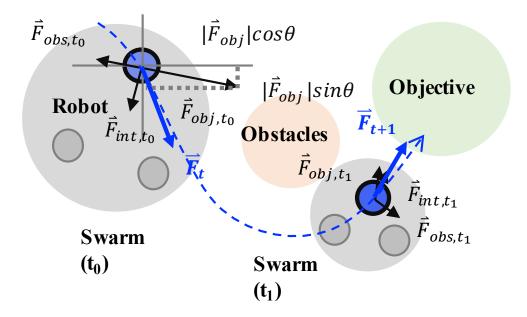

| 5.2  | Schematic map showing APF-based path-planning and formation                                                                                                                                                                                                                                                              | 100 |

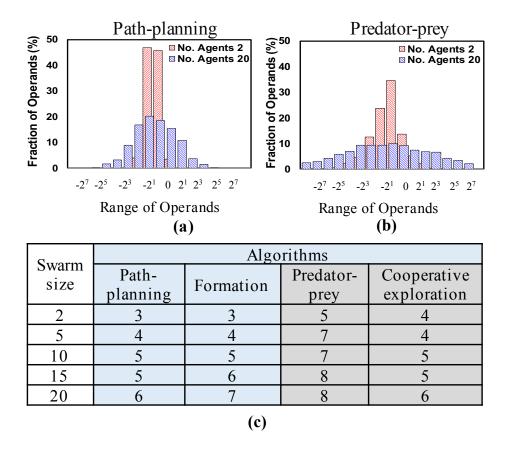

| 5.3  | Algorithmic simulations demonstrate how the required bit-precision scales with the swarm size for two template problems: (a) collaborative path-<br>planning and (b) multi-agent predator-prey. The number of bits required to accurately compute different template algorithms for varying swarm sizes is shown in (c). | 107 |

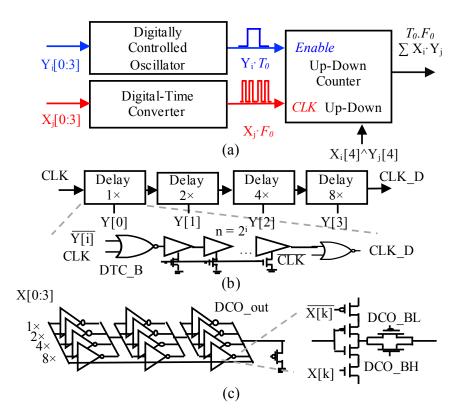

| 5.4  | Circuit schematic illustrating (a) the time-domain-mixed-signal MAC cir-<br>cuit (b) the digital-to-pulse-converter (DPC) (c) the digitally-controlled-<br>oscillator (DCO).                                                                                                                                             | 109 |

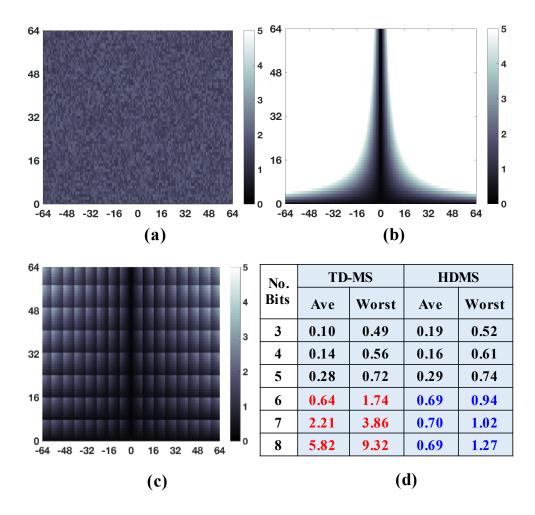

| 5.5  | Energy map vs. operand range in pJ for (a) digital (b) TDMS and (c) HDMS<br>MAC implementations. (d) The energy/MAC (normalized to a digital im-<br>plementation) for TDMS and HDMS implementations. We see that HDMS<br>out-performs TDMS (average and worst cases) and digital (average case)<br>for large swarm sizes |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

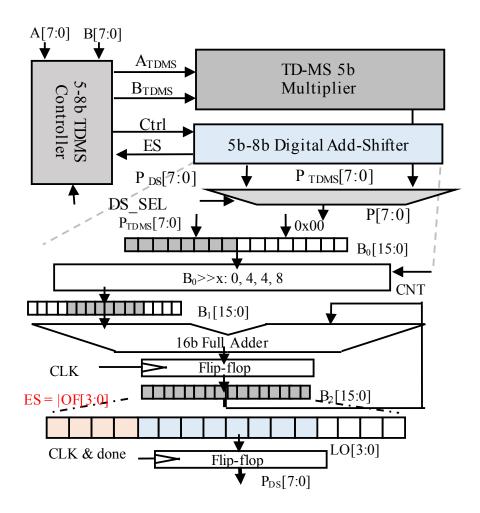

| 5.6  | Circuit schematic of the HDMS circuit illustrating the 5b TDMS kernel and the digital peripherals to enable efficient scaling to 8b                                                                                                                                                                                      |

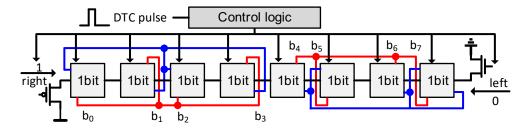

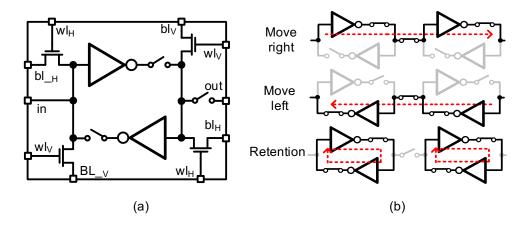

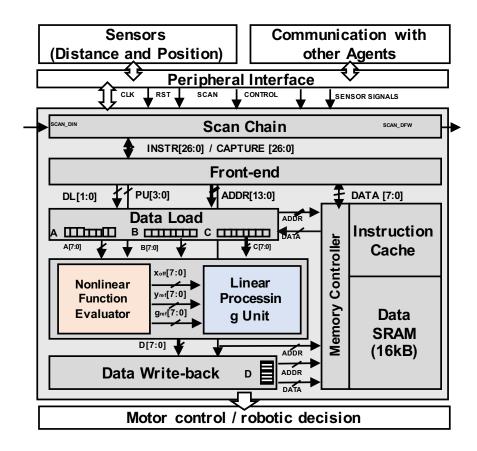

| 5.7  | Overall system architecture of the unified computing platform                                                                                                                                                                                                                                                            |

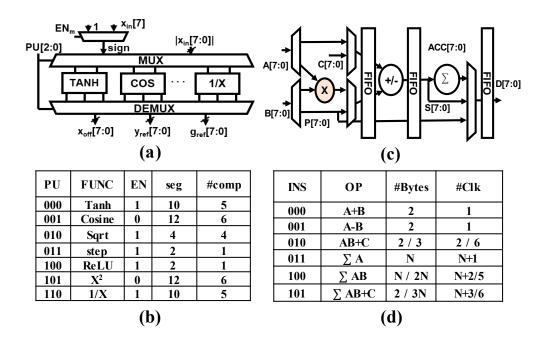

| 5.8  | <ul><li>(a) Circuit schematic and (b) the corresponding control bits for the NFE.</li><li>(c) Circuit schematic and (d) the instructions for the LPU</li></ul>                                                                                                                                                           |

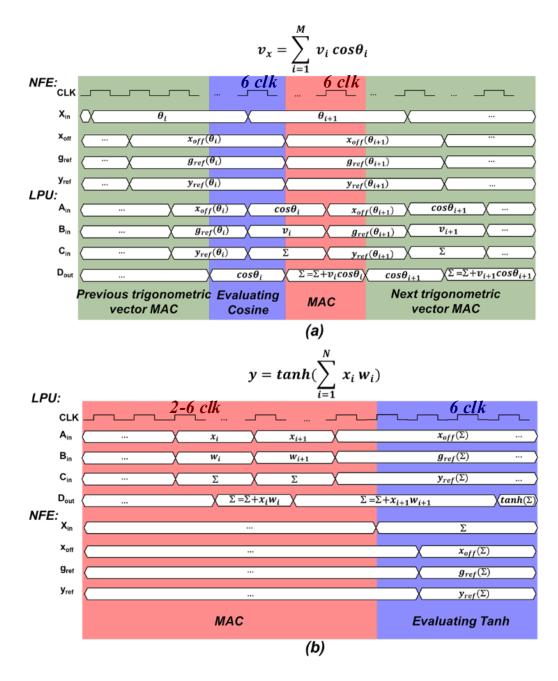

| 5.9  | Clock diagram for examples in APF (a) and cooperative RL(b)                                                                                                                                                                                                                                                              |

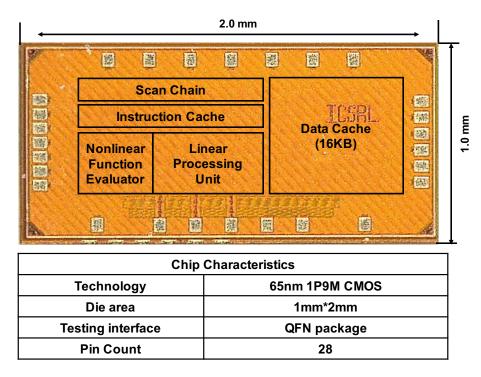

| 5.10 | Die photo and chip characteristic                                                                                                                                                                                                                                                                                        |

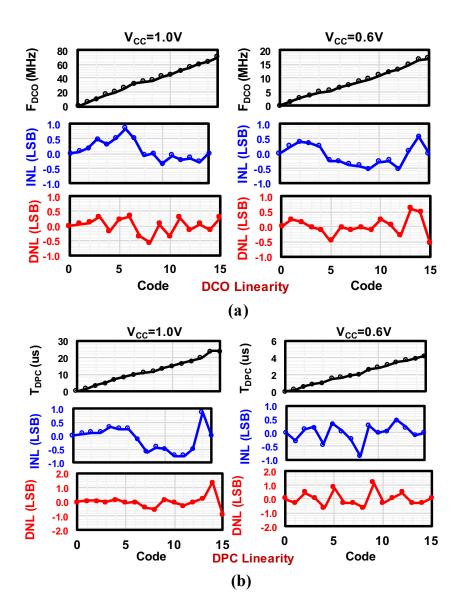

| 5.11 | Measured linearity of (a) DCO and (b) DPC                                                                                                                                                                                                                                                                                |

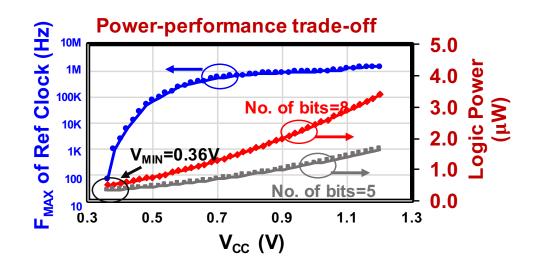

| 5.12 | Measured power-performance trade-off                                                                                                                                                                                                                                                                                     |

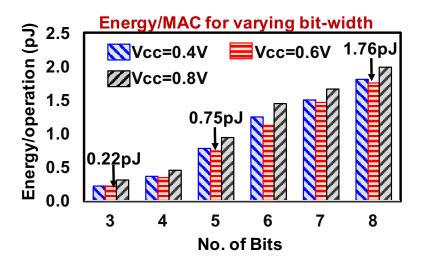

| 5.13 | Measured energy per MAC across for different bit-widths at $V_{CC} = 0.4V$ , 0.6V, 0.8V                                                                                                                                                                                                                                  |

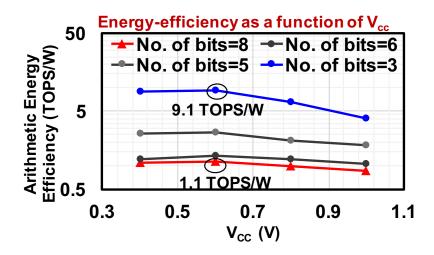

| 5.14 | Measured arithmetic energy efficiency as a function of the operating volt-<br>age for differnet bit-widths                                                                                                                                                                                                               |

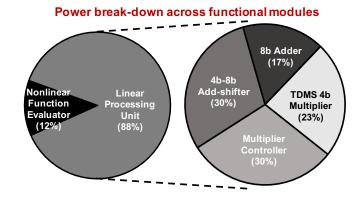

| 5.15 | Measured power break-down among different computational blocks 121                                                                                                                                                                                                                                                       |

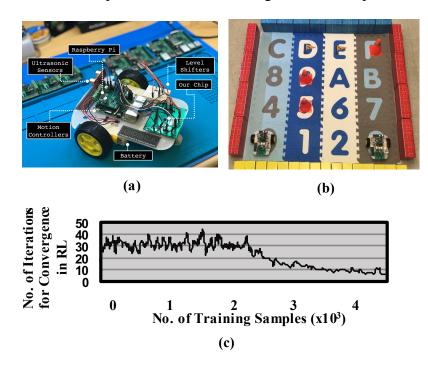

| 5.16 | (a) Test-chip mounted on a robotic car with peripheral circuits, (b) experi-<br>mental set-up and (c) the number of iterations required for convergence in<br>co-operative RL                                                                                                                                            |

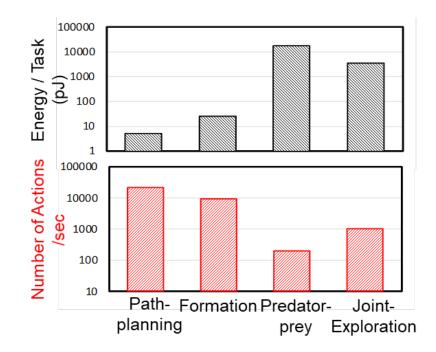

| 5.17 | Application level benchmarking demonstrating measured energy/performance for different template algorithms                                                                                                                                                                                                               |

# **SUMMARY**

In this dissertation, Chapter I will provide an overview of *Edge Intelligence* (EI), including a definition, a design landscape, a generic EI design methodology and reviews of stateof-art research/industrial EI demonstrations. Then, Chapter II-V will discuss several EI works in details to cover various EI design challenges/opportunities. Data-aware algorithm for EI will be discussed in Chapter II with an example of data-fusion-based edge occupancy detection for HVAC control. The fusion algorithm enables  $5 \times$  detection error deduction and  $3 \times$  sensor lifetime expansion while offering 26% energy savings for HVAC system in various environment through accurate occupancy detection. In Chapter III, contextaware wireless sensor control will be discussed through a self-optimizing wireless video surveillance camera platform. The self-optimizing control strategy systematically enables  $4.3 \times$  energy reduction per frame compared with baseline designs. Further, a continued self-optimizing wireless image processing system-on-chip (SoC) work will be discussed in Chapter IV. This work is going to demonstrate silicon effectiveness with respect to energy, latency and area through state-of-art circuit techniques and full computation, communication and control on-chip integration. The test chip features (1) a 1.05TOPS/W (peak) programmable DNN image processor, (2) a 768pJ/b digitally-adaptive transceiver and (3) 0.59pJ/MAC actor-critic controller for efficiently controlling computation, communication blocks separately as well as jointly. In Chapter V, distributed intelligence and its hardware design considerations will be discussed via a swarm robotic application-specific-integratedcircuit (ASIC). The test chip supports both model-based and learning-based algorithm and the hybrid-digital-mixed-signal computation enables excellent scalability with number of robotic agents. A 1.1-9.1 TOPS/W efficiency is measured across various swarm size and computation precision. Finally, conclusions will be drawn in Chapter VI with both insights gained from previous chapters as well as discussions on promising future EI research directions.

# CHAPTER 1 INTRODUCTION

From manually collecting and processing real-world data, to cloud-based *Internet of Things*, the evolution of technology has fundamentally changed the way human interface the real world. When we look at the trend, we are essentially trying to perceive, interpret and respond to our living surroundings more intelligently. In pursuing this goal, we have come to an era of cloud-based *Internet of Things*: *IoT* sensors collect data and transmit to the back-end cloud servers, and servers process the raw data for further action.

Despite extensive research efforts devoted to and significant societal achievements driven by such a paradigm, numerous bottlenecks inherent in cloud-IoT system have urged us to look for an alternative that can push the advances further. Firstly, wireless data has increased tremendously that creates significant transmission workload for the network. This rapid data growth has resulted from both an exponential growth of *IoT* sensors deployed in the real-word and also high dimensional data demanded by applications. These trends are manifested in Fig. 1.1. Further, the consequent heavy communication for individual IoT

Figure 1.1: Cloud traffic and IoT device analysis [1, 2].

node brings heavy energy burden on wireless devices which either results in degraded quality of service (QoS), or increased form-factor making them less preferable. Nevertheless, due to network leaks in recent years, security/privacy concerns also prevent us from fully trusting the cloud service.

To mitigate aforementioned problems inherent in cloud-based solutions, there have been significant demands to enable *edge intelligence* (EI) paradigm for IoT development. Instead of simple "sample-transit" procedure in a centralized mannaer, EI tends to bring intelligence closer to the IoT devices that directly connect us with the real world targeting a more responsive, private and efficient IoT service. In this Chapter, I will first introduce EI and its design challenges. Then the EI design landscape and methodology will be discussed. Then, I will present a literature survey on state-of-art EI designs. Finally, I will provide an overview of the dissertation.

## **1.1 Edge Intelligence**

"Edge intelligence" (EI) refers to the ability to empower resource-constrained edge devices at the source of the data, using advanced devices, circuits, architecture, algorithms, and

Figure 1.2: Edge intelligence overview.

control techniques to enhance the ability of data to be transformed into information (shown in Fig. 1.2). In particular, EI features machine learning (ML) and artificial intelligence (AI) applications on the IoT nodes. These edge ML/AI usages not only include computation for perception, classification, decision making and learning, but also smart control and collaboration in a dynamic wireless network. Enabling ML/AI on edge nodes will greatly enhance the smartness of the network. This improvement is reflected in many aspects.

1. EI improves IoT service efficiency. Compared to the centralized cloud-IoT paradigm that introduces enormous communication workload, EI greatly reduces the amount of data transmission via edge computation. On one hand, such a scheme minimizes network congestion hazard introduced by immense IoT devices in the network and largely mitigates the the ever-increasing communication latency problem; on the other hand, system-level energy efficiency is expected to improve by trading powerexhaustive communication with edge computation. The energy advantage is illustrated in Fig. 1.3. Processing 1 bit of data in the worst case in practice, consumes  $10^4 \times$  less energy than transmitting the same bit.

Figure 1.3: Computation vs. communication energy analysis [3]

- 2. EI improves IoT adaptability to dynamic environment. Embedding intelligence on end devices will help IoT system gain the capability to react to the environment in a responsive and smart manner. This allows hundreds of millions of edge devices to be dynamically controlled and self-optimized.

- 3. EI has inherent advantages in privacy and security. Embedded edge computation will greatly minimize information leakage risk. Needless to say that encryption essentially requires processing capability on the end devices which further enhances security.

- 4. EI has the potential to solve complex problems through distributed intelligence. When each edge device has a certain amount of intelligent resources and interacts with each other to form a smart cluster, they can potentially perform complex data processing tasks.

However, due to the constrained resources of IoT nodes, such as limited chip area, available bandwidth, energy storage and manufacture budget, enabling ML/AI on IoT nodes is challenging. On one hand, we have witnessed the slow demise of Dennard's scaling and Moore's Law. This has further led to slowing down of the processor performance improvement and flattening of the cost per transistor. This trend exposes the vulnerability

Figure 1.4: (a) processor performance scaling [4], (b) transistor cost scaling [5] and (c) battery density improvement [6] vs. edge computation required clock frequency in order to process in real time [7]

of the road map for the microprocessor performance improvement, as technology scaling will no longer be able to provide a straight-forward solution to sustain performance growth (Fig. 1.4.(a-b)). Further, the limited energy resources constrain the potential applications of edge devices. Although there has been significant improvement on battery capacity and energy-density (around  $3 \times$  within 15 years), the rapidly evolving demand for complex workloads, from environmental sensing to high-definition video processing in surveillance applications, has motivated us to explore fundamental innovations in computational hardware. The real-time computation requirements for typical IoT applications in the past 10 years in terms of clock frequency are compared with the battery capacity improvement trend in Fig. 1.4.(c).

### 1.2 EI Design Landscape, FoM and Design Methodology

EI design is an emerging research discipline that requires systematic investigation. First of all, what are major research fields in EI landscape need to be comprehensively defined. At the same time, a figure-of-merit (FoM) has to be proposed to facilitate EI design/research evaluation procedure. Finally, a generic EI design methodology is highly desired to shed light on important design considerations and potential solutions.

#### 1.2.1 EI Design Examples

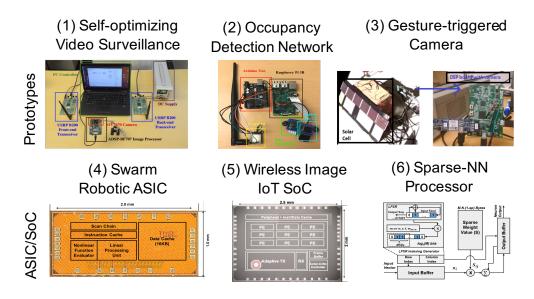

To explore EI landscape, FoM and design methodology, the author has extensively investigated various EI research topics, including EI algorithm, control scheme, hardware integration, distributed intelligence and so on . And further, beyond theoretical/simulated efforts, to facilitate real-world performance and efficiency evaluations, the author demonstrated actual physical platforms (shown in Fig. 1.5) including: (1) a wireless self-optimizing video surveillance camera prototype; (2) a wireless HVAC data-fusion occupancy detection sensor and network; (3) a self-powered camera with compress-domain gesture-triggered wakeup; (4) a swarm robotic ASIC; (5) a wireless image processing SoC with computation-

Figure 1.5: Example EI works.

communication trade-off; (6) LFSR-based DNN pruning ASIC. These works have broadly investigated research topics of IoT system, ML/AI algorithm, computer architecture, digital/mixed-signal/analog circuit design and so on. They aim at maximizing intelligence on resource-constrained devices across design layers.

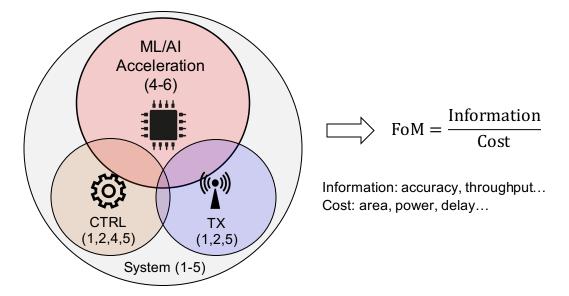

# 1.2.2 EI Design Landscape and FoM

Despite the fact that these preliminary works covered a broad range of research topics/ML applications/design layers, like most EI works, they fall into one or more design fields in the EI landscape shown in Fig. 1.6. At the core is the capability to implement computation, especially ever-evolving ML/AI, on edge devices. It targets efficient computation through innovations in circuit techniques (example 4-5), computer architecture (example 5) or algorithm design (example 2, 6). At the same time, smart control (example 1,2,4,5) and efficient data exchange (example 1,2,5) are both crucial for the IoT to handle dynamic environment and reduce communication cost. Finally, seamless solid-state system integration of discrete components determines EI platforms' ultimate performance in the real-world (example 4-6). Although EI design demands extensive efforts from various design fields, the goal is

Figure 1.6: EI design landscape and figure-of-merit.

to efficiently derive "actionable intellegence" under severe resource constraints. Or we can represent this target as a figure-of-merit (FoM): *intelligence per cost*. "Intelligence" may be in form of accuracy, throughput and etc., and cost may be in form of area, power and etc. The EI landscape and FoM have provided a comprehensive view of EI design/research as well an evaluation criteria.

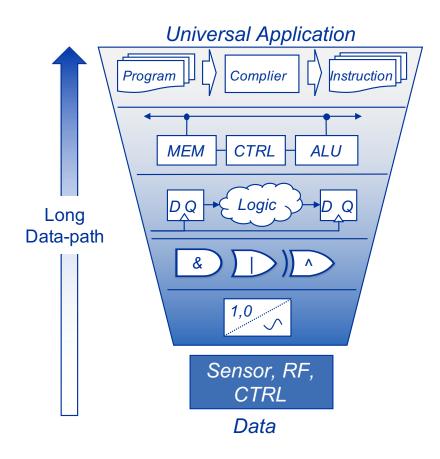

## 1.2.3 Conventional IoT Design Methodology

Traditional IoT devices are designed and implemented with general-purpose digital processors together with discrete peripherals, such as controller and transceiver. By evaluating EI FoM, we have found that, although they feature fast prototyping as a proof-of-concept, their efficiencies are far below our expectations for real-time ultra-low power edge devices. The details will be covered in Chapter II and III. To understand the cause of inefficiency, we need to first look at the conventional IoT design scheme described in Fig. 1.7.

Data is first sampled or produced by discrete peripherals from sensor, radio frequency (RF) modules and controllers. Then, the data is fed into digital computation system. The data will first be quantized in voltage domain, and then binary data will go through Boolean combination logic. The logic needs to be augmented with significant amount of memory

(cache, scratchpad, registers) with synchronous movement across the logic-memory boundary. At the architectural level, usually Von-Neumann architecture is adopted, where data storage (memory) and computation (arithmetic logic unit) are separated and they are controlled by a central controller. Finally, general-purpose compiler will optimize instruction execution to support universal applications.

Though it is a successful design scheme in most scenarios, but in the case of EI, it is incompatible due to the lack of efficiency caused by the various layers of abstraction from the source of physical data to the final information. Energy loss occurs when data go through each layer of the abstraction. (1) Data converters are required to transfer all physical data representations into digital voltage signals. Both information loss and ADC overhead introduces energy expenditure. (2) During Boolean operations, both dynamic

Figure 1.7: Conventional IoT design methodology.

and static power are consumed to make sure computation/storage are correct and signal is preserved rail-to-rail. (3) For the system to run in a synchronized manner, clock signal together with the large clock tree and buffers have to constantly run; thus introducing significant power consumption. (4) Separate memory and computation architecture results in significant data movement cost, especially in the era of ML/AI where large models need to constantly accessed. To push efficiency to extreme and support ML/AI on edge devices, we have to flatten the levels of abstraction bringing processing closer to the data and eliminating unwanted data-conversions and optimizing for the minimum amount of bit resolution.

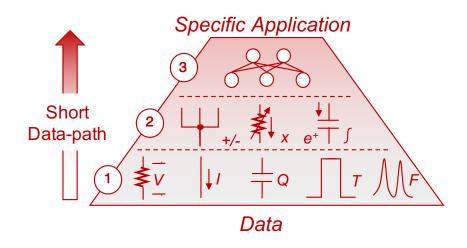

#### 1.2.4 Proposed EI Design Methodology

To flatten the design hierarchy, the author has proposed a generic EI design methodology as shown in Fig. 1.8.

Context-aware Integrated System: the system integration has to take into account the physical representation of data as well as the device's environmental context. It should be open to any physical data encoding scheme to reduce data conversion overhead, and it should adapt to the dynamics of the environmental conditions.

Figure 1.8: Proposed EI design methodology.

- 2. Algorithm-aware Hardware: the computational circuit design should be aware of the algorithm it implements and optimizes for the application it supports. By taking into account the data encoding scheme, any physical computation scheme can be adopted to maximize a target cost function, e.g., latency or energy-efficiency.

- 3. **Hardware-aware Algorithm**: the algorithm design should be aware of the hardware constraints and available hardware opportunities. We need to investigate hardware-friendly algorithms and mathematical operations that can be incorporated into the design flow.

Through proposed design methodology, the design hierarchy is flattened as much as possible. This will provide a scheme to trade-off the universality of digital microprocessors for the target FoM in EI. The details will be discussed from Chapter II to Chapter IV.

## 1.3 Literature Survey

As discussed in the previous sections, EI requires knowledge and innovations in various design fields. In this section, we are going to discuss state-of-art academic/industrial designs in fields of 1) data acquisition, 2) edge computation, 3) wireless communication and 4) system integration.

Upon data acquisition, researchers have been looking for opportunities in improving the capability of performing sensor data analytics while extending the lifetime of the sensors. By incorporating limited computation to the traditional sensor, the sensor can pre-process raw data to either facilitate further computation or extract useful information for optimized operation of the overall system. In computer vision field, for example, pre-processing unit for motion detection, binarization and gesture recognition [8, 9, 10] been proposed for efficient in-camera analytics. At the same time, researchers have also worked on self-powered camera sensors which convert the incident light into electrical energy to provide an in-situ energy source [11]. Another important data acquisition research field is acoustic

sensing and, in particular, ultra-low power (ULP) always-on voice activity detection (VAD) is gaining attention as an enabling technology for IoT platforms. Various silicon chip sets have been presented to enhance power efficiency, programmability and context-awareness of VAD [12, 13, 14]. Besides efforts to enhance data acquisition performance by single sensor, researchers have also investigated multi-sensors for application optimization. While a high-performance single sensor is usually both costly and power-hungery, data fusion of low-resolution sensors with orthogonal information becomes an promising alternative. [15] presents a skin-disease diagnosis system with both optical and electrical dual tomographic imaging. [16] deals with detection of occupancy in a room from various ambient sources like temperature, humidity, light, and CO2 to leverage HVAC control in real time.

At the core of EI, the ability to handle computation-intensive task on the edge hardware is a major challenge. With slow-down of Moore's law as well as the reducing opportunities of scaling in digital VLSI, analog and mixed-signal circuit innovations are being actively explored. These innovations include dedicated ultra-low-power, moderate precision mixed-signal/analog computational block, but also architectures to improve data movement/computation. For example, [17] presented an SoC that performs continuous-time hybrid approximate computation, in which both analog and digital signals are functions of continuous time. [18] demonstrated a matrix multiplying ADC to enable feature extraction and classification with data conversion, mitigating the need for further computation. Similarly, [19] built a switched-capacitor matrix multiplier with co-designed bitline-less memory to reduce A/D conversion rate and improve MAC computation energy efficiency. A novel spike-based SLAM accelerator has been presented in [20]. [21] features an energy-efficient switched-capacitor (SC) neuron that addresses energy challenge, employing a 1024-bit thermometer-coded capacitive digital-to-analog converter (CDAC) section for summing point-wise-products of CNN filter weights and activation and a 9-bit binary weighted section for adding the filter bias. Meanwhile, with ever-increasing data-centric computation, people are also looking for alternatives for von-Neuman architecture, where

data storage and computation are tightly coupled. [22] demonstrates a 7b energy efficient SRAM with embedded convolution computation for CNN-based machine learning applications. [23] proposed a 'sandwich' architecture of in-memory binary weight network (BWN) to blend feature and partial-weight memory with a computing circuit together that achieves significantly less data access. From a larger scope, the spatio-data-correlation has been investigated and utilized to improve system preformance as in [24]. [25] presented a nonvolatile compute-in-memory ReRAM macro for binary DNN AI edge processors for low power feature and fast IO accesses. Nevertheless, novel devices, especially energy-efficient, low-cost and high data-rate non-volatile memory together with compatible computation architecture are widely researched. [26] demonstrates Ferroelectric FET Analog Synapse for Acceleration of Deep Neural Network Training. [27] provides a 3D-flash memory with improved area capacity. [28] built STT based RAM for high-yield, high performance and high-endurance.

Towards a fully connected internet of things, innovations in wireless data communication is crucial in maximizing datarate while minimizing latency, energy-per-bit (EPB) and bit-error-rate (BER). On the circuit level, researchers mainly target improved RF block metrics, such as improved transmission resolution at low loss [29] or obtaining high output power while maintaining efficiency [30]. At the same time, the community is also exploring SoC-level RF solutions, such as [31], to push throughput limits and enable 5G networks and beyond. At the same time, as communication units are usually designed to meet minimum requirement at worst-case, energy/performance are not optimal in a dynamic environment. In this background, cognitive radio where RF is optimally controlled in a context-aware manner is widely investigated. [32] advocates the use of Reinforcement Learning (RL) incontext-aware and intelligent Dynamic Channel Selection (DCS) scheme to enhance QoS in Cognitive Radio (CR) networks. [33] demonstrates orthogonal tuning knobs using an inductorless LNA which has 14dB Gain tuning range and 30 dB OIP3 tuning range with power consumption goes down by 20. [34] develops a multidimensional adaptive power management approach that optimally trades-off power versus performance across temporally changing operating conditions by concurrently tuning control parameters in the RF and digital baseband components of the wireless receiver. [35] demonstrates a real time BER vs. power consumption modulation of RF front-end devices in MIMO system. Beyond circuit and context-aware control, communication schemes for dedicated scenarios are also important for optimized performance. [36] demonstrates characterization of human body communication for ultra-low power high-accuracy medical applications. [37] reports results from wireless chip-to-chip communication experiments with 16 bit words pass from one chip to another in parallel without detectable error at 1.35 billion data items per second for a total data rate of 21.6 Gigabits per second.

On top of efforts in optimizing each functional block of EI (data acquisition, edge computation and wireless communication), efficient system integration is also challenging and provides the ultimate evaluation metrics for EI hardware design. [38] presented a complete "edge-gateway-cloud" IoT system prototype for an example application that highlights the key advanced capabilities of the cm-scale, self-powered, intelligent and secure mote hardware platform at the edge. In [39], Intel showed another wireless sensor node (WSN) that integrates near-threshold voltage (NTV) 32-bit Intel Architecture (IA) microcontroller (MCU) in 14nm tri-gate CMOS, along with solar cell, energy harvester, flash memory, sensors and Bluetooth Low Energy (BLE) radio, to enable always-on alwayssensing (AOAS) and advanced edge computing capabilities in Internet-of-Things (IoT) systems. [40] demonstrated a low-power Robot SoC in 22nm CMOS that is integrated in the cm-scale minibot platform along with audiovisual and motion sensors, battery, lowpower wireless communication and motion actuator components. [41] presents a single chip VLSI architecture of wireless image sensor node, which is constituted by an enhanced embedded 8051 microcontroller, a CMOS camera interface and hardware accelerators.

As a broad topic and emerging area, it is challenging for individual researchers to demonstrate a complete study of EI. Instead the field continues to advance through collabo-

rations. During the literature study, the author has found several informative survey papers providing insightful knowledge from various perspective. [42] provided an overview of technologies associated with IoT in embedded systems' landscape. They have investigated essential technologies for development of IoT systems, existing trends, and its distinguishing properties. By discussing the key characteristics, main application domains, and major research issues in IoT, this paper provides a comprehensive IoT perspective for embedded system design. On the other end, from an an industry and government perspective, [43] provided insight to the problem of intelligence resource constrained IoT nodes and presented the vision of the future and important technologies that might play a strong role in enabling the vision of trillion smart connected sensors. Finally, [44] provided an academic perspective of the problem, starting with a survey of recent advances in intelligent sensing, computation, communication, and energy management for resource-constrained IoT sensor nodes leading to future outlook and needs.

### **1.4 Dissertation Overview**

In the following Chapters, the author will discuss algorithm design, control strategy, system integration as well as distributed intelligence via dedicated example works. In Chapter II, a fusion-based occupancy detection algorithm, together with an HVAC occupancy detection wireless camera system will be discussed. In Chapter III, an online EI computation-communication trade-off control scheme is introduced with a wireless video surveillance camera. Continuing further in the same light, Chapter IV describes an SoC implementation of computation-communication trade-off control strategy in wireless image processing applications. The silicon effectiveness in energy, latency and area will be fully investigated. After discussing single-agent EI algorithm, control and system design, Chapter V is going to discuss multi-agent distributed EI through a unified swarm robotic ASIC. In particular, this Chapter will address hardware requirements to meet scalability issues in multi-agent learning scenarios. Finally, the author will draw conclusion in Chapter VI.

## **CHAPTER 2**

# EI FOR DATA-FUSION-BASED OCCUPANCY DETECTION IN HVAC CONTROL