# HARDWARE ASSISTED MEMORY CHECKPOINTING AND APPLICATIONS IN DEBUGGING AND RELIABILITY

A Thesis Presented to The Academic Faculty

by

Ioannis Doudalis

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Computer Science

Georgia Institute of Technology December 2011

# HARDWARE ASSISTED MEMORY CHECKPOINTING AND APPLICATIONS IN DEBUGGING AND RELIABILITY

Approved by:

Professor Milos Prvulovic, Advisor School of Computer Science *Georgia Institute of Technology*

Professor Hyesoon Kim School of Computer Science *Georgia Institute of Technology*

Professor Hsien-Hsin Lee School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr Gabriel Loh Research and Advanced Development Laboratories Advanced Micro Devices (AMD)

Professor Alessandro Orso School of Computer Science *Georgia Institute of Technology*

Date Approved: June 2nd 2011

Dedicated to Dimitrios, Elisavet, Stylianos and Thaleia-Dimitra

## ACKNOWLEDGEMENTS

My first thanks are due to my advisor Prof. Milos Prvulovic. He gave me the opportunity to pursue my PhD studies in the US, and guided me through this long and not always smooth journey. Always open for discussion, always willing to explain everything, no matter how easy or hard it was, Prof. Prvulovic taught me how to think as a computer architect and a researcher.

I would also like to thank my PhD committee: Prof. Hyesoon Kim, Prof Hsien-Hsin S. Lee, Dr Gabriel Loh and Prof Alessandro Orso. All four have served as a motivation for me, assisting me at different times of my PhD, advising me both on academic and as professional issues.

Fellow students also played an important role in my life as a PhD student. I would like to thank Guru, who helped me from the first time I joined the PhD program and gave me invaluable advice about PhD life and research, Samantika, Kiran, Chenyu, Dong, Nak Hee for the long and lively discussions we had, Jungju and Anshuman for patiently helping me with my papers and presentation slides, the attendees at our architecture seminar for their useful comments about my research. I would also like to thank Alan and Susie for their prompt administrative support, and Chad and Peter for their IT support.

Finally I would like to thank my family, my father Dimitris, my mother Elisavet, my brother Stylianos and my sister Thaleia-Dimitra for their support at every step of my PhD career, from the point I decided to go to the US until now. They have always been by my side and taught me patience and optimism, I will always be grateful to them.

# TABLE OF CONTENTS

| DE  | DEDICATION          |                                                            |   |  |  |  |  |  |

|-----|---------------------|------------------------------------------------------------|---|--|--|--|--|--|

| AC  | ACKNOWLEDGEMENTS iv |                                                            |   |  |  |  |  |  |

| LIS | LIST OF TABLES      |                                                            |   |  |  |  |  |  |

| LIS | T OF                | FIGURES                                                    | X |  |  |  |  |  |

| SUI | MMA                 | RY xii                                                     | i |  |  |  |  |  |

| I   | INT                 | RODUCTION                                                  | 1 |  |  |  |  |  |

|     | 1.1                 | The Problems of Debugging and Reliability.                 | 1 |  |  |  |  |  |

|     | 1.2                 | Techniques for Improving Debugging and System Reliability. | 2 |  |  |  |  |  |

|     | 1.3                 | Overview                                                   | 2 |  |  |  |  |  |

|     | 1.4                 | Scope of this Dissertation                                 | 5 |  |  |  |  |  |

| II  | OVE                 | ERVIEW OF MEMORY CHECKPOINTING TECHNIQUES                  | 6 |  |  |  |  |  |

|     | 2.1                 | Introduction to Checkpointing and Logging                  | 6 |  |  |  |  |  |

|     | 2.2                 | Checkpoint Implementations                                 | 8 |  |  |  |  |  |

|     | 2.3                 | Checkpoint Storage                                         | 0 |  |  |  |  |  |

|     | 2.4                 | Checkpointing of Multi-Processor Systems                   | 1 |  |  |  |  |  |

|     | 2.5                 | Summary                                                    | 2 |  |  |  |  |  |

| III | HAF                 | RDWARE-ASSISTED BIDIRECTIONAL DEBUGGING                    | 3 |  |  |  |  |  |

|     | 3.1                 | A Review of Bidirectional Debugging 10                     | 6 |  |  |  |  |  |

|     | 3.2                 | HARE: Hardware Assisted Reverse Execution                  | 9 |  |  |  |  |  |

|     |                     | 3.2.1 Memory Modification Tracking                         | 1 |  |  |  |  |  |

|     |                     | 3.2.2 Checkpoint Creation                                  | 2 |  |  |  |  |  |

|     |                     | 3.2.3 Checkpoint Consolidation                             | 3 |  |  |  |  |  |

|     |                     | 3.2.4 Restoring Checkpointed State                         | 4 |  |  |  |  |  |

|     |                     | 3.2.5 Checkpoint Log Organization                          | 5 |  |  |  |  |  |

|     | 3.3                 | HARE: Implementation Details                               | 5 |  |  |  |  |  |

|     |                     | 3.3.1 Caching Memory Modification Bits                     | 5 |  |  |  |  |  |

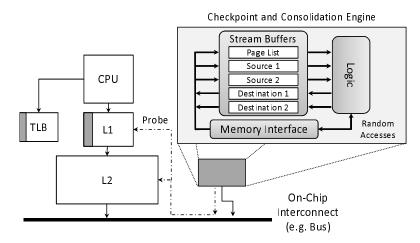

|     |                     | 3.3.2 Checkpoint/Consolidation Engine 20                   | 6 |  |  |  |  |  |

|     |                     | 3.3.3 System and Race Logging                              | 7 |  |  |  |  |  |

|    |     | 3.3.4   | OS Interaction                                      | 28 |

|----|-----|---------|-----------------------------------------------------|----|

|    | 3.4 | Euripu  | s: Hardware Assisted Reverse Execution Using a Trie | 29 |

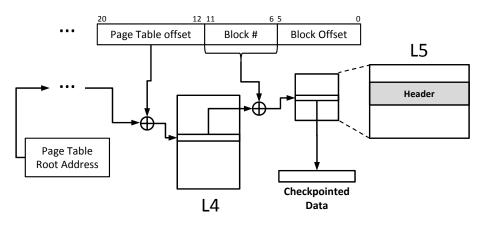

|    |     | 3.4.1   | Undo-Log Construction                               | 29 |

|    |     | 3.4.2   | Redo-Log Construction                               | 30 |

|    |     | 3.4.3   | Checkpoint Consolidation                            | 33 |

|    |     | 3.4.4   | Improving Reverse Execution Latency                 | 34 |

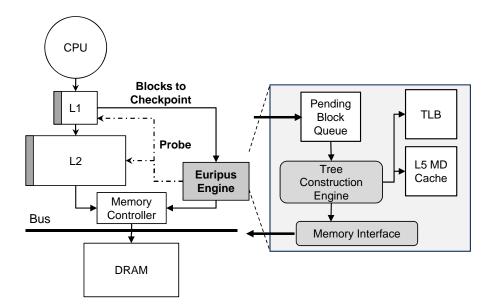

|    | 3.5 | Euripu  | Is Implementation                                   | 35 |

|    |     | 3.5.1   | Undo Log Creation                                   | 35 |

|    |     | 3.5.2   | Redo Log Creation                                   | 36 |

|    |     | 3.5.3   | L5 Node Meta-Data Organization                      | 37 |

|    |     | 3.5.4   | Interaction with the OS/VM                          | 37 |

|    |     | 3.5.5   | Improved Reverse Execution                          | 39 |

|    | 3.6 | Perfor  | mance Evaluation of HARE and Euripus                | 39 |

|    |     | 3.6.1   | Evaluation Setup                                    | 39 |

|    |     | 3.6.2   | Hardware Cost                                       | 40 |

|    |     | 3.6.3   | HARE: Performance Overhead Evaluation               | 41 |

|    |     | 3.6.4   | Euripus: Performance Overhead Evaluation            | 46 |

|    |     | 3.6.5   | Concurrent Undo and Redo Log Construction           | 50 |

|    |     | 3.6.6   | Memory Requirements                                 | 53 |

|    |     | 3.6.7   | Reverse Execution Latency                           | 57 |

|    |     | 3.6.8   | Enhanced Reverse Execution Functionality            | 63 |

|    | 3.7 | Summ    | ary                                                 | 66 |

| IV | HYI | BRID H  | IARDWARE ACCELERATED CHECKPOINTING FOR RECOVERY     | •  |

|    | FRO | OM A W  | VIDE RANGE OF ERRORS AND DETECTION LATENCIES        | 67 |

|    | 4.1 | Fault 7 | Types and Detection Mechanisms                      | 70 |

|    |     | 4.1.1   | Fault Types                                         | 70 |

|    |     | 4.1.2   | Error Detection Mechanisms                          | 71 |

|    | 4.2 | Check   | pointing for Reliability                            | 73 |

|    | 4.3 | The K   | yma Checkpointing Technique                         | 75 |

|    | 4.4 | Impler  | nentation Details of Kyma                           | 79 |

|    |     | 4.4.1   | Undo-Log Checkpointing                              | 79 |

| RE | FERF | NCES . |                                                            | 124 |

|----|------|--------|------------------------------------------------------------|-----|

| AP | PEND | OIX A  | - MULTI-LEVEL CHECKPOINTING RELIABILITY MODEL              | 111 |

| V  | CON  | ICLUS  | IONS                                                       | 109 |

|    | 4.6  | Summa  | ary                                                        | 108 |

|    |      | 4.5.9  | PCM Memory Requirements and Power Considerations           | 107 |

|    |      | 4.5.8  | PCM Latency Sensitivity Analysis                           | 106 |

|    |      | 4.5.7  | 3D-Stacked Memory Performance Evaluation                   | 105 |

|    |      | 4.5.6  | Kyma Engine Hardware Cost Sensitivity Analysis             | 103 |

|    |      | 4.5.5  | Checkpointing Frequency Sensitivity Analysis               | 100 |

|    |      | 4.5.4  | Performance Comparison With Other Checkpointing Techniques | 96  |

|    |      | 4.5.3  | Availability Analysis                                      | 92  |

|    |      | 4.5.2  | Performance Overhead of Kyma                               | 91  |

|    |      | 4.5.1  | Evaluation Setup                                           | 89  |

|    | 4.5  | Evalua | tion of Kyma                                               | 89  |

|    |      | 4.4.4  | I/O and Multiprocessor Issues                              | 87  |

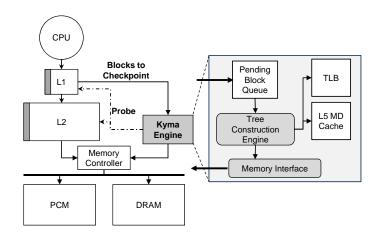

|    |      | 4.4.3  | Kyma Engine Description                                    | 85  |

|    |      | 4.4.2  | Redo-Log Checkpoint Creation and Organization              | 82  |

# LIST OF TABLES

| 1 | Type of checkpoint constructed and meta-data data-structures used for checkpoint |    |

|---|----------------------------------------------------------------------------------|----|

|   | representation by the evaluated techniques                                       | 41 |

# LIST OF FIGURES

| 1  | Example of undo and redo-log checkpoints                                                                                                                                                      | 7  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Examples of consistent and inconsistent checkpoints.                                                                                                                                          | 11 |

| 3  | Debugging example with back-tracking.                                                                                                                                                         | 14 |

| 4  | Reverse-execution via checkpoint/replay                                                                                                                                                       | 15 |

| 5  | Space used for frequent checkpointing                                                                                                                                                         | 18 |

| 6  | Checkpointing with undo and with redo logs.                                                                                                                                                   | 20 |

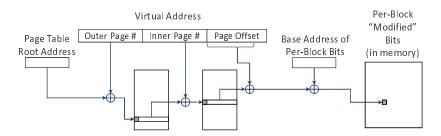

| 7  | Modification tracking bits (shown in gray)                                                                                                                                                    | 21 |

| 8  | Hardware support for HARE, with added hardware shown as gray                                                                                                                                  | 26 |

| 9  | Trie data-structure used by Euripus for representing the undo-log checkpoints                                                                                                                 | 30 |

| 10 | Synergies that develop when both undo and redo-log checkpoints are created. $\ldots$                                                                                                          | 31 |

| 11 | Extended trie data-structure used in Euripus when constructing both undo and redo-<br>log checkpoints.                                                                                        | 32 |

| 12 | The Euripus hardware engine.                                                                                                                                                                  | 35 |

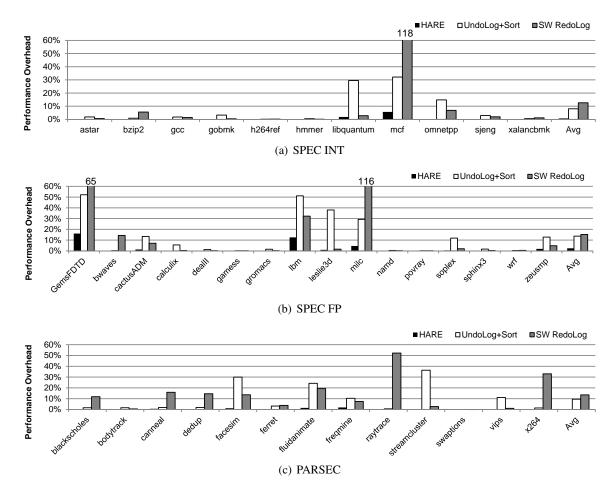

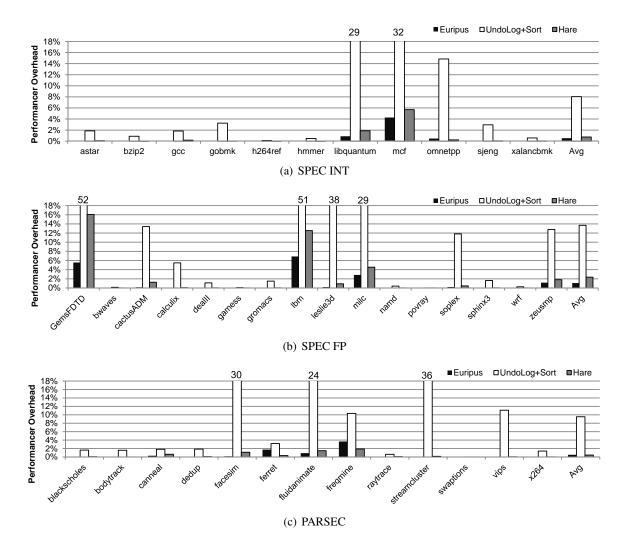

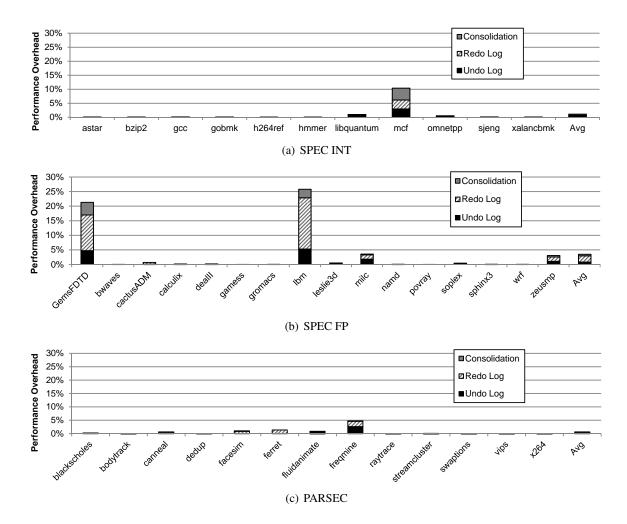

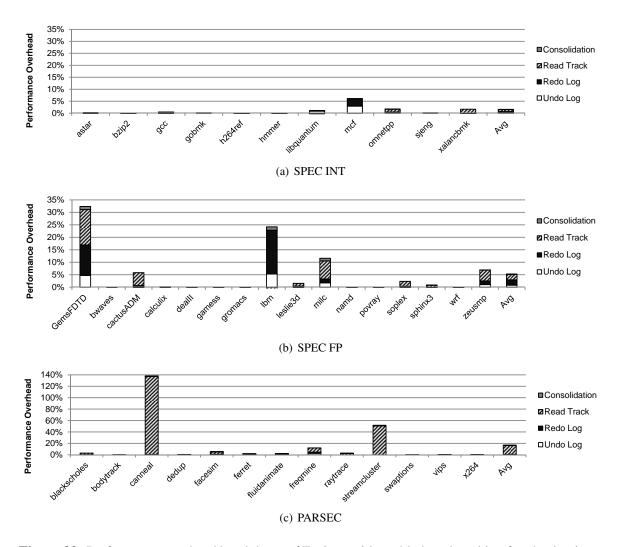

| 13 | Performance overhead comparison of HARE with with UndoLog+Sort and SW RedoLog for checkpointing interval of 0.5 sec                                                                           | 42 |

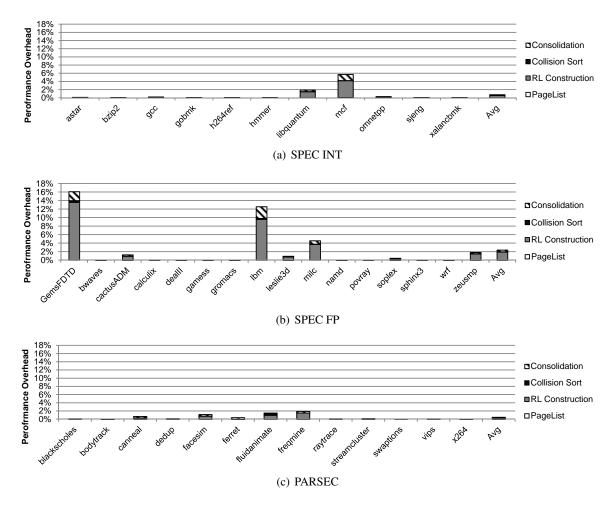

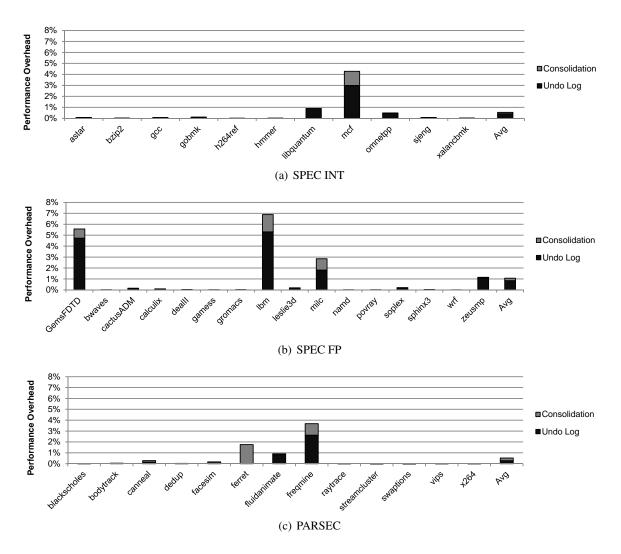

| 14 | Performance overhead breakdown of HARE for checkpointing interval of 0.5 sec                                                                                                                  | 44 |

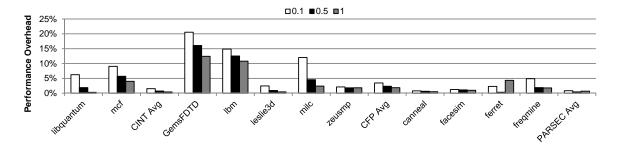

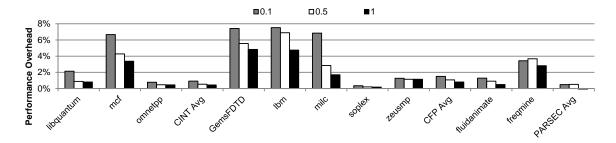

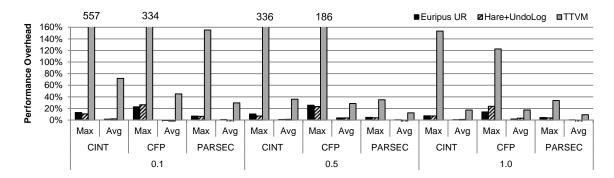

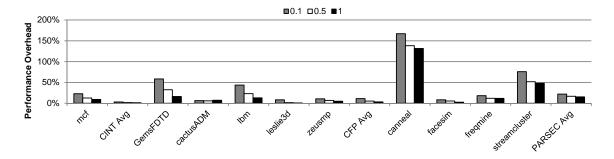

| 15 | Performance overhead of HARE for checkpointing intervals of 0.1, 0.5 and 1 sec, for the SPEC INT (CINT), SPEC FP (CFP) and PARSEC benchmarks                                                  | 45 |

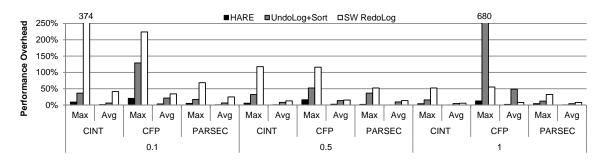

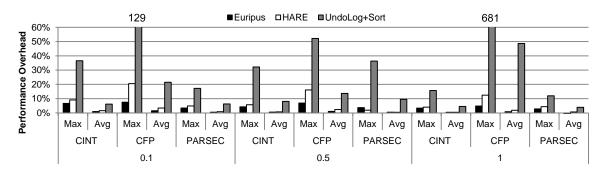

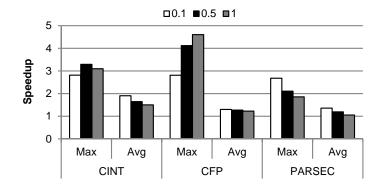

| 16 | Maximum and average performance overhead of HARE, UndoLog+Sort and SW RedoLog for checkponting intervals of 0.1, 0.5 and 1 sec, for the SPEC INT (CINT), SPEC FP (CFP) and PARSEC benchmarks. | 45 |

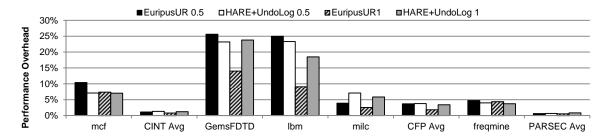

| 17 | Performance overhead of Euripus, UndoLog+Sort and Hare for a checkpointing interval of 0.5 sec                                                                                                | 47 |

| 18 | Performance overhead break down of Euripus for checkpointing interval of 0.5 sec.                                                                                                             | 48 |

| 19 | Performance overhead of Euripus for checkpointing intervals 0.1, 0.5 and 1 sec, for the SPEC INT (CINT), SPEC FP (CFP) and PARSEC benchmarks                                                  | 49 |

| 20 | Performance overhead of Euripus, HARE and UndoLog+Sort for checkpointing in-<br>tervals of 0.1, 0.5 and 1 sec, for the SPEC INT (CINT), SPEC FP (CFP) and PAR-<br>SEC benchmarks.             | 49 |

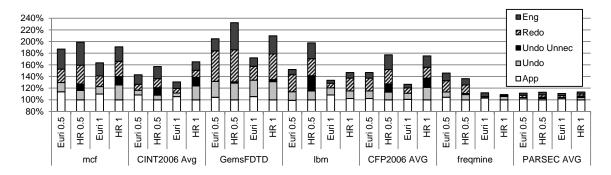

| 21 | Performance overhead breakdown of Euripus when both undo and redo-log check-<br>points are create for a checkpointing interval of 0.5 sec                                                     | 50 |

| 22 | Maximum and average performance overheads of EuripusUR, Hare+UndoLog and TTVM for checkpointing intervals of 0.1, 0.5 and 1 sec, for the SPEC INT (CINT), SPEC FP (CFP) and PARSEC benchmarks.                                                                                                | 51 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 23 | Performance overhead of worst performing applications and averages for Euripus (EuripusUR) and Hare+UndoLog for checkpointing intervals of 0.5 and 1 sec, for the SPEC INT (CINT), SPEC FP (CFP) and PARSEC benchmarks                                                                        | 52 |

| 24 | Break down of the memory accesses of Euripus (Euri) and HARE+UndoLog(HR) for the highest overhead applications and the averages for checkpointing intervals of 0.5 and 1 sec.                                                                                                                 | 52 |

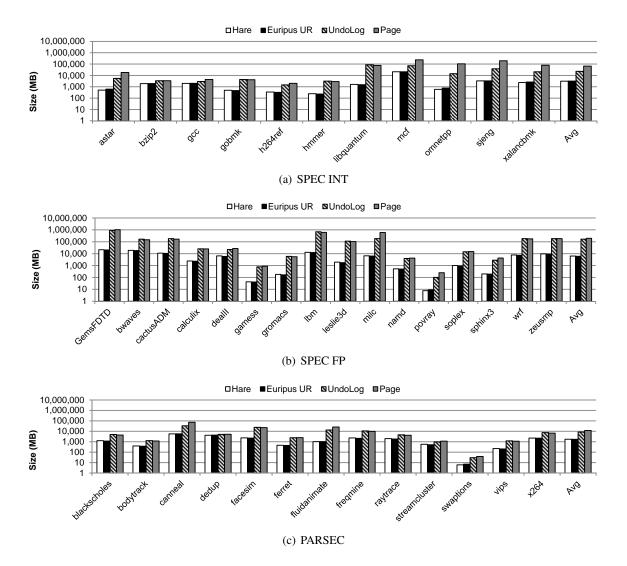

| 25 | Memory requirements of HARE, EuripusUR, UndoLog and Page for checkpointing interval of 0.5 sec.                                                                                                                                                                                               | 55 |

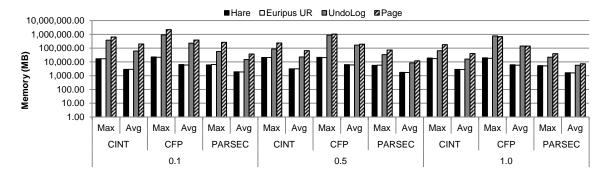

| 26 | Maximum and average memory requirements of HARE, EuripusUR, UndoLog and Page for checkpointing intervals of 0.1, 0.5 and 1 sec, for the SPEC INT (CINT), SPEC FP (CFP) and PARSEC benchmarks.                                                                                                 | 56 |

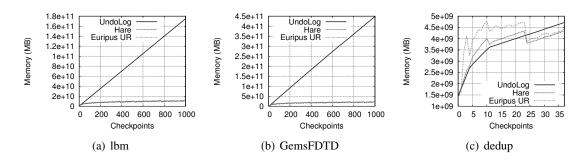

| 27 | Memory requirements of UndoLog, Hare and EuripusUR after a number of check-<br>points has been created for a checkpointing interval of 0.5 sec.                                                                                                                                               | 57 |

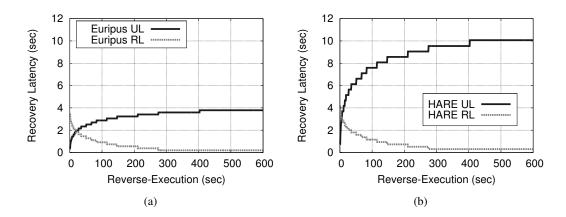

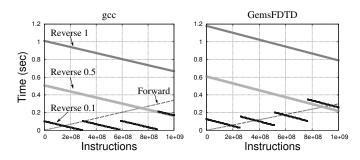

| 28 | Program memory recovery latency of GemsFDTD when reverse-executing a number of seconds of original program execution using undo-log only (Euripus UL, HARE UL) and redo-log (Euripus UR, HARE UL) checkpoints.                                                                                | 58 |

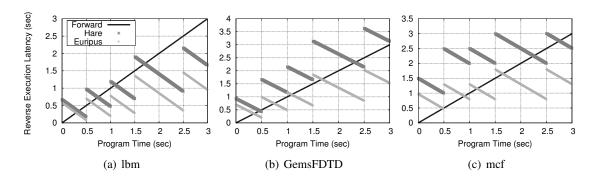

| 29 | Comparison of reverse-execution latency with forward execution time for HARE and Euripus for different applications.                                                                                                                                                                          | 60 |

| 30 | Maximum and average memory recovery latency speedup of Euripus over HARE for checkpointing intervals of 0.1, 0.5 and 1 sec, for the SPEC INT (CINT), SPEC FP (CFP) and PARSEC benchmarks.                                                                                                     | 61 |

| 31 | Forward and reverse-execution latency of Euripus for checkpointing intervals of 0.1, 0.5 and 1 seconds                                                                                                                                                                                        | 62 |

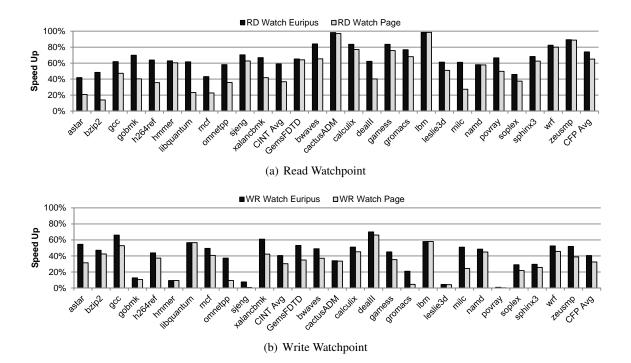

| 32 | Reverse-execution latency speedup when Euripus's meta-data are used to accelerate "reverse-continue" for read or write watchpoints, and comparison with a technique that keeps track of the same information at the page granularity, for the SPEC INT (CINT) and SPEC FP (CFP) applications. | 63 |

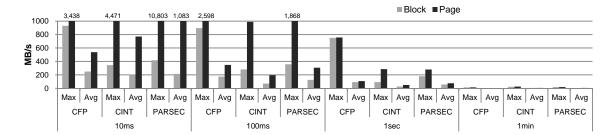

| 33 | Performance overhead breakdown of Euripus with enabled read tracking for check-<br>pointing interval of 0.5 sec                                                                                                                                                                               | 64 |

| 34 | Performance overhead of Euripus with read tracking enabled for checkpointing in-<br>tervals of 0.1, 0.5 and 1 sec, for the SPEC INT (CINT), SPEC FP (CFP) and PAR-<br>SEC benchmarks.                                                                                                         | 65 |

| 35 | Undo-log and redo-log checkpoint creation.                                                                                                                                                                                                                                                    | 74 |

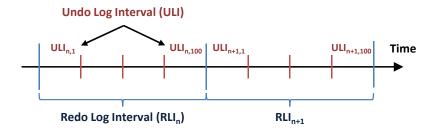

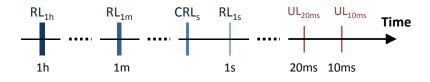

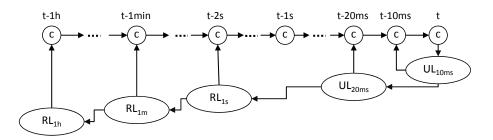

| 36 | Distribution of undo-log and redo-log intervals over time                                                                                                                                                                                                                                     | 77 |

| 37 | Distribution of undo-logs and redo-logs checkpoints over time                                                                                                                                                                                                                                 | 78 |

| 38 | Maximum and average memory bandwidth requirements in MB/s of checkpointing mechanisms for different checkpointing intervals (in seconds) when using block or page tracking granularities for the SPEC 2006 [96] floating point (CFP), integer (CINT) and PARSEC 2.1 [8] benchmarks. | 79         |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

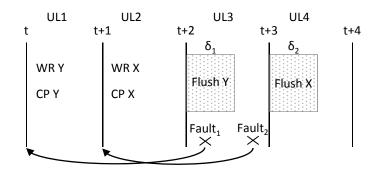

| 39 | Implications of delayed cache-flushing on error recovery.                                                                                                                                                                                                                           | 81         |

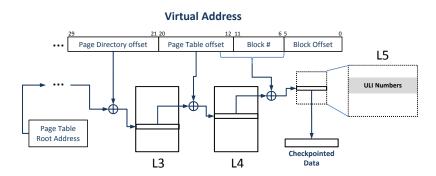

| 40 | Redo-log checkpoint meta-data trie data structure used by Kyma                                                                                                                                                                                                                      | 83         |

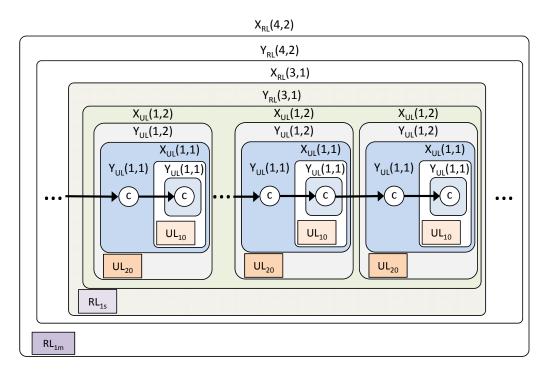

| 41 | Architecture of the Kyma hardware engine.                                                                                                                                                                                                                                           | 86         |

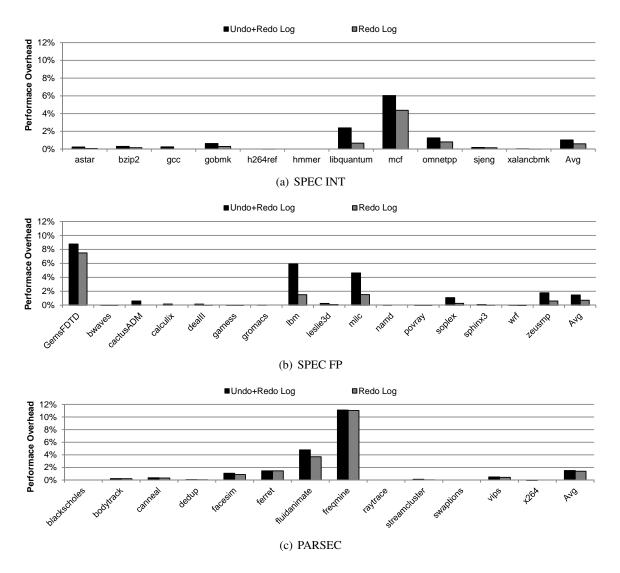

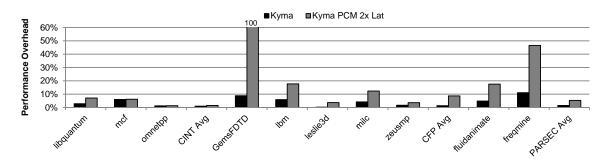

| 42 | Performance overhead comparison of Kyma when both undo and redo-logs and only redo-log are created for undo-log interval of 0.01 sec and redo-log interval of 1 sec.                                                                                                                | 90         |

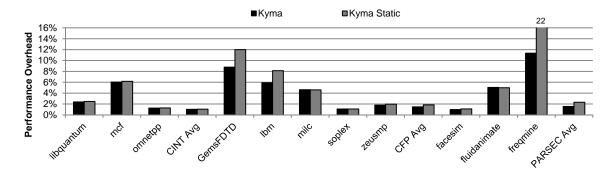

| 43 | Performance overhead comparison of Kyma's adaptive checkpointing policy with the static policy, for the SPEC INT (CINT), SPEC FP (CFP) and PARSEC benchmarks.                                                                                                                       | 91         |

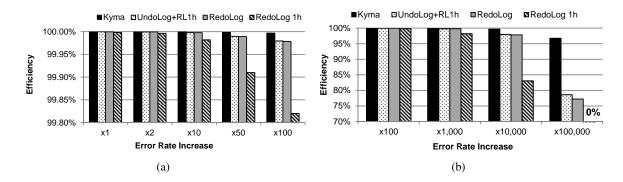

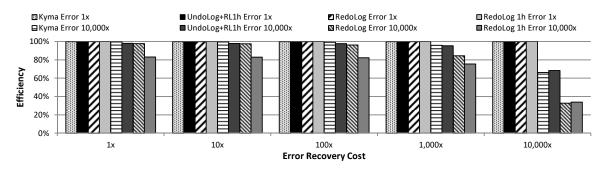

| 44 | Achieved efficiency of a system using Kyma, compared to other checkpointing approaches, for increasing error rates.                                                                                                                                                                 | 93         |

| 45 | Achieved efficiency of a system using Kyma, compared to other checkpointing approaches, for different error rates and increasing error recovery cost.                                                                                                                               | 95         |

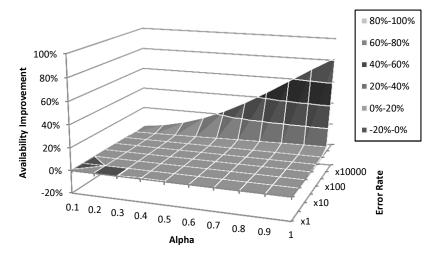

| 46 | Improvement of efficiency of Kyma over UndoLog+RL1h for different distributions of errors across checkpoint levels, and different error rates.                                                                                                                                      | 96         |

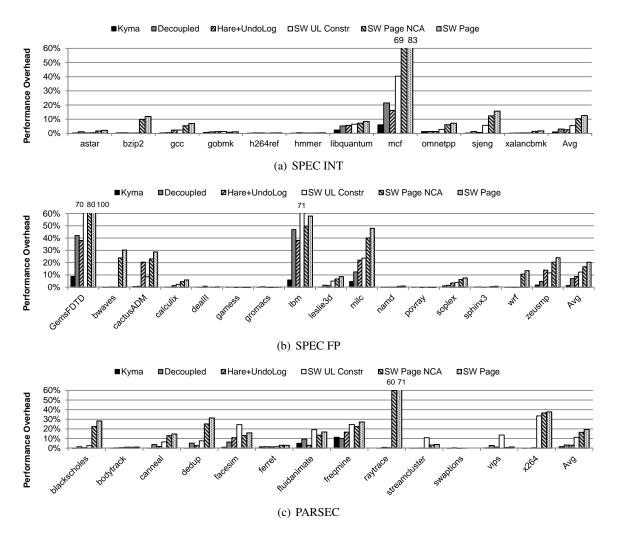

| 47 | Performance overhead comparison of Kyma with alternative checkpointing techniques, with undo-log interval of 0.01 sec and redo-log interval of 1 sec                                                                                                                                | 98         |

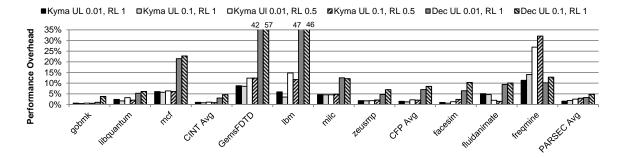

| 48 | Performance overhead comparison of Kyma for different undo-log (UL) and redo-<br>log (RL) checkpointing intervals and comparison with the decoupled engine (Dec),<br>for the SPEC INT (CINT), SPEC FP (CFP) and PARSEC benchmarks                                                   | 100        |

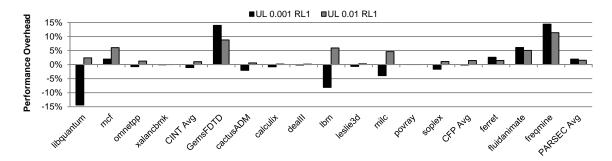

| 49 | Performance overhead of Kyma for undo-log intervals of 0.001 and 0.01 sec and redo-log interval of 1sec , for the SPEC INT (CINT), SPEC FP (CFP) and PARSEC benchmarks.                                                                                                             | 101        |

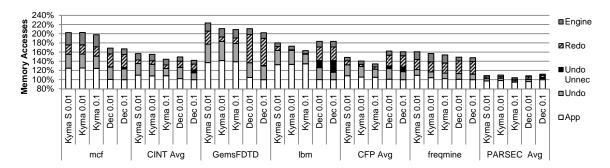

| 50 | Break-down of the type memory accesses of the Kyma, Kyma with a static redo-<br>log policy (Kyma S) and the Decoupled engine (Dec) for undo-log checkpointing<br>intervals of 0.01 and 0.1 sec.                                                                                     | 103        |

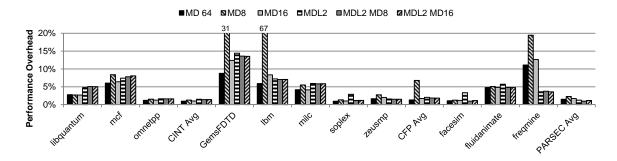

| 51 | Performance overhead of Kyma for different L5MD cache configurations, for the SPEC INT (CINT), SPEC FP (CFP) and PARSEC benchmarks.                                                                                                                                                 | 104        |

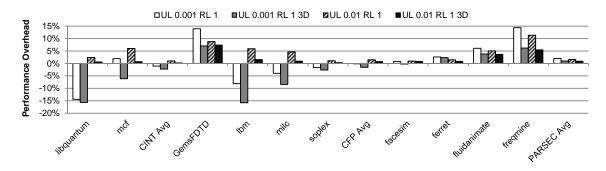

| 52 | Performance overhead of Kyma for the original and 3D-stacked (3D) memory con-<br>figuration, for the SPEC INT (CINT), SPEC FP (CFP) and PARSEC benchmarks.                                                                                                                          | 106        |

| 53 | PCM latency sensitivity analysis of Kyma's performance overhead, for the SPEC INT (CINT), SPEC FP (CFP) and PARSEC benchmarks.                                                                                                                                                      | 106<br>106 |

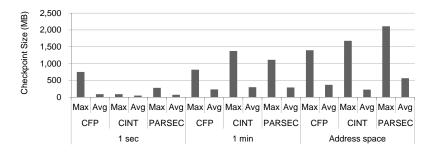

| 54 | Maximum and average memory requirements in MB of the one second, one minute checkpoints and the address-space of the application.                                                                                                                                                   | 108        |

| 55 | Markov Queue model of a multi-level checkpointing system.           | 112 |

|----|---------------------------------------------------------------------|-----|

| 56 | Recursive representation of the Markov Model.                       | 113 |

| 57 | Transition state with multiple incoming and a single out-going edge | 114 |

| 58 | Transition state with a loop edge.                                  | 114 |

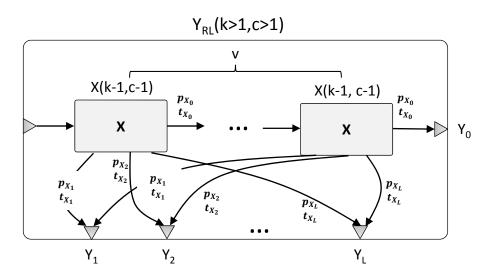

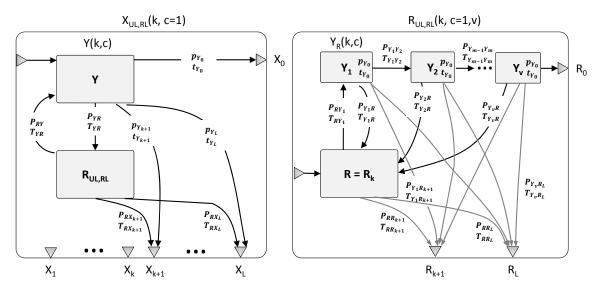

| 59 | The $Y_{RL}(k)$ computation state for $k, c > 1$                    | 116 |

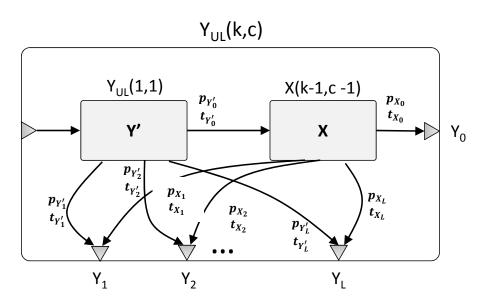

| 60 | The $Y_{UL}(k)$ computation block for $k, c > 1$ .                  | 117 |

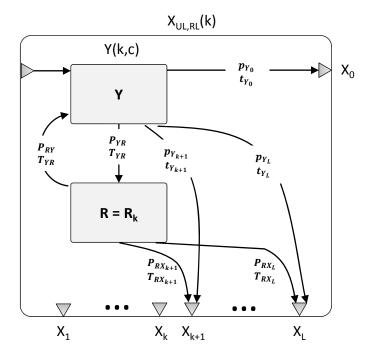

| 61 | The X block for redo-log checkpoint recovery.                       | 119 |

| 62 | The $X_{UL,RL}(k,c=1)$ state.                                       | 121 |

## SUMMARY

Thesis statement: Memory and performance overheads of application and system checkpoints can be significantly reduced with the assistance of hardware techniques.

The problems of software debugging and system reliability/availability are among the most challenging problems the computing industry is facing today, with direct impact on the development and operating costs of computing systems. A promising debugging technique that assists programmers identify and fix the causes of software bugs a lot more efficiently is *bidirectional debugging*, which enables the user to execute the program in "reverse", and a typical method used to recover a system after a fault is backwards error recovery, which restores the system to the last error-free state. Both reverse execution and backwards error recovery are enabled by creating memory checkpoints, which are used to restore the program/system to a prior point in time and re-execute until the point of interest. The checkpointing frequency is the primary factor that affects both the latency of reverse execution and the recovery time of the system; more frequent checkpoints reduce the necessary re-execution time.

Frequent creation of checkpoints poses performance challenges, because of the increased number of memory reads and writes necessary for copying the modified system/program memory, and also because of software interventions, additional synchronization and I/O, etc., needed for creating a checkpoint. In this thesis I examine a number of different hardware accelerators, whose role is to create frequent memory checkpoints in the background, at minimal performance overheads. For the purpose of reverse execution, I propose the HARE and Euripus hardware checkpoint accelerators. HARE and Euripus create different types of checkpoints, and employ different methods for keeping track of the modified memory. As a result, HARE and Euripus have different hardware costs and provide different functionality which directly affects the latency of reverse execution. For improving the availability of the system, I propose the Kyma hardware accelerator. Kyma enables simultaneous creation of checkpoints at different frequencies, which allows the system to recover from multiple types of errors and tolerate variable error-detection latencies. The Kyma and Euripus hardware engines have similar architectures, but the functionality of the Kyma engine is optimized for further reducing the performance overheads and improving the reliability of the system. The functionality of the Kyma and Euripus engines can be combined into a unified accelerator that can serve the needs of both bidirectional debugging and system recovery.

## **CHAPTER I**

# **INTRODUCTION**

# 1.1 The Problems of Debugging and Reliability.

The problems of software debugging and system reliability are among the most challenging problems the computing industry is facing today, with direct impact on the development and operating costs of computing systems. These two problems, even though they seem to be disjoint, share a lot characteristics and sub-problems. Those common traits across areas are the target of current and future research that will result in efficient and retargetable solutions, which will in turn reduce the overall design, manufacturing, programing and operating cost.

Software debugging is the process of identifying and correcting the causes of program errors. It has been estimated [39] that debugging accounts for 60%–70% of the development effort and 80% of project overruns. It has also been estimated that in the early stages of development bugs cost an order of magnitude (50 to 200 times) [10, 11] less to fix than in later stages, and that 20% of bugs cause approximately 80% of program code rework. Software errors are expected to cost to the U.S economy approximately \$59.5 billion [78]. Beyond the financial cost, software bugs can result in the loss of human lives [41]. An important problem for software debugging is how to accelerate the process of identifying the causes of incorrect program execution, thus reducing the overall software development and testing time, as well as the associated costs.

System reliability targets the uninterrupted correct operation of computing systems, as well as quick detection and recovery from errors. The types of errors that might affect a system span across the whole hardware/software stack. For example, as processor circuits scale to smaller transistor sizes they become increasingly vulnerable to radiation [13] (e.g. alpha particles) that can cause transient errors, which in turn can result in erroneous computation. Software bugs can also disrupt the correct operation of a system. For example, the power outage that in 2001 affected 50 million people across eight US states and Canada [67,100], was partly caused by a software bug that resulted in the alarm system's failure.

## 1.2 Techniques for Improving Debugging and System Reliability.

In debugging, in order to isolate the cause of an error, we often have to re-execute the program multiple times using breakpoints and watchpoints, a process that is extremely time-consuming for long-running applications. To accelerate the debugging process, bidirectional debugging [12] has been proposed. Bidirectional debugging creates for the programmer the illusion of executing the program seamlessly in either direction (forward or in reverse). This functionality avoids multiple re-executions and thus allows the programmer to more rapidly isolate the cause of the program error. The illusion of *reverse execution* is created with a combination of application state checkpointing, which can restore the program to a past point in time, and deterministic replay. A checkpoint is a copy of the whole system state (e.g processor registers and program memory) at a given point in time. The key parameter that affects the interactivity of reverse execution, and effectively its usability, is the frequency of checkpointing. More frequent checkpoints result in the application spending less time in deterministic-replay in order to restore the system to the desired point in time.

For reliability, once an error has been detected, the system has to recover and resume execution. A simplistic recovery approach would be to restart the executing program from the beginning, a solution that would have high cost, especially for long-running applications (e.g. weeks-long protein folding, drug interaction, nuclear explosion, etc. simulations). Restarting the program is not enough to guarantee completion of the execution, especially for cases where the error frequency is high. To improve the availability of the system, a common recovery approach is backwards error recovery, which relies on checkpointing. When an error gets detected, the program is restored to the most recent undamaged checkpoint and resumes execution from there, instead of re-executing the program from the beginning. Like reverse execution, in error recovery frequent checkpointing reduces the amount of time the application will have to waste recomputing the lost state, and thus improves the availability and the efficiency of the system.

# 1.3 Overview

Even though frequent checkpointing could deliver the desired reverse-execution interactivity and system availability results, it is generally associated with high performance and storage overheads. Such prohibitive overheads render bidirectional debugging a rarely used and not widely applied

debugging technique. Moreover, because of the expected increasing error rates [83] and the limitations of the current I/O infrastructure, the increased checkpointing requirements of future systems are expected to limit their scalability [61].

This dissertation proposes a number of different hardware accelerators for application and system memory checkpointing, with applications in reverse execution and system reliability. The system/application memory typically represents the biggest fraction of the state which needs to be checkpointed. All hardware accelerators which I propose aim to reduce both the performance and memory overheads, and construct memory checkpoints very often. The rest of this dissertation is organized as follows:

Chapter 2 provides an overview of the existing system and application checkpointing techniques.

Chapter 3 describes HARE and Euripus, two hardware assisted checkpointing mechanisms which aim to accelerate and reduce the performance and memory costs of bidirectional debugging. HARE and Euripus employ different mechanisms for keeping track of the modified memory and create different types of checkpoints. The primary goal of both techniques is to reduce the memory footprint of bidirectional debugging by enabling the consolidation of checkpoints. For this reason HARE creates redo-log checkpoints, which can be created to be ordered by address and thus efficiently consolidated, contrary to previous checkpointing techniques [68, 94] which use unordered undo-logs. In contrast of HARE, Euripus creates undo-log checkpoints, but uses a trie as its metadata data-structure for the checkpoints, instead of the commonly used list-of-addresses. This trie can be efficiently traversed in address-order which enables Euripus to consolidate the undo-log checkpoints. Euripus's meta-data data-structure also allows it to store and search for other information efficiently, enabling the mechanism to construct both types of checkpoints (undo and redo-log) simultaneously for limited additional cost. To accomplish this, Euripus exploits a number of synergies that develop when both types of checkpoints are being created. Moreover, Euripus's functionality is extended to track additional application information which can further accelerate bidirectional debugging. The different design decisions of the two techniques affect the hardware cost, performance/memory overheads, reverse-execution latency, as well as the additional functionality that each technique can support.

Chapter 4 discusses the Kyma hardware checkpoint accelerator, which approaches the problem of checkpointing from the perspective of reliability. Kyma is structurally similar to the Euripus accelerator, but has been adapted to the characteristics of checkpointing used in system reliability. In reliability, the goal is to improve the availability of the system by reducing its down-time. The down-time of a system consists of the time to restore the system state to the last checkpoint and the time to re-execute to the point of failure, and frequent checkpointing is required to minimize the re-execution time. At the same time, multiple and different types of checkpoints have to be maintained in order to enable the recovery from different types of errors (transient or permanent), as well as allow recovery from errors that escape early detection and corrupt the state of a number of checkpoints. For these reasons, Kyma creates both undo-log checkpoints at high frequencies (e.g. 10msec), for quick recovery from transient errors, and redo-log checkpoints less frequently (e.g. every 1sec), for recovery from permanent errors or errors that undo-log checkpoints cannot be used to recover from. When both types of checkpoints are being created, the potential overhead practically doubles and two memory tracking mechanisms are necessary. To reduce the performance cost, similarly to Euripus, Kyma takes advantage of the synergies of undo and redo-log checkpoints. This allows Kyma to eliminate the modification-tracking mechanism for creating redo-log checkpoints, as well as to reduce the overall memory bandwidth requirements and performance overhead. To represent the checkpoint meta-data, Kyma uses a data-structure similar to the one that Euripus maintains during checkpoint construction. Kyma also exploits checkpoint consolidation in order to create checkpoints at lower frequencies (e.g. 1 minute and 1 hour) at no additional memory copying cost. Those multiple levels of checkpoints allow the system to recover a lot more quickly by exploiting the frequent checkpoints and being able to fall-back to an older checkpoint when the system cannot recover the error using the latest checkpoint. Kyma also leverages fast non-volatile memory (e.g. PCM) to store frequently created checkpoints, thus overcoming the bandwidth limitations of other permanent storage solutions.

Finally, Chapter 5 presents the conclusions of this work.

# 1.4 Scope of this Dissertation

The main goal of my work is to demonstrate to the reader that specialized hardware accelerators, designed for constructing memory checkpoints, can efficiently reduce the performance overheads of software techniques and retain the benefits of software solutions, e.g. ability to consolidate checkpoints. The proposed solutions are evaluated through simulations that demonstrate the performance benefits, and analytical models have been used to show the impact of the proposed techniques in the reverse-execution latency that the user will experience during bidirectional debugging (HARE, Euripus) and the availability of the system (Kyma). The evaluation results demonstrate that through careful design the proposed accelerators provide the benefits of both hardware (low performance overhead) and software (low memory requirements) techniques.

## **CHAPTER II**

# **OVERVIEW OF MEMORY CHECKPOINTING TECHNIQUES**

### 2.1 Introduction to Checkpointing and Logging

This chapter presents an overview of checkpointing and logging techniques and how they are typically implemented. Checkpointing and logging have been studied across multiple fields. Their purpose is to record the modifications of the system over-time, with the intent to restore the system to a past point in time if needed.

A checkpoint is a consistent snapshot of the full state of the system (or an application) at a given point in time t. To create such a snapshot, the system pauses execution (to prevent any further modifications), copies all its state to a secondary location, and then resumes execution. To restore the system to a specific point in time (t), the snapshot taken at time t is copied back to the system's state.

Logging has a similar purpose to checkpointing, and is often used synonymously. However we can make a distinction: logging records the modifications of the state of a system over-time, e.g. as a set of records of the form <state\_id,value>. The state\_id can be, for example, an address, if the system is tracking modifications to memory, while the value can be either the old or the new value of the modified memory location. Based on the value recorded, old or new, the log can be used to "move" the system's state either to a past or to a future point in time.

Given these descriptions of checkpointing and logging, checkpointing appears to have higher performance overheads than logging, especially when performed frequently. Checkpointing typically needs the execution of the system to be paused for the checkpoint to be constructed, while logging records the modifications as they occur, with a less drastic impact on the system's/application's execution. To improve the performance of checkpointing, several techniques have been proposed that construct checkpoints incrementally, by checkpointing only the state of the system that has been modified during a checkpointing interval, and not the full state. Such an incremental checkpoint is similar to a log that has recorded the latest values of the modified state of the system. As a result,

| _          | Men                           | nory                         | Prog                                 | ram                            | Undo                     | o Log                   | Redo                     | o Log                         | <u> </u> |

|------------|-------------------------------|------------------------------|--------------------------------------|--------------------------------|--------------------------|-------------------------|--------------------------|-------------------------------|----------|

| Interval N | Addr<br>A<br>B<br>C<br>D<br>E | Val<br>1<br>2<br>3<br>4<br>5 | WR E<br>WR A<br>WR C<br>WR A<br>WR B | 10<br>1000<br>20<br>4000<br>40 | Addr<br>E<br>A<br>C<br>B | Val<br>5<br>1<br>3<br>2 | Addr<br>A<br>B<br>C<br>E | Val<br>4000<br>40<br>20<br>10 | T+1      |

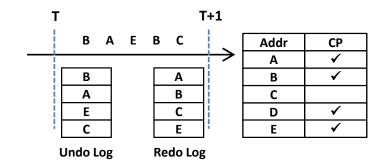

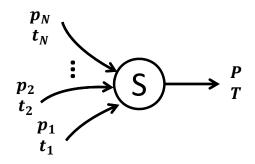

Figure 1: Example of undo and redo-log checkpoints

the terms checkpointing and logging have few differences, and in the rest of this thesis I am going to use these two terms interchangeably to denote a mechanism that records the set of changes needed to "move" the system's state to a specific point in time.

Checkpoints/logs can have three typical forms: First, there is the full checkpoint, which corresponds to the original definition of checkpointing: it saves the full state of the system as it was at the time when the checkpoint was created. Such a checkpoint is expensive, so it is typically created in order to establish a common starting point for incremental checkpoints. Second, a redo-log checkpoint (Figure 1) is an incremental checkpoint/log that records the latest values of the modified state of the system at the end of the checkpointing interval at time T+1. A redo-log checkpoint cannot by itself restore the system to time T+1, because it does not contain the full state of the system. Instead, a redo-log alone can only move the state of the system forward in time, from T to T+1. To restore the system to time T+1 from another point in time (not T) using redo-log checkpoints, the process has to start with a full checkpoint, and then apply all subsequent redo-log checkpoints in chronological order until time T+1. Finally, an undo-log checkpoint (Figure 1) records the oldest values of the modified state of the system during the checkpointing interval. Recording the oldest value during an interval allows the undo-log checkpoints to roll-back the system state from the end of the current interval (time T+1) to the beginning (time T). Undo log checkpoints can be used to restore the system to a more distant past state, e.g. to time T-3, by applying them in reverse chronological order. Like redo-log checkpoints, undo-log checkpoints also do not contain the full state of the system, so they require a valid state of the system as a starting point, but this starting point should be more recent than the "target" point. For this purpose, undo-logs can use the current state of the system, if it is consistent and undamaged. This gives them a significant advantage if the

"target" state is in the recent past relative to the current state of the system., e.g. when performing a rollback in case of an error or for reverse execution.

There are cases though, that the point in time t we want to restore the system/application to does not correspond to an existing checkpoint. In such a case the system is restored to the closest checkpoint in the past from time t, and the system re-executes until it reaches time t. The ability to restore the application to practically any point in time with the help of checkpoints has multiple applications. This dissertation focuses on two such applications of checkpointing: error recovery (reliability) and bidirectional debugging. In error recovery, after an error is identified, checkpoints are used to recover the system to a past or a future state, allowing the user to move to any point in time in the application's execution, and inspect how the program's values change over time.

### 2.2 Checkpoint Implementations

A checkpointing mechanism can be implemented with the assistance of the application, library, operating system, virtual machine, a dedicated hardware mechanism, or by some combination of these (e.g. hardware-assisted OS-based checkpointing). it should be noted that checkpoints at different levels of the HW/SW stack capture a different part of the system state and, if used alone, can be used only for recovering that specific subset of the system state.

**Application Level:** Checkpoints can be created at the application level through explicit application code [30, 52], with the assistance of compiler instrumentation [6, 15, 16], or with the help of a checkpointing library [17, 63–65]. In application-driven checkpointing [30, 52], the application periodically pauses computation and stores (e.g. to a file) any intermediate results it has generated. In case of a crash, the application can resume execution using the last saved data. Compiler-assisted checkpointing [6, 15, 16] relies on compiler instrumentation for creating checkpoints at intervals that minimize the overall checkpointed memory state [6], and enforces the consistency of checkpoints in multi-threaded applications [15, 16] with the help of the underlying run-time system. Library checkpointers [17, 63–65] attach to the application's code and keep track of the application's modified memory. A typical implementation [63] uses memory protection to identify the modified memory and create incremental undo-log checkpoints using the "copy-on-write" functionality provided to

the library by the underlying OS.

**Operating System Level:** Creating application checkpoints at the operating system level [95] relies on existing operating system mechanisms for keeping track the application's memory modifications. For example, to support bidirectional debugging, Flashback [95] establishes checkpoints of the executing application by creating "shadow clones" of the application using OS functionality similar to the "fork" system call. The "fork" system call creates a copy of the original application, and uses memory protection to copy, in a lazy fashion, the modified memory locations. Every "fork" creates a new checkpoint of the application that the debugger can use to recover the application to.

**Virtual Machine Level:** Checkpointing implemented using virtual machine functionality [23, 24, 80, 104] aims to provide reliability or bidirectional debugging functionality for the whole guest operating system. Similarly to how libraries or the kernel monitors the application's modifications, the virtual machine keeps track of the modified memory state and creates memory checkpoints, and also records any communication of the VM with the external environment. For the purpose of reliability, the state of the checkpointed VM can be replicated on another system [104], allowing non-interrupted operation if the original system experiences an error.

**Hardware Level:** Checkpointing at the hardware level [1, 36, 54, 68, 94] allows recovery of the whole system state, not just of a specific application or VM. Hardware assisted checkpointing generally incurs lower overheads comparing to checkpointing at higher levels of the system, and can create checkpoints more frequently. The performance advantage is due to the buffering and delayed copying, which enable hardware techniques [1,68,94] to efficiently create checkpoints in the background, without stopping the application's execution. Moreover, the finer tracking granularity, of blocks instead of pages, that hardware uses to track memory modifications, allows hardware to identify more precisely the modified memory locations, and avoid copying non-modified memory that a coarser tracking granularity might checkpoint. These optimizations dramatically reduce the performance overhead of hardware techniques.

# 2.3 Checkpoint Storage

Checkpoints and logs need to be stored in a location separate from the system's working data. When the checkpoints are used for recovering the system from errors, the storage medium used should have higher resiliency to errors than the part of the system that suffers the error. Checkpoints are typically stored in non-volatile memory, such as hard-disks [30], to survive power failures. Because checkpointed data are rarely accessed, access latency is not a primary concern. However, checkpointing can require non-negligible throughput. Disks for example, may provide limited bandwidth, increasing the construction time of checkpoints. For this reason massively parallel processing (MPP) systems, such as Blue Gene, use high bandwidth I/O subsystems [114]. In the future I/O bandwidth is expected to increase at a lower rate than the processor's computing power. This asymmetry in the system, if not solved, could cause future systems to spend more than 50% of the execution time in checkpointing [61].

To reduce the performance cost of checkpoint storage, some checkpointing techniques store checkpoints in memory [52, 65, 66, 68, 94]. This reduces the resiliency of the system to memory errors (e.g. a bit flip because of an alpha particle) and or power failures. To overcome this limitation in systems with multiple nodes, checkpoints are stored across multiple nodes using memory redundancy, e.g. N+1 memory parity or other error correcting codes [52, 65]. If a node of the system fails and there is a spare node, then the original memory state of the failed node can be reconstructed using the redundant memory information distributed across the other nodes of the system. Memory-cached checkpoints have lower performance cost than the ones stored on a hard-disk, and can significantly improve the performance of the system. Another proposed memory-based storage solution is to leverage future non-volatile memory technologies such as Phase Change Memory (PCM). Dong *et al.* [22] have demonstrated that the use of such memory technologies can overcome the limitations of checkpointing in future MPP systems.

Another approach to checkpoint storage is multi-level checkpointing [31,52,92,101,102], which creates different types of checkpoints, one cached on the nodes of the computing system in memory, and another one stored in disks. This approach allowed systems like the one proposed by Moody *et al.* [52] to exploit the benefits of both types of checkpoints. Memory-based checkpoints can be

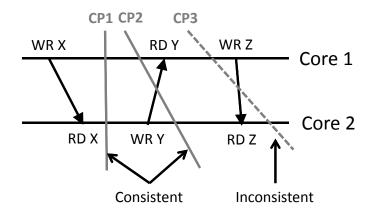

Figure 2: Examples of consistent and inconsistent checkpoints.

created frequently enough, satisfying the checkpointing requirements of future MPP systems, while checkpoints stored on disks can be constructed at a rate that the I/O subsystem can sustain, allowing the system to recover from errors that memory-based checkpoints cannot recover from, e.g. total power failures.

#### 2.4 Checkpointing of Multi-Processor Systems

Checkpointing faces another challenge in a system that has multiple computing elements, such as a distributed system, a multi-processor system, or a multi-threaded application. The challenge is how to create consistent checkpoints, especially when the processing elements of such systems communicate, e.g. through shared memory. Figure 2 shows two cores communicating through shared memory and examples of consistent and inconsistent checkpoints. The first and the second checkpoints (CP1 and CP2 respectively) are consistent checkpoints because, if the system is restored using from CP1 or CP2, the consumers of variables X and Y will not observe the modifications before they actually happen. On the other hand, the third checkpoint will not restore the system to a consistent state, because the second core will have an updated value of variable Z before the first core has actually performed the write.

Consistent checkpoints can be constructed using three methods:

**Global:** In global checkpointing [36, 47, 54, 55, 65, 66, 68, 94], all processors of the system periodically synchronize to create a single global checkpoint. The synchronization is typically implemented with the help of a two-phase commit protocol [91]. **Coordinated:** In coordinated checkpoints [1, 2, 4, 5, 66, 109], each processor creates checkpoints locally, while the system keeps track of the communication between the processors. When processor *A* decides to checkpoint, all other processors which have consumed values from *A* have to checkpoint as well. This approach creates a consistent checkpoint similar to checkpoints CP1 and CP2 in Figure 2.

**Uncoordinated:** In uncoordinated checkpointing [25,26,97,98], individual processors are also creating local checkpoints, but unlike coordinated checkpoints not all processors which have communicated are forced to create a checkpoint together. Interactions between processors are still recorded, similar to coordinated checkpointing, and this information is used only at recovery time. When processor *A* rolls back to a past state, all processors who consumed values from *A* are forced to roll-back as well. The advantage of this approach is that it eliminates the synchronization cost during checkpointing. The disadvantage is that, it is possible under some scenarios that the roll-backs might extend to the beginning of the computation, causing the system to start computation from the beginning, a phenomenon also known as *domino effect* [72].

# 2.5 Summary

This chapter presented an overview of the different checkpointing techniques and how they can be implemented at different levels of the system. It also highlighted the performance issues that have to be taken into consideration when creating checkpoints, and also the challenges that appear when designing checkpointing solutions for multi-processing systems. Chapters 3 and 4 discuss how these techniques are used for the purposes of bidirectional debugging and reliability respectively.

### **CHAPTER III**

# HARDWARE-ASSISTED BIDIRECTIONAL DEBUGGING

Debugging is an important and costly part of software development. It has been estimated [39] that debugging accounts for 60%–70% of the development effort and 80% of project overruns. It has also been estimated that in the early stages of development bugs cost an order of magnitude (50 to 200 times) [11] less to fix than in later stages. Much of the debugging time and effort is spent on back-tracking from the point where an error is manifested (e.g. the program crashes) to the point where the problem originated (e.g. an incorrect value was computed). Typical back-tracking consists of finding the variable directly responsible for error manifestation, finding where that variable was last modified, checking if that modification is a direct result of incorrect computation, and repeating this process if the modification simply propagates another incorrect value.

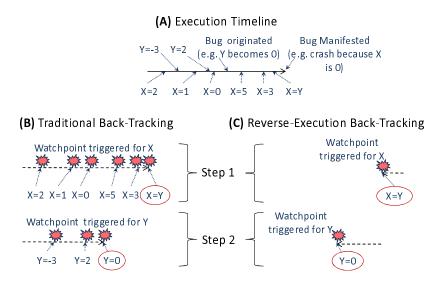

An example of buggy execution is shown in Figure 3(A), where a zero value in variable X causes the program to crash, e.g. with a divide-by-zero exception. Traditional back-tracking (Figure 3(B)) would involve placing a write watchpoint on X, re-running the program, inspecting the state of the program each time the watchpoint is triggered, and eventually finding the statement that placed the problematic value (zero) into X. In our example, this statement is simply "X=Y" so another backtracking step (with a write watchpoint on Y) is needed to find where Y became zero. In this example, the buggy code is the one that sets Y to zero, so back-tracking ends there and the programmer can start figuring out how to fix that code.

This traditional approach to back-tracking is both time-consuming and labor-intensive; multiple re-executions of the program may be needed (one for each back-tracking step), often with numerous programmer interactions in each re-execution (to inspect state whenever watchpoints are triggered). bidirectional debugging [12, 27, 80, 112] (also called reverse-debugging) has been proposed as a powerful technique to reduce both time and effort needed for back-tracking. In addition to (traditional) forward execution, bidirectional debugging aids back-tracking by also providing backward

Figure 3: Debugging example with back-tracking.

(reverse) execution. As shown in Figure 3(C), reverse-execution saves back-tracking time and effort. It saves time by only going through past execution once (not once per back-tracking step). It also saves effort, by involving the programmer only once in each back-tracking step (to inspect code that writes the watched variable).

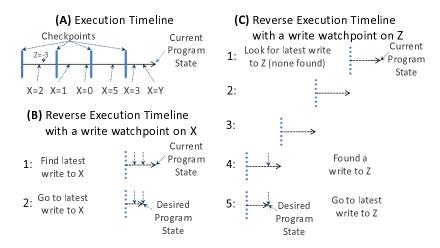

True reverse-execution is not supported in real processors and systems, so the *appearance* of reverse-execution is typically implemented using checkpointing and deterministic replay, as shown in Figure 4. Checkpoints are created periodically during forward execution (Figure 4(A)). For reverse-execution (Figure 4(B)), a prior checkpoint is restored, re-execution finds the latest occurrence of a watchpoint, the checkpoint is restored again, and in another re-execution we stop where the latest watchpoint was found. As shown in Figure 4(C), the most recent checkpoint interval may have no watchpoint occurrences. In this case, increasingly older checkpoint intervals are replayed until a watchpoint occurrence is found.

From the user's perspective, this checkpoint/replay implementation of reverse-execution is indistinguishable from "real" reverse execution if it has similar "speed" and "reach"<sup>1</sup> as forward execution. For "speed", the time needed to reverse some execution should be similar to the time that was needed to forward-execute it. For "reach", we should be able to reverse-execute from any point all the way to the start of the program, just like we can forward-execute all the way to the end.

<sup>&</sup>lt;sup>1</sup>Reverse-execution, its "speed", and its "reach" refer to what the user (of the debugger) perceives during bidirectional debugging.

Figure 4: Reverse-execution via checkpoint/replay.

Disproportionally long reverse-execution times and/or inability to reverse-execute far enough into the past are likely to frustrate programmers and cause them to revert to "traditional" debugging approaches. Ability to reverse long periods of execution is also needed for analysis of security attacks that may deliberately exploit bugs with long dormancy periods.

Unfortunately, "speed" and "reach" create conflicting demands for checkpointing frequency: "speed" needs frequent checkpointing so short periods of execution can be reversed quickly, but for "reach" checkpoints should be created rarely to retain a lot of checkpoints without running out of space. To achieve both goals, some software-only tools create checkpoints frequently (for short-term "speed" of reverse-execution) and then *consolidate* [12] them as they age (to conserve space over the long term). Unfortunately, software-only checkpointing approaches for reverse-execution [12, 23, 24, 27, 63, 79, 80, 95, 112] have large performance overheads (when checkpointing often enough for good "speed" of reverse-execution), and they cannot efficiently record memory races for deterministic replay of multi-core execution.

Hardware support has been proposed as a way to minimize performance overheads of checkpointing for error recovery [60, 68, 110] and, in combination with deterministic replay, for debugging [60, 69, 110]. Performance overheads are reduced mostly 1) by saving checkpoint data in the background and on-demand, as application execution modifies memory content, and 2) by tracking race outcomes in hardware. In recent years, memory space needed to record race outcomes has been reduced by multiple orders of magnitude [32, 51, 59, 111]. However, the total memory used for checkpoint storage is dominated by saving modified data blocks (Data Log in Figure 5), where hardware schemes could only reduce space consumption (typically by a factor of 2 to 3) using compression of individual checkpoints. In contrast, consolidation would result in orders-of-magnitude space reduction for data logs. Unfortunately, checkpoints produced by existing hardware schemes are not amenable to efficient consolidation because 1) consolidation of two checkpoints relies on finding and eliminating duplicate data blocks (those saved in both original checkpoints), which requires checkpoints to be sorted (or at least searchable) by data address, whereas 2) existing hardware schemes save data blocks on-demand, thus data blocks in each checkpoint are ordered by time of modification (or use), not by data address. As a result, these schemes must sacrifice space (by giving up on consolidation) or performance (by sorting checkpoints after they are created).

This chapter presents two hardware memory-checkpoint accelerators: HARE (Hardware-Assisted Reverse Execution) and Euripus. Both are low-cost hardware solutions which provide efficient checkpointing and enable *consolidation*. The two techniques follow different approaches regarding the type of checkpoints they create. I study the effects that this design decision has on the hardware requirements, the performance and checkpoint storage overheads, and the reverse-execution latency that each technique can achieve. I also propose techniques that leverage the additional functionality provided by the hardware in order to further accelerate reverse-execution. Overall, both techniques incur minimal performance overheads at high checkpointing frequencies, they reduce the memory requirements of long-running applications by more than an order of magnitude by using checkpoint consolidation, and they provide reverse-execution times similar to forward execution times for the same number of instructions.

The rest of this chapter reviews bidirectional debugging (Section 3.1), describes the HARE (Section 3.2) and Euripus (Section 3.4) techniques and their implementation details (Section 3.3 and Section 3.5 respectively), and finally presents a quantitative evaluation (Section 3.6) and conclusions (Section 3.7).

# 3.1 A Review of Bidirectional Debugging

In addition to commands for executing the application forward (step, continue, etc.), a bidirectional debugger also provides commands for reverse-execution (rstep, rcontinue, etc.). As described, reverse-execution is typically implemented by restoring a checkpoint and then forward-executing to the desired point, using the number of executed instructions to define "position" in the execution time-line. For example, if N instructions have been executed since the last checkpoint, a rstepi command (undo one instruction) causes the debugger to restore the last checkpoint and re-execute N-1 instructions. In some cases, the desired point is unknown a priori. A typical example (shown in Figure 4), is when the user (of the debugger) sets a write watchpoint on some variable and then uses a rcontinue command (reverse-execute until watchpoint is triggered). The desired point in this case is the most recent write to the watched variable(s). The example in Figure 4(B) shows a situation where the watchpoint is triggered while replaying (phase 1) the most recent checkpoint interval. In this phase, replay continues to find if an even more recent write exists in that checkpoint interval. Once the instruction count for the last write is ascertained, another replay of the same checkpoint interval (phase 2) is used to reach that point. Alternatively, the debugger creates temporary checkpoints as it finds each write in phase 1, then phase 2 consists of simply restoring the most recent temporary checkpoint. If the watchpoint is not triggered while replaying the most recent checkpoint interval (Figure 4(C)), the debugger replays progressively older intervals until it finds one where the watchpoint is triggered.

Assuming that checkpoints can be restored as quickly as they can be created, and assuming that replay is as quick as original forward execution, the time needed for reverse-execution will be equal to the time that was needed for the same execution in the forward direction, plus the time to restore and replay the rest of the target checkpoint interval (once if no temporary checkpoints are created, twice otherwise). Therefore, the "speed" of reverse and forward execution will be similar if the target checkpoint interval is relatively short compared to the amount of execution being reversed. For small amounts of reverse-execution, e.g. reverse-executing only a few instructions, recent checkpoint intervals must be very short (so their replay appears instantaneous), thus leading to very frequent checkpointing (at least several times per second). On the other hand, long-range reverse-execution achieves good "speed" even with longer checkpoint intervals.

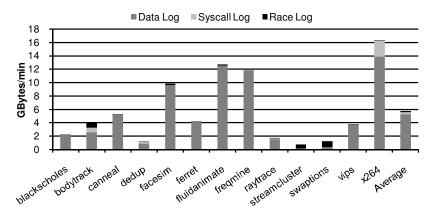

Frequent checkpointing that can provide good "speed" for small amounts of reverse-execution leads, over long periods of execution, to huge space overheads. To illustrate this, Figure 5 shows, for 8-threaded execution of PARSEC 2.0 benchmarks, the rate (in GBytes/minute) at which space is consumed by checkpoints when they are created whenever 1 billion instructions are executed

Figure 5: Space used for frequent checkpointing.

(by all threads, resulting in 10-30 checkpoints per second) without using consolidation. We see that facesim, fluidanimate, freqmine, and x264 consume more than 10 GBytes per minute, so good "reach" of reverse-execution would be infeasible for long-running applications (e.g. hours of execution time) with similar memory access patterns.

The checkpointing space requirements in Figure 5 are broken down into checkpointed data (Data Log), system event logs for deterministic replay (Syscall Log), and race logs for deterministic replay of multi-threaded execution (Race Log). Data Log and Race Log sizes are obtained by modeling the approach used in FDR [110], but without using compression (which typically can only reduce these space requirements by a factor of 2 to 3). We observe that Data Log (checkpoints themselves) is the dominant component (by far). This may seem to contradict recent research in deterministic replay, which focuses almost exclusively on reducing Race Log sizes [32, 51, 59, 111], especially knowing that PARSEC is not as I/O intensive as commercial workloads used to evaluate work that focused on recording races and *non-deterministic system events* (such as I/O) [79, 95, 110]. However, results presented for commercial workloads by Xu et al. [110] lead to similar conclusions (data logs are the dominant component).

As described previously, frequently taken checkpoints are only needed to achieve good "speed" for reversing small amounts of execution, and long-range reverse-execution can achieve good "speed" using checkpoints that are further apart from each other. Some software schemes for bidirectional debugging [12] build on this insight by using *checkpoint consolidation* to dramatically reduce the to-tal space consumed by checkpoints, while retaining good "speed" for short-range reverse-execution.

With consolidation, incremental checkpoints are created often, for "speed" of short-term reverseexecution, but are then merged as they age into progressively coarser-grained checkpoints to reduce space requirements while still supporting good "speed" of long-term reverse-execution.

A consolidated checkpoint is the union of its input checkpoints, but without duplicates (data blocks present in both input checkpoints). To efficiently find duplicates during consolidation, checkpoints must be searchable by data address or, preferably, arranged by address so a single merging pass can eliminate all duplicates. This is relatively easy to achieve in software schemes, which can use sophisticated data structures (e.g. search trees) to facilitate checks for duplicates. Additionally, many such schemes identify changes at page granularity [12,27,63,80,95], so there are fewer saved records to search or sort than in schemes with finer (e.g. cache block or even word) granularity.

In contrast, hardware checkpointing schemes [60, 68, 94, 110] dramatically reduce performance overheads of checkpointing by saving data on-demand (without stopping the application) and at finer (typically cache-block) granularity. Sophisticated data structures would result in increased costs, so these schemes simply write out data blocks to a contiguous log in memory as each block is modified (in BugNet [60], when modified data is used for the first time). This results in checkpoint logs with many fine-grain entries that are not sorted by address. Unfortunately, this prevents efficient consolidation: these logs cannot be searched for duplicates efficiently, and sorting them is either time-consuming (if sorting in software) or requires expensive sorting hardware. It should be noted that some hardware solutions [60,94] compress checkpoints, which typically reduces space requirements by a factor of 2 to 3. In contrast, as will be shown in Section 3.6.6, if efficient consolidation could be supported it would provide orders-of-magnitude reduction is total space requirements.

# 3.2 HARE: Hardware Assisted Reverse Execution

As explained in Section 3.1, to support efficient consolidation we must either 1) sort checkpoints by address after they are created, 2) create checkpoints that are already sorted by address, or 3) use meta-data structures that can be efficiently traversed in order of addresses. Sorting is timeconsuming if done in software, and expensive if done in hardware. In HARE, I investigate the second option, i.e. a mechanism that can create already-sorted checkpoints by address.

To efficiently create such a checkpoint, one must 1) know which blocks will be saved before we

| (A)          | Execution Timeline | <b>(B)</b> Undo Log Activity | (C) Redo Logging Activity             |  |  |  |

|--------------|--------------------|------------------------------|---------------------------------------|--|--|--|

| 1            | Checkpoint C       |                              |                                       |  |  |  |

|              | WR X               | Save old X, Mark X as Saved  | Mark X as modified                    |  |  |  |

|              | WR Y               | Save old Y, Mark Y as Saved  | Mark Y as modified                    |  |  |  |

|              | WR X               | No action (X already saved)  | No action (X already marked)          |  |  |  |

|              | WR Z               | Save old Z, Mark Z as Saved  | Mark Z as modified                    |  |  |  |

|              | WRY                | No action (Y already saved)  | No action (Y already marked)          |  |  |  |

| $\downarrow$ | Checkpoint C+1     | Start new undo log for C+1   | Save X, Y, and Zinto redo log for C+1 |  |  |  |

|              |                    |                              |                                       |  |  |  |

Figure 6: Checkpointing with undo and with redo logs.

actually save any of them, and at that time 2) efficiently discover these modified blocks in order of address and save them without stopping the execution of the application. The undo-log approach used in prior hardware schemes [68, 94] is incompatible with the first requirement. Figure 6(A) shows an example execution and Figure 6(B) shows the corresponding undo log activity, which saves each old data value just before it is overwritten for the first time in this checkpoint interval. Because data is actually saved during the checkpoint interval, the next checkpoint (Checkpoint C+1) is "created" by simply marking the position in the undo log (or by starting a new log). To restore a prior checkpoint, one would simply restore to memory all values saved since that checkpoint, starting with most recent log entries. However, the entire set of modified blocks is known only at the end of the checkpoint interval – after data from all these blocks is already read out from memory and saved to the log. To produce a sorted checkpoint, considerable on-chip resources would be needed to buffer these blocks (or at least records that contain pointers to saved blocks), as well as expensive hardware to sort these records by address before they can be written out as a sorted undo log. Note that BugNet [60] does not use undo logs, but its logs are sorted by time of first read and thus suffer from similar limitations when it comes to consolidation.

Due to these considerations, for the HARE scheme I forgo undo-log and loaded-value-log approaches, and use redo logs instead. Redo-logging for the execution example in Figure 6(A) is shown in Figure 6(C). A redo-log contains *new* values for modified data, recorded at the end of the checkpoint interval when the set of blocks that must be saved is known and can be written to the log in order of original address. However, redo-logs present two main challenges that should be addressed. First, it is needed to track blocks that are modified during the checkpoint interval and efficiently save these modified blocks (in order of data address) when actually creating the checkpoint. Second, redo-logs can directly support a *roll-forward* from older to newer checkpoints, not

Figure 7: Modification tracking bits (shown in gray).

*roll-back* from newer to older checkpoints that is needed to provide reverse-execution.

The rest of this section describes HARE's modification-tracking approach, our checkpoint creation approach, how to roll back to past checkpoints created by HARE, how redo logs can be efficiently consolidated, and how logs are organized to reduce memory bandwidth needed for consolidation.

#### 3.2.1 Memory Modification Tracking

Creation of checkpoint C+1 involves saving new values of all blocks that were modified between checkpoint C and checkpoint C+1. To track which blocks were modified, HARE uses a packed bit-array with a "modified" flag (bit) for each memory block in the application's address space, and keeps, looks-up, and updates these per-block bits using a MemTracker-like approach [103].

When creating a checkpoint, a linear search of this bit-array can discover modified blocks in order of their (virtual) address. However, checkpoints will be created often, so only a small fraction of blocks in the entire address space is modified, and blocks that are modified tend to be clustered (because of spatial locality of writes in the application). This means that a linear search of the bit-array would be time-consuming, with most of that time spent scanning through bits that correspond to unmodified blocks.

To improve efficiency of the search for modified blocks, HARE also marks modifications in page tables and TLBs by using an additional dirty bit in each page table (and TLB) entry. Figure 7 shows an example with hierarchical page tables (a page table with only two levels is shown for clarity). When creating a checkpoint, modified pages can be found by identifying modified entries in outer levels, descending towards inner levels for such entries, and eventually searching only the parts of the bit-array that correspond to pages marked as modified. HARE clears "modified" bits

in page table entries and the bit-array as it discovers them and saves the blocks they indicate, so when a checkpoint is created the same bits can be used to track modified blocks for the next one. Overall, for each modified page at most one page table node at each level is examined (e.g. 4 nodes for 4-level page tables) and tens of bits in the bit-array (e.g. 64 bits for 4kB page size and 64-byte blocks). Since each modified page contains at least one modified data block that must be copied to the checkpoint, the scan for modified blocks represents only a small fraction (<2%) of the total time and memory bandwidth used for checkpointing.

To simplify HARE's hardware support, it uses a software handler to discover modified pages and create a list of such pages. The hardware checkpointing support then reads this list, scans corresponding parts of the bit-array, and saves discovered blocks to the checkpoint's data log. Note that, as an alternative to using additional page table bits and the bit-vector array, the modification tracking could also be implemented with a single hierarchical meta-data structure, e.g. HARE can use a trie structure from Mondrian Memory Protection [108] with "modified" bits at each level to quickly zero in on modified blocks. The choice of the specific mechanism to track modified blocks is largely orthogonal to the design of our checkpointing and consolidation support, the use of such a data-structure is demonstrated in Euripus (Section 3.4)

#### 3.2.2 Checkpoint Creation