# **RADIO FREQUENCY AND MILLIMETER WAVE CIRCUIT COMPONENT DESIGN WITH SIGE BICMOS TECHNOLOGY**

A Dissertation Presented to The Academic Faculty

by

Yunyi Gong

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2020

# COPYRIGHT © 2020 BY YUNYI GONG

## **RADIO FREQUENCY AND MILLIMETER WAVE CIRCUIT COMPONENT DESIGN WITH SIGE BICMOS TECHNOLOGY**

Approved by:

Dr. John D. Cressler, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Farrokh Ayazi School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Hua Wang School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Shaolan Li School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Taiyun Chi Electrical and Computer Engineering *Rice University*

Date Approved: December 2<sup>nd</sup>, 2020

### ACKNOWLEDGEMENTS

I would like to thank my advisor Dr. John D. Cressler for his unwavering support and mentorship throughout my years as his student. His research philosophy and attitude towards life guided me through the difficult times in my Ph.D. journey and will continue to be the beacons that illuminate my career ahead.

I would like to thank Dr. Farrokh Ayazi and Dr. Hua Wang for taking the time to serve on my thesis reading committee. I am grateful for their encouragement and valuable feedback on my work. I would also like to thank Dr. Shaolan Li and Dr. Taiyun Chi for their time and efforts serving on my defense committee.

I am grateful to Mike McPartlin and Dr. Paul Huang from Skyworks Solutions Inc. for their financial and technical support. The collaboration with them and the internships with Skyworks have offered me valuable training and experience. I would like to thank Dr. Edward Gebara for his patient guidance during my collaborative project with NANOWAVE Technologies Inc. I would also like to thank Dr. Tummala Rao and Dr. Venky Sandaram from Georgia Tech 3D System Packaging Research Center for their support at the beginning of my graduate studies. I am also thankful for the generously amount of free wafer fabrication space provided by GlobalFoundries and TowerJazz, without which this research would not have been possible. I would like to thank the members of TSRB and GEDC staff, especially Daniel, Maria, Alison, David, and Scott, for all their support over the years. I would not have made this far without the help and support of my friends and colleagues in the SiGe Devices and Circuits group. I would like to thank Peter, Michael, and Saeed for their mentorship during my first few years in the group. I would also like to thank Moon-Kyu, Ickhyun, Inchan, Milad, Sunil, Cliff, Seokchul, Nelson, Zach, Adrian, Jeff, Brian, Uppili, Anup, Victor, and Harrison, for the teaching, collaboration, and support over the years.

Lastly, I would like to thank friends and family. Their words of encouragement and company never failed to cheer me up and help me through the difficult time. I am particularly thankful to Taiyun, Sensen, Tso-Wei, and Tzu-Yuan from GEMS group and Hang from the SPC research lab for the countless hotpot and BBQ parties together. There is no pain in the world that cannot be healed by a hefty meal with them.

# **TABLE OF CONTENTS**

| LIST OF TABLESviiLIST OF FIGURESviiiSUMMARYxvCHAPTER 1. Introduction11.1 Silicon-Based Radio Frequency and Millimeter Wave Technologies11.2 Technology Device Performance Comparison21.2.1 Device Noise Performance for Low Noise Amplifier (LNA) Design41.2.2 Device Comparison for RF and mm-wave Switch Applications71.2.3 Breakdown Voltage of Advanced RF-CMOS and SiGe BiCMOS111.2.4 Unique Design Concerns for Using Bipolar Technologies121.2.5 Other Advantages of SiGe BiCMOS over RF CMOS Technologies141.3 Organization15CHAPTER 2. Bi-Directional Amplifiers172.1 Introduction172.2 A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS ActiveDouble-Pole Double-Throw (DPDT) Switches182.2.1 Circuit Design282.3.1 Circuit Design282.3.1 Circuit Design282.3.1 Circuit Design302.3.3 Discussion34CHAPTER 3. Broadband Logarithmic Power Detector443.1 Introduction443.2 Circuit Design463.3 Measurement Results302.3.4 Summary55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1 Introduction574.2 A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1 Circuit Design604.2.2 Measurement Results613.4 Summary55CHAPTER 4. Millimeter-Wave Switch | ACKNOWLEDGEMENTS                                                         | iii  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|

| SUMMARYxvCHAPTER 1. Introduction11.1Silicon-Based Radio Frequency and Millimeter Wave Technologies11.2Technology Device Performance Comparison21.2.1Device Noise Performance for Low Noise Amplifier (LNA) Design41.2.2Device Comparison for RF and mm-wave Switch Applications71.2.3Breakdown Voltage of Advanced RF-CMOS and SiGe BiCMOS111.2.4Unique Design Concerns for Using Bipolar Technologies121.2.5Other Advantages of SiGe BiCMOS over RF CMOS Technologies141.3Organization172.1Introduction172.1Introduction172.2A Bi-Directional Amplifiers172.1Circuit Design192.2.2Measurement Results222.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using NeutralizedCommon-Emitter Differential Pair282.3.1Circuit Design302.3.3Discussion34CHAPTER 3. Broadband Logarithmic Power Detector443.4Summary55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results603.4Summary55                                                                                                                                                               | LIST OF TABLES                                                           | vii  |

| CHAPTER 1.Introduction11.1Silicon-Based Radio Frequency and Millimeter Wave Technologies11.2Technology Device Performance Comparison21.2.1Device Noise Performance for Low Noise Amplifier (LNA) Design41.2.2Device Comparison for RF and mm-wave Switch Applications71.2.3Breakdown Voltage of Advanced RF-CMOS and SiGe BiCMOS111.2.4Unique Design Concerns for Using Bipolar Technologies121.2.5Other Advantages of SiGe BiCMOS over RF CMOS Technologies15CHAPTER 2.Bi-Directional Amplifiers172.1Introduction172.2A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS ActiveDouble-Pole Double-Throw (DPDT) Switches2.2.1Circuit Design192.2.2Measurement Results222.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using NeutralizedCommon-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology 574.1Introduction574.2A compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design574.2.1Circuit Design574.2.2Measurem                                                                | LIST OF FIGURES                                                          | viii |

| 1.1Silicon-Based Radio Frequency and Millimeter Wave Technologies11.2Technology Device Performance Comparison21.2.1Device Noise Performance for Low Noise Amplifier (LNA) Design41.2.2Device Comparison for RF and mm-wave Switch Applications71.2.3Breakdown Voltage of Advanced RF-CMOS and SiGe BiCMOS111.2.4Unique Design Concerns for Using Bipolar Technologies121.2.5Other Advantages of SiGe BiCMOS over RF CMOS Technologies141.3Organization15CHAPTER 2.Bi-Directional Amplifiers172.1Introduction172.2A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS Active19Double-Pole Double-Throw (DPDT) Switches182.2.1Circuit Design292.2.2Measurement Results222.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using NeutralizedCommon-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                       | SUMMARY                                                                  | XV   |

| 1.2Technology Device Performance Comparison21.2.1Device Noise Performance for Low Noise Amplifier (LNA) Design41.2.2Device Comparison for RF and mm-wave Switch Applications71.2.3Breakdown Voltage of Advanced RF-CMOS and SiGe BiCMOS111.2.4Unique Design Concerns for Using Biolar Technologies121.2.5Other Advantages of SiGe BiCMOS over RF CMOS Technologies141.3Organization15CHAPTER 2.Bi-Directional Amplifiers172.1Introduction172.2A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS Active19Double-Pole Double-Throw (DPDT) Switches182.2.1Circuit Design292.2.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using NeutralizedCommon-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.1Introduction443.2Circuit Design453.3Measurement Results493.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results <td< td=""><td></td><td></td></td<>                                                                        |                                                                          |      |

| 1.2.1Device Noise Performance for Low Noise Amplifier (LNA) Design41.2.2Device Comparison for RF and mm-wave Switch Applications71.2.3Breakdown Voltage of Advanced RF-CMOS and SiGe BiCMOS111.2.4Unique Design Concerns for Using Bipolar Technologies121.2.5Other Advantages of SiGe BiCMOS over RF CMOS Technologies141.3Organization15CHAPTER 2. Bi-Directional Amplifiers172.1Introduction172.2A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS Active18Double-Pole Double-Throw (DPDT) Switches182.2.1Circuit Design192.2.2Measurement Results222.2.3Summary282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3. Broadband Logarithmic Power Detector3.4Summary55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology 574.1Introduction574.2.1Circuit Design604.2.2Measurement Results55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology 574.2.1Circuit Design604.2.2Measurement Results574.2.1Circuit Design604.2.2Measurement Results574.2.1Circuit Design604.2.2Measurement Results <td< th=""><th></th><th></th></td<>                                                                                                               |                                                                          |      |

| 1.2.2Device Comparison for RF and mm-wave Switch Applications71.2.3Breakdown Voltage of Advanced RF-CMOS and SiGe BiCMOS111.2.4Unique Design Concerns for Using Bipolar Technologies121.2.5Other Advantages of SiGe BiCMOS over RF CMOS Technologies141.3Organization15CHAPTER 2. Bi-Directional Amplifiers172.1Introduction172.2A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS Active19Double-Pole Double-Throw (DPDT) Switches182.2.1Circuit Design192.2.2Measurement Results222.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using NeutralizedCommon-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2.1Circuit Design604.2.2Measurement Results574.2.1Circuit Design604.2.2Measurement Results574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                    | 80 1                                                                     |      |

| 1.2.3Breakdown Voltage of Advanced RF-CMOS and SiGe BiCMOS111.2.4Unique Design Concerns for Using Bipolar Technologies121.2.5Other Advantages of SiGe BiCMOS over RF CMOS Technologies141.3Organization15CHAPTER 2.Bi-Directional Amplifiers172.1Introduction172.2A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS Active18Double-Pole Double-Throw (DPDT) Switches182.2.1Circuit Design192.2.2Measurement Results222.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using NeutralizedCommon-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology 574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes 574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                        | · · · · · · · · · · · · · · · · · · ·                                    |      |

| 1.2.4Unique Design Concerns for Using Bipolar Technologies121.2.5Other Advantages of SiGe BiCMOS over RF CMOS Technologies141.3Organization15CHAPTER 2.Bi-Directional Amplifiers172.1Introduction172.2A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS Active18Double-Pole Double-Throw (DPDT) Switches182.2.1Circuit Design192.2.2Measurement Results222.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using Neutralized28Common-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.1Introduction463.3Measurement Results493.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                           | 1 11                                                                     |      |

| 1.2.5Other Advantages of SiGe BiCMOS over RF CMOS Technologies141.3Organization15CHAPTER 2.Bi-Directional Amplifiers172.1Introduction172.2A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS Active18Double-Pole Double-Throw (DPDT) Switches182.2.1Circuit Design192.2.2Measurement Results222.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using NeutralizedCommon-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.1Introduction463.3Measurement Results493.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                          |      |

| 1.3Organization15CHAPTER 2.Bi-Directional Amplifiers172.1Introduction172.2A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS Active19Double-Pole Double-Throw (DPDT) Switches182.2.1Circuit Design192.2.2Measurement Results222.3.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using Neutralized28Common-Emitter Differential Pair292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.1Introduction443.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                          |      |

| CHAPTER 2.Bi-Directional Amplifiers172.1Introduction172.2A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS Active19Double-Pole Double-Throw (DPDT) Switches182.2.1Circuit Design192.2.2Measurement Results222.3.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using NeutralizedCommon-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.1Introduction443.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | e e                                                                      |      |

| 2.1Introduction172.2A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS Active18Double-Pole Double-Throw (DPDT) Switches182.2.1Circuit Design192.2.2Measurement Results222.2.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using Neutralized28Common-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.1Introduction443.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.3 Organization                                                         | 15   |

| 2.1Introduction172.2A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS ActiveDouble-Pole Double-Throw (DPDT) Switches182.2.1Circuit Design192.2.22.2.2Measurement Results222.2.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using Neutralized28Common-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.1Introduction443.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CHAPTER 2. Bi-Directional Amplifiers                                     | 17   |

| Double-Pole Double-Throw (DPDT) Switches182.2.1Circuit Design192.2.2Measurement Results222.2.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using Neutralized28Common-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.1Introduction443.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •                                                                        | 17   |

| Double-Pole Double-Throw (DPDT) Switches182.2.1Circuit Design192.2.2Measurement Results222.2.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using Neutralized28Common-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.1Introduction443.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.2 A Bi-Directional, X-Band 6-Bit Phase Shifter with SiGe BiCMOS Active |      |

| 2.2.2Measurement Results222.2.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using Neutralized28Common-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.1Introduction443.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                          | 18   |

| 2.2.3Summary282.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using Neutralized28Common-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3.Broadband Logarithmic Power Detector443.1Introduction443.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                          | 19   |

| 2.3A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using NeutralizedCommon-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3. Broadband Logarithmic Power Detector443.1Introduction3.4Summary463.3Measurement Results493.4Summary55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | e e                                                                      | 22   |

| Common-Emitter Differential Pair282.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3. Broadband Logarithmic Power Detector443.1Introduction3.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.2.3 Summary                                                            | 28   |

| 2.3.1Circuit Design292.3.2Measurement Results302.3.3Discussion34CHAPTER 3. Broadband Logarithmic Power Detector3.1Introduction443.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.3 A 28 GHz Switchless, SiGe Bi-Directional Amplifier Using Neutralized |      |

| 2.3.2Measurement Results302.3.3Discussion34CHAPTER 3. Broadband Logarithmic Power Detector3.1Introduction443.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Common-Emitter Differential Pair                                         | 28   |

| 2.3.3 Discussion34CHAPTER 3. Broadband Logarithmic Power Detector443.1 Introduction443.2 Circuit Design463.3 Measurement Results493.4 Summary55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1 Introduction574.2 A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1 Circuit Design604.2.2 Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.3.1 Circuit Design                                                     | 29   |

| CHAPTER 3. Broadband Logarithmic Power Detector443.1 Introduction443.2 Circuit Design463.3 Measurement Results493.4 Summary55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1 Introduction574.2 A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1 Circuit Design604.2.2 Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.3.2 Measurement Results                                                | 30   |

| 3.1Introduction443.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.3.3 Discussion                                                         | 34   |

| 3.1Introduction443.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CHAPTER 3 Broadband Logarithmic Power Detector                           | 44   |

| 3.2Circuit Design463.3Measurement Results493.4Summary55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                        |      |

| 3.3Measurement Results493.4Summary55CHAPTER 4. Millimeter-Wave Switch Design with SiGe BiCMOS Technology4.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                          |      |

| 3.4Summary55CHAPTER 4.Millimeter-Wave Switch Design with SiGe BiCMOS Technology574.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                        |      |

| 4.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                          |      |

| 4.1Introduction574.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CHAPTER 4 Millimeter-Wave Switch Design with SiCe RiCMOS Technology      | 57   |

| 4.2A Compact High-Power SPDT Switch Using Shut-Series SiGe PIN Diodes574.2.1Circuit Design604.2.2Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8 8                                                                      |      |

| 4.2.1 Circuit Design604.2.2 Measurement Results62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                          |      |

| 4.2.2 Measurement Results 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 0 0                                                                    |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | e                                                                        |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                          |      |

| 4.3 MM-Wave Switch Using Reverse-Saturated SiGe HBTs in Grounded |     |

|------------------------------------------------------------------|-----|

| Emitter (GE) vs. Floating Emitter (FE) Configurations            | 67  |

| 4.3.1 TCAD Simulation and Test Structure Design                  | 68  |

| 4.3.2 Measurement Results and Observations                       | 71  |

| 4.4 Summary                                                      | 79  |

| CHAPTER 5. A High-Power 60 GHz SiGe Balanced Power Amplifier     | 81  |

| 5.1 Introduction                                                 | 81  |

| 5.2 Circuit Design                                               | 83  |

| 5.2.1 Three-Conductor T-Line Wilkinson Balun                     | 84  |

| 5.2.2 Three-Conductor T-Line Asymmetric Coupler                  | 91  |

| 5.2.3 Power Cell Design                                          | 95  |

| 5.3 Experiment Results                                           | 101 |

| 5.4 Summary                                                      | 107 |

| CHAPTER 6. Conclusion                                            | 108 |

| 6.1 Summary of Contributions                                     | 108 |

| 6.2 Future Work                                                  | 110 |

| REFERENCES                                                       | 112 |

# LIST OF TABLES

| Table 1.1 | - Relative Performance Comparisons of Various Device Technologies<br>for RFICs (Excellent: ++; Very good: +; Good: 0; Fair: -; Poor:) [9] | 3   |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.1 | - Performance Comparison of X-Band Phase Shifters                                                                                         | 27  |

| Table 2.2 | - Performance Comparison of Switchless BDAs                                                                                               | 34  |

| Table 3.1 | - Performance Comparison of Power Detectors                                                                                               | 55  |

| Table 4.1 | - Performance Comparison with mm-wave SPDT Switches [4]                                                                                   | 66  |

| Table 5.1 | - Performance Comparison with SOA Millimeter-wave PAs                                                                                     | 106 |

## LIST OF FIGURES

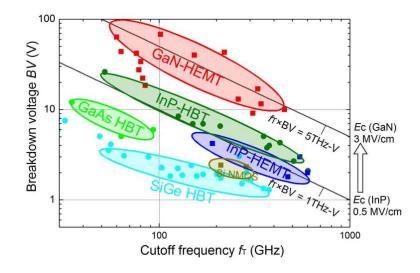

- Figure 1.1 A technology survey in 2013 comparing the state-of-the-art 3 semiconductor technologies in the breakdown voltage vs.  $f_T$  trade space [16] © 2013 IEEE.

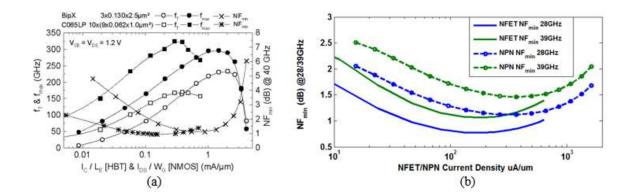

- Figure 1.2 (a) Measured *fT*, *fMAX* and *NFmin* at 40 GHz vs. current density for 5

BipX and 65 nm LP NMOS [20] © 2006 IEEE, and (b) *NFmin* comparison between GLOBALFOUNDRIES 40 nm 45RFSOI and 130 nm SiGe HBT [23] © 2018 IEEE.

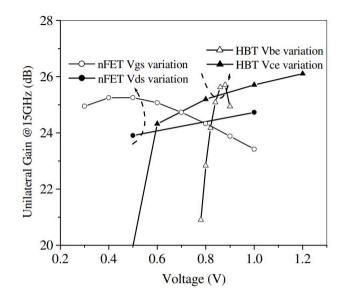

- Figure 1.3 Comparison of unilateral gain vs.  $V_{gs}$  ( $V_{be}$ ) and  $V_{ds}$  ( $V_{ce}$ ) between a 6 130 nm SiGe BiCMOS and 90 nm bulk RF CMOS technology [26] © 2004 IEEE.

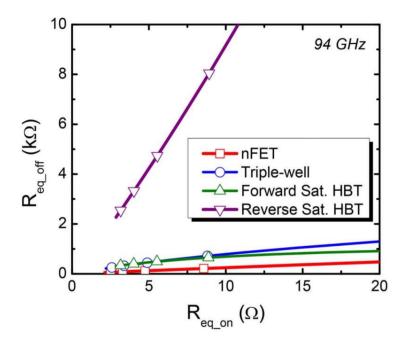

- Figure 1.4 Comparison of equivalent OFF impedance vs. ON impedance for available shunt switching device configurations in GlobalFoundries 90 nm 9HP SiGe BiCMOS technology at 94 GHz [30] © 2014 IEEE.

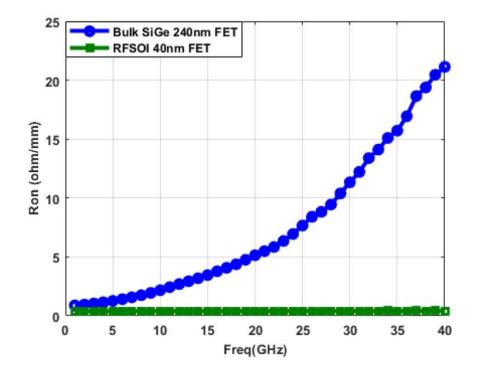

- Figure 1.5 Measured effective *R<sub>ON</sub>* comparison of BiCMOS 240 nm FET (blue) 9 and 45RFSOI 40 nm FET (green) [23] © 2018 IEEE.

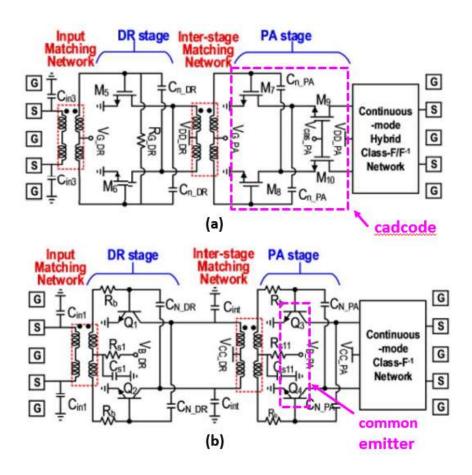

- Figure 1.6 Two mm-wave 5G power amplifier design with similar design 10 concept, output power, efficiency, and gain in (a) a 45 nm RFSOI and (b) a 130 nm SiGe BiCMOS [41] © 2019 IEEE.

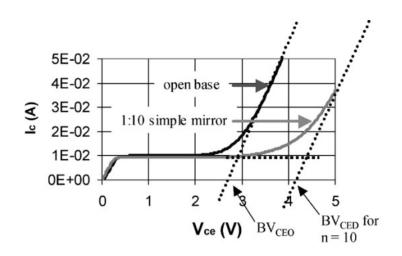

- Figure 1.7 I<sub>C</sub> vs. V<sub>ce</sub> of a 250 nm QUBiC4G SiGe HBT bias with open base and 12 1:10 simple current mirror [48] © 2005 IEEE.

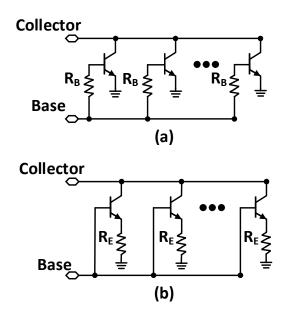

- Figure 1.8 Schematic of HBT arrays with(a) base ballasting and (b) emitter 13 ballasting.

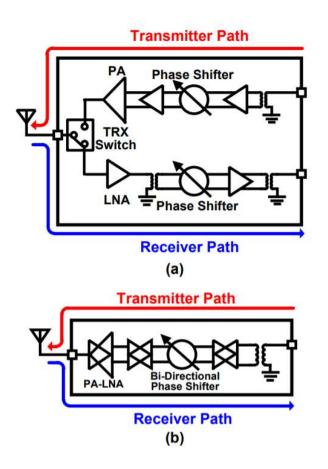

- Figure 2.1 (a) Conventional bi-directional beamformer and (b) bi-directional 17 beamformer with BDA [59] © 2020 IEEE.

- Figure 2.2 Simplified schematic of passive DPDT switch. 19

- Figure 2.3 The schematic of SiGe active DPDT proposed in [68] © 2016 IEEE. 19

- Figure 2.4 Effective circuit when signal configured to flow from P1 to P4 [68] 20 © 2016 IEEE.

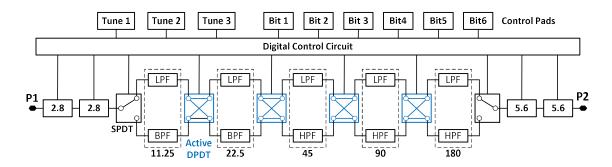

- Figure 2.5 The proposed 6-bit phase shifter using bi-directional active DPDT 21 switches, with three additional tuning bits © 2017 IEEE.

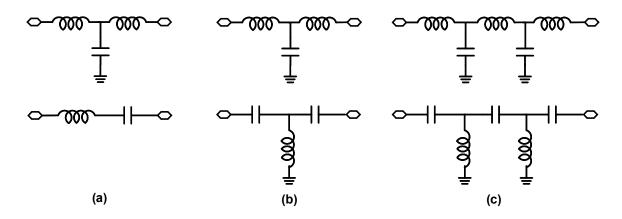

- Figure 2.6 Filter networks used for (a) 11.25° and 22.5° bits, (b) 45° and 90° bits, 22 and (c) 180° bit. A compact L-band broadband 6-bit.

- Figure 2.7 LSB and tuning bit design with SPDT switch. 22

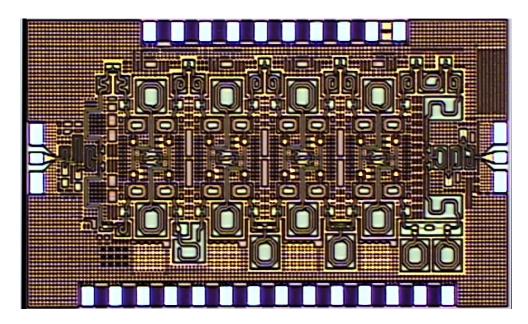

- Figure 2.8 Microphotograph of the X-band 6-bit phase shifter [1] © 2017 IEEE. 23

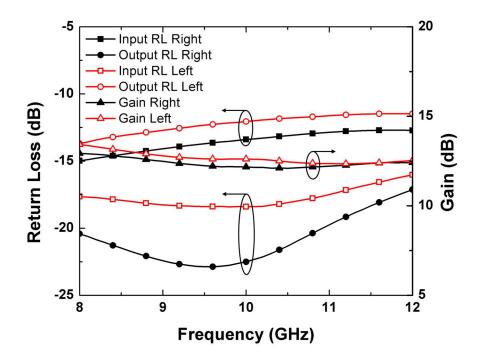

- Figure 2.9 Input and output return loss and gain of the reference state in the 24 forward and backward operations [1] © 2017 IEEE.

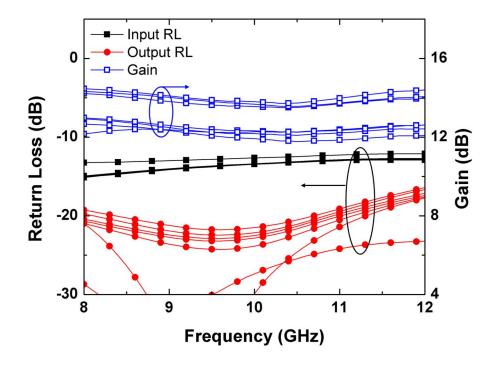

- Figure 2.10 Input and output return loss and gain of the major states for the 24 forward operation [1] © 2017 IEEE.

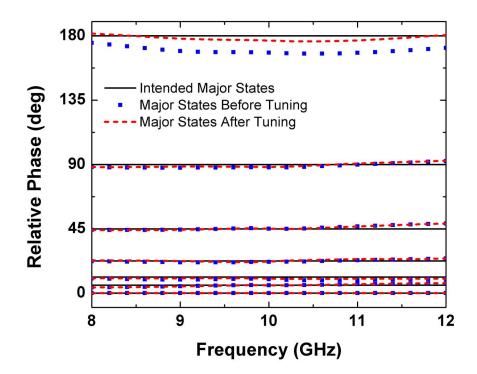

- Figure 2.11 Reference phase and measured major relative phase before and after 25 bit tuning [1] © 2017 IEEE.

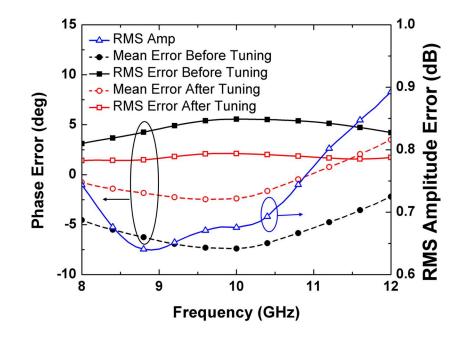

- Figure 2.12 Measured mean and RMS phase error before and after tuning, and 26 RMS amplitude error [1] © 2017 IEEE.

- Figure 2.13 Input-referred 1 dB compression point of the phase shifter measured 27 at center frequency at reference phase stage under forward operation.

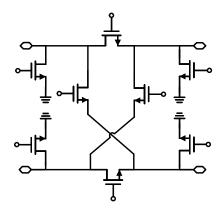

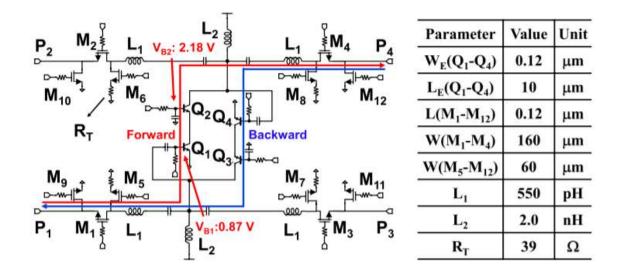

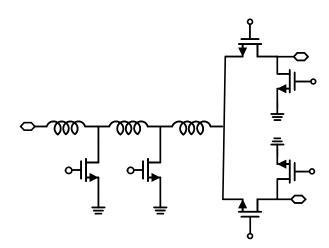

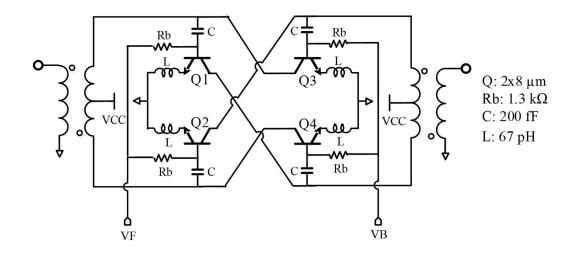

- Figure 2.14 Schematic of differential BDA using cross-coupled SiGe HBT 29 common-emitter differential pairs [2] © 2018 IEEE.

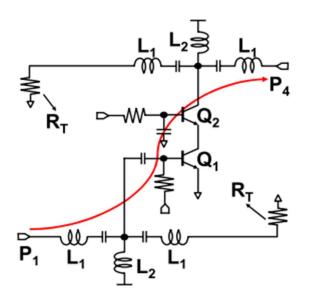

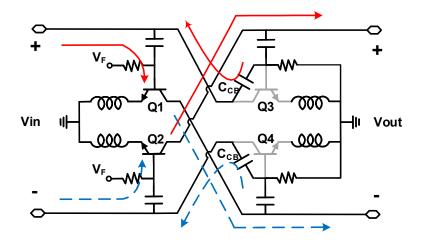

- Figure 2.15 Simplified equivalent circuit of the differential BDA core under 30 forward operation with arrows indicating signal flow.

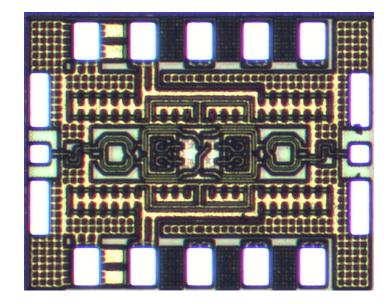

- Figure 2.16 Microphotograph of the 28 GHz switchless differential BDA [2] © 31 2018 IEEE.

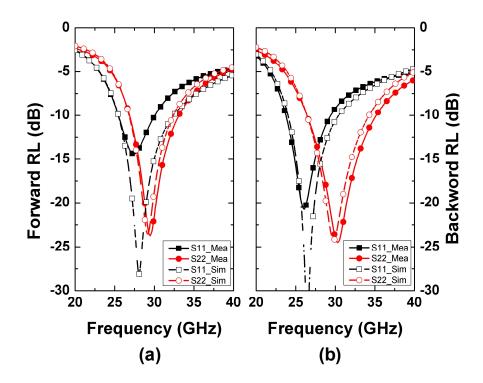

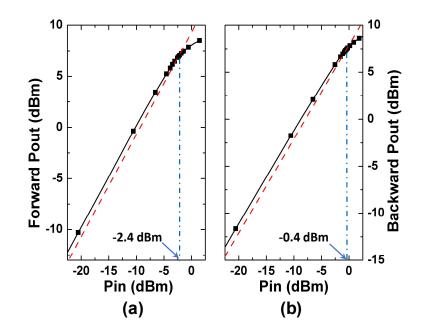

- Figure 2.17 –Simulated and measured return loss of the differential BDA under (a) 32 forward and (b) backward operations [2] © 2018 IEEE.

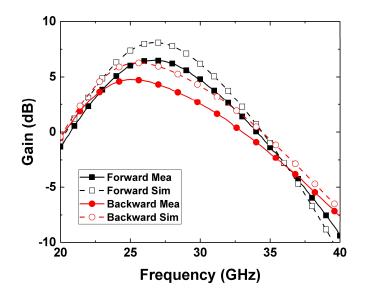

- Figure 2.18 Simulated and measured gain of the differential BDA under forward 32 and backward operations [2] © 2018 IEEE.

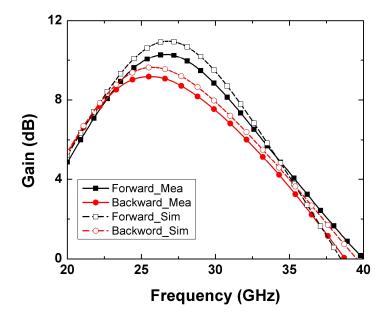

- Figure 2.19 –Measured and simulated NF under (a) forward and (b) backward 33 operations [2] © 2018 IEEE.

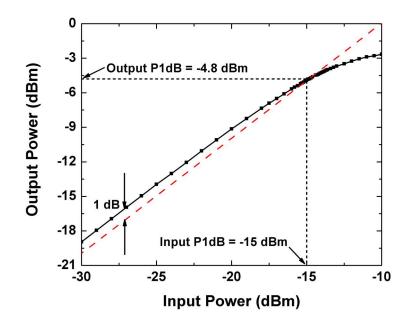

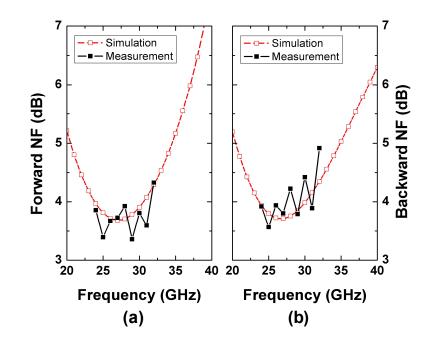

- Figure 2.20 Measured  $P_{OUT}$  vs.  $P_{IN}$  of the differential BDA under (a) forward 34 operation and (b) backward operation [2] © 2018 IEEE.

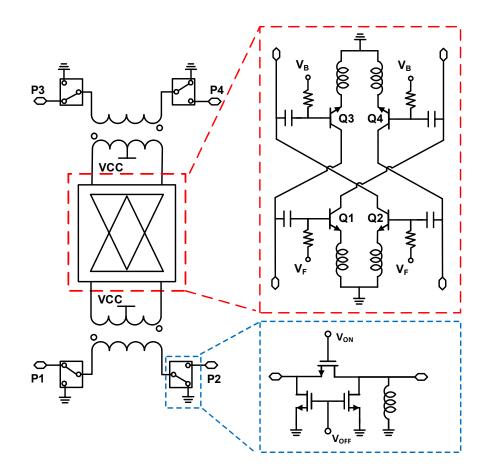

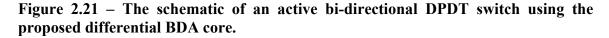

- Figure 2.21 The schematic of an active bi-directional DPDT switch using the 35 proposed differential BDA core.

- Figure 2.22 Active DPDT circuit operation when configured for signal flow from 36 P1 to P3.

- Figure 2.23 Microphotograph of the proposed active bi-directional DPDT with 38 differential BDA core.

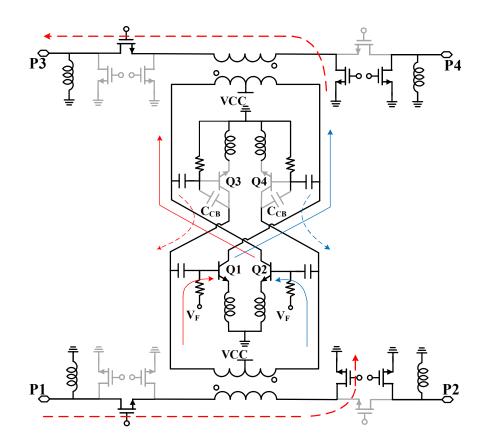

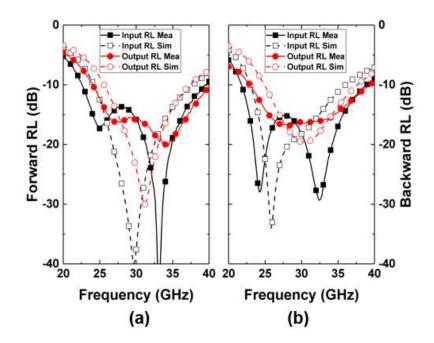

- Figure 2.24 (a) Simulated and measured return loss under P1-to-P3 (forward) 39 operation, and (b) under P3-to-P1 (backward) operation.

- Figure 2.25 Simulated and measured gain of forward and backward operations. 40

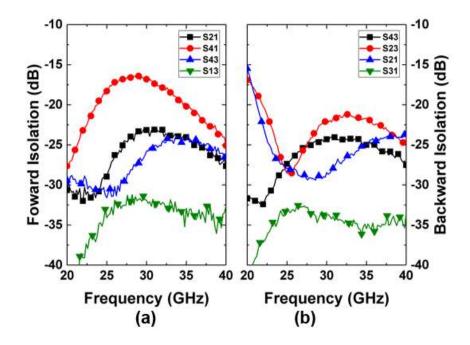

- Figure 2.26 Port-to-port isolation of the (a) forward and (b) backward operations. 41

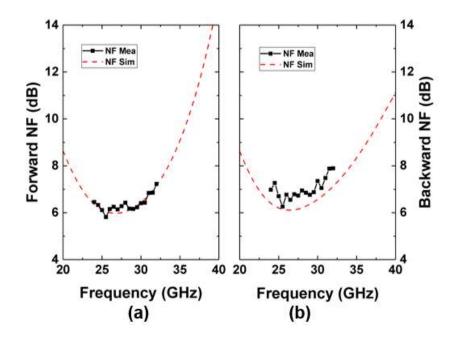

- Figure 2.27 Simulated and measured noise figure of the (a) forward and (b) 41 backward operations.

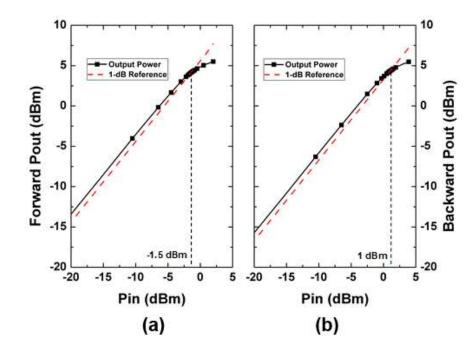

- Figure 2.28 The measured input-referred  $P_{1dB}$  of the (a) forward and (b) backward 42 operations at 28 GHz.

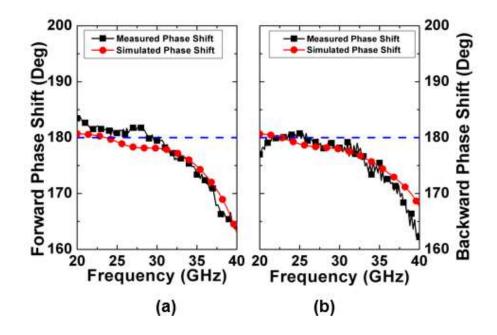

- Figure 2.29 (a) Simulated and measured relative phase shift between P1-to-P3 and 43 P1-to-P4 paths in forward operation. (b) Simulated and measured relative phase shift between P3-to-P1 and P3-to-P2 paths in backward operation.

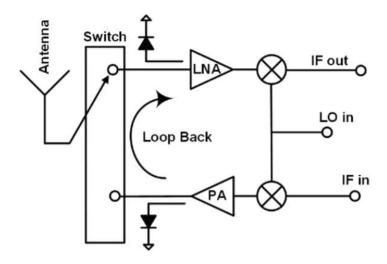

- Figure 3.1 Block diagram of a W-band transceiver with BIST [77] © 2019 IEEE. 44

- Figure 3.2 Block diagram of an IEEE 801.11ac power amplifier using an on-chip d5 logarithmic power detector for automatic power control © 2017 IEEE.

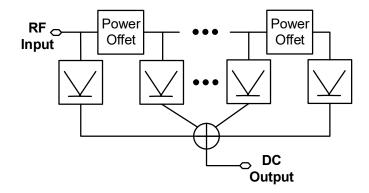

- Figure 3.3 Block diagram of the piece-wise linear approximation 45 implementation of logarithmic power detector.

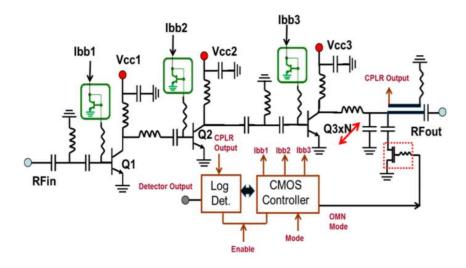

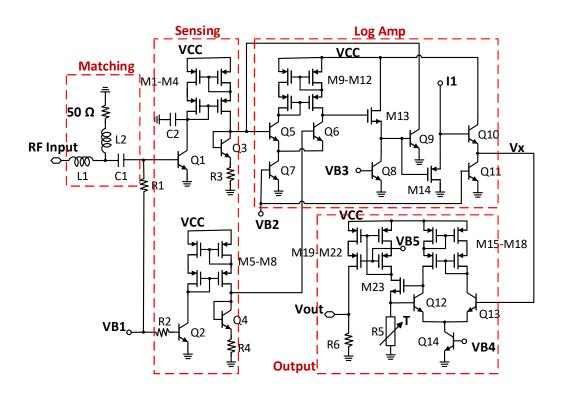

- Figure 3.4 Schematic of the proposed log detector with bias circuit omitted for 47 presentation purpose [3] © 2019 IEEE.

- Figure 3.5 Simplified block diagram of the two-branch log detector. Input power 48 level to the two branches are offset through external amplifier and step attenuator for testing purposes [3] © 2019 IEEE.

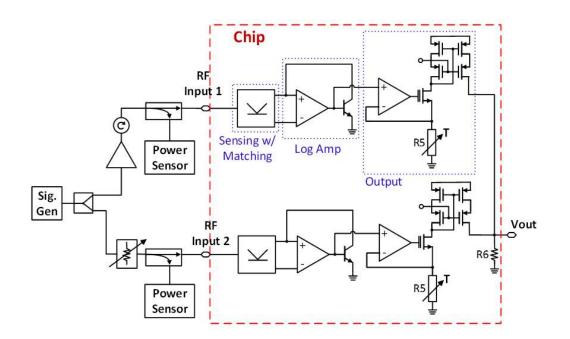

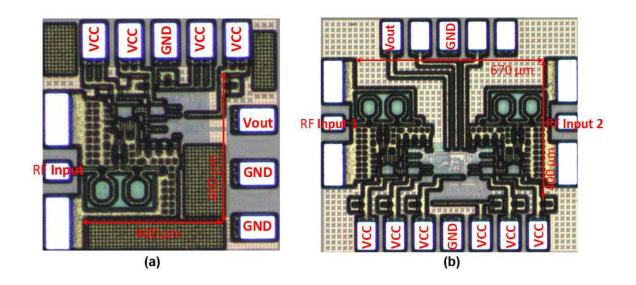

- Figure 3.6 Chip micrograph of (a) single branch log detector and (b) two-branch 49 log detector [3] © 2019 IEEE.

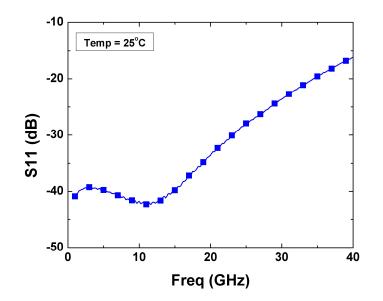

- Figure 3.7 Input matching of the single branch log detector measured at room 50 temperature. Result shows better than 15 dB return loss below 40 GHz [3] © 2019 IEEE.

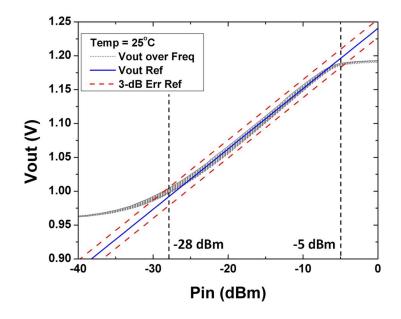

- Figure 3.8  $-V_{out}$  vs  $P_{in}$  of single branch log detector measured from 2 GHz to 40 50 GHz with 2 GHz frequency steps at room temperature. Reference with  $\pm 1.5$  dB log error reference lines are plotted. Results show from -28

dBm to -5 dBm logging range within  $\pm 1.5$  dB log error [3] © 2019 IEEE.

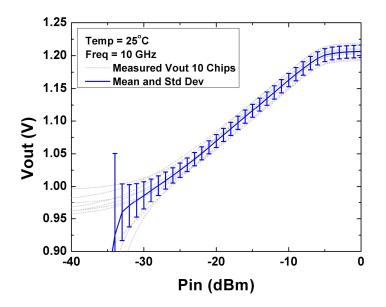

- Figure 3.9 Measured Vout vs. Pin response of the single branch log detector at 51 room temperature of 10 chips with 10 GHz input signal. Mean and standard deviation plotted with solid dash and error bar [3] © 2019 IEEE.

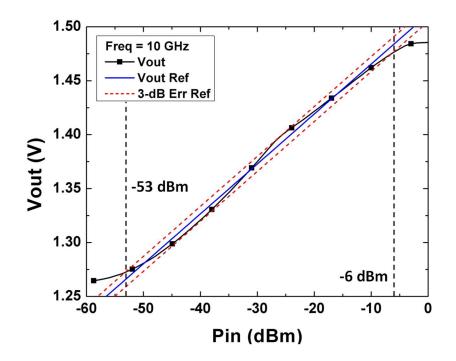

- Figure 3.10  $V_{out}$  vs.  $P_{in}$  of the two-branch log detector at 10 GHz and room 52 temperature with 25 dB input power level. The reference and ±1.5 dB log error reference lines are plotted in solid and dotted lines respectively. Results show 47 dB dynamic range within ±1.5 dB log error [3] © 2019 IEEE.

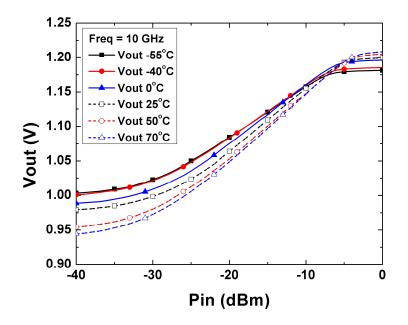

- Figure 3.11 Measured  $V_{out}$  vs.  $P_{in}$  response of single branch log detector over 53 temperature with 10 GHz input signal [3] © 2019 IEEE.

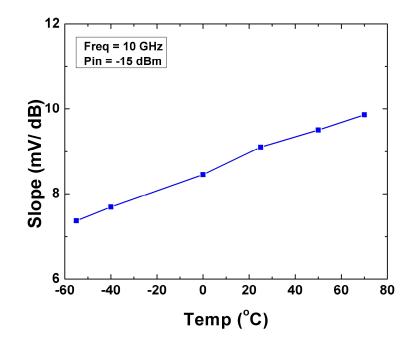

- Figure 3.12 Slope of the  $V_{out}$  vs.  $P_{in}$  response in Figure 3.11 over temperature at 54 15 dBm input level [3] © 2019 IEEE.

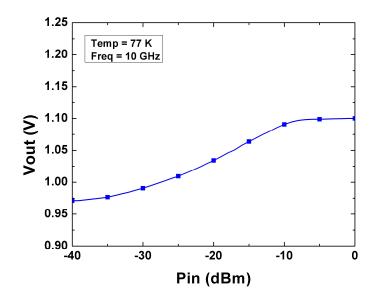

- Figure 3.13 The measured  $V_{out}$  vs.  $P_{in}$  response of the single branch log detector 55 at 77 K with 10 GHz input signal [3] © 2019 IEEE.

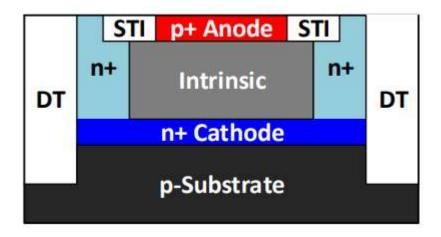

- Figure 4.1 Cross-section of a vertical SiGe PIN diode [31] © 2014 IEEE. 58

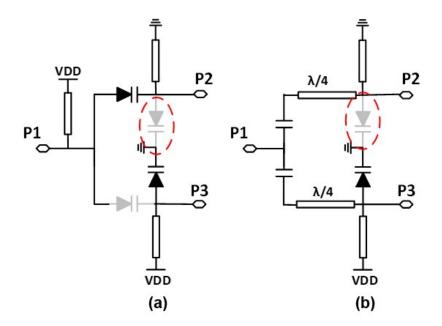

- Figure 4.2 Simplified schematic of (a) series-shunt and (b)  $\lambda/4$ -shunt PIN diode 59 switches with P1 as the antenna port, P2 as the thru port, and P3 as the isolation port. The off-state shunt diodes, circled in the schematics, are usually the limiting factor of the SPDT designs [4] © 2019 IEEE.

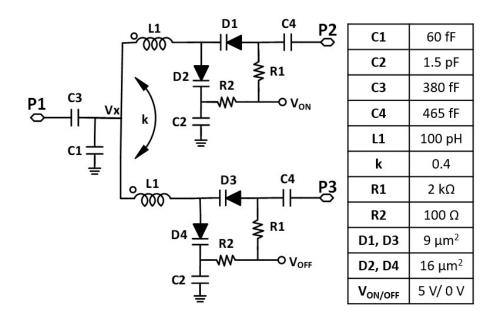

- Figure 4.3 Schematic, passive component values and bias condition of the 60 proposed 60 GHz SiGe PIN diode SPDT switch design [4] © 2019 IEEE.

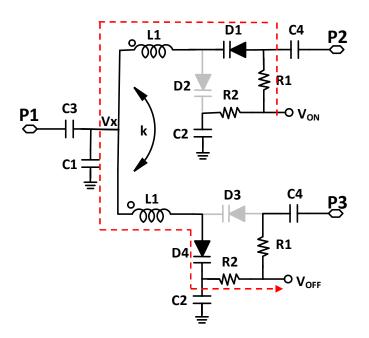

- Figure 4.4 Circuit operation when P2 is the thru port. The red dotted arrow 61 indicates the DC current path [4]  $\bigcirc$  2019 IEEE.

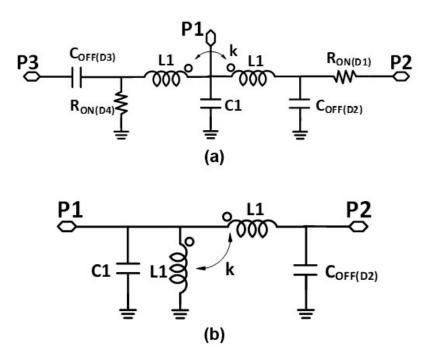

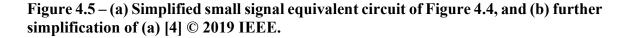

- Figure 4.5 (a) Simplified small signal equivalent circuit of Figure 4.4, and (b) 62 further simplification of (a) [4] © 2019 IEEE.

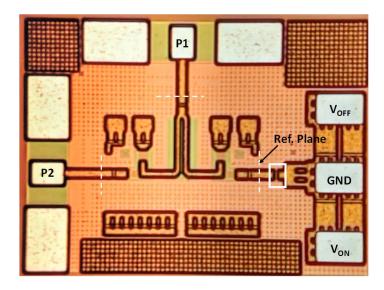

- Figure 4.6 Chip microphotograph of the proposed PIN SPDT switch with P3 63 terminated with on die 50  $\Omega$  resistor [4] © 2019 IEEE.

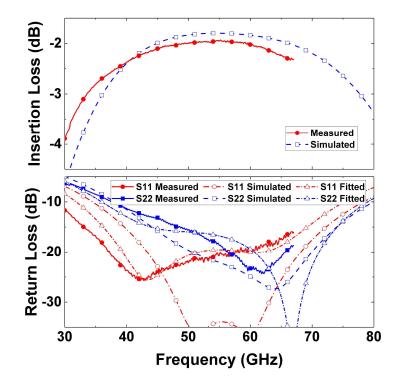

- Figure 4.7 Simulated and measured insertion loss and return loss of the proposed 63 PIN SPDT switch [4] © 2019 IEEE.

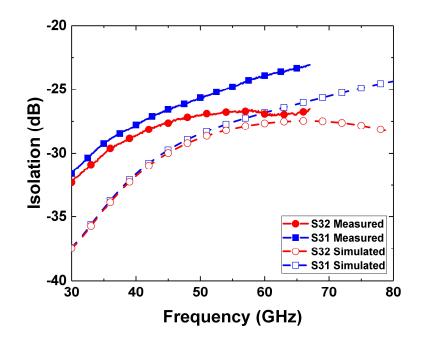

- Figure 4.8 Simulated and measured switch isolation of the proposed PIN SPDT 64 switch [4] © 2019 IEEE.

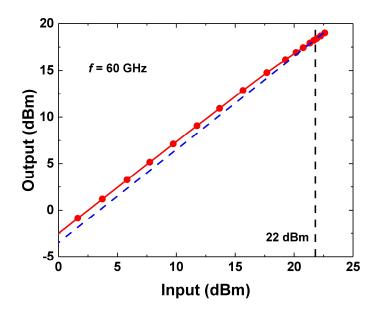

- Figure 4.9 Measured  $P_{1dB}$  of the proposed PIN SPDT switch at 60 GHz [4]  $\bigcirc$  65 2019 IEEE.

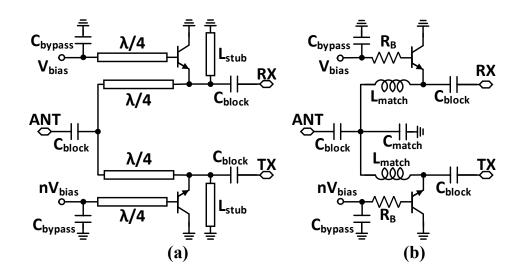

- Figure 4.10 Circuit schematics of (a) conventional quarter-wave shunt SPDT 67 switch design with short shunt stubs in parallel with HBTs, and (b) C-L-C  $\pi$ -network switch [5].

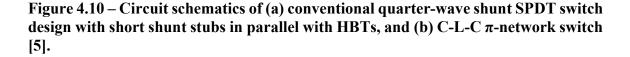

- Figure 4.11 2-D cross-section of the TCAD SiGe HBT biased in the ON-state, 69 showing simulated conduction band energy contours and streamlines of the internal electron current flow. The emitter is grounded for the left half-device and is floating for the right half-device [55].

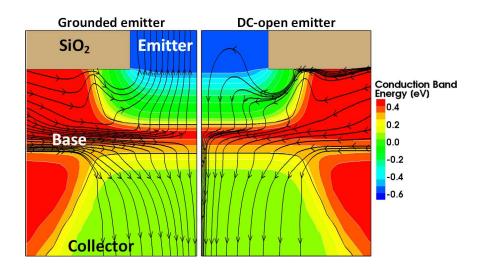

- Figure 4.12 -(a) The schematic and (b) chip micrograph of the W-band SPDT test 70 structure. The dimensions of the test structure are  $1.18 \times 0.48 \text{ mm}^2$  including bondpads [5].

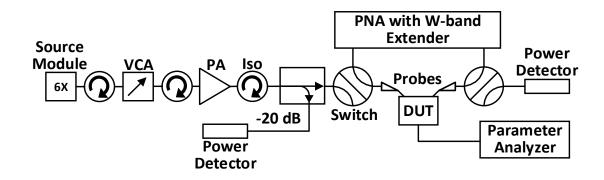

- Figure 4.13 Block diagram of the measurement setup [5]. 72

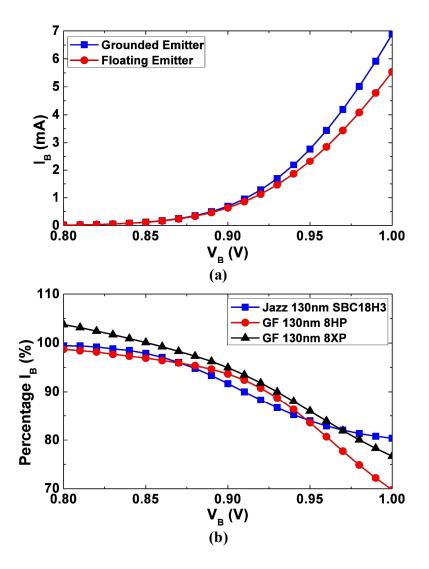

- Figure 4.14 Measured (a) I<sub>B</sub> vs. V<sub>B</sub> of HBT in switch test structure in GE and FE 73 configurations, and (b) percentage I<sub>B</sub> in FE configuration w.r.t. I<sub>B</sub> in GE configuration vs. V<sub>B</sub> of 2×5 µm Jazz SBC18H3, 10 µm GF 8HP, and 12 µm GF 8XP devices [5].

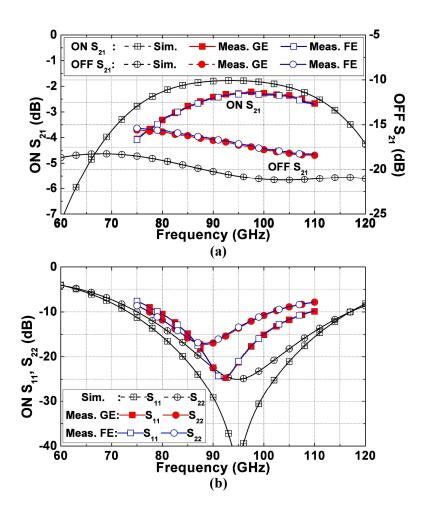

- Figure 4.15 Measured and simulated (a)  $S_{21}$  in both ON and OFF state, and (b)  $S_{11}$  74 and  $S_{22}$  in ON state operation [5].

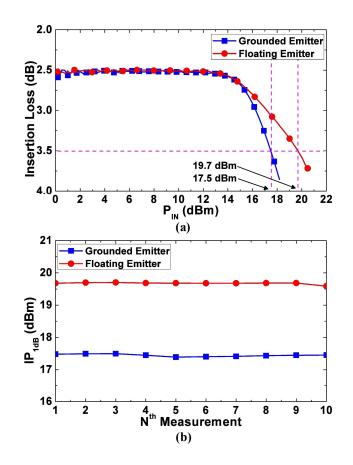

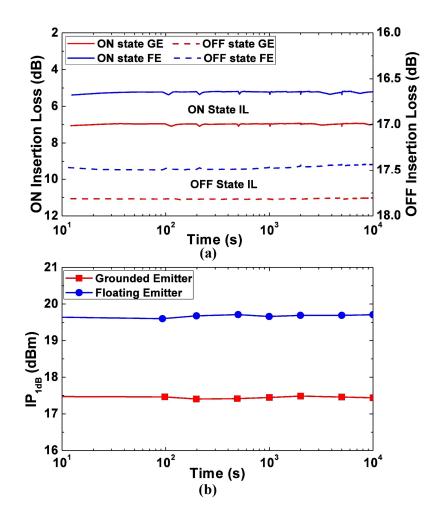

- Figure 4.16 Measured (a) insertion loss of the GE and FE configured test 75 structures vs.  $P_{IN}$ , and (b) the  $IP_{1dB}$  of the GE and FE test structure over 10 measurements. The GE configured switch showed 17.5 dBm  $IP_{1dB}$  and the FE switch demonstrates 19.7 dBm  $IP_{1dB}$ [5].

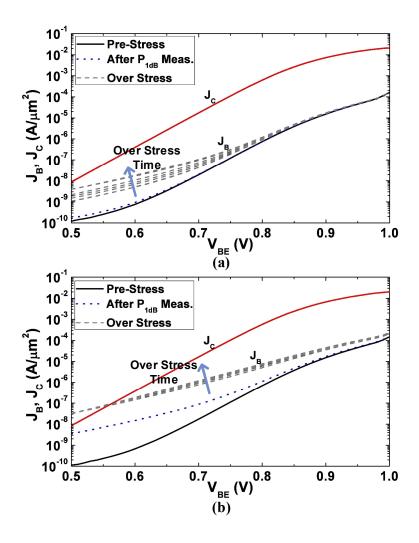

- Figure 4.17 Measured Gummel characteristics with 0 V  $V_{CB}$  of  $Q_{Top}$  before power 78 sweep, after sweep, and over the period of 10,000 s ON state RF stress in (a) GE configured and (b) FE configured switches [5].

- Figure 4.18 (a) Measured insertion loss of the GE and FE configured switches in 79 ON and OFF state with 23.3 dBm input power at 92 GHz, and (b) measured IP<sub>1dB</sub> (at 92 GHz) of the GE and FE configured switches between stress intervals [5].

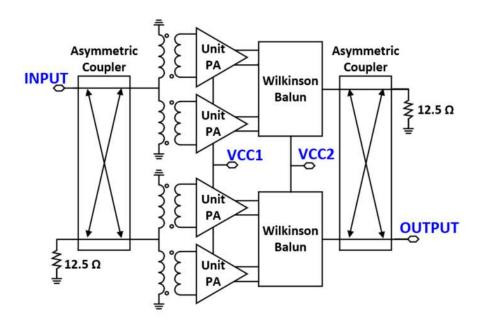

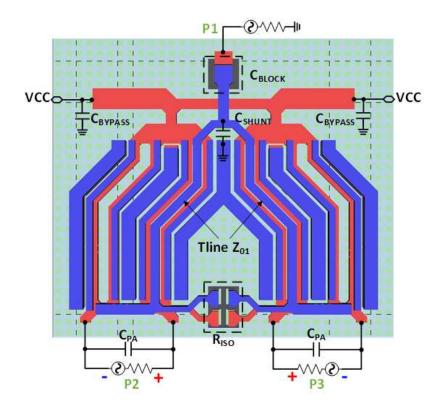

- Figure 5.1 Circuit block diagram of the 60 GHz SiGe balanced PA featuring 83 three-conductor T-line based asymmetric coupled-line coupler and Wilkinson baluns for power combining [7] © 2020 IEEE.

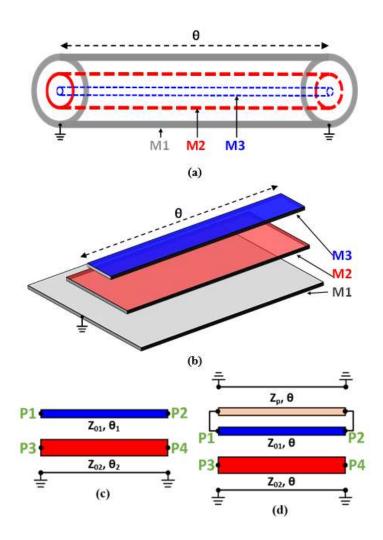

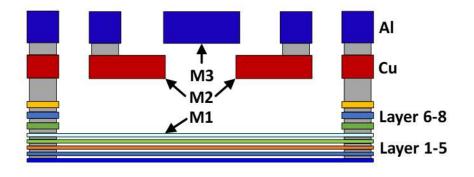

- Figure 5.2 (a) Three-conductor coaxial transmission line, where the center 84 conductor M3 is isolated from the ground M1 by the intermediate conductor M2, and its (b) IC planar counterpart. (c) The simplified circuit diagram representation of the coaxial three-conductor T-line, and (d) the circuit diagram of planar three-conductor T-line with an additional parasitic T-line of characteristic impedance  $Z_p$  to model non-ideal shielding [7] © 2020 IEEE.

- Figure 5.3 Circuit diagram of 2:1 sub-quarter wavelength balun [7] © 2020 85 IEEE.

- Figure 5.4 Circuit diagram of the proposed Wilkinson balun [7] © 2020 IEEE. 86

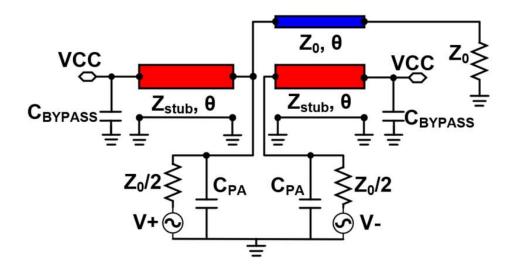

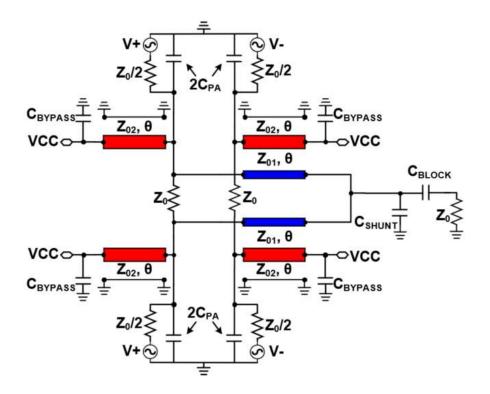

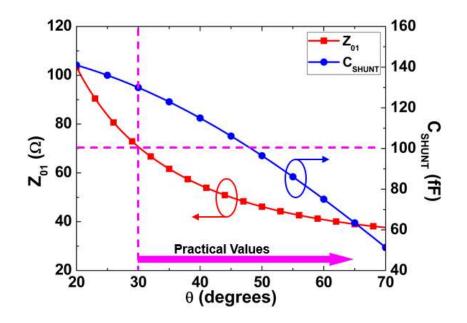

- Figure 5.5 Calculated  $Z_{01}$  and  $C_{SHUNT}$  vs.  $\theta$  with  $Z_0 = 25 \Omega$  and  $f_0 = 60$  GHz. A 88 70  $\Omega Z_{01}$  is required for  $\theta = 30^{\circ}$  [7]  $\odot$  2020 IEEE.

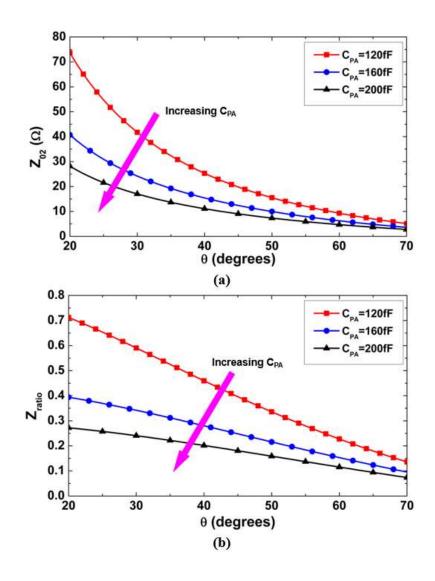

- Figure 5.6 Calculated (a)  $Z_{01}$  and (b)  $Z_{ratio}$  vs.  $\theta$  with  $C_{PA}$  of 120 *fF*, 160 *fF* and 89 200 *fF*.  $Z_0 = 25 \Omega$  and  $f_0 = 60$  GHz [7] © 2020 IEEE.

- Figure 5.7 Cross-section of the three-conductor transmission line implemented 89 in the Wilkinson balun combiner [7] © 2020 IEEE.

- Figure 5.8 Top view of the proposed Wilkinson balun [7]  $\bigcirc$  2020 IEEE. 90

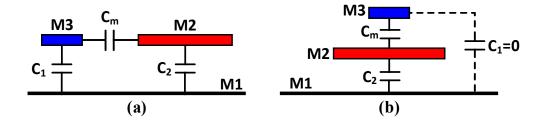

- Figure 5.9 (a) Asymmetric coupled-line and its equivalent capacitance network, 91 where  $C_{1,2}$  are the self-capacitance of each line and  $C_m$  is the mutual-capacitance between the two, and (b) three-conductor transmission line where  $C_I = 0$  [7] © 2020 IEEE.

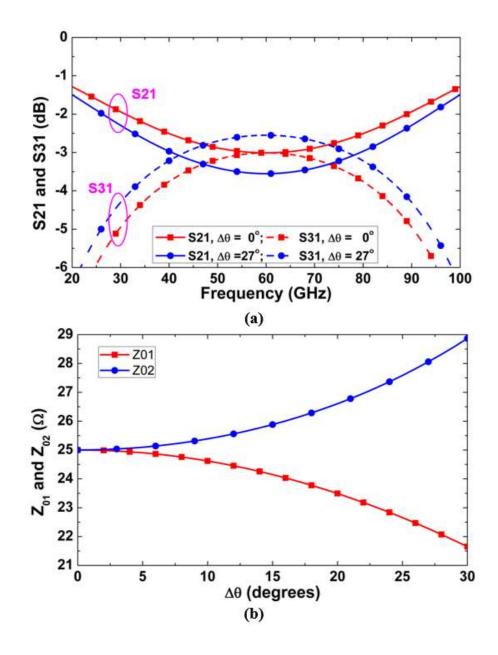

- Figure 5.10 Simulated (a)  $S_{21}$ ,  $S_{31}$ , and (b)  $S_{11}$  of the asymmetric coupler with 93 parasitic transmission line.  $Z_1 = 50 \Omega$ ,  $Z_{01} = Z_{02} = Z_2 = Z_3 = 25 \Omega$ ,  $Z_4 = 12.5 \Omega$ , and  $\theta = 90^{\circ}$  at the 60 GHz. Performance exhibits undercoupling and degradation in matching as coupling between M1 and M3 increases[7] © 2020 IEEE.

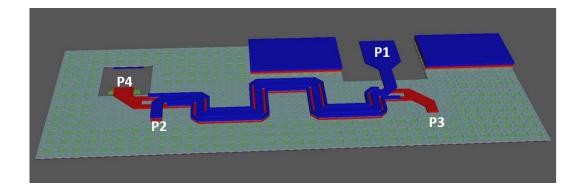

- Figure 5.11 3-D view of the output asymmetric coupler with output RF GSG pad. 95

P1 is the output port, P2 and P3 are the thru and coupled port, respectively. P4 is terminated with 12.5 Ω N+ sub-collector resistor [7]

© 2020 IEEE.

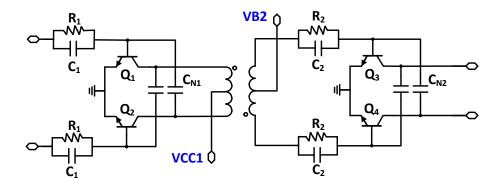

- Figure 5.12 Schematic of the unit PA core. Simple two-stage differential CE with 95 inductor-based transformer inter-stage matching topology was adopted [7] © 2020 IEEE.

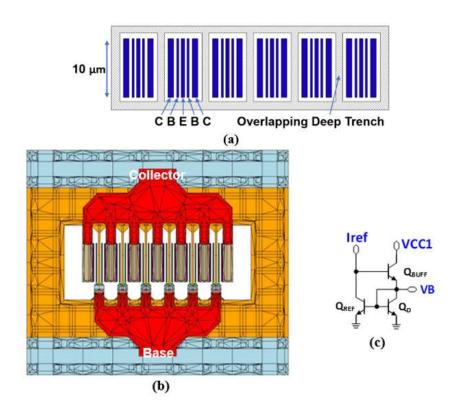

- Figure 5.13 (a) The top view of power transistor  $(Q_3 / Q_4)$ . Six CBEBC 10 µm 96 HBTs were placed in parallel with overlapping DT. (b) The top view of

power transistor test structure. (c) Buffered current mirror bias circuit with additional avalanche current diode  $Q_D$  [7] © 2020 IEEE.

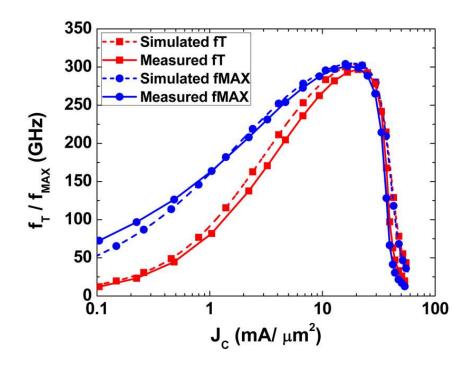

- Figure 5.14 Measured and simulated  $f_T$  and  $f_{MAX}$  of the power transistor test 97 structure with 0.3 V  $V_{CB}$ . Measured  $f_T$  and  $f_{MAX}$  show a close match with simulation [7] © 2020 IEEE.

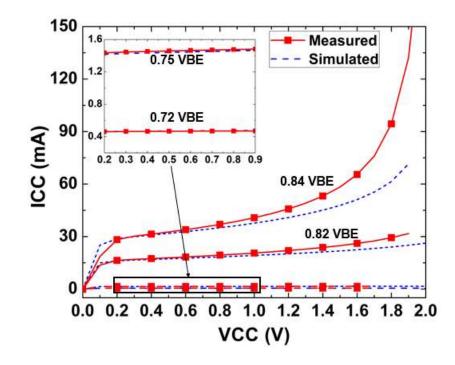

- Figure 5.15 Measured and simulated DC-IV characteristics of the power transistor 99 test structure with  $V_{BE} = 0.72 \text{ V}, 0.75 \text{ V}, 0.82 \text{ V}, \text{ and } 0.84 \text{ V} [7] © 2020$ IEEE.

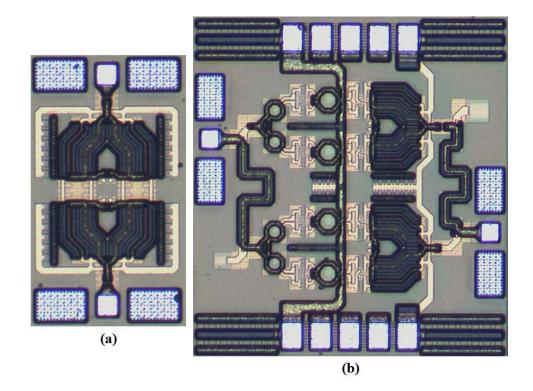

- Figure 5.16 Chip micrograph of the (a) back-to-back Wilkinson balun test 100 structure and (b) the proposed 60 GHz balanced PA. [7] © 2020 IEEE.

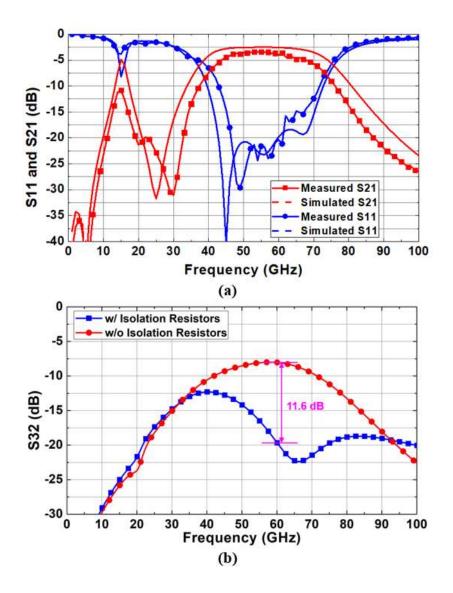

- Figure 5.17 Measured and simulated  $S_{11}$  and  $S_{22}$  of the back-to-back Wilkinson 102 balun test structure. Minimum measured insertion loss is 3.1 dB including loss from loading capacitors. (b) Simulated port isolation of the Wilkinson balun with and without the isolation resistors [7] © 2020 IEEE.

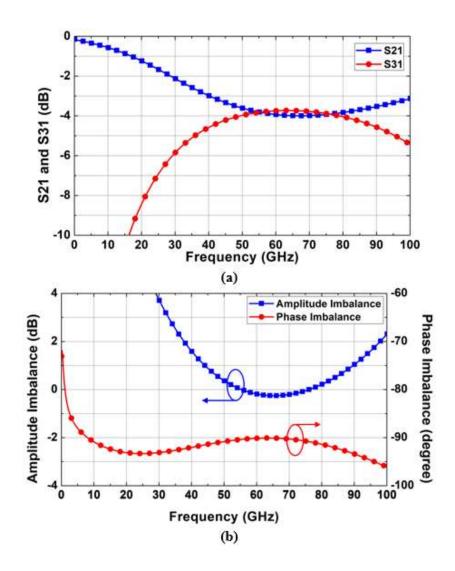

- Figure 5.18 (a) Simulated  $S_{21}$  and  $S_{31}$  of the output asymmetric coupler, showing 103 0.8 dB insertion loss at 60 GHz, and (b) simulated amplitude and phase imbalance between the coupled and thru ports [7] © 2020 IEEE.

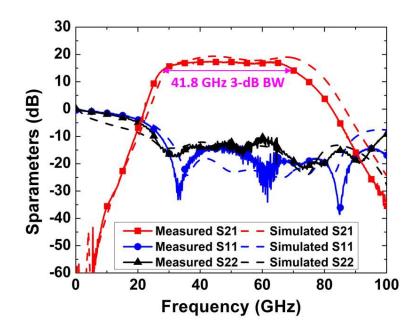

- Figure 5.19 Measured and simulated S-parameters of the balanced SiGe PA. The 104 design 17.3 dB with a 41.8 GHz 3-dB bandwidth. Both input and output return loss are better than 11 dB cross the 3-dB bandwidth [7] © 2020 IEEE.

- Figure 5.20 Measured and simulated  $P_{OUT}$ , Gain, and PAE plotted vs.  $P_{IN}$  at 60 105 GHz [7] © 2020 IEEE.

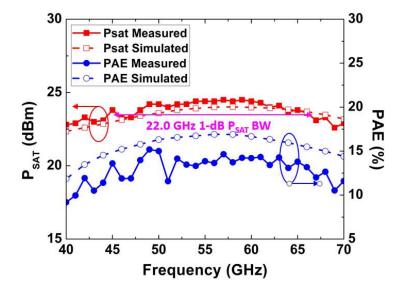

- Figure 5.21 Measured and simulated  $P_{SAT}$  and peak *PAE* from 40 GHz to 70 GHz. 105 The 1-dB  $P_{SAT}$  bandwidth is 22.0 GHz with peak *PAE* greater than 11.5% across the bandwidth [7] © 2020 IEEE.

#### SUMMARY

The objective of this research is to study and leverage the unique properties and advantages of silicon-germanium (SiGe) heterojunction bipolar transistor (HBT) integrated circuit technologies to better design radio frequency (RF) and millimeter wave (mm-wave) circuit components. With recent developments, the high yield and modest cost siliconbased semiconductor technologies have proven to be attractive and cost-effective alternatives to high-performance III-V technology platforms. Between SiGe bipolar complementary metal-oxide-semiconductor (BiCMOS) technology and advanced RF complementary metal-oxide-semiconductor (CMOS) technology, the fundamental devicelevel differences between SiGe HBTs and field-effect transistors (FETs) grant SiGe HBTs clear advantages as well as unique design concerns. The work presented in this dissertation identifies several advantages and challenges on design using SiGe HBTs and provides design examples that exploit and address these unique benefits and problems with circuit component designs using SiGe HBTs.

The following is a summary of the contributions of this research:

- A detailed analysis of the benefits of SiGe HBT technologies versus traditional semiconductor technologies, with focuses on the comparison of advanced RF CMOS and SiGe BiCMOS technologies.

- 2. The design and demonstration of high-performance bi-directional amplifiers exploiting the superior transconductance/ area property of SiGe HBTs through a loss-compensated X-band phase shifter [1] and a 28 GHz differential bi-directional amplifier (BDA) [2]. These two designs were presented in the 2017 IEEE Radio

Frequency Integrated Circuits Symposium © 2017 IEEE and published in the August 2018 issue of the IEEE Microwave and Wireless Components Letters © 2018 IEEE, respectively.

- 3. A wideband logarithmic power detector utilizing the exponential *I-V* characteristics of SiGe HBT with temperature compensated bias circuitry. This work was presented in the 2019 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium [3] © 2019 IEEE.

- 4. The design and demonstration of novel biasing techniques in SiGe BiCMOS RF switch design for improved performance, illustrated by a high power 60 GHz single-pole double-throw (SPDT) switch and a W-band SPDT switch performance comparison using grounded-emitter vs. floating-emitter reverse-saturated SiGe HBTs. The 60 GHz SPDT switch was presented in the 2019 IEEE Radio Frequency Integrated Circuits Symposium [4] © 2019 IEEE, and the W-band SPDT switch performance study has been submitted to the 2021 IEEE/ MTT-S International Microwave Symposium [5].

- 5. A 60 GHz high power SiGe differential common-emitter power amplifier with novel three-conductor transmission-line-based Wilkinson baluns and asymmetric directional couplers, exploiting the multi-layered back end of line (BEOL) offered by advanced SiGe BiCMOS technology. This work was presented in the 2020 IEEE/ MTT-S International Microwave Symposium [6] © 2020 IEEE and is to be published in the IEEE Transactions on Microwave Theory and Techniques [7] © 2020 IEEE.

# Copyright Statement

In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of Georgia Institute of Technology's products or services. Internal or personal use of this material is permitted. If interested in reprinting/ republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html to learn how to obtain a License from RightsLink.

Portions of the enclosed text and many of the figures will become IEEE copyrighted material in the future.

### CHAPTER 1. INTRODUCTION

#### 1.1 Silicon-Based Radio Frequency and Millimeter Wave Technologies

Since the first demonstration of silicon integrated circuit (IC) in 1960, tremendous efforts and innovations have pushed the advancement of silicon-based semiconductor technology at a revolutionary pace. Initially driven by the need for digital complementary metal-oxide-semiconductor (CMOS) switching speed and device density improvement, innovations in CMOS technology provided strong basis and helped the development of silicon-based platforms, such as silicon-germanium (SiGe) bipolar CMOS (BiCMOS) and RF silicon on insulator (SOI), which opened their way for use in the emerging radio frequency (RF) and millimeter wave (mm-wave) applications [8]. The need for highly integrated and cost-effective advanced modern RF and mm-wave radar and communication systems has led to a significant effort in the development of silicon semiconductor platforms as competing alternative to the traditionally dominating III-V compound semiconductor technologies [9].

With additional device, process, and modelling optimization, RF CMOS technologies benefitted greatly from the aggressive digital CMOS scaling that drastically improved transistor switching speed. In recent years, there has been growing interests in further bulk CMOS scaling to move from a planar device to a fin field-effect transistor (FinFET) [10]. However, RF performance of advanced RF CMOS technologies does not scale as well as digital CMOS due to the high sensitivity to layout parasitic resistance and capacitance from device structure, substrate, and BEOL [11]. Other than device scaling, engineering innovations such as SOI [12], the use of high-k dielectric, the introduction of

mobility stressor, and etc. [13] have also pushed the performance of advanced RF CMOS technologies further.

SiGe BiCMOS, on the other hand, has entered the commercial market at a much later time compared to RF CMOS. However, since the first commercially available SiGe HBT platform [14], the tremendous generational growth of SiGe HBT technologies has led to an increasing presence of SiGe BiCMOS platforms in various modern RF and mm-wave applications. In SiGe BiCMOS technologies, SiGe HBTs are normally added to a lagging edge CMOS node, with additional process optimization. While the unity gain cutoff frequency ( $f_T$ ) performance of CMOS depends greatly on lateral scaling, the  $f_T$ improvement of SiGe HBT is primarily driven by vertical scaling [8]. Current state-of-theart SiGe BiCMOS platforms offers an  $f_T$  of 505 GHz and a maximum oscillation frequency ( $f_{MAX}$ ) of 720 GHz at room temperature [15].

#### 1.2 Technology Device Performance Comparison

The choice for semiconductor technologies needs to be made specific to application. For applications requiring significant portion of logic and lower-power operations, a bulk CMOS technology that is suit for an integrated solution with highdensity and low-cost becomes the clear winner. However, for high performance RF and mm-wave front-end designs, CMOS technologies can appear limiting, and a dis-integrated solution with a combination of different platforms is more practical. Therefore, a comparison among the available semiconductor technologies is very informative.

Given the diverse choices of SiGe BiCMOS, RF CMOS, and III-V technologies, reaching a sweeping generalization of the performance differences among them is

inevitably unfair, if not impossible. Nonetheless, some general observations of the differences are helpful to better understand the advantages and disadvantages associated with each device technology. Authors in [9] summarized a relative comparison of the performance metrics of various device technologies as shown in Table 1.1.

| Performance Metric     | SiGe<br>HBT | Si<br>BJT | Si<br>CMOS | III-V<br>MESFET | III-V<br>HBT | III-V<br>HEMT |

|------------------------|-------------|-----------|------------|-----------------|--------------|---------------|

| Frequency response     | +           | 0         | 0          | +               | ++           | ++            |

| 1/f and phase noise    | ++          | +         | -          |                 | 0            |               |

| Broadband Noise        | +           | 0         | 0          | +               | +            | ++            |

| Linearity              | +           | +         | +          | ++              | +            | ++            |

| Output conductance     | ++          | +         | -          | -               | ++           | -             |

| Transconductance/ area | ++          | ++        |            | -               | ++           | -             |

| Power dissipation      | ++          | +         | -          | -               | +            | 0             |

| CMOS integration       | ++          | ++        | N/A        |                 |              |               |

| IC cost                | 0           | 0         | +          | _               | -            |               |

Table 1.1 – Relative Performance Comparisons of Various Device Technologies for RFICs (Excellent: ++; Very good: +; Good: 0; Fair: -; Poor: --) [9]

Figure 1.1 – A technology survey in 2013 comparing the state-of-the-art semiconductor technologies in the breakdown voltage vs.  $f_T$  trade space [16] © 2013 IEEE.

From a pure device performance perspective, III-V technologies in general are superior compared to silicon-based technologies, as shown by the survey comparing the state-of-the-art semiconductor technology in the breakdown voltage vs.  $f_T$  trade space in Figure 1.1, [16]. For sub-terahertz, ultra-wide band, high power, or mission-critical applications, III-V technologies are undoubtedly favored for their device RF characteristics [17], [18]. Though falling behind in device performance, SiGe BiCMOS and RF CMOS technologies outshine III-V technologies from low cost, high yield, and high-level integration perspectives. As a result, there has been increasing interests in advanced RF CMOS and SiGe BiCMOS technologies as potential candidates for the optimization of performance, system size, and die cost [19].

Comparing among Si-based technologies, the state-of-the-art SiGe HBTs offer better frequency response over aggressively scaled RF-CMOS both on bulk Si and SOI. However, both advanced SiGe BiCMOS and RF-CMOS technologies offers device featuring  $f_T$  and  $f_{MAX}$  close to, or higher than, 300 GHz, which meets the need of significant portion of the RF and mm-wave applications. Perhaps, instead of comparing the best of SiGe BiCMOS and RF-CMOS technologies, comparison studies between SiGe BiCMOS and RF-CMOS technologies with similar  $f_T$  and  $f_{MAX}$  are more relevant.

### 1.2.1 Device Noise Performance for Low Noise Amplifier (LNA) Design

When first introduced to the market, SiGe HBTs demonstrated superior device noise performance compared with RF CMOS technologies. This gap was soon closed by the rapid scaling of RF CMOS. In modern low noise applications, both SiGe BiCMOS and RF CMOS technologies are heavily utilized. The device noise performance comparison between SiGe HBT and RF CMOS has been commented on by various researchers and engineers.

Figure 1.2 – (a) Measured  $f_T$ ,  $f_{MAX}$  and  $NF_{min}$  at 40 GHz vs. current density for BipX and 65 nm LP NMOS [20] © 2006 IEEE, and (b)  $NF_{min}$  comparison between GLOBALFOUNDRIES 40 nm 45RFSOI and 130 nm SiGe HBT [23] © 2018 IEEE.