# DESIGN, MODELING, AND CHARACTERIZATION OF EMBEDDED PASSIVES AND INTERCONNECTS IN INHOMOGENEOUS LIQUID CRYSTALLINE POLYMER (LCP) SUBSTRATES

A Dissertation Presented to The Academic Faculty

by

WANSUK YUN

In Partial Fulfillment of the Requirements for the Degree Doctor of Philasophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2007

Copyright © 2007 by Wansuk Yun

# DESIGN, MODELING, AND CHARACTERIZATION OF EMBEDDED PASSIVES AND INTERCONNECTS IN INHOMOGENEOUS LIQUID CRYSTALLINE POLYMER (LCP) SUBSTRATES

Approved by:

Dr. Madhavan Swaminathan, Advisor School of Electrical and Computer *Georgia Institute of Technology*

Dr. James S. Kenney School of Electrical and Computer *Georgia Institute of Technology*

Dr. Mahadevan Iyer School of Electrical and Computer *Georgia Institute of Technology*  Dr. Alan Doolittle School of Electrical and Computer *Georgia Institute of Technology*

Dr. Suresh K. Sitaraman Mechanical Engineering *Georgia Institute of Technology*

Date Approved: November 2007

# ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to those who have helped make this work possible. First, I would like to thank my advisor, Professor Madhavan Swaminathan, for his guidance and for giving me the opportunity to work in EPSILON group. His depth of understanding and ability to relate many ideas together has provided the push in the right direction and has made this work possible. I would also like to thank Professor Mahadevan Iyer for his valuable advices on research and career. I would also like to thank Professors James Kenney, Alan Doolittle, and Suresh Sitaraman for serving on my committee.

I would like to extend my heartfelt thanks to my colleagues in the EPSILON group: Dr. Ege Engin, Tae Hong Kim, Subramanian N Lalgudi, Krishna Bharath, Krishna Srinivasan, Ki Jin Han, Nevin Altunyurt, Abhilash Goyal, Janani Chandrasekhar, Bernie J.Yang, Aswani Kurra, Narayanan V T, Ranjeeth Doppalapudi for their cooperation, their help, and for all the informative discussions we had together. I also wish all the best for new students: Seunghyun Hwang, Suzanne Lynn Huh, Myunghyun Ha, Rishiraj A Bheda, Vishal Laddha, Sukruth G Pattanagiri. I would like to thank again all of EPSILON members for their friendship.

I would also like to acknowledge the help of alumni who provided assistance in many ways: Dr. Sidharth Dalmia, Dr. Vinu Govind, Dr. Amit Bavisi, Dr. Souvik Mukherjee, Mr. Abdemanaf Tambawala, Dr. Prathap Muthana, Ms. Marie Milleron, Dr. Bhyrav Mutnury, Dr. Jinwoo Choi, Dr. Rohan Mandrekar, Dr. Jifeng Mao. Specific thanks go to Mr. Venky Sundaram of Georgia Tech. PRC and Dr. George White of Jacket Micro Devices for providing me with LCP process.

iii

Finally, I want to thank my dedicated parents who have always set a strong example for me and have supported me through all of the accomplishments of my life. I also want to give special thanks to my dear wife Sujung Park for her dedication and endless love for the last five and half years. I also want to thank my young daughter Yujin Yun for giving me so much joy in my life even though I did not have a chance to give her back that much.

# TABLE OF CONTENTS

|                                                                                   | Page            |

|-----------------------------------------------------------------------------------|-----------------|

| ACKNOWLEDGEMENTS                                                                  | iii             |

| LIST OF TABLES                                                                    | viii            |

| LIST OF FIGURES                                                                   | ix              |

| SUMMARY                                                                           | xiv             |

| CHAPTER 1 INTRODUCTIOIN                                                           | 1               |

| 1.1 System on Package                                                             | 3               |

| 1.2 Characterization of High-frequency Materials                                  | 4               |

| 1.3 Characterization of Vias                                                      | 8               |

| 1.4 Embedded Passive Technology; High-Q Passive Design                            | 12              |

| 1.5 RF Front-end Modules using High-Q Embedded Passive Components                 | 13              |

| 1.6 Completed Research                                                            | 14              |

| 1.7 Dissertation Outline                                                          | 16              |

| CHAPTER 2 CHARACTERIZATION OF INHOMOGENEOUS LCP<br>SUBSTRATES                     | 17              |

| 2.1 Introduction                                                                  | 17              |

| 2.2 Inhomogeneous LCP Technology                                                  | 20              |

| 2.3 Loss Characterization of Inhomogeneous LCP substrates                         | 24              |

| 2.4 Model-to-Hardware Correlation                                                 | 29              |

| 2.5 Summary                                                                       | 33              |

| CHAPTER 3 MEASUREMENT-BASED TWO-PORT CHARACTERIZATIO<br>OF VERTICAL INTERCONNECTS | <b>DN</b><br>34 |

| 3.1 Introduction                                                                  | 34              |

| 3.1.1 One-Port Characterization                                                   | 35              |

| 3.1.2 Two-Port Characterization                                                                                  | 36                |

|------------------------------------------------------------------------------------------------------------------|-------------------|

| 3.2 Principle of a Measurement-Based Two-Port Via Characterization                                               | 38                |

| 3.3 Design of Test Vehicles                                                                                      | 42                |

| 3.4 Measured Results                                                                                             | 44                |

| 3.5 Model-to-Hardware Correlation                                                                                | 51                |

| 3.6 Via Model                                                                                                    | 55                |

| 3.7 Summary                                                                                                      | 57                |

| CHAPTER 4 DESIGN AND CHARACTERIZATION OF HIGH-Q EMBED<br>PASSVIES IN INHOMOGENEOUS MULTI-LAYER LCP<br>SUBSTRATES | <b>DDED</b><br>58 |

| 4.1 Introduction                                                                                                 | 58                |

| 4.2 High-Q Embedded Inductor Characterization in Test Vehicle 1                                                  | 59                |

| 4.3 High-Q Embedded Inductor Characterization in TVs 2 and 3                                                     | 64                |

| 4.4 Accuracy and Sensitivity of Quality-Factor Measurement                                                       | 70                |

| 4.5 Two-Step de-embedding technique                                                                              | 73                |

| 4.6 Measurement-Based Inductor Model                                                                             | 75                |

| 4.7 Design and Characterization of Compact 3D Capacitors                                                         | 79                |

| 4.8 Measurement-Based Capacitor Model                                                                            | 82                |

| 4.8 Summary                                                                                                      | 85                |

| CHAPTER 5 DESIGN OF LUMPED ELEMENT RF CIRCUITS IN<br>INHOMOGENEOUS MULTI-LAYER LCP SUBSTRATES                    | 86                |

| 5.1 Introduction                                                                                                 | 86                |

| 5.2 C-Band Filter                                                                                                | 87                |

| 5.3 Double-balanced Mixer                                                                                        | 89                |

| 5.4 Doubly Double-Balanced Mixer                                                                                 | 95                |

| 5.5 Design of 30 GHz Distributed Band-Pass Filter in Inhomogeneou<br>Multi-layer LCP Substrates                  | s<br>103          |

| 5.6 Summary                          | 108 |

|--------------------------------------|-----|

| CHAPTER 6 CONCLUSION AND FUTURE WORK | 109 |

| 6.1 Conclusion                       | 109 |

| 6.2 Future Work                      | 112 |

| 6.3 Publications                     | 112 |

| REFERENCES                           | 115 |

| VITA                                 | 122 |

# LIST OF TABLES

|                                                                                                      | Page         |

|------------------------------------------------------------------------------------------------------|--------------|

| Table 3.1: TRL lines                                                                                 | 42           |

| Table 3.2: Specifications of the TVs                                                                 | 44           |

| Table 3.3: Extracted values of the via                                                               | 55           |

| Table 4.1: Summary of inductors at two different locations in TV1                                    | 64           |

| Table 4.2: Physical dimensions and locations of the inductors in TV2 and TV3                         | 65           |

| Table 4.3: Measurement results of the selected inductors in TV2 and TV3                              | 69           |

| Table 4.4: Dimensions of the fabricated Inductor 3_tops in TV2 and TV3                               | 71           |

| Table 4.5: Measured results of the inductors after the de-embedding and correlatio simulated results | n with<br>74 |

| Table 4.6: Extracted parameters of the measurement-based inductor model                              | 79           |

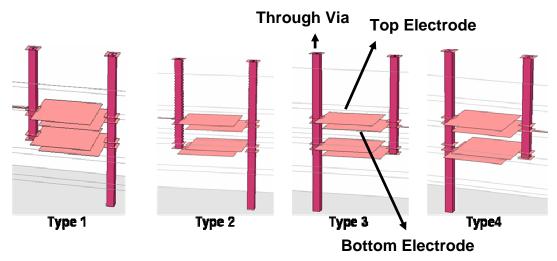

| Table 4.7: Four types of 3D capacitors                                                               | 80           |

| Table 4.8: Summary of measured results of 3D capacitors                                              | 80           |

| Table 4.9: Extracted parameters of the measurement-based capacitor model                             | 82           |

| Table 5.1: Performance of the lumped baluns                                                          | 99           |

| Table 5.2: Design values of 30 GHz gap-coupled band-pass filter                                      | 106          |

# LIST OF FIGURES

|                                                                                                                                                       | Page        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 1.1: Multi-band system architecture                                                                                                            | 2           |

| Figure 1.2: The state-of-the-art mixed-signal SOP technology                                                                                          | 4           |

| Figure 1.3: The vertical interconnects in SOP                                                                                                         | 8           |

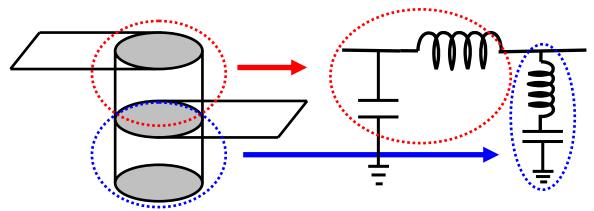

| Figure 1.4: The structure of a via and its equivalent circuit model                                                                                   | 9           |

| Figure 1.5: A T-resonator for characterizing single via                                                                                               | 11          |

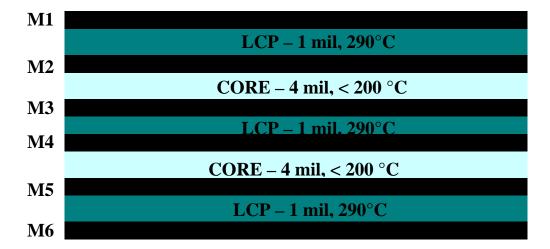

| Figure 2.1: Cross-section of the homogeneous LCP substrate with melt temperatures                                                                     | 17          |

| Figure 2.2: Cross-section of the inhomogeneous three-layer LCP substrate with melt temperatures                                                       | 18          |

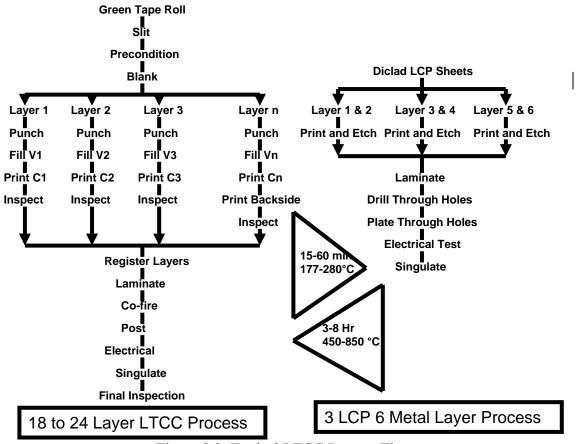

| Figure 2.3: Typical LTCC Process Flow                                                                                                                 | 19          |

| Figure 2.5: Multiple LCP Layer Process Flow                                                                                                           | 24          |

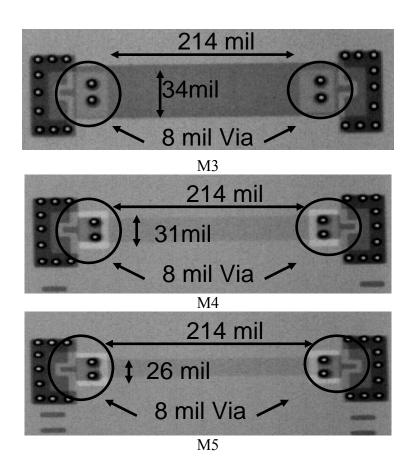

| Figure 2.6: X-rays of the 214 mil transmission lines in M3, M4, and M5 in inhomogeneous multi-layer LCP substrates                                    | 25          |

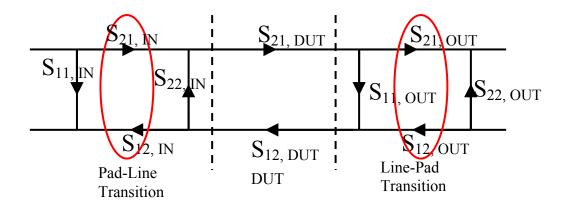

| Figure 2.7: Signal flow graph of the measurement set up for embedded transmission                                                                     | lines<br>26 |

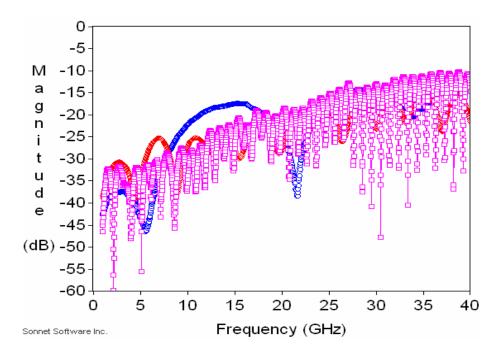

| Figure 2.8: Measured S11 of the embedded transmission lines in M3                                                                                     | 28          |

| Figure 2.9: Measured S21 of the embedded transmission lines in M3                                                                                     | 28          |

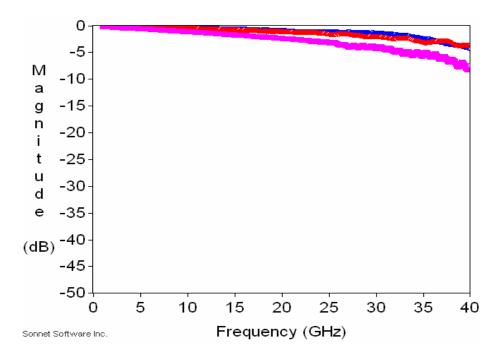

| Figure 2.10: Measured S11 of the embedded transmission lines in M5                                                                                    | 29          |

| Figure 2.11: Measured S21 of the embedded transmission lines in M5                                                                                    | 29          |

| Figure 2.12: Attenuation characteristics [dB/inch] of inhomogeneous multi-layer LC substrates, compared with other high-frequency materials           | P<br>30     |

| Figure 2.13: Model of the embedded transmission lines including through-via connections                                                               | 31          |

| Figure 2.14: Model for the via interconnection between signal lines including parasit to the ground because of the hanging portion of the through via | tics<br>32  |

| Figure 2.15: Model-to-hardware correlation of the transmission lines in M3                                                                            | 32          |

| Figure 2.16: Model-to-hardware correlation of the transmission lines in M4                            | 33         |

|-------------------------------------------------------------------------------------------------------|------------|

| Figure 2.17: Model-to-hardware correlation of the transmission lines in M5                            | 33         |

| Figure 2.18: Model-to-hardware correlation of the transmission lines in M6                            | 34         |

| Figure 3.1: Vertical interconnects in 3D integration using SOP                                        | 35         |

| Figure 3.2: Two possible configurations for the two-port characterization of a vertical interconnect  | l<br>38    |

| Figure 3.3: The procedure for characterizing vertical interconnect                                    | 42         |

| Figure 3.4: The layout of the through standard                                                        | 43         |

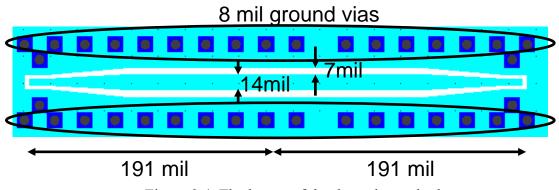

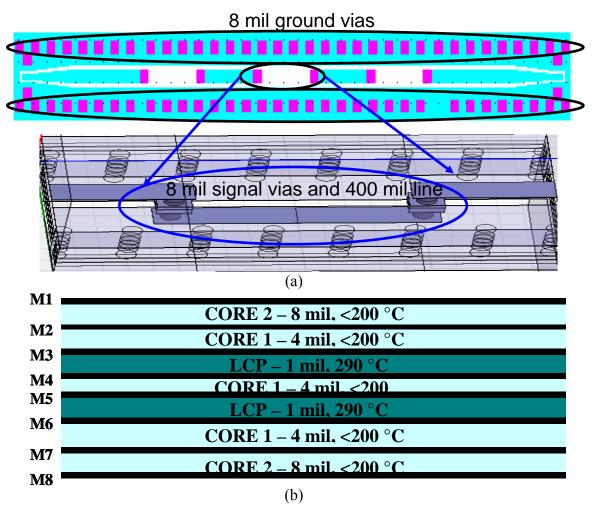

| Figure 3.5: The designed TV 1: (a) layout and (b) Inhomogeneous LCP stack-up                          | 44         |

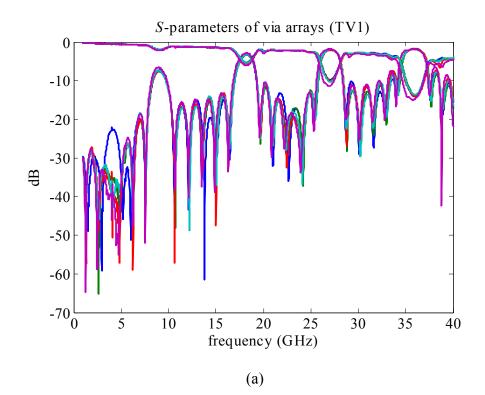

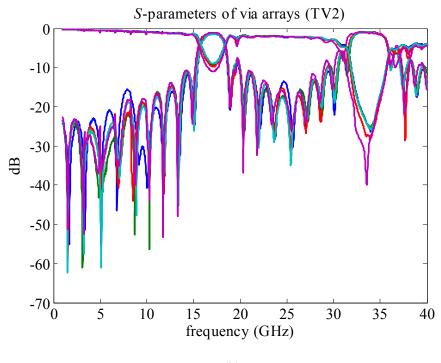

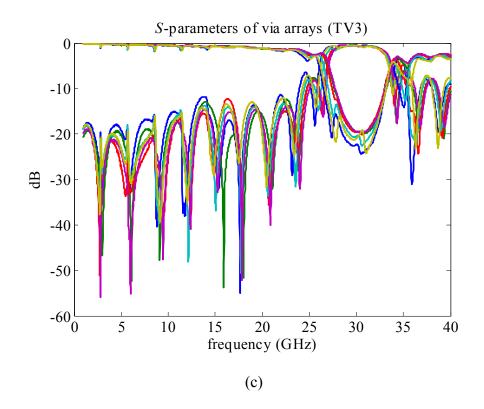

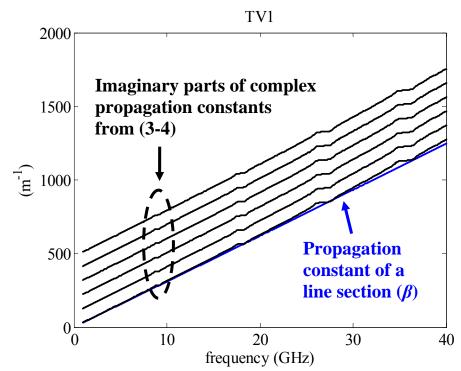

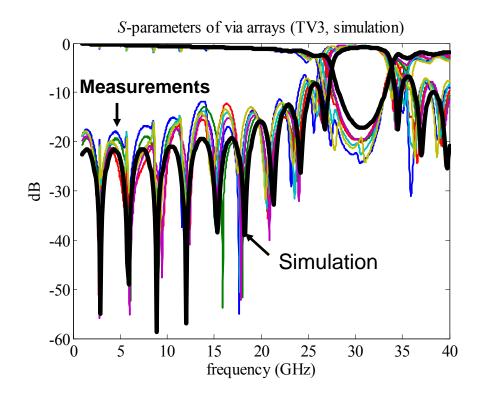

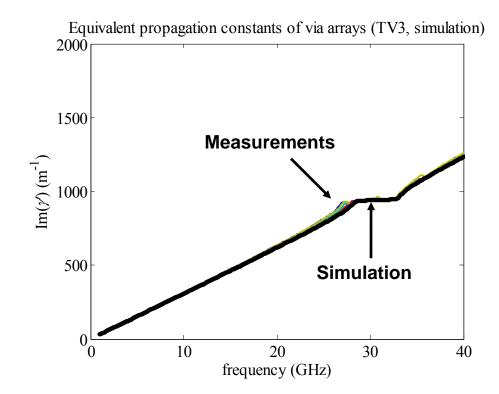

| Figure 3.6: Measured S parameters of (a) TV1, (b) TV 2, and (c) TV3                                   | 46         |

| Figure 3.7: Physical propagation constant of TV1 among solutions                                      | 47         |

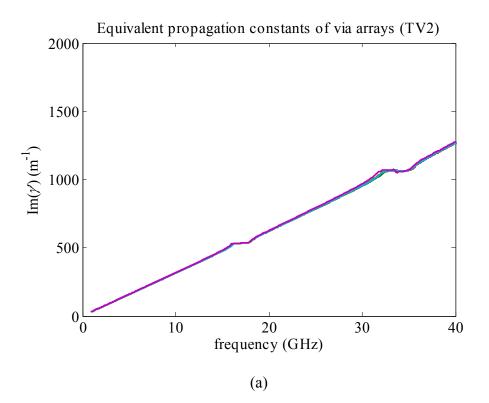

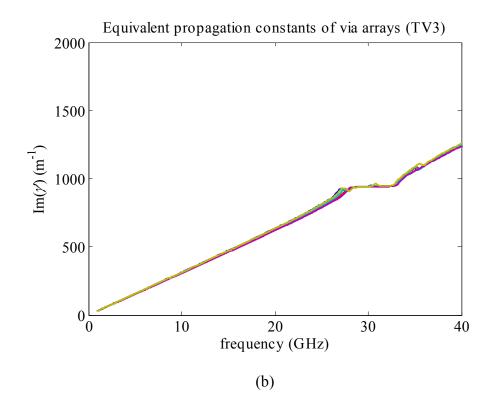

| Figure 3.8: Extracted propagation constants of TVs 2 and 3 from the measurements                      | 48         |

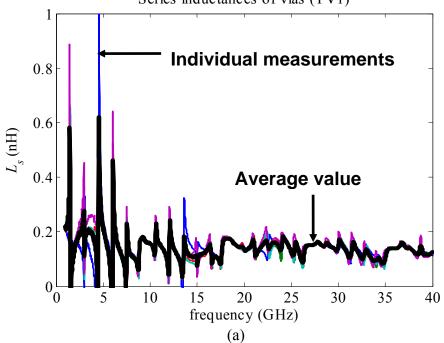

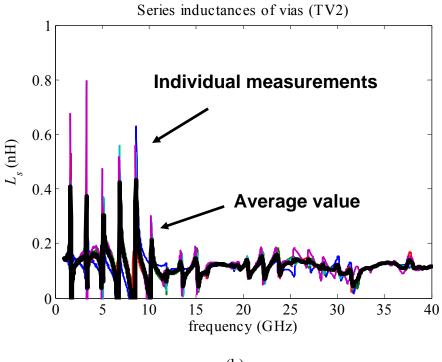

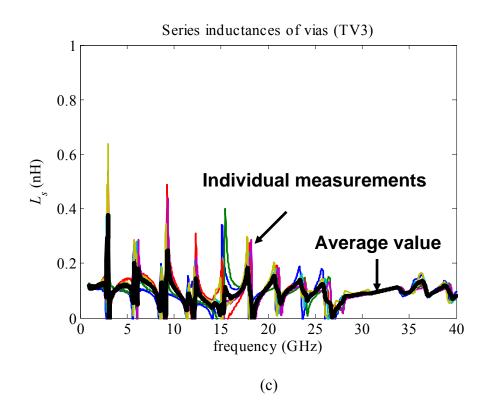

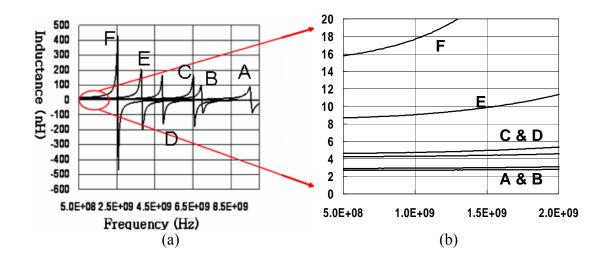

| Figure 3.9: Extracted series inductances (Ls) of (a) TV1, (b) TV 2, and (c) TV 3 from measurements    | the<br>50  |

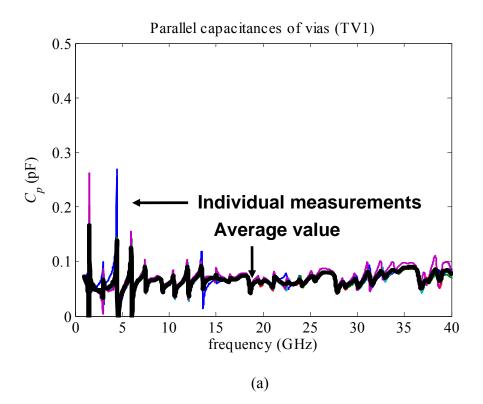

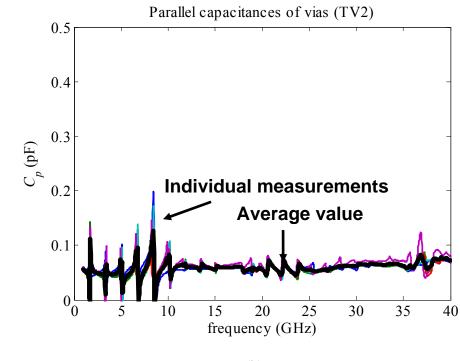

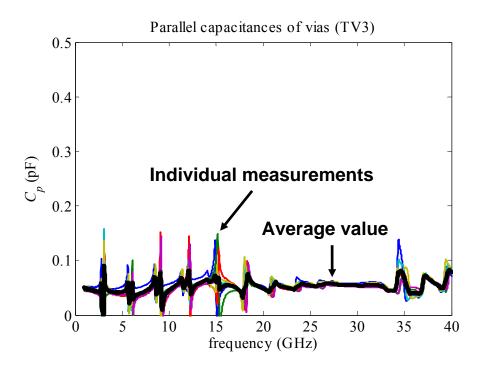

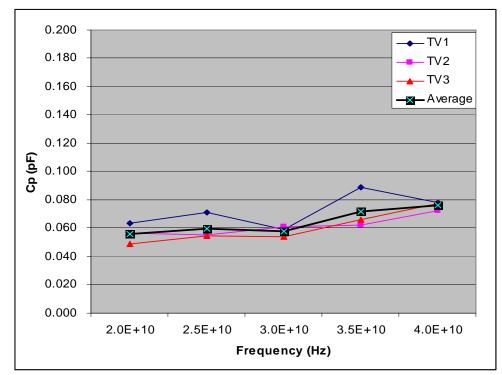

| Figure 3.10: Extracted parallel capacitances (Cp) of (a) TV1, (b) TV 2, and (c) TV 3 the measurements | from<br>52 |

| Figure 3.11: Model-to-hardware correlation of the S parameters for the entire structur                | re<br>53   |

| Figure 3.12: Model-to-hardware correlation of propagation constants                                   | 53         |

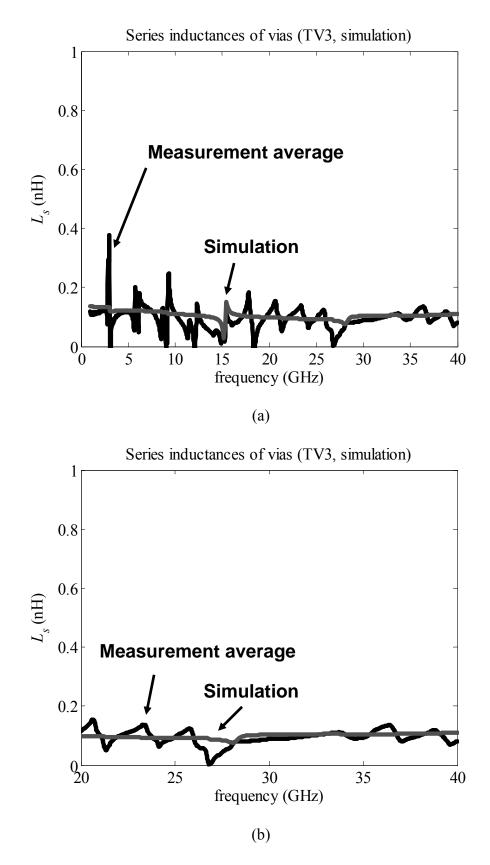

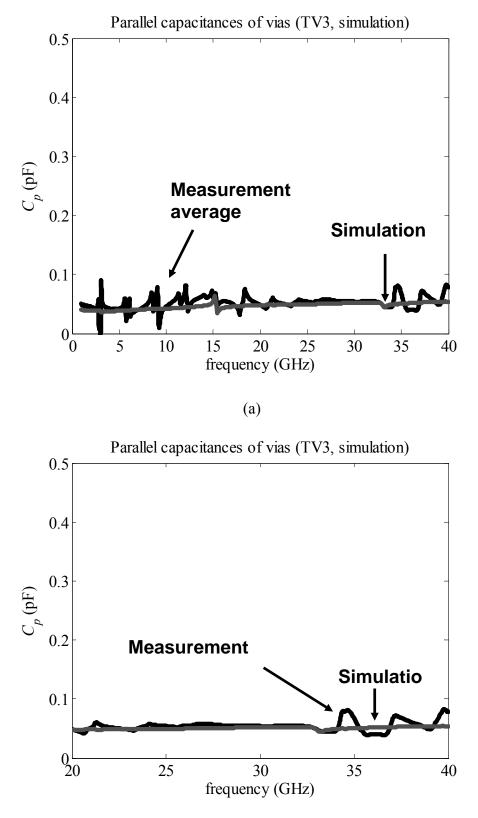

| Figure 3.13: Model-to-hardware correlation of Ls (a) 1-40 GHz and (b) 20-40 GHz                       | 54         |

| Figure 3.14: Model-to-hardware correlation of Cp (a) 1-40 GHz and (b) 20-40GHz                        | 55         |

| Figure 3.15: Equivalent circuit model of via                                                          | 56         |

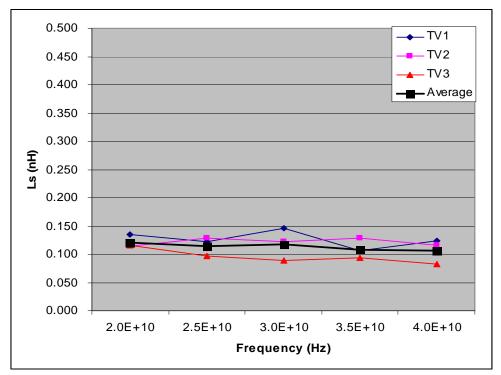

| Figure 3.16: Extracted series inductance (Ls) values for each TV and average value                    | 57         |

| Figure 3.17: Extracted parallel capacitance (Cp) values for each TV and average valu                  | e<br>57    |

| Figure 4.1: Cross-section of the balanced-LCP substrate                                               | 61         |

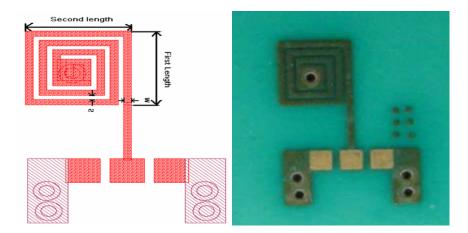

| Figure 4.2: Layout and photograph of the designed inductor                                            | 62         |

| Figure 4.3: Photograph of the TV1 (12" x 9")                                                                                                              | 62           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Figure 4.4: Measured results of Set 1 in TV1: (a) inductance profile, (b) sampled inductance, and (c) quality factor                                      | 64           |

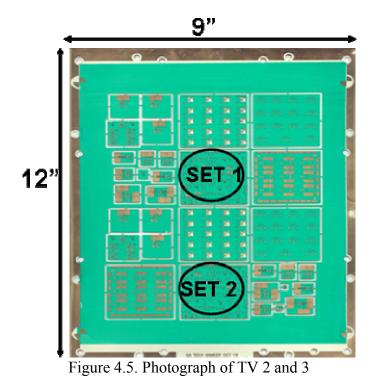

| Figure 4.5: Photograph of TV 2 and 3                                                                                                                      | 66           |

| Figure 4.6: X-ray of Inductor 3 in TV2                                                                                                                    | 67           |

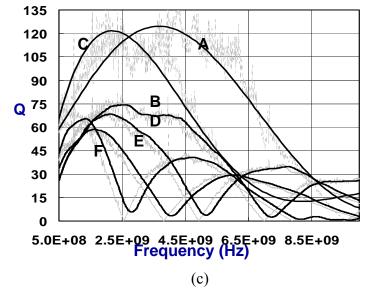

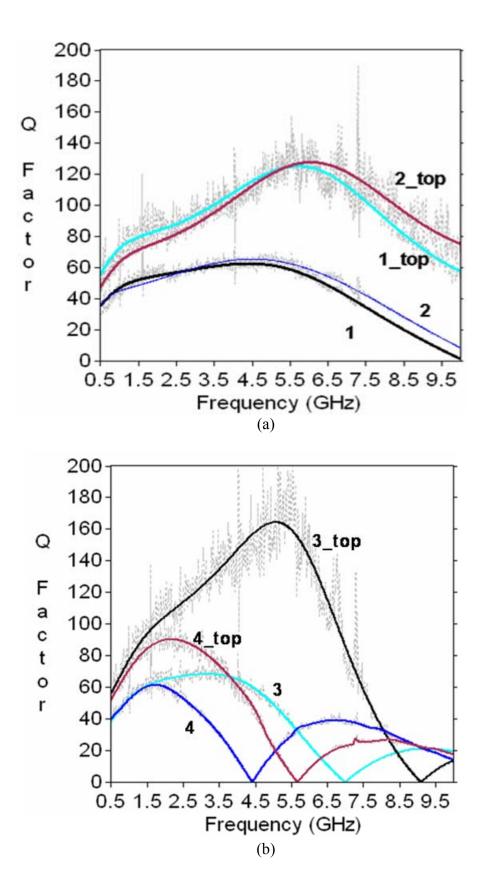

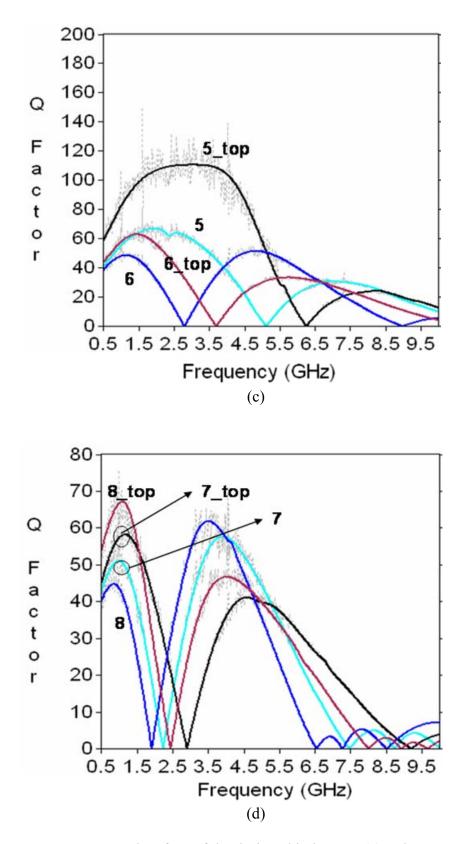

| Figure 4.7: Measurement results of Qs of the designed inductors: (a) Inductor 1 and 2<br>Inductor 3 and 4, (c) Inductor 5 and 6, and (d) Inductor 7 and 8 | 2, (b)<br>69 |

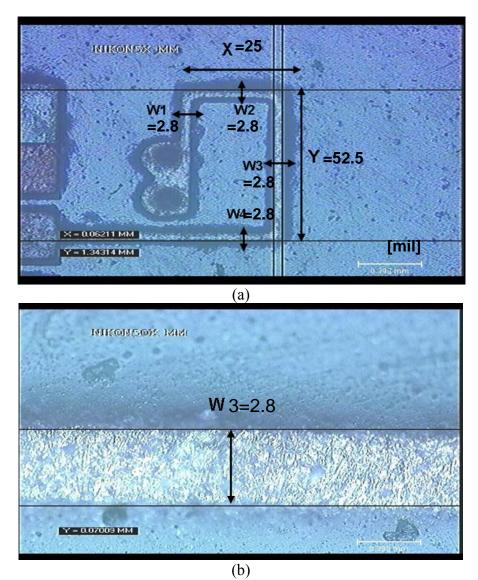

| Figure 4.8: (a) Photographs of Inductor 3_top (M1), and (b) W3 of TV3 Set 1                                                                               | 71           |

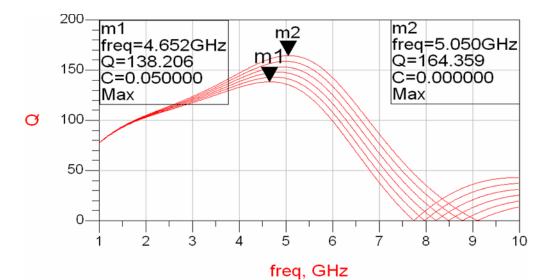

| Figure 4.9: Effects of the parasitic capacitances at input of Inductor 3_top of TV3, Se                                                                   | et 2<br>73   |

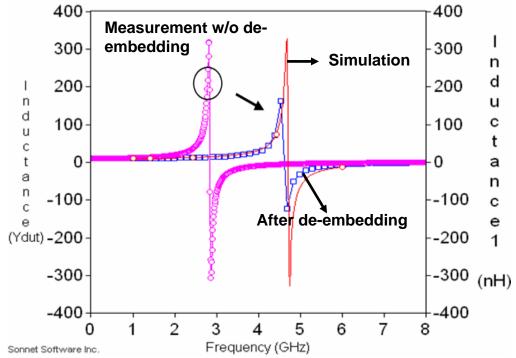

| Figure 4.10: Measured results after de-embedding and correlation with simulation res                                                                      | sults<br>75  |

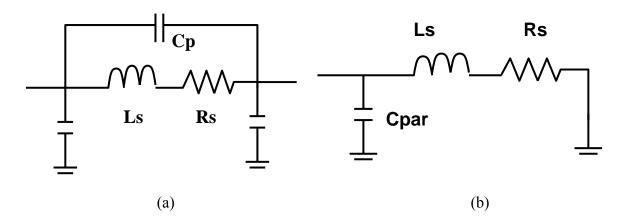

| Figure 4.11: Equivalent circuits of (a) two-port and (b)one-port inductor                                                                                 | 76           |

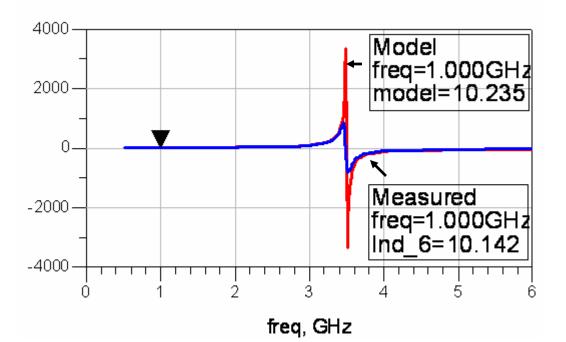

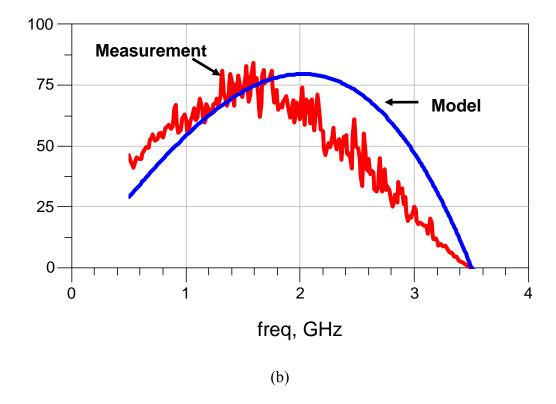

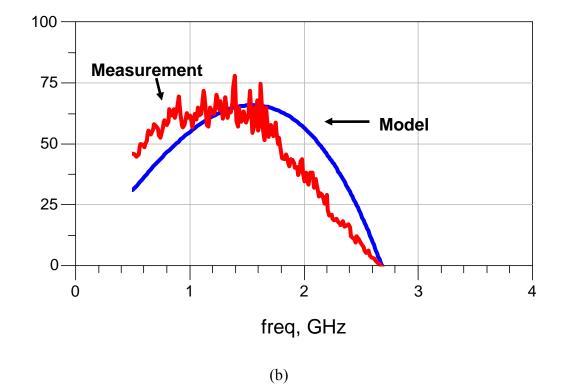

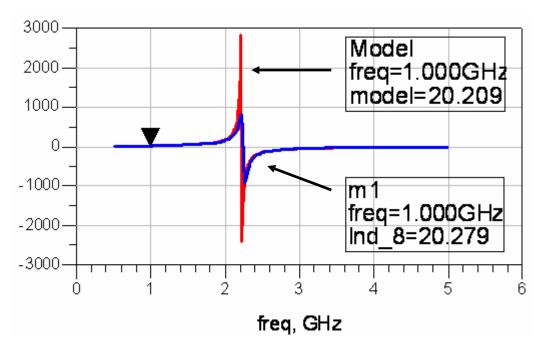

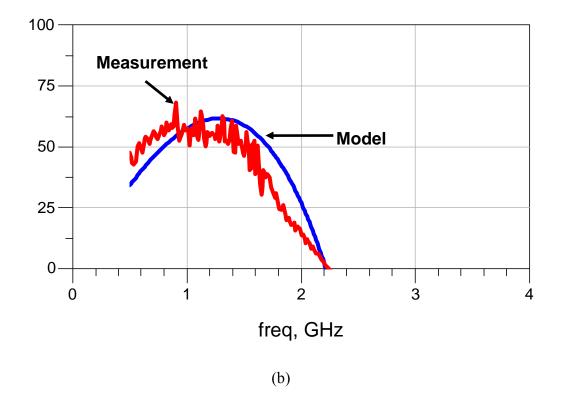

| Figure 4.12: Model-to-hardware correlations in (a) Inductance and (b) Q of Inductor TV2, Set1                                                             | 6 at<br>77   |

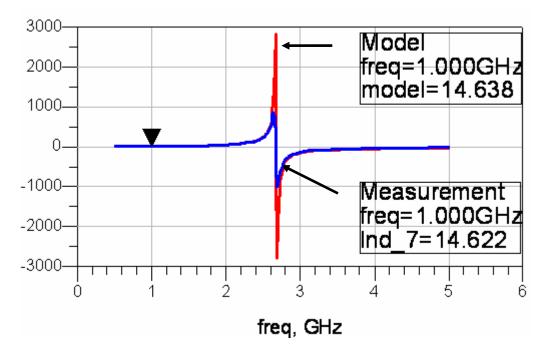

| Figure 4.13: Model-to-hardware correlations in (a) Inductance and (b) Q of Inductor TV2, Set1                                                             | 7 at<br>78   |

| Figure 4.14: Model-to-hardware correlations in (a) Inductance and (b) Q of Inductor TV2, Set1                                                             | 8 at<br>79   |

| Figure 4.15: 3D layout of the four types of 3D capacitors                                                                                                 | 81           |

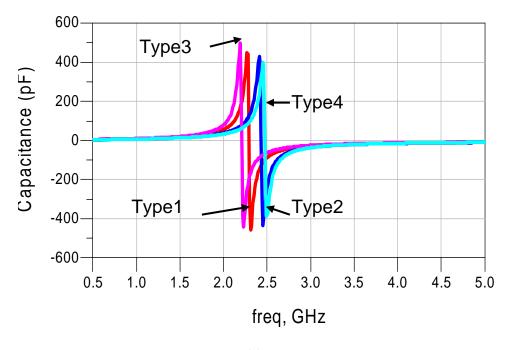

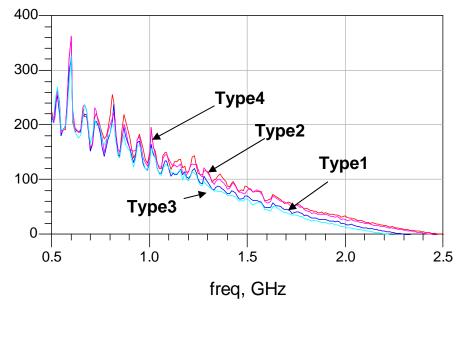

| Figure 4.16: Measurement results of the designed capacitors after de-embedding: (a) capacitance and (b) Q                                                 | 82           |

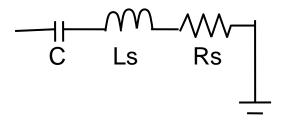

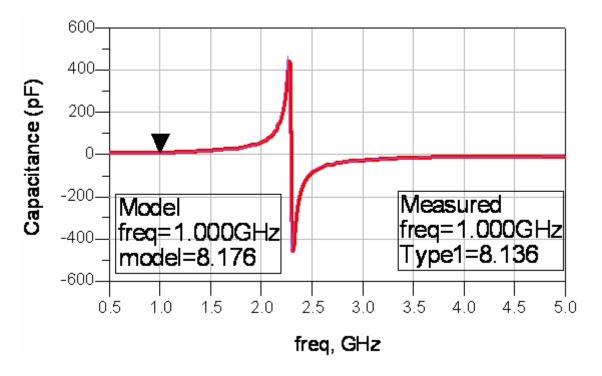

| Figure 4.17: Equivalent circuit of one-port capacitor                                                                                                     | 83           |

| Figure 4.18: Model-to-hardware correlations in (a) Capacitance and (b) Q of capacitor Type 1                                                              | or<br>84     |

| Figure 4.19: Model-to-hardware correlations in (a) Capacitance and (b) Q of capacitor<br>Type 2                                                           | or<br>85     |

|                                                                                                                                                           |              |

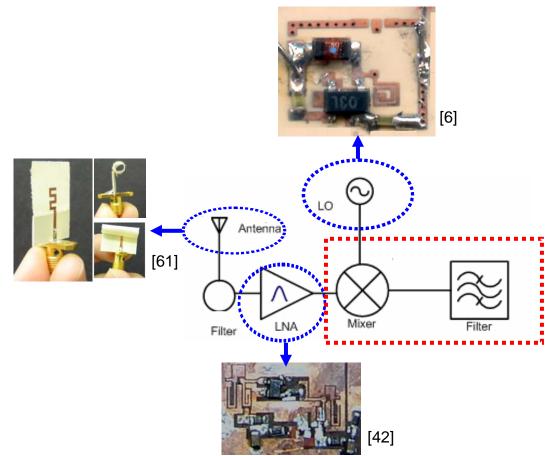

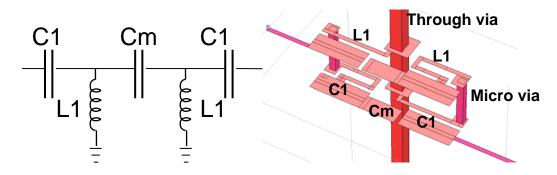

| Figure 5.1: RF Receiver Front end in inhomogeneous multi-layer LCP substrates                                                                             | 88           |

| Figure 5.1: RF Receiver Front end in inhomogeneous multi-layer LCP substrates<br>Figure 5.2: Cross-section of the three-layer LCP substrate               | 88<br>89     |

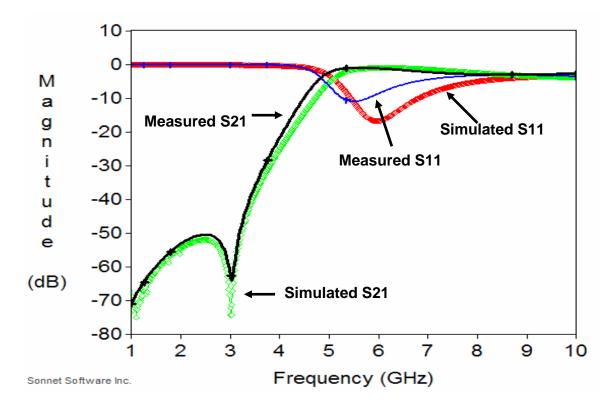

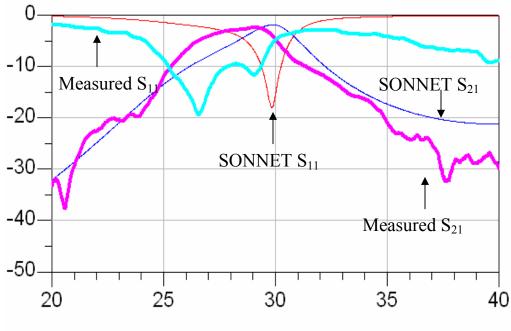

| Figure 5.4: Measured and simulated results of the C-band filter                                                                                                                           | 90         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 5.5: Schematic and photograph of a lumped balun                                                                                                                                    | 91         |

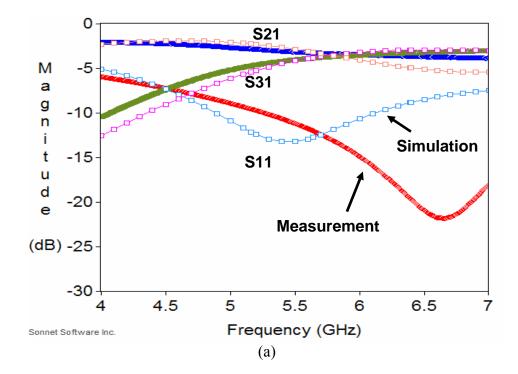

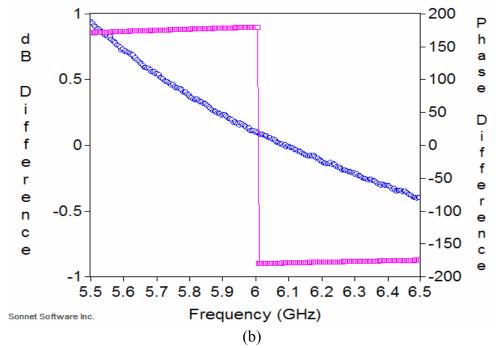

| Figure 5.6: Measured results of the lumped balun: (a) S parameters and (b) Phase and magnitude imbalances                                                                                 | d<br>92    |

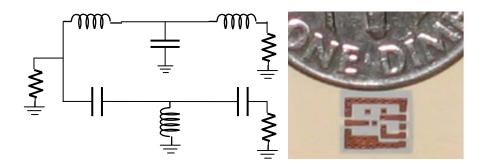

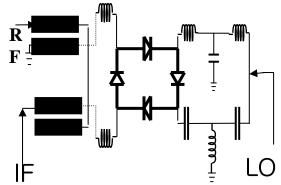

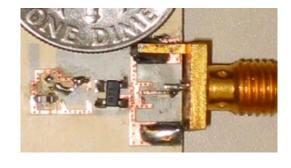

| Figure 5.7: Double balanced mixer: schematic and photograph                                                                                                                               | 93         |

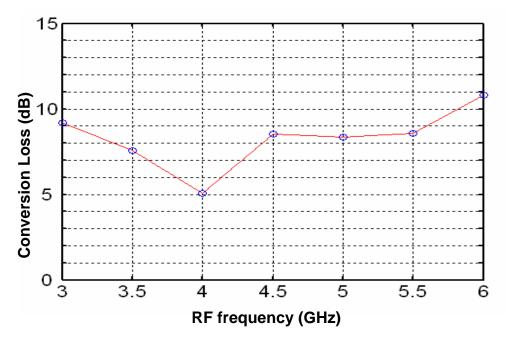

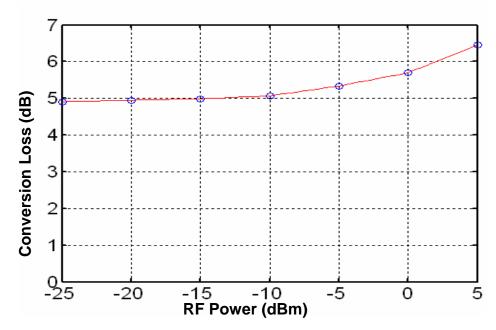

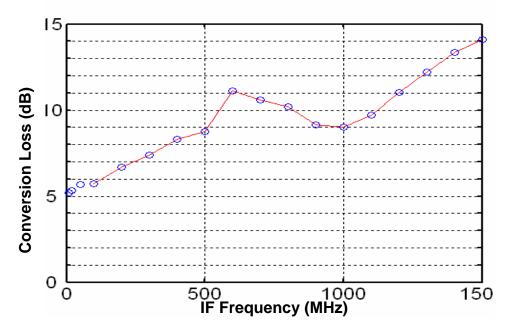

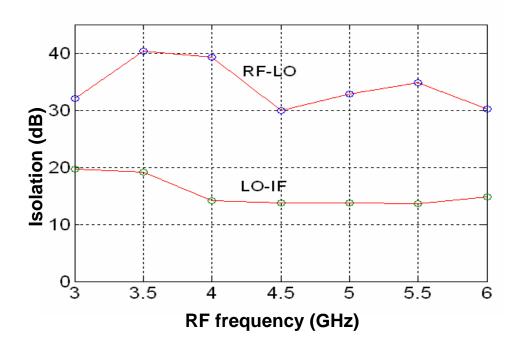

| Figure 5.8: Measured results of the double balanced mixer: Conversion Loss vs RF Frequency                                                                                                | 94         |

| Figure 5.9: Measured results of the double balanced mixer: Conversion Loss vs RF<br>Power                                                                                                 | 94         |

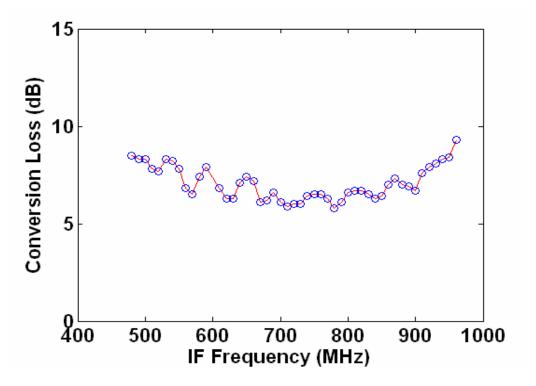

| Figure 5.10: Measured results of the double balanced mixer: Conversion Loss vs IF<br>Frequency                                                                                            | 95         |

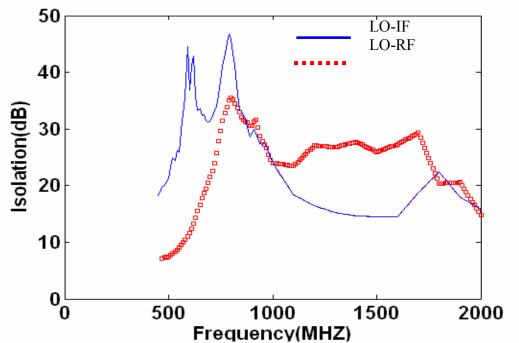

| Figure 5.11: Measured results of the double balanced mixer: Isolation vs RF Frequen                                                                                                       | ncy<br>95  |

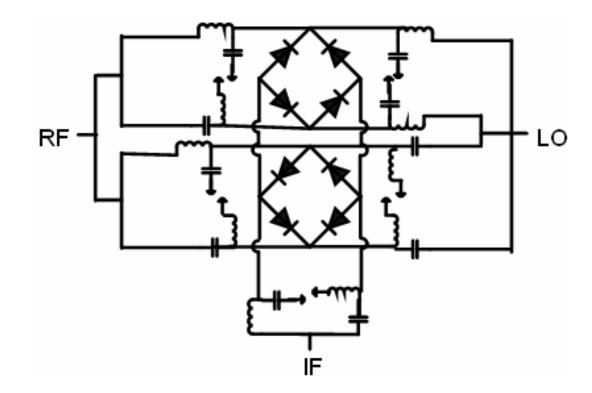

| Figure 5.12: Schematic of a double doubly balanced mixer                                                                                                                                  | 96         |

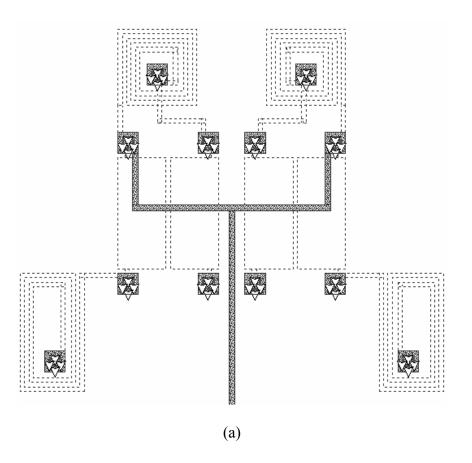

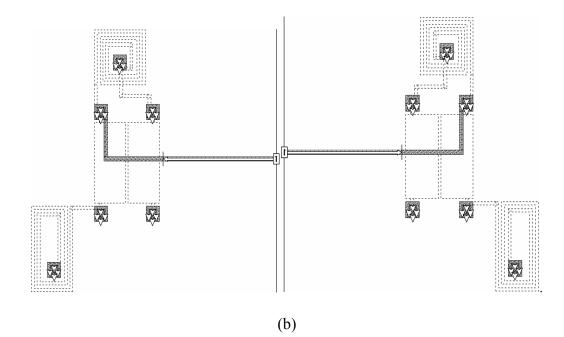

| Figure 5.12: Layout of LO balun and multi-section simulation in SONNET: (a) entire circuit and (b) multi-section simulation                                                               | e<br>98    |

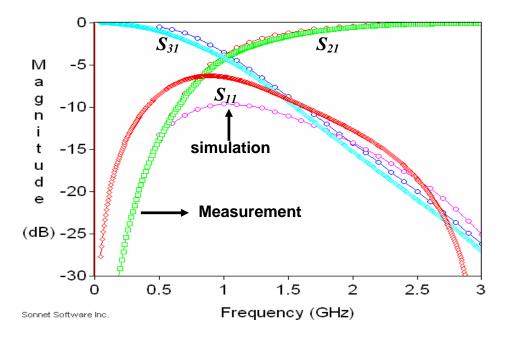

| Figure 5.13: Measured S parameter results of LO balun                                                                                                                                     | 99         |

| Figure 5.14: Measured S parameter results of IF balun                                                                                                                                     | 99         |

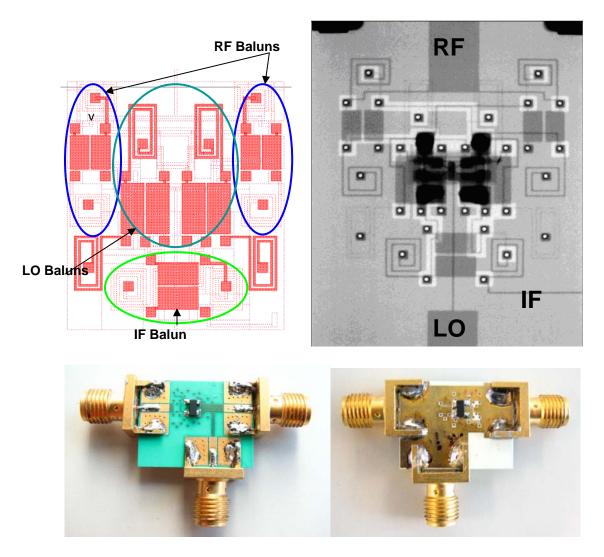

| Figure 5.15: Layout, X-ray and photograph of the fabricated doubly double-balanced mixer                                                                                                  | l<br>101   |

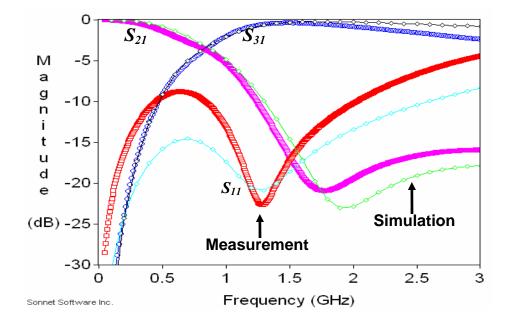

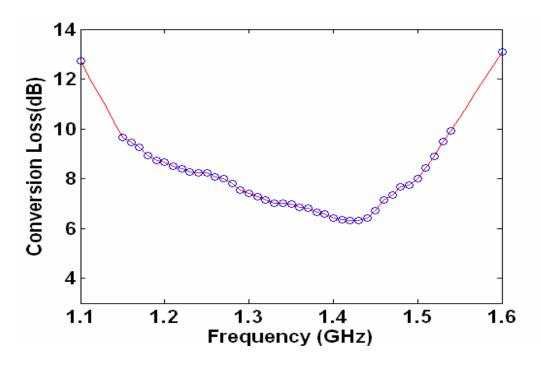

| Figure 5.16: Measured performance of a doubly double-balanced mixer with embedd<br>passive components: Conversion Loss vs. RF Frequency                                                   | led<br>102 |

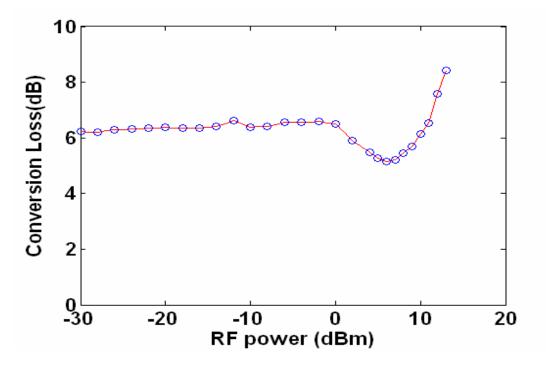

| Figure 5.17: Measured performance of a doubly double-balanced mixer with embedded passive components: Conversion Loss vs. RF Power                                                        | led<br>102 |

| Figure 5.18: Measured performance of a doubly double-balanced mixer with embedded passive components: Conversion Loss vs. IF Frequency                                                    | led<br>103 |

| Figure 5.19: Measured performance of a doubly double-balanced mixer with embedded passive components: Isolation vs. RF Frequency                                                          | led<br>104 |

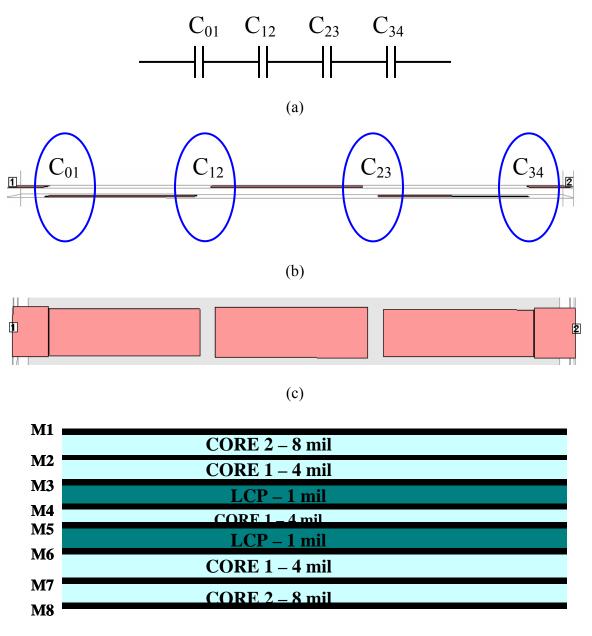

| Figure 5.20: Schematic and cross-section of a gap-coupled band-pass filter with a lay<br>in multi-layer LCP technology: (a) schematic, (b) cross section, (c) top vie<br>and (d) stack-up |            |

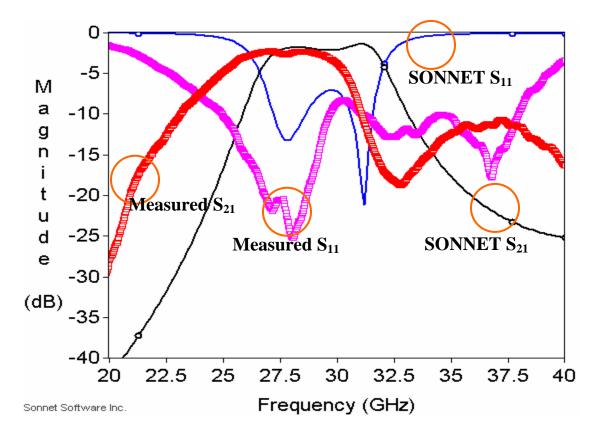

- Figure 5.21: Simulated and measured results of 30 GHz gap-coupled band-pass filter 108

- Figure 5.22: Model-to-hardware correlations of 30 GHz gap-coupled band-pass filter after TRL calibration 108

#### SUMMARY

The goal of the research in this dissertation is to design and characterize embedded passive components, interconnects, and circuits in inhomogeneous, multi-layer liquid crystalline polymer (LCP) substrates.

The attenuation properties of inhomogeneous multi-layer LCP substrates were extracted up to 40 GHz. This is the first result for an inhomogeneous LCP stack-up that has been reported. The characterization results show excellent loss characteristics, much better than FR-4-based technology, and they are similar to LTCC and homogeneous LCP-based technology.

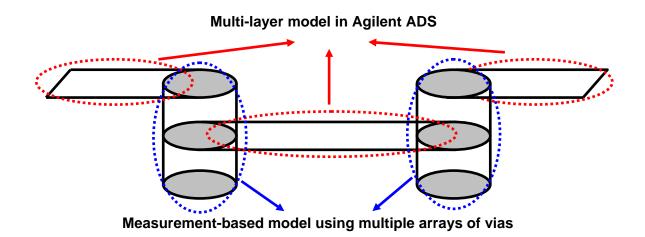

A two-port characterization method based on measurements of multiple arrays of vias is proposed. The method overcomes the drawbacks of the one-port and other two-port characterizations. Model-to-hardware correlation was verified using multi-layer model in Agilent ADS and measurement-based via model using arrays of the vias. The resulting correlations show that this method can be readily applied to other vertical interconnect structures besides via structures.

Comprehensive characterizations have been conducted for the efficient 3D integration of high-Q passives using a balanced LCP substrate. At two different locations from three different large M-LCP panels, 76 inductors and 16 3D capacitors were designed and measured. The parameters for the measurement-based inductor model were extracted from the measured results. The results validate the large panel process of the M-LCP substrate. To reduce the lateral size, multi-layer 3D capacitors were designed. The designed 3D capacitors with inductors can provide optimized solutions for more

efficient RF front-end module integration. In addition, the parameters for the measurement-based capacitor model were extracted.

Various RF front-end modules have been designed and implemented using high-Q embedded passive components in inhomogeneous multi-layer LCP substrates. A C-band filter using lumped elements has been designed and measured. The lumped baluns were used to design a double balnced-mixer for 5 GHz WLAN application and a doubly double-balanced mixer for 1.78 GHz CDMA receiver miniaturization. Finally, to overcome the limitations of the lumped component circuits, a 30 GHz gap-coupled band-pass filter in inhomogeneous multi-layer LCP substrates, and the measured results using SOLT and TRL calibrations have been compared to the simulation results.

## CHAPTER 1

## **INTRODUCTION**

The goal of the research in this dissertation is to design and characterize embedded passive components, interconnects, and circuits in inhomogeneous, multi-layer liquid crystalline polymer (LCP) substrates. To achieve this goal, three main tasks are performed: (1) the characterization of inhomogeneous multi-layer LCP stack-ups; (2) the development of measurement-based via characterization using periodic arrays of vias; and (3) the design and characterization of high-quality factor (Q) embedded passive components in inhomogeneous multi-layer LCP substrates for system-on-package (SOP) technology. In addition, to validate inhomogeneous, multi-layer LCP substrates as a promising SOP solution for RF and microwave applications, lumped and distributed RF circuits based on embedded passive components were designed, fabricated, and measured.

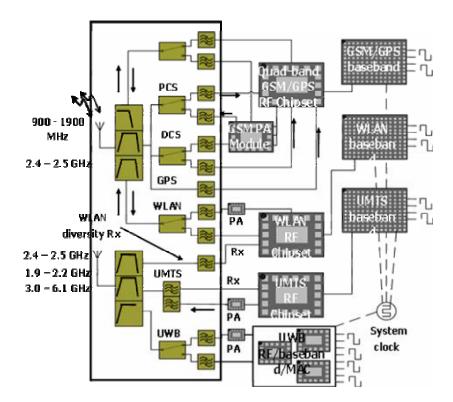

The trend in wireless systems is toward multi-functionality and higher miniaturization at higher speeds and lower cost. System-on-chip (SOC), system-in-package (SIP), and multiple-chip-module (MCM) are the system platforms that are currently being widely pursued by industry to accommodate such challenging tasks. Even though complementary metal–oxide–semiconductor (CMOS) technology can be the most cost-effective solution for certain digital and RF applications, it is not an optimal technology for entire RF and digital applications. As the number of components in a multi-band system has increased exponentially, as shown in Figure 1.1, new system integration platforms such as SOC and SOP are critical.

Figure 1.1. Multi-band system architecture

SIP and SOP have been known as attractive system platforms for wireless communication systems because they can provide benefits such as cost reduction, fast time to market, compact size, low profile, and high performance. SIP and SOP provide functionality in a package through the integration of passive components such as inductors [1], 0 capacitors, and resistors. Therefore, highly-integrated SIP and SOP can provide a multi-band system solution with a compact size and high performance.

To support new system architectures, new high-performance and high-frequency packaging materials also have been intensely researched. The first method for determining the feasibility of these packaging materials is to examine their performance. . An electrical characterization using various methods has been performed along with mechanical and thermal characterizations. For the microwave frequency range, extremely accurate calibration, de-embedding, measurement, and modeling methods are required to properly characterize new materials. Component and circuit realizations using new materials are another way to show their feasibility as high-frequency materials while minimizing size and cost and maximizing performance.

Section 1.1 addresses the advantages and disadvantages of SOP as a new mixedsignal system platform, and Section 1.2 presents the characterization of high-frequency materials. Section 1.3 reviews the characterization of vias, and Section 1.4 examines embedded passive technology. Section 1.5 presents embedded passive-based circuits up to the microwave frequency range, and finally, Section 1.6 provides the goal of this dissertation.

#### **1.1. System on Package**

SOC is an approach to incorporate every component using silicon technology. SOC can achieve very high density components, leading to size reduction. However, SOC has certain limitations, such as low-Q passive, substrate coupling, and testing. Using SOC alone, it is difficult to realize filters, duplexers, power amplifiers, and antennas. In addition, the nano-scale integration trend increases wiring resistance, leading to delay, causing increased latency in digital circuits.

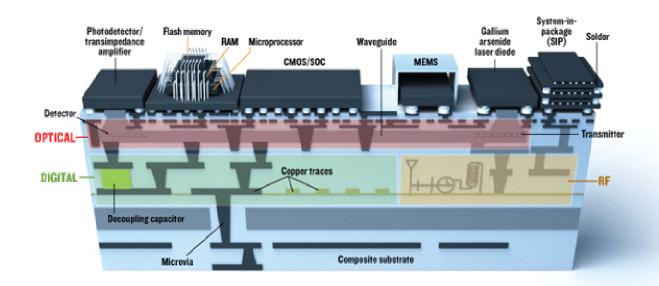

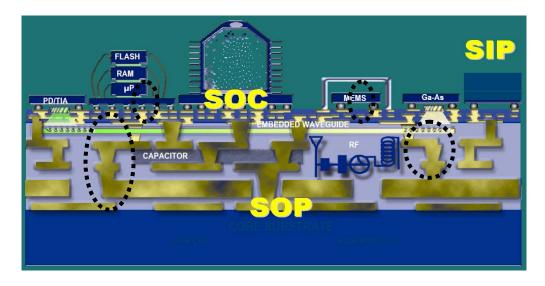

SOP combines the best of on-chip integration with the best of package integration for convergent and microminiaturized mobile systems. The SOP concept overcomes a number of the engineering limits of SOC. To reduce the delay latency in SOC technology, SOP can provide global wiring on the package. The wireless integration limits of SOC are also handled effectively through SOP. Figure 2 shows the state-of-theart mixed-signal SOP technology. RF components such as capacitors, filters, antennas, switches, and high-frequency and high-Q inductors are best fabricated in the package rather than on silicon. The highest Q factors of inductors reported on silicon are about 10-25, in contrast to 100-400 achieved in the SOP package. SOP has proven that it is an effective system with low cost, high performance, and small form factor [3], [4], [5], [6], [7], [8], and [9]. As shown in Figure 1.2, the high-Q embedded passive serves not only as RF components, including filters, baluns, and antennas, but also as low parasitic and low insertion loss interconnects using high-Q passives in the substrate.

Figure 1.2. The state-of-the-art mixed-signal SOP technology [10]

#### **1.2.** Characterization of High-frequency Materials

Embedded-passive technology plays a crucial role in the SOP platform because the passive component often occupies more than 80% of the real estate in the board, while the assembly cost accounts for around 70% of product assembly cost [11]. The embedded-passive technology makes an overall board size smaller, leading to higher throughput. It also helps improve the electrical performance because it eliminates soldering, which in turn improves system reliability while achieving both cost reduction and fast time to market by removing surface-mount devices (SMDs). Such advantages as lower cost, compactness, reliability, and higher performance make the embedded-passive technology a suitable package solution for systems as well as a key technology for higher integration.

Accordingly, the need for an extended supply of high-frequency packaging materials with high performance has become critical. Teflon and ceramic-based materials have been commonly used in high-frequency applications for many years [12]. Recently, the use of low-temperature, co-fired ceramic (LTCC) technology, or MCM-D technology [1], [3], [4], [5], [6], [7], and [8] in RF circuit design, has become very popular because of its advantages, including low loss, high integration density, and high reliability. LTCC, a multi-layer ceramic technology, enables the embedding of passive components into multiple layers while active elements are mounted on the surface layer. Although LTCC can provide high-Q passives, it cannot be used as a final substrate for systems. In addition, because of its coefficient of thermal expansion (CTE) mismatch with printed wiring board (PWB), it can lead to reliability issues.

In contrast, liquid crystalline polymer (LCP) can provide high-Q passives embedded in the packaging substrate [13]. However, unlike LTCC, LCP allows designers to achieve completely integrated wireless systems [4] since the LCP process is compatible with PWB processes such as FR-4. Therefore, LCP can ultimately become the final PWB. If used as a module, LCP has a similar CTE as PWB. To effectively integrate the entire system into a package, multi-layer integration is essential due to its vertical integration capability in addition to lateral integration. A typical multi-layer substrate is composed of homogeneous materials, including LCP. However, a homogeneous LCP process requires a higher temperature process (290 °C) than inhomogeneous LCP process (less than 200 °C). In addition, the difficulty in controlling the flow of bonding film causes registration problems, which limit the number of layers.

Other organic materials besides LCP also have been used for integration. Sanmina ZBC2000 in [14] provides improved electromagnetic interference (EMI), improved reliability, and improved manufacturability with lower cost. While LCP has a loss tangent of 0.002, ZBC 2000 has a loss tangent of 0.015, resulting in higher losses compared to LCP losses for embedded RF circuits. Dupont HK04 is an all polyimide, unfilled dielectric. Even though it provides excellent voltage resistance, its water absorption of 0.8% is much higher than that of LCP, which is 0.04% [15], and hence, Dupont HK04 causes large variations in RF performance. Since the circuit size decreases as operating frequency increases, the impact of water absorption on RF performance can be significant for most organic materials.

As an alternative solution to homogeneous LCP technology, inhomogeneous, multi-layer LCP-based substrates were developed, and they have demonstrated their manufacturability and high performance [1], [16], [17], [18], [19], and [20]. To fully utilize this new multi-layer inhomogeneous LCP substrate, a thorough characterization of the entire stack-up is required. Unlike the characterization of homogeneous multi-layer stack-ups such as LTCC, the characterization of inhomogeneous multi-layer LCP

substrates requires the characterization of embedded structures, including transmission lines, vias, inductors, and capacitors.

The characterization of LCP for multi-chip module technology was introduced in [21]. This approach was based on exploiting the barrier and dielectric properties of LCP to interconnect and package MMICs. For RF characterization, LCP films were bonded onto a 20-mil thick alumina substrate having metallization on one side and laminated with conventional 9-um copper foil. Transmission lines, CPW, cavity backed CPW, and ring resonator were characterized for extracting the electrical properties of this homogeneous LCP substrate. The attenuation of 0.3dB/cm was achieved at 35 GHz, which was low enough for packaging applications even though it is not low enough in comparison to Duroid. A 125-um homogeneous LCP BIAC copper clad laminate with 18um copper foil was characterized in [12].

A ring resonator was used to extract the relative dielectric constant at discrete frequency points up to 35 GHz in [22]. A 125um LCP using CPW structures up to 50 GHz was also characterized in [22]. Line-reflect-match (LRM) calibration was performed and the results showed attenuation of 1dB/cm at 50GHz, but only one CPW structure was used. The authors in [23] and [24] did more intensive characterization on a homogeneous LCP substrate. The authors in [24] used a 50um LCP with 18um copper foil on both sides to characterize attenuation and effective dielectric constant using a cavity-backed CPW structure up to 110 GHz. This work was extended by comparing the results with results using the cavity resonator method in [24]. Although the above mentioned characterizations are valid up to the millimeter-wave region, they only have characterized single-layered LCP substrate. This is because most research has been based on

homogeneous multi-layer LCP technology such as in [11], [25], and [26]. However, homogeneous multi-layer LCP has not been used for product manufacturing because of its processing difficulties and higher cost resulting from smaller board size and melt temperature.

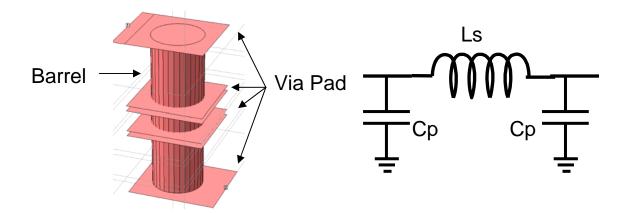

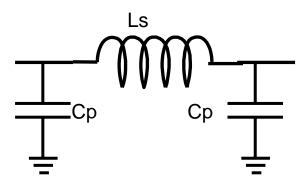

## **1.3.** Characterization of Vias

A via, a widely used vertical structure, connects separate layers in chips, packages, and boards. Figure 1.3 shows the vias in a system-on-package (SOP) structure, in which the package-level vias are circled. It consists of a barrel, a pad, and an anti-pad, as shown in Figure 1.4. The barrel is a structure that connects the layers with conductive materials, and the via pad connects the barrel to other traces or components. An anti-pad is a clearance between the via pad and the nearest metal on the layer.

Figure 1.3. The vertical interconnects in SOP

Figure 1.4. The structure of a via and its equivalent circuit model

Figure 1.4 also shows an equivalent circuit model composed of a series inductor representing the barrel inductance and parallel capacitors representing the capacitances between the pads and the ground. The approximate value of capacitance can be calculated from [27]:

$$C_{via} \approx \frac{1.41\varepsilon_r D_1 T}{D_2 - D_1} \text{ pF}, \tag{1-1}$$

where  $D_1$  is the diameter of the via pad,  $D_2$  is the diameter of the anti-pad, T is the thickness of the board, and  $\varepsilon_r$  is the relative dielectric constant. The approximate value of inductance can be calculated from [27]:

$$L_{via} \approx 5.08h[\ln(\frac{4h}{d}) + 1]_{\rm nH},$$

(1-2)

in which h is the via length and d is the barrel diameter with units of inches. The rule of thumb for the inductance is 25nH per inch for a 1mil diameter rod. The inductance is inversely proportional to the natural log of the diameter [28].

Importance of accurate modeling of vias increases as the operating frequency and data rates increase. Small parasitics in the signal path cause signal distortions that can lead to system failure. In [13], [29], and [30], the authors used 8 mil through holes for vertical connections because of easy processing and fast fabrication time, even though micro vias, the diameter of which is less than 4 mil, were available for inhomogeneous multi-layer LCP stack-ups. However, 8 mil through holes introduce unwanted parasitics to the precise high-frequency and high-speed circuits, leading to deviations in the responses between electromagnetic (EM) simulations and circuit-based simulations using Agilent Advanced Design System (ADS). The expected response therefore requires many iterations. To avoid time-consuming iteration in the EM simulation, both accurate modeling and the measurement of through holes are required.

Research on via characterization has focused on the modeling of vias using numerical methods such as the quasi-static and full-wave techniques. Although numerical methods can model and analyze vias, an EM solver can accurately model and optimize via structures more practically. In [31], the authors analyzed vias according to height, diameter, and ground openings using Maxwell Strata [32], a field solver based on the mixed potential integration equation. An equivalent circuit of a circular via in a stripline-to-stripline interconnect structure was modeled as a lumped inductance and a lumped capacitance. Then, the overall inductance and capacitance were obtained from the

simulated S parameters. Even though inductance and capacitance of the via were extracted, the simulated results were not confirmed with any measurement results.

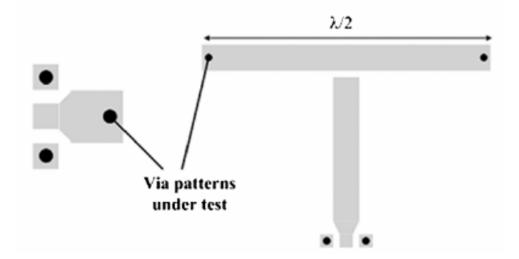

The measurement-based via modeling approach was used in [33]. In that paper, a half-wavelength T-resonator was used to characterize a single via structure up to 20 GHz, as shown in Figure 1.5. The pad capacitance was removed using an open dummy structure as in equations (1-3) and (1-4):

$$Y_{deemb} = Y_{meas} - Y_{open\_pad} \tag{1-3}$$

$$Z_{test\_via} = Z_{deemb} - 0.5 \cdot Z_{pad\_via} \tag{1-4}$$

Single, double, and quadruple vias were characterized up to 20 GHz. The above mentioned de-embedding method is not as accurate as the through-reflect-line (TRL) calibration method at higher frequencies.

Figure 1.5. T-resonator for characterizing single via

#### 1.4. Embedded Passive Technology; High-Q Passive Design

The improvements of Q-factor in LTCC-based, embedded-passive technology have been shown in [12], [34], and [35]. Vertically stacked helical inductors have a Q of 70 but need multiple layers (up to 19) to reduce the parasitic capacitance between spiral lines in [12] and [34]. The multi-layer inductor in [35] also achieved a Q of 60, but the placement of each spiral line of the inductor restricts effective utilization of the space in multi-layer RF SOP. In [36], the authors adopted an air cavity in multi-layer LTCC and showed a maximum Q of 51 and self-resonant frequency (SRF) of 9.1 GHz, while conventional spiral inductors showed a maximum Q of 43 and SRF of 8 GHz with an effective inductance of 2.7 nH. In [36], the air cavity reduced the capacitance between the spiral inductor line and ground plane, but it introduced additional processing, resulting in a cost increase and poor yield.

Although LTCC also can provide high-Q passives, it cannot be used as a substrate for systems because of its CTE mismatch. In addition, it has disadvantages, including wide line width and line-to-line spacing limitations, small processing area (typically 8" x 8"), and high cost per component. Finally, the high roughness of metal lines also causes high loss because of skin effect, causing high power consumption.

LCP can provide high-Q passives embedded in the packaging substrate [1], allowing the designer to achieve completely integrated wireless systems [4]. LCP-based technology using fewer layers can achieve a lower profile than LTCC does. Such a low-profile characteristic is critical in RF-digital integration because stacking RF and digital modules on top of each other is an attractive option.

Low loss, minimal dependency on temperature, and the near hermiticity of LCP make it an excellent candidate for RF applications [37]. In [24], a single-layer LCP showed excellent material characteristics up to 110 GHz.

#### 1.5. RF Front-end Modules using High-Q Embedded Passive Components

A filter is widely considered as an essential circuit in wireless communication and electronic systems. As a new standard is developed every year, the center frequency of new standards continues to increase, resulting in an increase of loaded Q in the filter. Such an increase in loaded Q places a lot of pressure on the unloaded Q of components, including inductors and capacitors. Mono-block and ceramic-cavity filters have been widely used for their high performance [11] because they can provide such high-Qs. Their benefits include sharp roll-off, low loss, and high performance [38]. However, they suffer from high manufacturing costs.

Rapid growth and advances in filter design result from the development of multilayer, high-frequency substrates such as LTCC and LCP, together with the development of embedded passive components. Much research has already been conducted for the RF filter design in LTCC [39] and [40], but relatively few designs have been researched and implemented in the LCP substrate using embedded passive components [1], [1], [3], [4], and [41].

The single-layer LCP substrate for RF front ends has been characterized and applied to various applications such as low-noise amplifiers (LNAs) [42], filters, baluns [5], and voltage-controlled oscillators (VCOs) [43].

Lumped-element circuits can achieve a very compact size while maintaining good performance up to 10 GHz. The disadvantage of this approach is that it is not feasible to design a filter operating over 10 GHz because most of the embedded passive components resonate below 10 GHz, resulting in a decrease in Q as the frequency approaches SRF. This phenomenon also limits embedded passive values less than 20 nH for inductors and less than 10 pF for capacitors.

However, distributed circuits can overcome this frequency limitation. Large size, the main disadvantage of distributed circuits, can be less of a problem than at low frequency because the electrical wavelength gets shorter as the frequency increases. Many researchers have started designing 30-60 GHz filters in LTCC and LCP [26], [44]. All of the designs utilize single or homogeneous multi-layer substrates. It is still questionable whether these designs are suitable for mass manufacturing with low cost.

#### **1.6. Completed Research**

The goal of the research is to design and characterize the embedded RF passive components and circuits in inhomogeneous multi-layer LCP substrates up to 40 GHz.

For the characterization of inhomogeneous multi-layer LCP substrates, the embedded transmission lines in the substrates were characterized and attenuation per unit length was extracted. To validate the inhomogeneous multi-layer LCP substrate as a high-frequency material, this study compared the characterized attenuation characteristics to other high-frequency materials such as FR-4, LTCC and the homogeneous LCP substrate. This is the first characterization of inhomogeneous multi-layer LCP substrates

up to 30 GHz that has been reported in the open literature. In contrast, the characterization of the homogeneous multi-layer configuration has been reported [24].

For the characterization of via holes in the inhomogeneous multi-layer LCP substrate, this research proposes measurement-based via-hole characterization methods using periodic arrays of via holes. The extracted parameters are series inductance and parallel capacitances, with excellent model-to-hardware correlations in S parameters, characteristic impedance, and propagation constant.

For the design and characterization of embedded high-Q passives, inductors and capacitors were designed and characterized in this stack-up, and various components at two locations in three 12"x9" panels were characterized to test the process variations. The model-to-hardware correlation was verified after de-embedding and calibration techniques were applied.

The designed high-Q passives were incorporated with lumped-element RF circuit designs. A 5 GHz filter in triple-balanced inhomogeneous LCP substrate was designed. The lumped baluns and mixers were designed, fabricated, and measured in triple- and double-balanced inhomogeneous multi-layer LCP substrates for frequency ranges from 780 MHz to 5.8 GHz.

Finally, for millimeter wave application, a 30 GHz distributed band-pass filter was designed in multi-layer LCP substrate. The designed band-pass filters showed excellent model-to-hardware correlation with TRL calibration.

A major contribution of this dissertation is the development of interconnect, via, and embedded passive models that have been characterized up to 40 GHz in inhomogeneous multi-layer LCP substrates.

- 15 -

### **1.7. Dissertation Outline**

The rest of this dissertation is divided into four main Chapters. Chapter 2 addresses the characterization of the material properties of inhomogeneous multi-layer LCP substrates. Section 3 presents the characterization methods of vias using periodic arrays of vias. Section 4 discusses the characterization of high-Q inductors and capacitors in inhomogeneous multi-layer LCP substrates and shows the scalability of Q by 3D integration. Section 5 presents designed lumped-element circuits such as filters, baluns, and mixers using high-Q embedded passive components, and a distributed gap-coupled 30 GHz band-pass filter. Finally, the conclusions and future work are discussed in Chapter 6.

## **CHAPTER 2**

# CHARACTERIZATION OF INHOMOGENEOUS LCP SUBSTRATES

### 2.1. Introduction

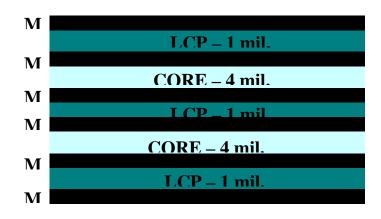

SOP provides an excellent system platform in that it can provide high-quality embedded passive components. The realization of high-Q embedded passives in SOP depends highly on the substrate material, and therefore, new high-frequency materials have been studied by several researchers. Inorganic (ceramic) substrates have been used for last few decades. It is high-k, low-loss and multi-layer solutions, and it can provide high-Q passives. However, it is relatively small-size process, 8" x 8", resulting in higher cost solution than large panel process. High-temperature requirement for the process and tape shrinkage are another drawbacks of the inorganic-based technology. Organic-based technology can be divided into homogeneous and inhomogeneous substrates. One promising high-frequency organic material is LCP, which presents excellent highfrequency electrical characteristics, including low loss and low-moisture uptake. One possible multi-layer LCP structure is homogeneous LCP, as shown in Figure 2.1.

| LCP 1 (315°C) |  |

|---------------|--|

| LCP 2 (290°C) |  |

| LCP 1 (315°C) |  |

| LCP 2 (290°C) |  |

| LCP 1 (315°C) |  |

Figure 2.1. Cross-section of the homogeneous LCP substrate with melt temperatures

It is composed of multiple LCP layers that have different melting temperatures that are stacked together. Homogeneous LCP can provide high-Q passive components and excellent electrical performance since it utilizes homogeneous substrates. In addition, thinner multi-layer solution is possible using thin LCP sheets. However, it is difficult to control the flow of the bonding film, which leads to registration problems. The registration problem limits the total number of layers in multi-layer solution. It is also not suitable for large-panel processing due to its manufacturability. As an alternative multi-layer structure, inhomogeneous multi-layer LCP substrates have proven to have excellent high-frequency properties with manufacturability related issues such as alignment tolerances. The inhomogeneous stack-ups are shown in Figure 2.2.

Figure 2.2. Cross-section of the inhomogeneous three-layer LCP substrate with melt temperatures

If the electrical properties of inhomogeneous LCP structure are to be fully exploited, conventional single-layer characterization, which was described in the previous chapter, cannot be used. Therefore, new research is needed to (1) characterize inhomogeneous multi-layer LCP substrates and (2) design and characterize high-Q embedded passives in inhomogeneous multi-layer LCP substrates. Furthermore, measurement-based rigorous multiple via-hole characterization has to be performed because virtually every vertical interconnect is made using vias or thru-holes in 3D SOP technology.

Figure 2.3 shows a comparison of the process flows of LCP-based technology and LTCC-based technology. LTCC uses 18 to 24 layers, which requires more processing time and cost. In contrast, because LCP-based technology uses three to six layers, it results in less processing time and cost. This also makes LCP-based technology more attractive for a low-profile mixed-signal system integration. In addition, LCP-based process has an advantage of the lower processing temperature of 177 to  $280^{\circ}$ C, while LTCC requires 450 to  $850^{\circ}$ C (see Figure 2.3).

Figure 2.3. Typical LTCC Process Flow

This chapter focuses on the characterization of inhomogeneous multi-layer LCP substrates. The embedded transmission lines in the multi-layer substrates were characterized and attenuation per unit length were extracted. To validate the inhomogeneous multi-layer LCP substrates as a high-frequency material, characterized attenuation characteristics were compared with other high-frequency materials such as FR-4, LTCC and homogeneous LCP stack-ups.

#### 2.2. Inhomogeneous LCP Technology

Both LCP and LTCC can consist of vertically integrated layers that allow for 3D integration. However, LCP can be integrated inside printed circuit boards (PCBs), while LTCC is not compatible with PCB processes. The LCP-based technology is available in single-layer [3], [4], [9], [37], three-layer [5], [6], [30] and balanced configurations[6], [13], [41]. The inhomogeneous multi-layer LCP structure was introduced in [30], in which a 5 GHz double-balanced mixer was designed using embedded passive components in a triple-layer inhomogeneous LCP substrate. The inhomogeneous multilayer LCP technology is a low-cost, low-temperature, high-performance, and large panel process alternative to homogeneous LCP substrates and therefore can be used for highfrequency applications. The inhomogeneous LCP technology was invented and developed at Georgia Tech. Packaging Research Center (PRC). In [13], high-Q embedded passive components were characterized in inhomogeneous multi-layer LCP substrates and showed a high-Q factor. Since inhomogeneous multi-layer LCP stack-ups utilize different core and pre-preg materials with 25 um-LCP layers in between, the characterization of such inhomogeneous LCP stack-ups are necessary, which is the focus of this chapter.

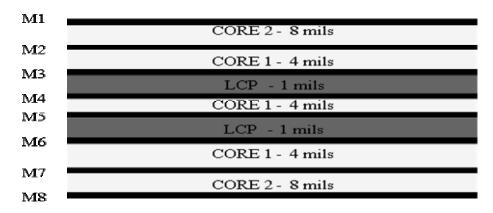

A three-layer LCP cross-section is shown in Figure 2.2. Three LCP layers are bonded together by lower-melt adhesives (CORE). This process combines 25 um thick LCP dielectrics with low-loss tangent glass-reinforced organic prepregs in a multi-layer stack-up. Based on this process, four to ten metal layer laminates can be fabricated. The LCP layers have a dielectric constant of 2.9 and a loss tangent of 0.002 at 10GHz and 23°C. The adhesive layers have a loss tangent of 0.0035 with a dielectric constant of 3.38. The top-metal layer (M1) of the cross-section can be used for SMDs and for high Q (>100) inductors in [11]. The thickness of the copper layers (M1-M8) is 17 um. The bottom-metal layer (M6) can be used as a microstrip ground. The ability to form microvias in the stack up represents an improvement in component and routing density.

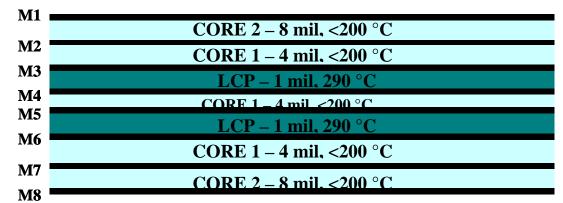

The cross-section of the balanced-LCP substrate is shown in Figure 2.4. Two balanced-LCP layers were circuitized separately, followed by the lamination of LCP layers using organic pre-preg layers. Thru-holes were mechanically drilled and plated to form interconnections. A liquid-photoimageable solder mask was used, and an electroless nickel immersion gold finish was plated on the bond pads and terminals. All processes, including lamination (<200°C), electroless and electrolytic copper plating, and dry film photoresists, are compatible with standard FR-4 and PCB processes. The panels were fabricated on 12" x 18" and 9" x 12" panels using large-area PCB tooling. The large-panel process results in low-cost implementation that can be easily scaled to an 18" x 24" panel for further cost reduction. Typically, ceramic or LTCC components are manufactured on a panel size of 8" x 8". The fabrication of components on 18" x 24" panels can yield more than 5,400 devices of 5mm x 5mm size, which results in more than

a ten-fold increase in number of components for a given board over ceramic-based processes.

Figure 2.4. Cross-section of two-layer balanced LCP substrate with melt temperature

The high-precision RF passive components in the LCP layers are packaged using laminate layers, providing mechanical strength and enhanced reliability. Unlike conventional PCB materials, the proprietary process technology utilizes organic dielectrics with extremely low moisture uptake comparable to ceramic dielectrics. Typical moisture uptake rates for the packaging materials are less than 0.05%, leading to ceramic-like near-hermetic packaging at organic PCB manufacturing costs. The fully-packaged substrate has CTE matched to the typical organic materials used in PCB technology such as FR-4 with CTE around 18-20ppm/°C.

The CTE match allows for large modules to be implemented with very high reliability. The material set can be adjusted to tailor the CTE of the package in the 3-20ppm/C range, resulting in expansion-matched packages and modules for various RF IC platforms, including Si CMOS, SiGe, and GaAs. IC assemblies, high-frequency electrical and full functional testings, and over-molding operations are performed on the sub-panels of 6" x 6" prior to dicing the individual modules. A novel and proprietary

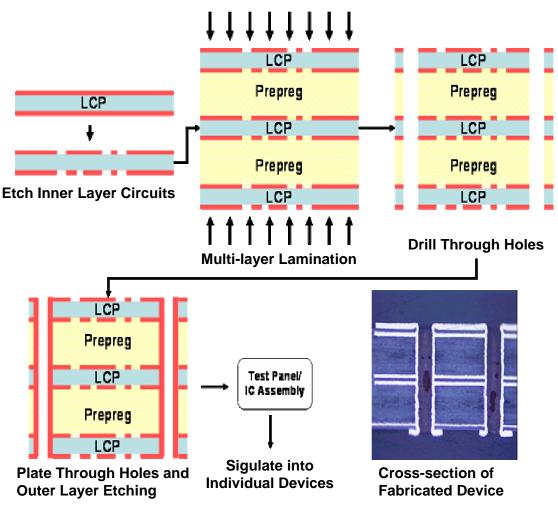

structure, developed as a part of this research, allows for the on-board RF shielding of each of the devices prior to singulation, in turn precludes the need for EMI cans, which increase both cost and size. This novel and patented approach results in higher performance with a much lower cost than ceramic-based technology [45]. Figure 2.5 shows the processing flow of multi-layer LCP technology.

Figure 2.5. Multiple LCP Layer Process Flow

### 2.3. Loss Characterization of Inhomogeneous LCP substrates

In Figure 2.4, the top metal layer (M1) of the cross-section can be used for surface

mount components while the bottom metal (M8) can be used for the microstrip ground layer. M2 and M7 have not been used in the design, but additional metal layers can be used as needed. Three different transmission lines of 214, 814, and 3214 mil were characterized in M3, M4, M5, and M6. Figure 2.6 shows x-rays of the designed embedded transmission lines. In M3 and M5, the ground clearances for the signal via are shown, and the line-width of the transmission lines decrease as lines are closer to the ground layers because the characteristic impedances of the lines decrease.

Figure 2.6. X-rays of the 214 mil transmission lines in M3, M4, and M5 in inhomogeneous multi-layer LCP substrates

To achieve 50  $\Omega$  characteristic impedance up to 40 GHz, each transmission line in M3 to M6 was simulated in full wave solver SONNET [46]. Short-open-load-through

(SOLT) calibration was conducted up to 40GHz with the Cascade 250 um GSG probes. S11 and S21 were measured using the Agilent PNA 8363B and the Cascade probe station. Figures 2.7 and 2.8 show the measured S11 and S21 of three fabricated embedded transmission lines with three different lengths on M3 and M5.

Figure 2.7 shows the signal flow graph of the measurement setup including input and output transition indicated as circles. The signal flow graph analysis below shows that the  $S_{21}$  of transmission lines with lengths of L1 and L2 (L1 $\neq$ L2) can be expressed as (2-1), and (2-2). The transmission line section of the structure can be expressed as (2-3).

$$S_{21,L1} = \frac{b_2}{a_1} = \frac{S_{21,IN} \cdot S_{21,DUT1} \cdot S_{21,out}}{1 - S_{22,IN} \cdot S_{21,DUT1} \cdot S_{22,out} \cdot S_{12,DUT1}}$$

(2-1)

$$S_{21,L2} = \frac{b_2}{a_1} = \frac{S_{21,IN} \cdot S_{21,DUT2} \cdot S_{21,out}}{1 - S_{22,IN} \cdot S_{21,DUT2} \cdot S_{22,out} \cdot S_{12,DUT1}}$$

(2-2)

$$S_{21, DUT1} = e^{-\gamma L1}, S_{21, DUT2} = e^{-\gamma L2}$$

(2-3)

To obtain the attenuation constant, (2-1), (2-2), and (2-3) can be combined such that:

$$e^{-\gamma(L2 - L1)} = \frac{S_{21, L2}}{S_{21, L1}} \cdot \left( \frac{1 - e^{-\gamma L1} \cdot S_{22, IN} \cdot S_{22, OUT}}{1 - e^{-\gamma L2} \cdot S_{22, IN} \cdot S_{22, OUT}} \right)$$

(2-4)

If  $|e^{-2\gamma L} \cdot S_{22, IN} \cdot S_{22, OUT}| \ll 1$  (assuming good match),

then,

$$e^{-\gamma(L2-L1)} = \frac{S_{21,L2}}{S_{21,L1}} \Rightarrow \alpha = real \left[ \frac{S_{21,L2}(dB) - S_{21,L1}(dB)}{L_2 - L_1} \right]$$

(2-5)

Figure 2.7. Signal flow graph of the measurement set up for embedded transmission lines

Attenuations per unit length can be extracted from equation (2-5). 250 um GSG pads were carefully designed to guarantee a good match between the probes and pads. A full wave solver, SONNET [46] was used to simulate the pads to minimize the return loss from the input and output pads.

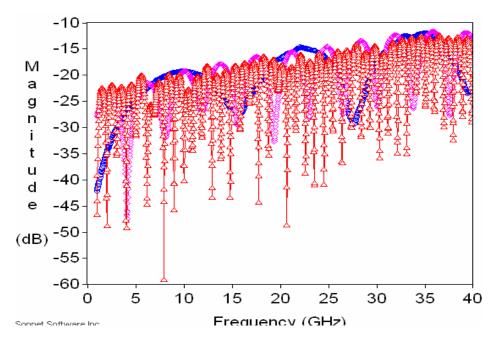

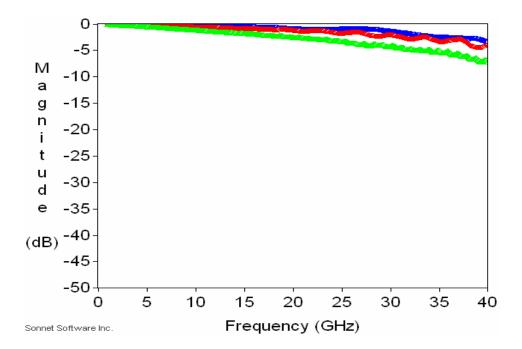

The top metal layer (M1) of the cross-section (See Figure 2.2) can be used for surface mount components, while the bottom metal (M8) can be used for the microstrip ground layer. M2 and M7 have not been used in the design, but additional metal layers can be used as needed. Three different-length transmission lines of 0.615 cm, 2.15 cm, and 8.12 cm, as shown in Figure 2.6, were characterized on metal layers M3 through M6. To ensure 50  $\Omega$  up to 40 GHz, each transmission line was simulated in SONNET [46]. The short-open-load-through (SOLT) calibration was conducted up to 30GHz with Cascade 250 um GSG probes. S11 and S21 parameters were measured using an Agilent PNA 8363B and a Cascade probe station. Figures 2.8 to 2.11 show the measured S11 and S21 of three fabricated embedded transmission lines with three different lengths on layers M3 and M5.

Figure 2.8. Measured S11 of the embedded transmission lines in M3

Figure 2.9. Measured S21 of the embedded transmission lines in M3

Figure 2.10. Measured S11 of the embedded transmission lines in M5

Figure 2.11. Measured S21 of the embedded transmission lines in M5

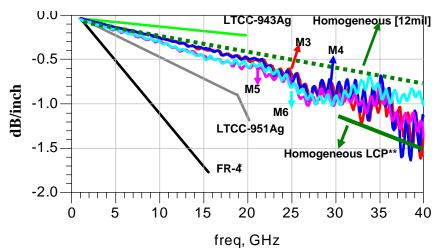

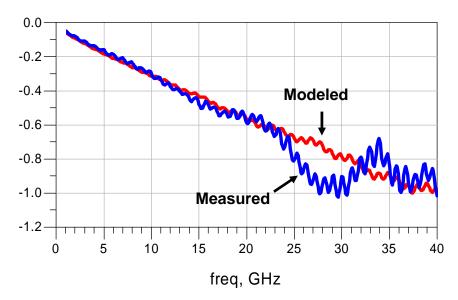

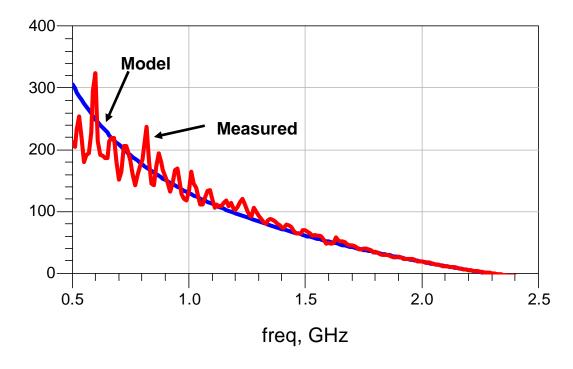

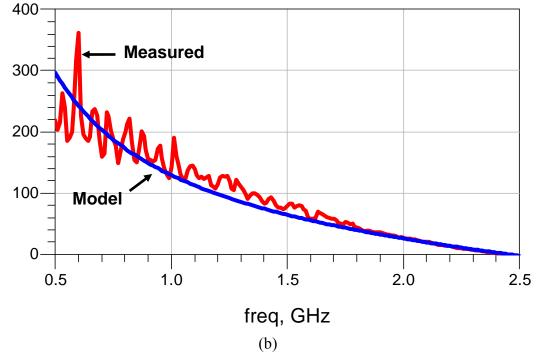

As shown in Figure 2.12, the attenuation per inch on each layer was extracted from equation (5) using the individual measurements of embedded transmission lines with three different lengths on M3-M6 layers in Figure 2.2. Figure 2.12 also shows the attenuation characteristics of other high-frequency materials, including FR-4 [47], homogeneous LCP substrate [24], Dupont 951 Ag and the Dupont 943 Low Loss Ag system [48]. The dotted line is the loss of the 12 mil homogeneous LCP substrate, which was interpolated from [24]. The measured attenuation characteristics are much better than FR-4, and compatible with LTCC and homogeneous LCP substrates.

Figure 2.12. Attenuation characteristics [dB/inch] of inhomogeneous multi-layer LCP substrates, compared with other high-frequency materials

#### 2.4. Model-to-hardware Correlation

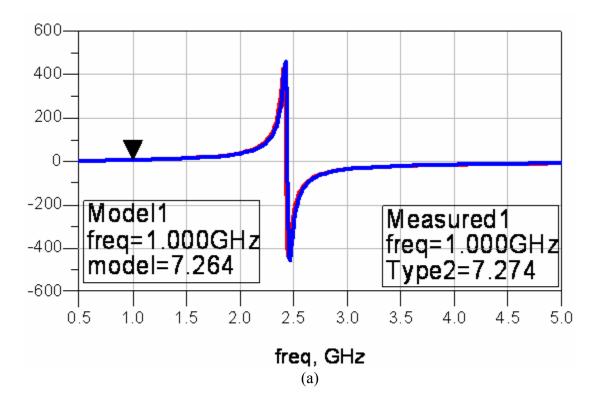

The extracted characteristics of the embedded transmission lines were compared to the model using multi-layer model in Agilent ADS, combined together with via model from the same stack-ups. The inductance and capacitance of the identical through via (30 mil long, 8mil diameter) were characterized using measurement-based methods utilizing multiple arrays of the vias from 20 to 40 GHz. The detailed method for via characterization is discussed in Chapter 3. The entire models for the embedded transmission lines are shown in Figure 2.13.

Since the embedded transmission lines were connected in the middle of the through via, the inductance values were scaled according to the corresponding length. The values of the inductances and capacitances for via connections are shown in Table 2.2. Figure 2.14 shows the model for via connections. A series inductor and parallel capacitor represent partial via connection between signal lines. The series inductance and capacitance to the ground represent the hanging via, connected to the ground through capacitive coupling. Figure 2.15 through 2.18 show the model-to-hardware correlation in loss characteristics for the transmission lines in M3 through M6.

Figure 2.13. Model of the embedded transmission lines including through-via connections

Figure 2.14. Model for the via interconnection between signal lines including parasitics to the ground because of the hanging portion of the through via

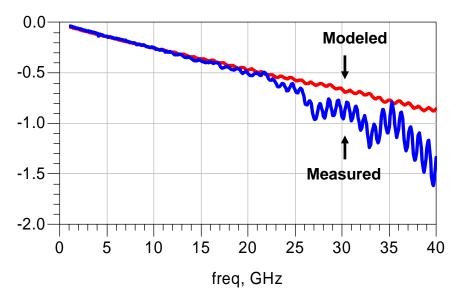

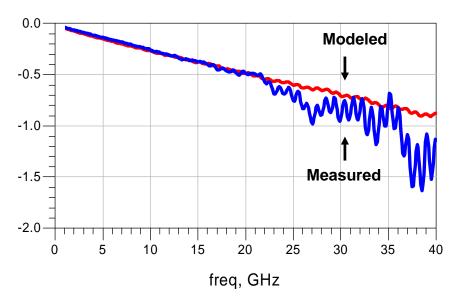

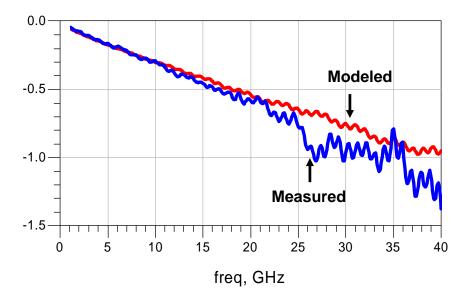

Excellent correlations are achieved between model and measured values up to 25 GHz. The deviations in the correlation after 25 GHz are resulted from model limitation, possible higher-order modes and surface roughness. At these high frequency, the height of the surface roughness are much profound compared to skin depth, the losses are significantly affected by the roughness of the conductor.

Figure 2.15. Model-to-hardware correlation of the transmission lines in M3

Figure 2.16. Model-to-hardware correlation of the transmission lines in M4

Figure 2.17. Model-to-hardware correlation of the transmission lines in M5

Figure 2.18. Model-to-hardware correlation of the transmission lines in M6

#### 2.5. Summary

The attenuation properties of inhomogeneous multi-layer LCP substrates were extracted up to 40 GHz. This is the first result for an inhomogeneous LCP stack-up that has been reported. The characterization results show excellent loss characteristics, much better than FR-4-based technology, and they are similar to LTCC and homogeneous LCP-based technology. This result confirms that such a stack-up, which is more easily manufacturable, can be used to design RF and microwave circuits.

Model-to-hardware correlation was verified using multi-layer model in Agilent ADS and measurement-based via model using arrays of the vias. To apply through via values to the designed via connections, the extracted inductor values were scale according to the corresponding length of vias between the transmission lines. This showed the excellent model-to-hardware correlation.

# **CHAPTER 3**

# MEASUREMENT-BASED TWO-PORT CHARACTERIZATION OF VERTICAL INTERCONNECTS

## **3.1. Introduction**

An increasing demand for multi-function, high-performance, and small formfactor systems necessitates highly-integrated systems. In addition, as demand for higher bandwidth has continued to increase, more fine-pitch arrays of interconnects between chip to chip, chip to substrate are required [49]. To support such a demand, a promising candidate is three-dimensional (3D) integration. In 3D integration, vertical interconnects play an important role for high-frequency and high-speed applications such as communication devices and high-performance computing systems, as shown in Figure 3.1.

Figure 3.1. Vertical interconnects in 3D integration using SOP

As operating frequencies and data rates increase, both horizontal and vertical interconnects should be controlled to maintain their electrical characteristics, including characteristic impedances, delays, and parasitics. Impedance mismatches and delays can affect signal quality by decreasing the edge rates in high-speed systems and by increasing the return loss in high-frequency circuits. However, in general, vertical interconnects have not been designed to precisely meet the rigid specifications because of routing complexities and processing limitations. Therefore, interconnects must be designed so that they are more accurately characterized, and the extracted parameters can be referenced for future designs. The characterization of more fine-pitch interconnects with low parasitics, such as G-helix in [49] is very challenging, but it is very critical at high-speed and high-frequency applications. Accurate method is required to properly extract the electrical properties of vertical interconnects such as vias and G-helix [49].

This chapter focuses on the development of the measurement-based characterization methods for vertical interconnects. The advantages and disadvantages of the current methods are addressed and measurement-based via characterization using arrays of vias are introduced in following section. The parasitic inductance and capacitance were extracted using this method and the extracted values were compared to the simulated values. Finally, the equivalent model and the extracted values are presented.

#### **3.1.1. One-Port Characterization**

The simplest characterization of vias is one-port characterization because it requires a single calibration for measurement. However, since it relies on S11 to extract the inductance and the capacitances, it is not suitable for very low impedance structures, including vias, power distribution networks (PDN), and de-coupling capacitors [28]. The

impedance of the device under test (DUT) can be obtained as (3-1):

$$S_{11} = \frac{Z_{DUT} - Z_0}{Z_{DUT} + Z_0} = \frac{Z_{DUT} - 50}{Z_{DUT} + 50}$$

(3-1)

For 1 $\Omega$  impedance,  $S_{11}$  is -0.35dB, which is acceptable, but for 0.1 $\Omega$  impedance,  $S_{11}$  is -0.035dB, which is close to the tolerance of calibration errors in most vector network analyzers (VNA).

#### **3.1.2. Two-Port Characterization**

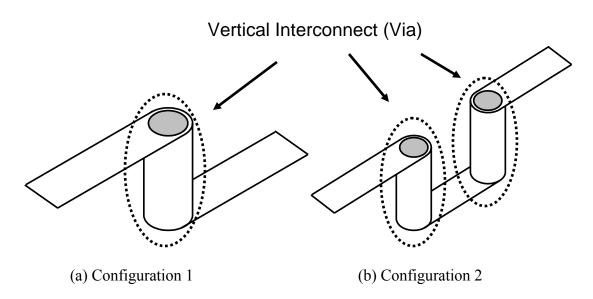

The previously discussed limitations of one-port characterization can be overcome using two-port characterization. Figure 3.2 shows two possible configurations of the two-port characterization of vias. Configuration 1, the simplest one, allows the effects of the input and the output transmission lines to be easily removed using either measurements or simulations. The drawback of this approach is that it requires two-sided probing that cannot be performed with a general probe station. This limitation can be overcome if Configuration 2 is used. This configuration is well suited for a conventional one-sided probe station. However, another limitation for one- and two port (both configurations) measurements for very low impedance structures is the parasitic effects on the overall characterization. Even with a very precise high-frequency probe, it still has a few residual, uncompensated inductances because of over-travel (downward movement of the probe after initial touchdown on the substrate) [28].

Figure 3.2. Two possible configurations for the two-port characterization of a vertical interconnect

Given an approximate inductance of 25 pH per mil for one-mil over-travel, the residual inductances of a 250 um GSG probe range from 75 to 125 pH since its calibration is based on an over-travel of 3 to 5 mil. The contact resistance varies from 0.01  $\Omega$  to 0.1  $\Omega$ , depending on the metallization of the probe tip and the surface of the pad [28].

During the characterization, the variation of the vias throughout the board must also be considered. That is, obtaining the average of the values from various vias in the one- and two-port characterization requires multiple measurements. In summary, oneand two-port characterizations have the following limitations.

- One-port characterization relies on S11 for the impedance measurement, which is not suitable for very low impedance measurements.

- (2) One- and two-port measurements suffer from uncompensated residual inductances and contact resistances even with the microprobe.

- (3) Two-port configuration 1 requires a two-sided probe station.

(4) Multiple one- and two-port characterizations are required for averaging the effects of process variations.

#### 3.2. Principle of a Measurement-Based Two-Port Via Characterization

To overcome the previously mentioned limitations in the characterization of the vertical interconnects, this chapter provides a measurement-based two-port via characterization. The proposed characterization of the vertical interconnects does not require two-sided probing, and it is a two-port characterization, which does not suffer from the same limitations as the one-port characterization. In addition, it can significantly reduce the effects of the variation of residual inductances and contact impedances by a single characterization of via arrays.

Several challenges in two-port characterization are removing the effects of measurement setup and extracting pure interconnect data. To address these issues, the proposed characterization method extracts interconnect data from a periodic network with an assumption that interconnects are manufactured within a reasonable tolerance.

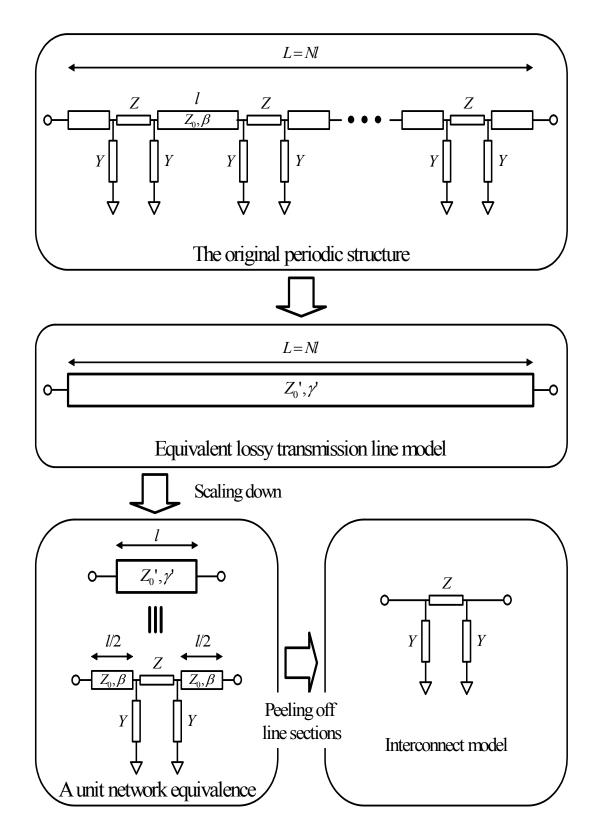

Figure 3.2 shows the general procedure for the proposed method. First, we convert a periodic structure composed of several identical unit networks, including unknown interconnects with two short line sections, to an equivalent lossy transmission line with the same length as that of the entire periodic network. A required measurement datum for this process is a transmission matrix (*ABCD* matrix) of the entire periodic network, which is modeled as a lossy transmission, as shown in Figure 3-4. That is,

$$A_{T} = \begin{bmatrix} \cosh \gamma' L & Z_{0}' \sinh \gamma' L \\ Y_{0}' \sinh \gamma' L & \cosh \gamma' L \end{bmatrix},$$

(3-2)

in which  $A_T = \begin{bmatrix} A_l & B_l \\ C_l & D_l \end{bmatrix}$  is the measured transmission matrix,  $\gamma', Z_0'$  are the propagation constant and the characteristic impedance of a lossy transmission line, and L = Nl is the total length of the entire network, which is N times as long as section length l. The equivalent lossy transmission line is specified by its virtual characteristic impedance and complex propagation constant. These electrical parameters are obtained from the following formula [50]:

$$Z_0^{'2} = B_t / C_t, (3-3)$$

$$\gamma' = \frac{1}{L} \ln \left| A_t + \sqrt{B_t C_t} \right| + j \frac{1}{L} \left[ \arg \left( A_t + \sqrt{B_t C_t} \right) + 2n\pi \right], \quad n = 0, \dots, N-1.$$

(3-4)

The condition according to which the real value of the characteristic impedance should be positive in passive structures enables us to select one from two possible solutions in (3-3). Among N solutions of the propagation constant in (3-4), to choose one physically reasonable solution, the interconnect or via network was assumed to have small resistive values such that the imaginary part of the propagation constant is close to the propagation constant of the uniform transmission line. Thus, the selected propagation constant minimizes:

$$\left|\operatorname{Im}(\gamma') - \beta\right| \tag{3-5}$$

where,  $\beta$  is the propagation constant of the uniform line, obtained from the following formula:

$$\beta = \frac{2}{l} \arg\left(\frac{1 - S_{22}}{S_{21}}\right)$$

(3-6)

In (3-6), the S-parameters are the measured or simulated data of a transmission line

section. The selection criteria finds physically reasonable parameters more effectively than solving the  $N^{\text{th}}$  order equation or using other numerical iterative procedures.

With the virtual parameters, the length of the equivalent line can be scaled down to that of the short line section, which becomes a lossy equivalent model of a single unit section. Since the unit contains two line sections with length of l/2, the transmission matrix of the unit section can be expressed as follows:

$$A_{l/2} \begin{bmatrix} 1 + YZ & Z \\ 2Y + ZY^2 & 1 + YZ \end{bmatrix} A_{l/2} = \begin{bmatrix} \cosh \gamma' l & Z_0' \sinh \gamma' l \\ Y_0' \sinh \gamma' l & \cosh \gamma' l \end{bmatrix}$$

(3-7)

where  $A_{l/2}$  is the transmission matrix of the l/2 line and the interconnect network is assumed as a symmetric  $\pi$ -network, parameters of which are described in Figure 3.3.

Finally, the short-line effects are peeled off from the lossy model in (3-7) to extract the frequency response data of the interconnect. From simulation or measurement in this step, we need additional data for the transmission line section with a length of l/2. Since  $\gamma'$  and  $Z_0'$  are already known values from (3-3) and (3-4), the unknown values in (3-7) are *Y* and *Z* of the interconnect model. They can be found from the following deembedding process:

$$\begin{bmatrix} 1+YZ & Z\\ 2Y+ZY^2 & 1+YZ \end{bmatrix} = A_{l/2}^{-1} \begin{bmatrix} \cosh \gamma' l & Z_0' \sinh \gamma' l\\ Y_0' \sinh \gamma' l & \cosh \gamma' l \end{bmatrix} A_{l/2}^{-1}$$

(3-8)

Generally, the left side matrix of (3-8) can be any other transmission matrix such as Tnetwork. In a typical case, in which the serial impedance is dominant in the interconnect model, we can simply find the value of *Z* from the (1, 2) element of the left side matrix in (3-8).

Figure 3.3. The procedure for characterizing vertical interconnect

#### 3.3. Design of Test Vehicle